#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/085257 A1

(43) International Publication Date 5 June 2014 (05.06.2014)

(51) International Patent Classification: G11C 29/02 (2006.01) G11C 16/06 (2006.01) G11C 11/56 (2006.01)

(21) International Application Number:

PCT/US2013/071505

(22) International Filing Date:

22 November 2013 (22.11.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

29 November 2012 (29.11.2012) 61/731,198 13/791,200 8 March 2013 (08.03.2013)

US US

- SANDISK **TECHNOLOGIES** (71) Applicant: [US/US]; Two Legacy Town Center, 6900 North Dallas Parkway, Plano, Texas 75024 (US).

- (72) Inventors: AVILA, Chris Nga Yee: 19839 Charters Avenue, Saratoga, California 95070 (US). DONG, Yingda;

1598 Valley Crest Drive, San Jose, California 95131 (US). MUI, Man Lung; 485 Ironwood Ter., Fremont, California 94539 (US).

- (74) Agents: GALLAGHER, Peter A. et al.; Davis Wright Tremaine LLP, 505 Montgomery Street, Suite 800, San Francisco, California 94111 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

[Continued on next page]

#### (54) Title: ADAPTION OF MEMORY OPERATION PARAMETERS ACCORDING TO PREDICTED VARIATIONS IN CELL DIMENSION

(57) Abstract: Configurable parameters may be used to access NAND flash memory according to schemes that optimize such parameters according to predicted characteristics of memory cells, for example, as a function of certain memory cell device geometry, which may be predicted based on the location of a particular device within a memory array.

FIG. 15

##

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

# ADAPTION OF MEMORY OPERATION PARAMETERS ACCORDING TO PREDICTED VARIATIONS IN CELL DIMENSION

#### **BACKGROUND**

[0001] This application relates to the operation of re-programmable non-volatile memory systems such as semiconductor flash memory which record data using charge stored in charge storage elements of memory cells.

5

10

15

20

25

30

[0002] Solid-state memory capable of nonvolatile storage of charge, particularly in the form of EEPROM and flash EEPROM packaged as a small form factor card, has recently become the storage of choice in a variety of mobile and handheld devices, notably information appliances and consumer electronics products. Unlike RAM (random access memory) that is also solid-state memory, flash memory is nonvolatile, and retains its stored data even after power is turned off. Also, unlike ROM (read only memory), flash memory is rewritable similar to a disk storage device. In spite of the higher cost, flash memory is increasingly being used in mass storage applications.

[0003] Flash EEPROM is similar to EEPROM (electrically erasable and programmable read-only memory) in that it is a non-volatile memory that can be erased and have new data written or "programmed" into their memory cells. Both utilize a floating (unconnected) conductive gate, in a field effect transistor structure, positioned over a channel region in a semiconductor substrate, between source and drain regions. A control gate is then provided over the floating gate. The threshold voltage characteristic of the transistor is controlled by the amount of charge that is retained on the floating gate. That is, for a given level of charge on the floating gate, there is a corresponding voltage (threshold) that must be applied to the control gate before the transistor is turned "on" to permit conduction between its source and drain regions. Flash memory such as Flash EEPROM allows entire blocks of memory cells to be erased at the same time.

[0004] The floating gate can hold a range of charges and therefore can be programmed to any threshold voltage level within a threshold voltage window. The size of the threshold voltage window is delimited by the minimum and maximum threshold levels of the device, which in turn correspond to the range of the charges

that can be programmed onto the floating gate. The threshold window generally depends on the memory device's characteristics, operating conditions and history. Each distinct, resolvable threshold voltage level range within the window may, in principle, be used to designate a definite memory state of the cell.

- [0005] In order to improve read and program performance, multiple charge storage elements or memory transistors in an array are read or programmed in parallel. Thus, a "page" of memory elements are read or programmed together. In existing memory architectures, a row typically contains several interleaved pages or it may constitute one page. All memory elements of a page are read or programmed together.

- 10 [0006] Nonvolatile memory devices are also manufactured from memory cells with a dielectric layer for storing charge. Instead of the conductive floating gate elements described earlier, a dielectric layer is used. Such memory devices utilizing dielectric storage element have been described by Eitan et al., "NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol. 21, 15 no. 11, November 2000, pp. 543-545. An ONO dielectric layer extends across the channel between source and drain diffusions. The charge for one data bit is localized in the dielectric layer adjacent to the drain, and the charge for the other data bit is localized in the dielectric layer adjacent to the source. For example, United States patents nos. 5,768,192 and 6,011,725 disclose a nonvolatile memory cell having a 20 trapping dielectric sandwiched between two silicon dioxide layers. Multi-state data storage is implemented by separately reading the binary states of the spatially separated charge storage regions within the dielectric.

#### SUMMARY OF THE INVENTION

[0007] Examples of the present invention relate to configurable parameters used to access memory arrays and to schemes for optimizing such parameters according to predicted characteristics of memory cells, for example, as a function of certain memory cell device geometry, which may be predicted based on the location of a particular device within a memory array. In 3-dimensional memory arrays, such as 3-D NAND, cell geometry may vary in a predictable manner according to distance from the substrate. Parameters may be configured to compensate for such variation.

[0008] An example of a method of operating a charge-storage memory cell array

includes: identifying a pattern of variation of at least one memory cell dimension within the charge-storage memory cell array; determining a first set of parameters to use in accessing a first plurality of memory cells based on the at least one memory cell dimension of the first plurality of memory cells; determining a second set of parameters to use in accessing a second plurality of memory cells based on the at least one memory cell dimension of the second plurality of memory cells, the second set of parameters including at least one parameter that is different from the first set of parameters; subsequently accessing the first plurality of memory cells using the first set of parameters; and accessing the second plurality of memory cells using the second set of parameters.

5

10

15

20

25

30

[0009] The at least one memory cell dimension may be a diameter of a cylindrical memory hole. The charge-storage memory cell array may be a three-dimensional memory array, the first plurality of memory cells may be located in a lower portion of the three-dimensional memory array, the second plurality of memory cells may be located in an upper portion of the three-dimensional memory array, and the identified pattern of variation may indicate that the diameter of the cylindrical memory hole is greater in the second plurality of memory cells than in the first plurality of memory cells. The at least one parameter that is different may be a voltage that is applied to program memory cells. The at least one parameter that is different may be a number of voltage pulses used to program memory cells. The at least one parameter that is different may be a read voltage that is used to read memory cells. The at least one parameter may be an erase voltage that is used to erase memory cells. A write-erase cycle count may be maintained for blocks of the charge-storage memory array and the first and second sets of parameters may be updated according to the write erase cycle counts. The first set of parameters may be updated according to a first update scheme and the second set of parameters may be updated according to a second update scheme that is different from the first update scheme.

[0010] An example of a charge-storage memory cell array includes: an array of memory cells, each memory cell having a memory cell dimension, the memory cell dimension having a pattern of variation across the array of memory cells; and memory access circuits that access memory cells of the array of memory cells according to access parameters, the memory access circuits having a first set of parameters for

5

10

15

20

25

accessing a first plurality of memory cells and a second set of parameters for accessing a second plurality of memory cells, the second set of parameters including at least one parameter that is different from the first set of parameters, the first plurality of memory cells and the second plurality of memory cells defined according to the pattern of variation.

[0011] The charge-storage memory cell array may be a three-dimensional memory array. The charge-storage memory cell array may be a three-dimensional NAND memory array which includes a plurality of NAND strings that extend vertically in a direction that is perpendicular to a substrate surface. The pattern of variation across the array of memory cells may be a pattern of variation of the memory cell dimension according to vertical distance from the substrate surface. The memory cell dimension may be a diameter of an opening that extends vertically through word lines with a channel extending vertically through the opening. A write-erase cycle count circuit may maintain write-erase cycle counts for blocks in the charge-storage memory cell array and update access parameters according to write-erase cycle counts. The write-erase cycle count circuit may have a first update scheme for updating the first set of parameters and a second update scheme for updating the second set of parameters.

[0012] Various aspects, advantages, features and embodiments of the present invention are included in the following description of exemplary examples thereof, which description should be taken in conjunction with the accompanying drawings. All patents, patent applications, articles, other publications, documents and things referenced herein are hereby incorporated herein by this reference in their entirety for all purposes. To the extent of any inconsistency or conflict in the definition or use of terms between any of the incorporated publications, documents or things and the present application, those of the present application shall prevail.

## BRIEF DESCRIPTION OF THE DRAWINGS

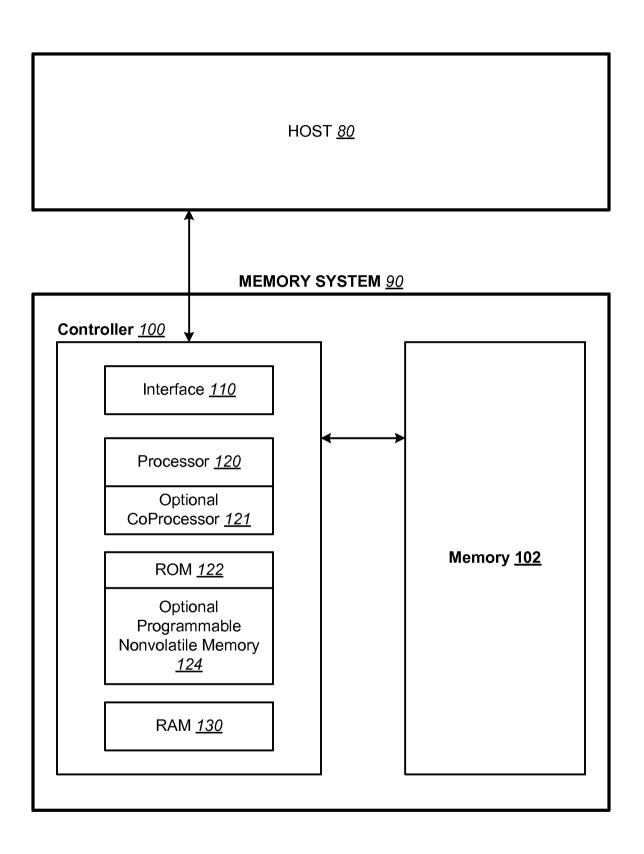

[0013] FIG. 1 illustrates schematically the main hardware components of a memory system suitable for implementing the present invention.

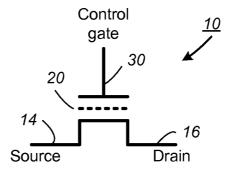

[0014] FIG. 2 illustrates schematically a non-volatile memory cell.

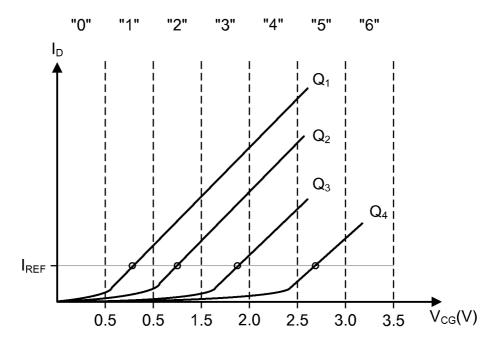

30 [0015] FIG. 3 illustrates the relation between the source-drain current  $I_D$  and the

control gate voltage  $V_{CG}$  for four different charges Q1-Q4 that the floating gate may be selectively storing at any one time at fixed drain voltage.

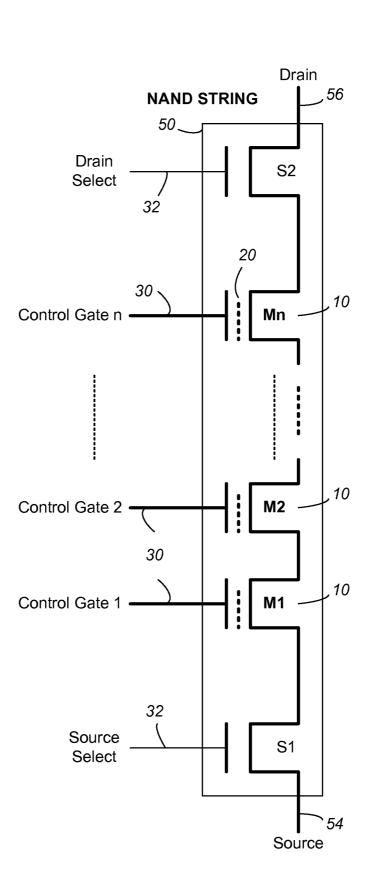

- [0016] FIG. 4A illustrates schematically a string of memory cells organized into a NAND string.

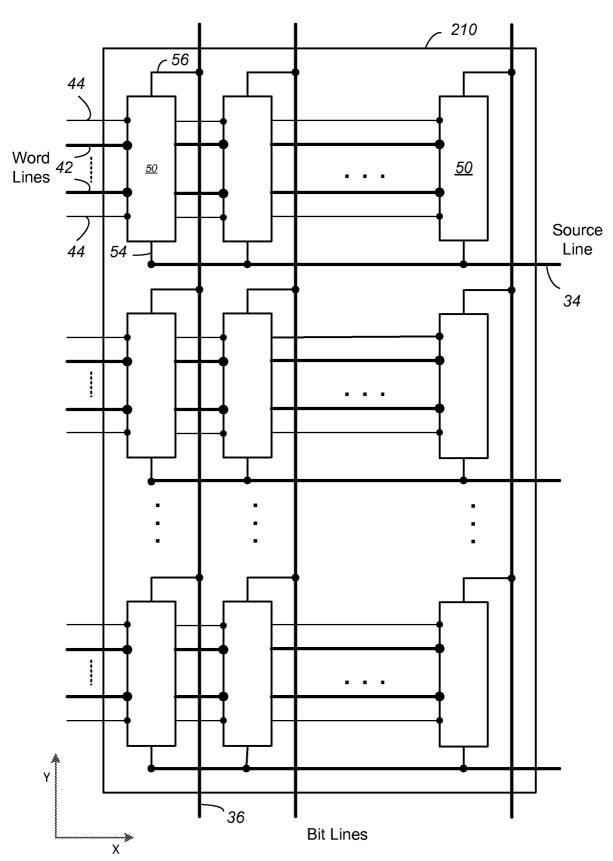

- 5 [0017] FIG. 4B illustrates an example of a NAND array 210 of memory cells, constituted from NAND strings 50 such as that shown in FIG. 4A.

- [0018] FIG. 5 illustrates a page of memory cells, organized in the NAND configuration, being sensed or programmed in parallel.

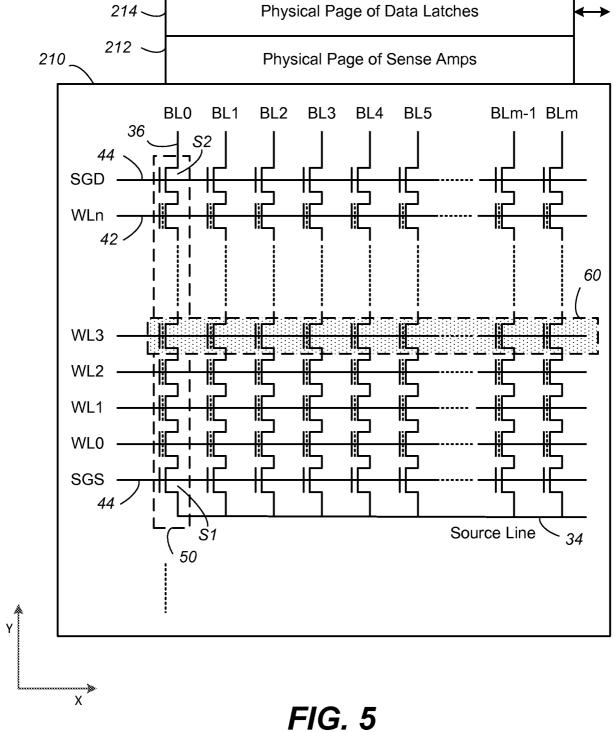

- [0019] FIGs. 6A 6C illustrate an example of programming a population of 4-state memory cells.

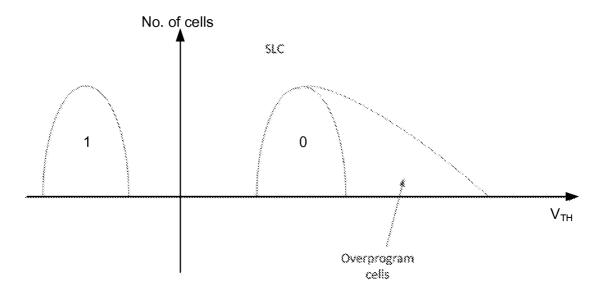

- [0020] FIG. 7 illustrates an example of overprogramming in SLC memory

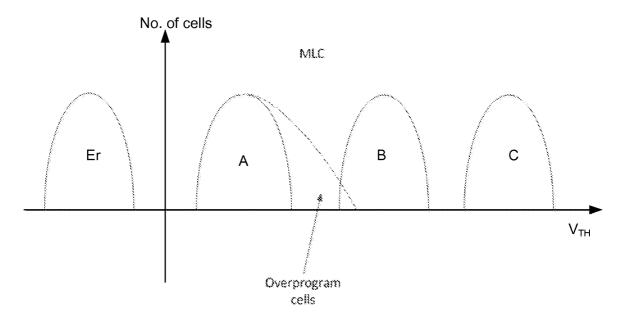

- [0021] FIG. 8 illustrates an example of overprogramming in MLC memory.

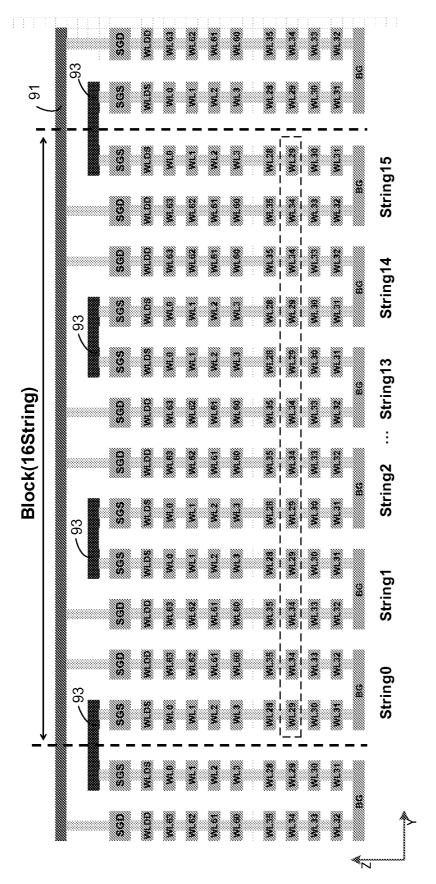

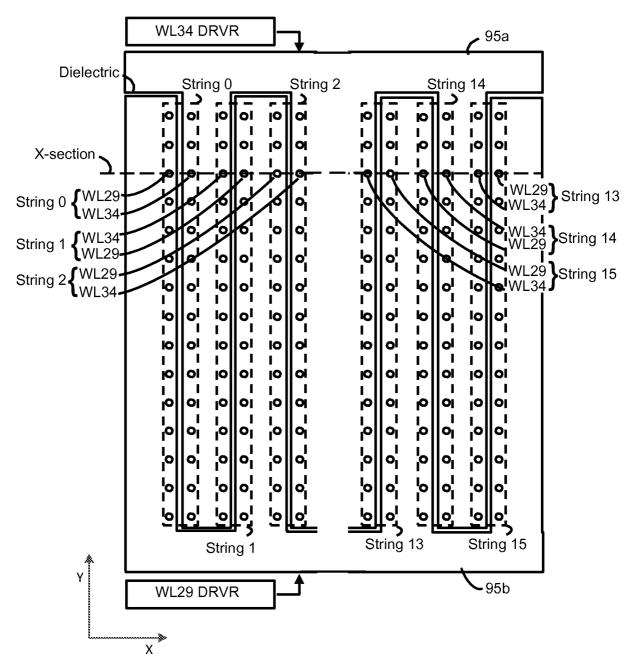

- [0022] FIGs. 9A 9B show an example of a 3-D NAND memory array.

- [0023] FIG. 10 shows an example of a 3-D NAND memory at an intermediate stage of fabrication.

- [0024] FIG. 11 shows the structure of FIG. 10 at a later stage of fabrication.

- [0025] FIG. 12 shows the structure of FIG. 11 after formation of memory holes.

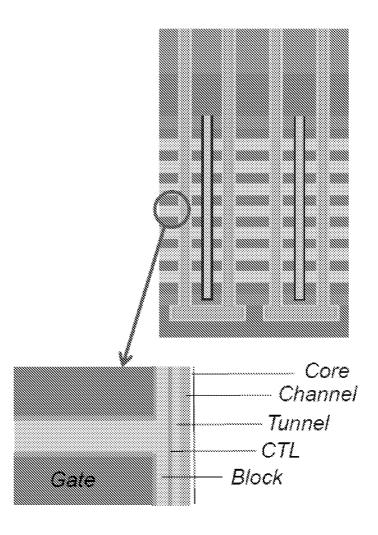

- [0026] FIG. 13 shows a detailed view of memory elements in a memory hole of a 3-D NAND memory.

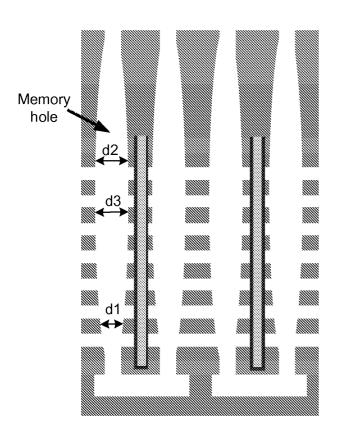

- 20 [0027] FIG. 14 shows an example of a non-uniform memory hole.

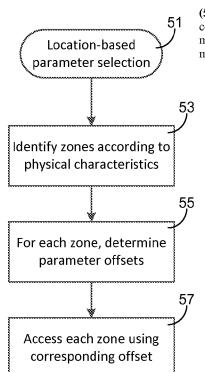

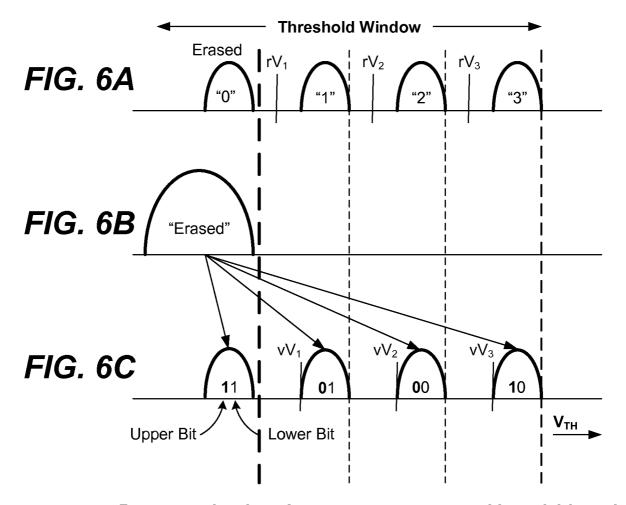

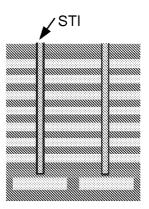

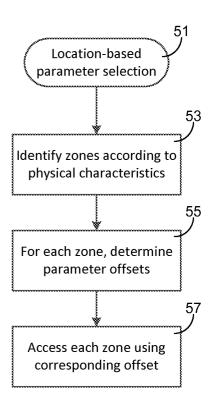

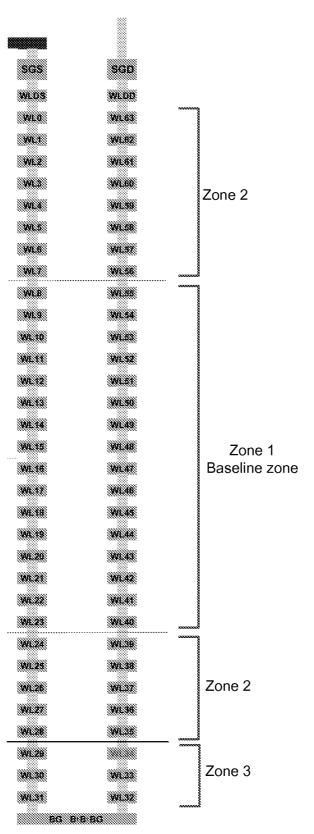

- [0028] FIG. 15 illustrates an example of location-based parameter selection.

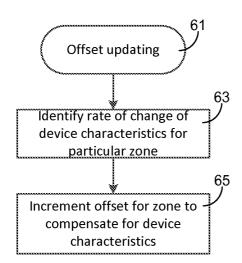

- [0029] FIG. 16 illustrates updating of offsets for different zones.

- [0030] FIG. 17 illustrates an example of zones in a 3-D NAND memory array.

#### **DETAILED DESCRIPTION**

#### MEMORY SYSTEM

5

10

25

30

[0031] FIG. 1 illustrates schematically the main hardware components of a memory system suitable for implementing the present invention. The memory system 90 typically operates with a host 80 through a host interface. The memory system is typically in the form of a memory card or an embedded memory system. The memory system 90 includes a memory 102 whose operations are controlled by a controller 100. The memory 102 comprises one or more array of non-volatile memory cells distributed over one or more integrated circuit chip. The controller 100 may include interface circuits 110, a processor 120, ROM (read-only-memory) 122, RAM (random access memory) 130, programmable nonvolatile memory 124, and additional components. A controller is typically formed as an ASIC (application specific integrated circuit) and the components included in such an ASIC generally depend on the particular application.

## 15 <u>Physical Memory Structure</u>

[0032] FIG. 2 illustrates schematically a non-volatile memory cell. The memory cell 10 can be implemented by a field-effect transistor having a charge storage unit 20, such as a floating gate or a dielectric layer. The memory cell 10 also includes a source 14, a drain 16, and a control gate 30.

20 [0033] There are many commercially successful non-volatile solid-state memory devices being used today. These memory devices may employ different types of memory cells, each type having one or more charge storage element.

[0034] Typical non-volatile memory cells include EEPROM and flash EEPROM. Examples of EEPROM cells and methods of manufacturing them are given in United States patent no. 5,595,924. Examples of flash EEPROM cells, their uses in memory systems and methods of manufacturing them are given in United States patents nos. 5,070,032, 5,095,344, 5,315,541, 5,343,063, 5,661,053, 5,313,421 and 6,222,762. In particular, examples of memory devices with NAND cell structures are described in United States patent nos. 5,570,315, 5,903,495, 6,046,935. Also, examples of memory devices utilizing dielectric storage elements have been described by Eitan et

al., "NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol. 21, no. 11, November 2000, pp. 543-545, and in United States patents nos. 5,768,192 and 6,011,725.

[0035] In practice, the memory state of a cell is usually read by sensing the conduction current across the source and drain electrodes of the cell when a reference voltage is applied to the control gate. Thus, for each given charge on the floating gate of a cell, a corresponding conduction current with respect to a fixed reference control gate voltage may be detected. Similarly, the range of charge programmable onto the floating gate defines a corresponding threshold voltage window or a corresponding conduction current window.

5

10

15

20

25

30

[0036] Alternatively, instead of detecting the conduction current among a partitioned current window, it is possible to set the threshold voltage for a given memory state under test at the control gate and detect if the conduction current is lower or higher than a threshold current (cell-read reference current). In one implementation the detection of the conduction current relative to a threshold current is accomplished by examining the rate the conduction current is discharging through the capacitance of the bit line.

[0037] FIG. 3 illustrates the relation between the source-drain current  $I_D$  and the control gate voltage  $V_{CG}$  for four different charges Q1-Q4 that the floating gate may be selectively storing at any one time. With fixed drain voltage bias, the four solid  $I_D$  versus  $V_{CG}$  curves represent four charge levels that can be programmed on a floating gate of a memory cell, respectively corresponding to four of eight possible memory states. As an example, the threshold voltage window of a population of cells may range from 0.5V to 3.5V. Seven programmed memory states "0", "1", "2", "3", "4", "5", "6", respectively, and one erased state (not shown), may be demarcated by partitioning the threshold window into regions in intervals of 0.5V each. For example, if a reference current, IREF of 2  $\mu$ A is used as shown, then the cell programmed with Q1 may be considered to be in a memory state "1" since its curve intersects with  $I_{REF}$  in the region of the threshold window demarcated by VCG = 0.5V and 1.0V. Similarly, Q4 is in a memory state "5".

[0038] As can be seen from the description above, the more states a memory cell is

made to store, the more finely divided is its threshold window. For example, a memory device may have memory cells having a threshold window that ranges from -1.5V to 5V. This provides a maximum width of 6.5V. If the memory cell is to store 16 states, each state may occupy from 200mV to 300mV in the threshold window. This will require higher precision in programming and reading operations in order to be able to achieve the required resolution.

#### **NAND Structure**

5

10

15

20

25

30

[0039] FIG. 4A illustrates schematically a string of memory cells organized into a NAND string. A NAND string 50 comprises a series of memory transistors M1, M2, ... Mn (e.g., n= 4, 8, 16 or higher) daisy-chained by their sources and drains. A pair of select transistors S1, S2 controls the memory transistor chain's connection to the external world via the NAND string's source terminal 54 and drain terminal 56 respectively. In a memory array, when the source select transistor S1 is turned on, the source terminal is coupled to a source line (see FIG. 4B). Similarly, when the drain select transistor S2 is turned on, the drain terminal of the NAND string is coupled to a bit line of the memory array. Each memory transistor 10 in the chain acts as a memory cell. It has a charge storage element 20 to store a given amount of charge so as to represent an intended memory state. A control gate 30 of each memory transistor allows control over read and write operations. As will be seen in FIG. 4B, the control gates 30 of corresponding memory transistors of a row of NAND string are all connected to the same word line. Similarly, a control gate 32 of each of the select transistors S1, S2 provides control access to the NAND string via its source terminal 54 and drain terminal 56 respectively. Likewise, the control gates 32 of corresponding select transistors of a row of NAND string are all connected to the same select line.

[0040] When an addressed memory transistor 10 within a NAND string is read or is verified during programming, its control gate 30 is supplied with an appropriate voltage. At the same time, the rest of the non-addressed memory transistors in the NAND string 50 are fully turned on by application of sufficient voltage on their control gates. In this way, a conductive path is effectively created from the source of the individual memory transistor to the source terminal 54 of the NAND string and likewise for the drain of the individual memory transistor to the drain terminal 56 of

the cell. Memory devices with such NAND string structures are described in United States patent nos. 5,570,315, 5,903,495, 6,046,935.

[0041] FIG. 4B illustrates an example of a NAND array 210 of memory cells, constituted from NAND strings 50 such as that shown in FIG. 4A. Along each column of NAND strings, a bit line such as bit line 36 is coupled to the drain terminal 56 of each NAND string. Along each bank of NAND strings, a source line such as source line 34 is coupled to the source terminals 54 of each NAND string. Also the control gates along a row of memory cells in a bank of NAND strings are connected to a word line such as word line 42. The control gates along a row of select transistors in a bank of NAND strings are connected to a select line such as select line 44. An entire row of memory cells in a bank of NAND strings can be addressed by appropriate voltages on the word lines and select lines of the bank of NAND strings.

[0042] FIG. 5 illustrates a page of memory cells, organized in the NAND configuration, being sensed or programmed in parallel. FIG. 5 essentially shows a bank of NAND strings 50 in the memory array 210 of FIG. 4B, where the detail of each NAND string is shown explicitly as in FIG. 4A. A physical page, such as the page 60, is a group of memory cells enabled to be sensed or programmed in parallel. This is accomplished by a corresponding page of sense amplifiers 212. The sensed results are latched in a corresponding set of latches 214. Each sense amplifier can be coupled to a NAND string via a bit line. The page is enabled by the control gates of the cells of the page connected in common to a word line 42 and each cell accessible by a sense amplifier accessible via a bit line 36. As an example, when respectively sensing or programming the page of cells 60, a sensing voltage or a programming voltage is respectively applied to the common word line WL3 together with appropriate voltages on the bit lines.

## Physical Organization of the Memory

5

10

15

20

25

30

[0043] One important difference between flash memory and other of types of memory is that a cell must be programmed from the erased state. That is the floating gate must first be emptied of charge. Programming then adds a desired amount of charge back to the floating gate. It does not support removing a portion of the charge from the floating gate to go from a more programmed state to a lesser one. This means that

update data cannot overwrite existing one and must be written to a previous unwritten location.

[0044] Furthermore erasing is to empty all the charges from the floating gate and generally takes appreciable time. For that reason, it will be cumbersome and very slow to erase cell by cell or even page by page. In practice, the array of memory cells is divided into a large number of blocks of memory cells. As is common for flash EEPROM systems, the block is the unit of erase. That is, each block contains the minimum number of memory cells that are erased together. While aggregating a large number of cells in a block to be erased in parallel will improve erase performance, a large size block also entails dealing with a larger number of update and obsolete data.

[0045] Each block is typically divided into a number of physical pages. A logical page is a unit of programming or reading that contains a number of bits equal to the number of cells in a physical page. In a memory that stores one bit per cell, one physical page stores one logical page of data. In memories that store two bits per cell, a physical page stores two logical pages. The number of logical pages stored in a physical page thus reflects the number of bits stored per cell. In one embodiment, the individual pages may be divided into segments and the segments may contain the fewest number of cells that are written at one time as a basic programming operation. One or more logical pages of data are typically stored in one row of memory cells. A page can store one or more sectors. A sector includes user data and overhead data.

#### All-bit, Full-Sequence MLC Programming

5

10

15

20

25

30

[0046] FIG. 6A – 6C illustrate an example of programming a population of 4-state memory cells. FIG. 6A illustrates the population of memory cells programmable into four distinct distributions of threshold voltages respectively representing memory states "0", "1", "2" and "3". FIG. 6B illustrates the initial distribution of "erased" threshold voltages for an erased memory. FIG. 6C illustrates an example of the memory after many of the memory cells have been programmed. Essentially, a cell initially has an "erased" threshold voltage and programming will move it to a higher value into one of the three zones demarcated by verify levels vV<sub>1</sub>, vV<sub>2</sub> and vV<sub>3</sub>. In this way, each memory cell can be programmed to one of the three programmed states "1", "2" and "3" or remain un-programmed in the "erased" state. As the memory gets

more programming, the initial distribution of the "erased" state as shown in **FIG. 6B** will become narrower and the erased state is represented by the "0" state.

[0047] A 2-bit code having a lower bit and an upper bit can be used to represent each of the four memory states. For example, the "0", "1", "2" and "3" states are respectively represented by "11", "01", "00" and '10". The 2-bit data may be read from the memory by sensing in "full-sequence" mode where the two bits are sensed together by sensing relative to the read demarcation threshold values  $rV_1$ ,  $rV_2$  and  $rV_3$  in three sub-passes respectively.

#### Overprogramming

5

15

20

25

30

10 **[0048]** One problem that may occur in either SLC or MLC memory is the problem of overprogramming of cells. When a cell is overprogrammed, too much charge is added to its charge storage element (e.g. floating gate) so that the cell is not within the expected distribution for the memory state to which it is being programmed.

[0049] FIG. 7 shows a first example of overprogramming. This example shows an SLC memory although the same phenomenon may occur in MLC memory cells. The programmed ("0") state shows a distribution (dashed line) that extends beyond the ideal distribution (shown by solid line). Thus, there are many cells that have a threshold voltage that is higher than the threshold voltage range that is assigned to the 0 state. One problem with such cells is that their high threshold voltage means that they can only be turned on (channel made conductive) by applying a higher control gate voltage. A voltage that is sufficient to turn on a cell that is within the assigned threshold voltage range may not be sufficient to turn on a cell that is overprogrammed as shown. In general a pass voltage, Vpass, used to turn on unselected cells in a NAND string when reading or programming a selected cell, is sufficient to turn on all cells within the assigned threshold voltage range. However, Vpass may not be sufficient to turn on an overprogrammed cell. Thus, an overprogrammed cell in a NAND string may remain nonconductive when Vpass is applied, causing other cells in the string to be read as being in the programmed "0" state even if they are in the "1" state. Significant numbers of overprogrammed cells may make an array, or a portion of an array, unusable. MLC cells programmed to the highest threshold voltage range, which are overprogrammed, may also have increased threshold voltages so that

Vpass is not sufficient to turn them on.

5

10

15

[0050] FIG. 8 shows another example of overprogramming. This example shows an MLC memory. Memory states are marked as Erased "Er", "A," "B," and "C." It can be seen that the distribution of cells for state A as shown by the dashed line is different to the ideal distribution shown by the solid line. Thus, there are many cells that are overprogrammed so that they have a threshold voltage that is higher than the threshold voltage range assigned to state A. Some of these cells are sufficiently overprogrammed that their threshold voltages are in the threshold voltage range assigned to state B. Such cells will be read as being in state B and thus will provide incorrect data. Some of the cells of this distribution that are between the ranges assigned to A and B will also be read as being in state B. The number of such cells depends on the particular discrimination voltage used. While not shown in FIG. 8, similar overprogramming may also occur between state B and state C. Where more than four memory states are used, such overprogramming may occur between any two programmed (non-erased) states.

[0051] In many memories, overprogramming becomes worse as the memory array becomes worn (i.e. as the number of write-erase cycles increases). Repeated writing and erasing can produce physical changes in the memory cell that make overprogramming increasingly likely for a given cell.

[0052] Overprogramming may be related to the geometry of a particular memory device. While memory cells may all have the same nominal dimensions, real memory cells have some distribution of dimensions. Cells with dimensions that deviate from the nominal dimensions may have device characteristics that deviate from nominal device characteristics (for example having significantly faster programming times causing them to become overprogrammed). In particular, certain 3-D memory arrays have been found to have high programming speeds (and resulting overprogramming) as a result of particular dimensions.

## 3-D NAND structure

[0053] An alternative arrangement to a conventional two-dimensional (2-D) NAND array is a three-dimensional (3-D) array. In contrast to 2-D NAND arrays, which are formed along a planar surface of a semiconductor wafer, 3-D arrays extend up from

the wafer surface and generally include stacks, or columns, of memory cells extending up from the wafer surface. Various 3-D arrangements are possible. In one arrangement a NAND string is formed vertically with one end (e.g. source) at the wafer surface and the other end (e.g. drain) on top. In another arrangement a NAND string is formed in a U-shape so that both ends of the NAND string are accessible on top, thus facilitating connections between such strings. Examples of such NAND strings and their formation are described in U.S. Patent Publication Number 2012/0220088.

5

10

15

20

25

30

[0054] FIG. 9A shows a physical implementation of a 3-D NAND array. The bit line 91 extends as a continuous conductor (e.g. metal line) in the y-direction with vertical connections formed between the bit line and drains of strings (only strings 0-2 and 13-15 are shown – it will be understood that strings 3-12 are also present). Below the bit line, common source lines extend perpendicular to the cross section shown (i.e. extend in the x-direction) and connect sources of neighboring strings. Source select lines extend in the x-direction and form source select gates (SGS) where they intersect vertical columns. Drain select lines extend in the x-direction and form drain select gates (SGD) where they intersect vertical columns. Word lines WL0-WL63 extend in the x-direction and form control gates of memory cells where they intersect vertical columns. In one example, word lines are formed from conductive layers separated by dielectric layers, with channels of memory cells being formed in vertical holes ("memory holes") that extend through the conductive layers and dielectric layers.

[0055] The structure of the 3-D memory array of FIG. 9A is comprised of multiple layers, with each layer having the same replicated pattern (e.g. layer in dashed lines containing WL34 and WL29 is replicated at each level). Taking word line 34 as a typical word line, it can be seen that word line 34 alternates with word line 29 along the y-direction. While word lines of each string may be separately controlled in some memory systems, combining word lines saves space for driver circuits. In the present example, all word lines of the same number within a block are formed from a single portion of conductive material and remain as an electrically continuous unit. For example, all word lines marked WL34 are formed of a single electrically-conductive portion of material, and all word lines marked WL29 are formed of another electrically-conductive portion of material (which may be formed from the same

layer).

5

10

15

20

30

[0056] FIG. 9B shows a top-down view of the structure of word lines 34 and 29 with the horizontal dashed line showing the location of the cross section of FIG. 9A. It can be seen that a portion of conductive material 95a extends along the top in this view with extensions extending down (negative y-direction). These extensions form pairs of word lines shown in FIG. 9A (WL34) with memory cells formed where memory holes containing channels pass through the word lines. A driver circuit "WL34 DRVR" is connected to portion of conductive material 95a so that a controllable voltage can be applied to it and thus to control gates of all memory cells connected to any WL34 in this block. A similar portion of conductive material 95b extends along the bottom in this view with extensions extending up (positive y-direction). These extensions form pairs of word lines shown in FIG. 9A (WL29) with memory cells formed where memory holes pass through the word lines. A driver circuit "WL29 DRVR" is connected to portion of material 95b so that a controllable voltage can be applied to it and thus to control gates of all memory cells connected to any word line 29 in this block. The two portions of material 95a, 95b, may be formed by depositing a single layer of conductive material and patterning it into the portions shown (and similar portions for other blocks). A dielectric material may be used to fill the gap between portions. For example, a Shallow Trench Isolation (STI) process may be used to physically separate, and electrically isolate, the two portions. Dielectric layers above and below these portions (in the z-direction) insulate these portions from other similar layers. This pattern may be replicated for each pair of word lines in the block so that for 64 word lines, there are 32 layers similar to that shown in FIG. 9B, with dielectric layers in between.

## 25 <u>Device characteristics and location</u>

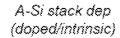

[0057] FIGs. 10-13 show formation of a 3-D memory array of the type previously shown. FIG. 10 shows a substrate with a stack of layers on an upper surface. The substrate contains back gate structures which are later removed when forming the back gate. The stack of layers consists of alternating layers of Boron-doped (electrically conductive) polysilicon ("poly") and insulating dielectric (e.g. SiO2).

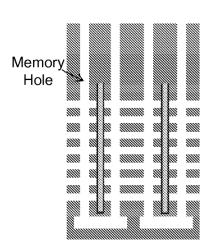

[0058] FIG. 11 shows formation of Shallow Trench Isolation (STI) trenches with

dielectric filling to provide isolation between the two sides of a string. This dielectric separates the portions of conductive material that make up the word lines of a given layer (e.g. separating WL34 and WL29 above).

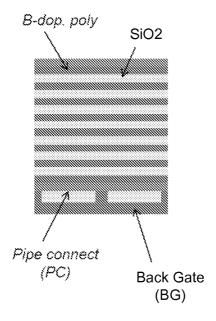

[0059] FIG. 12 shows additional layers including an etch mask layer with openings that are used to etch cylindrical memory holes as shown. In addition to etching the memory holes, a selective etch is used to remove insulating dielectric while leaving doped polysilicon throughout the stack. Back gate structures are also removed by selective etching. The remaining doped polysilicon portions become word lines.

5

10

15

20

25

30

[0060] FIG. 13 shows the structure after deposition of a stack of layers in the memory holes to form memory cells. It can be seen that a blocking dielectric "Block" is deposited on the doped polysilicon to provide electrical isolation. A Charge Trapping Layer (CTL) is deposited on the blocking dielectric. The CTL forms charge storage elements where the CTL is in close proximity to polysilicon word line. A tunnel dielectric is deposited to provide electrical isolation and to allow charge to tunnel into the CTL under certain conditions. A channel material is deposited to form the channel of the memory cells along the string. A core material is deposited that forms the core of the column that is located in the memory hole.

[0061] While FIGs. 10-13 show an idealized profile for memory hole formation and subsequent formation of memory cells, real profiles may deviate from this profile, and memory holes may not have perfect cylindrical shapes. A memory hole may have a larger diameter at some locations than others leading to memory cells with different device characteristics. Such differences may be predictable to some extent so that memory operation can compensate accordingly.

[0062] FIG. 14 shows a cross section of memory holes formed by an etch process that provides a narrower memory hole at the bottom (diameter = d1) than at the top (diameter = d2), with the widest memory hole close to the middle of the stack (diameter = d3). In general, such a profile is a characteristic of the process used (i.e. materials being etched, etch chemistry, temperature, pressure, time, etc.). Thus, the profile of a memory hole is generally non-uniform in a predictable way (though not necessarily in the particular way shown in FIG 14).

[0063] In a cylindrical memory cell the smaller the cylinder of the memory hole, the

5

10

15

20

25

30

greater the coupling between the control gate (word line) and the CTL. As the diameter of the memory hole gets smaller, the electric field strength between the control gate and channel gets larger for a given voltage difference, so that a given control gate voltage has more effect. This means that programming speed is generally higher for memory cells with smaller memory holes.

[0064] Memory hole size is predictable as a function of location within a stack of layers. For example, the lowest memory cells in the stack, nearest to the back gate, have the smallest memory holes in the above example and have a greater risk of overprogramming. Memory cells at the top or at some mid-point may be least at risk of overprogramming. Thus, the susceptibility of memory cells to overprogramming may be predicted based on location (e.g. by word line) and appropriate action can be taken making overprogramming of such cells less likely.

[0065] Appropriate action to compensate for variation in a device dimension may include modifying certain operating parameters. In this way, a variation in the physical geometry of memory cells from location-to-location can be offset by making appropriate modifications to parameters used to access different memory cells. For example, different programming parameters may be used to program different word lines in order to avoid overprogramming along particular word lines or to overcome other location-dependent problems. Programming voltage may be modified for certain word lines, and/or programming times may be modified, and/or number of programming pulses used, or other parameters may be modified.

[0066] Read parameters may also be modified according to location to compensate for physical device variation. For example, a lower read voltage, Vread, may be used for memory cells having a smaller memory hole. Other read parameters may also be modified.

[0067] Erase parameters may also be modified according to location to compensate for physical device variation. In some cases a sub-block erase scheme may use a first set of erase parameters for a sub-block near the bottom of a 3-D memory array and a different set of erase parameters for a sub-block near the middle or top of a 3-D memory array. Specific parameters that may be modified include erase voltage, and erase verify conditions.

[0068] While the above examples refer to memory hole size as an example of a device dimension that varies with location in a predictable manner, any dimension that varies in a predictable manner may also cause variation in device characteristics in a predictable pattern, and operating parameters can be modified based on location to compensate for such variation. Such variation in device dimensions are not limited to variation between different levels (along z axis) but may also occur from location-to-location in a level, and thus may occur in planar structures such as planar NAND.

5

10

15

20

25

30

[0069] Modifying operating parameters based on location as described above may be combined with other modifications of operating parameters. For example, there may be variation in device characteristics from one die to another within a wafer, or from block to block within a die, and some scheme may compensate for such variation by modifying certain operating parameters. In some cases, factory testing measures some variation and sets certain operating parameters accordingly in a parameter trimming process. In some cases, operating parameters are modified as a memory array, or a portion of a memory array, becomes worn. For example, a count may be maintained of the number of write-erase cycles ("hot count") for blocks of a memory array, with operating parameters being modified to compensate for changes to memory cells as they become worn. The present scheme may be combined with any such scheme, or schemes. For example, a location based scheme may provide one or more offsets, or deltas, to parameters used in a baseline zone. The parameters used in the baseline zone may be based on factory testing, and may be updated according to write-erase cycle count or other updating mechanism.

[0070] FIG. 15 is a flow chart showing a scheme for location-based parameter selection 51. Initially, zones are identified according to physical characteristics 53. For example, in a 3-D memory array, zones may reflect the diameter of the memory hole at different levels above the substrate. Zones may include only a single layer (two word lines) or may include multiple layers that share similar physical characteristics (e.g. approximately the same memory hole diameter). For each zone a set of parameter offsets are determined 55. In an example, a set of parameters of a baseline zone may provide a starting point for any scheme, with a set of parameters for a given zone defined by a set of offsets from parameters of the baseline zone. Access to each zone is then performed using the corresponding offsets to the default

parameters 57.

5

10

15

20

25

30

[0071] In some schemes, a set of offsets for a particular zone remain constant throughout the lifecycle of the device. The parameters of the baseline zone may be updated to account for wear and the parameters for all zones are thereby updated because the parameters are set by offsets from the baseline parameters. However, in some cases it is desirable to update the offsets themselves in addition to (or instead of) updating the baseline parameters. For example, memory cells with a smaller memory hole may wear faster because of the higher field strength generated between their control gate and channel. Updating operating parameters on a block-by-block basis does not take into account such faster wearing of certain portions of the block (e.g. word lines towards the bottom). It is sometimes advantageous to use dynamic offsets instead of static offsets in order to keep operating parameters optimized in all zones over the lifecycle of the device.

[0072] FIG. 16 is a flow chart showing a scheme for updating offsets 61. The rate of change of device characteristics is identified for individual zones 63. For example, the baseline zone may have a particular rate of change of programming speed, or erase speed, or other characteristic that may be used to determine how baseline parameters are updated as a function of write-erase cycle count. Another zone may have a different rate of change of a characteristic so that updating of baseline parameters is not sufficient to account for change in the other zone. Accordingly, the offset of that parameter for the zone is incremented 65 (either when incrementing baseline parameters, or separately) to compensate for the different rates of change.

[0073] A memory array may be divided into zones in any suitable manner to account for different physical characteristics of memory cells in different locations. In general, it is desirable to keep the number of zones small in order to keep the system simple, and reduce overhead. FIG. 17 shows an example of a zoning scheme for use in a 64 cell/string 3-D NAND array (while just one NAND string is shown, it will be understood that zoning may be similarly applied to all strings in a block, or all strings in a memory array, or some portion of a memory array). Three zones are used in this example. The largest zone is the baseline zone, zone 1, which includes memory cells with substantially uniform memory hole diameter along WL8-WL23 and WL40-WL55. Zone 1 has memory cells with relatively large memory holes. Zone 2 includes

memory cells above (along WL0-WL7, WL56-WL63) and below (along WL24-WL28, WL35-WL39) zone 1. Thus, zone 2 is not continuous in this example. Zone 2 includes memory cells with somewhat smaller memory holes than zone 1. Zone 3 includes memory cells near the bottom of the stack (WL29-34), which have the smallest memory holes. Parameters for zone 1 may be baseline parameters. These may be factory-set, and may be updated based on write-erase cycle count. Parameters for zone 2 may be offset according to a first set of offsets. Parameters for zone 3 may be offset according to a second, different, set of offsets. The offsets for zone 3 may be greater than for zone 2.

10 [0074] It will be understood that any suitable zoning scheme may be used including providing a different zone for each level. It will also be understood that aspects of the above examples may be used separately (e.g. zoning does not require updated offsets, or that a particular baseline zone be used). Zones used for parameter modification may be the same for all parameters (read, write, and erase) or may be different for different operations (e.g. one zoning scheme for read parameters, a different zoning scheme for write parameters, and another zoning scheme for erase parameters).

#### Conclusion

20

25

5

[0075] The foregoing detailed description of the invention has been presented for purposes of illustration and description. It is not intended to be exhaustive or to limit the invention to the precise form disclosed. Many modifications and variations are possible in light of the above teaching. The described embodiments were chosen in order to best explain the principles of the invention and its practical application, to thereby enable others skilled in the art to best utilize the invention in various embodiments and with various modifications as are suited to the particular use contemplated. It is intended that the scope of the invention be defined by the claims appended hereto.

#### IT IS CLAIMED:

1. A method of operating a charge-storage memory cell array comprising: identifying a pattern of variation of at least one memory cell dimension within the charge-storage memory cell array;

5

determining a first set of parameters to use in accessing a first plurality of memory cells based on the at least one memory cell dimension of the first plurality of memory cells;

10

15

determining a second set of parameters to use in accessing a second plurality of memory cells based on the at least one memory cell dimension of the second plurality of memory cells, the second set of parameters including at least one parameter that is different from the first set of parameters;

subsequently accessing the first plurality of memory cells using the first set of parameters; and

accessing the second plurality of memory cells using the second set of parameters.

- 2. The method of claim 1 wherein the at least one memory cell dimension is a diameter of a cylindrical memory hole.

- 3. The method of claim 2 wherein the charge-storage memory cell array is a three-dimensional memory array, the first plurality of memory cells are located in a lower portion of the three-dimensional memory array, the second plurality of memory cells are located in an upper portion of the three-dimensional memory array, and the identified pattern of variation indicates that the diameter of the cylindrical memory hole is greater in the second plurality of memory cells than in the first plurality of memory cells.

- 4. The method of claim 1 wherein the at least one parameter that is different is a voltage that is applied to program memory cells.

30

5. The method of claim 1 wherein the at least one parameter that is different is a number of voltage pulses used to program memory cells.

6. The method of claim 1 wherein the at least one parameter that is different is a read voltage that is used to read memory cells.

- 7. The method of claim 1 wherein the at least one parameter is an erase voltage that is used to erase memory cells.

- 8. The method of claim 1 further comprising maintaining a write-erase cycle count for blocks of the charge-storage memory array and updating the first and second sets of parameters according to the write erase cycle counts.

10

9. The method of claim 8 further comprising updating the first set of parameters according to a first update scheme and updating the second set of parameters according to a second update scheme that is different from the first update scheme.

15

10. A charge-storage memory cell array comprising:

an array of memory cells, each memory cell having a memory cell dimension, the memory cell dimension having a pattern of variation across the array of memory cells; and

memory access circuits that access memory cells of the array of memory cells according to access parameters, the memory access circuits having a first set of parameters for accessing a first plurality of memory cells and a second set of parameters for accessing a second plurality of memory cells, the second set of parameters including at least one parameter that is different from the first set of parameters, the first plurality of memory cells and the second plurality of memory cells defined according to the pattern of variation.

11. The charge-storage memory cell array of claim 10 wherein the charge-storage memory cell array is a three-dimensional memory array.

30

12. The charge-storage memory cell array of claim 11 wherein the charge-storage memory cell array is a three-dimensional NAND memory array which includes a plurality of NAND strings that extend vertically in a direction that is perpendicular to a substrate surface.

13. The charge-storage memory cell array of claim 12 wherein the pattern of variation across the array of memory cells is a pattern of variation of the memory cell dimension according to vertical distance from the substrate surface.

- The charge-storage memory cell array of claim 13 wherein the memory cell dimension is a diameter of an opening that extends vertically through word lines with a channel extending vertically through the opening.

- 15. The charge-storage memory cell array of claim 10 further comprising a write-erase cycle count circuit that maintains write-erase cycle counts for blocks in the charge-storage memory cell array and updates access parameters according to write-erase cycle counts.

- 16. The charge-storage memory cell array of claim 15 wherein the write-15 erase cycle count circuit has a first update scheme for updating the first set of parameters and a second update scheme for updating the second set of parameters.

FIG. 1

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

Programming into four states represented by a 2-bit code

FIG. 7

FIG. 8

F/G. 9A

FIG. 9B

FIG. 10

FIG. 12

FIG. 11

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

## **INTERNATIONAL SEARCH REPORT**

International application No PCT/US2013/071505

|                                                                                                                               | FICATION OF SUBJECT MATTER G11C29/02 G11C11/56 G11C16/0                                                                      | 06                                                                                                                                                                                                  |                                                         |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|

| According to International Patent Classification (IPC) or to both national classification and IPC                             |                                                                                                                              |                                                                                                                                                                                                     |                                                         |  |  |  |  |  |  |

| Minimum do                                                                                                                    | SEARCHED commentation searched (classification system followed by classification                                             | on symbols)                                                                                                                                                                                         |                                                         |  |  |  |  |  |  |

| G11C                                                                                                                          |                                                                                                                              |                                                                                                                                                                                                     |                                                         |  |  |  |  |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |                                                                                                                              |                                                                                                                                                                                                     |                                                         |  |  |  |  |  |  |

| Electronic d                                                                                                                  | ata base consulted during the international search (name of data bas                                                         | se and, where practicable, search terms use                                                                                                                                                         | ed)                                                     |  |  |  |  |  |  |

|                                                                                                                               | ternal, WPI Data                                                                                                             |                                                                                                                                                                                                     |                                                         |  |  |  |  |  |  |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                        |                                                                                                                              |                                                                                                                                                                                                     |                                                         |  |  |  |  |  |  |

| Category*                                                                                                                     | Citation of document, with indication, where appropriate, of the rele                                                        | evant passages                                                                                                                                                                                      | Relevant to claim No.                                   |  |  |  |  |  |  |

| Х                                                                                                                             | US 2010/271891 A1 (DELL RICHARD  <br>ET AL) 28 October 2010 (2010-10-2                                                       | 1,4-12,<br>15,16                                                                                                                                                                                    |                                                         |  |  |  |  |  |  |

| A                                                                                                                             | paragraph [0022] - paragraph [002<br>figures 2,3                                                                             | 2,3,13,<br>14                                                                                                                                                                                       |                                                         |  |  |  |  |  |  |

| А                                                                                                                             | US 2011/096601 A1 (GAVENS LEE M<br>AL) 28 April 2011 (2011-04-28)<br>paragraph [0121] - paragraph [012<br>figure 14          | 1-16                                                                                                                                                                                                |                                                         |  |  |  |  |  |  |

| А                                                                                                                             | US 2003/195714 A1 (JEDDELOH JOSE<br>16 October 2003 (2003-10-16)<br>claim 1; figure 3                                        | 1-16                                                                                                                                                                                                |                                                         |  |  |  |  |  |  |

| Furtl                                                                                                                         | her documents are listed in the continuation of Box C.                                                                       | X See patent family annex.                                                                                                                                                                          |                                                         |  |  |  |  |  |  |

| "A" docume                                                                                                                    | ategories of cited documents : ent defining the general state of the art which is not considered of particular relevance     | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |                                                         |  |  |  |  |  |  |

| "E" earlier a<br>filing d                                                                                                     | application or patent but published on or after the international<br>late                                                    | "X" document of particular relevance; the considered novel or cannot be considered.                                                                                                                 |                                                         |  |  |  |  |  |  |

| cited to                                                                                                                      | ent which may throw doubts on priority claim(s) or which is<br>o establish the publication date of another citation or other | step when the document is taken alon "Y" document of particular relevance; the c                                                                                                                    | e                                                       |  |  |  |  |  |  |

| "O" docume                                                                                                                    | ıl reason (as specified)<br>ent referring to an oral disclosure, use, exhibition or other                                    | considered to involve an inventive ste<br>combined with one or more other such                                                                                                                      | o when the document is<br>o documents, such combination |  |  |  |  |  |  |

|                                                                                                                               | s<br>ent published prior to the international filing date but later than<br>ority date claimed                               | being obvious to a person skilled in the art "&" document member of the same patent family                                                                                                          |                                                         |  |  |  |  |  |  |

| Date of the                                                                                                                   | actual completion of the international search                                                                                | Date of mailing of the international search report                                                                                                                                                  |                                                         |  |  |  |  |  |  |

| 6                                                                                                                             | March 2014                                                                                                                   | 14/03/2014                                                                                                                                                                                          |                                                         |  |  |  |  |  |  |

| Name and r                                                                                                                    | nailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2                                                | Authorized officer                                                                                                                                                                                  |                                                         |  |  |  |  |  |  |

|                                                                                                                               | NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                   | Wolff, Norbert                                                                                                                                                                                      |                                                         |  |  |  |  |  |  |

## **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2013/071505

| Patent document cited in search report |    | Publication<br>date |                                        | Patent family<br>member(s)                                                                                  | Publication date                                                                               |  |

|----------------------------------------|----|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| US 2010271891                          | A1 | 28-10-2010          | NON                                    | NONE                                                                                                        |                                                                                                |  |

| US 2011096601                          | A1 | 28-04-2011          | CN<br>EP<br>JP<br>KR<br>TW<br>US<br>WO | 102667943 A<br>2494554 A1<br>2013509651 A<br>20120093295 A<br>201140604 A<br>2011096601 A1<br>2011056483 A1 | 12-09-2012<br>05-09-2012<br>14-03-2013<br>22-08-2012<br>16-11-2011<br>28-04-2011<br>12-05-2011 |  |

| US 2003195714                          | A1 | 16-10-2003          | US<br>US                               | 2003195714 A1<br>2005119849 A1                                                                              | 16-10-2003<br>02-06-2005                                                                       |  |