등록특허 10-2198021

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년01월05일

(11) 등록번호 10-2198021

(24) 등록일자 2020년12월28일

- (51) 국제특허분류 (Int. Cl.)

*H01L 27/02* (2006.01) *H01L 27/06* (2006.01)

*H01L 29/778* (2006.01)

- (52) CPC특허분류

*H01L 27/0248* (2013.01)

*H01L 27/0605* (2013.01)

- (21) 출원번호 10-2015-7031623

- (22) 출원일자(국제) 2014년05월02일

심사청구일자 2019년04월09일

- (85) 번역문제출일자 2015년11월03일

- (65) 공개번호 10-2016-0004290

- (43) 공개일자 2016년01월12일

- (86) 국제출원번호 PCT/US2014/036499

- (87) 국제공개번호 WO 2014/179651

국제공개일자 2014년11월06일

(30) 우선권주장

61/819,252 2013년05월03일 미국(US)

14/267,185 2014년05월01일 미국(US)

(56) 선행기술조사문현

JP2003347417 A

US07881029 B1

US20120262828 A1

KR1020070100026 A

전체 청구항 수 : 총 20 항

심사관 : 송상용

## (54) 발명의 명칭 콤팩트 정전기 방전 (ESD) 보호 구조

**(57) 요약**

멀티-게이트 쇼트키 공핍-모드 전계 효과 트랜지스터(FET), 적어도 하나의 다이오드 및 두 개의 저항기들은 콤팩트 정전기 방전(ESD) 보호 구조를 포함한다. 이 ESD 보호 구조는 전형적인 다중 다이오드 ESD 디바이스들보다 작은 영역에 배치될 수 있다. 멀티-게이트 FET는 여러 유형의 고 전자 이동도 트랜지스터(HEMT) 디바이스들, 예를

(뒷면에 계속)

**대 표 도** - 도3

들어 (부정형) pHEMT, (변성) mHEMT, 유도 HEMT를 포함할 수 있다. 쇼트키 전계 효과 디바이스의 다중 게이트들은 ESD 보호 디바이스에 따른 회로들의 보호를 위해 ESD 트리거 및 전하 배출 경로들을 형성하는데 사용된다. 단일 및 이중 극성 ESD 보호 디바이스들은 둘 다 집적 회로 다이의 입-출력 회로들의 보호를 위해 집적 회로 다이에 제공될 수 있다.

(52) CPC특허분류

*H01L 27/0629* (2013.01)

*H01L 27/0676* (2013.01)

*H01L 29/778* (2013.01)

(72) 발명자

주, 징

미국, 캘리포니아 90404, 산타 모니카, 아파트

104, 캔자스 아베 2546

셸, 스티븐

미국, 캘리포니아 90503, 토란스, 톰리 애비뉴

20601

---

## 명세서

### 청구범위

#### 청구항 1

정전기 방전(ESD) 보호 디바이스로서,

드레인, 적어도 두 개의 게이트들, 및 소스를 구비한 제 1 전계 효과 트랜지스터(FET) - 상기 제 1 FET의 상기 드레인은 ESD 이벤트로부터 보호될 회로의 회로 노드에 결합됨 -;

상기 제 1 FET의 상기 소스와 공통 노드 사이에 결합된 적어도 하나의 제 1 다이오드; 및

상기 제 1 FET의 상기 적어도 두 개의 게이트들 중 제 1 게이트와 상기 공통 노드 사이에 직렬로 결합된 제 1 저항기 및 제 2 저항기 - 상기 제 1 저항기와 상기 제 2 저항기 사이의 제 1 노드는 상기 제 1 FET의 상기 적어도 두 개의 게이트들 중 제 2 게이트에 결합됨 - 를 포함하는, ESD 보호 디바이스.

#### 청구항 2

제 1 항에 있어서,

상기 공통 노드는 전원 공통부인, ESD 보호 디바이스.

#### 청구항 3

제 1 항에 있어서,

드레인, 적어도 두 개의 게이트들, 및 소스를 구비한 제 2 전계 효과 트랜지스터(FET) - 상기 제 2 FET의 상기 드레인은 전원 공통부에 결합됨 -;

상기 적어도 하나의 제 1 다이오드의 캐소드에 결합된 캐소드를 구비한 적어도 하나의 제 2 다이오드;

상기 제 2 FET의 제 1 게이트와 상기 공통 노드 사이에 직렬로 결합된 제 3 저항기 및 제 4 저항기 - 상기 제 3 저항기와 상기 제 4 저항기 사이의 제 2 노드는 상기 제 2 FET의 제 2 게이트에 결합됨 -; 를 더 포함하는, ESD 보호 디바이스.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 FET의 상기 적어도 두 개의 게이트들 중 하나는, 트리거 게이트이고,

상기 적어도 두 개의 게이트들 중 다른 하나는, 방전 게이트인, ESD 보호 디바이스.

#### 청구항 5

제 3 항에 있어서,

상기 제 1 FET의 또는 상기 제 1 FET와 상기 제 2 FET의 상기 적어도 두 개의 게이트들 중 하나는, 트리거 게이트이고,

상기 적어도 두 개의 게이트들 중 다른 하나는, 방전 게이트인, ESD 보호 디바이스.

#### 청구항 6

제 1 항에 있어서,

상기 제 1 FET는, 공핍-모드 FET인, ESD 보호 디바이스.

#### 청구항 7

제 3 항에 있어서,

상기 제 1 FET는 또는 상기 제 1 FET와 상기 제 2 FET는, 공핍-모드 FET인, ESD 보호 디바이스.

#### 청구항 8

제 1 항에 있어서,

상기 적어도 하나의 제 1 다이오드는, 상기 제 1 FET의 상기 소스와 상기 공통 노드 사이에 직렬로 연결된 두 개의 다이오드인, ESD 보호 디바이스.

#### 청구항 9

제 3 항에 있어서,

상기 적어도 하나의 제 1 다이오드는 또는 상기 적어도 하나의 제 1 다이오드와 상기 적어도 하나의 제 2 다이오드는 각각, 상기 제 1 FET의 또는 상기 제 2 FET의 상기 소스와 상기 공통 노드 사이에 직렬로 연결된 두 개의 다이오드인, ESD 보호 디바이스.

#### 청구항 10

제 1 항에 있어서,

상기 공통 노드가 전기 그라운드에 결합된, ESD 보호 디바이스.

#### 청구항 11

제 6 항 또는 제 7 항에 있어서,

상기 공핍-모드 FET는 고-전자-이동도 트랜지스터(HEMT)인, ESD 보호 디바이스.

#### 청구항 12

제 11 항에 있어서,

상기 HEMT는 부정형 HEMT(pseudomorphic HEMT; pHEMT)인, ESD 보호 디바이스.

#### 청구항 13

제 11 항에 있어서,

상기 HEMT는 변성 HEMT(metamorphic HEMT; mHEMT)인, ESD 보호 디바이스.

#### 청구항 14

제 11 항에 있어서,

상기 HEMT는 유도(induced) HEMT인, ESD 보호 디바이스.

#### 청구항 15

제 1 항에 있어서,

상기 제 1 FET, 상기 적어도 하나의 제 1 다이오드, 그리고 상기 제 1 저항기와 상기 제 2 저항기는, 집적 회로 다이 상에 제조되고 또한 상기 집적 회로 다이의 외부 연결부에 결합된 상기 회로 노드에 결합되는, ESD 보호 디바이스.

#### 청구항 16

제 3 항에 있어서,

상기 제 1 FET 또는 상기 제 1 FET와 상기 제 2 FET, 상기 적어도 하나의 제 1 다이오드 또는 상기 적어도 하나의 제 1 다이오드와 상기 적어도 하나의 제 2 다이오드, 그리고 상기 제 1 저항기와 상기 제 2 저항기 또는 상기 제 1 저항기와 상기 제 2 저항기와 상기 제 3 저항기와 상기 제 4 저항기는, 집적 회로 다이 상에 제조되고 또한 상기 집적 회로 다이의 외부 연결부에 결합된 상기 회로 노드에 결합되는, ESD 보호 디바이스.

**청구항 17**

제 2 항에 있어서,

상기 제 1 FET, 상기 적어도 하나의 제 1 다이오드, 그리고 상기 제 1 저항기와 상기 제 2 저항기는, 집적 회로 다이 상에 제조되고 또한 상기 집적 회로 다이의 외부 연결부에 결합된 상기 회로 노드에 결합되고, 그리고 상기 집적 회로 다이의 상기 외부 연결부는 아날로그 입력부, 디지털 입력부, 아날로그 출력부, 디지털 출력부, 아날로그 입/출력부, 디지털 입/출력부, 전원 연결부, 바이어스 입력부, 및 외부 보상 커패시터로 이루어진 그룹으로부터 선택되는, ESD 보호 디바이스.

**청구항 18**

제 3 항에 있어서,

상기 제 1 FET 또는 상기 제 1 FET와 상기 제 2 FET, 상기 적어도 하나의 제 1 다이오드 또는 상기 적어도 하나의 제 1 다이오드와 상기 적어도 하나의 제 2 다이오드, 그리고 상기 제 1 저항기와 상기 제 2 저항기 또는 상기 제 1 저항기와 상기 제 2 저항기와 상기 제 3 저항기와 상기 제 4 저항기는, 집적 회로 다이 상에 제조되고 또한 상기 집적 회로 다이의 외부 연결부에 결합된 상기 회로 노드에 결합되고, 그리고

상기 집적 회로 다이의 상기 외부 연결부는 아날로그 입력부, 디지털 입력부, 아날로그 출력부, 디지털 출력부, 아날로그 입/출력부, 디지털 입/출력부, 전원 연결부, 바이어스 입력부, 및 외부 보상 커패시터로 이루어진 그룹으로부터 선택되는, ESD 보호 디바이스.

**청구항 19**

제 3 항에 있어서,

상기 제 1 FET 또는 상기 제 1 FET와 상기 제 2 FET, 상기 적어도 하나의 제 1 다이오드 또는 상기 적어도 하나의 제 1 다이오드와 상기 적어도 하나의 제 2 다이오드, 그리고 상기 제 1 저항기와 상기 제 2 저항기 또는 상기 제 1 저항기와 상기 제 2 저항기와 상기 제 3 저항기와 상기 제 4 저항기는, 집적 회로 다이 상에 제조되고 또한 상기 집적 회로 다이의 외부 연결부에 결합된 상기 회로 노드에 결합되고, 그리고

상기 집적 회로 다이의 상기 외부 연결부는 무선 주파수 신호 입력부를 포함하는, ESD 보호 디바이스.

**청구항 20**

제 3 항에 있어서,

상기 제 1 FET 또는 상기 제 1 FET와 상기 제 2 FET, 상기 적어도 하나의 제 1 다이오드 또는 상기 적어도 하나의 제 1 다이오드와 상기 적어도 하나의 제 2 다이오드, 그리고 상기 제 1 저항기와 상기 제 2 저항기 또는 상기 제 1 저항기와 상기 제 2 저항기와 상기 제 3 저항기와 상기 제 4 저항기는, 집적 회로 다이 상에 제조되고 또한 상기 집적 회로 다이의 외부 연결부에 결합된 상기 회로 노드에 결합되고, 그리고

상기 집적 회로 다이의 상기 외부 연결부는 무선 주파수 신호 출력부를 포함하는, ESD 보호 디바이스.

**청구항 21**

삭제

**발명의 설명****기술 분야****관련 특허 출원**

[0001] 본 출원은, Pei-Ming Daniel Chow, Yon-Lin Kok, Jing Zhu 그리고 Steven Schell에 의해 2013년 5월 3일 출원된 발명의 명칭이 "Compact ESD Protection Structure"인 공동 소유의 미국 출원 번호 61/819,252 호의 우선이익을 주장하며, 상기 미국 출원은 모든 목적들을 위해 본 출원에 참조로 통합된다.

**기술 분야**

[0004] 본 개시는 반도체 보호 구조에 관한 것으로, 특히 정전기 방전(ESD) 보호 구조들에 관한 것이다.

## 배경 기술

[0005] 쇼트키 게이트 공핍-모드 전계 효과 디바이스는 그의 부서지기 쉬운 금속 게이트 구조( $0.5 \mu m$  이하의 금속 게이트 길이)로 인해 ESD 손상에 민감하다. CMOS 실리콘이나 바이폴라 트랜지스터 프로세스들과는 달리, 고-전자-이동도 트랜지스터(HEMT) 프로세스에는 콤팩트 ESD 보호 다이오드를 형성하는데 사용될 수 있는 강한 P-N 접합 다이오드가 없다. 헤테로구조 FET(HFET) 또는 변조-도핑된 FET(MODFET)라고도 알려진 HEMT는, 서로 다른 밴드 갭들을 갖는 두 개의 재료들 사이의 접합(즉, 헤테로접합)을, (일반적으로 MOSFET의 경우와 같이) 도핑 영역 대신에 채널로서 포함하는 전계-효과 트랜지스터이다. HEMT의 몇 가지 버전들이 있는데, 예를 들면, 부정형 HEMT(pseudomorphic HEMT; pHEMT), 변성 HEMT(metamorphic HEMT; mHEMT), 유도된(induced) HEMT 등이 있다. pHEMT 디바이스의 게이트와 함께 형성된 몇 가지 큰 쇼트키 다이오드들은 활성 HEMT 회로들을 적절하게 보호하기 위해 직렬로 캐스케이드(cascade)되어야 한다. 이 다중 쇼트키 다이오드들은 고가의 GaAs 집적 회로에서 큰 면적을 소모한다.

[0006] 핫 캐리어(hot carrier) 다이오드라고도 알려진 쇼트키 다이오드는 낮은 순방향 전압 강하와 매우 빠른 스위칭 동작을 구비한 반도체 다이오드이다. 다이오드를 통해 전류가 흐를 때 다이오드 단자들을 가로질러 작은 전압 강하가 있다. 정상 다이오드는 0.6 내지 1.7 볼트 사이의 전압 강하를 갖겠지만, 쇼트키 다이오드 전압 강하는 보통 0.15와 0.45 볼트 사이에 있다. 이러한 보다 낮은 전압 강하는 보다 좋은 시스템 효율과 보다 높은 스위칭 속도를 제공한다. 쇼트키 다이오드에서는 반도체-금속 접합이 반도체와 금속 사이에 형성되고 따라서 쇼트키 장벽을 생성한다. N형 반도체는 캐소드 역할을 하며, 금속 층은 쇼트키 다이오드의 애노드 역할을 한다. 이 쇼트키 장벽으로 인해 순방향 전압 강하가 낮아지고 또한 스위칭이 매우 빨라진다. 몇몇 큰 쇼트키 다이오드들을 캐스케이드함으로써 ESD 보호가 제공될 수 있다. 쇼트키 다이오드의 낮은 턴 온 전압으로 인하여, 동작 전압을 처리하기 위해서는 여러 적층 다이오드들이 필요하고, 또한 전류를 처리하기 위해서는 큰 영역이 필요하다. 따라서, 쇼트키 다이오드 구성은 이용하는 것은 큰 영역을 필요로 한다.

## 발명의 내용

### 해결하려는 과제

[0007] 그러므로, 쇼트키 다이오드를 사용할 필요가 없는 HEMT 및 다른 반도체 디바이스들과 호환성 있는 효율적이고 콤팩트한 ESD 보호 구조가 필요하다.

### 과제의 해결 수단

[0008] 실시예에 따르면, 정전기 방전(ESD) 보호 디바이스는: 드레인, 적어도 두 개의 게이트들, 및 소스를 구비한 전계 효과 트랜지스터(FET) - 상기 드레인은 ESD 이벤트로부터 보호될 회로의 노드에 결합될 수 있음 -; 상기 FET의 소스와 전원 공통부 사이에 결합하는 적어도 하나의 다이오드; 상기 FET의 상기 적어도 두 개의 게이트들 사이에 결합하는 제 1 저항기; 및 상기 적어도 두 개의 게이트들 중 하나와 상기 전원 공통부에 결합하는 제 2 저항기를 포함할 수 있다.

[0009] 추가 실시예에 따르면, 상기 적어도 두 개의 게이트들 중 하나는 트리거 게이트일 수 있고, 상기 적어도 두 개의 게이트들 중 다른 하나는 방전 게이트일 수 있다. 추가 실시예에 따르면, 상기 FET는 공핍-모드 FET일 수 있다. 추가 실시예에 따르면, 상기 적어도 하나의 다이오드는 상기 FET의 소스와 전원 공통부 사이에 직렬로 연결되는 두 개의 다이오드일 수 있다. 추가 실시예에 따르면, 상기 전원 공통부는 전기 그라운드에 결합할 수 있다. 추가 실시예에 따르면, 상기 공핍-모드 FET는 고-전자-이동도 트랜지스터(HEMT)일 수 있다. 추가 실시예에 따르면, 상기 HEMT는 부정형 HEMT(pseudomorphic HEMT; pHEMT)일 수 있다. 추가 실시예에 따르면, 상기 HEMT는 변성 HEMT(metamorphic HEMT; mHEMT)일 수 있다. 추가 실시예에 따르면, 상기 HEMT는 유도(induced) HEMT일 수 있다.

[0010] 추가 실시예에 따르면, 상기 FET, 상기 적어도 하나의 다이오드, 및 상기 제 1 및 제 2 저항기들은 집적 회로 다이 상에 제조될 수 있고, 상기 집적 회로 다이의 외부 연결부에 결합될 수 있는 상기 회로 노드와 결합할 수 있다. 추가 실시예에 따르면, 상기 집적 회로 다이의 상기 외부 연결부의 기능부는 아날로그 입력부, 디지털 입력부, 아날로그 출력부, 디지털 출력부, 아날로그 입/출력부, 디지털 입/출력부, 전원 연결부, 바이어스 입력부, 및 외부 보상 커패시터로 이루어진 그룹으로부터 선택될 수 있다.

[0011]

또 하나의 실시예에 따르면, 정전기 방전(ESD) 보호 디바이스는: 드레인, 적어도 두 개의 게이트들, 및 소스를 구비한 제 1 전계 효과 트랜지스터(FET) - 상기 제 1 FET의 드레인은 ESD 이벤트로부터 보호될 회로의 노드에 결합될 수 있음 -; 상기 제 1 FET의 소스에 결합하는 애노드를 갖는 적어도 하나의 제 1 다이오드; 상기 제 1 FET의 상기 적어도 두 개의 게이트들 사이에 결합하는 제 1 저항기; 상기 적어도 두 개의 게이트들 중 하나와 상기 적어도 하나의 제 1 다이오드의 캐소드에 결합하는 제 2 저항기; 드레인, 적어도 두 개의 게이트들, 및 소스를 구비한 제 2 전계 효과 트랜지스터(FET) - 상기 제 2 FET의 드레인은 전원 공통부에 결합될 수 있음 -; 상기 적어도 하나의 제 1 다이오드의 캐소드를 구비하는 적어도 하나의 제 2 다이오드; 상기 제 2 FET의 상기 적어도 두 개의 게이트들 사이에 결합하는 제 3 저항기; 및 상기 제 2 FET의 상기 적어도 두 개의 게이트들 중 하나와 상기 적어도 하나의 제 2 다이오드의 캐소드에 결합하는 제 4 저항기를 포함할 수 있다.

[0012]

추가 실시예에 따르면, 상기 제 1 및 제 2 FET들의 상기 적어도 두 개의 게이트들 중 하나는 트리거 게이트들일 수 있고, 상기 제 1 및 제 2 FET들의 상기 적어도 두 개의 게이트들 중 다른 하나는 방전 게이트들일 수 있다. 추가 실시예에 따르면, 상기 제 1 및 제 2 FET들은 공핍-모드 FET들일 수 있다. 추가 실시예에 따르면, 상기 적어도 하나의 제 1 및 제 2 다이오드들은 두 개의 다이오드들일 수 있으며, 이 두 개의 다이오드들의 각각은 상기 제 1 및 제 2 FET들의 소스들 사이에 직렬로 연결된다. 추가 실시예에 따르면, 상기 전원 공통부는 전기 그라운드에 결합할 수 있다. 추가 실시예에 따르면, 상기 제 1 및 제 2 공핍-모드 FET들은 고-전자-이동도 트랜지스터(HEMT)들일 수 있다. 추가 실시예에 따르면, 상기 HEMT들은 부정형 HEMT(pHEMT)들, 변성 HEMT(mHEMT)들 및 유도 HEMT들로 이루어진 그룹으로부터 선택될 수 있다.

[0013]

추가 실시예에 따르면, 상기 제 1 및 제 2 FET들, 상기 적어도 하나의 제 1 및 제 2 다이오드들, 및 상기 제 1, 제 2, 제 3 및 제 4 저항기들은 접적 회로 다이 상에 제조될 수 있고, 상기 접적 회로 다이의 외부 연결부에 결합될 수 있는 상기 회로 노드와 결합할 수 있다. 추가 실시예에 따르면, 상기 접적 회로 다이의 상기 외부 연결부의 기능부는 무선 주파수 신호 입력부를 포함할 수 있다. 추가 실시예에 따르면, 상기 접적 회로 다이의 상기 외부 연결부의 기능부는 무선 주파수 신호 출력부를 포함할 수 있다.

### 도면의 간단한 설명

[0014]

본 개시는 첨부 도면들과 결합된 이하의 설명을 참조하면 보다 완전하게 이해될 수 있다.

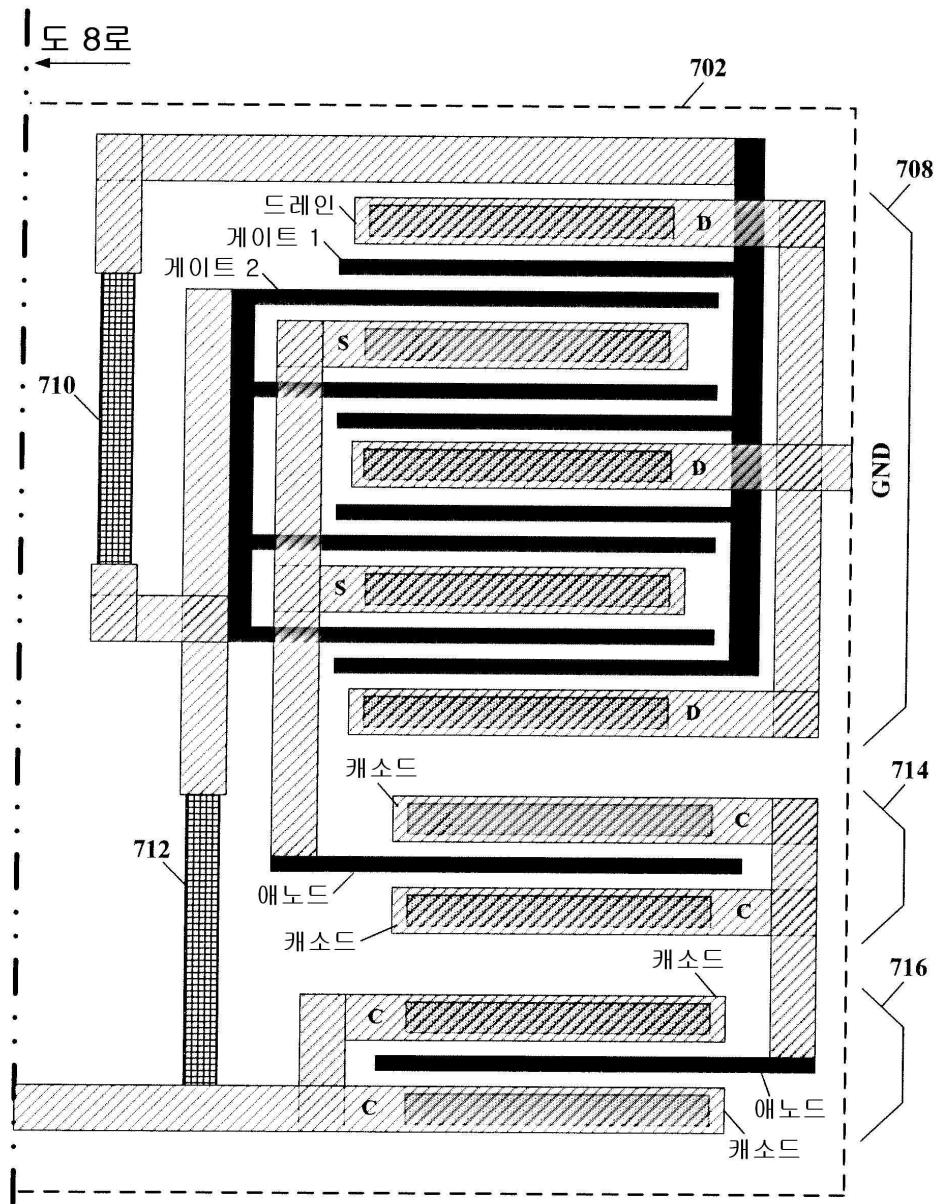

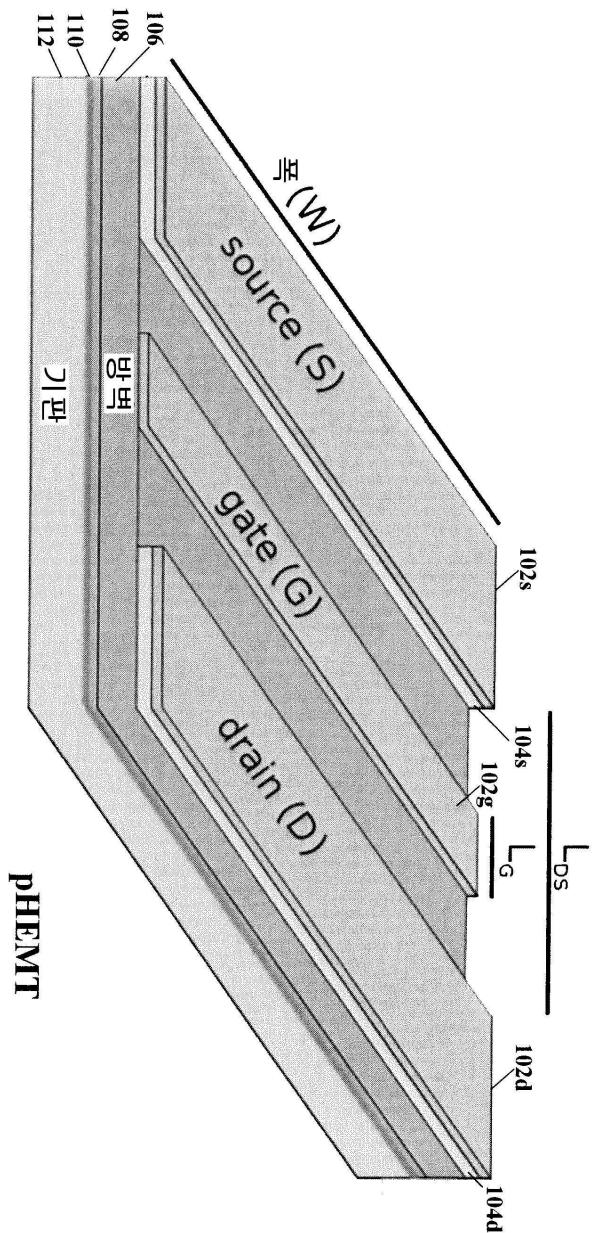

도 1은 본 개시의 교시에 따른, HEMT 디바이스의 개략적인 등각 단면도(isometric cross section diagram)이다.

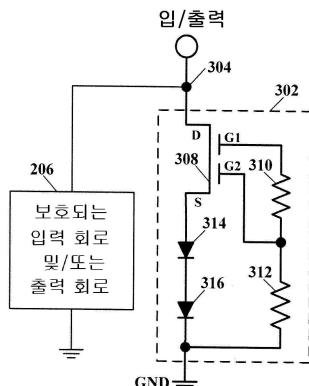

도 2는 직류(DC) 및 제어 포트들을 위한 종래 기술의 단일 극성 공핍-모드 FET ESD 보호 디바이스의 개략도이다.

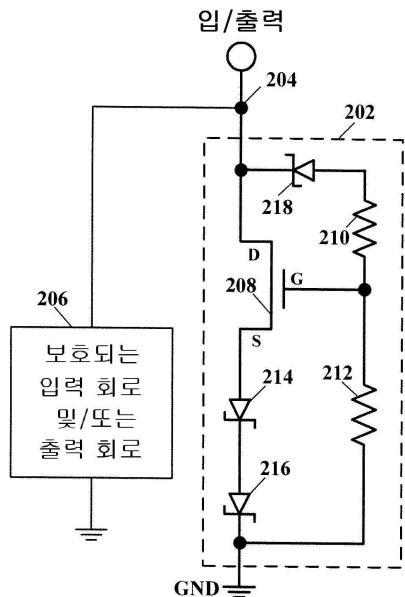

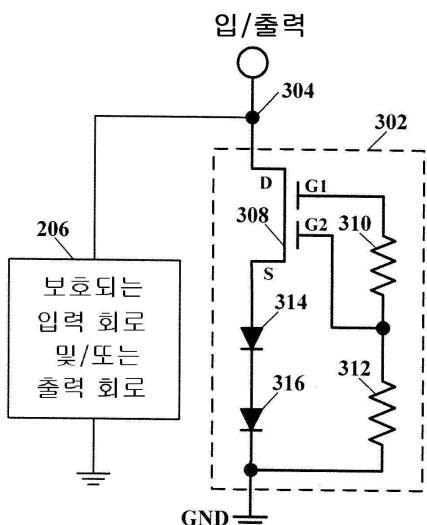

도 3은 본 개시의 특정 예시의 실시예에 따른, 직류(DC) 및 제어 포트들을 위한 단일 극성 멀티-게이트 쇼트키 공핍-모드 FET ESD 보호 디바이스의 개략도이다.

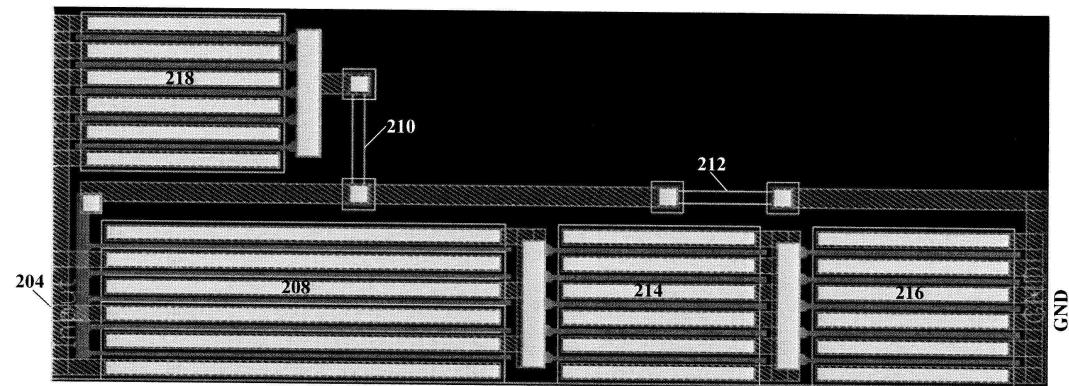

도 4는 도 2에 도시된 ESD 보호 디바이스에 대한 종래 기술 구조의 개략적인 평면도이다.

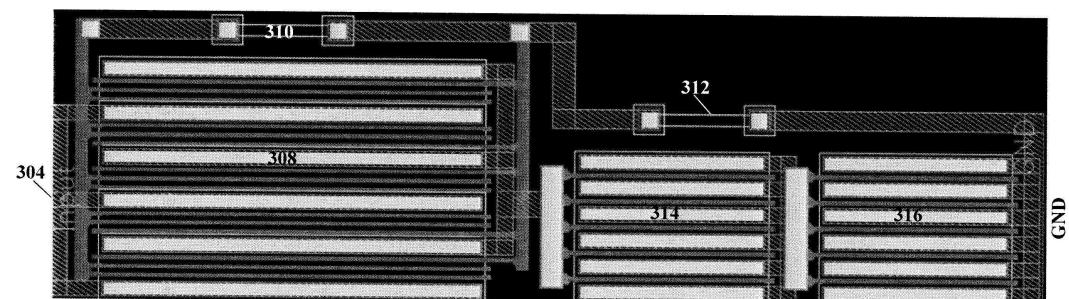

도 5는 본 개시의 특정 예시의 실시예에 따른, 도 3에 도시된 ESD 보호 디바이스에 대한 구조의 개략적인 평면도이다.

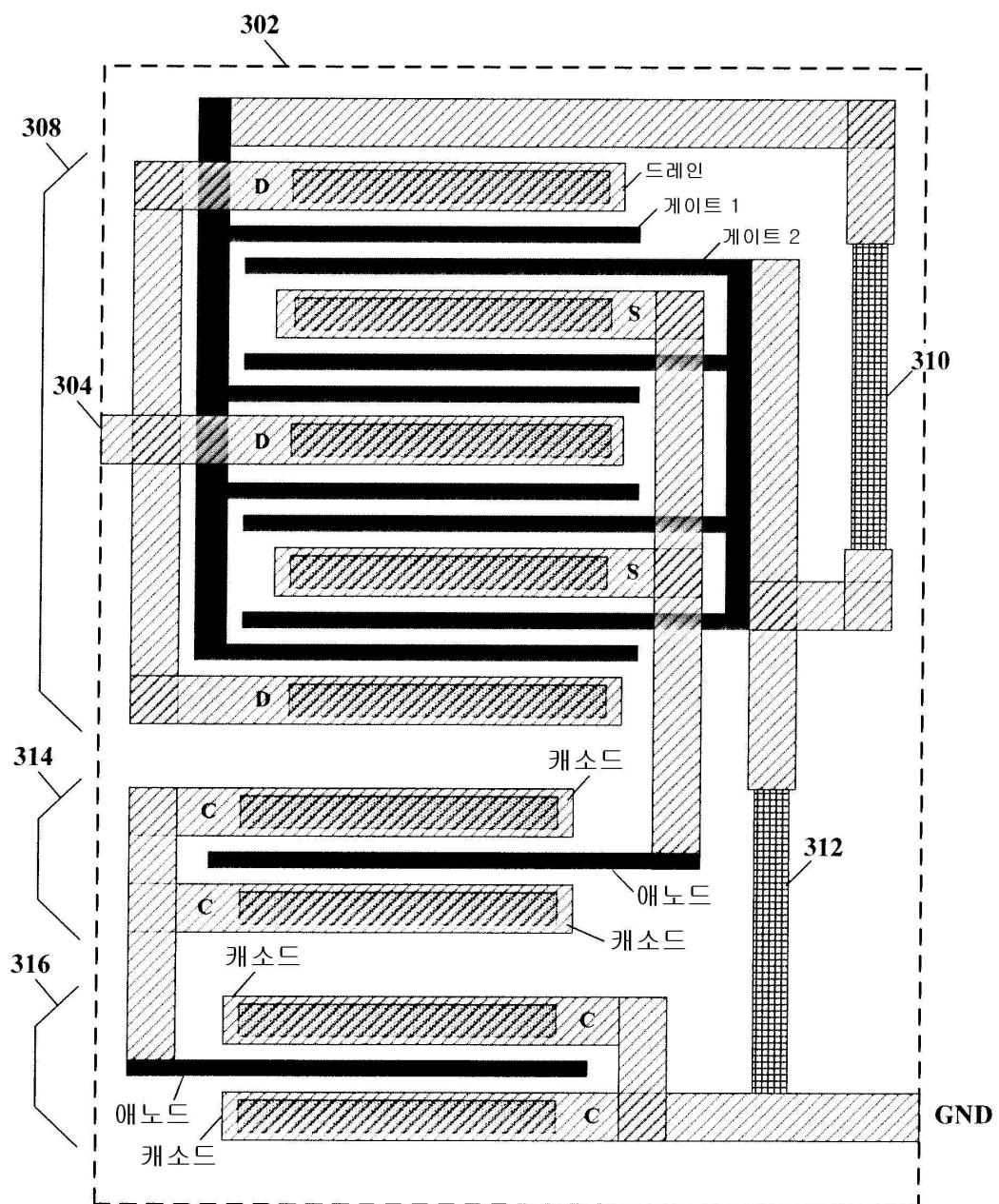

도 6은 본 개시의 특정 예시의 실시예에 따른, 도 3에 도시된 ESD 보호 디바이스에 대한 구조의 보다 상세한 개략적인 평면도이다.

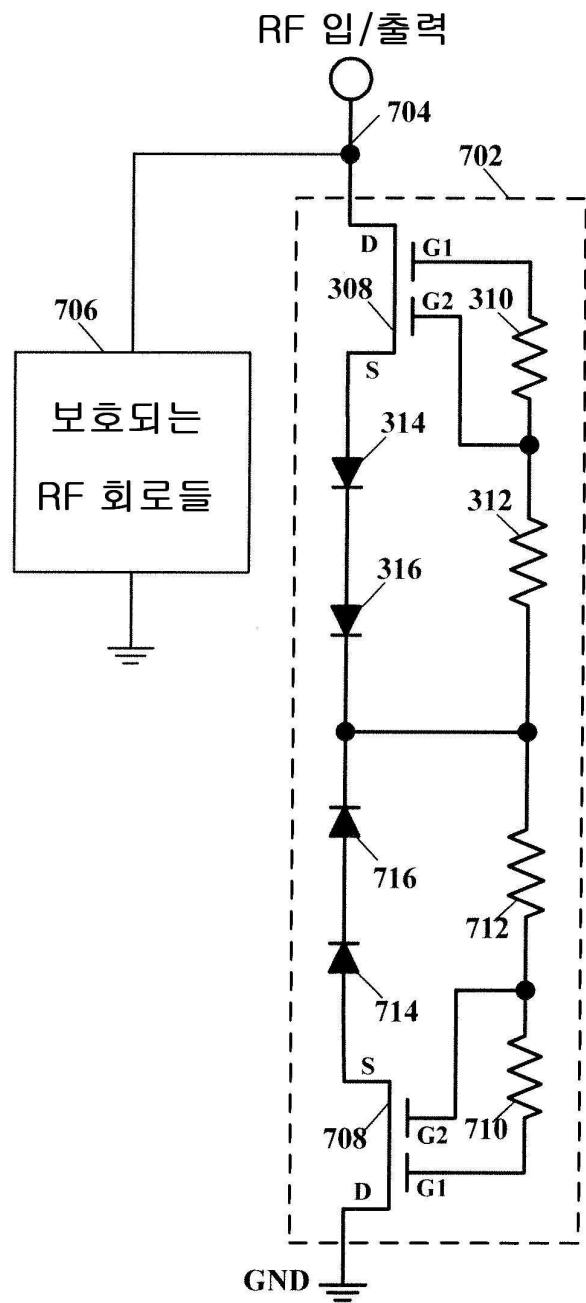

도 7은 본 개시의 또 하나의 특정 예시의 실시예에 따른, 무선 주파수(RF) 포트들을 위한 이중 극성 멀티-게이트 쇼트키 공핍-모드 FET ESD 보호 디바이스의 개략도이다.

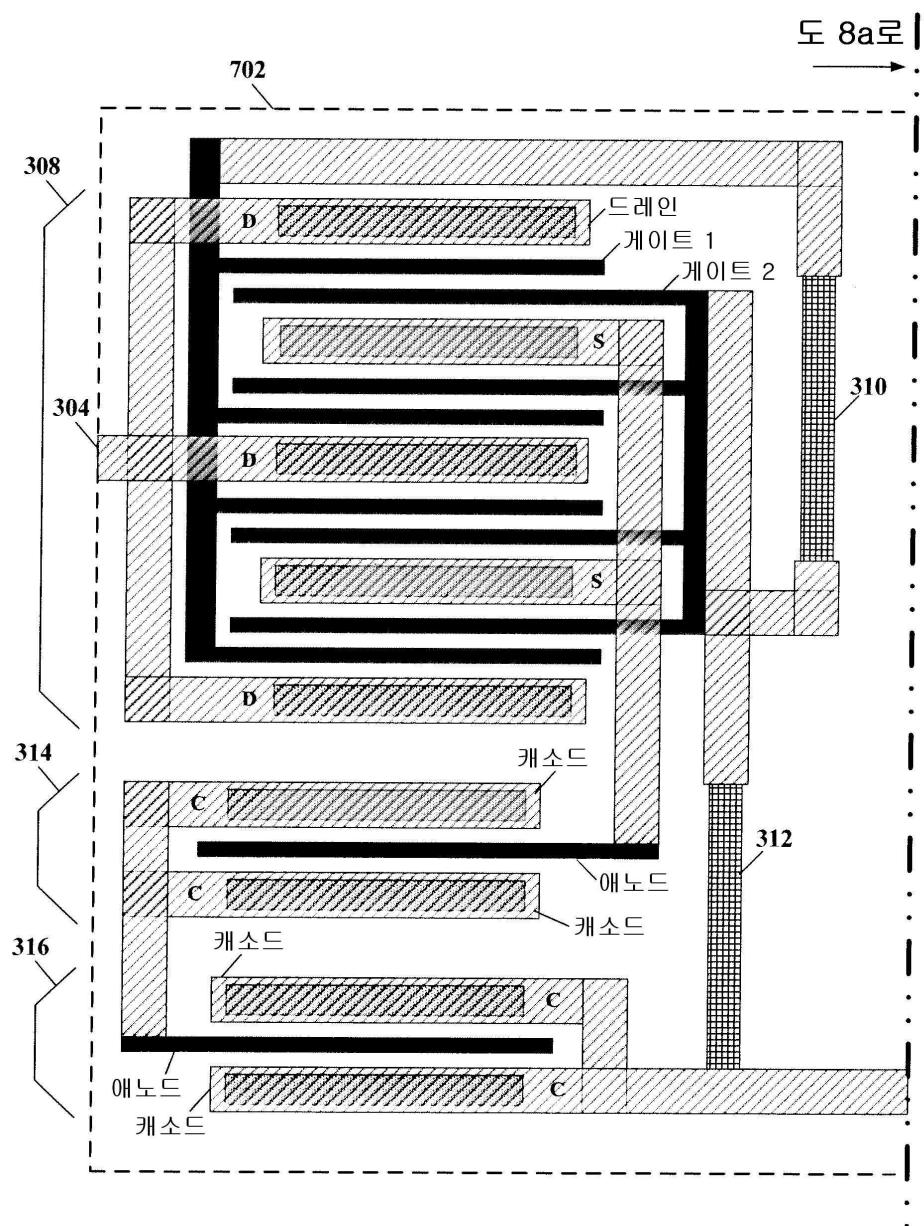

도 8 및 도 8a는 본 개시의 특정 예시의 실시예에 따른, 도 7에 도시된 ESD 보호 디바이스에 대한 구조의 개략적인 평면도이다.

본 개시는 다양한 변형들 및 대안의 형태들을 허용하지만, 그의 특정 예시의 실시예들이 도면들에 도시되었고 본 명세서에서 상세히 설명된다. 하지만, 그 특정 예시의 실시예들에 대한 설명은 본 개시를 여기에서 개시된 특정 형태들로 한정하고자 하는 것이 아니고, 오히려, 본 개시는 부속 특허청구범위에 의해 정의되는 모든 변형들 및 균등물들을 포함하는 것으로 이해되어야 한다.

### 발명을 실시하기 위한 구체적인 내용

- [0015] 다양한 실시예들에 따르면, 헤테로구조 FET 또는 변조-도핑된 FET라고도 알려진 유사 형태의 고 전자 이동도 트랜지스터(pseudomorphic high electron mobility transistor; pHEMT)가 여기서는 본 명세서에 개시된 다양한 실시예들에 따른 콤팩트 ESD 보호 디바이스의 개념을 설명하기 위한 예로서 사용된다. 지금까지 몇몇 큰 쇼트키 다이오드들은, 전압을 증가시키고 활성 회로들을 적절하게 보호하기 위해 pHEMT 디바이스의 게이트와 함께 형성되고 직렬로 캐스케이드되어야 했다. 이 다중 다이오드 디바이스들은 고가의 GaAs 집적 회로 다이에서 큰 면적을 소모했다. 본 개시의 다양한 실시예들에 따르면, 콤팩트 ESD 보호 디바이스를 형성하기 위해 다중-게이트 HEMT를 사용하는 것이 제안된다. HEMT 디바이스의 다중-게이트들은 ESD 보호 디바이스들 및 구조들의 후에 있는 (following) 회로들의 보호를 위해 ESD 트리거 및 전하 배출(charge draining) 경로들을 형성하는데 사용될 수 있다. ESD 보호 디바이스 구조는 다중 다이오드 ESD 디바이스 구조보다도 훨씬 더 작은 영역에 배치될 수 있다. 다양한 유형들의 HEMT 디바이스들, 예를 들어 pHEMT, mHEMT, 유도 HEMT 등은 여기에 개시된 ESD 보호 디바이스들과 함께 사용될 수 있음이 예상되고 본 개시의 범위 내에 있다.

- [0016] 이제 도면들을 보면, 예시적인 실시예들의 세부사항들이 개략적으로 도시되어 있다. 도면들에서 같은 요소들은 같은 숫자들로 나타내어지며, 유사한 요소들은 같은 숫자들에 다른 소문자 첨자를 붙여서 나타내어질 것이다.

- [0017] 도 1을 보면, 본 개시의 교시에 따른, HEMT 디바이스의 개략적인 등각 단면도가 도시되어 있다. pHEMT는 예시를 위해 도시되었지만, 다른 HEMT 디바이스들이 본 개시의 교시에 따라 유사하게 사용될 수 있음이 예상되고 본 발명의 범위 내에 있다. HEMT 디바이스는 기판(112), 2차원 전자 가스 층(110), 스페이서(108), 방벽(106), 캡핑(capping) 층(104), 및 금속 드레인, 소스 및 게이트 전극들(102)을 포함할 수 있다. 소스, 게이트 및 드레인 금속(102)은 금(gold)을 포함할 수 있지만 이것으로 한정되는 것은 아니다. 방벽(106)은 알루미늄 갈륨 비소(AIGaAs)를 포함할 수 있지만 이것으로 한정되는 것은 아니다. 스페이서(108)는 갈륨 비소(GaAs)를 포함할 수 있지만 이것으로 한정되는 것은 아니다. 2차원 전자 가스 층(110)은 인듐 갈륨 비소(InGaAs)를 포함할 수 있지만 이것으로 한정되는 것은 아니다. 기판은 고 저항성 GaAs를 포함할 수 있지만 이것으로 한정되는 것은 아니다. 제 1 저항기(210)는 약 500 옴(ohms) 내지 약 2000 옴의 저항값을 가질 수 있다. 제 2 저항기(212)는 약 2000 옴의 저항값을 가질 수 있다.

- [0018] 도 2 및 도 4를 보면, 직류(DC) 및 제어 포트들을 위한 종래 기술의 단일 극성 공핍-모드 FET ESD 보호 디바이스의 개략도와, 도 2에 도시된 ESD 보호 디바이스에 대한 종래 기술 구조의 개략적인 평면도가 도시되어 있다. 단일 극성 단일-게이트 ESD 보호 디바이스(202)는 집적 회로 패키지(미도시됨)의 회로들(206)의 제어 신호 및/또는 바이어스 전원(bias supply) 노드들(핀들)을 보호하는데 사용되어 왔다. ESD 보호 디바이스(202)는 드레인(D), 소스(S) 및 단일 게이트(G)를 갖는 전계 효과 트랜지스터(FET)(208); 제 1 및 제 2 쇼트키 다이오드들(214 및 216), 제 3 다이오드(218), 및 제 1 및 제 2 게이트 저항기들(210 및 212)을 포함할 수 있다. 제 3 다이오드(218)는, ESD 이벤트가 발생할 때 전도함으로써(애벌란시 항복(avalanche breakdown)으로 됨으로써) 트랜지스터(208)를 턴 온하는 트리거 다이오드이다. 쇼트키 다이오드들(214 및 216)은 공핍 모드 트랜지스터(208)가 정상 동작 중에 턴 온하여 전류를 전도하는 것을 방지하기 위해 전압 레벨 시프팅에 사용된다.

- [0019] 도 3, 도 5 및 도 6을 보면, 본 개시의 특정 예시의 실시예에 따른, 직류(DC) 및 제어 포트들을 위한 단일 극성 멀티-게이트 쇼트키 공핍-모드 FET ESD 보호 디바이스의 개략도와, 도 3에 도시된 ESD 보호 디바이스에 대한 구조의 개략적인 평면도들이 도시되어 있다. 쇼트키 멀티-게이트들을 갖는 단일 극성 ESD 보호 디바이스(302)는 집적 회로 패키지(미도시됨)의 회로들(306)의 제어 신호 및/또는 바이어스 전원 노드들(핀들)을 보호하는데 사용될 수 있다. ESD 보호 디바이스(302)는 드레인(D), 소스(S), 제 1 및 제 2 트리거 게이트들(G1 및 G2)을 갖는 멀티-게이트 쇼트키 공핍-모드 전계 효과 트랜지스터(FET)(308) - 예컨대, HEMT 디바이스 -, 제 1 및 제 2 다이오드들(314, 316), 및 제 1 및 제 2 게이트 저항기들(310 및 312)을 포함할 수 있다. FET(308)은 두 개 이상의 게이트들을 가질 수 있음이 예상되고 본 개시의 범위 내에 있다. FET(308)의 소스와 전원 공통부, 예컨대 전기 그라운드 사이에는 적어도 하나의 레벨 시프팅 다이오드가 결합될 수 있다. FET(308)의 드레인은 집적 회로(IC) 패키지(미도시됨)의 외부 연결부(핀)에 결합될 수 있는 노드(304)에 결합할 수 있다. IC 패키지의 외부 연결부(핀)는 예를 들어 아날로그 입력부, 디지털 입력부, 아날로그 출력부, 디지털 출력부, 아날로그 입/출력부, 디지털 입/출력부, 전원 연결부, 바이어스 입력부, 외부 보상 커패시터 등으로 사용될 수 있지만, 이것들로 한정되지는 않는다.

- [0020] 네거티브 정전기 전하들이 노드(304)에 축적될 때, 제 2 트리거 게이트(G2)는 순방향 바이어스되어 이 전하들을 제 2 게이트 저항기(312)를 통해 그라운드로 배출할 것이다. 포지티브 정전기 전하들이 노드(304)에 축적될 때에는, 제 1 트리거 게이트(G1)가 역방향 절연파괴(reverse breakdown)에 있을 때까지 포지티브 전위가 높아질(built up) 것이다. 이 절연파괴 전류(breakdown current)는 그라운드로 흐르고 제 2 게이트 저항기(312)의 양

단에 포지티브 전위를 확립할 것이다. 따라서, 게이트-소스 전위가 직렬 연결된 제 1 및 제 2 다이오드들(314 및 316)의 턴-온 전압보다 더욱 포지티브할 때, 제 2 게이트(G2)를 가진 FET(308)를 턴 온하기에 충분한 전압을 제공한다. 이 제 1 및 제 2 다이오드들(314 및 316)은 FET(308)의 소스와 전원 공통부, 예를 들어 그라운드 사이에 결합되고, 그리고 공핍 모드 트랜지스터가 턴 온(전도)하는 것을 방지하기 위하여 전압 레벨 시프팅을 제공한다. FET(308)의 드레인 전류는 노드(304)에서의 포지티브 정전기 전하들을 소산시키기 위한 또 하나의 경로를 제공하고, 제 1 트리거 게이트(G1)가 제 1 트리거 게이트(G1)를 손상시킬 수 있는 과도한 절연파괴 전류를 갖지 않도록 돋는다.

[0021] 따라서, 멀티-게이트 구조 FET(308)는 트리거 다이오드 디바이스와 방전 게이트 FET를 결합하고 값비싼 집적 회로 다이 영역을 절약하는 유일한 방법이다. 게다가, 단지 3개의 활성 디바이스 영역들만이 단일 극성 멀티-게이트 ESD 보호 디바이스(302)에 필요하다: 1) FET(308), 2) 및 3) 제 1 및 제 2 다이오드들(314 및 316). 종래 기술의 ESD 보호 디바이스(202)는 4개의 활성 디바이스 영역들, 즉 1) FET(208), 2) 트리거 제 3 다이오드(218), 3) 및 4) 레벨 시프팅 다이오드들(214 및 216)을 필요로 한다. 따라서, 본 개시의 교시에 따르면, 종래 기술의 ESD 보호 디바이스(202)는, 동일한 ESD 보호 레벨을 달성하기 위해서는 단일 극성 다중-게이트 ESD 보호 디바이스(302)가 필요로 하는 것보다 집적 회로 다이(미도시됨) 상에 더 큰 활성 디바이스 영역을 필요로 한다.

[0022] 도 7, 도 8 및 도 8a를 보면, 본 개시의 또 하나의 특정 예시의 실시예에 따른, 무선 주파수(RF) 포트들을 위한 이중 극성 멀티-게이트 쇼트키 공핍-모드 FET ESD 보호 디바이스의 개략도와, 도 7에 도시된 ESD 보호 디바이스에 대한 구조의 개략적인 평면도가 도시되어 있다. 이중 극성 멀티-게이트 쇼트키 공핍-모드 FET ESD 보호 디바이스(702)는 집적 회로 패키지(미도시됨)의 회로들(706)의 제어, 신호 및/또는 바이어스 전원 노드들(핀들)을 보호하는데 사용될 수 있다. ESD 보호 디바이스(702)는, 드레인, 소스, 및 제 1 및 제 2 게이트들(G1 및 G2)을 구비한 제 1 HEMT 디바이스(308); 제 1 및 제 2 다이오드들(314 및 316); 제 1 및 제 2 게이트 저항기들(310 및 312); 드레인, 소스, 및 제 1 및 제 2 게이트들(G1 및 G2)을 구비한 제 2 HEMT 디바이스(708); 제 3 및 제 4 다이오드들(714 및 716); 그리고 제 3 및 제 4 게이트 저항기들(710 및 712)을 포함할 수 있다. ESD 보호 디바이스(702)는 높은 RF 파워 디바이스들과 연관되는 RF 포트들과 함께 유리하게 사용될 수 있다. 이 ESD 보호 회로는 큰 포지티브 및 네거티브 RF 전압 스윙(swing)들의 존재 하에 사용될 수 있다. 이러한 이중 극성 멀티-게이트 FET ESD 보호 디바이스(702)의 동작 원리는 단일 극성 멀티-게이트 ESD 보호 디바이스(308)의 동작 원리와 실질적으로 유사하다. 요소들(708-716)은 요소들(308-316)의 거울상(mirror image)으로서 역할을 한다.

[0023] 본 개시의 실시예들은 본 개시의 예시적인 실시예들을 참조하여 도시되고 설명되고 정의되었지만, 이러한 참조는 본 개시의 한정을 의미하지 않고 이러한 한정이 추정되지도 않는다. 개시된 본 발명은 이 기술분야에 통상의 기술을 가지고 본 개시의 혜택을 갖는 사람들에게는 형태와 기능에 있어서 상당한 수정, 대체, 및 균등물들이 가능하다. 본 개시의 도시되고 설명된 실시예들은 단지 예로서, 본 개시의 범위를 한정하지 않는다.

## 도면

## 도면1

## 도면2

## 종래기술

## 도면3

도면4

종래기술

도면5

도면6

도면7

## 도면8

도면8a