(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4856544号

(P4856544)

(45) 発行日 平成24年1月18日(2012.1.18)

(24) 登録日 平成23年11月4日(2011.11.4)

(51) Int.Cl.

H01L 21/20 (2006.01)

H01L 27/12 (2006.01)

H01L 21/02 (2006.01)

F 1

H01L 21/20

H01L 27/12

E

請求項の数 26 (全 14 頁)

(21) 出願番号 特願2006-526273 (P2006-526273)

(86) (22) 出願日 平成16年9月10日 (2004.9.10)

(65) 公表番号 特表2007-505502 (P2007-505502A)

(43) 公表日 平成19年3月8日 (2007.3.8)

(86) 國際出願番号 PCT/US2004/029378

(87) 國際公開番号 WO2005/031810

(87) 國際公開日 平成17年4月7日 (2005.4.7)

審査請求日 平成19年9月4日 (2007.9.4)

(31) 優先権主張番号 10/662,028

(32) 優先日 平成15年9月12日 (2003.9.12)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】埋込多孔質シリコン層の酸化によるシリコン・ゲルマニウムオンインシュレータ構造の形成

## (57) 【特許請求の範囲】

## 【請求項1】

SiGeオンインシュレータ基板材料を製作する方法であって、正孔を多く含む領域が中に形成されたSi含有基板、および前記Si含有基板の上のGe含有層を備える構造を提供するステップであって、当該ステップは、

(i) 初期Si含有基板上でp型を多く含むエピタキシャル層を成長させ、前記p型を多く含むエピタキシャル層の上に単結晶Si含有層を形成し、前記単結晶Si含有層上に前記Ge含有層を形成すること、

(ii) 初期単結晶Si含有基板にp型ドーパントをイオン注入し、次いで、前記基板上に前記Ge含有層を形成すること、または

(iii) 初期単結晶Si含有基板上に前記Ge含有層を形成し、次いで、前記基板にp型ドーパントをイオン注入して正孔を多く含む前記領域を形成すること、のいずれか1つを含み、

さらに、正孔を多く含む前記領域を多孔質領域に転換するステップと、緩和したSiGeオンインシュレータ材料を提供するために、酸素含有環境で前記多孔質領域を含む前記構造をアニールする第1のアニール・ステップを含む、方法。

## 【請求項2】

前記p型ドーパントは、Ga、Al、B、またはBF<sub>2</sub>である、請求項1に記載の方法。

## 【請求項3】

10

20

前記 p 型ドーパントは B (ボロン) であり、前記 B は、100 keV ~ 500 keV のエネルギー、かつ、 $5 \times 10^{15}$  原子 / cm<sup>2</sup> ~  $5 \times 10^{16}$  原子 / cm<sup>2</sup> のドーズで注入される、請求項 1 に記載の方法。

【請求項 4】

前記 p 型ドーパントは BF<sub>2</sub> であり、前記 BF<sub>2</sub> は、500 keV ~ 2500 keV のエネルギー、かつ、 $5 \times 10^{15}$  原子 / cm<sup>2</sup> ~  $5 \times 10^{16}$  原子 / cm<sup>2</sup> のドーズで注入される、請求項 1 に記載の方法。

【請求項 5】

正孔を多く含む前記領域の p 型ドーパント濃度は、 $1 \times 10^{19}$  原子 / cm<sup>3</sup> であるか、またはそれよりも高い、請求項 1 に記載の方法。

10

【請求項 6】

正孔を多く含む前記領域の p 型ドーパント濃度は、 $1 \times 10^{20}$  原子 / cm<sup>3</sup> ~  $5 \times 10^{20}$  原子 / cm<sup>3</sup> である、請求項 1 に記載の方法。

【請求項 7】

前記転換するステップの前に、前記イオン注入した領域を活性化するための第 2 のアニール・ステップをさらに含む、請求項 1 に記載の方法。

【請求項 8】

前記第 1 または第 2 のアニール・ステップは、熱処理炉によるアニール、急速熱アニール、およびスパイク・アニールからなる群から選択される、請求項 1 または 7 に記載の方法。

20

【請求項 9】

前記第 1 または第 2 のアニール・ステップは熱処理炉によるアニール・ステップであり、前記熱処理炉によるアニール・ステップは、不活性ガス雰囲気または酸化環境あるいはその組合せの存在下で、600 またはそれよりも高い温度で 15 分またはそれよりも長く実施される、請求項 8 に記載の方法。

【請求項 10】

前記第 1 または第 2 のアニール・ステップは急速熱アニール (RTA) ステップであり、前記 RTA ステップは、不活性ガス雰囲気または酸化雰囲気あるいはその組合せの存在下で、800 またはそれよりも高い温度で 5 分またはそれよりも短く実施される、請求項 8 に記載の方法。

30

【請求項 11】

前記第 1 または第 2 のアニール・ステップはスパイク・アニール・ステップであり、前記スパイク・アニール・ステップは、不活性ガス雰囲気または酸化雰囲気あるいはその組合せの存在下で、900 またはそれよりも高い温度で 1 秒またはそれよりも短く実施される、請求項 8 に記載の方法。

【請求項 12】

前記転換ステップは、電解陽極化プロセスを含む、請求項 1 に記載の方法。

【請求項 13】

前記陽極化プロセスは、HF 含有溶液の存在下で実施される、請求項 12 に記載の方法

【請求項 14】

前記陽極化プロセスは、0.05 ~ 50 ミリアンペア / cm<sup>2</sup> の電流密度で動作する定電流源を使用して実施される、請求項 12 に記載の方法。

40

【請求項 15】

前記多孔質領域の多孔率は0.1 % であるか、またはそれよりも高い、請求項 1 に記載の方法。

【請求項 16】

前記転換ステップの後、前記アニール・ステップの前に、前記 Ge 含有層の上にキャップ層を形成することをさらに含む、請求項 1 に記載の方法。

【請求項 17】

前記キャップ層は Si 材料を含む、請求項 16 に記載の方法。

50

## 【請求項 18】

前記酸素含有環境はさらに、不活性ガスを含む、請求項 1 に記載の方法。

## 【請求項 19】

前記酸素含有環境は、O<sub>2</sub>、NO、N<sub>2</sub>O、オゾン、および空気からなる群から選択される、請求項 18 に記載の方法。

## 【請求項 20】

前記アニールは、650 ~ 1350 の温度で実施される、請求項 1 に記載の方法。

## 【請求項 21】

前記アニールにより、前記緩和した SiGe オンインシュレータ材料の上に表面酸化物が形成される、請求項 1 に記載の方法。

10

## 【請求項 22】

前記 SiGe オンインシュレータ材料は熱酸化物である、請求項 1 に記載の方法。

## 【請求項 23】

前記緩和した SiGe オンインシュレータ材料の上に Si 層を形成することをさらに含む、請求項 1 に記載の方法。

## 【請求項 24】

正孔を多く含む前記領域は離散アイランドを含み、前記緩和した SiGe オンインシュレータ材料は、熱酸化物の離散アイランドを含む、請求項 1 に記載の方法。

## 【請求項 25】

前記提供するステップ、転換するステップ、およびアニール・ステップを任意の回数繰り返して、多層 SiGe オンインシュレータ材料を提供することをさらに含む、請求項 1 に記載の方法。

20

## 【請求項 26】

SiGe オンインシュレータ基板材料を製作する方法であって、

高濃度の p 型ドーパントの領域が中に形成された Si 含有基板、および前記 Si 含有基板の上の Ge 含有層を備える構造を提供するステップと、

HF 含有溶液を使用する陽極化プロセスを利用して、前記 p 型ドーパントの領域を多孔質領域に転換するステップと、

緩和した SiGe オンインシュレータ材料を提供するために、前記多孔質領域を含む前記構造を酸化するステップとを含む、方法。

30

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体構造を製作する方法に関し、より詳細には、製作プロセスにおいてウエハ接合または酸素注入あるいはその両方を用いない SiGe オンインシュレータ (SGOI) 構造を製作する方法に関する。

## 【背景技術】

## 【0002】

半導体産業では、最近、CMOS に応用するために、歪みシリコン系ヘテロ構造を使用して高キャリア移動度構造を実現する高水準の活動がなされている。従来、NFT 型および PFT 型のデバイスの性能を高めるためにこれを実施するための先行技術の方法は、(約 1 ~ 約 5 ミクロン程度の) 厚い緩和 SiGe 緩衝層上に歪みシリコン層を成長させることであった。

40

## 【0003】

厚い SiGe 緩衝層を使用すると、先行技術のヘテロ構造について報告されているようにチャネル電子移動度が高くなるが、それに伴ういくつかの顕著な欠点が生じる。第 1 に、厚い SiGe 緩衝層は一般に、既存のシリコン系 CMOS 技術と合わせて用いるのが容易ではない。第 2 に、貫通転位 (TD) およびミスフィット転位を含めて欠陥密度が約 10<sup>6</sup> ~ 約 10<sup>8</sup> 欠陥 / cm<sup>2</sup> になり、これは現実的な VLSI (超大規模集積) 応用例にとって依然として大きすぎる値である。第 3 に、先行技術の構造の性質により、SiGe

50

緩衝層が選択的に成長することができず、そのため、歪みSi、無歪みSi、およびSiGeの材料を含む素子を使用する回路が難しくなり、ある種の例では、集積化がほぼ不可能である。

【0004】

Si基板上に緩和SiGe材料を形成するために、先行技術の方法では一般に、均一な、または傾斜状に変化する、あるいは階段状に変化するSiGe層を準安定臨界厚さ（すなわち、それ以上厚くなると、転位が形成されて応力が緩和される厚さ）よりも厚く成長させ、SiGe緩衝層全体にわたってミスフィット転位を、それに関連する貫通転位とともに形成させる。様々な緩衝構造を用いてこれらの構造内でミスフィット転位部分の長さを長くし、それによってTD密度を低くすることが試みられてきた。

10

【0005】

先行技術による典型的な準安定歪みSiGe層を十分に高い温度でアニールすると、ミスフィット転位が形成され成長して、この被膜の全歪みが緩和される。すなわち、結晶格子の塑性変形の開始によって、この被膜の初期弾性歪みが緩和される。シリコンオンインシュレータ(SOI)基板で成長させた先行技術の準安定な歪みSiGeでは、ほとんどのアニール/酸化条件下で、約700よりも高い温度のアニール履歴の初期にミスフィット転位が形成されることが実験により示されている。その後、これらの欠陥の多くは、この構造を高温アニールする間に、消滅するか、あるいは完全になくなるが、当初のミスフィット・アレイの表面トポロジーは、酸化中も残ったままである。さらに、熱拡散によって製作されるSGOI基板材料では、SiGe合金層は完全には緩和しない。その代わり、最終的なSiGe格子は、平衡値の何分の一かまでしか膨張しない。

20

【0006】

SOI基板の上で厚いSiGe緩衝層を成長させ、次いで、このSiGe層をアニール/酸化によって緩和させることに加えて、ウエハ接合、または酸素注入、あるいはその両方によってSiGeオンインシュレータ基板を形成することが知られている。これらの先行技術のプロセスにより、緩和SiGeオンインシュレータ基板を形成することができるが、これらのプロセスでは、SiGeオンインシュレータ基板を製作するために、特にウエハ接合の場合に追加の処理ステップが必要になるか、または、余分なコストがかかるか、あるいはその両方が生じる。

30

【0007】

先行技術に伴う上記欠点に鑑みて、歪みSi層を上に形成するための格子不整合テンプレートとして使用し得る実質的に緩和した高品質SiGeオンインシュレータ基板を形成する簡単でコストが低い方法を提供することが求められている。

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明の一目的は、実質的に緩和した高品質SiGeオンインシュレータ基板材料を製作する方法を提供することである。

【0009】

本発明の別の目的は、実質的に緩和した高品質SiGeオンインシュレータ基板材料を、実質的に緩和したSiGe層が薄く（すなわち、約2000程度またはそれ未満の厚さに）なるように製作する方法を提供することである。

40

【0010】

本発明の別の目的は、熱力学的に安定しておりミスフィット転位および貫通転位などの欠陥が生成されない、実質的に緩和した薄い高品質SiGeオンインシュレータ基板材料を製作する方法を提供することである。

【0011】

本発明の別の目的は、相補型金属酸化膜半導体(CMOS)処理ステップと適合する、実質的に緩和した薄い高品質SiGeオンインシュレータ基板材料を製作する方法を提供することである。

50

**【0012】**

本発明の別の目的は、歪みSi層を形成する格子不整合のテンプレートすなわち基板として使用し得る、実質的に緩和した薄い高品質SiGeオンインシュレータ基板材料を製作する方法を提供することである。

**【0013】**

本発明の別の目的は、キャリア移動度が大きく、高性能CMOS応用例で有用な、歪みSiと、実質的に緩和したSiGeオンインシュレータとの構造を提供することである。

**【課題を解決するための手段】****【0014】**

上記その他の目的および利点は、本発明において、Ge含有層の下に生成される多孔質シリコンの層（または領域）を酸化することによる簡単かつ直接的な方法を用いることによって実現される。本発明の方法は、ウエハ接合または酸素注入あるいはその両方を利用してSiGeオンインシュレータ（SGOI）基板材料を製作する先行技術のプロセスに代わる低成本の方法を提供する。さらに、SiGeオンインシュレータ基板材料を形成する本発明の方法は、単独で、ウエハ接合技術または酸素イオン注入技術あるいはその両方に頼ることなく、SiGe合金層の下に埋込酸化物領域を同時に形成することができる。

10

**【0015】**

具体的には、本発明の方法は広義には、

正孔を多く含む領域が中に形成されたSi含有基板、およびこのSi含有基板の上のGe含有層を備える構造を提供するステップと、

20

この正孔を多く含む領域を多孔質領域に転換するステップと、

この多孔質領域を含む構造をアニールして、実質的に緩和したSiGeオンインシュレータ材料を提供するステップとを含む。

**【0016】**

本発明では、この多孔質領域は、陽極化浴がHF含有溶液を含む陽極化処理ステップを用いることによって形成される。この陽極化プロセスにより、この構造の他の領域よりも、正孔を多く含む領域、すなわち高濃度のp型ドーパントを含む領域内で速く多孔質が生成される。本発明のアニール・ステップは、多孔質Si領域が埋込酸化物領域に転換され、同時に、この埋込酸化物の上に実質的に緩和したSiGe合金層が形成される酸化条件下で実施される。このアニール・ステップ中には表面酸化物も形成され、そのため、効果的な相互混合が可能になり、実質的に緩和したSiGeオンインシュレータ基板材料が形成される。

30

**【発明を実施するための最良の形態】****【0017】**

次に、本出願に添付の図面を参照して、ウエハ接合または酸素注入あるいはその両方を利用せずに、実質的に緩和したSiGeオンインシュレータ基板材料を形成する低成本の方法を提供する本発明をより詳細に説明する。添付の図面では、同様の要素、または対応する要素、あるいはその両方を同様の参照数字で参照する。

**【0018】**

40

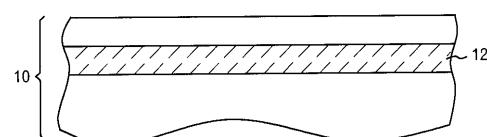

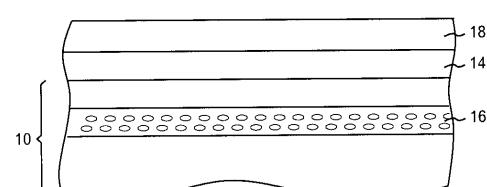

まず、ウエハの表面全体を延びる連続埋込酸化物の上に実質的に緩和したSiGe合金層が形成される本発明の実施形態を示す図1～図4を参照する。図1に、本発明の初期段階における構造を示す。具体的には、図1に示す構造はSi含有基板10を含み、Si含有基板10の中に、正孔を多く含む領域12が形成される。

**【0019】**

本発明では、「Si含有基板」という用語を用いて、少なくともシリコンを含む半導体材料を示す。このようなSi含有材料の例には、Si、SiGe、SiC、SiGeC、Si/Si、Si/SiC、Si/SiGeC、ならびに、任意の数の（連続的な、または不連続的な、あるいは連続と不連続を組み合わせた）埋込絶縁領域を内部に含み得るあらかじめ形成されたシリコンオンインシュレータ（SOI）またはSiGeオンインシュ

50

レータが含まれるが、これらに限定されるものではない。本発明で使用する Si 含有基板は、ドープしていないものとすることもできるし、電子または正孔を多く含む Si 含有基板とすることもできる。

【0020】

正孔を多く含む領域 12 は、周囲の Si 含有材料よりも濃くドープされた領域である。典型的には、この正孔を多く含む領域は、約  $1 \times 10^{19}$  原子 /  $\text{cm}^3$  以上の濃度の p 型ドーパント、より好ましくは、約  $1 \times 10^{20}$  ~ 約  $5 \times 10^{20}$  原子 /  $\text{cm}^3$  の濃度の p 型ドーパントを含む。

【0021】

本発明の一実施形態では、正孔を多く含む領域 12 は、まず、初期 Si 含有基板の表面上で p 型を多く含むエピタキシャル層を成長させ、次いで、先に成長させた層の上で、この p 型を多く含むエピタキシャル層よりも薄くドープした単結晶 Si 含有層を成長させることによって形成することができる。この p 型を多く含むエピタキシャル層は、Si 供給源ガスがドーパントを含む周知のエピタキシャル成長法を利用して成長させる。本発明のこの時点を利用し得る様々なエピタキシャル成長法の例には、例えば、低圧化学気相堆積法 (LPCVD)、急速加熱化学気相堆積法 (RTCVD)、低エネルギー・プラズマ堆積法 (LEPD)、超高真空化学気相堆積法 (UHVCVD)、大気圧化学気相堆積法 (APCVD)、分子ビーム・エピタキシ法 (MBE)、およびプラズマ励起化学気相堆積法 (PECVD) が含まれる。

【0022】

これら p 型を多く含むエピタキシャル層および単結晶 Si 含有層の厚さは、SGOI 層または SOI 層内の最終的な埋込酸化物の厚さの要件に応じて変化し得る。典型的には、p 型を多く含むエピタキシャル層の厚さは、約 5 ~ 約 500 nm、極めて好ましくは約 100 ~ 約 200 nm であり、単結晶 Si 含有層の厚さは、約 50 ~ 約 1000 nm、極めて好ましくは約 100 ~ 約 500 nm である。

【0023】

これら p 型を多く含むエピタキシャル層および単結晶 Si 含有層は、異なる 2 つのステップで成長させることもできるし、あるいは、真空を保ったまま、1 つのステップを用いて p 型を多く含むエピタキシャル層および単結晶 Si 含有層を形成することもできる。図 1 では、単結晶 Si 含有層は、正孔を多く含む領域 12 の上に配置される。この単結晶 Si 含有層は、Si 含有基板 10 と同じ Si 材料とすることもできるし、異なるものでもよい。

【0024】

本発明の別の実施形態では、図 1 に示す構造は、初期単結晶 Si 含有基板の上面の下の所定の深さのところで p 型ドーパントの濃度が最大になるように、基板に p 型ドーパントをイオン注入することによって形成される。

【0025】

本明細書では、「p 型ドープ」という用語を用いて、元素周期表の I II - A 群の元素を指す。正孔を多く含む領域を形成するのに使用し得る p 型ドープの例には、Ga、Al、B、および  $\text{BF}_2$  が含まれるが、これらに限定されるものではない。p 型注入物の場合、本発明では、B または  $\text{BF}_2$  が特に好ましい。好ましい実施形態では、約  $5 \times 10^{15}$  原子 /  $\text{cm}^2$  ~ 約  $5 \times 10^{16}$  原子 /  $\text{cm}^2$  のドーズで、ホウ素を約 100 keV ~ 500 keV のエネルギーで使用するか、あるいは  $\text{BF}_2$  を約 500 keV ~ 約 2500 keV のエネルギーで使用して正孔を多く含む領域 12 を形成し得る。

【0026】

Si 含有基板 10 内に正孔を多く含む領域 12 を形成するのにイオン注入を利用する実施形態では、任意選択のアニール・ステップを実施してホウ素を電気的に活性化し、それによって正孔を生成することができる。

【0027】

本発明のこの時点で用いるアニール処理は、熱処理炉によるアニール、急速熱アニール

10

20

30

40

50

、またはスパイク・アニールを含み得る。熱処理炉によるアニールを用いる場合、この熱処理炉によるアニールは、典型的には、約 600 またはそれよりも高い温度で約 15 分またはそれよりも長く実施する。好ましくは、この熱処理炉によるアニールは、約 650 ~ 約 800 の温度で約 15 分 ~ 約 250 分実施する。熱処理炉によるアニールは、典型的には、例えば He、Ar、O<sub>2</sub>、N<sub>2</sub> およびこれらの混合物を含む不活性ガス雰囲気または酸化環境あるいはその両方の存在下で実施する。

#### 【0028】

急速熱アニール (RTA) を用いる場合、このRTAは、典型的には、約 800 またはそれよりも高い温度で約 5 分またはそれよりも短く実施する。好ましくは、RTAは、約 900 ~ 約 1050 の温度で約 5 秒 ~ 約 30 秒実施する。RTAは、典型的には、例えば He、Ar、O<sub>2</sub>、N<sub>2</sub> およびこれらの混合物を含む不活性ガス雰囲気または酸化環境あるいはその両方の存在下で実施する。

10

#### 【0029】

スパイク・アニールを実施する場合、このスパイク・アニールは、典型的には、約 900 またはそれよりも高い温度で約 1 秒またはそれよりも短く実施する。好ましくは、スパイク・アニールは、約 900 ~ 約 1100 の温度で実施する。スパイク・アニールは、典型的には、例えば He、Ar、O<sub>2</sub>、N<sub>2</sub> およびこれらの混合物を含む不活性ガス雰囲気または酸化環境あるいはその両方の存在下で実施する。

#### 【0030】

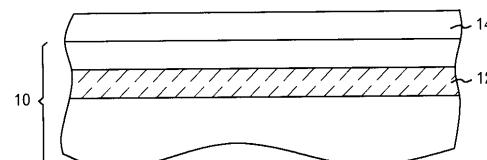

図 1 に示す構造が得られた後で、正孔を多く含む領域 12 を含む Si 含有基板 10 の上面の上に Ge 含有層 14 が形成される。例えば図 2 に、得られた構造が Ge 含有層 14 を含むところを示す。「Ge 含有層」という用語は、100 原子%の Ge を含む純粋な Ge 層、または最大で 99.99 原子%の Ge を含む SiGe 合金を示す。SiGe 合金を使用する場合、この SiGe 合金中の Ge 含有率は、好ましくは約 0.1 ~ 約 99.9 原子%であり、極めて好ましくは、Ge 原子%は、約 10 ~ 約 35 原子%である。

20

#### 【0031】

本発明によれば、Ge 含有層 14 は、(i) 热力学的に安定な(臨界厚さ未満の) Ge 含有層を成長させることができるか、(ii) 欠陥、すなわちミスフィット転位および TD 転位が実質的でない準安定な Ge 含有層を成長させることができるか、あるいは、(iii) 欠陥を含む緩和 Ge 含有層を成長させることができる当業者に周知の任意の従来のエピタキシャル成長法を利用して、Si 含有基板 10 の上面の上に形成される。

30

#### 【0032】

(i)、(ii)、または(iii)の条件を満足し得るエピタキシャル成長プロセスの例には、低圧化学気相堆積法 (LPCVD)、急速加熱化学気相堆積法 (RTCAVD)、低エネルギー・プラズマ堆積法 (LEPD)、超高真空化学気相堆積法 (UHVCVD)、大気圧化学気相堆積法 (APCVD)、分子ビーム・エピタキシ法 (MBE)、およびプラズマ励起化学気相堆積法 (PECVD) が含まれるが、これらに限定されるものではない。

#### 【0033】

本発明のこの時点で形成される Ge 含有層 14 の厚さは様々なものとし得るが、典型的には、Ge 含有層 14 の厚さは、約 10 ~ 約 500 nm、極めて好ましくは約 20 ~ 約 200 nm である。

40

#### 【0034】

本発明の任意選択の実施形態では、図 1 および図 2 に示す構造を形成する際に用いる各ステップは、1 つの被着ステップですべての層をエピタキシャル成長させることによって 1 つにすることができる。すなわち、正孔を多く含む領域をエピタキシャル成長させた後で、単結晶 Si 層を成長させ、次いで、Ge 含有層を成長させる。

#### 【0035】

本発明の別の代替実施形態では、正孔を多く含む領域 12 は、Si 含有基板 10 の上に Ge 含有層 14 が形成された後でこの構造に導入される。このような実施形態では、正孔

50

を多く含む領域 1 2 は、 G e 含有層 1 4 の形成後、イオン注入によって形成され、そのため、2つの別々の処理ステップが不要になる。イオン注入ステップ後、先に述べたアニール技術の1つを利用してドーパントを活性化させる。

【 0 0 3 6 】

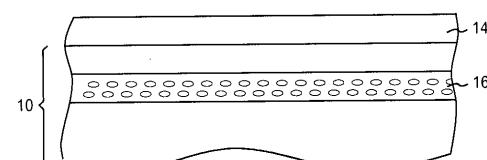

次に、図2に示す構造を、正孔を多く含む領域 1 2 を多孔質領域 1 6 に転換し得る電解陽極化プロセスにかける。例えば図3に、得られた構造が、陽極化処理後に形成された多孔質領域 1 6 を含むところを示す。

【 0 0 3 7 】

この陽極化処理は、図2に示す構造を H F 含有溶液内に浸し、この構造に、やはり H F 含有溶液内に配置された電極に関して電気的なバイアスを印加することによって実施される。このようなプロセスでは、この構造は、典型的には、電気化学的な電池の陽極として働き、 S i などの別の半導体材料または金属が陰極として用いられる。

【 0 0 3 8 】

一般に、 H F による陽極化により、 p 型にドープした単結晶 S i が多孔質 S i に転換される。このようにして形成される多孔質 S i の形成速度および性質（多孔率および微細構造）は、材料の特性、すなわちドープのタイプおよび濃度と、陽極化プロセス自体の反応条件（電流密度、バイアス、照明、および H F 含有溶液内の添加物）とによって決まる。具体的には、より濃くドープされた領域内では極めて効率よく多孔質 S i が形成され、したがって、正孔を多く含む埋込領域 1 2 が、効率よく多孔質 S i に転換される。

【 0 0 3 9 】

一般に、本発明で形成される多孔質 S i 領域 1 6 は、約 0 . 1 % またはそれよりも高い多孔率を有する。この構造の最上面から多孔質 S i の最上面まで測定した多孔質 S i 領域 1 6 の深さは、約 5 0 n m またはそれよりも深い。

【 0 0 4 0 】

「 H F 含有溶液」という用語には、濃縮 H F ( 4 9 % ) 、 H F と水の混合物、 H F と 1 価アルコール、例えば、メタノール、エタノール、プロパノールなどとの混合物、または H F と少なくとも 1 種類の界面活性剤との混合物が含まれる。 H F 溶液中に存在する界面活性剤の量は、典型的には、 4 9 % H F の場合には約 1 ~ 約 5 0 % である。

【 0 0 4 1 】

正孔を多く含む領域 1 2 を多孔質 S i 領域 1 6 に転換する陽極化プロセスは、約 0 . 0 5 ~ 約 5 0 ミリアンペア / c m <sup>2</sup> の電流密度で動作する定電流源を使用して実施される。任意選択で光源を使用して、このサンプルを照明する。より好ましくは、本発明で用いる陽極化プロセスでは、約 0 . 1 ~ 約 5 ミリアンペア / c m <sup>2</sup> の電流密度で動作する定電流源を使用する。

【 0 0 4 2 】

この陽極化プロセスは、典型的には、室温または室温よりも高い温度で実施される。陽極化プロセス後、典型的には、この構造を脱イオン水で洗浄し、乾燥させる。

【 0 0 4 3 】

本発明の任意選択の実施形態では、本発明のこの時点で、 G e 含有層 1 4 の上に任意選択のキャップ層 1 8 が形成される。例えば図4に、任意選択のキャップ層 1 8 を含む構造を示す。本発明で使用する任意選択のキャップ層 1 8 は、例えば、エピタキシャル S i ( e p i - S i ) 、アモルファス S i ( a : S i ) 、単結晶または多結晶の S i , またはこれらの任意の組合せを含めて、任意の S i 材料を含む。上記で列挙した様々な S i 材料のうち、任意選択のキャップ層 1 8 として e p i - S i を使用することが好ましい。

【 0 0 4 4 】

任意選択のキャップ層 1 8 を設ける場合、この層の厚さは、約 1 ~ 約 1 0 0 n m であり、極めて好ましくは約 1 ~ 約 3 0 n m である。任意選択のキャップ層 1 8 は、先に述べたエピタキシャル成長プロセスの1つを含む周知の被着プロセスを利用して形成される。

【 0 0 4 5 】

次いで、 G e 含有層 1 4 およびこのように形成された多孔質 S i 領域 1 6 を含み、かつ

10

20

30

40

50

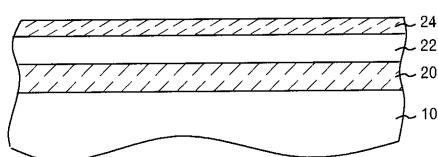

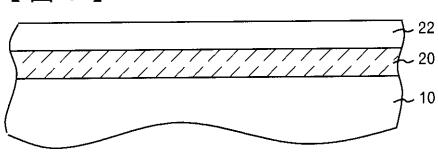

任意選択のキャップ層 18 も含む(図3参照)構造、または任意選択のキャップ層 18 は含まない構造(図4参照)を、多孔質 Si の上の主に単結晶 Si 層内で Ge が相互拡散し得る温度で加熱し、すなわちアニールして実質的に緩和した単結晶 SiGe 層 22 を形成し、同時に、多孔質 Si 領域 16 を埋込酸化物層 20 に転換する。例えば図5に、得られた構造を示す。すなわち、この加熱ステップにより、埋込酸化物層 20 の上に緩和した単結晶 SiGe 層 22 が形成される。この加熱ステップ中に、SiGe 層 22 の上に酸化物層 24 が形成されることに留意されたい。この表面酸化物層、すなわち酸化物層 24 は、典型的には、加熱ステップの後で、SiGe よりも酸化物を除去する選択性が大きいHFなどの化学エッチ液を使用する従来方式のウェット・エッティング・プロセスを利用してこの構造から除去されるが、常にそうではない。

10

#### 【0046】

この酸化物層を除去するときに、第2単結晶 Si 層を SiGe 層 22 の上に形成し得ることに留意されたい。この第2単結晶 Si 層を歪ませるか、歪ませないかは、SiGe 層の緩和状態によって決まる。本発明の上記処理ステップを任意の数だけ繰り返して、緩和した多層 SiGe 基板材料を生成することができる。この第2の Si 層の歪みを測定すると、典型的には 0% ~ 約 1.5% になる。

#### 【0047】

本発明の加熱ステップ後に形成される表面酸化物層 24 の厚さは、約 10 から約 100 nm の範囲で様々であるが、極めて好ましい厚さは、約 20 ~ 約 500 nm である。

20

#### 【0048】

具体的には、本発明の加熱ステップは、約 650 ~ 約 1350 の温度、極めて好ましくは、約 1200 ~ 約 1320 の温度で実施されるアニール・ステップである。さらに、本発明の加熱ステップは、O<sub>2</sub>、NO、N<sub>2</sub>O、オゾン、空気その他類似の酸素含有ガスなど、少なくとも 1 種類の酸素含有ガスを含む酸化環境で実施される。この酸素含有ガスは、(O<sub>2</sub> と NO の混合物など) 互いに混合することもできるし、このガスを、He、Ar、N<sub>2</sub>、Xe、Kr、または Ne などの不活性ガスで希釈することもできる。希釈した環境を用いる場合、この希釈環境は、約 0.5 ~ 約 100% の酸素含有ガスを含み、最大 100%までの残りの部分は不活性ガスである。

#### 【0049】

この加熱ステップを実施する時間は、典型的には約 10 ~ 約 1800 分の範囲で様々であるが、極めて好ましい時間は、約 60 ~ 約 600 分である。この加熱ステップは、単一の目標温度で実施することもできるし、様々な増加減少速度および浸漬時間を使って様々な増加減少 / 浸漬サイクルを採用することもできる。

30

#### 【0050】

この加熱ステップは、Ge 原子に対する拡散障壁として働く酸化物層、すなわち酸化物層 20 および 24 が設けられる酸化環境下で実施される。多孔質 Si 領域と拡散する酸素とが反応する速度は速いことに留意されたい。これらの酸化物層(表面酸化物および埋込酸化物)が形成されると、Ge はこれらの酸化物層間に捕捉される。この酸化プロセスが継続し、Ge 含有層および単結晶が使い尽くされると、合金層内の Si に対する Ge の比は増加する。というのは、Ge は酸化物から追い出され、Si は成長中の表面酸化物層に組み込まれるからである。

40

#### 【0051】

本発明では、加熱ステップが、希釈酸素含有ガス中で約 1200 ~ 約 1320 の温度で実施されるときに、効率的な熱混合が実現される。

#### 【0052】

本明細書では、SiGe 層の融点に基づいて調整した加熱サイクルを用いることも企図されている。このような例では、温度は、SiGe 層の融点未満で推移するように調節される。

#### 【0053】

酸化が急激すぎると、Ge は表面酸化物 / SiGe 界面から十分に高速に拡散すること

50

ができず、この酸化物の中を運ばれる（かつ失われる）か、界面Ge濃度がかなり高くなり、そのため、合金の溶融温度に達することになることに留意されたい。

【0054】

本発明の加熱ステップの役割は、（1）Ge原子をより迅速に拡散させて、アニール処理中の均一な分布を維持し、（2）（「初期」）歪み層構造を、平衡構成を容易にするサーマル・バジェットにかけ、（3）多孔質Si領域を熱による埋込酸化物領域に転換することである。この加熱ステップが実施された後で、この構造に、埋込酸化物層20と表面酸化物層24の間に挟まれた実質的に緩和した均一なSiGe合金層、すなわちSiGe層22が設けられる。

【0055】

本発明によれば、実質的に緩和したSiGe層22の厚さは、約2000nm以下、極めて好ましくは、約10～約100nmである。本発明で形成される実質的に緩和したSiGe層22は、先行技術のSiGe緩衝層よりも薄く、ミスフィットおよびTDを含めて欠陥の密度が、約10<sup>8</sup>欠陥/cm<sup>2</sup>未満になることに留意されたい。加熱ステップ中に形成される埋込酸化物層20の厚さは、約50nm～約500nm、極めて好ましくは、約100～約200nmである。埋込酸化物層20は、その上にある実質的に緩和したSiGe層22との間に、滑らかで連続した界面を有する。

【0056】

本発明で形成される実質的に緩和したSiGe層22の最終的なGe含有率は、約0.1～約99.9原子%、極めて好ましくは、約10～約35原子%である。実質的に緩和したSiGe層22の別の特性上の特徴は、その格子緩和測定値が、約1～約100%、極めて好ましくは、約50～約80%であることである。

【0057】

先に述べたように、本発明のこの時点で、表面酸化物層24を除去することができ、それによって、例えば図6に示すSiGeオンインシュレータ基板材料が得られる。

【0058】

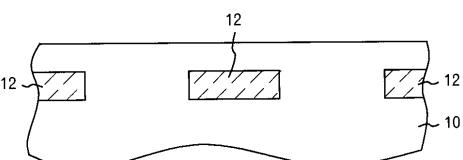

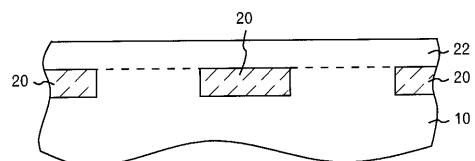

上記図1～図6に示すパターン形成しない構造に加えて、本発明は、パターン形成した構造を形成することも企図している。例えば図7～図9に、パターン形成した構造およびこの構造を形成するのに用いるプロセスを示す。具体的には、図7に、Si含有基板10が、その中に形成された正孔を多く含む領域12からなる離散的な分離アイランドを有する実施形態の初期構造を示す。これら正孔を多く含む離散領域12は、マスク付きイオン注入プロセスを利用することによって、あるいは、正孔を多く含む連続層を成長させ、この新たに成長させた層をリソグラフィおよびエッティングにかけることによって形成し得る。エッティング・ステップの後で、構造全体の上に単結晶Si層を成長させ、それによって図7に示す構造が得られる。

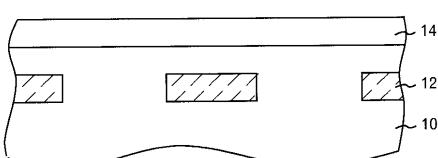

【0059】

図8に、図7に示す構造の表面上にGe含有層14が形成された後で形成される構造を示す。Ge含有層14は、先に述べたエピタキシャル成長法の1つを利用して形成される。図1～図6で説明した実施形態の場合と同様に、Si含有基板10上にGe含有層14を形成した後で、Si含有基板10内に正孔を多く含む領域12を形成することができる。次に、Ge含有層14および正孔を多く含む領域12を含む図8に示す構造を、先に述べた陽極化プロセスにかける。先に述べたように、この陽極化プロセスにより、基板内の正孔を多く含む領域内に多孔質Si領域16が形成される。次いで、この構造の上に、（図示しない）任意選択のキャップ層を形成し得る。

【0060】

その後、任意選択のキャップ層の有無にかかわらず、この構造を先に述べたアニール・ステップにかけ、それによって、例えば図9に示す構造が得られる。参照数字10、20、および22は上記で説明したのと同じものを指し、この構造から表面酸化物層24が除去されていることに留意されたい。

【0061】

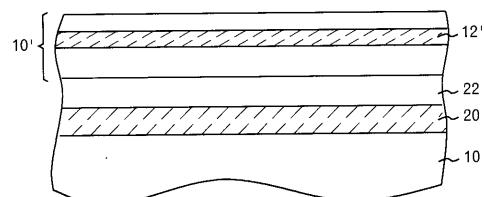

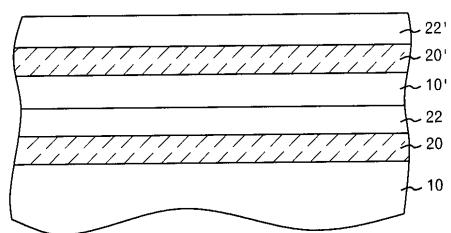

図10および図11に、同じ構造内に2重SGOI層が形成される本発明の別の代替実施形態を示す。この2重SGOI層は、まず、図6に示す構造を提供する際に先に述べたステップを実施することによって形成される。この構造が得られた後で、この構造の上に、正孔を多く含む領域12'を有するSi含有層10'が形成され、次いで、Si含有層10'の上にGe含有層14'が形成される。最初にSi含有層10'およびGe含有層14'を形成し、次いで、Si含有層10'内に正孔を多く含む領域12'を形成することも可能である。図10に、この構造を示す。次に、陽極化ステップおよびアニール・ステップを繰り返し、それによって、例えば図11に示す構造が得られる。図11では、第2の埋込酸化物層20'および第2の実質的に緩和したSiGe層22'が形成される。同じ手順を多数回繰り返して、複数のSGOIの積層構造を提供することができる。この複数のSGOIの層は、すべて連続体または不連続体とすることもできるし、これらの組合せとして設けることもできる。

#### 【0062】

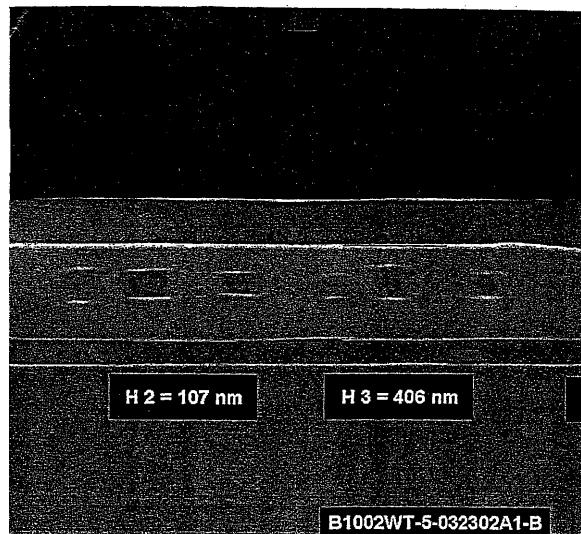

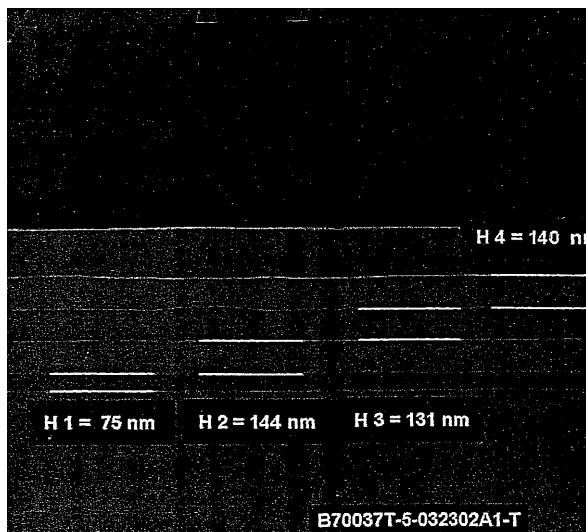

図12および図13に、本発明の方法を用いて生成した実質的に緩和したSiGeオンインシュレータ基板材料の実際のSEM画像を示す。図12は、多孔質Si層を酸化することによって形成されたSGOI基板材料の断面SEM画像である。H2(107nm)と標示された薄く暗い帯は、埋込酸化物層である。その上の層H3(406)は、2原子%GeのSiGe層である。この層の中の小さな空所は、第2埋込酸化物層を形成しようと試みたものである。最上部の灰色の層は、表面酸化物である。図13は、多孔質Siを酸化することによって形成された2層SGOI基板材料の断面SEM画像である。H1(75nm)と標示された薄く暗い帯は、第1埋込酸化物層である。その上の層H2(144nm)は、第1のSiGe層(0.2原子%Ge)である。H3(131nm)と標示された隣の暗い帯は、第2埋込酸化物層であり、隣の層H4(140nm)は、第2のSiGe層(4.5原子%Ge)である。最上部の暗い灰色の層は、表面酸化物層である。

#### 【0063】

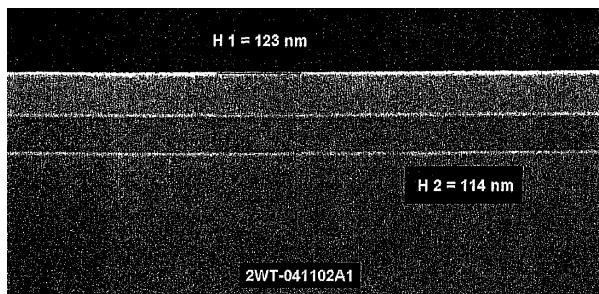

図14に、図12および図13に示すと類似の基板から得られたSGOI構造を示すが、この構造は、高温アニール中の酸化を強め、この強められた酸化によって図12および図13の上部SGOI層およびBOX層が使い尽くされた後に得られたものである。酸化は、図12および図13に示す構造をアニールするのに用いたものに比べてアニール環境中の酸素濃度を高くするか、あるいは、図12および図13の構造を生成するのに用いたものと酸素濃度は同じにしてアニール時間を長くすることによって増強することができる。図14は、SGOIの断面SEM画像である。H1(123nm)と標示された薄い暗い帯は、Geが推定4.5%であるSGOI層である。H2(114nm)と標示された薄い暗い帯は、BOX層である。最上部の暗い灰色の層は、表面酸化物層である。

#### 【0064】

先に述べた実施形態のいずれかを実施した後で、当業者に周知の従来方式のエピタキシャル被着プロセスを利用して、SiGe層の上にSi層を形成することができる。このepi-Si層の厚さは様々であるが、典型的には、約1～約100nmである。

#### 【0065】

ある種の例では、先に述べた処理ステップを用いて緩和SiGe層の上に追加のSiGeを形成し、その後、epi-Siを形成することができる。この緩和SiGe層の面内格子パラメータは、epi-Si層に比べて大きいので、このepi-Si層は、引張歪みを受けることになる。

#### 【0066】

本発明では、少なくとも本発明のSiGeオンインシュレータ基板材料を含む超格子構造および格子不整合構造も企図されている。超格子構造の場合、このような構造は、少なくとも本発明の実質的に緩和したSiGeオンインシュレータ基板材料と、この基板材料の上に形成されたSiとSiGeの交互層とを含むことになる。

#### 【0067】

格子不整合構造の場合、本発明の実質的に緩和したSiGeオンインシュレータ基板材

10

20

30

40

50

料の上に、GaAs、GaPその他の類似の化合物が形成されることになる。

【0068】

本発明の好ましい実施形態について本発明を具体的に示し説明してきたが、本発明の範囲および趣旨から逸脱することなく、上記その他の形態および細部の変更を加えることができることが当業者には理解されよう。したがって、本発明は、上記で説明し例示したそのままの形態および細部に限定されるのではなく、添付の特許請求の範囲の範囲に含まれることが意図されている。

【図面の簡単な説明】

【0069】

【図1】本発明の基本処理ステップを(断面図で)示す、絵画的に表現した図である。 10

【図2】本発明の基本処理ステップを(断面図で)示す、絵画的に表現した図である。

【図3】本発明の基本処理ステップを(断面図で)示す、絵画的に表現した図である。

【図4】本発明の基本処理ステップを(断面図で)示す、絵画的に表現した図である。

【図5】本発明の基本処理ステップを(断面図で)示す、絵画的に表現した図である。

【図6】本発明の基本処理ステップを(断面図で)示す、絵画的に表現した図である。

【図7】本発明の代替実施形態を(断面図で)示す、絵画的に表現した図である。

【図8】本発明の代替実施形態を(断面図で)示す、絵画的に表現した図である。

【図9】本発明の代替実施形態を(断面図で)示す、絵画的に表現した図である。

【図10】本発明の代替実施形態を(断面図で)示す、絵画的に表現した図である。

【図11】本発明の代替実施形態を(断面図で)示す、絵画的に表現した図である。 20

【図12】本発明の方法を用いて形成したSiGeオンインシュレータ材料の断面SEM画像である。

【図13】本発明の方法を用いて形成した2層SiGeオンインシュレータ材料の断面SEM画像である。

【図14】本発明のSGOI基板の断面SEM画像である。

【図1】

【図2】

【図3】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 ベデル、ステファン、ダブリュ

アメリカ合衆国12590 ニューヨーク州ワッピンガーズ・フォールズ ニコル・ドライブ 3

2

(72)発明者 チョー、クワン、ス

大韓民国京畿道463-786 城南市亭子洞 122 サンロク・ウースン・アパート 323

- 905

(72)発明者 フォゲル、キース、エフ

アメリカ合衆国10547 ニューヨーク州モヒガン・レーク ルクス・レーン 4

(72)発明者 サダナ、デベンドラ、ケイ

アメリカ合衆国10570 ニューヨーク州プレザントビル スカイ・トップ・ドライブ 30

審査官 太田 一平

(56)参考文献 特開2001-148473 (JP, A)

特開2000-156484 (JP, A)

米国特許第05950094 (US, A)

特開昭56-110247 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/20

H01L 21/02

H01L 27/12

H01L 23/52

H01L 21/76

H01L 21/70 - 21/76