(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-81036

(P2007-81036A)

(43) 公開日 平成19年3月29日(2007.3.29)

| (51) Int.CI.                  | F 1         | テーマコード (参考) |

|-------------------------------|-------------|-------------|

| <b>H01L 21/66</b> (2006.01)   | H01L 21/66  | S 2 G001    |

| <b>H01L 21/8242</b> (2006.01) | H01L 27/10  | 681Z 4 M106 |

| <b>H01L 27/108</b> (2006.01)  | H01L 21/66  | Y 5 F083    |

| <b>G01N 23/225</b> (2006.01)  | G01N 23/225 |             |

審査請求 未請求 請求項の数 9 O L (全 11 頁)

|           |                              |            |                                                                                                                                                               |

|-----------|------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2005-265446 (P2005-265446) | (71) 出願人   | 500174247<br>エルピーダメモリ株式会社<br>東京都中央区八重洲2-2-1                                                                                                                   |

| (22) 出願日  | 平成17年9月13日 (2005.9.13)       | (74) 代理人   | 100096231<br>弁理士 稲垣 清                                                                                                                                         |

|           |                              | (72) 発明者   | 本部 誠一<br>東京都中央区八重洲2-2-1 エルピー<br>ダメモリ株式会社内                                                                                                                     |

|           |                              | F ターム (参考) | 2G001 AA03 BA07 CA03 GA06 JA13<br>KA03 LA11 MA05<br>4M106 AA01 AA07 AB07 AB15 AB17<br>BA02 CA16 DH07 DH24 DH33<br>5F083 AD00 GA27 MA03 MA06 NA01<br>PR09 ZA20 |

|           |                              |            |                                                                                                                                                               |

(54) 【発明の名称】半導体装置の検査方法、及び、検査用半導体装置の製造方法

## (57) 【要約】

【課題】 コンタクトプラグのショートを効率的に検出可能な半導体装置の検査方法を提供する。

【解決手段】 半導体基板11の表面部分に、素子形成領域13を相互に区画する素子分離領域14のパターン、及び、半導体基板11を覆う絶縁膜16を形成する工程と、半導体基板の素子形成領域13に導通する複数のコンタクトプラグを形成するためのマスクパターンを用い、このマスクパターンを素子分離領域14のパターンに対して相対的に所定距離ずらすことによって、絶縁膜16を貫通し一部が素子分離領域14で絶縁される複数のコンタクトプラグ18を形成する工程と、複数のコンタクトプラグ18の内で、素子分離領域14で絶縁されたコンタクトプラグ18に電子線を照射するステップと、電子線を照射したコンタクトプラグ18から放出される二次電子量を検出するステップと、検出された二次電子量に基づいて、電子線が照射されたコンタクトプラグ18の異常を判定するステップとを有する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板上に、導電性部分と絶縁性部分とを含む下地パターン、及び、該下地パターンを覆う絶縁膜を形成する工程と、

前記導電性部分に導通する複数のコンタクトプラグを形成するためのマスクパターンを用い、該マスクパターンを前記下地パターンに対して相対的に所定距離ずらすことによって、前記絶縁膜を貫通し少なくとも一部が前記絶縁性部分で絶縁される複数のコンタクトプラグを形成する工程と、

前記複数のコンタクトプラグの内で、少なくとも前記絶縁性部分で絶縁されたコンタクトプラグに電子線を照射するステップと、10

前記電子線を照射したコンタクトプラグから放出される二次電子量を検出するステップと、

前記検出された二次電子量に基づいて、前記電子線が照射されたコンタクトプラグの異常を判定するステップと

を有することを特徴とする半導体装置の検査方法。

**【請求項 2】**

前記下地パターンの導電性部分及び絶縁性部分がそれぞれ、半導体基板の素子形成領域及び素子分離領域である、請求項 1 に記載の半導体装置の検査方法。

**【請求項 3】**

前記下地パターンの導電性部分が、導体膜の選択エッチングで形成される配線パターンである、請求項 1 に記載の半導体装置の検査方法。20

**【請求項 4】**

製品用半導体装置の状態を検査するための検査用半導体装置を製造する方法であって、前記製品用半導体装置を製造するプロセス条件と同じプロセス条件を用いて、導電性部分と絶縁性部分とを含む下地パターン、及び、該下地パターンを覆う絶縁膜を形成する工程と、

前記製品用半導体装置で前記絶縁膜を貫通して前記導電性部分に導通する複数のコンタクトプラグを形成するためのマスクパターンを用い、該マスクパターンを前記下地パターンに対して相対的に所定距離ずらすことによって、前記絶縁膜を貫通し少なくとも一部が前記絶縁性部分で絶縁される複数のコンタクトプラグを形成する工程と30

を備えることを特徴とする検査用半導体装置の製造方法。

**【請求項 5】**

前記下地パターンの導電性部分及び絶縁性部分がそれぞれ、半導体基板の素子形成領域及び素子分離領域である、請求項 4 に記載の検査用半導体装置の製造方法。

**【請求項 6】**

前記下地パターンの導電性部分が、導体膜の選択エッチングで形成される配線パターンである、請求項 4 に記載の検査用半導体装置の製造方法。

**【請求項 7】**

前記製品用半導体装置が D R A M である、請求項 4 ~ 6 の何れか一に記載の検査用半導体装置の製造方法。40

**【請求項 8】**

請求項 4 ~ 7 の何れか一に記載の検査用半導体装置を用いて製品用半導体装置を評価する半導体装置の検査方法であって、

前記複数のコンタクトプラグの内で、少なくとも前記絶縁性部分上に形成されたコンタクトプラグに電子線を照射するステップと、

前記電子線を照射したコンタクトプラグから放出される二次電子量を検出するステップと、

前記検出された二次電子量に基づいて、前記電子線が照射されたコンタクトプラグの異常を判定するステップと

を有することを特徴とする半導体装置の検査方法。50

**【請求項 9】**

前記異常判定ステップでは、前記絶縁性部分で絶縁されたコンタクトプラグが、前記導電性部分、他のコンタクトプラグ、及び、他の導電性材料の少なくとも1つに導通するか否かを判定する、請求項8に記載の半導体装置の検査方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の検査方法、及び、検査用半導体装置の製造方法に関し、更に詳細には、半導体装置内部に配設された導体間のショート（短絡）を検査する、半導体装置の検査方法、及び、検査用半導体装置の製造方法に関する。 10

**【背景技術】****【0002】**

半導体装置内部の導体間のショートは、半導体装置の動作不良の原因となり、半導体装置製造の歩留りを低下させる大きな要因となっている。近年、半導体装置製品の設計から量産までの期間が益々短縮され、量産に先立つインライン検査等で、半導体装置内部の導体間のショートを効率的に検出し、ショートの少ないプロセス条件に早期に調整することが要請されている。

**【0003】**

導体間のショートを検出するために、従来、光学式の検査装置を用いて肉眼で検査を行っていた。しかし、半導体装置の微細化に伴って、光学式の検査装置による検査では、ショートが生じた箇所を発見するために多くの時間を要すると共に、発見自体が困難になっている。この問題に対して、近年、SEM(Scanning Electron Microscope:走査型電子顕微鏡)式の検査装置を用いた検査が実用化されている。 20

**【0004】**

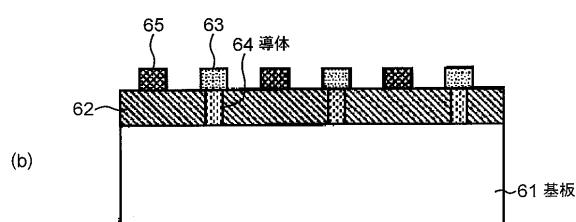

SEM式検査装置を用いた検査方法については、例えば特許文献1に記載されている。図7(a)に、特許文献1に記載の検査方法で用いる検査用の半導体装置の構成を示す。図7(b)は、図7(a)のB-B線に沿った断面を示している。この検査方法では、先ず、半導体装置の絶縁膜62の表面に、導体64を介して基板61に接続される導体パターン63、及び、基板61に接続されない導体パターン(非接続パターン)65を、直交する2方向の何れにも交互に配列されるように、つまり千鳥状に配列されるように形成する。次いで、半導体装置60の表面に対して電子線を照射し、半導体装置60の表面を走査しつつ、各導体パターン63, 65から放出される二次電子の量を測定する。 30

**【0005】**

ここで、電子線が照射された非接続パターン65は万一、通常の導体パターン63などの他の導体に導通している場合には、帯電量が少くなり、また、導通していない場合には、帯電量が多くなる。非接続パターン65から放出される二次電子量は、非接続パターン65の帯電量に応じた電位によって異なるため、放出される二次電子量に異常が認められた非接続パターン65について、近傍の導体との間でショートしたと判定できる。また、ショートしたと判定された非接続パターン65の近傍についてのみ、精密な検査を行うことによって、ショートが生じた詳細な部位を特定できる。 40

**【特許文献1】特開2001-305194号(図1、2)****【発明の開示】****【発明が解決しようとする課題】****【0006】**

ところで、近年の半導体装置の微細化に伴い、隣接するワード線間の間隔が益々狭くなっている。このため、ワード線間で絶縁膜の埋め込み不良が生じ易く、これに起因して、コンタクトプラグとワード線との間のショートや、コンタクトプラグ同士のショートなどのコンタクトプラグを介したショートが発生し、半導体装置の品質を低下させる主要な要因の一つとなっている。しかし、上記従来のSEM式検査方法では、コンタクトプラグのショートを検出しようとしても、コンタクトプラグのそれぞれは、半導体基板の表面部分 50

などの他の導体に導通しているため、電子線の照射後にほぼ同じ電位に保たれる。従って、そのショートを検出することが容易でなかった。

#### 【0007】

半導体装置製造の歩留りを大きく向上させるためには、コンタクトプラグのショートを効率的に検出することが必須である。本発明は、上記に鑑み、コンタクトプラグのショートを効率的に検出可能な半導体装置の検査方法、及び、検査用半導体装置の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

上記目的を達成するために、本発明の第1の視点に係る半導体装置の検査方法は、基板上に、導電性部分と絶縁性部分とを含む下地パターン、及び、該下地パターンを覆う絶縁膜を形成する工程と、10

前記導電性部分に導通する複数のコンタクトプラグを形成するためのマスクパターンを用い、該マスクパターンを前記下地パターンに対して相対的に所定距離ずらすことによって、前記絶縁膜を貫通し少なくとも一部が前記絶縁性部分で絶縁される複数のコンタクトプラグを形成する工程と、

前記複数のコンタクトプラグの内で、少なくとも前記絶縁性部分で絶縁されたコンタクトプラグに電子線を照射するステップと、

前記電子線を照射したコンタクトプラグから放出される二次電子量を検出するステップと、20

前記検出された二次電子量に基づいて、前記電子線が照射されたコンタクトプラグの異常を判定するステップと

を有することを特徴とする。

#### 【0009】

本発明に係る検査用半導体装置の製造方法は、製品用半導体装置の状態を検査するための検査用半導体装置を製造する方法であって、

前記製品用半導体装置を製造するプロセス条件と同じプロセス条件を用いて、導電性部分と絶縁性部分とを含む下地パターン、及び、該下地パターンを覆う絶縁膜を形成する工程と、

前記製品用半導体装置で前記絶縁膜を貫通して前記導電性部分に導通する複数のコンタクトプラグを形成するためのマスクパターンを用い、該マスクパターンを前記下地パターンに対して相対的に所定距離ずらすことによって、前記絶縁膜を貫通し少なくとも一部が前記絶縁性部分で絶縁される複数のコンタクトプラグを形成する工程と30

を備えることを特徴とする。

#### 【0010】

本発明の第2の視点に係る半導体装置の検査方法は、上記検査用半導体装置を用いて製品用半導体装置を評価する半導体装置の検査方法であって、

前記複数のコンタクトプラグの内で、少なくとも前記絶縁性部分上に形成されたコンタクトプラグに電子線を照射するステップと、

前記電子線を照射したコンタクトプラグから放出される二次電子量を検出するステップと、40

前記検出された二次電子量に基づいて、前記電子線が照射されたコンタクトプラグの異常を判定するステップと

を有することを特徴とする。

#### 【発明の効果】

#### 【0011】

本発明に係る半導体装置の検査方法によれば、絶縁性部分で絶縁されたコンタクトプラグがショートした際に生じる電位の変化を、コンタクトプラグから放出される二次電子量の異常で検出することによって、そのコンタクトプラグのショートを直接的に検出できる。これによって、コンタクトプラグのショートを効率的に検出し、半導体装置製造の歩留50

りを大きく向上させることが出来る。

#### 【0012】

また、絶縁性部分で絶縁されたコンタクトプラグの形成に際して、導電性部分に導通する複数のコンタクトプラグを形成するためのマスクパターンを用いるため、検査用の半導体装置におけるコンタクトプラグ及びその近傍を、製品用の半導体装置と同じ構造で形成できる。従って、製品用の半導体装置におけるコンタクトプラグのショートを的確に検出できる。

#### 【0013】

本発明の第1の視点に係る半導体装置の検査方法、及び、検査用半導体装置の製造方法によれば、検査用の半導体装置の製造に際して、製品用の半導体装置の製造工程中で、導電性部分に導通する複数のコンタクトプラグを形成するためのマスクパターンを、下地パターンに対して相対的に所定距離ずらす変更を行うだけでよいので、検査用の半導体装置製造に要するコストを低減できる。

#### 【0014】

本発明の第1の視点に係る半導体装置の検査方法、及び、検査用半導体装置の製造方法では、前記下地パターンの導電性部分及び絶縁性部分がそれぞれ、半導体基板の素子形成領域及び素子分離領域であってもよく、或いは、前記下地パターンの導電性部分が、導体膜の選択エッチングで形成される配線パターンであってもよい。本発明に係る検査用半導体装置の製造方法では、製品用半導体装置がDRAMであってもよい。

#### 【0015】

本発明の第2の視点に係る半導体装置の検査方法の前記異常判定ステップでは、例えば、前記絶縁性部分で絶縁されたコンタクトプラグが、前記導電性部分、他のコンタクトプラグ、及び、他の導電性材料の少なくとも1つに導通するか否かを判定することが出来る。

#### 【発明を実施するための最良の形態】

#### 【0016】

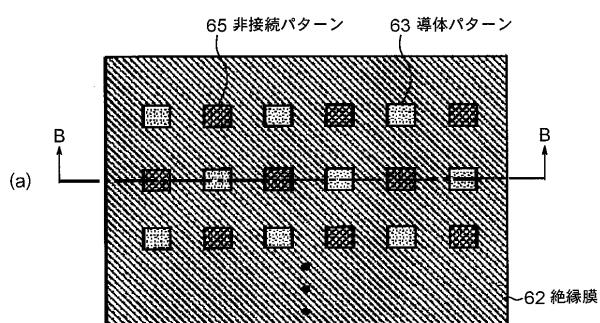

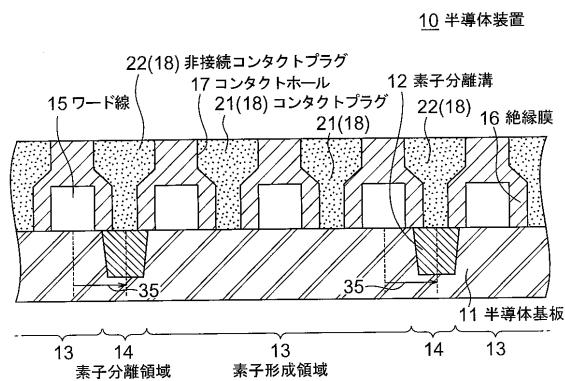

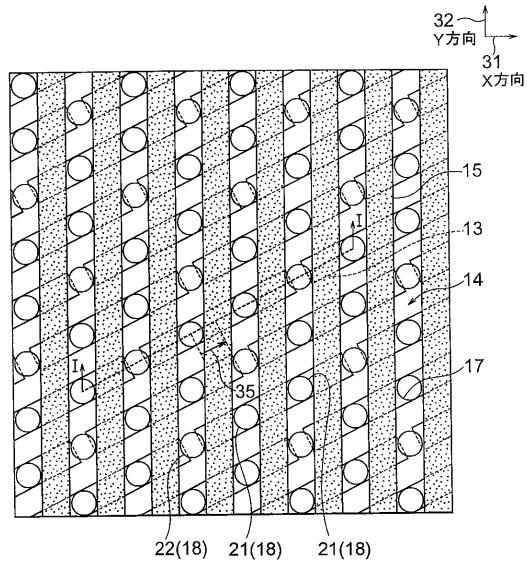

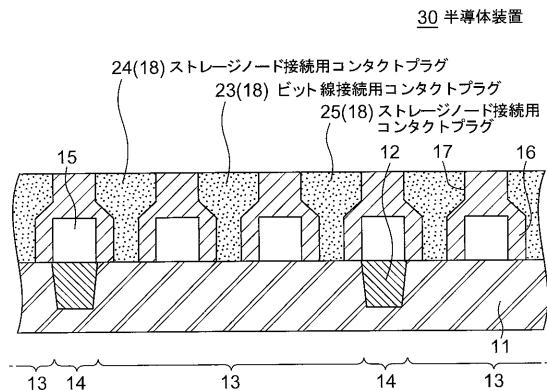

以下に、実施形態を挙げ、添付図面を参照して、本発明の実施の形態を具体的且つ詳細に説明する。図1は、製品用の半導体装置の状態を検査するための、検査用の半導体装置の構成を示す断面図である。半導体装置10は、DRAM(Dynamic Random Access Memory)として構成され、半導体基板11を備える。半導体基板11の表面部分には、絶縁材料を所定のパターンで埋め込んだ素子分離溝12が形成され、素子分離溝12によって構成される素子分離領域14は、半導体素子が形成される素子形成領域13を相互に区画している。

#### 【0017】

半導体基板11上には、図示しないゲート絶縁膜を介して、複数のワード線15が形成され、ワード線15を覆って、絶縁膜16が成膜されている。絶縁膜16を貫通して、半導体基板11に接続するコンタクトホール17が開孔され、コンタクトホール17の内部を埋め込んで、導電材料から成るコンタクトプラグ18が形成されている。コンタクトホール17は、ワード線15の表面を被覆する絶縁膜をマスクとするSAC(Self Align Contact)法によって、隣接するワード線15間の半導体基板11の表面に接続するように形成されている。

#### 【0018】

1つの素子形成領域13には、3つのワード線15が交差し、ワード線15に隣接して半導体基板11にコンタクトする2つのコンタクトプラグ21が形成されている。1つの素子分離領域14には、ワード線15に隣接して素子分離溝12によって絶縁された1つのコンタクトプラグ(非接続コンタクトプラグ)22が形成されている。素子形成領域13、ワード線15、及び、コンタクトプラグ18は、それぞれ等間隔で配設されている。

#### 【0019】

図2は、図1に記載の検査用の半導体装置10の平面構造を示している。図1は、同図のI-I線に沿って見た断面を示している。素子形成領域13は長方形状を有し、ワード

10

20

30

40

50

線 15 は、素子形成領域 13 の長手方向に対して斜め方向に交差している。

#### 【 0 0 2 0 】

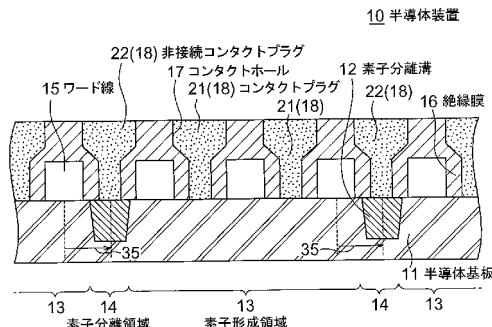

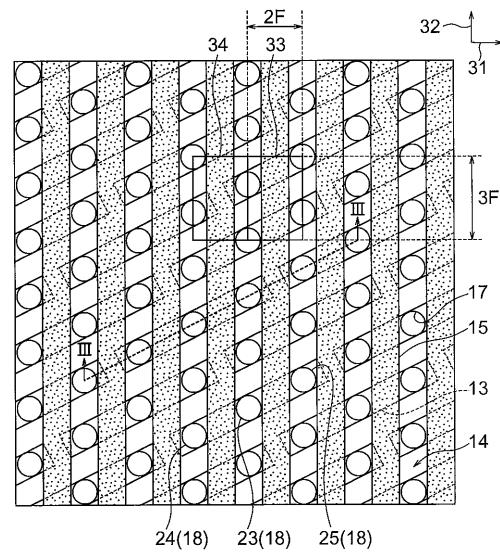

図 3 は、図 1 の検査用の半導体装置に対応する、製品用の半導体装置の構成を示す断面図である。半導体装置 30 では、1 つの素子形成領域 13 には、2 つのワード線 15 が交差し、ワード線 15 に隣接して半導体基板 11 にコンタクトする 3 つのコンタクトプラグ 18 が形成されている。1 つの素子分離領域 14 には、1 つのワード線 15 が交差している。中央のコンタクトプラグ 18 は、図示しない上部のビット線に接続され、ビット線接続用コンタクトプラグ 23 を構成し、両端のコンタクトプラグ 18 は、図示しない上部のストレージノードに接続され、ストレージノード接続用コンタクトプラグ 24, 25 を構成している。

10

#### 【 0 0 2 1 】

図 4 は、図 3 の半導体装置の平面構造を示す図面上で、横方向を X 方向、縦方向を Y 方向としている。図 3 は、同図の III - III 線に沿った断面を示している。半導体装置 30 は、1 交点 6F2 の単位セル 33 を備え、ワード線 15 のピッチの 1/2 の長さを F とすると、単位セル 33 の寸法は X 方向 31 に 2F、Y 方向 32 に 3F であり、その面積は  $6F^2$  ( $2F \times 3F$ ) である。半導体装置 30 は、単位セル 33 と、半導体基板 11 上の構造が、この単位セル 33 の形状と線対称の形状を有する単位セル 34 とが対となって繰り返し配置されるツインセル構造を有する。

#### 【 0 0 2 2 】

図 1、2 に戻り、検査用の半導体装置 10 において、素子分離領域 14 のパターンは、符号 35 で示すように、製品用の半導体装置 30 に対して、X 方向 31 に F、Y 方向 32 に 0.5F だけ全体的にずらして形成されている。これによって、製品用の半導体装置 30 における一方のストレージノード接続用コンタクトプラグ 24 は、素子分離領域 14 に接続され、非接続コンタクトプラグ 22 を構成する。製品用の半導体装置 30 における、ビット線接続用コンタクトプラグ 23、及び、他方のストレージノード接続用コンタクトプラグ 25 は、製品用の半導体装置 30 におけるコンタクトプラグと同様に素子形成領域 13 に接続され、通常のコンタクトプラグ 21 を構成する。検査用の半導体装置 10 では、製品用の半導体装置 30 における絶縁膜 16 より上側の構造は形成されていない。

20

#### 【 0 0 2 3 】

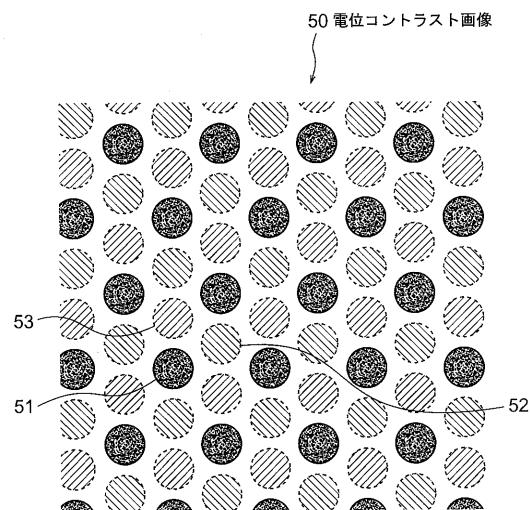

本実施形態に係る半導体装置の検査方法では、SEM 式検査装置を用い、検査用の半導体装置 10 の表面に対して電子線を照射し、半導体装置 10 の表面を走査しつつ、各コンタクトプラグ 18 から放出される二次電子量を測定する。SEM 式検査装置は、二次電子量の測定によって、図 5 に示すように、各コンタクトプラグ 18 から放出された二次電子量に応じた輝度で、各コンタクトプラグ 18 の位置を表示する電位コントラスト画像 50 を表示する。同図中、符号 51 ~ 53 が、非接続コンタクトプラグ 22、ビット線接続用コンタクトプラグ 23 を構成する通常のコンタクトプラグ 21、及び、ストレージノード接続用コンタクトプラグ 25 を構成する通常のコンタクトプラグ 21 に対応する部分をそれぞれ示している。

30

#### 【 0 0 2 4 】

非接続コンタクトプラグ 22 が他の導体とショートしていない場合には、非接続コンタクトプラグ 22 は正又は負に帯電する。逆に、非接続コンタクトプラグ 22 が、例えばワード線 15 との間でショートしている場合には、ワード線 15 を介して電子が逃がされるため、非接続コンタクトプラグ 22 の帯電量は少ない。また、非接続コンタクトプラグ 22 が、通常のコンタクトプラグ 21 との間でショートしている場合にも同様に、非接続コンタクトプラグ 22 の帯電量は少ない。

40

#### 【 0 0 2 5 】

コンタクトプラグ 18 から放出される二次電子量は、各コンタクトプラグ 18 の帯電量に応じた電位によって異なるため、電位コントラスト画像 50 で、ショートした非接続コンタクトプラグ 22 は、ショートしていない非接続コンタクトプラグ 22 とは異なる輝度で表示される。従って、電位コントラスト画像 50 で、個々の非接続コンタクトプラグ 2

50

2の輝度を観察し、他の非接続コンタクトプラグ22と異なる輝度で表示された非接続コンタクトプラグ22を、ショートした非接続コンタクトプラグ22と判定できる。

#### 【0026】

なお、ショートした非接続コンタクトプラグ22の検出に際して、非接続コンタクトプラグ22から放出される二次電子量の上限又は下限のしきい値を設定し、これらのしきい値を上回り又は下回った非接続コンタクトプラグ22を、ショートした非接続コンタクトプラグ22と判定しても構わない。

#### 【0027】

ショートしたと判定された非接続コンタクトプラグ22について更に精密な検査を行うことによって、ショートした詳細な部位を特定できる。なお、非接続コンタクトプラグ22の帯電の正負及び帯電量は、非接続コンタクトプラグ22の材質及び大きさ、絶縁膜16の材質、照射する電子線のエネルギーの大きさによって変化する。

#### 【0028】

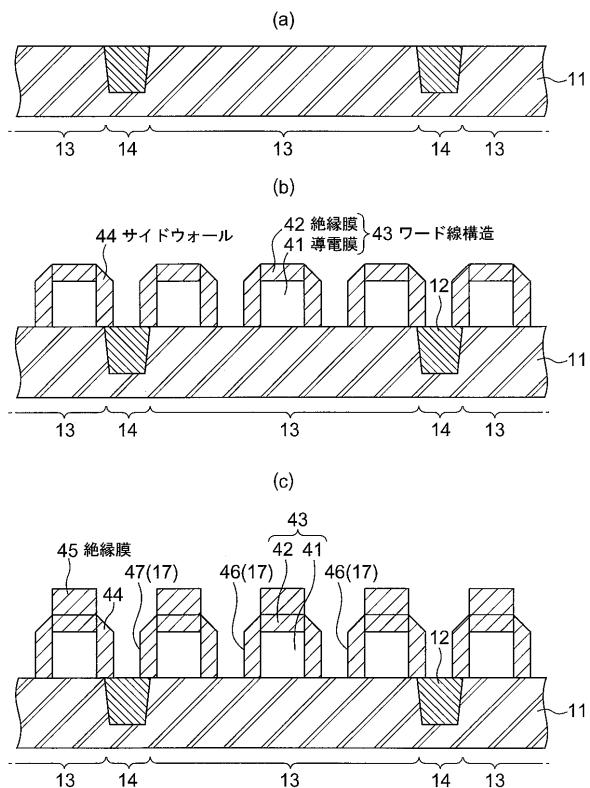

図6(a)～(c)は、図1、2に記載の検査用の半導体装置を製造する各製造段階を順次に示す断面図である。先ず、図6(a)に示すように、公知の方法により、半導体基板11の表面部分に所定のパターン形状で素子分離溝12を形成し、素子分離溝12で構成される素子分離領域14によって、素子形成領域13を区画する。

#### 【0029】

半導体基板11上にゲート絶縁膜(図示なし)を形成した後、ゲート絶縁膜上に導電膜41及び絶縁膜42を順次に成膜する。公知のフォトリソグラフィ技術及びエッチング技術を用いて絶縁膜42及び導電膜41をパターニングし、ワード線構造43を形成する。ワード線構造43の形成に際して、1つの素子形成領域13に3つのワード線構造43が交差し、且つ素子分離領域14に交差しないようにパターニングする。ワード線構造43を覆って全面に絶縁膜を成膜した後、エッチバックを行い、ワード線構造43の側面にサイドウォール44を形成する(図6(b))。

#### 【0030】

全面に絶縁膜45を成膜した後、公知のフォトリソグラフィ技術及びエッチング技術を用い、サイドウォール44をマスクとして自己整合的に絶縁膜45を開孔し、半導体基板11を露出させるコンタクトホール17を形成する。コンタクトホール17の形成に際して、半導体基板の素子形成領域13を露出するコンタクトホール46と、素子分離領域14を露出するコンタクトホール47とが形成される(図6(c))。

#### 【0031】

引き続き、公知の方法を用いて、コンタクトホール17の内部を導電性材料で埋め込むことによって、コンタクトプラグ18を形成する。コンタクトホール46,47に収容されるコンタクトプラグ18が、通常のコンタクトプラグ21及び非接続コンタクトプラグ22をそれぞれ構成し、図1に示した検査用の半導体装置10を製造できる。

#### 【0032】

検査用の半導体装置10の製造方法は、素子分離領域14のパターンを、符号35に示した距離だけずらして形成すること、及び、絶縁膜16より上側の構造を形成しないことを除いては、図3、4に示した製品用の半導体装置30の製造方法と同様である。

#### 【0033】

本実施形態に係る半導体装置の検査方法によれば、製品用の半導体装置30におけるストレージノード接続用コンタクトプラグ24を、半導体基板の素子分離領域14で絶縁して非接続コンタクトプラグ22とし、検査用の半導体装置10を製造する。この検査用の半導体装置10で、非接続コンタクトプラグ22がショートした際に生じる電位の変化を、非接続コンタクトプラグ22から放出される二次電子量の異常で検出することによって、ストレージノード接続用コンタクトプラグ24のショートを直接的に検出できる。これによって、コンタクトプラグのショートを効率的に検出し、半導体装置製造の歩留りを大きく向上させることが出来る。

#### 【0034】

10

20

30

40

50

ところで、図7(a)、(b)に示した半導体装置で、非接続パターン65を半導体基板61の表面部分に形成された素子分離溝にコンタクトプラグを介して接続することによって、このコンタクトプラグのショートを検出することも出来る。しかし、この場合、コンタクトプラグやワード線等の構造が、製品用の半導体装置と同一にならないため、コンタクトプラグとワード線、又は、コンタクトプラグ同士のショートを正確に評価することが容易でない。また、コンタクトプラグを形成するためのマスクが、製品用の半導体装置に用いられるものと同一でないため、マスクを製造するためのコストが別途に必要となる。

#### 【0035】

しかし、本実施形態に係る検査用の半導体装置10は、素子分離領域14のパターンが全体的にずらして形成されていること、及び、絶縁膜16より上側の構造が形成されていないことを除いては、製品用の半導体装置30と同じ構成を備える。つまり、本検査用の半導体装置10は、ワード線15やコンタクトプラグ18、及び、それらを収容する絶縁膜16が、製品用の半導体装置30と同じ構成を有するので、製品用の半導体装置30におけるコンタクトプラグ18のショートを的確に検出できる。10

#### 【0036】

また、検査用の半導体装置10の製造に際して、製品用の半導体装置30の製造工程中で、素子分離領域14のパターンの形成の際に用いるマスクを所定距離だけずらす変更を行うだけでよいので、検査用の半導体装置10製造に要するコストを低減できる。なお、素子分離領域14のパターンの形成の際に用いるマスクに代えて、半導体基板11上に形成されるワード線15やコンタクトホール17等のパターンを形成するためのマスクを、それぞれ所定距離だけずらす変更を行うことによっても、検査用の半導体装置10を製造できる。20

#### 【0037】

本実施形態に係る半導体装置の検査方法では、更に、ショートした非接続コンタクトプラグ22の検出に際して、電位コントラスト画像50を参照して、他の非接続コンタクトプラグ22と輝度が異なる非接続コンタクトプラグ22を検出する方法を用いることによつて、ショートした非接続コンタクトプラグ22を容易に検出できる。

#### 【0038】

なお、上記実施形態では、通常のコンタクトプラグ21のそれぞれは、素子形成領域13に導通しているため、電子線の照射後にほぼ同じ電位に保たれ、相互間のショートの検出は容易でない。しかし、例えば、上記検査用の半導体装置10とは別に、ビット線接続用コンタクトプラグ23、又は、他方のストレージノード接続用コンタクトプラグ25を素子分離領域14に位置合わせして、非接続コンタクトプラグ22とする検査用の半導体装置を製造することによって、これらコンタクトプラグ23、25のショートを検出できる。30

#### 【0039】

また、半導体基板11表面に成膜された絶縁膜16を貫通するコンタクトプラグだけでなく、絶縁膜16上に成膜された上層の絶縁膜を貫通するコンタクトプラグのショートを検出することも出来る。この場合、例えば、上層の絶縁膜を貫通するコンタクトプラグの内の一部を、導体膜の選択エッチングで形成された配線パターンや下層のコンタクトプラグ等の導体に接続して通常のコンタクトプラグとし、他のコンタクトプラグを、下層の絶縁膜の表面等に接続して非接続コンタクトプラグとする。この場合にも、製品用の半導体装置の製造方法において、1又は複数の所定のマスクを所定量だけずらすことによって、製品用の半導体装置の製造に用いるマスクと同じマスクを用いて、検査用の半導体装置を製造できる。40

#### 【0040】

以上、本発明をその好適な実施形態に基づいて説明したが、本発明に係る半導体装置の検査方法、及び、検査用半導体装置の製造方法は、上記実施形態の構成にのみ限定されるものではなく、上記実施形態の構成から種々の修正及び変更を施した半導体装置の検査方50

法、及び、検査用半導体装置の製造方法も本発明の範囲に含まれる。

【図面の簡単な説明】

【0041】

【図1】本発明の一実施形態に係る検査用の半導体装置の構成を示す断面図である。

【図2】図1の半導体装置の平面構造を示す平面図である。

【図3】製品用の半導体装置の構成を示す断面図である。

【図4】図3の半導体装置の平面構造を示す平面図である。

【図5】図1、2の半導体装置の測定によって得られた電位コントラスト画像を模式的に示す平面図である。 10

【図6】図6(a)～(c)は、図1、2の半導体装置を製造する各製造段階を順次に示す断面図である。

【図7】図7(a)は、特許文献1に記載の検査用の半導体装置の構成を示す平面図であり、図7(b)は、図7(a)のB-B線に沿った断面を示す断面図である。

【符号の説明】

【0042】

10 : 検査用の半導体装置

11 : 半導体基板

12 : 素子分離溝

13 : 素子形成領域

14 : 素子分離領域

15 : ワード線

16 : 絶縁膜

17 : コンタクトホール

18 : コンタクトプラグ

21 : (通常の)コンタクトプラグ

22 : 非接続コンタクトプラグ

23 : ビット線接続用コンタクトプラグ

24, 25 : ストレージノード接続用コンタクトプラグ

31 : X方向

32 : Y方向

33, 34 : 単位セル

35 : 素子分離領域のパターンのずれ量

41 : 導電膜

42 : 絶縁膜

43 : ワード線構造

44 : サイドウォール

45 : 絶縁膜

46, 47 : コンタクトホール

50 : 電位コントラスト画像

51 : 非接続コンタクトプラグに対応する部分

52, 53 : 通常のコンタクトプラグに対応する部分 40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

60 半導体装置