(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6397635号

(P6397635)

(45) 発行日 平成30年9月26日(2018.9.26)

(24) 登録日 平成30年9月7日(2018.9.7)

(51) Int.Cl.

H01L 29/786 (2006.01)

F 1

H01L 29/78 618 E

H01L 29/78 618 B

請求項の数 3 (全 51 頁)

(21) 出願番号 特願2014-35120 (P2014-35120)

(22) 出願日 平成26年2月26日 (2014. 2. 26)

(65) 公開番号 特開2014-195063 (P2014-195063A)

(43) 公開日 平成26年10月9日 (2014. 10. 9)

審査請求日 平成29年2月20日 (2017. 2. 20)

(31) 優先権主張番号 特願2013-37673 (P2013-37673)

(32) 優先日 平成25年2月27日 (2013. 2. 27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 須澤 英臣

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 下村 明久

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 田中 哲弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

n型の導電性を付与する不純物を含有する第1の領域と、前記第1の領域よりもn型の導電性を付与する不純物濃度が低い第2の領域を有する第1の酸化物半導体層と、

前記第1の領域の少なくとも一部と接する第2の酸化物半導体層と、

前記第1の酸化物半導体層の下層に接する第1の酸化物層と、

前記第2の酸化物半導体層の上層に接する第2の酸化物層と、

前記第1の領域及び前記第2の領域と重なるゲート電極層と、

前記第1の酸化物半導体層と前記ゲート電極層との間のゲート絶縁層と、

前記第1の酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、を有し、 10

前記第1の酸化物層は、前記第1の酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含み、

前記第2の酸化物層は、前記第2の酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含み、

前記第2の酸化物半導体層は、前記第1の酸化物半導体層の上面と接する領域と、前記第1の酸化物半導体層の側面と接する領域とを有する半導体装置。

## 【請求項 2】

請求項1において、

前記第1の領域の少なくとも一部は、前記ソース電極層及び前記ドレイン電極層とそれ

10

20

それ重なる半導体装置。

【請求項 3】

請求項 1 または 2 において、

前記ゲート電極層は、前記ソース電極層と重なる領域を有し、且つ、前記ドレイン電極層と重なる領域を有さない半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、物（プロダクト。機械（マシン）、製品（マニュファクチャ）、組成物（コンポジション・オブ・マター）を含む。）及び方法（プロセス。単純方法及び生産方法を含む。）に関する。特に、本発明の一態様は、半導体装置、発光装置、蓄電装置、それらの駆動方法又はそれらの製造方法に関する。

10

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、パワーデバイス、パワーデバイスを有する集積回路、電源回路、又は電力変換回路の他、電気光学装置、半導体回路、電子機器は、半導体装置の範疇に入る、あるいは、半導体装置を含む。

【背景技術】

【0003】

パワーデバイスとして用いられる半導体装置には、シリコンを用いて作製されるパワーデバイスが広く流通している。しかしながら、シリコンを用いたパワーデバイスの性能は限界に近づいており、さらなる高性能化を実現することが困難となってきている。

20

【0004】

また、シリコンはバンドギャップが小さいため、シリコンを用いたパワーデバイスは動作温度範囲に限界がある。このため、近年ではバンドギャップの広いSiCやGaNを用いたパワーデバイスの開発が進められている。

【0005】

また、大電力向けのパワーデバイスとして用いられる半導体装置に、酸化物半導体を適用する技術が開示されている（特許文献 1 及び特許文献 2）。

30

【先行技術文献】

【特許文献】

【0006】

【特許文献 1】特開 2011 - 91382 号公報

【特許文献 2】特開 2011 - 172217 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の一態様は、大電力向けのパワーデバイスに適用可能な、酸化物半導体を含む半導体装置を提供することを課題の一とする。または、本発明の一態様は、大電流を流すことが可能な半導体装置を提供することを課題の一とする。または、本発明の一態様は、信頼性の高い半導体装置を提供することを課題の一とする。

40

【0008】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様はこれらの全てを解決する必要はないものとする。また、これら以外の課題は、明細書、図面、請求項等の記載から自ずと明らかになるものである。従って、明細書、図面、請求項からこれら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0009】

本発明の一態様は、電流の主な経路（チャネル形成領域）として、n型領域を含む酸化物半導体層を適用することで、オン電流の大きい半導体装置を実現する。また、該n型領域

50

を含む酸化物半導体層とソース電極層との間に、i型領域を含む酸化物半導体層を設けることで、ピンチオフ動作を可能とする。または、本発明の一態様の半導体装置は、チャネル長方向の断面図において、チャネル形成領域として機能する、n型領域を含む酸化物半導体層を取り囲むように、i型の酸化物半導体層が設けられた構造を含む。より具体的には、例えば以下の構成とすることができます。

#### 【0010】

本発明の一態様は、n型の導電性を付与する不純物を含有する第1の領域を含む第1の酸化物半導体層と、第1の領域の少なくとも一部と接する第2の酸化物半導体層と、第1の酸化物半導体層の下層に接する第1の酸化物層と、第2の酸化物半導体層の上層に接する第2の酸化物層と、第1の領域と重なるゲート電極層と、第1の酸化物半導体層とゲート電極層との間のゲート絶縁層と、第1の酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、を有し、第1の酸化物層は、第1の酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含み、第2の酸化物層は、第2の酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含み、第2の酸化物半導体層は、第1の酸化物半導体層の上面及び側面を覆う半導体装置である。

#### 【0011】

本発明の一態様は、n型の導電性を付与する不純物を含有する第1の領域と、i型の酸化物半導体を含む第2の領域とを含む第1の酸化物半導体層と、第1の領域の少なくとも一部と接する第2の酸化物半導体層と、第2の領域の少なくとも一部と接し、第1の酸化物半導体層の下層に設けられた第1の酸化物層と、第2の酸化物半導体層の上層に接する第2の酸化物層と、第1の領域と重なるゲート電極層と、第1の酸化物半導体層とゲート電極層との間のゲート絶縁層と、第1の酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、を有し、第1の酸化物層は、第1の酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含み、第2の酸化物層は、第2の酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含み、第2の酸化物半導体層は、第1の酸化物半導体層の上面及び側面を覆う半導体装置である。

#### 【0012】

上記の半導体装置において、ソース電極層及びドレイン電極層は第2の酸化物層上に接して設けられていてもよい。または、上記の半導体装置において、ソース電極層及びドレイン電極層は第2の酸化物半導体層上に接して設けられ、ソース電極層及びドレイン電極層上に第2の酸化物層が設けられていてもよい。

#### 【0013】

また、上記の半導体装置において、第1の領域の少なくとも一部はソース電極層及びドレイン電極層とそれぞれ重なって設けられていてもよい。または、チャネル長方向の断面において、第1の領域の一方の端部はソース電極層の一方の端部と一致し、第1の領域の他方の端部はドレイン電極層の一方の端部と一致してもよい。

#### 【0014】

また、上記の半導体装置において、ゲート電極層はソース電極層と重なる領域を有し、且つ、ドレイン電極層と重なる領域を有さない構造としてもよい。

#### 【発明の効果】

#### 【0015】

本発明の一態様により、大電力向けのパワーデバイスに適用可能な、酸化物半導体を含む半導体装置を提供することができる。または、本発明の一態様により、大電流を流すことが可能な半導体装置を提供することができる。または、本発明の一態様により、信頼性の高い半導体装置を提供することができる。

#### 【図面の簡単な説明】

#### 【0016】

【図1】半導体装置の一態様を説明する平面図及び断面図。

10

20

30

40

50

【図2】半導体装置に含まれる積層構造及びバンド構造を説明する図。

【図3】半導体装置の作製方法の一例を説明する断面図。

【図4】半導体装置の作製方法の一例を説明する断面図。

【図5】半導体装置の一態様を説明する断面図。

【図6】半導体装置の一態様を説明する平面図及び断面図。

【図7】半導体装置の作製方法の一例を説明する断面図。

【図8】半導体装置の一態様を説明する平面図及び断面図。

【図9】半導体装置の一態様を説明する平面図及び断面図。

【図10】半導体装置の作製方法の一例を説明する断面図。

【図11】半導体装置の作製方法の一例を説明する断面図。

【図12】半導体装置の一態様を説明する平面図及び断面図。

10

【図13】実施の形態に係る、酸化物半導体の極微電子線回折パターン。

【図14】実施の形態に係る、電力変換回路の構成例。

【図15】実施の形態に係る、電力変換回路の構成例。

【図16】実施の形態に係る、電源回路の構成例。

【図17】実施の形態に係る、電源回路の構成例。

【図18】実施の形態に係る、電子機器。

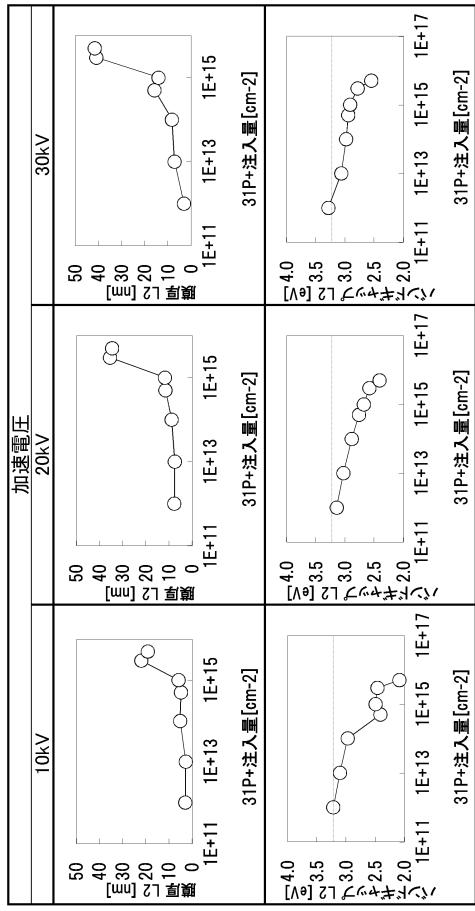

【図19】実施例に係る、加速電圧とリンのドーザ量に対する酸化物半導体膜の低抵抗領域の深さとバンドギャップの関係を示す図。

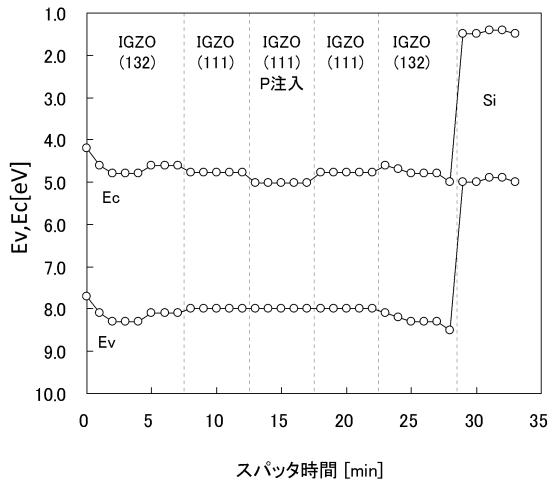

【図20】実施例に係る、バンド構造を示す図。

20

【発明を実施するための形態】

【0017】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0018】

なお、以下に説明する本発明の構成において、同一部分又は同様の機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を有する部分を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

30

【0019】

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0020】

なお、本明細書あるいは請求項において、第1、第2等として付される序数詞は、便宜上用いるものであり、工程順または積層順を示すものではない。また、発明を特定するための事項として固有の名称を示すものではない。

【0021】

(実施の形態1)

40

本実施の形態では、半導体装置及び半導体装置の作製方法の一形態を図1乃至図8を参照して説明する。本実施の形態では、半導体装置の一例として、酸化物半導体層を含むトップゲート型のトランジスタを示す。

【0022】

<半導体装置の構成例1>

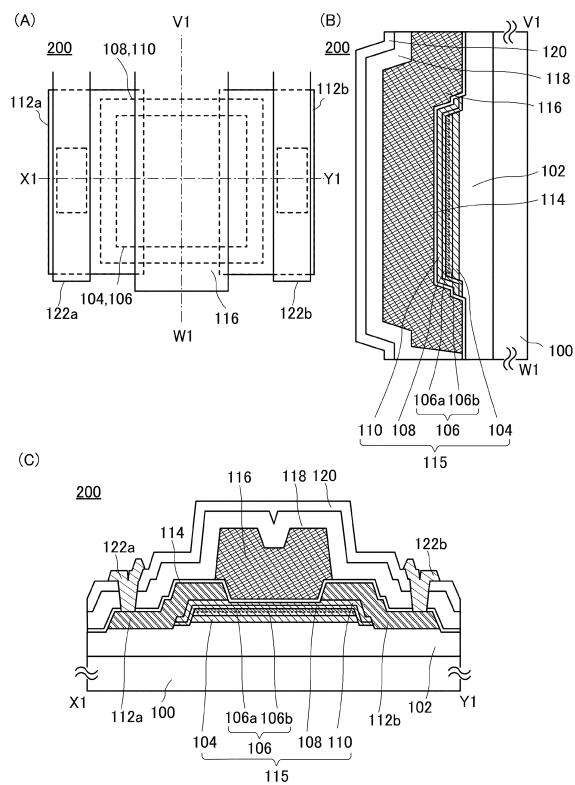

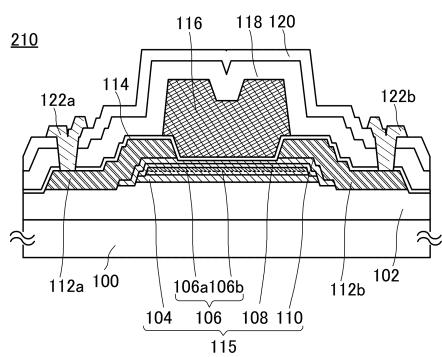

図1にトランジスタ200の構成例を示す。図1(A)は、トランジスタ200の平面図であり、図1(B)は、図1(A)のV1-W1における断面図であり、図1(C)は、図1(A)のX1-Y1における断面図である。

【0023】

図1に示すトランジスタ200は、絶縁表面を有する基板100上に設けられた下地絶縁

50

層 102 と、下地絶縁層 102 上の第 1 の酸化物層 104 と、第 1 の酸化物層 104 上の第 1 の酸化物半導体層 106 と、第 1 の酸化物半導体層 106 の上面及び側面を覆う第 2 の酸化物半導体層 108 と、第 2 の酸化物半導体層 108 上の第 2 の酸化物層 110 と、第 2 の酸化物層 110 上のソース電極層 112a 及びドレイン電極層 112b と、第 2 の酸化物層 110 上のゲート絶縁層 114 と、ゲート絶縁層 114 を介して第 1 の酸化物半導体層 106 と重なるゲート電極層 116 と、を含む。また、ゲート電極層 116 上の絶縁層 118 及び絶縁層 120 をそれぞれトランジスタ 200 の構成要素に含んでもよい。また、ゲート絶縁層 114、絶縁層 118 及び絶縁層 120 に設けられたコンタクトホールを介してソース電極層 112a 及びドレイン電極層 112b とそれぞれ電気的に接続する電極層 122a 及び電極層 122b を含んでもよい。

10

## 【0024】

トランジスタ 200 に含まれる構成要素について、以下に詳述する。

## 【0025】

## 基板

基板 100 は、単なる支持部材に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタ 200 のゲート電極層 116、ソース電極層 112a、ドレイン電極層 112b、電極層 122a 又は電極層 122b の少なくとも一つは、上記の他のデバイスと電気的に接続されていてもよい。

## 【0026】

## 下地絶縁層

20

下地絶縁層 102 は、基板 100 からの不純物の拡散を防止する役割を有する他、第 1 の酸化物層 104、第 1 の酸化物半導体層 106、第 2 の酸化物半導体層 108、及び／又は第 2 の酸化物層 110 に酸素を供給する役割を担う。よって、下地絶縁層 102 には酸素を含む絶縁層を用いるものとする。下地絶縁層 102 から酸素が供給されることで、第 1 の酸化物半導体層 106 及び第 2 の酸化物半導体層 108 における酸素欠損を低減することが可能となる。また、基板 100 として他のデバイスが形成された基板を適用する場合、下地絶縁層 102 は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるように CMP (Chemical Mechanical Polishing) 法等で平坦化処理を行うことが好ましい。

## 【0027】

30

本実施の形態のトランジスタ 200 において、酸素を含有する下地絶縁層 102 がチャネル形成領域となる第 1 の酸化物半導体層 106 を含む積層構造の下方に設けられている。このような構成とすることで、下地絶縁層 102 に含まれる酸素をチャネル形成領域へ供給することが可能となる。下地絶縁層 102 は、化学量論的組成より過剰に酸素を含有することが好ましい。下地絶縁層 102 が過剰に酸素を含有することで、チャネル形成領域への酸素の供給がより促進される。

## 【0028】

なお、本明細書や請求項において、過剰な酸素とは、加熱処理により酸化物半導体層中、又は酸化シリコン中、又は酸化窒化シリコン中を移動可能な酸素、又は、本来の化学量論的組成にある酸素より過剰に存在する酸素を示す。

40

## 【0029】

## 第 1 及び第 2 の酸化物層、第 1 及び第 2 の酸化物半導体層

トランジスタ 200 は、下地絶縁層 102 とゲート絶縁層 114 との間に、第 1 の酸化物層 104、第 1 の酸化物半導体層 106、第 2 の酸化物半導体層 108、及び第 2 の酸化物層 110 を含む積層構造（以下、酸化物積層 115 とも表記する。）を有する。

## 【0030】

第 1 の酸化物半導体層 106 及び第 2 の酸化物半導体層 108 としては、インジウム (In) もしくは亜鉛 (Zn) を含むことが好ましい。または、In と Zn の双方を含むことが好ましい。また、酸化物半導体層を用いたトランジスタの電気特性のばらつきを減らすため、インジウム及び亜鉛と共に、スタビライザーを含むことが好ましい。

50

## 【0031】

スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)等がある。

## 【0032】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、In-Zn酸化物、Sn-Zn酸化物、Al-Zn酸化物、Zn-Mg酸化物、Sn-Mg酸化物、In-Mg酸化物、In-Ga酸化物、In-Ga-Zn酸化物、In-Al-Zn酸化物、In-Sn-Zn酸化物、Sn-Ga-Zn酸化物、Al-Ga-Zn酸化物、Sn-Al-Zn酸化物、In-Hf-Zn酸化物、In-La-Zn酸化物、In-Ce-Zn酸化物、In-Pr-Zn酸化物、In-Nd-Zn酸化物、In-Sm-Zn酸化物、In-Eu-Zn酸化物、In-Gd-Zn酸化物、In-Tb-Zn酸化物、In-Dy-Zn酸化物、In-Ho-Zn酸化物、In-Er-Zn酸化物、In-Tm-Zn酸化物、In-Yb-Zn酸化物、In-Lu-Zn酸化物、In-Sn-Ga-Zn酸化物、In-Hf-Ga-Zn酸化物、In-Al-Ga-Zn酸化物、In-Sn-Al-Zn酸化物、In-Sn-Hf-Zn酸化物、In-Hf-Al-Zn酸化物等を用いることができる。

10

## 【0033】

なお、第1の酸化物半導体層106及び第2の酸化物半導体層108は、構成元素を同一とすることが好ましく、その組成を同一とすることがより好ましい。第1の酸化物半導体層106と第2の酸化物半導体層108の組成を揃えることにより、伝導帯下端のエネルギーをできるだけ近づけることができる。その結果、いずれかの層に電流経路が偏ることなくいずれの層も主たる電流経路として用いることができるため、トランジスタのソース-ドレイン間の直列抵抗を低減することができる。

## 【0034】

本実施の形態においては、第1の酸化物半導体層106及び第2の酸化物半導体層108として、少なくともインジウム、亜鉛、及びM(Mは、Al、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物で表記される酸化物半導体を適用する。

30

## 【0035】

第1の酸化物半導体層106の下層に接する第1の酸化物層104、及び第2の酸化物半導体層108の上層に接する第2の酸化物層110には、酸化物半導体層において不純物となる元素(例えば、シリコン)以外の元素を、主成分として含む酸化物層を適用する。例えば、第1の酸化物層104には、第1の酸化物半導体層106を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含む酸化物層を適用する。また、第2の酸化物層110は、第2の酸化物半導体層108を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含む酸化物層を適用する。

40

## 【0036】

本実施の形態では、第1の酸化物層104として、In-M-Zn酸化物(Mは、Al、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)で表記され、第1の酸化物半導体層106よりもMの原子数比が高い酸化物層を含む。具体的には、第1の酸化物層104として、第1の酸化物半導体層106よりも上述の元素Mを1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物層を適用する。前述の元素Mはインジウムよりも酸素と強く結合するため、酸化物層に酸素欠損が生じることを抑制する機能を有する。すなわち、第1の酸化物層104は、第1の酸化物半導体層106よりも酸素欠損が生じにくい酸化物層である。また、インジウム又は亜鉛に対する

50

前述の元素Mの割合が大きいほど、エネルギーギャップの大きい酸化物となるため、第1の酸化物層104は、第1の酸化物半導体層106よりも大きなバンドギャップを有する酸化物層である。

#### 【0037】

また、本実施の形態では、第2の酸化物層110として、In-M-Zn酸化物(Mは、Al、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)で表記され、第2の酸化物半導体層108よりもMの原子数比が高い酸化物層を含む。具体的には、第2の酸化物層110として、第2の酸化物半導体層108よりも上述の元素Mを1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物層を適用する。よって、第2の酸化物層110は、第2の酸化物半導体層108よりも酸素欠損が生じにくく、且つ、第2の酸化物半導体層108よりも大きなバンドギャップを有する酸化物層である。トランジスタ200において、第2の酸化物層110は、チャネル形成領域として機能する第1の酸化物半導体層106と、ソース電極層112a及びドレイン電極層112bとの間に位置する酸化物層であるため、Mの原子数比は、第2の酸化物層110が半導体として機能することが可能なバンドギャップを維持できる程度以下に調整することが好ましい。但し、Mの原子数比によっては第2の酸化物層110がゲート絶縁層の一部として機能することもある。

#### 【0038】

第1の酸化物層104、第1の酸化物半導体層106、第2の酸化物半導体層108及び第2の酸化物層110が、少なくともインジウム、亜鉛、及びM(Mは、Al、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物であるとき、第1の酸化物層104を、 $In : M : Zn = x_1 : y_1 : z_1$  [原子数比]、第1の酸化物半導体層106及び第2の酸化物半導体層108を $In : M : Zn = x_2 : y_2 : z_2$  [原子数比]、第2の酸化物層110を $In : M : Zn = x_3 : y_3 : z_3$  [原子数比]とすると、 $y_1 / x_1$  および  $y_3 / x_3$  が  $y_2 / x_2$  よりも大きくなることが好ましい。 $y_1 / x_1$  および  $y_3 / x_3$  は  $y_2 / x_2$  よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、第1の酸化物半導体層106及び第2の酸化物半導体層108において、 $y_2$  が  $x_2$  以上であるとトランジスタの電気特性を安定させることができる。ただし、 $y_2$  が  $x_2$  の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$  は  $x_2$  の3倍未満であることが好ましい。

#### 【0039】

なお、第1の酸化物層104がIn-M-Zn酸化物であるとき、Znと酸素を除くと、好ましくはInが50 atomic %未満、Mが50 atomic %以上、さらに好ましくはInが25 atomic %未満、Mが75 atomic %以上とする。また、第1の酸化物半導体層106及び第2の酸化物半導体層108がそれぞれIn-M-Zn酸化物であるとき、Znと酸素を除くと、好ましくはInが25 atomic %以上、Mが75 atomic %未満、さらに好ましくはInが34 atomic %以上、Mが66 atomic %未満とする。また、第2の酸化物層110がIn-M-Zn酸化物であるとき、Znと酸素を除くと、好ましくはInが50 atomic %未満、Mが50 atomic %以上、さらに好ましくはInが25 atomic %未満、Mが75 atomic %以上とする。

#### 【0040】

なお、第1の酸化物層104と第2の酸化物層110とは、異なる構成元素を含む層としてもよいし、同じ構成元素を同一の原子数比で、又は異なる原子数比で含む層としてもよい。

#### 【0041】

第1の酸化物層104、第1の酸化物半導体層106、第2の酸化物半導体層108、第2の酸化物層110には、例えばインジウム、亜鉛、及びガリウムを含んだ酸化物半導体を用いることができる。

#### 【0042】

10

20

30

40

50

第1の酸化物層104、第1の酸化物半導体層106、第2の酸化物半導体層108、及び第2の酸化物層110の各々の厚さは、トランジスタ200に要求される電気的特性（出力電流など）に応じて設定すればよい。例えば、第2の酸化物層110の厚さは、3nm以上500nm以下、好ましくは3nm以上100nm以下、より好ましくは3nm以上50nm以下とする。また、第1の酸化物半導体層106及び第2の酸化物半導体層108のそれぞれの厚さは、3nm以上500nm以下、好ましくは3nm以上200nm以下、より好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。また、第1の酸化物層104の厚さは、上記第2の酸化物層110、第1の酸化物半導体層106、または第2の酸化物半導体層108と同等かそれ以上の厚さとすることが好ましい。

10

#### 【0043】

また、第1の酸化物層104は、第1の酸化物半導体層106を構成する金属元素を一種以上含み、伝導帯下端のエネルギーが第1の酸化物半導体層106よりも、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上であって、2eV以下、1eV以下、0.5eV以下、または0.4eV以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。同様に、第2の酸化物層110は、第2の酸化物半導体層108を構成する金属元素を一種以上含み、伝導帯下端のエネルギーが第2の酸化物半導体層108よりも、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上であって、2eV以下、1eV以下、0.5eV以下、または0.4eV以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

20

#### 【0044】

ここで、第1の酸化物半導体層106は、n型の導電性を付与する不純物を含有する第1の領域106aを含む。トランジスタ200では、ソース電極層112a、ドレイン電極層112b及びゲート電極層116と重なるように、第1の酸化物半導体層106の上面の全領域に第1の領域106aが形成される。また、第2の酸化物半導体層108の一部は、第1の領域106aに接するように設けられる。

#### 【0045】

本明細書等において、第1の領域106aに含まれるn型の導電性を付与する不純物としては、例えば、リン(P)、砒素(As)、アンチモン(Sb)、ホウ素(B)、アルミニウム(Al)、窒素(N)、アルゴン(Argon)、ヘリウム(Helium)、ネオン( Neon )、インジウム(Indium)、フッ素(F)、塩素(Cl)、水素(H)、チタン(Titanium)、及び亜鉛(Zinc)などが挙げられる。

30

#### 【0046】

なお、ここでは、第1の酸化物半導体層106の上面に導電性が高められた第1の領域106aを有している場合を示すが、当該領域が第1の酸化物半導体層106の厚さ方向の全域に渡って形成されていてもよいし、第1の酸化物層104の一部にn型の導電性を付与する不純物が含まれていてもよい。但し、第1の酸化物半導体層106において、第1の領域106aと第1の酸化物層104との間には、n型不純物の含有濃度が低い領域、好ましくは、i型又は実質的にi型の酸化物半導体を含む領域である、第2の領域106bを含むことが好ましい。

40

#### 【0047】

このような構造において、ゲート電極層116に電界を印加すると、酸化物半導体層を含む積層構造のうち、伝導帯下端のエネルギーが最も小さい層である第1の酸化物半導体層106及び第2の酸化物半導体層108（特に、第1の酸化物半導体層106の第1の領域106a）にチャネルが形成される。すなわち、第1の領域106aを含む第1の酸化物半導体層106とゲート絶縁層114との間に第2の酸化物層110が形成されていることによって、トランジスタ200のチャネルをゲート絶縁層114と接しない構造とすることができる。

#### 【0048】

また、第1の酸化物半導体層106の上側及び下側に、第1の酸化物半導体層106より

50

も酸素欠損の生じにくい酸化物層を設けることで、トランジスタのチャネルにおける酸素欠損の形成を抑制することができる。

【0049】

第1の酸化物半導体層106に、n型の導電性を付与する不純物を含む第1の領域106aを設けることにより、トランジスタ200のオン状態におけるソース・ドレイン間の直列抵抗を低減することができる。その結果、オン状態におけるソース・ドレイン間に流れる電流（オン電流ともいう）を高めることができる。

【0050】

また、図1(C)に示すように、ソース電極層112aと第1の領域106aとが重なるように設けられることにより、第2の酸化物層110及び第2の酸化物半導体層108を介して、ソース電極層112aから第1の領域106aへキャリアが供給されやすくなり、オン電流を増加させることができる。

10

【0051】

第1の酸化物半導体層106にn型の導電性を付与する不純物を導入する方法としては、例えばイオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法などを用いることができる。

【0052】

第1の領域106aにおいて、上述した元素の濃度は、第1の酸化物半導体層106の厚さ方向に連続的な勾配を有していてもよい。

20

【0053】

第2の酸化物半導体層108は、第1の酸化物半導体層106の第1の領域106aと接し、第1の酸化物半導体層106の上面及び側面を覆うように設けられる（図1(B)及び図1(C)参照）。第2の酸化物半導体層108は、i型又は実質的にi型の酸化物半導体を含むことが好ましい。ソース電極層112aと第1の領域106aとの間に、i型又は実質的にi型である第2の酸化物半導体層108を設けることで、トランジスタ200のオン動作、オフ動作を確実なものとすることができる。さらにはノーマリーオフ型のトランジスタ200を実現することができる。

【0054】

ここで、ソース電極層112aと第1の領域106aとが接しないよう、これらの距離を十分にとるために、第2の酸化物半導体層108の厚さを調整することが好ましい。例えば、ソース電極層112aと重なる領域において、第2の酸化物半導体層108の厚さを10nm以上40nm以下、好ましくは20nm以上40nm以下とすると、オン電流を犠牲にすることなくトランジスタ200のオン動作、オフ動作を確実なものとすることができ、さらにはノーマリーオフ型のトランジスタ200を実現できる。

30

【0055】

また、第2の酸化物半導体層108は、第1の酸化物半導体層106の側面及び上面を覆うように設けられているため、第1の領域106aとソース電極層112aとの間とともに、第1の領域106aとドレイン電極層112bとの間にも位置している。これにより、第1の領域106aがソース電極層112a及びドレイン電極層112bと直接接することができないため、トランジスタ200のオフ状態におけるソース・ドレイン間のリーク電流（オフ電流ともいう）を低減しつつ、トランジスタ200のオン電流を高めることができる。

40

【0056】

また、図1(B)に示すように、トランジスタ200はチャネル幅方向の断面において、島状の第1の酸化物半導体層106の側面を第2の酸化物半導体層108が覆い、さらに第2の酸化物半導体層108の側面を第2の酸化物層110によって覆う構成を有する。当該構成とすることで、第1の酸化物半導体層106及び/又は第2の酸化物半導体層108のチャネル幅方向端部において生じうる寄生チャネルの影響を低減することができる。よって、トランジスタ200の信頼性を向上させることができる。

【0057】

50

なお、酸素を十分に含み、高純度化された酸化物半導体層（第1の酸化物半導体層106及び第2の酸化物半導体層108）は、バンドギャップが2.8eV乃至3.2eV程度であり、少数キャリアが $1 \times 10^{-9}$ 個/cm<sup>3</sup>程度と極めて少なく、多数キャリアはトランジスタのソースから来るのみである。そのため、当該酸化物半導体層を用いたトランジスタはアバランシェブレークダウンがない。

#### 【0058】

そのため、数10V、または数100Vといった高い電圧で駆動した場合であっても、トランジスタのチャネル長に対するチャネル幅を極めて大きく設定することができ、結果として、トランジスタのオン電流をより高めることができる。例えばチャネル長に対するチャネル幅の比（W/L）を、10<sup>3</sup>以上、さらには10<sup>4</sup>以上、あるいは10<sup>5</sup>以上とした場合でも、良好なオンオフ動作が実現できる。例えば30V以下で駆動させる場合、チャネル長を3μmとしたときのチャネル幅は、1cm以上10m以下の範囲、例えば80cmとすればよい。

10

#### 【0059】

また、酸化物半導体はバンドギャップが大きいため、酸化物半導体を適用したトランジスタは、その電気的特性の温度依存性を極めて小さいものとすることができます。例えば半導体としてシリコンを用いた場合などに比べて、しきい値電圧やオン電流、オフ電流などの温度依存性の小さいトランジスタを実現できる。したがって、酸化物半導体を適用したトランジスタは高温環境下における動作に適しているといえる。

#### 【0060】

20

##### ソース電極層及びドレイン電極層

ソース電極層112a及びドレイン電極層112bには、酸素と結合し易い導電材料を好ましく用いることができる。例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどを用いることができる。後のプロセス温度が比較的高くできることなどから、融点の高いWを用いることが特に好ましい。なお、酸素と結合し易い導電材料には、酸素が拡散し易い材料も含まれる。

#### 【0061】

30

このような導電材料と酸化物積層115を接触させると、酸化物積層115中の酸素が、酸素と結合し易い導電材料側に取り込まれる。トランジスタの作製工程には、いくつかの加熱工程があることから、上記酸素の移動により、酸化物積層115においてソース電極層112a又はドレイン電極層112bと接触した界面近傍の領域に酸素欠損が発生し、n型化した領域を形成することがある。該n型化した領域はトランジスタ200のソースまたはドレインとして作用させることができる。

#### 【0062】

なお、n型化した領域には、ソース電極層112a及びドレイン電極層112bの構成元素が混入することがある。また、n型化した領域に接するソース電極層112a及びドレイン電極層112bでは、一部酸素の濃度が高い領域が形成されうる。また、ソース電極層112a及びドレイン電極層112bにおいてn型化した領域に接する領域では、酸化物積層115の構成元素が混入することがある。

#### 【0063】

40

このように、酸化物積層115においてソース電極層112a及びドレイン電極層112bと接する領域に低抵抗領域を形成することにより、ソース電極層112a及びドレイン電極層112bと酸化物積層115との接触抵抗が低減され、トランジスタ200におけるソース-ドレイン間の寄生抵抗を低減できる。その結果、トランジスタのオン電流を増大させることができる。

#### 【0064】

なお、チャネル長が極短いトランジスタを形成する場合、上記酸素欠損の発生によってn型化した領域がトランジスタのチャネル長方向に延在してしまうことがある。n型化した領域のチャネル長方向への延在は、しきい値電圧のシフトや、ゲート電圧でオンオフの制御ができない状態（導通状態）等のトランジスタの電気特性の不良が現れる要因となりう

50

る。そのため、チャネル長が極短いトランジスタを形成する場合は、ソース電極層及びドレイン電極層には、酸素と結合しにくい導電材料を用いることが好ましい。当該導電材料としては、例えば、窒化タンタル、窒化チタンなどを用いることが好ましい。なお、酸素と結合しにくい導電材料には、酸素が拡散しにくい材料も含まれる。

#### 【0065】

##### ゲート絶縁層

ゲート絶縁層 114 としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜等を用いることができる。ゲート絶縁層 114 は酸素を含む膜であると、第 2 の酸化物層 110、第 2 の酸化物半導体層 108 及び / 又は第 1 の酸化物半導体層 106 へ酸素を供給しうるため好ましい。また、ゲート絶縁層 114 には、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート、ハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、酸化ランタンなどの材料を用いてもよい。さらに、ゲート絶縁層 114 は、単層構造としてもよいし、積層構造としてもよい。

#### 【0066】

##### ゲート電極層

ゲート電極層 116 の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウムから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タングステン膜）等を用いることができる。また、ゲート電極層 116 としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。又は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

#### 【0067】

また、ゲート電極層 116 は単層構造又は積層構造とすることができます。なお、ゲート絶縁層 114 と接するゲート電極層 116 の一層として、窒素を含む金属酸化物膜、具体的には、窒素を含む  $In-Ga-Zn-O$  膜や、窒素を含む  $In-Sn-O$  膜や、窒素を含む  $In-Ga-O$  膜や、窒素を含む  $In-Zn-O$  膜や、窒素を含む  $Sn-O$  膜や、窒素を含む  $In-O$  膜や、金属窒化膜 ( $InN$ ,  $SnN$  など) を用いることができる。これらの膜は 5 eV (電子ボルト) 以上、又は 5.5 eV (電子ボルト) 以上の仕事関数を有し、ゲート電極層として用いた場合、トランジスタのしきい値電圧をプラス側にシフトさせることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

#### 【0068】

##### <トランジスタに含まれる積層構造のバンド構造>

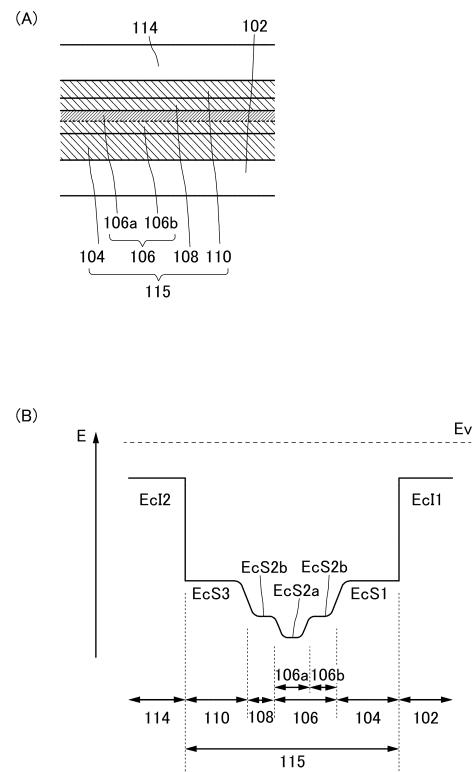

トランジスタ 200 に含まれる下地絶縁層 102、第 1 の酸化物層 104、第 1 の酸化物半導体層 106、第 2 の酸化物半導体層 108、第 2 の酸化物層 110、及びゲート絶縁層 114 の有するバンド構造について図 2 を用いて説明する。

#### 【0069】

図 2 (A) は酸化物積層 115 を含む積層構造の一部を模式図であり、図 2 (B) は、図 2 (A) で例示した積層構造のエネルギー・バンド構造の一部を模式的に示している。

#### 【0070】

図 2 (B) において、 $E_{cI1}$  は下地絶縁層 102 の伝導帯下端のエネルギーを模式的に示している。同様に、 $E_{cS1}$  は第 1 の酸化物層 104、 $E_{cS3}$  は第 2 の酸化物層 110、 $E_{cI2}$  はゲート絶縁層 114 の伝導帯下端のエネルギーを模式的に示している。また、 $E_{cS2b}$  は第 1 の酸化物半導体層 106 中の第 2 の領域 106b、及び第 2 の酸化物半導体層 108 における伝導帯下端のエネルギーであり、 $E_{cS2a}$  は第 1 の酸化物半

10

20

30

40

50

導体層 106 中の第 1 の領域 106a における伝導帯下端のエネルギーを示している。E<sub>cS2a</sub>はE<sub>cS2b</sub>よりも低いエネルギーとなる。なお、ここでは便宜上、図2(A)でのそれぞれの厚さは考慮されていない。

#### 【0071】

なお、図2(B)では第1の酸化物層104及び第2の酸化物層110が同様の伝導帯下端のエネルギーを有する酸化物層である場合について示したが、それぞれが異なるエネルギーギャップを有し、伝導帯下端のエネルギーが異なる酸化物層であってもよい。同様に、ここでは第1の酸化物半導体層106及び第2の酸化物半導体層108が同様の伝導帯下端のエネルギーを有する酸化物半導体層である場合について示したが、これらが異なるエネルギーギャップを有し、伝導帯下端のエネルギーが異なっていてもよい。

10

#### 【0072】

ここで、真空準位と伝導帯下端のエネルギーとの差(電子親和力ともいう)は、真空準位と価電子帯上端のエネルギーとの差(イオン化ポテンシャルともいう)からエネルギーギャップを引いた値となる。なお、エネルギーギャップは、分光エリプソメータ(例えばHORIBA JOBIN YVON社 UT-300)を用いて測定できる。また、真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析(UPS: Ultraviolet Photoelectron Spectroscopy)装置(例えばPHI社 VersaProbe)を用いて測定できる。

#### 【0073】

図2(B)に示すように、第1の酸化物層104と第1の酸化物半導体層106、及び第2の酸化物半導体層108と第2の酸化物層110において、伝導帯下端のエネルギーはこれらの間に障壁が無く連続的に変化する。これは、第1の酸化物層104と第1の酸化物半導体層106、及び第2の酸化物半導体層108と第2の酸化物層110のそれぞれの組成が近似することにより酸素が相互に拡散しやすく、これらの間に混合層とも呼ぶべき層が形成されているためと理解できる。また、第1の領域106aと第2の領域106bにおいて、伝導帯下端のエネルギーはこれらの間に障壁がなく連続的に変化する。これは第1の領域106aに含まれる酸化物半導体にn型の導電性を付与する元素の濃度が厚さ方向に連続的に変化しているためと理解できる。

20

#### 【0074】

また、第2の酸化物半導体層108を形成した後の熱処理などにより第1の領域106aに含まれる上記元素が第2の酸化物半導体層108中に拡散する場合がある。このような場合、第1の領域106aから第2の酸化物半導体層108の向きに上記元素の濃度が連続的に変化する。その結果、図2(B)に示すように、第1の領域106aと第2の酸化物半導体層108の間でも伝導帯下端のエネルギーに障壁がなく連続的に変化する。

30

#### 【0075】

図2(B)より、酸化物積層115中において、第1の酸化物半導体層106及び第2の酸化物半導体層108が第1のウェル(井戸)を構成し、さらに、該第1のウェル中ににおいて、第1の酸化物半導体層106に含まれる第1の領域106aが第2のウェルを構成する。すなわち、酸化物積層115中において埋め込みチャネル形成され、埋め込みチャネルの中にさらにウェルが形成されている。このように2段階のウェルを有することから、このような構成を二重井戸(Double Well)構造とも呼ぶことができる。第1の酸化物半導体層106中にウェルを有することにより、より大きな電流を流すことが可能となる。

40

#### 【0076】

さらに、第1の領域106aが構成するウェルが、第1の酸化物層104と下地絶縁層102との界面、及び第2の酸化物層110とゲート絶縁層114との界面と隔離されているため、これらの界面に生成されるトラップ準位の影響が、トランジスタのキャリアの主要な経路となる第1の領域106aに及ぶことを抑制することができる。

#### 【0077】

図2(B)に示す連続接合を形成するためには、ロードロック室を備えたマルチチャンバ

50

一方式の成膜装置（スパッタリング装置）を用いて各層を大気に触れさせることなく連続して積層することが好ましい。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa 乃至  $1 \times 10^{-4}$  Pa 程度まで）することができる。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

#### 【0078】

高純度真性酸化物半導体を得るために、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も行われる。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が -40 以下、好ましくは -80 以下、より好ましくは -100 以下にまで高純度化することで酸化物半導体に水分等が取り込まれることを可能な限り防ぐことができる。10

#### 【0079】

第1の酸化物半導体層 106 の下層に設けられる第1の酸化物層 104、及び第2の酸化物半導体層 108 の上層に設けられる第2の酸化物層 110 はバリア層として機能し、酸化物積層 115 に接する絶縁層（下地絶縁層 102 及びゲート絶縁層 114）と、酸化物積層 115 との界面に形成されるトラップ準位の影響が、トランジスタのキャリアの主な経路（キャリアパス）となる第1の酸化物半導体層 106 の第1の領域 106a へと及ぶことを抑制することができる。20

#### 【0080】

例えば、酸化物半導体層に含まれる酸素欠損は、酸化物半導体のエネルギーギャップ内の深いエネルギー位置に存在する局在準位として働く。このような局在準位にキャリアがトラップされることで、トランジスタの信頼性が低下するため、酸化物半導体層に含まれる酸素欠損を低減することが必要となる。本実施の形態のトランジスタ 200 では第1の酸化物半導体層 106 及び第2の酸化物半導体層 108 と比較して酸素欠損の生じにくい第1の酸化物層 104 及び第2の酸化物層 110 を第1の酸化物半導体層 106 又は第2の酸化物半導体層 108 に接して設けることで、第1の酸化物半導体層 106 及び第2の酸化物半導体層 108 における酸素欠損を低減することができる。例えば、第1の酸化物半導体層 106 は、一定光電流測定法（CPM：Constant Photocurrent Method）により測定された局在準位による吸収係数を  $1 \times 10^{-3} / \text{cm}$  未満、あるいは  $1 \times 10^{-4} / \text{cm}$  未満とすることができる。30

#### 【0081】

また、酸化物半導体層が、構成元素の異なる絶縁層（例えば、酸化シリコン膜を含む下地絶縁層）と接する場合、2層の界面に界面準位が形成され、該界面準位はチャネルを形成することがある。このような場合、しきい値電圧の異なる第2のトランジスタが出現し、トランジスタの見かけ上のしきい値電圧が変動することがある。しかしながら、本実施の形態のトランジスタ 200 においては第1の酸化物半導体層 106 を構成する金属元素を一種以上含んで第1の酸化物層 104 が構成されるため、第1の酸化物層 104 と第1の酸化物半導体層 106 の界面に界面準位を形成しにくくなる。よって第1の酸化物層 104 を設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。40

#### 【0082】

また、ゲート絶縁層 114 と第2の酸化物半導体層 108 との界面にチャネルが形成される場合、該界面で界面散乱が起こり、トランジスタの電界効果移動度が低くなる。しかしながら、本実施の形態のトランジスタ 200 においては、第2の酸化物半導体層 108 を構成する金属元素を一種以上含んで第2の酸化物層 110 が構成されるため、第2の酸化物半導体層 108 と第2の酸化物層 110 との界面ではキャリアの散乱が起こりにくく、トランジスタの電界効果移動度を高くすることができる。

#### 【0083】

また、第1の酸化物層 104 及び第2の酸化物層 110 は、下地絶縁層 102 及びゲート

10

20

30

40

50

絶縁層 114 の構成元素が、酸化物半導体層（第 1 の酸化物半導体層 106 又は第 2 の酸化物半導体層 108）へ混入して、不純物による準位が形成されることを抑制するためのバリア層としても機能する。

**【0084】**

例えば、第 1 の酸化物層 104 又は第 2 の酸化物層 110 に接する下地絶縁層 102、又はゲート絶縁層 114 として、シリコンを含む絶縁層を用いる場合、該絶縁層中のシリコン、又は絶縁層中に混入されうる炭素が、第 1 の酸化物層 104 又は第 2 の酸化物層 110 の中へ界面から数 nm 程度まで混入することがある。シリコン、炭素等の不純物が酸化物半導体層中に入ると不純物準位を形成し、不純物準位が電子の生成要因となることで n 型化することがある。

10

**【0085】**

しかしながら、第 1 の酸化物層 104 及び第 2 の酸化物層 110 の膜厚が、数 nm よりも厚ければ、混入したシリコン、炭素等の不純物が酸化物半導体層にまで到達しないため、不純物準位の影響は低減される。

**【0086】**

なお、酸化物半導体層中の不純物濃度は、例えば二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）で測定することができる。

**【0087】**

<半導体装置の作製方法>

20

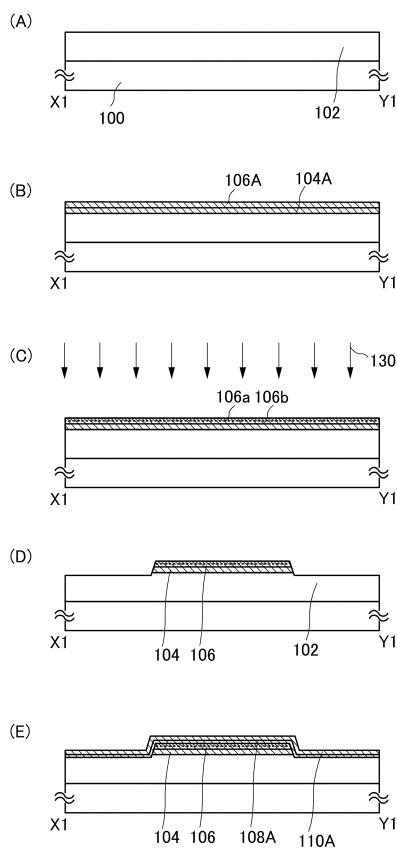

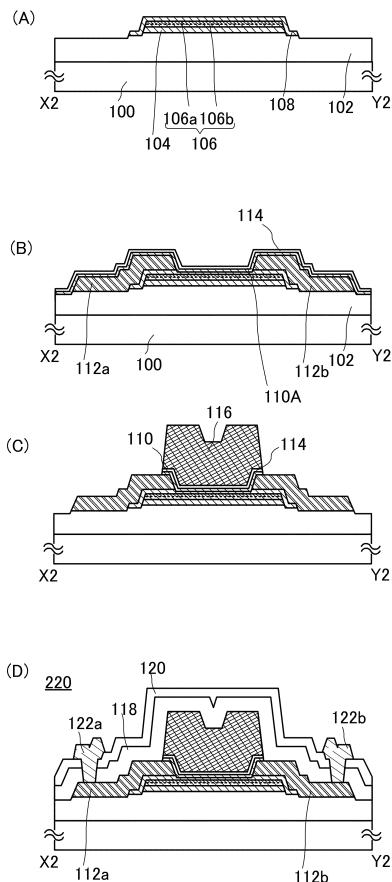

図 1 に示すトランジスタ 200 の作製方法の一例を図 3 及び図 4 を用いて説明する。

**【0088】**

まず、絶縁表面を有する基板 100 上に、下地絶縁層 102 を形成する（図 3（A）参照）。

**【0089】**

下地絶縁層 102 は、単層としても積層としてもよい。但し、少なくとも後に形成される第 1 の酸化物層 104 と接する領域は、該第 1 の酸化物層 104 を含む酸化物積層 115 への酸素の供給源となり得るよう、酸素を含む材料で形成する。また、過剰に酸素を含む層とすることが好ましい。

**【0090】**

30

下地絶縁層 102 に過剰に酸素を含有させるには、例えば、酸化雰囲気下にて下地絶縁層 102 を成膜すればよい。又は、成膜後の下地絶縁層 102 に酸素を導入して過剰に酸素を含有させてもよく、双方の手段を組み合わせてもよい。

**【0091】**

また、下地絶縁層 102 は、第 1 の酸化物層 104 と接する絶縁層であるため、膜中の水素濃度が低減されていることが好ましい。よって、下地絶縁層 102 を成膜後、水素の除去を目的とした熱処理（脱水化処理、又は脱水素化処理）を行うことが好ましい。

**【0092】**

熱処理の温度は、250 以上 650 以下、好ましくは 350 以上 600 以下、又は基板の歪み点以下とする。例えば、加熱処理装置の一つである電気炉に基板を導入し、下地絶縁層 102 に対して真空（減圧）雰囲気下 450 1 時間の熱処理を行う。

40

**【0093】**

なお、熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体から熱伝導又は熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、G R T A (Gas Rapid Thermal Anneal) 装置、L R T A (Lamp Rapid Thermal Anneal) 装置等の R T A (Rapid Thermal Anneal) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプが発する光（電磁波）の輻射により、被処理物を加熱する装置である。G R T A 装置は、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反

50

応しない不活性気体を高温に加熱して熱処理を行う装置である。なお、熱処理装置としてG R T A装置を用いる場合には、その処理時間が短いため、650乃至700に加熱した不活性ガス中で基板を加熱してもよい。

#### 【0094】

熱処理は、窒素、酸素、超乾燥空気（水の含有量が20 ppm以下、好ましくは1 ppm以下、好ましくは10 ppb以下の空気）、または希ガス（アルゴン、ヘリウムなど）の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥空気、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、加熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上（即ち不純物濃度を1 ppm以下、好ましくは0.1 ppm以下）とすることが好ましい。10

#### 【0095】

なお、熱処理によって下地絶縁層102から酸素が脱離することがある。そのため、脱水化又は脱水素化処理を行った下地絶縁層102に対して酸素（少なくとも、酸素ラジカル、オゾン、酸素原子、酸素イオン（分子イオン、クラスタイオンを含む）のいずれかを含む）を導入する処理を行うことが好ましい。

#### 【0096】

下地絶縁層102への酸素の導入は、例えばイオン注入法、イオンドーピング法、プラズマイオンイマージョンイオン注入法、プラズマ処理等を用いることができる。酸素の導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよい。下地絶縁層102への酸素の導入処理によって、熱処理によって脱離されうる酸素を補填することができる。20

#### 【0097】

次いで、下地絶縁層102上に、第1の酸化物層104となる第1の酸化物膜104Å、及び、第1の酸化物半導体層106となる第1の酸化物半導体膜106Åを順に成膜する（図3(B)参照）。第1の酸化物膜104Å及び第1の酸化物半導体膜106Åは、スパッタリング法、CVD(Chemical Vapor Deposition)法、MBE(Molecular Beam Epitaxy)法、ALD(Atomic Layer Deposition)法、またはPLD(Pulsed Laser Deposition)法等を用いて成膜する。30

#### 【0098】

第1の酸化物膜104Å及び第1の酸化物半導体膜106Åには、上述の材料を用いることができる。

#### 【0099】

例えば、第1の酸化物層104となる第1の酸化物膜104Åをスパッタリング法で成膜する場合には、原子数比がIn:Ga:Zn=1:3:2のスパッタリングターゲット、原子比がIn:Ga:Zn=1:6:4のスパッタリングターゲット、又は原子数比がIn:Ga:Zn=1:9:6のスパッタリングターゲット、又はその近傍の組成を有するスパッタリングターゲットを用いることが好ましい。40

#### 【0100】

また、例えば、第1の酸化物半導体層106となる第1の酸化物半導体膜106Åをスパッタリング法で成膜する場合には、原子数比がIn:Ga:Zn=1:1:1のスパッタリングターゲット、又は原子数比がIn:Ga:Zn=3:1:2のスパッタリングターゲット、又はその近傍の組成を有するスパッタリングターゲットを用いることが好ましい。

#### 【0101】

ただし、上述したように、第1の酸化物膜104Åは、第1の酸化物半導体膜106Åよりも電子親和力が小さくなるように材料を選択する。

#### 【0102】

10

20

30

40

50

なお、スパッタリング法によって成膜された膜の組成は、ターゲットの組成とは異なる場合がある。例えば、ZnOを含むスパッタリングターゲットを用いて酸化物半導体膜を成膜した場合、成膜中にZnOが昇華する等によって、成膜された酸化物半導体膜におけるIn及び/又はGaに対するZnの原子数比がスパッタリングターゲットと比較して低減することがある。

#### 【0103】

なお、第1の酸化物膜104Å及び第1の酸化物半導体膜106Åの成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。特に、成膜時に発生するゴミを低減でき、かつ膜厚分布も均一とすることからDCスパッタ法を用いることが好ましい。

10

#### 【0104】

なお、第1の酸化物膜104Å及び第1の酸化物半導体膜106Åを成膜する際、できる限り膜中に含まれる水素濃度を低減させることができることが好ましい。水素濃度を低減させるには、例えば、スパッタリング法を用いて成膜を行う場合には、スパッタリング装置の成膜室内に供給する雰囲気ガスとして、水素、水、水酸基を有する化合物、又は水素化物などの不純物が除去された高純度の希ガス（代表的にはアルゴン）、酸素、及び希ガスと酸素との混合ガスを適宜用いる。

#### 【0105】

また、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入して成膜を行うことで、成膜された膜中の水素濃度を低減させることができる。成膜室内的残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプは、例えば、水素分子、水（H<sub>2</sub>O）など水素原子を含む化合物（あるいは炭素原子を含む化合物）等の排気能力が高いため、クライオポンプを用いて排気した成膜室で成膜した酸化物膜及び酸化物半導体膜に含まれる不純物の濃度を低減できる。

20

#### 【0106】

なお、第1の酸化物膜104Åを成膜後、第1の酸化物半導体膜106Åの成膜前に、第1の酸化物膜104Åに対して酸素を導入してもよい。当該酸素導入処理により、第1の酸化物膜104Åが過剰に酸素を含有し、その後の成膜工程における熱処理によって該過剰な酸素を第1の酸化物半導体膜106Åへ供給することができる。

30

#### 【0107】

第1の酸化物膜104Å及び第1の酸化物半導体膜106Åを形成後、熱処理を行うことが好ましい。熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、又は減圧雰囲気で行えばよい。また、熱処理の雰囲気は、不活性ガス雰囲気で熱処理を行った後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。ここでの加熱処理によって、下地絶縁層102、第1の酸化物膜104Å、又は第1の酸化物半導体膜106Åの少なくとも一から水素や水などの不純物を低減又は除去することができる。

40

#### 【0108】

なお、当該熱処理は、第1の酸化物膜104Å及び第1の酸化物半導体膜106Åを島状に加工した後に行ってもよい。但し、下地絶縁層102に含まれる酸素が、島状の第1の酸化物層104及び第1の酸化物半導体層106から露出した領域から熱処理によって放出されるのを防止するために、島状に加工する前に熱処理を行うことが好ましい。

#### 【0109】

続いて、第1の酸化物半導体膜106Åに、元素130を導入して第1の領域106aを形成する（図3（C）参照）。

#### 【0110】

元素130としては、n型の導電性を付与する不純物を適用することができ、例えば、リ

50

ン( P )を用いることができる。またリン( P )のほか、15族元素( 例えば窒素( N )、砒素( As )、アンチモン( Sb ) )や、ホウ素( B )、アルミニウム( Al )、アルゴン( Ar )、ヘリウム( He )、ネオン( Ne )、インジウム( In )、フッ素( F )、塩素( Cl )、水素( H )、チタン( Ti )、及び亜鉛( Zn )を用いてもよい。

#### 【 0 1 1 1 】

また、導入する元素 130 は、ラジカル、原子、分子、又はイオンのいずれかの状態で含まれていれば良い。

#### 【 0 1 1 2 】

元素 130 を第 1 の酸化物半導体膜 106 Å に導入する方法としては、例えばイオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法などを用いることができる。

10 または、上記元素 130 を含む雰囲気下における熱処理やプラズマ処理を行ってもよい。

#### 【 0 1 1 3 】

元素 130 の導入において、第 1 の酸化物半導体膜 106 Å の第 1 の酸化物膜 104 Å との界面に元素 130 が達しないように導入の条件を設定することが好ましい。また、元素 130 の濃度の最も高い領域が、第 1 の酸化物半導体膜 106 Å の表面近傍( 例えば表面から 20 nm 以下、好ましくは 10 nm 以下、より好ましくは 5 nm 以下の範囲 ) に位置するように元素 130 を導入することが好ましい。または、元素 130 の濃度の最も高い領域が、第 1 の酸化物半導体膜 106 Å の表面から第 1 の酸化物半導体膜 106 Å の厚さの 3 / 4 以下、好ましくは 1 / 2 以下、より好ましくは 1 / 4 以下の範囲に位置するよう 20 に、元素 130 を導入することが好ましい。

#### 【 0 1 1 4 】

このような方法により元素 130 を導入することで、第 1 の酸化物半導体膜 106 Å 中に n 型領域である第 1 の領域 106a と、第 1 の領域 106a よりも元素 130 の濃度の低い第 2 の領域 106b を形成することができる。ここで、第 2 の領域 106b は好ましくは i 型または実質的に i 型であることが好ましい。

#### 【 0 1 1 5 】

次いで、第 1 の酸化物膜 104 Å 及び第 1 の酸化物半導体膜 106 Å を加工して島状の第 1 の酸化物層 104 及び第 1 の酸化物半導体層 106 を形成する( 図 3 ( D ) 参照 )。ここでは、第 1 の酸化物層 104 及び第 1 の酸化物半導体層 106 は同一のマスクを用いたエッチングによって加工することができる。よって、第 1 の酸化物層 104 と第 1 の酸化物半導体層 106 の平面形状は同一であり、第 1 の酸化物層 104 の側面の上端と第 1 の酸化物半導体層 106 の側面の下端は一致している。換言すると、第 1 の酸化物層 104 の側面と第 1 の酸化物半導体層 106 の側面は同一平面である。

30

#### 【 0 1 1 6 】

なお、本明細書や請求項において「同一」又は「一致」の表現は、厳密に同一、又は一致であることを要しない趣旨で用いるものであり、略同一又は略一致を範疇に含む。例えば、同一のマスクを用いたエッチングによって得られた形状における一致の程度を包含する。

#### 【 0 1 1 7 】

なお、第 1 の酸化物層 104 及び第 1 の酸化物半導体層 106 への加工の際に、第 1 の酸化物膜 104 Å のオーバーエッチングによって下地絶縁層 102 の一部( 島状の第 1 の酸化物層 104 及び第 1 の酸化物半導体層 106 から露出した領域 ) がエッチングされ膜厚が減少することがある。

40

#### 【 0 1 1 8 】

次いで、第 1 の酸化物半導体層 106 の上面及び側面を覆うように、第 2 の酸化物半導体膜 108 Å 、及び第 2 の酸化物膜 110 Å を順に積層する( 図 3 ( E ) 参照 )。

#### 【 0 1 1 9 】

第 2 の酸化物半導体層 108 となる第 2 の酸化物半導体膜 108 Å 、及び第 2 の酸化物層 110 となる第 2 の酸化物膜 110 Å は、上述の材料を用いて形成することができる。ま

50

た、形成方法は、第1の酸化物膜104Å又は第1の酸化物半導体膜106Åと同様とすることができる。

#### 【0120】

例えば、第2の酸化物半導体膜108Åをスパッタリング法で成膜する場合には、第1の酸化物半導体膜106Åと同じスパッタリングターゲットを用いることが好ましい。この場合、原子数比がIn:Ga:Zn=1:3:2のスパッタリングターゲット、原子比がIn:Ga:Zn=1:6:4のスパッタリングターゲット、又は原子数比がIn:Ga:Zn=1:9:6のスパッタリングターゲット、又はその近傍の組成を有するスパッタリングターゲットを用いることが好ましい。

#### 【0121】

第2の酸化物半導体膜108Å及び第2の酸化物膜110Åの形成後、加熱処理を行うことが好ましい。加熱処理は、250以上650以下、好ましくは300以上500

以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、または減圧状態で行えばよい。また、加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。加熱処理によって下地絶縁層102、第1の酸化物層104、第1の酸化物半導体層106、第2の酸化物半導体膜108Å又は第2の酸化物膜110Åから水素や水などの不純物を除去することができる。また、当該加熱処理により、下地絶縁層102上に設けられた酸化物積層115に対して下地絶縁層102から酸素を供給することができる。

#### 【0122】

なお、上記熱処理は、少なくとも第1の酸化物半導体膜106Åを形成した後であればどの段階で行ってもよく、また複数回繰り返し行ってもよい。例えば、第1の酸化物半導体層106の形成直後、第2の酸化物層110の形成直後、またはそれ以降の段階で行ってもよい。

#### 【0123】

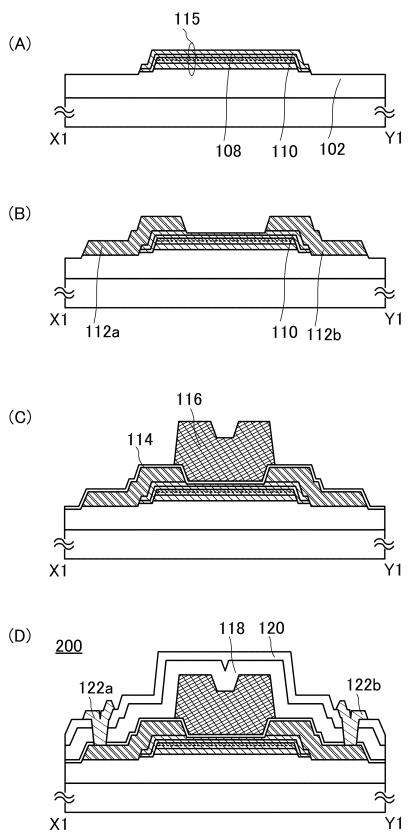

続いて、フォトリソグラフィ法等を用いて第2の酸化物半導体膜108Å及び第2の酸化物膜110Åを加工して、第2の酸化物半導体層108及び第2の酸化物層110を形成する(図4(A)参照)。ここでは、第2の酸化物半導体層108及び第2の酸化物層110は同一のマスクを用いたエッチングによって加工することができる。よって、第2の酸化物半導体層108と第2の酸化物層110の平面形状は同一であり、第2の酸化物半導体層108の側面の上端と第2の酸化物層110の側面の下端とは一致している。

#### 【0124】

ここでの加工処理によって、第1の酸化物層104、第1の酸化物半導体層106、第2の酸化物半導体層108及び第2の酸化物層110を含む酸化物積層115が形成される。

#### 【0125】

なお、第2の酸化物半導体層108及び第2の酸化物層110への加工の際に、第2の酸化物半導体膜108Åのオーバーエッチングによって下地絶縁層102の一部(島状の第2の酸化物半導体層108及び第2の酸化物層110から露出した領域)がエッチングされ膜厚が減少することがある。

#### 【0126】

次に、第2の酸化物層110上に導電膜を形成し、該導電膜を加工してソース電極層112a及びドレイン電極層112bを形成する(図4(B)参照)。

#### 【0127】

なお、ソース電極層112a及びドレイン電極層112bは、アッティングによってレジストマスクを後退させる工程とエッチングの工程を交互に複数回行うことで、端部に階段状の複数の段を設けた形状としてもよい。ソース電極層112a及びドレイン電極層112bの膜厚が厚いほど、当該段数を増やすことが好ましい。なお、ソース電極層112a及びドレイン電極層112bの端部対称的でなくともよい。また、各階段形状の上面と断面との間に任意の曲率半径を有する曲面が形成されていてもよい。

10

20

30

40

50

**【0128】**

ソース電極層112a及びドレイン電極層112bを上記のような複数の段を設けた形状とすることで、それらの上方に形成される膜、具体的には、ゲート絶縁層114などの被覆性が向上し、トランジスタの電気特性や信頼性を向上させることができる。

**【0129】**

なお、ソース電極層112a及びドレイン電極層112bの加工の際に、導電膜のオーバーエッチングによって、下地絶縁層102の一部及び第2の酸化物層110の一部（ソース電極層112a及びドレイン電極層112bから露出した領域）がエッチングされ膜厚が減少することがある。

**【0130】**

なお、ソース電極層112a及びドレイン電極層112bとなる導電膜が残渣物として酸化物積層115上に残存すると、該残渣物が酸化物積層115中又は界面において不純物準位を形成することがある。または、該残渣物によって、酸化物積層115から酸素が引き抜かれてしまい、酸素欠損が形成されることがある。

**【0131】**

よって、ソース電極層112a及びドレイン電極層112bを形成後、第2の酸化物層110表面に該残渣物除去処理を施してもよい。残渣物除去処理は、エッチング（例えば、ウェットエッチング）による処理、もしくは、酸素又は一酸化二窒素を用いたプラズマ処理によって行うことができる。当該残渣物除去処理によって、ソース電極層112a及びドレイン電極層112b間に露出した第2の酸化物層110の膜厚が1nm以上3nm以下程度減少することがある。

**【0132】**

次いで、酸化物積層115、ソース電極層112a及びドレイン電極層112b上にゲート絶縁層114を形成する。

**【0133】**

ゲート絶縁層114の材料としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどを用いることができる。なお、ゲート絶縁層114は、上記材料の積層膜を用いてもよい。ゲート絶縁層114は、スパッタリング法、CVD法、MBE法、ALD法またはPLD法などを用いて形成することができる。

**【0134】**

ゲート絶縁層114は、上記下地絶縁層102と同様、酸化物積層115に酸素を供給する役割を有していてもよく、その場合、酸素を含む絶縁層を用いることが好ましい。

**【0135】**

ゲート絶縁層114の形成後、加熱処理を行ってもよい。加熱処理は上記と同様の条件で行うことができる。

**【0136】**

次いで、ゲート絶縁層114上に導電膜を形成し、不要な部分をエッチングすることにより、ゲート電極層116を形成する（図4（C）参照）。

**【0137】**

ゲート電極層116の形成後、加熱処理を行ってもよい。加熱処理は上記と同様の条件で行うことができる。

**【0138】**

次いで、ゲート絶縁層114及びゲート電極層116上に絶縁層118及び絶縁層120を順に積層する。

**【0139】**

絶縁層118及び絶縁層120の材料としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、

10

20

30

40

50

酸化ハフニウムおよび酸化タンタルなどを用いることができる。なお絶縁層 118 及び絶縁層 120 は、上記材料の積層膜を用いてもよい。絶縁層 118 及び絶縁層 120 は、スパッタリング法、CVD 法、MBE 法、ALD 法または PLD 法などを用いて形成することができる。

#### 【0140】

ここで、絶縁層 118 として、酸素に対する透過性の低い（酸素に対するバリア性を有する）層を用いることが好ましい。酸素に対する透過性の低い層の材料としては、酸化アルミニウムや、窒化シリコン、窒化酸化シリコンなどの窒化物が挙げられる。ゲート絶縁層 114 を覆って酸素に対する透過性の低い絶縁層 118 を設けることにより、その後の加熱処理によって下地絶縁層 102 等から放出される酸素が、絶縁層 118 を介して外部に放出されることを抑制し、当該酸素を効率的に酸化物積層 115 に供給することができる。

10

#### 【0141】

または、絶縁層 118 として酸化物積層 115 への酸素の供給源となり得る酸素を含む（過剰の酸素を含む）層とし、絶縁層 120 として酸素に対する透過性の低い層としてもよい。このとき、加熱処理によって絶縁層 118 から放出される酸素が絶縁層 120 を介して外部に放出されることが抑制され、より効率的に当該酸素を酸化物積層 115 に供給することができる。

#### 【0142】

絶縁層 118 の形成後、又は、絶縁層 118 及び絶縁層 120 の形成後、加熱処理を行つてもよい。加熱処理は上記と同様の条件で行うことができる。加熱処理により、酸化物積層 115 を囲む酸素を含む層から、酸化物積層 115 中に効果的に酸素が供給され、第 1 の酸化物半導体層 106 及び第 2 の酸化物半導体層 108 中の酸素欠損を低減できる。

20

#### 【0143】

続いて、絶縁層 120 及び絶縁層 118 を選択的にエッチングし、ソース電極層 112a に達する開口部、及びドレイン電極層 112b に達する開口部を形成する。

#### 【0144】

そして、絶縁層 120 上に導電膜を形成し、不要な部分をエッチングにより除去することにより、ソース電極層 112a と電気的に接続する電極層 122a、及びドレイン電極層 112b と電気的に接続する電極層 122b を形成する（図 4 (D) 参照）。

30

#### 【0145】

電極層 122a 及び電極層 122b の材料としては、ソース電極層 112a、ドレイン電極層 112b 又はゲート電極層 116 に用いる材料を適用できる。

#### 【0146】

以上の工程により、トランジスタ 200 を作製することができる。

#### 【0147】

##### <半導体装置の構成例 2>

図 5 にトランジスタ 210 の構成例を示す。図 5 に示すトランジスタ 210 は、酸化物積層 115 において、第 2 の酸化物半導体層 108 が、第 1 の酸化物半導体層 106 から露出した第 1 の酸化物層 104 の上面と、第 1 の酸化物半導体層 106 の側面及び上面とに接するように設けられており、これによって第 2 の酸化物半導体層 108 の端部が第 2 の酸化物層 110 によって覆われた構成を有する。換言すると、第 2 の酸化物半導体層 108 の側面は第 2 の酸化物層 110 と接している。なお、トランジスタ 210 のそのほかの構成は、トランジスタ 200 と同様であるため、詳細な説明は省略する。

40

#### 【0148】

トランジスタ 210 に含まれる酸化物積層 115 の作製方法を以下に説明する。まず、図 3 (A) 乃至図 3 (C) の工程と同様に、基板 100 上に、下地絶縁層 102 と、第 1 の酸化物膜 104A と、第 1 の領域 106a 及び第 2 の領域 106b を含む第 1 の酸化物半導体膜 106A と、を形成する。

#### 【0149】

10

20

30

40

50

次いで、フォトリソグラフィ法等によって、第1の酸化物半導体膜106Åを加工して、第1の酸化物膜104Å上に島状の第1の酸化物半導体層106を形成する。このとき、第1の酸化物半導体膜106Åのエッティングには、第1の酸化物膜104Åとエッティング選択比が十分に大きい条件を用いることが好ましい。なお、第1の酸化物膜104Åと第1の酸化物半導体膜106Åとの組成が近い場合や、エッティングの選択比が十分に大きくとれない場合等では、第1の酸化物膜104Åがエッティングされ、一部が薄膜化する場合がある。

#### 【0150】

次いで、島状の第1の酸化物半導体層106を覆って第1の酸化物膜104Å上に、第2の酸化物半導体膜108Åを形成する。フォトリソグラフィ法等によって、第1の酸化物膜104Å及び第2の酸化物半導体膜108Åを加工することで、第1の酸化物層104及び第2の酸化物半導体層108を形成する。ここでは、第1の酸化物層104及び第2の酸化物半導体層108は同一のマスクを用いたエッティングによって加工することができる。よって、第1の酸化物層104と第2の酸化物半導体層108の平面形状は同一であり、第1の酸化物層104の側面の上端と第2の酸化物半導体層108の側面の下端とは一致している。

#### 【0151】

なお、第1の酸化物層104及び第2の酸化物半導体層108への加工の際に、第1の酸化物膜104Åのオーバーエッティングによって下地絶縁層102の一部（島状の第1の酸化物層104及び第2の酸化物半導体層108から露出した領域）がエッティングされ膜厚が減少することがある。

#### 【0152】

その後、第1の酸化物層104の側面と、第2の酸化物半導体層108の側面及び上面とを覆って第2の酸化物膜110Åを形成し、フォトリソグラフィ法等で加工して第2の酸化物層110を形成する。以上によって、トランジスタ210に含まれる酸化物積層115を形成することができる。

#### 【0153】

上述した作製方法によって得られた酸化物積層115は、第1の酸化物層104及び第2の酸化物半導体層108によって、第1の酸化物半導体層106を内包した構成を有する。換言すると、第2の酸化物半導体層108の端部において、第2の酸化物半導体層108は、下地絶縁層102に代えて第1の酸化物層104と接する。よって、第1の酸化物半導体層106へのシリコン等の不純物の混入をさらに抑制することができる。また、第2の酸化物半導体層108の側面を第2の酸化物層110によって覆う構成とすることで、該側面からの酸素の脱離を抑制することができる。

#### 【0154】

##### <半導体装置の構成例3>

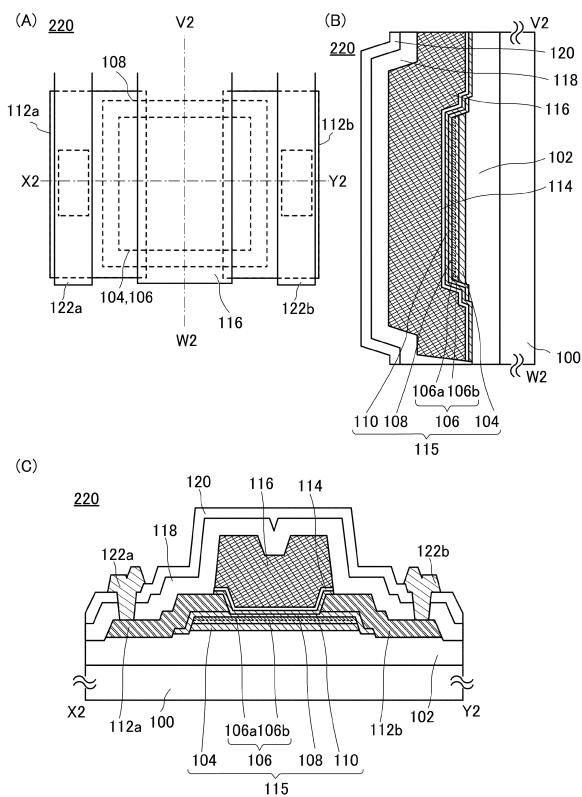

図6にトランジスタ220の構成例を示す。図6(A)は、トランジスタ220の平面図であり、図6(B)は、図6(A)のV2-W2における断面図であり、図6(C)は、図6(A)のX2-Y2における断面図である。

#### 【0155】

図6に示すトランジスタ220は、酸化物積層115において、第2の酸化物層110が、ソース電極層112a及びドレイン電極層112bから露出した第2の酸化物半導体層108に接して、ソース電極層112a及びドレイン電極層112b上に設けられた構成を有する。また、トランジスタ220において、第2の酸化物層110とゲート絶縁層114とは、ゲート電極層116をマスクとして自己整合的にエッティング加工されている。換言すると、トランジスタ220において、第2の酸化物層110とゲート絶縁層114とゲート電極層116とは、同一の平面形状を有する。なお、トランジスタ220のそのほかの構成は、上述のトランジスタ200と同様であるため、詳細な説明は省略する。

#### 【0156】

トランジスタ220に含まれる酸化物積層115の作製方法について図7を参照して説明

10

20

30

40

50

する。まず、図3(A)乃至図3(D)の工程と同様に、基板100上に、下地絶縁層102と、第1の酸化物層104と、第1の領域106a及び第2の領域106bを含む第1の酸化物半導体層106と、を形成する。

#### 【0157】

次いで、島状の第1の酸化物層104及び第1の酸化物半導体層106を覆って、第2の酸化物半導体膜を形成する。フォトリソグラフィ法等によって、第2の酸化物半導体膜を加工することで、第1の酸化物層104の側面と、第1の酸化物半導体層106の側面及び上面を覆い、下地絶縁層102の一部と接する第2の酸化物半導体層108を形成する(図7(A)参照)。

#### 【0158】

なお、第2の酸化物半導体層108への加工の際に、第2の酸化物半導体膜108Aのオーバーエッチングによって下地絶縁層102の一部(島状の第2の酸化物半導体層108から露出した領域)がエッチングされ膜厚が減少することがある。

#### 【0159】

その後、図4(B)の工程と同様の工程によって、第2の酸化物半導体層108上に導電膜を形成し、これを加工してソース電極層112a及びドレイン電極層112bを形成する。なお、導電膜の加工の際に下地絶縁層102及び/又は第2の酸化物半導体層108の一部(ソース電極層112a及びドレイン電極層112bから露出した領域)がエッチングされ、膜厚が減少ことがある。

#### 【0160】

次いで、ソース電極層112a及びドレイン電極層112bの間に露出した第2の酸化物半導体層108に接するようにソース電極層112a及びドレイン電極層112b上に第2の酸化物膜110Aを形成し、第2の酸化物膜110A上にゲート絶縁層114を形成する(図7(B)参照)。

#### 【0161】

なお、第2の酸化物膜110Aとゲート絶縁層114とを大気に開放せずに連続的に形成すると、第2の酸化物膜110A表面に水素や水分などの不純物が吸着することを防止することができるため、好ましい。

#### 【0162】

なお、ゲート絶縁層114の成膜時に、第2の酸化物膜110Aがパターン形成されて下地絶縁層102の一部が露出していると、ゲート絶縁層114の成膜時の加熱によって下地絶縁層102から脱離した酸素が外部(例えば、成膜雰囲気中)に放出されてしまうことがある。下地絶縁層102は、酸化物積層115への酸素の供給源となる層であるため、下地絶縁層102からの酸素の外部への放出は、第1の酸化物半導体層106へ供給されうる酸素の減少につながり、結果として酸化物積層115の酸素欠損発生の要因となる。しかしながら、図7に示すトランジスタ220の作製方法においては、ゲート絶縁層114の成膜時に、下地絶縁層102が第2の酸化物膜110Aによって覆われた構成を有しているため、トランジスタの作製工程中における下地絶縁層102からの酸素の脱離を抑制することが可能である。よって、トランジスタ220に含まれる酸化物積層115に生じうる酸素欠損を低減することができる。

#### 【0163】

次いで、図4(C)に示した工程と同様に、ゲート絶縁層114上にゲート電極層116を形成し、該ゲート電極層116をマスクとして自己整合的にゲート絶縁層114及び第2の酸化物膜110Aの加工を行う(図7(C)参照)。

#### 【0164】

第2の酸化物膜110Aを第2の酸化物層110へと加工することで、第2の酸化物層110に含有されるインジウムの外方拡散を抑制することができる。インジウムの外方拡散は、トランジスタの電気的特性の変動を引き起こす要因や、工程中の成膜室内の汚染要因となるため、ゲート電極層116をマスクとした第2の酸化物層110への加工は効果的である。また、後の工程でソース電極層112a及びドレイン電極層112bと、電極層

10

20

30

40

50

122a及び電極層122bとの電気的接続のためのコンタクトホールを開口する際に、該コンタクトホール形成領域に第2の酸化物膜110Aが残存していると、後に形成される絶縁層118又は絶縁層120と、第2の酸化物膜110Aとのエッティングレートの違いから、エッティング残渣物が発生しやすい。よって、第2の酸化物層110へと加工することで、該残渣物の発生を抑制することができる。

#### 【0165】

なお、第2の酸化物層110及びゲート絶縁層114の加工は、ゲート電極層116を形成する前に行うことも可能である。その場合、第1の酸化物層104及び第1の酸化物半導体層106の加工に用いたフォトマスク、又は第2の酸化物半導体層108の加工に用いたフォトマスクを転用すると、マスク枚数を削減することができるため好ましい。但し、第2の酸化物層110上に接してレジストマスクを形成すると、該レジストマスクを剥離する際の薬液処理等によって第2の酸化物層110の表面がダメージ（不純物による汚染、膜厚の減少、又は酸素欠損等）を受けることがあるため、第2の酸化物層110への加工は、ゲート絶縁層114上にレジストマスクを形成して行うことが好ましい。

10

#### 【0166】

その後、図4(D)の工程と同様に、絶縁層118及び絶縁層120を形成し、絶縁層118及び絶縁層120に設けられたコンタクトホールを介してソース電極層112a及びドレイン電極層112bと電気的に接続する電極層122a及び電極層122bを形成する（図7(D)参照）。

#### 【0167】

20

以上によって、トランジスタ220を形成することができる。

#### 【0168】

##### <半導体装置の構成例4>

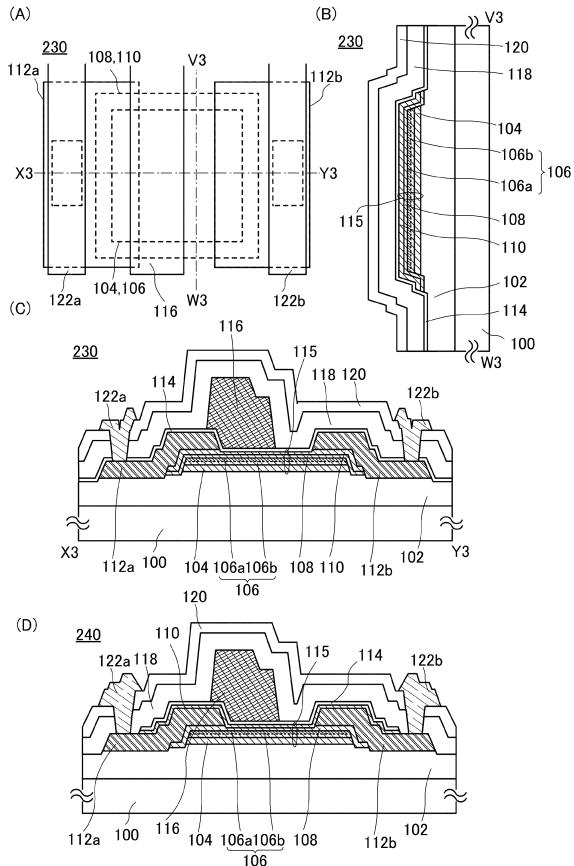

図8にトランジスタ230及びトランジスタ240の構成例を示す。

#### 【0169】

図8(A)は、トランジスタ230の平面図であり、図8(B)は、図8(A)のV3-W3における断面図であり、図8(C)は、図8(A)のX3-Y3における断面図である。

#### 【0170】

30

トランジスタ230は、ゲート電極層116の形状が異なる点でトランジスタ200と相違しており、そのほかの部分は共通である。なお、トランジスタ230のそのほかの構成は、上述のトランジスタ200と同様であるため、詳細な説明は省略する。

#### 【0171】

トランジスタ230のゲート電極層116は、ソース電極層112aと重畠し、且つドレイン電極層112bと重畠しないように設けられている。ドレイン電極層112bとゲート電極層116とが重ならないように離間して設けることにより、ゲート-ドレイン間の耐圧を向上させることができる。したがって極めて高い電圧でトランジスタ230を駆動した場合でも高い信頼性を確保することができる。

#### 【0172】

40

また、図8(D)に、トランジスタ240の断面図を示す。図8(D)に示すトランジスタは、トランジスタ230と同様に、ソース電極層112aと重畠し、且つドレイン電極層112bと重畠しないように設けられたゲート電極層116を有する。

#### 【0173】

また、図6のトランジスタ220と同様に、酸化物積層115において、第2の酸化物層110が、ソース電極層112a及びドレイン電極層112bから露出した第2の酸化物半導体層108に接して、ソース電極層112a及びドレイン電極層112b上に設けられた構成を有する。但し、トランジスタ240においては、ゲート電極層116とドレイン電極層112bが重ならない構造であるため、トランジスタ220の作製工程において示したように、ゲート電極層116をマスクとした第2の酸化物膜の加工を行うことが困難である。

50

## 【0174】

よって、第2の酸化物層110への加工は、フォトリソグラフィ法等によってマスクを形成して行うことが好ましい。なお、該マスクはゲート絶縁層114上に形成することが好ましい。また、第1の酸化物層104及び第1の酸化物半導体層106の加工に用いたフォトマスク、又は第2の酸化物半導体層108の加工に用いたフォトマスクを転用すると、マスク枚数を削減することができるため好ましい。

## 【0175】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【0176】

10

## (実施の形態2)

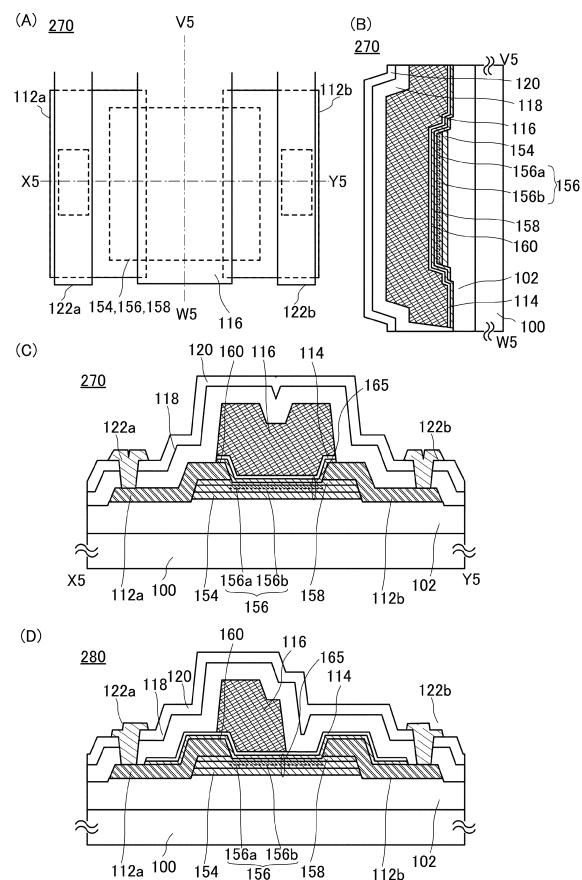

本実施の形態では、実施の形態1と異なる半導体装置及び半導体装置の作製方法の一形態を図9乃至図12を参照して説明する。なお、以下に示す本実施の形態の構成において、実施の形態1と同一部分又は同様の機能を有する部分については、実施の形態1を参照することができるため記載を省略して説明することができる。本実施の形態では、半導体装置の一例として、酸化物半導体層を含むトップゲート型のトランジスタを示す。

## 【0177】

## &lt;半導体装置の構成例5&gt;

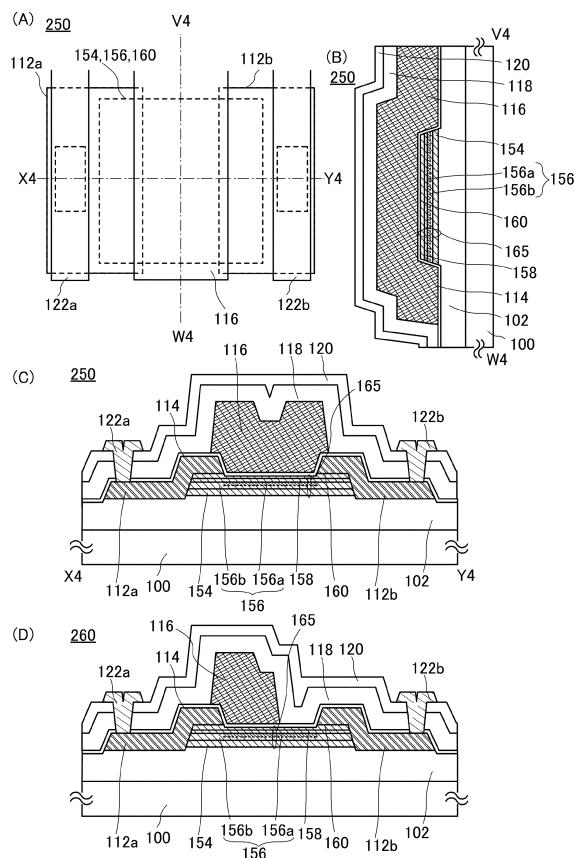

図9(A)乃至(C)にトランジスタ250の構成例を示す。図9(A)は、トランジスタ250の平面図であり、図9(B)は、図9(A)のV4-W4における断面図であり、図9(C)は、図9(A)のX4-Y4における断面図である。

20

## 【0178】

図9に示すトランジスタ250に含まれる酸化物積層165は、第1の酸化物層154と、第1の酸化物半導体層156と、第2の酸化物半導体層158と、第2の酸化物層160と、を含んで構成される。また、第1の酸化物半導体層156は、n型の導電性を付与する不純物を含む第1の領域156aと、i型または実質的にi型の第2の領域156bとを含んで構成される。なお、図9に示すトランジスタ250において、酸化物積層165以外の構成は、図1に示すトランジスタ200と同様である。

## 【0179】

30

酸化物積層165に含まれる第1の酸化物半導体層156及び第2の酸化物半導体層158は、少なくともインジウム(In)もしくは亜鉛(Zn)を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、酸化物半導体層を用いたトランジスタの電気特性のばらつきを減らすため、インジウム及び亜鉛と共に、スタビライザーを含むことが好ましい。詳細には、第1の酸化物半導体層106又は第2の酸化物半導体層108とそれぞれ同様の材料を適用することができる。

## 【0180】

酸化物積層165に含まれる第1の酸化物層154は、先に示した第1の酸化物層104と同様の構成とすることができる。また、酸化物積層165に含まれる第2の酸化物層160は、先に示した第2の酸化物層110と同様の構成とすることができる。

40

## 【0181】

第1の酸化物半導体層156に含まれる第1の領域156aは、ソース電極層112a及びドレイン電極層112bをマスクとして、n型の導電性を付与する不純物を導入することによって形成される。よって、平面図において、第1の領域156aのチャネル長方向の端部の一方は、ソース電極層112aのチャネル側の端部と一致し、第1の領域156aのチャネル長方向の端部の他方は、ドレイン電極層112bのチャネル側の端部と一致する。また、図9(B)に示すように、チャネル幅方向においては、第1の領域156aは第1の酸化物半導体層156の端部にまで延在し、ゲート絶縁層114と接する。

## 【0182】

また、第1の酸化物半導体層156は、ソース電極層112a及びドレイン電極層112bと重なる領域、及び、第1の酸化物層154との界面近傍領域に、i型又は実質的にi

50

型の第2の領域156bを含む。

**【0183】**

第2の酸化物半導体層158は、第1の酸化物半導体層156の第1の領域156aと接し、第1の酸化物半導体層156の上面を覆うように設けられる。第2の酸化物半導体層158は、i型又は実質的にi型の酸化物半導体を含むことが好ましい。

**【0184】**

トランジスタ250が、ソース電極層112a及びドレイン電極層112bと第1の領域156aとの間に、i型又は実質的にi型である第2の領域156bと、i型又は実質的にi型である第2の酸化物半導体層158とを含むことで、オン動作、オフ動作が確実なトランジスタとすることができる。さらにはノーマリーオフ型のトランジスタ250を実現することができる。10

**【0185】**

また、トランジスタ250は、チャネルを形成する第1の酸化物半導体層156のゲート電極層116と重なる領域にn型の導電性を付与する不純物を含む第1の領域156aを設けることにより、トランジスタ250のオン状態におけるソース-ドレイン間の直列抵抗を低減することができる。その結果、オン状態におけるソース-ドレイン間に流れる電流（オン電流ともいう）を高めることができる。

**【0186】**

また、トランジスタ250に含まれる酸化物積層165は、1枚のマスクを用いた一度のエッチング工程によって形成することが可能であるため、半導体装置作製の工程の短縮及びコストの削減を図ることができる。20

**【0187】**

図9(D)に示すトランジスタ260は、トランジスタ250の変形例であり、ゲート電極層116の形状が異なる点でトランジスタ250と相違しており、そのほかの部分は共通である。

**【0188】**

トランジスタ260のゲート電極層116は、実施の形態1のトランジスタ230及びトランジスタ240と同様に、ソース電極層112aと重畠し、且つドレイン電極層112bと重畠しないように設けられている。ドレイン電極層112bとゲート電極層116とが重ならないように離間して設けることにより、ゲート-ドレイン間の耐圧を向上させることができ。したがって極めて高い電圧でトランジスタ260を駆動した場合でも高い信頼性を確保することができる。30

**【0189】**

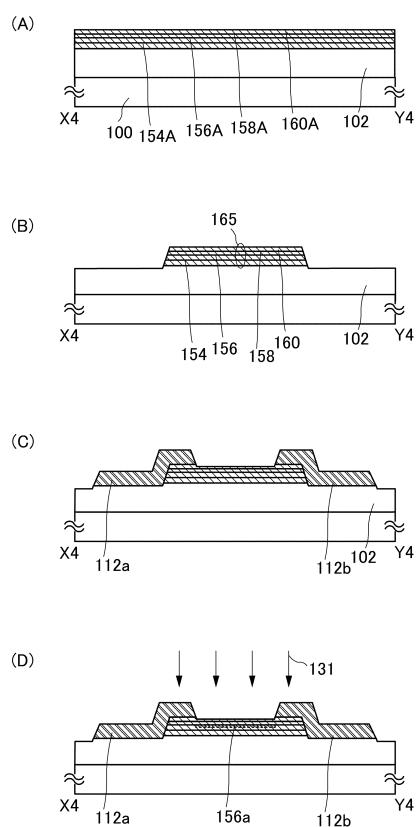

以下に、トランジスタ250の作製方法の一例について、図10を参照して説明する。

**【0190】**

まず、基板100上に下地絶縁層102を形成し、下地絶縁層102上に第1の酸化物膜154A、第1の酸化物半導体膜156A、第2の酸化物半導体膜158A及び第2の酸化物膜160Aを積層する（図10(A)参照）。なお、第1の酸化物半導体膜156Aと第2の酸化物半導体膜158Aとの積層構造に代えて単層の酸化物半導体膜としてもよい。40

**【0191】**

第1の酸化物膜154A、第1の酸化物半導体膜156A、第2の酸化物半導体膜158A及び第2の酸化物膜160Aの形成は、それぞれ実施の形態1の第1の酸化物膜104A、第1の酸化物半導体膜106A、第2の酸化物半導体膜108A及び第2の酸化物膜110Aの形成工程を参照することができる。

**【0192】**

次いで、フォトリソグラフィ法等を用いて第1の酸化物膜154A、第1の酸化物半導体膜156A、第2の酸化物半導体膜158A及び第2の酸化物膜160Aを加工して、第1の酸化物層154、第1の酸化物半導体層156、第2の酸化物半導体層158及び第2の酸化物層160を形成する（図10(B)参照）。ここでは、第1の酸化物膜15450

A、第1の酸化物半導体膜156Å、第2の酸化物半導体膜158Å及び第2の酸化物膜160Åは同一のマスクを用いたエッティングによって加工することができる。よって、第1の酸化物層154、第1の酸化物半導体層156、第2の酸化物半導体層158及び第2の酸化物層160の平面形状は同一であり、第1の酸化物層154の側面の上端と第1の酸化物半導体層156の側面の下端とは一致し、第1の酸化物半導体層156の側面の上端と第2の酸化物半導体層158の側面の下端とは一致し、第2の酸化物半導体層158の側面の上端と第2の酸化物層160の側面の下端とは一致している。

#### 【0193】

ここでの加工処理によって、第1の酸化物層154、第1の酸化物半導体層156、第2の酸化物半導体層158及び第2の酸化物層160を含む酸化物積層165が形成される。

10

。

#### 【0194】

なお、酸化物積層165への加工の際に、第1の酸化物膜154Åのオーバーエッティングによって下地絶縁層102の一部（島状の酸化物積層165から露出した領域）がエッティングされ膜厚が減少することがある。

#### 【0195】

次に、図4(B)の工程と同様に、第2の酸化物層160上に導電膜を形成し、該導電膜を加工してソース電極層112a及びドレイン電極層112bを形成する（図10(C)参照）。なお、ソース電極層112a及びドレイン電極層112bへの加工の際に、導電膜のオーバーエッティングによって下地絶縁層102の一部がエッティングされ膜厚が減少することがある。

20

#### 【0196】

続いて、ソース電極層112a及びドレイン電極層112bをマスクとして、第2の酸化物層160を介して第1の酸化物半導体層156に、元素131を導入し、該元素131を含有する第1の領域156aを形成する（図10(D)参照）。ここで、元素131は、第1の酸化物半導体層156の一部であって、ソース電極層112a及びドレイン電極層112bと重ならない領域に含まれる。

#### 【0197】

元素131としては、酸素と親和性のある元素を好ましく用いることができる。第1の酸化物半導体層156中に酸素と親和性のある元素を導入することで、第1の酸化物半導体層156を構成する酸素を該元素が引き抜き、酸素欠損を生じさせるため、該元素が導入された第1の領域156aはn型の領域となる。

30

#### 【0198】

酸素と親和性のある元素としては、例えば、タンゲステン(W)、チタン(Ti)、ホウ素(B)、アルミニウム(Al)、又は亜鉛(Zn)等を用いることができる。また、導入する元素131は、ラジカル、原子、分子、又はイオンのいずれかの状態で含まれていればよい。

#### 【0199】

元素131を導入する方法としては、上述の元素130を導入する方法を参照することができる。

40

#### 【0200】

なお、第1の酸化物半導体層156と第1の酸化物層154との界面に元素131が達しないように導入の条件を設定することが好ましい。第1の酸化物半導体層156と第2の酸化物半導体層158との界面近傍であって第1の酸化物半導体層156側（例えば界面から20nm以下、好ましくは10nm以下、より好ましくは5nm以下の範囲）に位置するように元素131を導入することが好ましい。または、元素131の濃度の最も高い領域が、該界面から第1の酸化物半導体層の厚さの3/4以下、好ましくは1/2以下、より好ましくは1/4以下の範囲に位置するように、元素131を導入することが好ましい。

#### 【0201】

50

但し、第1の酸化物半導体層156中のみに元素131の導入を制御することは困難であるため、元素131は、第2の酸化物半導体層158中及び第2の酸化物層160中であって、ソース電極層112a及びドレイン電極層112bと重ならない領域にも含まれる。

#### 【0202】

そこで、ソース電極層112a及びドレイン電極層112bをマスクとして、第2の酸化物層160及び第2の酸化物半導体層158に、酸素132を導入する(図11(A)参照)。酸素の導入によって、先の元素131の導入によって引き起こされることがある第2の酸化物半導体層158及び第2の酸化物層160中の酸素欠損を補填することができる。ここで酸素の導入によって、第2の酸化物層160及び第2の酸化物半導体層158を、i型化又は実質的にi型化することが可能となる。10

#### 【0203】

酸素132の導入は、例えばイオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。酸素の導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよい。

#### 【0204】

なお、酸素132の導入は、先の工程で導入された元素131の濃度の最も高い領域よりも、酸素132の濃度の最も高い領域が表面側に形成されるように、導入の条件を設定することが好ましい。これによって、第1の酸化物半導体層156に、n型領域である第1の領域156aを形成し、且つ、該第1の領域156aと酸化物積層165上面との間に、i型化又は実質的にi型化した領域である第2の酸化物半導体層158及び第2の酸化物層160を設けることが可能となる。すなわち、酸化物積層165において図2に示した二重井戸(Double Well)構造を形成することが可能となる。よって該酸化物積層165を含むトランジスタ250は大きな電流を流すことが可能となる。20

#### 【0205】

但し、酸素132の導入に代えて、酸素プラズマ処理、N<sub>2</sub>Oプラズマ処理等のプラズマ処理、又はO<sub>2</sub>アッシング処理によって、第2の酸化物層160及び/又は第2の酸化物半導体層158をi型化又は実質的にi型化してもよい。又は、酸素プラズマ処理、N<sub>2</sub>Oプラズマ処理等のプラズマ処理、又はO<sub>2</sub>アッシング処理と、酸素132の導入とを組み合わせて行ってもよい。30

#### 【0206】

なお、図10(D)に示す元素131の導入及び図11(A)に示す酸素132の導入は、双方ともソース電極層112a及びドレイン電極層112bをマスクとして自己整合的に行うことができるため、マスクの増加を伴うことなく、且つ制御性よく処理を行うことができる。

#### 【0207】

次いで、図4(C)の工程と同様に、酸化物積層165上にゲート絶縁層114及びゲート電極層116を形成する(図11(B)参照)。40

#### 【0208】

その後、図4(D)の工程と同様に、ゲート電極層116上に絶縁層118及び絶縁層120を形成し、絶縁層118及び絶縁層120に設けられたコンタクトホールを介してソース電極層112a及びドレイン電極層112bと電気的に接続する電極層122a及び電極層122bを形成する(図11(C)参照)。

#### 【0209】

以上によって、トランジスタ250を形成することができる。

#### 【0210】

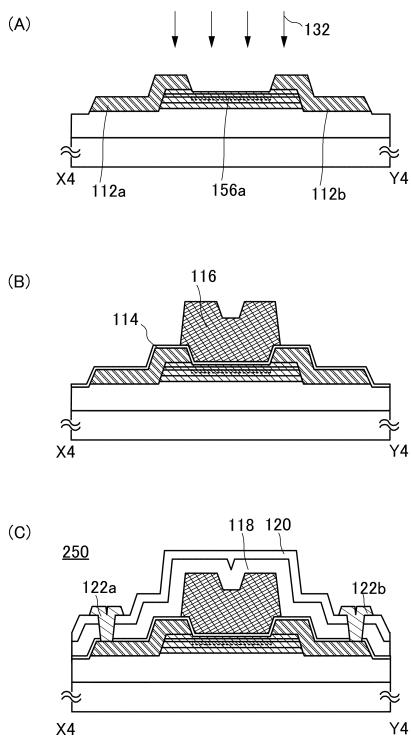

<半導体装置の構成例6>

図12(A)乃至(C)にトランジスタ270の構成例を示す。図12(A)は、トラン50

ジスタ 270 の平面図であり、図 12 (B) は、図 12 (A) の V5 - W5 における断面図であり、図 12 (C) は、図 12 (A) の X5 - Y5 における断面図である。

#### 【0211】

図 12 に示すトランジスタは、トランジスタ 250 の変形例であり、第 2 の酸化物層 160 が、ソース電極層 112a 及びドレイン電極層 112b から露出した第 2 の酸化物半導体層 158 に接して、ソース電極層 112a 及びドレイン電極層 112b 上に設けられた構成を有する。

#### 【0212】

トランジスタ 270 において、第 1 の酸化物半導体層 156 に含まれる第 1 の領域 156a は、島状の第 1 の酸化物層 154、第 1 の酸化物半導体層 156 及び第 2 の酸化物半導体層 158 上にソース電極層 112a 及びドレイン電極層 112b を形成し、該ソース電極層 112a 及びドレイン電極層 112b をマスクとして、図 10 (D) に示した工程と同様に酸素と親和性のある元素を導入することで形成される。

#### 【0213】

また、当該元素の導入工程において第 2 の酸化物半導体層 158 において第 1 の領域 156a と重なる領域に、酸素と親和性のある元素を導入されることがある。よって、酸素と親和性のある元素の導入処理を行った後には、第 2 の酸化物半導体層 158 において第 1 の領域 156a と重なる領域に対して酸素の導入処理を行うことが好ましい。酸素の導入処理は、前述のトランジスタ 250 の作製工程と同様に行ってもよいし、第 2 の酸化物半導体層 158 に接して形成される第 2 の酸化物層 160 に含まれる酸素を熱処理によって拡散させてもよい。

#### 【0214】

図 12 (D) に示すトランジスタ 280 は、トランジスタ 270 の変形例であり、ゲート電極層 116 の形状が異なる点でトランジスタ 270 と相違しており、そのほかの部分は共通である。

#### 【0215】

トランジスタ 280 のゲート電極層 116 は、実施の形態 1 のトランジスタ 230 及びトランジスタ 240 等と同様に、ソース電極層 112a と重畠し、且つドレイン電極層 112b と重畠しないように設けられている。ドレイン電極層 112b とゲート電極層 116 とが重ならないように離間して設けることにより、ゲート - ドレイン間の耐圧を向上させることができる。したがって極めて高い電圧でトランジスタ 280 を駆動した場合でも高い信頼性を確保することができる。

#### 【0216】

以上、本実施の形態で示したトランジスタは、チャネルを形成する第 1 の酸化物半導体層 156 のゲート電極層 116 と重なる領域に n 型の導電性を付与する不純物を含む第 1 の領域 156a を設けることにより、トランジスタのオン状態におけるソース - ドレイン間の直列抵抗を低減することができる。その結果、オン状態におけるソース - ドレイン間に流れる電流（オン電流ともいう）を高めることができる。

#### 【0217】

また、n 型の導電性を付与する不純物は、ソース電極層 112a 及びドレイン電極層 112b をマスクとして自己整合的に導入されるため、半導体装置作製の制御性及び歩留まりを向上させることができる。

#### 【0218】

また、ソース電極層 112a 及びドレイン電極層 112b と第 1 の領域 156a との間に、i 型又は実質的に i 型である第 2 の領域 156b と、i 型又は実質的に i 型である第 2 の酸化物半導体層 158 を含むことで、オン動作、オフ動作が確実なトランジスタとすることができる。さらにはノーマリーオフ型のトランジスタを実現することができる。

#### 【0219】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

10

20

30

40

50

## 【0220】

(実施の形態3)

本実施の形態では、実施の形態1又は実施の形態2のトランジスタに適用可能な酸化物半導体層の一例について説明する。

## 【0221】

<酸化物半導体層の結晶性>

酸化物半導体層は、単結晶酸化物半導体層と、非単結晶酸化物半導体層とに大別される。非単結晶酸化物半導体層としては、例えば、非晶質酸化物半導体膜、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜等が挙げられる。

10

## 【0222】

トランジスタに用いる第1の酸化物半導体層又は第2の酸化物半導体層は、例えばCAAC-OS膜を有してもよい。CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100nm未満の立方体内に収まる大きさである。したがって、CAAC-OS膜に含まれる結晶部は、一辺が10nm未満、5nm未満、または3nm未満の立方体内に収まる大きさの場合も含まれる。CAAC-OS膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

## 【0223】

CAAC-OS膜を透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって観察すると、結晶部同士の明確な境界、すなわち、結晶粒界(グレインバウンダリーともいう。)を確認できない。そのため、CAAC-OS膜は粒界に起因する電子移動度の低下が起こりにくいといえる。

20

## 【0224】

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察(断面TEM観察)すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-OS膜の被形成面または上面と平行に配列する。

## 【0225】

一方、CAAC-OS膜を、試料面と概略垂直な方向からTEMによって観察(平面TEM観察)すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

30

## 【0226】

断面TEM観察および平面TEM観察より、CAAC-OS膜の結晶部は配向性を有していることがわかる。

## 【0227】

CAAC-OS膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えば $InGaZnO_4$ の結晶を有するCAAC-OS膜のout-of-plane法による解析では、回折角( $2\theta$ )が $31^\circ$ 近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$ の結晶の(009)面に帰属されることから、CAAC-OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

40

## 【0228】

一方、CAAC-OS膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、 $2\theta$ が $56^\circ$ 近傍にピークが現れる場合がある。このピークは、 $InGaZnO_4$ の結晶の(110)面に帰属される。 $InGaZnO_4$ の単結晶酸化物半導体膜であれば、 $2\theta$ を $56^\circ$ 近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAAC-OS膜の場合は、 $2\theta$ を $56^\circ$ 近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

50

## 【0229】

以上のことから、C A A C - O S 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 T E M 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。なお、本明細書ならびに請求項において、単に垂直と記載する場合、80°以上100°以下、例えば85°以上95°以下の範囲も含まれる。また、単に平行と記載する場合、-10°以上10°以下、例えば-5°以上5°以下の範囲も含まれる。

## 【0230】

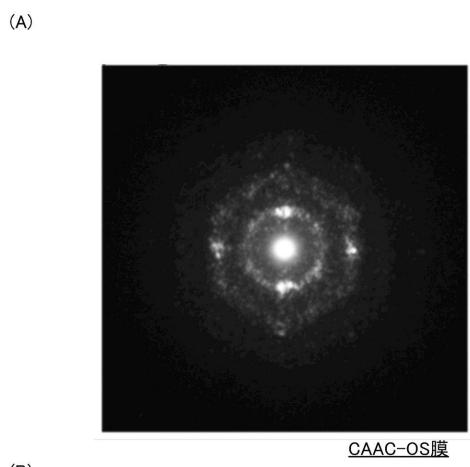

また、C A A C - O S 膜の電子線回折パターンにスポットが観測される場合がある。なお、ビーム径が10 nm 以下または5 nm 以下の電子線を用いて得られる電子線回折パターンを極微電子線回折パターンとよぶ。図13(A)はC A A C - O S 膜を有する試料の極微電子線回折パターンの一例である。ここでは、試料をC A A C - O S 膜の被形成面に垂直な方向に切断し、厚さが40 nm程度となるように薄片化し、ビーム径が1 nm の電子線を試料の切断面に垂直な方向から入射させている。図13(A)より、C A A C - O S 膜の極微電子線回折パターンにスポットが観測されることがわかる。

10

## 【0231】

C A A C - O S 膜は、不純物濃度を低減することで形成できる場合がある。ここで、不純物は水素、炭素、シリコン、遷移金属元素などの酸化物半導体の主成分以外の元素である。特にシリコンなどの元素は、酸化物半導体を構成する金属元素よりも酸素との結合力が強い。従って、当該元素が酸化物半導体から酸素を引き抜く際に酸化物半導体の原子配列を乱し、結晶性を低下させることがある。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、酸化物半導体の結晶性を低下させることがある。従って、C A A C - O S は不純物濃度の低い酸化物半導体であると言える。

20

## 【0232】

不純物濃度が低く、欠陥準位密度の低い(酸素欠損の少ない)状態を高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体はキャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、しきい値電圧がマイナス(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体は欠陥準位密度が低いため、トラップ準位密度も低くなる。従って、当該酸化物半導体をチャネル形成領域に用いることで、電気特性の変動が小さく、信頼性の高いトランジスタを与えることができる。一方、酸化物半導体に含まれる不純物はキャリア発生源となりやすく、容易にトラップ準位を形成する。また、酸化物半導体のトラップ準位に捕獲された電荷は消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体をチャネル形成領域に用いたトランジスタは電気特性が不安定になりやすい。

30

## 【0233】

なお、結晶部は、C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えばC A A C - O S 膜の形状をエッチングなどによって変化させた場合、結晶のc軸がC A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

40

## 【0234】

なお、C A A C - O S 膜の結晶化度は均一でなくてもよい。例えば、C A A C - O S 膜の結晶部がC A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は被形成面近傍の領域よりも結晶化度が高くなることがある。また、C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

50

**【0235】**

なお、 $\text{InGaZnO}_4$  の結晶を有する CAAc - OS 膜の out-of-plane 法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、 CAAc - OS 膜中の一部に、 c 軸配向性を有さない結晶が含まれることを示している。 CAAc - OS 膜は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。

**【0236】**

CAAc - OS 膜は、例えば、欠陥準位密度を低減することで形成することができる。酸化物半導体において酸素欠損は欠陥準位である。また、上述したように、酸素欠損はトラップ準位となることや、水素を捕獲することによってキャリア発生源となりやすい。 CAAc - OS 膜を形成するためには、酸化物半導体に酸素欠損を生じさせないことが重要となる。従って、 CAAc - OS 膜は、欠陥準位密度の低い酸化物半導体である。または、 CAAc - OS 膜は、酸素欠損の少ない酸化物半導体である。

**【0237】**

また、高純度真性または実質的に高純度真性である CAAc - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは信頼性が高い。

**【0238】**

CAAc - OS 膜は、例えば、 DC 電源を用いたスパッタリング法によって形成することができる。

**【0239】**

また、トランジスタに用いる第 1 の酸化物半導体層又は第 2 の酸化物半導体層は、複数の結晶粒を含む多結晶酸化物半導体膜であってもよい。多結晶酸化物半導体膜の TEM 像では、  $2\text{ nm}$  以上  $300\text{ nm}$  以下、  $3\text{ nm}$  以上  $100\text{ nm}$  以下または  $5\text{ nm}$  以上  $50\text{ nm}$  以下の粒径の結晶粒が確認されることが多い。また、多結晶酸化物半導体膜は、 TEM 像で結晶粒と結晶粒との境界を確認できる場合がある。

**【0240】**

多結晶酸化物半導体膜の複数の結晶粒では、結晶方位が異なっている場合がある。また、多結晶酸化物半導体膜を XRD 装置を用いて out-of-plane 法による分析を行うと、 $2\theta$  が  $31^\circ$  近傍のピークを含む複数種の配向ピークが現れる場合がある。また、多結晶酸化物半導体膜は、電子線回折パターンでスポットが観測される場合がある。

**【0241】**

多結晶酸化物半導体膜は高い結晶性を有するため、高い電子移動度を与えることができる。従って、多結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタは高い電界効果移動度を有する。ただし、粒界に不純物が偏析する場合、粒界は欠陥準位、キャリア発生源、あるいはトラップ準位となり得るため、多結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタは、 CAAc - OS 膜をチャネル形成領域に用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる場合がある。

**【0242】**

多結晶酸化物半導体膜は、高温での加熱処理、またはレーザ光処理によって形成することができる。

**【0243】**

また、トランジスタに用いる第 1 の酸化物半導体層又は第 2 の酸化物半導体層は、微結晶酸化物半導体膜であってもよい。微結晶酸化物半導体膜の TEM 像では、通常、明確に結晶部を確認することができない。微結晶酸化物半導体膜は、例えば、  $1\text{ nm}$  以上  $10\text{ nm}$  未満の大きさの微結晶（ナノ結晶ともいう）を含む。従って微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高く、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。同様に、微結晶酸化物半導体膜の TEM 像では、通常、結晶部と結晶部との境界を明確に確認できない。従って、微結晶酸化物半導体膜は、不純物が偏析することが少なく、欠陥準位密度が高くなりにくい。また、電子移動度の低下が

10

20

30

40

50

小さい。

**【0244】**

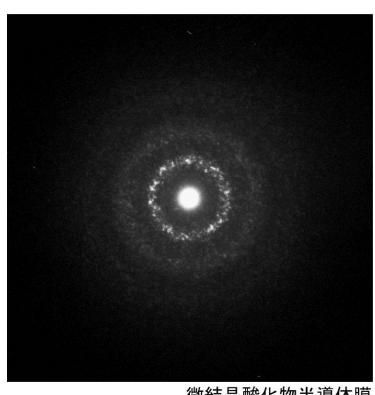

図13(B)は、微結晶酸化物半導体膜を有する試料の極微電子線回折パターンの一例である。ここでは、試料を、微結晶酸化物半導体膜の被形成面に垂直な方向に切断し、厚さが40nm程度となるように薄片化されている。また、ここでは、ビーム径が1nmの電子線を、試料の切断面に垂直な方向から入射させる。図13(B)より、微結晶酸化物半導体膜の極微電子線回折パターンは、円周状に分布した複数のスポットが観測されることがわかる。

**【0245】**

微結晶酸化物半導体膜は、微小な領域において原子配列に周期性を有するため、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、微結晶酸化物半導体膜は、結晶部と結晶部との間で規則性がないため、CAC-O<sub>S</sub>膜と比べて欠陥準位密度が高くなる。

10

**【0246】**

従って、微結晶酸化物半導体膜は、CAC-O<sub>S</sub>膜と比べて、キャリア密度が高くなる場合がある。キャリア密度が高い酸化物半導体は、電子移動度が高くなる傾向があるため、微結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタは、高い電界効果移動度を有する傾向にある。また、微結晶酸化物半導体膜は、CAC-O<sub>S</sub>膜と比べて、欠陥準位密度が高いため、トラップ準位密度も高くなりやすい。従って、微結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタは、CAC-O<sub>S</sub>膜をチャネル形成領域に用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなりやすい。ただし、微結晶酸化物半導体膜は、比較的不純物が多く含まれていても形成することができるため、CAC-O<sub>S</sub>膜よりも形成が容易となり、用途によっては好適に用いることができる。例えば、AC電源を用いたスパッタリング法などの成膜方法によって微結晶酸化物半導体膜を形成してもよい。AC電源を用いたスパッタリング法は、大型基板へ均一性高く成膜することができるため、微結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタを有する半導体装置は生産性高く作製することができる。

20

**【0247】**

トランジスタに用いる第1の酸化物半導体層又は第2の酸化物半導体層は、例えば非晶質酸化物半導体膜であってもよい。非晶質酸化物半導体膜は、膜中における原子配列が無秩序であり、結晶成分を有さない酸化物半導体である。膜全体が非晶質構造の酸化物半導体膜が典型である。非晶質酸化物半導体膜のTEM像では、結晶部を確認することができない。

30

**【0248】**

非晶質酸化物半導体膜のXRD装置を用いたout-of-plane法による分析では、結晶配向を示すピークが検出されない。また、非晶質酸化物半導体膜の電子線回折または極微電子線回折では、ハローパターンが観測される。

**【0249】**

非晶質酸化物半導体膜は、例えば、水素などの不純物を高い濃度で含ませることにより形成することができる。従って、非晶質酸化物半導体膜は、例えば、不純物を高い濃度で含む酸化物半導体である。

40

**【0250】**

酸化物半導体層に不純物が高い濃度で含まれると、酸化物半導体層に酸素欠損などの欠陥準位を形成する。従って、不純物濃度の高い非晶質酸化物半導体膜は、欠陥準位密度が高い。また、非晶質酸化物半導体膜は、結晶性が低いためCAC-O<sub>S</sub>膜や微結晶酸化物半導体膜と比べて欠陥準位密度が高い。

**【0251】**

従って、非晶質酸化物半導体膜は、微結晶酸化物半導体膜と比べて、さらにキャリア密度が高くなる。そのため、非晶質酸化物半導体膜をチャネル形成領域に用いたトランジスタは、ノーマリオンの電気特性になる場合があるため、ノーマリオンの電気特性が求められるトランジスタに好適に用いることができる場合がある。非晶質酸化物半導体膜は、欠陥

50

準位密度が高いため、トラップ準位密度も高くなりやすい。従って、非晶質酸化物半導体膜をチャネル形成領域に用いたトランジスタは、C A A C - O S 膜や微結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる。ただし、非晶質酸化物半導体膜は、比較的不純物が多く含まれる成膜方法によっても形成することができるため、形成が容易となり、用途によっては好適に用いることができる場合がある。例えば、スピンドルコート法、ゾル・ゲル法、浸漬法、スプレー法、スクリーン印刷法、コンタクトプリント法、インクジェット印刷法、ロールコート法、ミストC V D法などの成膜方法によって非晶質酸化物半導体膜を形成してもよい。従って、非晶質酸化物半導体膜をチャネル形成領域に用いたトランジスタを有する半導体装置は生産性高く作製することができる。

10

#### 【 0 2 5 2 】

なお、酸化物半導体層が、C A A C - O S 膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、C A A C - O S の領域、のいずれか二種以上の領域を有する。また、混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、C A A C - O S の領域、のいずれか二種以上の領域の積層構造を有する。

#### 【 0 2 5 3 】

トランジスタに用いる第1の酸化物半導体層又は第2の酸化物半導体層は、単結晶酸化物半導体膜であってもよい。単結晶酸化物半導体膜は、不純物濃度が低く、欠陥準位密度が低い（酸素欠損が少ない）ため、キャリア密度を低くすることができます。従って、単結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタは、ノーマリーオンになりにくい。また、単結晶酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる。従って、単結晶酸化物半導体膜をチャネル形成領域に用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。

20

#### 【 0 2 5 4 】

酸化物半導体層は、膜中の欠陥が少ないと密度が高くなり、結晶性が高いと密度が高くなる。また、酸化物半導体層は、例えば水素などの不純物濃度が低いと密度が高くなる。通常、単結晶酸化物半導体膜はC A A C - O S 膜よりも密度が高く、C A A C - O S 膜は微結晶酸化物半導体膜よりも密度が高く、多結晶酸化物半導体膜は微結晶酸化物半導体膜よりも密度が高く、微結晶酸化物半導体膜は非晶質酸化物半導体膜よりも密度が高い。

30

#### 【 0 2 5 5 】

なお、ここでは、酸化物半導体層（具体的には、酸化物積層に含まれる第1の酸化物半導体層又は第2の酸化物半導体層）の結晶性について詳述したが、本発明の一態様の半導体装置において、酸化物半導体層の上層または下層に接して設けられる第1の酸化物層及び第2の酸化物層は、酸化物半導体層と主成分を同じくする酸化物層であるから、酸化物半導体層と同様に、C A A C - O S 膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜又は単結晶酸化物半導体膜を含んでいてもよいし、これらの結晶状態を二種以上有する混合膜であってもよい。

#### 【 0 2 5 6 】

40

#### 《 C A A C - O S 膜の成膜方法》

C A A C - O S 膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa - b面から劈開し、a - b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、C A A C - O S 膜を成膜することができる。

#### 【 0 2 5 7 】

平板状のスパッタリング粒子は、例えば、a - b面に平行な面の円相当径が3 nm以上10 nm以下、厚さ（a - b面に垂直な方向の長さ）が0.7 nm以上1 nm未満である。

50

なお、平板状のスパッタリング粒子は、a - b面に平行な面が正三角形または正六角形であってもよい。ここで、面の円相当径とは、面の面積と等しい正円の直径をいう。

#### 【0258】

また、CAC-O<sub>S</sub>膜を成膜するために、以下の条件を適用することが好ましい。

#### 【0259】

一つは成膜時の基板温度を高めることである。具体的には、基板温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板温度を高めることで、以下のようなメカニズムによってCAC-O<sub>S</sub>膜が形成される可能性がある。すなわち、平板状のスパッタリング粒子が基板に到達して基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。このとき、スパッタリング粒子は正に帯電しているのでスパッタリング粒子同士が反発しながら基板に付着する。従って、スパッタリング粒子が偏って不均一に重なることがなく、厚さの均一なCAC-O<sub>S</sub>膜を成膜することができる。10

#### 【0260】

二つ目は、成膜時の不純物混入を低減させることである。これにより、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。20

#### 【0261】

三つ目は、また、成膜ガス中の酸素割合を高め、電力を最適化することである。これにより、成膜時のプラズマダメージが軽減される。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

#### 【0262】

または、CAC-O<sub>S</sub>膜は、以下の方法により形成する。

#### 【0263】

まず、第1の酸化物半導体膜を1nm以上10nm未満の厚さで成膜する。第1の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜する。30

#### 【0264】

次に、加熱処理を行い、第1の酸化物半導体膜を結晶性の高い第1のCAC-O<sub>S</sub>膜とする。加熱処理の温度は、350以上740以下、好ましくは450以上650以下とする。また、加熱処理の時間は1分以上24時間以下、好ましくは6分以上4時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えばよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第1の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第1の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は1000Pa以下、100Pa以下、10Pa以下または1Pa以下の減圧下で行ってもよい。減圧下では、第1の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。40

#### 【0265】

第1の酸化物半導体膜は、厚さが1nm以上10nm未満であることにより、厚さが10nm以上である場合と比べ、加熱処理によって容易に結晶化させることができる。

#### 【0266】

次に、第1の酸化物半導体膜と同じ組成である第2の酸化物半導体膜を10nm以上50nm以下の厚さで成膜する。第2の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜50

する。

#### 【0267】

次に、加熱処理を行い、第2の酸化物半導体膜を第1のCAC-O<sub>S</sub>膜から固相成長させることで、結晶性の高い第2のCAC-O<sub>S</sub>膜とする。加熱処理の温度は、350以上740以下、好ましくは450以上650以下とする。また、加熱処理の時間は1分以上24時間以下、好ましくは6分以上4時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えばよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第2の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第2の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は1000Pa以下、100Pa以下、10Pa以下または1Pa以下の減圧下で行ってもよい。減圧下では、第2の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

10

#### 【0268】

以上のようにして、合計の厚さが10nm以上であるCAC-O<sub>S</sub>膜を形成することができる。当該CAC-O<sub>S</sub>膜を、酸化物積層における酸化物半導体層として好適に用いることができる。

#### 【0269】

次に、被形成面が低温（例えば、130未満、100未満、70未満または室温（20乃至25）程度）である場合の酸化物膜の形成方法について説明する。

#### 【0270】

被形成面が低温の場合、スパッタ粒子は被成膜面に不規則に降り注ぐ。スパッタ粒子は、例えば、マイグレーションをしないため、既に他のスパッタ粒子が堆積している領域も含め、無秩序に堆積していく。即ち、堆積して得られる酸化物膜は、例えば、厚さが均一でなく、結晶の配向も無秩序になる。このようにして得られた酸化物膜は、スパッタ粒子の結晶性をある程度維持するため、結晶部（ナノ結晶）を有する。

#### 【0271】

また、成膜時の圧力が高い場合、放出されたスパッタ粒子がアルゴンなどの他の粒子（原子、分子、イオン、ラジカルなど）と衝突する頻度が高まる。スパッタ粒子は、飛翔中に他の粒子と衝突する（再スパッタされる）ことで、結晶構造が崩れる場合がある。例えば、スパッタ粒子は、他の粒子と衝突することで、平板状の形状を維持することができず、細分化（例えば各原子に分かれた状態）される場合がある。このとき、スパッタ粒子から分かれた各原子が被形成面に堆積していくことで、非晶質酸化物膜が形成される場合がある。

30

#### 【0272】

また、多結晶酸化物を有するターゲットを用いたスパッタリング法ではなく、ターゲットなどの固体を気化することで成膜する方法の場合、各原子に分かれた状態で放出して被形成面に堆積するなどして、非晶質酸化物膜が形成される場合がある。また、例えば、レーザアブレーション法では、ターゲットから放出された原子、分子、イオン、ラジカル、クラスターなどが被形成面に堆積するため、非晶質酸化物膜が形成されやすい。

40

#### 【0273】

本発明の一態様のトランジスタに含まれる第1の酸化物層、第1の酸化物半導体層、第2の酸化物半導体層又は第2の酸化物層にはそれぞれ、上述のいずれの結晶状態の酸化物層又は酸化物半導体層を適用してもよい。但し、チャネルとして機能する酸化物半導体層には、CAC-O<sub>S</sub>膜を適用することが好ましい。

#### 【0274】

また、第2の酸化物半導体層をCAC-O<sub>S</sub>膜とする場合、第2の酸化物半導体層上に接して設けられる第2の酸化物層は、第2の酸化物半導体層が有する結晶を種結晶として結晶成長して、結晶構造を有する膜となりやすい。従って、仮に、第1の酸化物層と第2

50

の酸化物層を同様の材料及び同様の作製方法を用いて形成しても、第2の酸化物層として第1の酸化物層より結晶性の高い膜が得られる場合がある。また、第2の酸化物層のうち、第2の酸化物半導体層と接する領域と、接しない領域とでは、結晶性が異なる場合がある。

#### 【0275】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0276】

##### (実施の形態4)

本実施の形態では本発明の一態様の半導体装置の一形態として、上記実施の形態で例示したトランジスタを具備するインバータ及びコンバータ等の電力変換回路の構成例について説明する。

10

#### 【0277】

##### [DCDCコンバータ]

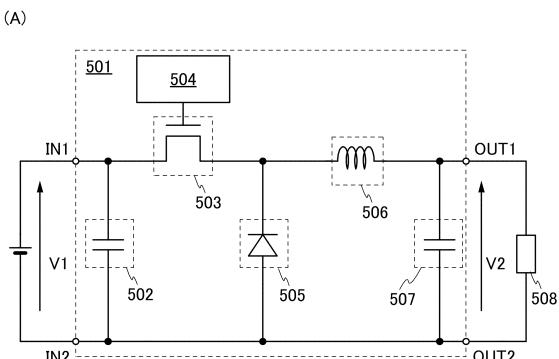

図14(A)に示すDCDCコンバータ501は、電力変換回路の一例であり、チョッパー回路を用いた、降圧型のDCDCコンバータである。DCDCコンバータ501は、容量素子502、トランジスタ503、制御回路504、ダイオード505、コイル506及び容量素子507を有する。

#### 【0278】

DCDCコンバータ501は、制御回路504によるトランジスタ503のスイッチング動作により動作する。DCDCコンバータ501により、入力端子IN1とIN2に印加される入力電圧V1は、出力端子OUT1とOUT2より降圧されたV2として負荷508に出力できる。DCDCコンバータ501が具備するトランジスタ503には、上記実施の形態で例示した半導体装置を適用することができる。そのため、スイッチング動作によって大きな出力電流を流すことができ、且つオフ電流を低減することができる。したがって消費電力が低減され、高速な動作が可能なDCDCコンバータを実現できる。

20

#### 【0279】

図14(A)では非絶縁型の電力変換回路の一例としてチョッパー回路を用いた降圧型のDCDCコンバータを示したが、他にもチョッパー回路を用いた昇圧型のDCDCコンバータ、チョッパー回路を用いた昇圧降圧型のDCDCコンバータが具備するトランジスタにも上記実施の形態で例示した半導体装置を適用することができる。そのため、スイッチング動作によって大きな出力電流を流すことができ、且つオフ電流を低減することができる。したがって消費電力が低減され、高速な動作が可能なDCDCコンバータを実現できる。

30

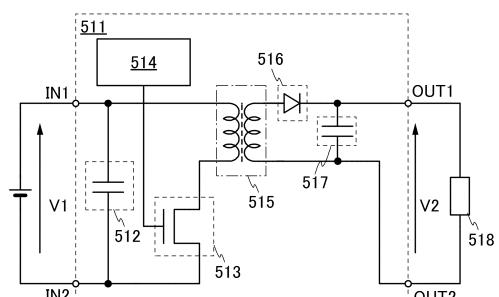

#### 【0280】

次いで図14(B)に示すDCDCコンバータ511は電力変換回路の一例であり、ここでは絶縁型の電力変換回路であるフライバックコンバータの回路構成例を示す。DCDCコンバータ511は、容量素子512、トランジスタ513、制御回路514、一次コイル及び二次コイルを具備する変圧器515、ダイオード516及び容量素子517を有する。

40

#### 【0281】

図14(B)に示すDCDCコンバータ511は、制御回路514によるトランジスタ513のスイッチング動作により動作する。DCDCコンバータ511により、入力端子IN1とIN2に印加される入力電圧V1は、出力端子OUT1とOUT2より昇圧または降圧されたV2として負荷518に出力できる。DCDCコンバータ511が具備するトランジスタ513には、上記実施の形態で例示した半導体装置を適用することができる。そのため、スイッチング動作によって大きな出力電流を流すことができ、且つオフ電流を低減することができる。したがって消費電力が低減され、高速な動作が可能なDCDCコンバータを実現できる。

#### 【0282】

50

なお、フォワード型のDCDCコンバータが具備するトランジスタにも上記実施の形態で例示した半導体装置を適用することができる。

**【0283】**

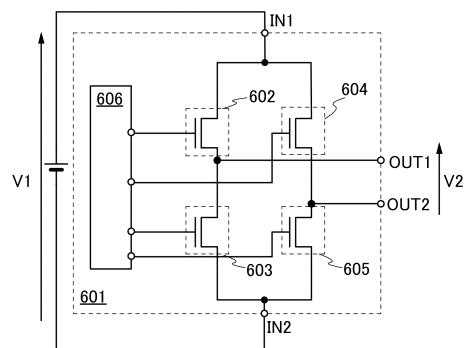

図15に示すインバータ601は、フルブリッジ型のインバータの一例である。インバータ601は、トランジスタ602、トランジスタ603、トランジスタ604、トランジスタ605、及び制御回路606を有する。

**【0284】**

図15に示すインバータ601は、制御回路606によるトランジスタ602乃至605のスイッチング動作により動作する。入力端子IN1とIN2に印加される直流電圧V1は、出力端子OUT1とOUT2より交流電圧V2として出力することができる。インバータ601が具備するトランジスタ602乃至605には、上記実施の形態で例示した半導体装置を適用することができる。そのため、スイッチング動作により大きな出力電流を流すことができ、且つオフ電流を低減することができる。したがって消費電力が低減され、高速な動作が可能なインバータとすることができる。

**【0285】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0286】**

(実施の形態5)

本実施の形態では本発明の一態様の半導体装置の一形態として、上記実施の形態で例示したトランジスタを具備する電源回路の構成例について説明する。

**【0287】**

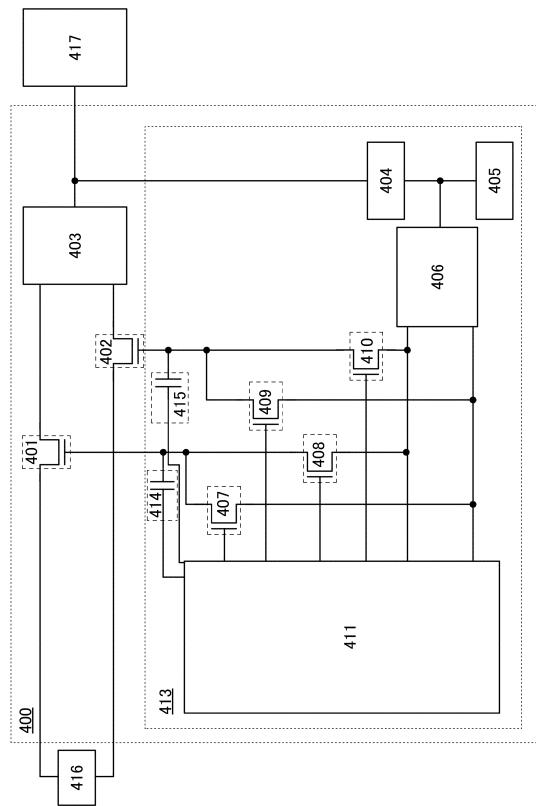

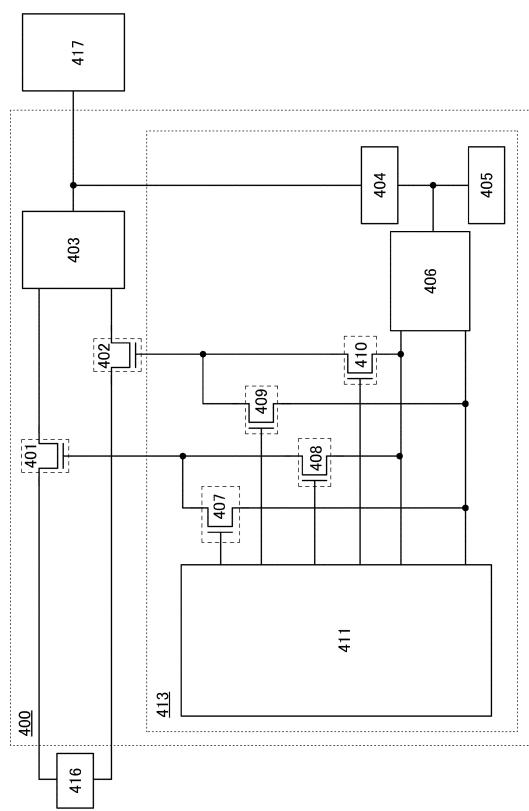

図16に、本発明の一態様に係る電源回路400の構成を、一例として示す。図16に示す電源回路400は、制御回路413と、パワースイッチ401と、パワースイッチ402と、電圧調整部403と、を有する。

**【0288】**

電源回路400には、電源416から電圧が供給されており、パワースイッチ401及びパワースイッチ402は、電圧調整部403への上記電圧の入力を制御する機能を有する。

**【0289】**

なお、電源416から出力される電圧が交流電圧である場合、図16に示すように、電圧調整部403への第1電位の入力を制御するパワースイッチ401と、電圧調整部403への第2電位の入力を制御するパワースイッチ402とを、電源回路400に設ける。電源416から出力される電圧が直流電圧である場合、図16に示すように、パワースイッチ401とパワースイッチ402とを電源回路400に設けてもよいし、或いは、第2電位を接地電位とし、パワースイッチ402を設けずにパワースイッチ401を電源回路400に設けてもよい。

**【0290】**

そして、本発明の一態様では、パワースイッチ401及びパワースイッチ402として、耐圧性の高いトランジスタを用いる。例えば上記トランジスタとして、実施の形態1又は実施の形態2で例示したトランジスタを用いることができる。

**【0291】**

パワースイッチ401及びパワースイッチ402として、上記酸化物積層を含むトランジスタを用いることにより、高い出力電流を流すことが可能で、且つ耐圧を高めることができる。

**【0292】**

本発明の一態様に係る酸化物半導体を活性層に用いたトランジスタを、パワースイッチ401またはパワースイッチ402に用いることで、炭化珪素や窒化ガリウムなどを活性層に用いたトランジスタよりも、パワースイッチ401またはパワースイッチ402のスイッチングを高速にすることができます、それにより、スイッチングに起因する電力損失を小さくすることができる。

10

20

30

40

50

く抑えることができる。

**【0293】**

電圧調整部403は、パワースイッチ401及びパワースイッチ402を介して電源416から電圧が入力されると、当該電圧の調整を行う機能を有する。具体的に、電圧調整部403における電圧の調整とは、交流電圧を直流電圧に変換すること、電圧の高さを変えること、電圧の高さを平滑化すること、のいずれか一つまたは複数を含む。

**【0294】**

電圧調整部403において調整された電圧は、負荷417と制御回路413に与えられる。

**【0295】**

また、図16に示す電源回路400では、蓄電装置404と、補助電源405と、電圧発生回路406と、トランジスタ407乃至トランジスタ410と、容量素子414と、容量素子415とを有する。

10

**【0296】**

蓄電装置404は、電圧調整部403から与えられた電力を、一時的に蓄える機能を有する。具体的に蓄電装置404は、電圧調整部403から与えられた電圧を用いて、電力を蓄えることができるキャパシタ、二次電池などの蓄電部を有する。

**【0297】**

補助電源405は、蓄電装置404から出力が可能な電力が不足しているときに、制御回路413の動作に要する電力を、補う機能を有する。補助電源405として、一次電池などを用いることができる。

20

**【0298】**

電圧発生回路406は、蓄電装置404または補助電源405から出力される電圧を用いて、パワースイッチ401及びパワースイッチ402のスイッチングを制御するための電圧を、生成する機能を有する。具体的に電圧発生回路406は、パワースイッチ401及びパワースイッチ402をオンにするための電圧を生成する機能と、パワースイッチ401及びパワースイッチ402をオフにするための電圧を生成する機能とを有する。

**【0299】**

無線信号入力回路411は、トランジスタ407乃至トランジスタ410のスイッチングに従ってパワースイッチ401及びパワースイッチ402を制御する機能を有する。

30

**【0300】**

具体的に、無線信号入力回路411は、外部から与えられる、パワースイッチ401及びパワースイッチ402の動作状態を制御するための無線信号に重畠した命令を電気信号に変換する入力部と、上記電気信号に含まれる命令をデコードし、トランジスタ407乃至トランジスタ410のスイッチングを、上記命令に従って制御するための信号を生成する信号処理部と、を有する。

**【0301】**

トランジスタ407乃至トランジスタ410は、無線信号入力回路411において生成された信号に従って、スイッチングを行う。具体的に、トランジスタ408及びトランジスタ410がオンであるとき、電圧発生回路406で生成された、パワースイッチ401及びパワースイッチ402をオフにするための電圧が、パワースイッチ401及びパワースイッチ402に与えられる。この状態において、トランジスタ408及びトランジスタ410をオフにすると、パワースイッチ401及びパワースイッチ402をオフにするための上記電圧が与えられた状態が維持される。引き続いでトランジスタ407及びトランジスタ409をオフにすると、電圧発生回路406で生成された、パワースイッチ401及びパワースイッチ402をオフにするための電圧が、パワースイッチ401及びパワースイッチ402に与えられる。この状態において、トランジスタ407及びトランジスタ409をオフにすると、パワースイッチ401及びパワースイッチ402に、パワースイッチ401及びパワースイッチ402をオフにするための上記電圧が与えられた状態が維持される。

40

50

**【0302】**

そして、本発明の一態様では、上記電圧がパワースイッチ401及びパワースイッチ402に与えられた動作状態を維持するために、トランジスタ407乃至トランジスタ410に、オフ電流の著しく小さいトランジスタを用いる。上記構成により、電圧発生回路406において、パワースイッチ401及びパワースイッチ402の動作状態を定めるための電圧の生成を停止しても、パワースイッチ401及びパワースイッチ402の動作状態を維持することができる。よって、電圧発生回路406における消費電力を削減し、延いては電源回路400における消費電力を小さく抑えることができる。

**【0303】**

なお、トランジスタ407乃至トランジスタ410にバックゲートを設け、バックゲートに電位を与えることにより、トランジスタ407乃至トランジスタ410の閾値電圧を制御してもよい。10

**【0304】**

バンドギャップがシリコンの2倍以上のワイドギャップ半導体である酸化物半導体を活性層に用いたトランジスタは、オフ電流が著しく小さいので、トランジスタ407乃至トランジスタ410に用いるのに好適である。

**【0305】**

また、酸化物半導体の中でもIn-Ga-Zn系酸化物、In-Sn-Zn系酸化物などは、炭化シリコンまたは窒化ガリウムと異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコンまたは窒化ガリウムとは異なり、In-Ga-Zn系酸化物は室温でも成膜が可能なため、ガラス基板上、或いはシリコンを用いた集積回路上に電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。20

**【0306】**

容量素子414は、トランジスタ407及びトランジスタ408がオフであるとき、パワースイッチ401に与えられている電圧を、保持する機能を有する。また、容量素子415は、トランジスタ409及びトランジスタ410がオフであるとき、パワースイッチ402に与えられている電圧を、保持する機能を有する。容量素子414及び415の一対の電極の一方は、無線信号入力回路411に接続される。なお、図17に示すように、容量素子414及び415を設けなくてもよい。30

**【0307】**

そして、パワースイッチ401及びパワースイッチ402がオンであるとき、電源416から電圧調整部403への電圧の供給が行われる。そして、上記電圧により、蓄電装置404には電力が蓄積される。

**【0308】**

また、パワースイッチ401及びパワースイッチ402がオフであるとき、電源416から電圧調整部403への電圧の供給が停止する。よって、蓄電装置404への電力の供給は行われないが、本発明の一態様では、上述したように、蓄電装置404または補助電源405に蓄えられている電力を用いて、制御回路413を動作させることができる。すなわち、本発明の一態様に係る電源回路400では、制御回路413によるパワースイッチ401及びパワースイッチ402の動作状態の制御を行いつつ、電圧調整部403への電圧の供給を停止することができる。そして、電圧調整部403への電圧の供給を停止することで、負荷417への電圧の供給が行われないときに、電圧調整部403が有する容量の充放電により電力が消費されるのを防ぐことができ、それにより、電源回路400の消費電力を小さく抑えることができる。40

**【0309】**

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

**【0310】**1020304050

(実施の形態 6 )

本発明の一態様に係る半導体装置(電力変換回路、電源回路などを含む)は、機器への電力の供給を制御するのに適しており、特に大きな電力が必要な機器に好適に用いることができる。例えば、モーターなどの電力によりその駆動が制御される駆動部を備える機器や、電力により加熱または冷却を制御する機器などに好適に用いることができる。

【 0 3 1 1 】

本発明の一態様に係る半導体装置を用いることのできる電子機器として、表示機器、パソコンコンピュータ、記録媒体を備えた画像再生装置(代表的にはDVD:Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)などがある。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機(ATM)、自動販売機、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、扇風機、ドライヤー、エアコンディショナーなどの空調設備、エレベータやエスカレータなどの昇降設備、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、電動ミシン、電動工具、半導体試験装置、などが挙げられる。また、本発明の一態様に係る半導体装置は、電力を用いて電動機により推進する移動体に用いられていてもよい。上記移動体には、自動車(自動二輪車、三輪以上の普通自動車)、電動アシスト自転車を含む原動機付自転車、航空機、船舶、鉄道車両などが、その範疇に含まれる。また、食品、家電製品、上記移動体、鉄鋼、半導体機器、土木、建築、建設などのあらゆる分野で用いられる産業用ロボットの駆動の制御に用いることもできる。

10

20

30

【 0 3 1 2 】

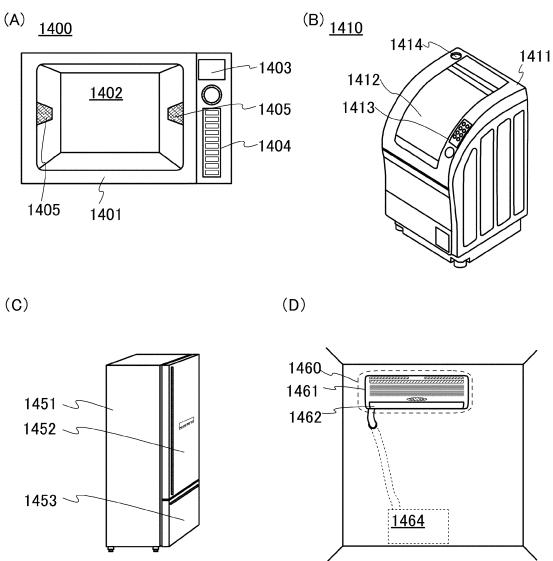

以下では、電子機器の具体例を図18に示す。

【 0 3 1 3 】

図18(A)は電子レンジ1400であり、筐体1401と、被処理物を載置するための処理室1402と、表示部1403と、操作盤などの入力装置1404と、筐体1401の内部に設置されている高周波発生装置から発生した電磁波を、処理室1402に供給する照射部1405とを、有する。

30

【 0 3 1 4 】

本発明の一態様に係る半導体装置は、例えば、高周波発生装置への電力の供給を制御する電源回路に用いることができる。

【 0 3 1 5 】

図18(B)は洗濯機1410であり、筐体1411と、筐体1411内に設けられた洗濯槽の入り口を、開閉させる開閉部1412と、操作盤などの入力装置1413と、洗濯槽の給水口1414とを、有する。

【 0 3 1 6 】

本発明の一態様に係る半導体装置は、例えば、洗濯槽の回転を制御するモーターへの電力の供給を制御する回路に用いることができる。

40

【 0 3 1 7 】

図18(C)は、電気冷凍冷蔵庫の一例である。図18(C)に示す電子機器は、筐体1451と、冷蔵室用扉1452と、冷凍室用扉1453と、を備える。

【 0 3 1 8 】

図18(C)に示す電子機器は、筐体1451の内部に本発明の一態様である半導体装置を有する。上記構成にすることにより、例えば、筐体1451内部の温度に応じて、または冷蔵室用扉1452及び冷凍室用扉1453の開閉に従って、筐体1451内の半導体装置に対する電源電圧の供給を制御できる。

【 0 3 1 9 】

図18(D)は、エアコンディショナーの一例である。図18(D)に示す電子機器は、

50

室内機 1460 及び室外機 1464 により構成される。

【0320】

室内機 1460 は、筐体 1461 と、送風口 1462 と、を備える。

【0321】

図 18 (D) に示す電子機器は、筐体 1461 の内部に本発明の一態様である半導体装置を有する。上記構成にすることにより、例えば、リモートコントローラからの信号に従つて、または室内の温度や湿度に応じて、筐体 1461 内の半導体装置に対する電源電圧の供給を制御できる。

【0322】

また、本発明の一態様の半導体装置は、室外機 1464 が有するファンの回転を制御するモーターへの電力の供給を制御する回路にも用いることができる。 10

【0323】

なお、図 18 (D) では、室内機と室外機で構成されるセパレート型のエアコンディショナーを例示しているが、室内機の機能と室外機の機能とを 1 つの筐体に有するエアコンディショナーであってもよい。

【0324】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【実施例】

【0325】

本実施例では、酸化物積層のバンド構造について調べた。 20

【0326】

[エネルギーギャップ]

まず、酸化物半導体層に対してイオン注入を異なる条件で行った試料を作製し、それぞれの試料に対してエネルギーギャップを測定した。

【0327】

[試料の作製]

試料の基板として石英基板を用いた。基板表面上に厚さ約 100 nm の酸化物半導体層を成膜した。酸化物半導体層の成膜は、In : Ga : Zn = 1 : 1 : 1 [原子数比] である多結晶のスパッタリングターゲットを用いたスパッタリング法を用いた。 30

【0328】

続いて、酸化物半導体層に対して、イオン注入法を用いてリンの注入を行った。リンの注入は、加速電圧を 10 kV、20 kV、及び 30 kV の 3 条件とし、リンのドーズ量を  $1 \times 10^{12} \text{ cm}^{-2}$ 、 $1 \times 10^{13} \text{ cm}^{-2}$ 、 $1 \times 10^{14} \text{ cm}^{-2}$ 、 $5 \times 10^{14} \text{ cm}^{-2}$ 、 $1 \times 10^{15} \text{ cm}^{-2}$ 、 $3 \times 10^{15} \text{ cm}^{-2}$ 、 $5 \times 10^{15} \text{ cm}^{-2}$  の 7 条件とした。

【0329】

[エリプソメトリーによる評価]

作製した各試料に対して、エリプソメトリー法によりバンドギャップを算出した。ここで、酸化物半導体層としては、基板側からリンのドープされていない第 1 層 (L1) とリンのドープされた第 2 層 (L2) の積層構造を仮定した。イオン注入の条件と第 2 層 (L2) の厚さの関係を図 19 の上段に、またイオン注入の条件と第 2 層 (L2) のバンドギャップの関係を図 19 の下段にそれぞれ示す。 40

【0330】

なお、図 19 の下段の各図中に示す破線は、リンの注入を行っていない試料におけるバンドギャップ (3.22 eV) を示している。

【0331】

図 19 の上段より、加速電圧が高いほど、また注入量が多いほど、リンがドープされ低抵抗化した領域が深さ方向に広がる傾向があることが確認できた。

【0332】

10

20

30

40

50

図19の下段より、注入量が多いほどバンドギャップが小さくなる傾向があることが確認できた。また加速電圧が低いほど深さ方向の分布小さくなり、その結果注入量に対するバンドギャップの変化量が大きい傾向があることが分かった。

### 【0333】

#### [バンド構造]

以下では、上記とは異なる試料を作製し、紫外光電子分光法(UPS)を用いて評価した。

### 【0334】

#### [試料の作製]

試料の基板として、シリコンウェハを用いた。まず、シリコン基板上の酸化膜を希フッ酸により除去したあと、シリコン基板上に厚さ約10nmの第1の酸化物層、及び厚さ約25nmの第1の酸化物半導体層を連続して成膜した。第1の酸化物層の成膜はIn:Ga:Zn = 1:3:2 [原子数比]である多結晶のスパッタリングターゲットを用いたスパッタリング法を用いた。第1の酸化物半導体層の成膜は、上記と同様に行った。すなわち、In:Ga:Zn = 1:1:1である多結晶のスパッタリングターゲットを用い、第1の酸化物層上に厚さ約100nmの酸化物半導体層をスパッタリング法によって形成した。

10

### 【0335】

続いて、第1の酸化物半導体層に対し、イオン注入法によりリンを注入した。リンの注入は、加速電圧を10kVとし、リンのドーズ量を $1 \times 10^{14} \text{ cm}^{-2}$ の条件で行った。

20

### 【0336】

続いて、厚さ約10nmの第2の酸化物半導体層、及び厚さ約10nmの第2の酸化物層を連続して成膜した。第2の酸化物半導体層の成膜は、上記第1の酸化物半導体層の成膜と同様を行い、第2の酸化物層の成膜は、上記第1の酸化物層の成膜と同様に行った。

### 【0337】

#### [UPSによる評価]

作製した試料について、UPSを用いて真空準位と価電子帯上端のエネルギー差(イオン化ポテンシャルともいう。)を測定した。測定は、試料表面からスパッタリング法によりエッチングしながら行うことで、イオン化ポテンシャルの深さ方向の分布を調べた。

### 【0338】

30

図20に、UPSによって求めたスパッタ時間に対する真空準位と価電子帯上端のエネルギー差(EV)を示す。また図20に示す破線は、EVの値から推定した、各膜の境界を示している。スパッタ時間は酸化物積層の膜厚に相当する。

### 【0339】

また図20には、当該EVと、上記エリプソメトリー法によって求めたバンドギャップの値とを用いて算出した真空準位と伝導帯下端のエネルギー差(EC)を示している。ここで、In:Ga:Zn = 1:1:1 [原子数比]である多結晶のスパッタリングターゲットを用いて成膜した膜(IGZO(111)と表記する)についてはバンドギャップを3.22eVとし、In:Ga:Zn = 1:3:2 [原子数比]である多結晶のスパッタリングターゲットを用いて成膜した膜(IGZO(132)と表記する)についてはバンドギャップを3.50eVとした。

40

### 【0340】

図20に示すように、IGZO(111)のEVは、リンの注入の有無に寄らず、ほぼ一定の値(約8.0eV)であった。

### 【0341】

また、図20に示すように、ECはIGZO(132)が最も小さく、次いでIGZO(111)、リンを注入したIGZO(111)の順に大きいことが確認できた。ここでIGZO(132)とIGZO(111)のEC差は約0.28eVであり、IGZO(111)とリンを注入したIGZO(111)のECの差は約0.24eVであった。

### 【0342】

50

以上の結果から、本発明の一態様の酸化物積層が2段階のウェルを有することが確認された。

【符号の説明】

【0 3 4 3】

|         |         |    |

|---------|---------|----|

| 1 0 0   | 基板      |    |

| 1 0 2   | 下地絶縁層   |    |

| 1 0 4   | 酸化物層    |    |

| 1 0 4 A | 酸化物膜    | 10 |

| 1 0 6   | 酸化物半導体層 |    |

| 1 0 6 a | 領域      |    |

| 1 0 6 A | 酸化物半導体膜 |    |

| 1 0 6 b | 領域      |    |

| 1 0 8   | 酸化物半導体層 |    |

| 1 0 8 A | 酸化物半導体膜 |    |

| 1 1 0   | 酸化物層    |    |

| 1 1 0 A | 酸化物膜    |    |

| 1 1 2 a | ソース電極層  |    |

| 1 1 2 b | ドレイン電極層 |    |

| 1 1 4   | ゲート絶縁層  |    |

| 1 1 5   | 酸化物積層   | 20 |

| 1 1 6   | ゲート電極層  |    |

| 1 1 8   | 絶縁層     |    |

| 1 2 0   | 絶縁層     |    |

| 1 2 2 a | 電極層     |    |

| 1 2 2 b | 電極層     |    |

| 1 3 0   | 元素      |    |

| 1 3 1   | 元素      |    |

| 1 3 2   | 酸素      |    |

| 1 5 4   | 酸化物層    |    |

| 1 5 4 A | 酸化物膜    | 30 |

| 1 5 6   | 酸化物半導体層 |    |

| 1 5 6 a | 領域      |    |

| 1 5 6 A | 酸化物半導体膜 |    |

| 1 5 6 b | 領域      |    |

| 1 5 8   | 酸化物半導体層 |    |

| 1 5 8 A | 酸化物半導体膜 |    |

| 1 6 0   | 酸化物層    |    |

| 1 6 0 A | 酸化物膜    |    |

| 1 6 5   | 酸化物積層   |    |

| 2 0 0   | トランジスタ  | 40 |

| 2 1 0   | トランジスタ  |    |

| 2 2 0   | トランジスタ  |    |

| 2 3 0   | トランジスタ  |    |

| 2 4 0   | トランジスタ  |    |

| 2 5 0   | トランジスタ  |    |

| 2 6 0   | トランジスタ  |    |

| 2 7 0   | トランジスタ  |    |

| 2 8 0   | トランジスタ  |    |

| 4 0 0   | 電源回路    |    |

| 4 0 1   | パワースイッチ | 50 |

|         |               |    |

|---------|---------------|----|

| 4 0 2   | パワースイッチ       |    |

| 4 0 3   | 電圧調整部         |    |

| 4 0 4   | 蓄電装置          |    |

| 4 0 5   | 補助電源          |    |

| 4 0 6   | 電圧発生回路        |    |

| 4 0 7   | トランジスタ        |    |

| 4 0 8   | トランジスタ        |    |

| 4 0 9   | トランジスタ        |    |

| 4 1 0   | トランジスタ        |    |

| 4 1 1   | 無線信号入力回路      | 10 |

| 4 1 3   | 制御回路          |    |

| 4 1 4   | 容量素子          |    |

| 4 1 5   | 容量素子          |    |

| 4 1 6   | 電源            |    |

| 4 1 7   | 負荷            |    |

| 5 0 1   | D C D C コンバータ |    |

| 5 0 2   | 容量素子          |    |

| 5 0 3   | トランジスタ        |    |

| 5 0 4   | 制御回路          |    |

| 5 0 5   | ダイオード         | 20 |

| 5 0 6   | コイル           |    |

| 5 0 7   | 容量素子          |    |

| 5 0 8   | 負荷            |    |

| 5 1 1   | D C D C コンバータ |    |

| 5 1 2   | 容量素子          |    |

| 5 1 3   | トランジスタ        |    |

| 5 1 4   | 制御回路          |    |

| 5 1 5   | 変圧器           |    |

| 5 1 6   | ダイオード         |    |

| 5 1 7   | 容量素子          | 30 |

| 5 1 8   | 負荷            |    |

| 6 0 1   | インバータ         |    |

| 6 0 2   | トランジスタ        |    |

| 6 0 3   | トランジスタ        |    |

| 6 0 4   | トランジスタ        |    |

| 6 0 5   | トランジスタ        |    |

| 6 0 6   | 制御回路          |    |

| 1 4 0 0 | 電子レンジ         |    |

| 1 4 0 1 | 筐体            |    |

| 1 4 0 2 | 処理室           | 40 |

| 1 4 0 3 | 表示部           |    |

| 1 4 0 4 | 入力装置          |    |

| 1 4 0 5 | 照射部           |    |

| 1 4 1 0 | 洗濯機           |    |

| 1 4 1 1 | 筐体            |    |

| 1 4 1 2 | 開閉部           |    |

| 1 4 1 3 | 入力装置          |    |

| 1 4 1 4 | 給水口           |    |

| 1 4 5 1 | 筐体            |    |

| 1 4 5 2 | 冷蔵室用扉         | 50 |

- 1 4 5 3 冷凍室用扉

1 4 6 0 室内機

1 4 6 1 筐体

1 4 6 2 送風口

1 4 6 4 室外機

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

(B)

【図14】

(B)

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 手塚 祐朗

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 棚田 一也

(56)参考文献 特開2013-038402(JP,A)

特開2013-038400(JP,A)

特開2011-172217(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786