(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4965974号

(P4965974)

(45) 発行日 平成24年7月4日(2012.7.4)

(24) 登録日 平成24年4月6日(2012.4.6)

(51) Int.Cl.

F 1

**G06F 12/08 (2006.01)**

G06F 12/08 12/08 531B

**G06F 12/10 (2006.01)**

G06F 12/08 531F

G06F 12/08 571

G06F 12/08 585

G06F 12/08 507F

請求項の数 10 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2006-307700 (P2006-307700)

(22) 出願日

平成18年11月14日 (2006.11.14)

(65) 公開番号

特開2008-123333 (P2008-123333A)

(43) 公開日

平成20年5月29日 (2008.5.29)

審査請求日

平成21年11月10日 (2009.11.10)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753 番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 芝原 真一

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 高田 雅士

東京都千代田区丸の内一丁目6番6号 株式会社日立製作所内

(72) 発明者 亀井 達也

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

キャッシュコヒーレンシ制御を行う半導体集積回路装置であって、複数の C P U コアと、スヌープコントローラと、を有し、前記複数の C P U コアは夫々中央処理装置と、キャッシュメモリと、キャッシュコントローラと、バスインターフェースコントローラと、を有し、前記スヌープコントローラは前記複数の C P U コア夫々のキャッシュメモリの情報を夫々複製した複数の複製タグを有し、前記キャッシュコントローラは、前記中央処理装置から、命令あるいはデータアクセス要求を受け取り、所望のデータをアクセスするために前記キャッシュメモリの制御あるいは前記バスインターフェースコントローラへのアクセス要求を行うものであり、前記バスインターフェースコントローラは前記アクセス要求を受け取り、所望のデータをアクセス制御するものであり、前記スヌープコントローラは、前記キャッシュコントローラから通知される情報を受け取り、キャッシュコヒーレンシの制御を行うものであり、前記キャッシュコントローラは、前記中央処理装置が、メモリ割り付けキャッシュアクセスによって前記キャッシュメモリの登録内容を更新した際に、前記キャッシュメモリの登録内容が更新されたことを検知する手段を有し、前記スヌープコントローラに前記キャッシュメモリの登録内容が更新されたことを通知する手段を有し、

10

20

前記スヌープコントローラは、前記キャッシュメモリの登録内容が更新されたことが通知されると、前記キャッシュメモリの更新された登録内容に従って前記複製タグを更新し

前記複数のCPUコアは夫々、前記キャッシュメモリの登録情報を更新するときに対応する前記複製タグを参照し、コピーレンシ制御を行うことを特徴とする半導体集積回路装置。

#### 【請求項2】

請求項1記載の半導体集積回路装置において、

前記スヌープコントローラは、

キャッシュクリアを行うキャッシュ操作命令の実行時に前記複製タグをクリアすることを特徴とする半導体集積回路装置。 10

#### 【請求項3】

請求項1または2記載の半導体集積回路装置において、

前記複数のCPUコアのうち、少なくとも1個以上のCPUコアはデータを共有しないアドレス領域を有し、

前記キャッシュコントローラは、

仮想アドレスを物理アドレスに変換するアドレス変換テーブルを備え、

前記アドレス変換テーブルは、

コピーレンシが有効か無効かを示す選択情報を有し、前記データを共有しないアドレス領域に対してコピーレンシを無効とするものであり。 20

前記キャッシュコントローラは、

前記アドレス変換テーブルの選択情報を参照し、コピーレンシ有効となっている際に前記キャッシュメモリの登録内容が更新されたことを前記スヌープコントローラに通知し、コピーレンシ制御を行うことを特徴とする半導体集積回路装置。

#### 【請求項4】

請求項1または2記載の半導体集積回路装置において、

前記複数のCPUコアのうち少なくとも1個以上のCPUコアはデータを共有しないアドレス領域を有し、

前記キャッシュコントローラは、

コピーレンシが有効か無効かを示す選択情報を格納するレジスタを有し、前記データを共有しないアドレス領域に対してコピーレンシを無効とするものであり。 30

アドレスデコード時に前記レジスタの選択情報を参照し、コピーレンシ有効となっている際に前記キャッシュメモリの登録内容が更新されたことを前記スヌープコントローラに通知し、コピーレンシ制御を行うことを特徴とする半導体集積回路装置。

#### 【請求項5】

請求項1～4のいずれか1項に記載の半導体集積回路装置において、

前記キャッシュコントローラは、

ライトスルーとコピーバックとを混在して使用するか否かを設定する設定レジスタを備えることを特徴とする半導体集積回路装置。

#### 【請求項6】

請求項5記載の半導体集積回路装置において、

前記キャッシュコントローラは、

ライトスルー設定時にキャッシュライトミスを起こした際に前記設定レジスタがライトスルーとコピーバックとを混在に設定されている場合、前記中央処理装置にダーティデータが存在することを考慮したスヌープ処理とライト処理を行うコマンドを発行し、

ライトスルー設定時にキャッシュライトミスを起こした際に前記設定レジスタが非混在に設定されている場合、前記中央処理装置がダーティデータを所持していないことを考慮したスヌープ処理とライト処理を行うコマンドを発行することを特徴とする半導体集積回路装置。

#### 【請求項7】

10

20

30

40

50

請求項 5 または 6 記載の半導体集積回路装置において、

前記キャッシュコントローラは、

ライトスルー設定時にキャッシュリードミスを起こした際に前記設定レジスタがライトスルーとコピーバックとを混在に設定されている場合、前記中央処理装置にデータが存在することを考慮したコマンドを発行し、

ライトスルー設定時にキャッシュリードミスを起こした際に前記設定レジスタが非混在に設定されている場合、前記中央処理装置にデータが存在しないことを考慮したコマンドを発行し、要求が受け付けられたと同時にフィル要求を出力することを発行することを特徴とする半導体集積回路装置。

#### 【請求項 8】

10

請求項 1 ~ 7 のいずれか 1 項に記載の半導体集積回路装置において、

前記キャッシュコントローラは、

前記中央処理装置から任意のアドレスのデータを有するキャッシュメモリの情報を操作するためのキャッシュ操作命令を実行する要求を受け取ると、前記任意のアドレスのデータを有するキャッシュメモリを有する前記 CPU コア内の中央処理装置に前記任意のアドレスのデータを有するキャッシュメモリの情報を操作するためのキャッシュ操作を行うことを前記スヌープコントローラに要求するスヌープバス要求を発生させることを特徴とする半導体集積回路装置。

#### 【請求項 9】

20

請求項 1 ~ 7 のいずれか 1 項に記載の半導体集積回路装置において、

前記キャッシュコントローラは、

前記中央処理装置から任意のアドレス範囲のデータを有するキャッシュメモリの情報をメモリに反映させるためのキャッシュ操作命令を実行する要求を受け取ると、前記任意のアドレス範囲のデータを有するキャッシュメモリを有する前記 CPU コア内の中央処理装置に前記任意のアドレス範囲のデータを有するキャッシュメモリの情報をメモリに反映させるためのキャッシュ操作を行うことを前記スヌープコントローラに要求することを特徴とする半導体集積回路装置。

#### 【請求項 10】

請求項 1 ~ 9 のいずれか 1 項に記載の半導体集積回路装置において、

前記スヌープコントローラは、

30

任意の 1 つの前記中央処理装置から、すべての前記複製タグを参照するアドレスマップ、および自己の前記中央処理装置に対応する前記複製タグを参照するアドレスマップを有し、

前記キャッシュコントローラは、

前記アドレスマップを参照可能であり、

前記スヌープコントローラは、

アクセス要求が発生した際にアドレスコードによってすべての前記複製タグを参照するアドレスマップであるか、または自己の前記中央処理装置に対応する前記複製タグであるかを判断することを特徴とする半導体集積回路装置。

#### 【発明の詳細な説明】

40

#### 【技術分野】

#### 【0001】

本発明は、複数の中央処理装置を備えた半導体集積回路装置におけるキャッシュアクセス技術に関し、特に、SMP (Symmetric Multiple Process or) 構造の半導体集積回路装置によるコピーレンシ制御に有効な技術に関する。

#### 【背景技術】

#### 【0002】

複数の CPU が処理を分担する、いわゆる SMP 構造の半導体集積回路装置では、CPU 間のキャッシュコピーレンシを保つ手段として、各 CPU のキャッシュ登録情報を格納する複製アドレスアレイ（複製タグ）と各 CPU から他の CPU のキャッシュ登録情報を

50

スヌープするための共有バス（以下、スヌープバスという）が存在するものが知られている。各CPUは、コヒーレンシ有効／無効を選択することができる。

【0003】

SMP構成の半導体集積回路装置におけるコヒーレンシ（共有）制御では、該コヒーレンシ制御に必要なのは真に複数のCPU間でデータ共有している領域のみである。よって、コヒーレンシ制御が不良な領域（データ共有しない領域）に対して、コヒーレンシ制御を行うことにより、性能が低下してしまうことになる。

【0004】

さらに、SMP構成の半導体集積回路装置では、プロセス毎に同一物理領域をライトスルーやコピーバックで使用したい場合があり、たとえば、プロトコルの混在を可能とする技術として、ライトスルーやコピーバックとの区別をスヌープバスのステータス信号に追加することにより、スヌープ処理の内容を選択するものが知られている（特許文献1参照）。

10

【0005】

また、SMP構成の半導体集積回路装置は、一般に、プロセスを実行するCPUの割り当てをOS（Operating System）が自動的に振り分けている。

【0006】

さらに、SMP構成の半導体集積回路装置をデバッグする際、すべてのCPUのキャッシュ登録状況を見るためには、全CPUのプログラム実行を一時停止した後、CPU毎にキャッシュ操作を行っている。

20

【特許文献1】特開平04-123151号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

ところが、上記のようなSMP構成の半導体集積回路装置では、次のような問題点があることが本発明者により見い出された。

【0008】

CPU間のキャッシュコヒーレンシを保つ技術において、複製アドレスアレイ（複製タグ）への登録は、各CPUがキャッシュミスした際に起こるスヌープバス要求のタイミングにて行われる。スヌープバス要求後のスヌープ処理を正しく行うためには、各CPUのキャッシュ登録情報と複製アドレスアレイ（複製タグ）の登録情報が一致している必要がある。

30

【0009】

また、各CPUのキャッシュ登録内容はメモリ割り付けキャッシュアクセスによって参照／更新可能な場合、メモリ割り付けキャッシュアクセスにより登録内容がクリア可能になる。クリアされた場合、複製アドレスアレイ（複製タグ）も情報一致させるために、複製アドレスアレイ（複製タグ）の内容をクリアしなければならないが、複製アドレスアレイ（複製タグ）をクリアする手段を有していない。

【0010】

そのため、キャッシュ格納情報を誤認識し、コヒーレンシ制御が正常に行われない可能性がある。

40

【0011】

また、シングルコア構成のソフトウェアを流用した場合、複製アドレスアレイ（複製タグ）をクリアする処理の追加が必要となってしまい、ソフトウェアの工数の増加、およびコスト向上などが発生してしまう。

【0012】

次に、コヒーレンシの有効／無効を選択する技術では、コヒーレンシの有効を選択した場合に、非共有領域に対してもスヌープ処理が発生してしまい、半導体集積回路装置の性能が劣化してしまうという問題がある。

【0013】

50

ライトルーとコピーバックとの区別をスヌープバスのステータス信号に追加する技術では、コピーレンシプロトコルが混在しないときでも、回避処理が発生してしまい、スヌープ処理性能が低下してしまうという問題がある。

#### 【0014】

プロセスを実行するCPUの割り当てをOSが振り分ける場合、コンテクストスイッチなどでプロセス実行が中断された際に、プロセスが再開した場合に同じCPUで行われない場合がある。

#### 【0015】

実行中断時点でデータがキャッシュに残存しているにも関わらず、他のCPUで実行再開される場合、再開以降に実行する命令の中にキャッシュ操作命令（指定したアドレスが登録されているキャッシュライン操作）があると、所望のキャッシュ操作ができない場合がある。10

#### 【0016】

この場合、キャッシュ操作命令実行後にDMA転送を行うプログラムを書いてしまうと、データを書き戻せないままDMA転送を行ってしまい、期待通りの動作にならない恐れがある。

#### 【0017】

さらに、他のCPUのキャッシュを操作する場合には、CPU間割り込みを用いて全CPUのプロセス実行を中断し、CPUそれぞれでキャッシュ操作命令を実行する必要があり、キャッシュ操作に手間が掛かってしまうという問題がある。20

#### 【0018】

また、デバッグの際に、すべてのCPUのキャッシュ登録状況を見る場合、前述したように、全CPUのプログラム実行を一時停止した後、CPU毎にキャッシュ操作を行わなければならず、他のCPUの割り込み要求、キャッシュ読み出し、共有領域への結果書き込み、および共有領域からの結果読み出しなどの処理が必要となり、デバッグ効率が低下してしまうという問題がある。

#### 【0019】

本発明の目的は、SMP構成の半導体集積回路装置において、キャッシュコピーレンシ制御の異常を防止し、処理性能を向上させる技術を提供することにある。

#### 【0020】

また、本発明の他の目的は、コピーレンシプロトコルによる性能劣化を防止し、ソフトウェア、およびデバッグの効率を向上させる技術を提供することにある。30

#### 【0021】

本発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0022】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0023】

本発明による半導体集積回路装置は、アクセス要求を受け取り、所望のデータをアクセスするバスインターフェースコントローラと、中央処理装置と、該中央処理装置からの命令、データアクセス要求を受け取り、所望のデータをアクセスするためにキャッシュ操作やバスインターフェースコントローラにアクセス要求を行うキャッシュコントローラとを備えた複数のCPUコアと、キャッシュミスが発生した際にキャッシュコントローラから発行されるスヌープ要求を受け取り、コピーレンシ制御を行うスヌープコントローラとを有した半導体集積回路装置であって、キャッシュコントローラは、中央処理装置が、メモリ割り付けキャッシュアクセスによって登録内容をクリアした際に、各中央処理装置のキャッシュ登録情報を格納する複製アドレスアレイ（複製タグ）の内容をクリアする要求を発行し、スヌープコントローラは、キャッシュコントローラから発行されたスヌープバス要求4050

を受理すると、複製アドレスアレイ（複製タグ）を参照し、スヌープバス要求に従って複製タグを更新するものである。

【0024】

また、本願のその他の発明の概要を簡単に示す。

【0025】

本発明による半導体集積回路装置は、前記スヌープコントローラが、キャッシングクリアを行うキャッシング操作命令の実行時に複製アドレスアレイ（複製タグ）をクリアするものである。

【0026】

また、本発明の半導体集積回路装置は、前記キャッシングコントローラが、仮想アドレスを物理アドレスに変換するアドレス変換テーブルを備え、該アドレス変換テーブルは、コヒーレンシが有効か無効かを示す選択情報を有し、キャッシングコントローラは、アドレス変換テーブルの選択情報を参照し、コヒーレンシ有効となっている際にスヌープコントローラにスヌープバス処理を発生させ、コヒーレンシ制御を行うものである。 10

【0027】

さらに、本発明の半導体集積回路装置は、前記キャッシングコントローラが、コヒーレンシが有効か無効かを示す選択情報を格納するレジスタを有し、アドレスデコード時にレジスタの選択情報を参照し、コヒーレンシ有効となっている際にスヌープコントローラにスヌープバス処理を発生させ、コヒーレンシ制御を行うものである。

【0028】

また、本発明の半導体集積回路装置は、前記キャッシングコントローラが、ライトスルーとコピーバックとを混在して使用するか否かを設定する設定レジスタを備え、スヌープバス要求が必要の際に、該設定レジスタを参照してバスコマンドを発行するものである。 20

【0029】

さらに、本発明の半導体集積回路装置は、前記キャッシングコントローラが、ライトスルー設定時にキャッシングライトミスを起こした際に設定レジスタが混在に設定されている場合、中央処理装置にダーティデータが存在することを考慮したスヌープ処理とライト処理を行うコマンドを発行し、ライトスルー設定時にキャッシングライトミスを起こした際に設定レジスタが非混在に設定されている場合、中央処理装置がダーティデータを所持していないことを考慮したスヌープ処理とライト処理を行うコマンドを発行するものである。 30

【0030】

また、本発明の半導体集積回路装置は、前記キャッシングコントローラが、キャッシングリードミスを起こした際に設定レジスタが混在に設定されている場合、中央処理装置にダーティデータが存在することを考慮したコマンドを発行し、中央処理装置のスヌープ要求完了まで待機し、キャッシングリードミスを起こした際に設定レジスタが非混在に設定されている場合、中央処理装置にダーティデータが存在しないことを考慮したコマンドを発行し、要求が受け付けられたと同時にフィル要求を出力することを発行するものである。

【0031】

さらに、本発明の半導体集積回路装置は、前記キャッシングコントローラが、中央処理装置からキャッシング操作命令を実行する要求を受け取ると、任意のアドレスを有する中央処理装置にキャッシング操作を行うことを要求するスヌープバス要求を発生させるものである。 40

【0032】

また、本発明の半導体集積回路装置は、前記キャッシングコントローラが、中央処理装置からキャッシング操作命令を実行する要求を受け取ると、任意のアドレス範囲を有する中央処理装置にキャッシング操作を行うことを要求するスヌープバス要求を発生させるものである。

【0033】

さらに、本発明の半導体集積回路装置は、前記スヌープコントローラが、任意の1つの中央処理装置から、すべての中央処理装置の複製アドレスアレイ（複製タグ）を参照する 50

アドレスマップ、および1つの中央処理装置の複製アドレスアレイ（複製タグ）を参照するアドレスマップを有し、前記キャッシュコントローラは、アドレスマップを参照可能であり、スヌープコントローラは、アクセス要求が発生した際にアドレスコードによってすべての中央処理装置の複製アドレスアレイ（複製タグ）を参照するアドレスマップであるか、または1つの中央処理装置の複製アドレスアレイ（複製タグ）を参照するアドレスマップであるかを判断するものである。

**【発明の効果】**

**【0034】**

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

10

**【0035】**

（1）複製アドレスアレイ（複製タグ）に関係なく、キャッシングの登録内容をクリアすることが可能となり、キャッシングコヒーレンシ制御を良好に行うことができる。

**【0036】**

（2）非共有領域に対するコヒーレンシ制御のペナルティをなくすことができるので、半導体集積回路装置の性能を向上させることができる。

**【0037】**

（3）ライトスルーコピーバックを使用することが可能となり、ソフトウェアなどの開発効率を向上させることができる。

20

**【0038】**

（4）プロセスマイグレーションを考慮したキャッシング操作を容易に実施することができる。

**【0039】**

（5）1つのCPUからすべてのCPUの複製アドレスアレイ（複製タグ）を参照することができるので、デバッグを容易に、効率よく行うことができる。

**【発明を実施するための最良の形態】**

**【0040】**

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

30

**【0041】**

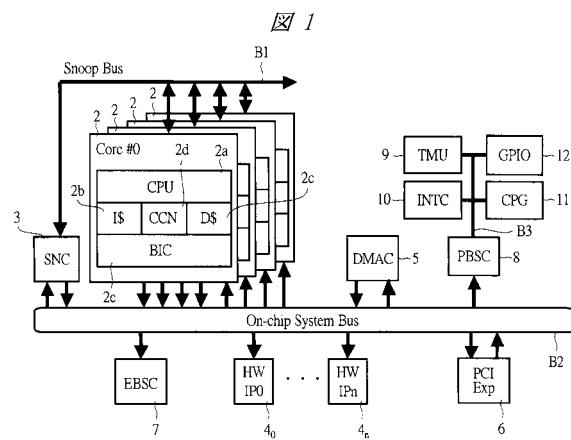

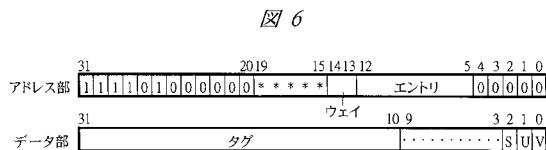

（実施の形態1）

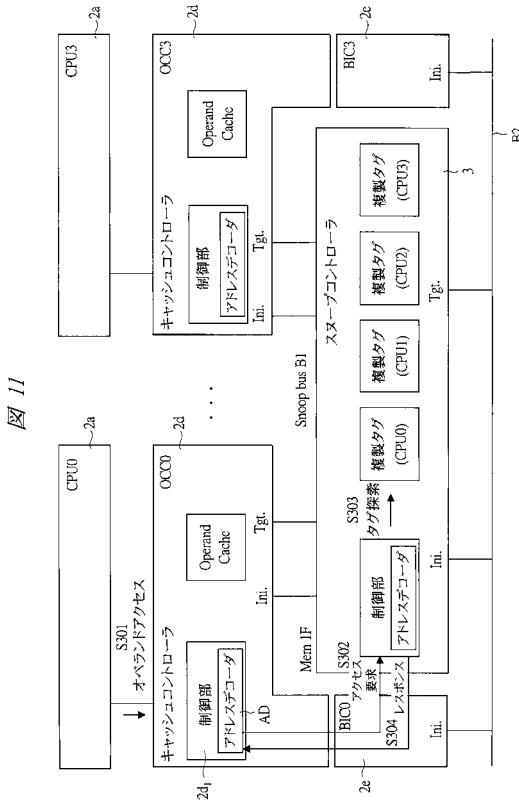

図1は、本発明の実施の形態1による半導体集積回路装置のブロック図、図2は、図1の半導体集積回路装置で用いられるオペランドキャッシュの構成例を示す説明図、図3は、図1の半導体集積回路装置で用いられる複製アドレスアレイ（複製タグ）の構成例を示す説明図、図4は、図1の半導体集積回路装置による通常のスヌープ処理の一例を示す説明図、図5は、図1の半導体集積回路装置によるスヌープ処理において、メモリ割り付けキャッシングアクセス結果と複製アドレスアレイ（複製タグ）の同期を行う際の一例を示す説明図、図6は、図1の半導体集積回路装置に用いられるオペランドキャッシュ／アドレスアレイの構成を示す説明図である。

40

**【0042】**

本実施の形態1において、半導体集積回路装置1は、SMP構成からなる。半導体集積回路装置1は、図1に示すように、複数のCPUコア2、スヌープコントローラ（SNC）3、ハードウェアIP（HW IPn）4<sub>0</sub>～4<sub>n</sub>、DMAコントローラ（DMAC）5、チップ外部高速転送インタフェース（PCI Exp）6、外部メモリインタフェース（EBS C）7、周辺モジュールバスコントローラ（P B S C）8、および周辺モジュールであるタイマ（TMU）9、割り込みコントローラ（INTC）10、クロックパルス生成器（CPG）11、汎用I/O（Input/Output）ポート（GPIO）12から構成されている。

**【0043】**

50

これら C P U コア 2 とスヌープコントローラ 3 とは、スヌープバス B 1 を介して相互に接続されている。C P U コア 2 、スヌープコントローラ 3 、ハードウェア I P 4<sub>0</sub> ~ 4<sub>n</sub> 、D M A コントローラ 5 、チップ外部高速転送インターフェース 6 、外部メモリインターフェース 7 、ならびに周辺モジュールバスコントローラ ( P B S C ) 8 は、オンチップシステムバス B 2 を介して相互に接続されている。

#### 【 0 0 4 4 】

また、周辺モジュールバスコントローラ 8 、タイマ 9 、割り込みコントローラ 1 0 、クロックパルス生成器 1 1 、ならびに汎用 I / O ポート 1 2 は、周辺モジュールバス B 3 を介して相互に接続されている。

#### 【 0 0 4 5 】

C P U コア 2 は、C P U 2 a 、命令キャッシュ ( I \$ ) 2 b 、データキャッシュ ( D \$ ) 2 c 、キャッシュコントローラ ( C C N ) 2 d 、ならびにバスインターフェースコントローラ ( B I C ) 2 e から構成されている。

#### 【 0 0 4 6 】

C P U 2 a は、メモリに記憶されたプログラムを定義された命令単位で読み、必要なデータを取り込みながら、演算・処理を実行する。命令キャッシュ 2 b は、C P U 2 a からの命令アクセスサイクルを短縮させるために、C P U コア 2 外に格納された命令を一時的に格納する。

#### 【 0 0 4 7 】

データキャッシュ 2 c は、C P U 2 a からのデータアクセスサイクルを短縮させるため、C P U コア 2 外に格納された命令を一時的に格納する。キャッシュコントローラ 2 d は、C P U 2 a からの命令、データアクセス要求を受け取り、所望のデータをアクセスするために、キャッシュ操作やバスインターフェースコントローラ 2 e にアクセス要求を行う。

#### 【 0 0 4 8 】

バスインターフェースコントローラ 2 e は、キャッシュコントローラ 2 d からアクセス要求を受け取り、オンチップシステムバス B 2 経由で所望のデータをアクセスする。

#### 【 0 0 4 9 】

また、スヌープコントローラ 3 は、キャッシュミスが発生した際にキャッシュコントローラ 2 d から発行されるスヌープ要求を受け取り、コヒーレンシ制御を行う。ハードウェア I P 4<sub>0</sub> ~ 4<sub>n</sub> は、ハードウェアアクセラレータなど、C P U 2 a の負担軽減化の為、アルゴリズムが確定したプログラムをハードウェア化してオンチップシステムバス B 2 に接続されたモジュールからなる。

#### 【 0 0 5 0 】

D M A コントローラ 5 は、C P U 2 a を介さずにメモリ間のデータ転送を制御する。チップ外部高速転送インターフェース 6 は、チップ間を高速データ転送するためのインターフェースからなる。

#### 【 0 0 5 1 】

外部メモリインターフェース 7 は、オンチップシステムバス B 2 経由からのアクセス要求を受け取り、チップ外部に接続される装置へのアクセス要求を行う。周辺モジュールバスコントローラ 8 は、周辺モジュールをアクセスする。

#### 【 0 0 5 2 】

タイマ 9 は、所望の時間設定をし、ある時間に到達すると、割り込みコントローラ 1 0 に割り込み要求を起こす。割り込みコントローラ 1 0 は、周辺モジュール / チップ外部から割り込み要求を受け付け、C P U 2 a に割り込み要求を行う。

#### 【 0 0 5 3 】

クロックパルス生成器 1 1 は、各モジュールにクロックを供給する。汎用 I / O ポート 1 2 は、チップ外部に固定信号を出力したり、チップ内部情報を出力するインターフェースである。

#### 【 0 0 5 4 】

半導体集積回路装置 1 では、複数の C P U コア 2 がスヌープ処理をスヌープバス B 1 か

10

20

30

40

50

らスヌープコントローラ3を介して行うことで、キャッシュコヒーレンシを保っている。

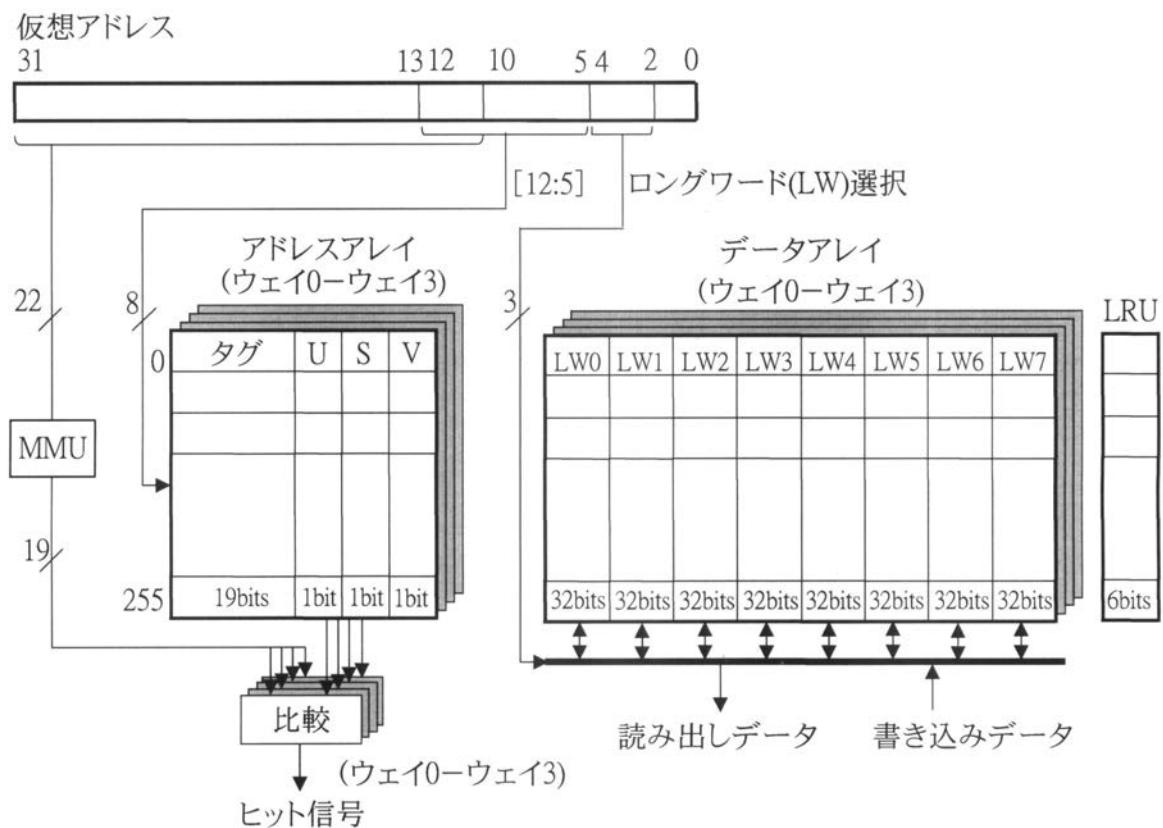

#### 【0055】

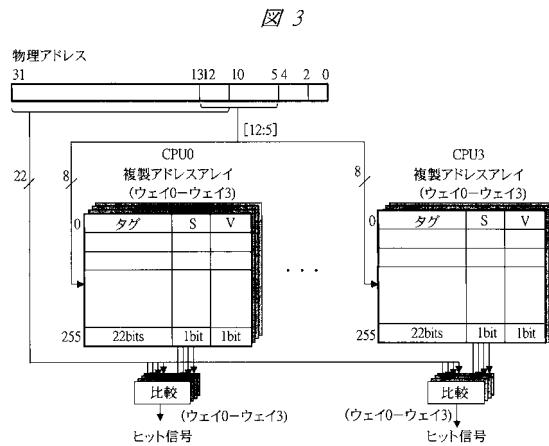

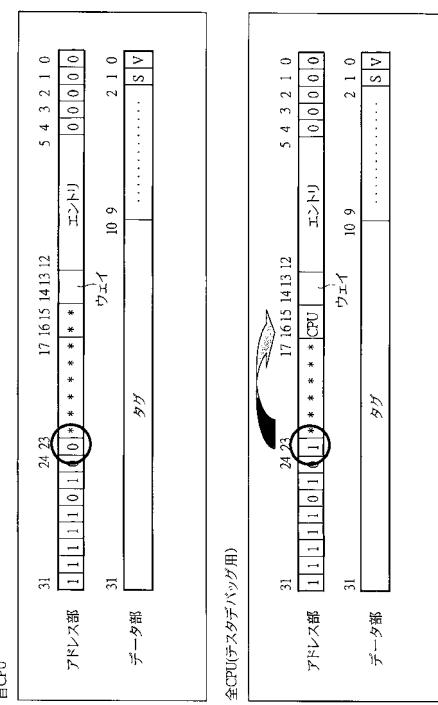

キャッシュは、図2に示すように、アドレスアレイとデータアレイに分類される。アドレスアレイは、アドレスを示すアドレスタグ、データが有効か無効かを示す有効ビット( V )、他のCPU2aと同じデータを有することを示す共有ビット( S )、キャッシュの転送されたデータが転送元と異なることを示すダーティビット( U )により構成されており、データアレイはアドレスタグに指定された領域のデータが保存される。

#### 【0056】

複製アドレスアレイ(複製タグ)は、図3に示すように、アドレスタグ、有効ビット( V )、共有ビット( S )により構成されている。また、各CPU2aにおけるアドレスアレイと複製アドレスアレイ(複製タグ)との内容は一致する。10

#### 【0057】

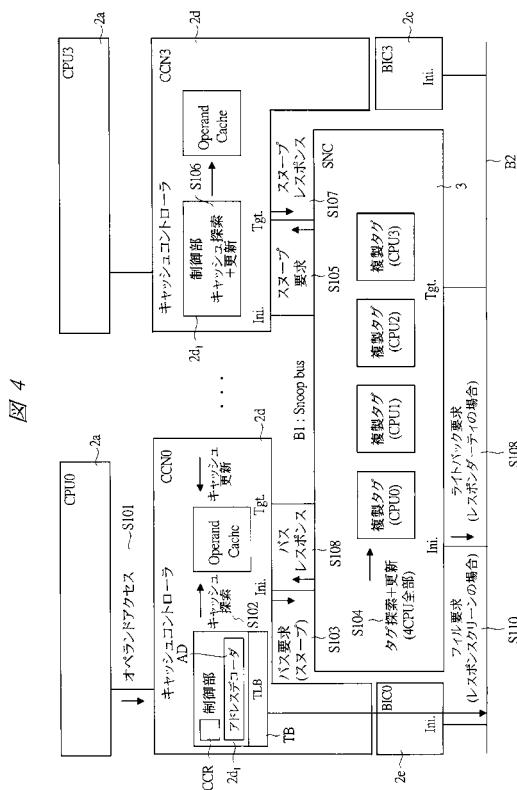

ここで、通常のスヌープ処理について説明する。

#### 【0058】

図4は、CPUコア2におけるCPU2a、キャッシュコントローラ2d、およびスヌープコントローラ3における通常のスヌープ処理の一例を示す説明図である。

#### 【0059】

スヌープ処理は、まず、CPU2aからのオペランド要求をキャッシュコントローラ2dが受理(ステップS101)し、キャッシュ探索(ステップS102)後にキャッシュコヒーレンシ動作が必要になった場合(たとえば、キャッシュミスにより他CPU2aのキャッシュ状況確認が必要になるとき)、スヌープコントローラ3にスヌープバス要求(ステップS103)を送る。20

#### 【0060】

スヌープバス要求受理後に複製アドレスアレイ(複製タグ)(ステップS104)を引き、各CPU2aにコヒーレンシを保つためのスヌープ要求を発行するか(ステップS105)どうかを判定する。

#### 【0061】

各CPU2aはスヌープ要求を受け、キャッシュ探索を行った後(ステップS106)、レスポンス(ステップS107)を返す。バス要求発行元はレスポンスを受け取った(ステップS108)後に、キャッシュ更新し(ステップS109)、他のCPU2aに最新データがない場合は、バスインターフェースコントローラB2経由で実デバイスにアクセス(ステップS110)を行う。30

#### 【0062】

また、最新データがあった場合は、スヌープコントローラ3から実デバイスにライトバック(ステップS108)と共にキャッシュを更新する。

#### 【0063】

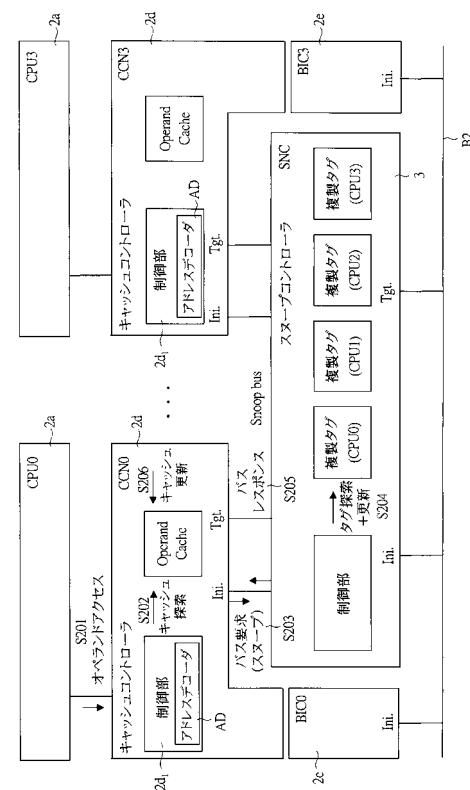

次に、本実施の形態における半導体集積回路装置1の動作について説明する。

#### 【0064】

図5は、CPUコア2におけるCPU2a、キャッシュコントローラ2d、およびスヌープコントローラ3におけるスヌープ処理において、メモリ割り付けキャッシュアクセス結果と複製アドレスアレイ(複製タグ)の同期を行う際の一例を示す説明図である。40

#### 【0065】

まず、メモリ割り付けキャッシュアクセスは、CPU2aからアクセス要求をキャッシュコントローラが受理した後(ステップS201)、キャッシュコントローラ2dのアドレスデコーダADで検知される。

#### 【0066】

キャッシュコントローラ2dに設けられた制御部2d1は、アクセス要求(図6によってアクセスすべきウェイ・エントリが決定する)に従ってキャッシュをアクセスする(ステップS202)。

#### 【0067】

これによって読み出されたキャッシュステータスと更新データとを比較し、有効ビットが有効から無効に変化した場合は登録内容をクリアしたと判断される。クリアと判断した後、「複製アドレスアレイ（複製タグ）内容をクリア」するスヌープバス要求を発行する（ステップS203）。

#### 【0068】

スヌープコントローラ3は、スヌープバス要求受理後に複製アドレスアレイ（複製タグ）を引き（ステップS204）、スヌープバス要求に従って複製アドレスアレイ（複製タグ）を更新する。更新が完了した後、レスポンスを返し（ステップS205）、アドレスアレイの更新を行う（ステップS206）。これにより、キャッシュと複製アドレスアレイ（複製タグ）の登録内容が同期化される。

10

#### 【0069】

それにより、本実施の形態1によれば、複製アドレスアレイ（複製タグ）を気にする必要なく、キャッシュの登録内容をクリアすることが可能となり、キャッシュコヒーレンシ制御を良好に行うことができる。

#### 【0070】

また、本実施の形態1では、メモリ割り付けキャッシュアクセスにおいて、複製アドレスアレイ（複製タグ）を同期する場合について記載したが、たとえば、キャッシュクリアを行うキャッシュ操作命令実行時においても複製アドレスアレイ（複製タグ）をクリアする機能を有するようにしてもよい。

20

#### 【0071】

この場合、命令デコード時にキャッシュ操作命令を検知し、キャッシュコントローラにおいて複製アドレスアレイ（複製タグ）をクリアするスヌープバス要求を発行する。キャッシュ構成は命令・キャッシュ分離型でも命令・キャッシュ一体型のいずれでもあってよい。

#### 【0072】

##### （実施の形態2）

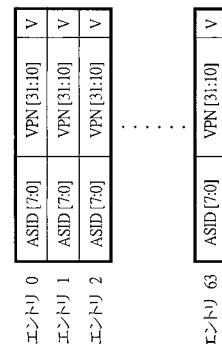

図7は、本発明の実施の形態2によるコヒーレンシ有効／無効選択情報が追加されたアドレス変換テーブルの構成例を示す説明図である。

#### 【0073】

本実施の形態2において、図1の半導体集積回路装置1は、非共有領域に対してコヒーレンシ制御を行わない機能を有している。

30

#### 【0074】

この場合、キャッシュコントローラ2dのアドレスデコーダADにおいて、コヒーレンシ有効／無効選択情報を参照し、コヒーレンシ有効のときのみスヌープバス要求を発生させる。

#### 【0075】

コヒーレンシ有効／無効選択情報は、図7に示すように、アドレス変換テーブル（TLB : Transition Looks side Buffer）TBに格納される。仮想アドレスを物理アドレスに変換する際にアドレス変換テーブルTBを引くため、その際に選択情報も同時に参照することができる。

40

#### 【0076】

アドレス変換テーブルTBは、プロセス番号ASID(Address Space Identifier)、仮想アドレスVPN(Virtual Page Number)、有効ビットVを索引とすると、物理アドレスPPN(Physical Page Number)、コヒーレンシ無効NCC(Not Cache Coherency Mode)、複数プロセス共有許可SH(SHare)、キャッシュブル領域指定C(Cacheable)、ダーティ状態D(Dirty)、コヒーレンシプロトコルWT(Write Through)情報がそれぞれ読み出せることになる。このアドレス変換テーブルTBへの情報登録は、ソフトウェアにて行う。

#### 【0077】

50

それにより、本実施の形態 2 では、非共有領域に対するコヒーレンシ制御のペナルティを減少させることができるので、半導体集積回路装置 1 における性能を向上させることができる。

#### 【 0 0 7 8 】

また、本実施の形態 2 においては、アドレス変換テーブル T B にコヒーレンシ有効 / 無効選択情報を備えた構成としたが、たとえば、コヒーレンシ有効 / 無効の選択情報を適当な領域毎に設定できるレジスタに設定するようにしてもよい。ここでは、そのレジスタとして、キャッシュコントローラ 2 d の制御部 2 d 1 に備えられている制御レジスタ C C R ( 図 4 参照 ) を用いる。

#### 【 0 0 7 9 】

この場合には、一定領域 ( P 0 , P 1 ... ) 每にコヒーレンシ制御を行うか否かを、図 8 に示す制御レジスタ C C R 内のビットに指定する。この指定ビットをアドレスコード時に参照することによって、コヒーレンシ制御を選択することができる。

#### 【 0 0 8 0 】

##### ( 実施の形態 3 )

図 9 は、本発明の実施の形態 3 による制御レジスタにおけるコヒーレンシプロトコル混在ビットの説明図である。

#### 【 0 0 8 1 】

本実施の形態 3 において、図 1 の半導体集積回路装置 1 は、コヒーレンシプロトコル混在 / 非混在を設定するレジスタとプロトコル混在に対応する機構を有している。

#### 【 0 0 8 2 】

この場合、コヒーレンシプロトコル混在 / 非混在を設定するレジスタは、たとえば、キャッシュコントローラ 2 d の制御部 2 d 1 に備えられている制御レジスタ C C R ( 図 4 ) を用いる。

#### 【 0 0 8 3 】

キャッシュコントローラ 2 d によるキャッシュ操作中に、スヌープバス要求が必要になった場合、図 9 に示す制御レジスタ C C R のコヒーレンシプロトコル混在ビット M C P を参照することにより、状況に対応したバスコマンドを発行する。

#### 【 0 0 8 4 】

制御レジスタ C C R は、メモリ割り付けアクセスにより制御することができる ( 例 : アドレス 0 x f f 0 0 0 0 1 c 番地 ) 。

#### 【 0 0 8 5 】

ライトスルー設定時にキャッシュライトミスを起こしたとき、混在の場合は、他 C P U 2 a にダーティデータが存在することを考慮したスヌープ処理とライト処理を行うコマンド B U S W T \_ S N W ( B U S W r i t e T h r o u g h w i t h S N o o p W a i t ) を発行し、非混在の場合には、他 C P U 2 a がダーティデータを所持していないことを考慮したスヌープ処理とライト処理を行うコマンド B U S W T ( B U S W r i t e T h r o u g h ) を発行する。

#### 【 0 0 8 6 】

また、キャッシュリードミスを起こしたとき、混在の場合は、他 C P U 2 a にダーティデータが存在することを考慮したコマンド B U S R D ( B U S R e a d w i t h S N o o p W a i t ) を発行し、他 C P U 2 a のスヌープ要求完了まで待つ ( これは、ダーティデータがレスポンスとして返り、キャッシュファイルするからである ) 。

#### 【 0 0 8 7 】

非混在の場合は、他 C P U 2 a にダーティデータが存在しないことを考慮したコマンド B U S R D ( B U S R e a d ) を発行し、要求が受け付けられたと同時にオンチップシステムバス B 2 ヘファイル要求を出す。

#### 【 0 0 8 8 】

これにより、全 C P U ライトスルー設定時にキャッシュリードミスを起こし、スヌープバス要求を行ってレスポンスを待つという動作が不要となる。また、レスポンスを待つ場

10

20

30

40

50

合、レスポンスを待っても、データが返って来ないと無駄な待ちになる。

**【0089】**

常にプロトコル混在を考慮したプロセッサの場合、このような無駄な待ち時間が多く発生してしまうことになるが、本実施の形態3のように、制御レジスタCCRのコヒーレンシプロトコル混在ビットMCPを参照することにより、無駄な待ちを減少させることができる。

**【0090】**

それにより、本実施の形態3によれば、プロセス毎に同一物理領域をライトスルーとコピーバックで使用することが可能となり、ソフトウェアなどの開発効率を向上させることができる。

10

**【0091】**

また、コヒーレンシプロトコル混在／非混在の制御は、たとえば、アドレス変換テーブルTBのエントリ毎、あるいは共有領域毎に制御を可変とするようにしてもよい。

**【0092】**

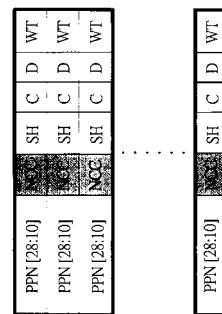

(実施の形態4)

図10は、本発明の実施の形態4によるプロセスマイグレーションを考慮したキャッシュ操作命令の処理例を示す説明図である。

**【0093】**

本実施の形態4において、図1の半導体集積回路装置1は、キャッシュ操作命令の実行時においてスヌープ要求を用いることにより、すべてのCPU2aに対してキャッシュ操作を可能にする機能を有している。

20

**【0094】**

図10は、中断されたプロセスが他のCPU2aで再開される、いわゆるプロセスマイグレーションを考慮したキャッシュ操作命令(OCBWB)の処理例を示す説明図である。

**【0095】**

キャッシュ操作命令は、CPU2aによる命令デコード検知される。CPU2aからキャッシュ操作命令を実行する旨をキャッシュコントローラ2dに通知し、制御部2d1にてキャッシュミス時と同様にスヌープバス要求を発生させる。

**【0096】**

そのとき、「所定アドレスを持つCPU2aにキャッシュ操作を行うこと」をスヌープバス要求内容とする。スヌープコントローラ3(図1)はスヌープバス要求を受理すると、複製アドレスアレイ(複製タグ)をリードした後、所定エントリを持つCPU2aにスヌープ要求を発行する。

30

**【0097】**

それにより、本実施の形態4では、プロセスマイグレーションを考慮したキャッシュ操作を容易に実施することが可能となる。

**【0098】**

また、キャッシュ操作命令を1つ用意するだけで、すべてのCPU2aのキャッシュ操作が可能となり、プロセスマイグレーションを考慮したキャッシュ操作処理を用意する必要がなくなり、ソフトウェアの開発効率を向上させることができる。

40

**【0099】**

さらに、上記した「所定アドレス」は、所定アドレス指定に範囲を持たせるようにしてよい(例:0×0000F????のキャッシュラインを持つエントリを全て操作)。これによって、1命令/1ブロックであった所を1命令で複数ブロックを操作することができ、プログラム容量を削減することができる。

**【0100】**

(実施の形態5)

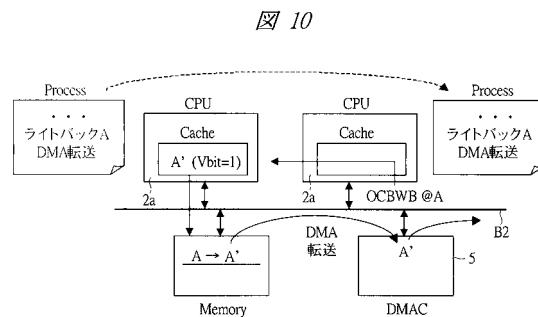

図11は、本発明の実施の形態5によるメモリ割り付けアクセスを検知する複製アドレスアレイ(複製タグ)の構成例を示す説明図である。

**【0101】**

50

本実施の形態 5において、図 1 の半導体集積回路装置 1は、1つの C P Uからすべての C P Uの複製アドレスアレイ（複製タグ）を参照する機能を有している。

#### 【 0 1 0 2 】

この場合、複製アドレスアレイ（複製タグ）へのアクセスは、スヌープバス B 1とは別に直接参照可能なインターフェースをバスインターフェースコントローラ 2 eとスヌープコントローラ 3との間で持つものとする（キャッシュコントローラ 2 dにその機能を有してもよい）。

#### 【 0 1 0 3 】

メモリ割り付けアクセスは、キャッシュコントローラ 2 dのアドレスデコーダ A Dで検知され、図 1 2 に示すように、アドレスビット 3 1 - 2 4で判定することができる。 10

#### 【 0 1 0 4 】

C P U 2 aからのアクセス要求をキャッシュコントローラが受理し（ステップ S 3 0 1）、複製アドレスアレイ（複製タグ）へのアクセスを検知すると、バスインターフェースコントローラ 2 e経由でスヌープコントローラ 3へアクセス要求を行う（ステップ S 3 0 2）。

#### 【 0 1 0 5 】

スヌープコントローラ 3は、アドレスデコードにより、すべての C P Uの複製アドレスアレイ（複製タグ）を参照できるアドレスマップか、自 C P Uの複製アドレスアレイ（複製タグ）のみ参照できるアドレスマップかを判断し、該複製アドレスアレイ（複製タグ）をアクセスする（ステップ S 3 0 3）。その後、アクセスしたデータをレスポンスとして返す（ステップ S 3 0 4）。 20

#### 【 0 1 0 6 】

図 1 2 の場合、アドレスビット 2 3で判定できる。すべての C P Uの複製アドレスアレイ（複製タグ）を参照する場合は、ビット 1 6 - 1 5で参照先を判定することができる。

#### 【 0 1 0 7 】

それにより、本実施の形態 5によれば、1つの C P Uからすべての C P Uの複製アドレスアレイ（複製タグ）を参照することが可能となるので、すべての C P Uのキャッシュ登録状況を見るためにそれらすべての C P Uのプログラム実行を割り込み要求などによって一時停止させる操作を不要とすることができるので、デバッグが容易に行うことができる。 30

#### 【 0 1 0 8 】

また、上記では、スヌープコントローラ 3が、アドレスデコードにより、すべての C P Uの複製アドレスアレイ（複製タグ）を参照できるアドレスマップか、自 C P Uの複製アドレスアレイ（複製タグ）のみ参照できるアドレスマップかを判断していたが、たとえば、複製アドレスアレイ（複製タグ）をアクセスする命令を追加するようにしてもよい。

#### 【 0 1 0 9 】

さらに、アクセス方法をオンチップシステムバス B 2経由とし、複製アドレスアレイ（複製タグ）へのアクセスもスヌープバス要求にし、レスポンスにリードデータを返すようにしてもよい。

#### 【 0 1 1 0 】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【産業上の利用可能性】

#### 【 0 1 1 1 】

本発明は、複数の中央処理装置を備えた S M P構造の半導体集積回路装置によるコピーレンシ制御に有効な技術に関する。

#### 【図面の簡単な説明】

#### 【 0 1 1 2 】

【図 1】本発明の実施の形態 1による半導体集積回路装置のブロック図である。 50

【図2】図1の半導体集積回路装置で用いられるオペランドキャッシュの構成例を示す説明図である。

【図3】図1の半導体集積回路装置で用いられる複製アドレスアレイ(複製タグ)の構成例を示す説明図である。

【図4】図1の半導体集積回路装置による通常のスヌープ処理の一例を示す説明図である。

【図5】図1の半導体集積回路装置によるスヌープ処理において、メモリ割り付けキャッシュアクセス結果と複製アドレスアレイ(複製タグ)の同期を行う際の一例を示す説明図である。

【図6】図1の半導体集積回路装置に用いられるオペランドキャッシュ/アドレスアレイの構成を示す説明図である。 10

【図7】本発明の実施の形態2によるコヒーレンシ有効/無効選択情報が追加されたアドレス変換テーブルの構成例を示す説明図である。

【図8】本発明の他の実施の形態によるコヒーレンシ制御を指定する制御レジスタにおける指定ビットの説明図である。

【図9】本発明の実施の形態3による制御レジスタにおけるコヒーレンシプロトコル混在ビットの説明図である。

【図10】本発明の実施の形態4によるプロセスマイグレーションを考慮したキャッシュ操作命令の処理例を示す説明図である。

【図11】図1の半導体集積回路装置で用いられるメモリ割り付け複製アドレスアレイ(複製タグ)アクセスの構成例を示す説明図である。 20

【図12】本発明の実施の形態5によるメモリ割り付けアクセスを検知する複製アドレスアレイ(複製タグ)の構成を示す説明図である。

#### 【符号の説明】

##### 【0113】

1 半導体集積回路装置

2 C P U コア

2 a C P U

2 b 命令キャッシュ

2 c データキャッシュ

2 d キャッシュコントローラ

2 e バスインターフェースコントローラ

3 スヌープコントローラ

4<sub>0</sub> ~ 4<sub>n</sub> ハードウェア I P

5 D M A コントローラ

6 チップ外部高速転送インターフェース

7 外部メモリインターフェース

8 周辺モジュールバスコントローラ

9 タイマ

10 割り込みコントローラ

11 クロックパルス生成器

12 汎用 I / O ポート

B 1 スヌープバス

B 2 オンチップシステムバス

B 3 周辺モジュールバス

C C R 制御レジスタ

A D アドレスデコーダ

10

20

30

40

【 図 1 】

【 図 3 】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

図8

| ビット | ビット名 | 説明                                                                                                                                                             |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6] | NCC1 | キャッシュコヒーレンシ対象1<br>PI領域がキャッシュコヒーレンシ対象領域かどうかを示します。<br>キャッシュコヒーレンシ制御無効状態では本ビットは無効になり、<br>非キャッシュコヒーレンシ領域になります。<br>1: 非キャッシュコヒーレンシ領域<br>0: キャッシュコヒーレンシ領域(初期値)       |

| [5] | NCC0 | キャッシュコヒーレンシ対象0<br>P0,U0,P3領域がキャッシュコヒーレンシ対象領域かどうかを示します。<br>キャッシュコヒーレンシ制御無効状態では本ビットは無効になり、<br>非キャッシュコヒーレンシ領域になります。<br>1: 非キャッシュコヒーレンシ領域<br>0: キャッシュコヒーレンシ領域(初期値) |

【図10】

【図9】

図9

| ビット  | ビット名 | 説明                                                                                                                                                           |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [17] | MCP  | コヒーレンシプロトコル混在(初期値:0)<br>同じ物理領域に対して異なるコヒーレンシプロトコルを使用する場合に設定します。<br>ICPでも複数CPUで共有しても異なるプロトコルを使用する場合は1を設定してください。<br>0: 同じコヒーレンシプロトコルを設定<br>1: 異なるコヒーレンシプロトコルを設定 |

【図 1 1】

【図 1 2】

全CPU(データデバッグ用)

|    | アドレス部                          | データ部                   |

|----|--------------------------------|------------------------|

| 31 | 24 23<br>アドレスデコード              | 24 23<br>タグデコード        |

| 31 | 11 11 11 0 1 0 1 *<br>アドレスデコード | 11 11 10 1 0 1 *<br>タグ |

| 31 | 10 9<br>エンドリバッフ                | 10 9<br>タグ             |

|    | 2 1 0                          | ..... SV               |

【図2】

図2

---

フロントページの続き

(51)Int.Cl.

F I

G 0 6 F 12/08 5 0 7 L

G 0 6 F 12/10 5 0 1 Z

(72)発明者 早瀬 清

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 中野 裕二

(56)参考文献 特開2006-72509 (JP, A)

特開2006-185284 (JP, A)

特開平10-254774 (JP, A)

特開平4-123151 (JP, A)

特開2001-184263 (JP, A)

特開2007-183702 (JP, A)

国際公開第2007/094046 (WO, A1)

ルネサス32ビットRISCマイクロコンピュータハードウェアマニュアルSH7706, 日本, 株式会社ル

ネサス テクノロジ 営業統括部, 2006年 5月24日, Rev.5.00, 5-9~5-12, [平成24年2

月23日検索], インターネット, U R L, [ftp://210.66.153.173/%B7s%A4H%B1%D0%AE%D7/F230N/4.%BDu%B8%F4%B9%CF/%A4%B8%A5%F3%A7%DE%B3N%A4%E5%A5%F3/CPU\\_rjj09b0163\\_sh7706.pdf](ftp://210.66.153.173/%B7s%A4H%B1%D0%AE%D7/F230N/4.%BDu%B8%F4%B9%CF/%A4%B8%A5%F3%A7%DE%B3N%A4%E5%A5%F3/CPU_rjj09b0163_sh7706.pdf)

(58)調査した分野(Int.Cl., DB名)

G 0 6 F 1 2 / 0 8

G 0 6 F 1 2 / 1 0