(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4565613号

(P4565613)

(45) 発行日 平成22年10月20日(2010.10.20)

(24) 登録日 平成22年8月13日(2010.8.13)

|                        |                  |

|------------------------|------------------|

| (51) Int.Cl.           | F 1              |

| G 06 F 13/38 (2006.01) | G 06 F 13/38 350 |

| B 41 J 29/38 (2006.01) | B 41 J 29/38 Z   |

| H 03 M 9/00 (2006.01)  | H 03 M 9/00 C    |

請求項の数 6 (全 18 頁)

(21) 出願番号 特願2004-113214 (P2004-113214)

(22) 出願日 平成16年4月7日 (2004.4.7)

(65) 公開番号 特開2005-301423 (P2005-301423A)

(43) 公開日 平成17年10月27日 (2005.10.27)

審査請求日 平成18年12月5日 (2006.12.5)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 小路 通陽

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】シリアルデータ転送方法、電子機器、及び記録装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電子機器から第2の電子機器に第1の信号線を用いて供給されるデータ信号を前記第1の電子機器から前記第2の電子機器に第2の信号線を用いて供給されるクロック信号により同期させて、前記第1の電子機器から前記第2の電子機器にシリアル転送するシリアルデータ転送方法であって、

前記データ信号を前記クロック信号に同期して前記第2の電子機器のシフトレジスタに入力する入力工程と、

前記入力工程において前記シフトレジスタに入力された前記データ信号を、前記第1の電子機器から前記第2の電子機器に第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記データ信号の信号レベルとに基づいて、前記第2の電子機器の複数のラッチの内の第1のラッチ、或いは第2のラッチへのラッチを選択的に行うラッチ工程とを有することを特徴とするシリアルデータ転送方法。

## 【請求項 2】

外部機器から第1の信号線を用いて供給されるデータ信号を前記外部機器から第2の信号線を用いて供給されるクロック信号に同期させてシリアル受信する電子機器であって、

前記データ信号を前記クロック信号に同期して入力するシフトレジスタと、

前記シフトレジスタに入力されたデータ信号をラッチする複数のラッチと、

前記シフトレジスタに入力された前記データ信号を、前記外部機器から第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記データ信号の信

10

20

号レベルとに基づいて、前記複数のラッチの内の第1のラッチ、或いは第2のラッチで選択的にラッチを行うよう制御する制御回路とを有することを特徴とする電子機器。

【請求項3】

第1の電子機器から第2の電子機器に第1の信号線を用いて供給されるデータ信号を前記第1の電子機器から前記第2の電子機器に第2の信号線を用いて供給されるクロック信号により同期させて、前記第1の電子機器から前記第2の電子機器にシリアル転送するシリアルデータ転送方法であって、

前記データ信号を前記クロック信号に同期して前記第2の電子機器のシフトレジスタに入力する入力工程と、

前記入力工程において前記シフトレジスタに入力された前記データ信号を、前記第1の電子機器から前記第2の電子機器に第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記クロック信号の信号レベルとに基づいて、前記第2の電子機器の複数のラッチの内の第1のラッチ、或いは第2のラッチへのラッチを選択的に行うラッチ工程とを有することを特徴とするシリアルデータ転送方法。

【請求項4】

外部機器から第1の信号線を用いて供給されるデータ信号を前記外部機器から第2の信号線を用いて供給されるクロック信号に同期させてシリアル受信する電子機器であって、

前記データ信号を前記クロック信号に同期して入力するシフトレジスタと、

前記シフトレジスタに入力されたデータ信号をラッチする複数のラッチと、

前記シフトレジスタに入力された前記データ信号を、前記外部機器から第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記クロック信号の信号レベルとに基づいて、前記複数のラッチの内の第1のラッチ、或いは第2のラッチで選択的にラッチを行うよう制御する制御回路とを有することを特徴とする電子機器。

【請求項5】

請求項2又は4に記載の電子機器を搭載した記録装置。

【請求項6】

前記電子機器は、モータドライバであることを特徴とする請求項5に記載の記録装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はシリアルデータ転送方法、電子機器、及び記録装置に関し、特に、インクジェット記録ヘッドを搭載した記録装置内部のデータ転送に適用されるシリアルデータ転送方法、電子機器、及び記録装置に関する。

【背景技術】

【0002】

従来より多ビットのデータを転送する際には、各ビットに1本のデータ信号ラインを対応させ、複数の信号ラインを用いて多ビットを同時転送するパラレルデータ転送が用いられてきた。しかしながら、同時転送を行なうビット数が、例えば、8ビット、16ビット、32ビット、64ビットなどと増加すると、パラレル転送では転送に用いるデータ信号ラインの数も増加するという問題もあるため、クロック信号に同期してデータをシフトしながら転送し、ストローブ信号によりそのデータを有効にするシリアルデータ転送が使用されるようになった。

【0003】

例えば、キャリッジに搭載したインクジェット記録ヘッド（以下、記録ヘッド）を往復走査することで記録を行なう記録装置の場合、キャリッジと記録装置本体とはフレキシブルプリンタケーブル（FPC）で接続され、このケーブルを介して種々の制御信号やデータ信号が記録ヘッドと記録装置本体との間で送受される構成となっている。この記録ヘッドと記録装置本体の間のデータ転送にはシリアル転送方式が採用されている。

【0004】

また、この記録装置には、キャリッジを駆動するためのキャリッジモータ、記録用紙な

10

20

30

40

50

どの記録媒体を搬送するための搬送モータなど様々なモータが搭載されており、それらのモータはモータドライバによって駆動制御されている。この記録装置の制御回路からモータドライバに対するモータ駆動制御信号の転送にもシリアル転送方式が採用されている。これら種々のモータはその用途に応じて種類も駆動方法も異なるので、モータドライバからは異なる種類の、その異なる数の制御信号をこれら対応するモータドライバに転送して駆動制御を実行することが求められる。従って、これまで夫々のモータに対応した専用のモータドライバを設け、個別的にモータの駆動制御を行なっていた。

#### 【0005】

更に、データを異なる複数の要因に従って転送したい場合、それら要因毎にデータ信号やクロック信号等を割り当てたり、要因毎にストローブ信号を割り当てたり、要因を切替える為の制御信号を追加してデータ転送を実現する方法も提案してきた。

10

【特許文献1】特開平8-130621号公報

【特許文献2】特開平9-207369号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0006】

しかしながら上記従来例のようなシリアル転送方式が、例えば、上記記録装置の制御回路とモータドライバとの間のデータ転送に適用された場合、本来クロック信号、データ信号、ストローブ信号の3つの信号を夫々供給する3本の信号ラインでシリアルデータ転送が可能であるにも係わらず、例えば、モータの種類の増加やモータ数の増加などに伴って、3本以上の信号ラインが必要になった場合には、当然、信号ラインの増加が発生し、これにともない、記録装置の制御回路とモータドライバには新たな信号パッドを設けたり、制御回路上のシリアル信号線の数が多くなり、そのための基板上のレイアウト面積が増大したりするなど、その仕様を大きく変更することが必要になる。

20

#### 【0007】

これに加えて、従来のように、記録装置に搭載された種々のモータ夫々に対応した専用のモータドライバで個別的にモータの駆動制御を行なうと、異なる種類のモータドライバが必要となり、それを開発するコストも莫大になり、モータの駆動方法や種類が違い、信号の数が増加などに対応した開発コストは削減したという要求がある。

#### 【0008】

30

また、上記従来例のようなシリアル転送方式を、例えば、上記記録装置のヘッドドライバと記録ヘッドとの間のデータ転送に適用された場合、記録ヘッドの機能増加などに伴って、従来以上の信号数が必要になった場合には、当然、信号ラインの増加が発生し、これにともない、記録ヘッドに新たな信号パッドを設けたり、キャリッジ内部にも電気的接続のためのピンやパッドを増やしたり、FPCの幅を大きくしたり、記録ヘッドを駆動するために記録装置本体に設けるヘッドドライバICの記録ヘッドインターフェースも、接続ピンの数が増加するなど、その仕様を変更することが必要になる。

#### 【0009】

従って、記録ヘッドの機能増加により信号ラインの数が増加すると、これを駆動するヘッドドライバの機能追加や仕様変更が必要となり、これは、ヘッドドライバを実現するドライバICの大型化につながり、記録装置全体の生産コストの増大にもつながる。

40

#### 【0010】

このように、シリアルデータ転送を、インクジェット記録装置に適用する場合、信号ラインの増加は、様々な個所に影響を与えることになる。

#### 【0011】

一方、記録装置や記録ヘッドに機能追加が求められるのは時代の趨勢であり、市場からの種々の要求に応じた高性能の記録装置や記録ヘッドを開発し、提供することも考慮するべき要件である。

#### 【0012】

以上のことから考慮すると、記録装置や記録ヘッドの高機能化を実現するために、信号数

50

の増加は避けられないが、信号ラインの増加は抑えるようにしつつ、シリアルデータ転送を実現することが求められる。

【0013】

本発明は上記従来例に鑑みてなされたもので、例えば、データ信号とクロック信号とストローブ信号転送用の3本の信号線を用いたシリアルデータ転送に、信号線や制御信号の追加をすることなく、種々の制御を可能にするシリアルデータ転送方法、電子機器、及び記録装置を提供することを目的としている。

【課題を解決するための手段】

【0014】

上記目的を達成するため本発明のシリアルデータ転送方法は以下の工程からなる。

10

【0015】

即ち、第1の電子機器から第2の電子機器に第1の信号線を用いて供給されるデータ信号を前記第1の電子機器から前記第2の電子機器に第2の信号線を用いて供給されるクロック信号により同期させて、前記第1の電子機器から前記第2の電子機器にシリアル転送するシリアルデータ転送方法であって、前記データ信号を前記クロック信号に同期して前記第2の電子機器のシフトレジスタに入力する入力工程と、前記入力工程において前記シフトレジスタに入力された前記データ信号を、前記第1の電子機器から前記第2の電子機器に第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記データ信号の信号レベルとに基づいて、前記第2の電子機器の複数のラッチの内の第1のラッチ、或いは第2のラッチへのラッチを選択的に行うラッチ工程とを有することを特徴とする。

20

或は、第1の電子機器から第2の電子機器に第1の信号線を用いて供給されるデータ信号を前記第1の電子機器から前記第2の電子機器に第2の信号線を用いて供給されるクロック信号により同期させて、前記第1の電子機器から前記第2の電子機器にシリアル転送するシリアルデータ転送方法であって、前記データ信号を前記クロック信号に同期して前記第2の電子機器のシフトレジスタに入力する入力工程と、前記入力工程において前記シフトレジスタに入力された前記データ信号を、前記第1の電子機器から前記第2の電子機器に第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記クロック信号の信号レベルとに基づいて、前記第2の電子機器の複数のラッチの内の第1のラッチ、或いは第2のラッチへのラッチを選択的に行うラッチ工程とを有することを特徴としても良い。

30

【0016】

また本発明は、上記方法を適用した電子機器を備えることで実現しても良い。

【0017】

即ち、外部機器から第1の信号線を用いて供給されるデータ信号を前記外部機器から第2の信号線を用いて供給されるクロック信号に同期させてシリアル受信する電子機器であって、前記データ信号を前記クロック信号に同期して入力するシフトレジスタと、前記シフトレジスタに入力されたデータ信号をラッチする複数のラッチと、前記シフトレジスタに入力された前記データ信号を、前記外部機器から第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記データ信号の信号レベルとに基づいて、前記複数のラッチの内の第1のラッチ、或いは第2のラッチで選択的にラッチを行うよう制御する制御回路とを有することを特徴とする。

40

或は、外部機器から第1の信号線を用いて供給されるデータ信号を前記外部機器から第2の信号線を用いて供給されるクロック信号に同期させてシリアル受信する電子機器であって、前記データ信号を前記クロック信号に同期して入力するシフトレジスタと、前記シフトレジスタに入力されたデータ信号をラッチする複数のラッチと、前記シフトレジスタに入力された前記データ信号を、前記外部機器から第3の信号線を用いて前記データ信号の入力後に供給される制御信号と前記入力後の前記クロック信号の信号レベルとに基づいて、前記複数のラッチの内の第1のラッチ、或いは第2のラッチで選択的にラッチを行うよう制御する制御回路とを有することを特徴としても良い。

50

**【0023】**

さらに本発明は、以上の構成の電子機器を用いた記録装置を備えることで実現しても良い。

**【発明の効果】****【0027】**

従って本発明によれば、第1～第3の信号線を用いて夫々シリアル転送される信号を効果的に用いることで信号線を増加させることなく、種々のデータ取り込みの制御を実現できるという効果がある。

**【発明を実施するための最良の形態】****【0028】**

以下添付図面を参照して本発明の好適な実施例について、さらに具体的かつ詳細に説明する。

10

**【0029】**

なお、この明細書において、「記録」（「プリント」という場合もある）とは、文字、図形等有意の情報を形成する場合のみならず、有意無意を問わず、また人間が視覚で知覚し得るように顕在化したものであるか否かを問わず、広く記録媒体上に画像、模様、パターン等を形成する、または媒体の加工を行う場合も表すものとする。

**【0030】**

また、「記録媒体」とは、一般的な記録装置で用いられる紙のみならず、広く、布、プラスチック・フィルム、金属板、ガラス、セラミックス、木材、皮革等、インクを受容可能なものも表すものとする。

20

**【0031】**

さらに、「インク」（「液体」と言う場合もある）とは、上記「記録（プリント）」の定義と同様広く解釈されるべきもので、記録媒体上に付与されることによって、画像、模様、パターン等の形成または記録媒体の加工、或いはインクの処理（例えば記録媒体に付与されるインク中の色剤の凝固または不溶化）に供され得る液体を表すものとする。

**【0032】**

またさらに、「ノズル」とは、特にことわらない限り吐出口ないしこれに連通する液路およびインク吐出に利用されるエネルギーを発生する素子を総括して言うものとする。

**【0033】**

30

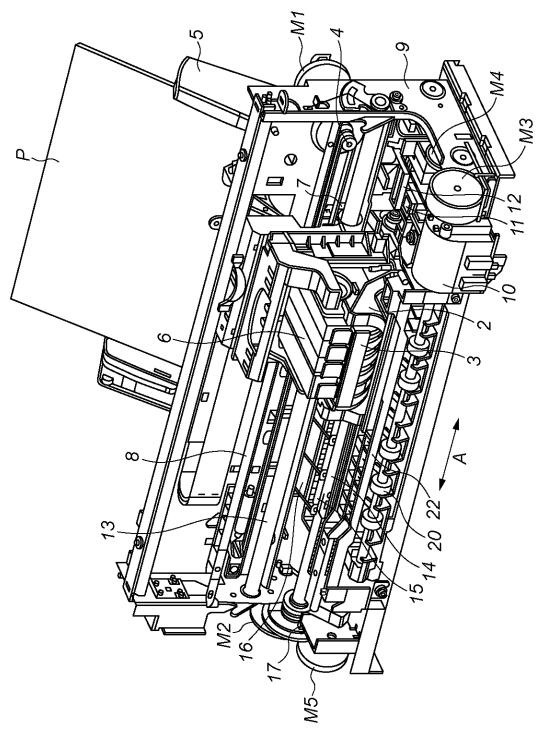

<インクジェット記録装置の説明（図1）>

図1は本発明の代表的な実施例であるインクジェット記録装置1の構成の概要を示す外観斜視図である。

**【0034】**

図1に示すように、インクジェット記録装置（以下、記録装置という）は、インクジェット方式に従ってインクを吐出して記録を行なう記録ヘッド3を搭載したキャリッジ2にキャリッジモータM1によって発生する駆動力を伝達機構4より伝え、キャリッジ2を矢印A方向に往復移動させるとともに、例えば、記録紙などの記録媒体Pを給紙モータM4によって駆動される給紙機構5を介して給紙し、記録位置まで搬送し、その記録位置において記録ヘッド3から記録媒体Pにインクを吐出することで記録を行なう。

40

**【0035】**

また、記録ヘッド3の状態を良好に維持するためにキャリッジ2を回復装置10の位置まで移動させ、間欠的に記録ヘッド3の吐出回復処理を行う。

**【0036】**

記録装置1のキャリッジ2には記録ヘッド3を搭載するのみならず、記録ヘッド3に供給するインクを貯留するインクカートリッジ6を装着する。インクカートリッジ6はキャリッジ2に対して着脱自在になっている。

**【0037】**

図1に示した記録装置1はカラー記録が可能であり、そのためにキャリッジ2にはマゼンタ（M）、シアン（C）、イエロ（Y）、ブラック（K）のインクを夫々、収容した4

50

つのインクカートリッジを搭載している。これら4つのインクカートリッジは夫々独立に着脱可能である。

#### 【0038】

さて、キャリッジ2と記録ヘッド3とは、両部材の接合面が適正に接触されて所要の電気的接続を達成維持できるようになっている。記録ヘッド3は、記録信号に応じてエネルギーを印加することにより、複数の吐出口からインクを選択的に吐出して記録する。特に、この実施例の記録ヘッド3は、熱エネルギーを利用してインクを吐出するインクジェット方式を採用し、熱エネルギーを発生するために電気熱変換体を備え、その電気熱変換体に印加される電気エネルギーが熱エネルギーへと変換され、その熱エネルギーをインクに与えることにより生じる膜沸騰による気泡の成長、収縮によって生じる圧力変化を利用して、吐出口よりインクを吐出させる。この電気熱変換体は各吐出口のそれぞれに対応して設けられ、記録信号に応じて対応する電気熱変換体にパルス電圧を印加することによって対応する吐出口からインクを吐出する。

#### 【0039】

図1に示されているように、キャリッジ2はキャリッジモータM1の駆動力を伝達する伝達機構4の駆動ベルト7の一部に連結されており、ガイドシャフト13に沿って矢印A方向に摺動自在に案内支持されるようになっている。従って、キャリッジ2は、キャリッジモータM1の正転及び逆転によってガイドシャフト13に沿って往復移動する。また、キャリッジ2の移動方向(矢印A方向)に沿ってキャリッジ2の絶対位置を示すためのスケール8が備えられている。この実施例では、スケール8は透明なPETフィルムに必要なピッチで黒色のバーを印刷したものを用いており、その一方はシャーシ9に固着され、他方は板バネ(不図示)で支持されている。

#### 【0040】

また、記録装置1には、記録ヘッド3の吐出口(不図示)が形成された吐出口面に対向してプラテン(不図示)が設けられており、キャリッジモータM1の駆動力によって記録ヘッド3を搭載したキャリッジ2が往復移動されると同時に、記録ヘッド3に記録信号を与えてインクを吐出することによって、プラテン上に搬送された記録媒体Pの全幅にわたって記録が行われる。

#### 【0041】

さらに、図1において、14は記録媒体Pを搬送するために搬送モータM2によって駆動される搬送ローラ、15はバネ(不図示)により記録媒体Pを搬送ローラ14に当接するピンチローラ、16はピンチローラ15を回転自在に支持するピンチローラホルダ、17は搬送ローラ14の一端に固着された搬送ローラギアである。そして、搬送ローラギア17に中間ギア(不図示)を介して伝達された搬送モータM2の回転により、搬送ローラ14が駆動される。

#### 【0042】

またさらに、20は記録ヘッド3によって画像が形成された記録媒体Pを記録装置外へ排出するための排出口ローラであり、排紙モータM5の回転が伝達されることで駆動されるようになっている。なお、排出口ローラ20は記録媒体Pをバネ(不図示)により圧接する拍車ローラ(不図示)により当接する。22は拍車ローラを回転自在に支持する拍車ホルダである。

#### 【0043】

またさらに、記録装置1には、図1に示されているように、記録ヘッド3を搭載するキャリッジ2の記録動作のための往復運動の範囲外(記録領域外)の所望位置(例えば、ホームポジションに対応する位置)に、記録ヘッド3の吐出不良を回復するための回復装置10が配設されている。

#### 【0044】

回復装置10は、記録ヘッド3の吐出口面をキャッピングするキャッピング機構11と記録ヘッド3の吐出口面をクリーニングするワイピング機構12を備えており、キャッピング機構11による吐出口面のキャッピングに連動して回復装置内の吸引手段(吸引ポン

10

20

30

40

50

プ等)により吐出口からインクを強制的に排出させ、それによって、記録ヘッド3のインク流路内の粘度の増したインクや気泡等を除去するなどの吐出回復処理を行う。

【0045】

また、非記録動作時等には、記録ヘッド3の吐出口面をキャッピング機構11によるキャッピングすることによって、記録ヘッド3を保護するとともにインクの蒸発や乾燥を防止することができる。一方、ワイピング機構12はキャッピング機構11の近傍に配され、記録ヘッド3の吐出口面に付着したインク液滴を拭き取るようになっている。

【0046】

これらキャッピング機構11及びワイピング機構12により、記録ヘッド3のインク吐出状態を正常に保つことが可能となっている。

10

【0047】

これら回復装置10の吸引ポンプ、キャッピング機構11、ワイピング機構12はメンテナンスマータM3により駆動力が供給される。

【0048】

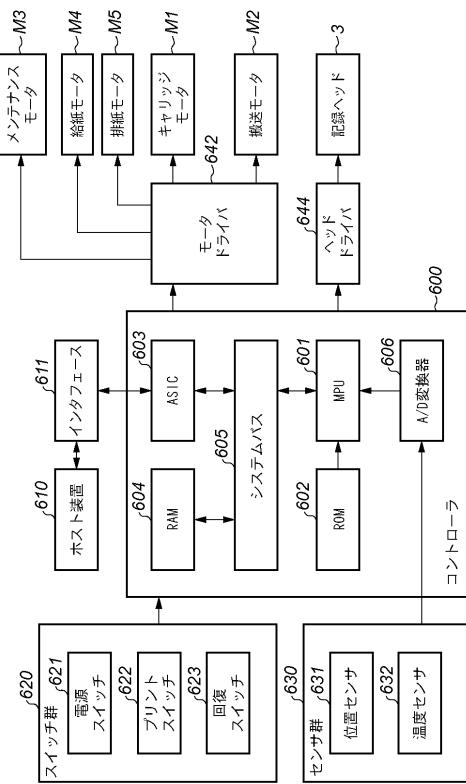

<インクジェット記録装置の制御構成(図2)>

図2は図1に示した記録装置の制御構成を示すブロック図である。

【0049】

図2に示すように、コントローラ600は、MPU601、後述する制御シーケンスに対応したプログラム、所要のテーブル、その他の固定データを格納したROM602、記録ヘッド3による記録走査の際に、RAM602の記憶領域に直接アクセスしながら記録ヘッド3に対して記録素子(吐出ヒータ)の駆動データ(DATA)を生成する特殊用途集積回路(ASIC)603、画像データの展開領域やプログラム実行のための作業用領域等を設けたRAM604、MPU601、ASIC603、RAM604を相互に接続してデータの授受を行うシステムバス605、以下に説明するセンサ群からのアナログ信号を入力してA/D変換し、デジタル信号をMPU601に供給するA/D変換器606などで構成される。

20

【0050】

また、図2において、610は画像データの供給源となるコンピュータ(或いは、画像読み取り用のリーダやデジタルカメラなど)でありホスト装置と総称される。ホスト装置610と記録装置1との間ではインターフェース(I/F)611を介して画像データ、コマンド、ステータス信号等を送受信する。

30

【0051】

さらに、620はスイッチ群であり、電源スイッチ621、プリント開始を指令するためのプリントスイッチ622、及び記録ヘッド3のインク吐出性能を良好な状態に維持するための処理(回復処理)の起動を指示するための回復スイッチ623など、操作者による指令入力を受けるためのスイッチから構成される。630はホームポジションhを検出するためのフォトカプラなどの位置センサ631、環境温度を検出するために記録装置の適宜の箇所に設けられた温度センサ632等から構成される装置状態を検出するためのセンサ群である。

【0052】

40

さらに、641はASIC603からのデータに基づいて、記録ヘッド3を駆動制御するための制御信号を生成し、記録ヘッド3を駆動するヘッドドライバ、642は記録動作に伴ってキャリッジモータM1、搬送モータM2、メンテナンスマータM3、給紙モータM4、及び排紙モータM5の制御を行うモータドライバである。

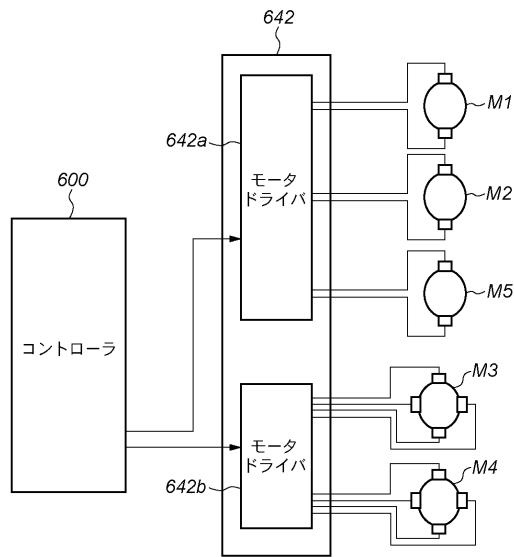

【0053】

図3はモータドライバと5つのモータとの関係を示すブロック図である。

【0054】

図1～図2を参照して説明したが、この記録装置には5個のモータM1～M5が搭載されており、キャリッジモータM1、搬送モータM2、及び排紙モータM5の3個がDCモータであり、メンテナンスマータM3と給紙モータM4の2個がステッピングモータであ

50

る。

【0055】

そして、図3に示されているように、モータドライバ642は3個のDCモータM1、M2、M5を駆動制御するモータドライバ642aと、2個のステッピングモータを駆動制御するモータドライバ642bとから構成されている。基本的にこれら2つのモータドライバの構成は共通である。

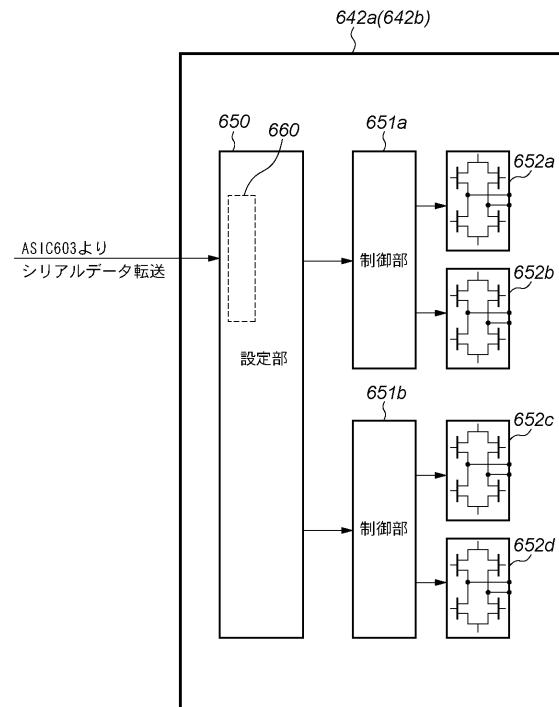

【0056】

図4は、モータドライバ642a(642b)の内部構造を示す図である。

【0057】

このモータドライバは、例えば、1チップの集積回路(IC)で構成される。この図に示すモータドライバは、4個のHブリッジ回路652a～652dを備え、駆動対象のモータの種類に対応してHブリッジの組み替えが可能な構成となっている。 10

【0058】

各々のHブリッジ回路は、4つのトランジスタ(例えば、FETトランジスタ)で構成されており、この4つのトランジスタに対して制御信号が入力される。この制御信号に応じて4つのトランジスタは、オンまたはオフして、電流の向きを切替えてモータの正転または逆転を行うようにしている。

【0059】

図4において、650はHブリッジ構成を設定する設定部、651aはHブリッジ652aとHブリッジ652bとを制御する制御部、652bはHブリッジ652c、Hブリッジ652dを制御する制御部である。 20

【0060】

図4に示す構成では、ステッピングモータ(この実施例ではメンテナンスモータM3と給紙モータM4)を駆動する場合は、Hブリッジ652aとHブリッジ652b、そしてHブリッジ652cとHブリッジ652dとがペアになる。また、DCモータ(この実施例では、キャリッジモータM1、搬送モータM2、排紙モータM5)を駆動する場合は、Hブリッジ652a、Hブリッジ652b、Hブリッジ652c、Hブリッジ652dがそれぞれ独立してモータを駆動する場合と、Hブリッジ652aとHブリッジ652bとがペアとなって1つのモータを駆動し、Hブリッジ652cとHブリッジ652dがペアとなって1つのモータを駆動する場合がある。 30

【0061】

大電流を必要としないタイプのDCモータ(以下、DCS)を駆動する場合には、Hブリッジ652a、Hブリッジ652b、Hブリッジ652c、及びHブリッジ652dは夫々独立して、別々のモータ駆動させることが出来る。一方、大電流を必要とするタイプDCモータ(以下、DCL)を駆動する場合には、Hブリッジ652aとHブリッジ652bがペアとなり、Hブリッジ652cとHブリッジ652dがペアとなる。

【0062】

ここで、DCモータの動作仕様について補足すると、DCSとDCLでは、例えば、初期トルク用の電流値やバリスタピーク電流値が異なる。例えば、DCSの初期トルク用の電流値は2.5Aであるが、DCLの初期トルク用の電流値は3Aである。 40

【0063】

このような組み替え変更の設定は設定部650に設定された情報に基づいて、制御部651a、651bが行うようになっている。

【0064】

設定部650にはASIC603よりシリアル転送でモータを駆動制御するための設定信号が供給される。従って、設定部650にはそのシリアル信号を受信するためのシリアルインターフェース回路660が備えられる。

【0065】

次に、以上の構成の記録装置のモータドライバに用いられるシリアルインターフェース回路660についてのいくつかの実施例を説明する。 50

## 【実施例 1】

## 【0066】

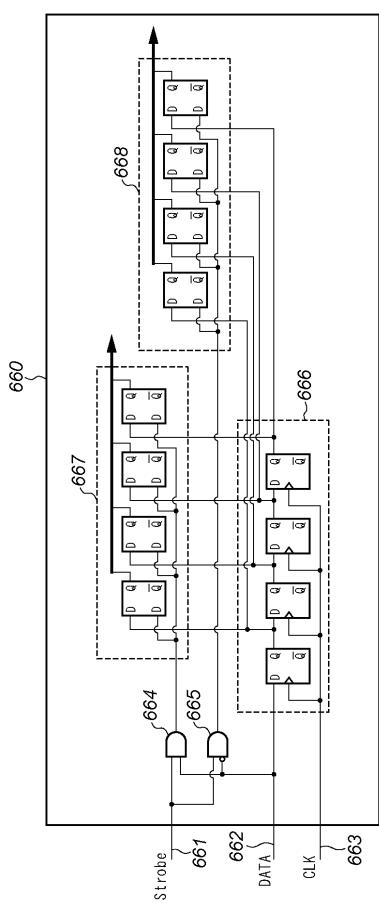

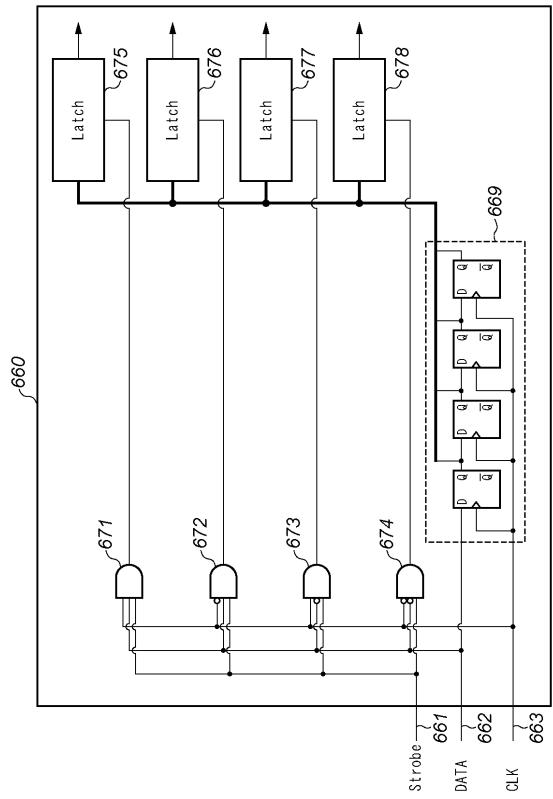

図5は実施例1に従うシリアルインターフェース回路660の構成を示す図である。

## 【0067】

シリアルインターフェース回路660には、ストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)の信号線661、データ信号(D<sub>A</sub>T<sub>A</sub>)の信号線662、クロック信号(C<sub>L</sub>K)の信号線663の合計3本の信号線が入力されている。シリアルデータ転送時、クロック信号(C<sub>L</sub>K)に同期して信号線662によって転送されるデータ信号(D<sub>A</sub>T<sub>A</sub>)を切替えることにより、シフトレジスタ666のフリップフロップ内に転送データ信号を入力する。

## 【0068】

この実施例では、シリアルインターフェース回路の構成を簡略化する為に、シフトレジスタ666は4ビット(即ち、フリップフロップ回路が4つ)になっているが、このビット数はデータ転送側のASIC603やシリアルインターフェース回路660を内蔵するモータドライバの制御バス幅に応じて、8ビット、16ビット、32ビット等の構成が可能である。

## 【0069】

シフトレジスタ666にデータ信号転送終了後、信号線662にストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)を入力し、転送データをラッチすることにより転送されたデータ信号は有効になる。その際、ストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)は、ANDゲート664を介してラッチ667、ANDゲート665を介してラッチ668に入力される。また、ANDゲート664には信号線662を介してデータ信号(D<sub>A</sub>T<sub>A</sub>)が、ANDゲート665には、インバータを介して反転されたデータ信号(D<sub>A</sub>T<sub>A</sub>)が入力される。

## 【0070】

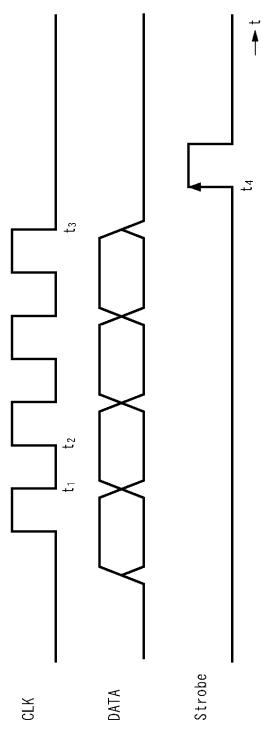

図6～図7は図5に示したインターフェース回路の動作を説明するために用いるシリアル転送される信号のタイムチャートである。

## 【0071】

図6に示す場合では、クロック信号(C<sub>L</sub>K)の立下りに同期して(例えば、 $t = t_1$ )、データ信号(D<sub>A</sub>T<sub>A</sub>)を変化させ、クロック信号(C<sub>L</sub>K)の立上りに同期して(例えば、 $t = t_2$ )、シフトレジスタ666に格納するデータ信号をシフトさせる。所定ビット数(この実施例では4ビット)のデータ信号(D<sub>A</sub>T<sub>A</sub>)をシフトレジスタ666に取込んだ後、データ信号(D<sub>A</sub>T<sub>A</sub>)はローレベル(L<sub>o</sub>w)の信号を出力する( $t = t_3$ )。この状態で、ストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)を発生させると( $t = t_4$ )、ANDゲート664からストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)がラッチ667に入力され、シフトレジスタ666内のデータ信号がラッチ667にラッチされる。一方、ゲート665には、インバータを介して反転されたデータ信号が入力されている為、ANDゲート665の出力はローレベル(L<sub>o</sub>w)に固定され、ラッチ668にストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)は入力されない。

## 【0072】

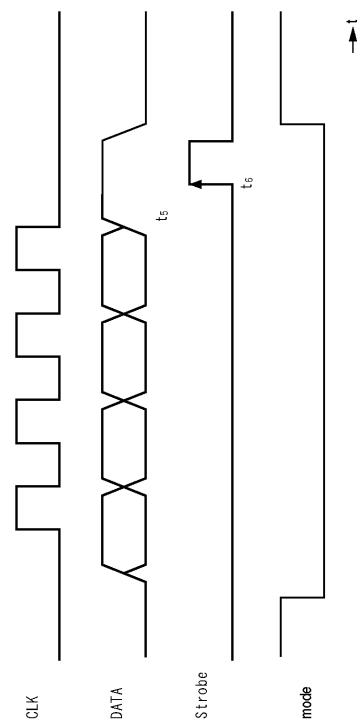

また、図7に示す場合では、図6のタイムチャートと同様に、クロック信号(C<sub>L</sub>K)とデータ信号(D<sub>A</sub>T<sub>A</sub>)の変化によりシフトレジスタ666内にデータ信号を取り込んだ後、データ信号(D<sub>A</sub>T<sub>A</sub>)はハイレベル(H<sub>i</sub>gh)の信号を出力する( $t = t_5$ )。この状態で、ストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)を発生させても( $t = t_6$ )、ANDゲート664の出力はローレベル(L<sub>o</sub>w)に固定される。一方、ANDゲート665にはインバータを介してデータ信号(D<sub>A</sub>T<sub>A</sub>)が入力されているため、ANDゲート665からストローブ信号(S<sub>t</sub>ro<sub>b</sub>e)がラッチ668に入力され、シフトレジスタ666内のデータ信号がラッチ668にラッチされる。

## 【0073】

従って以上説明した実施例によれば、3本の信号線によって供給されるクロック信号、データ信号、ストローブ信号の3つの信号により、異なる2つのラッチへのデータ書き込みの制御を行うことが可能になる。

## 【0074】

なお、シリアルインターフェース回路660にモード信号(mode)を設け、図13に示すように更にモード信号を用いてデータのラッチを行っても構わない。例えば、モード信号がハイレベルからローレベルに変化してから、そのローレベルの期間中にデータ信号の取り込みを行うのである。

## 【実施例2】

## 【0075】

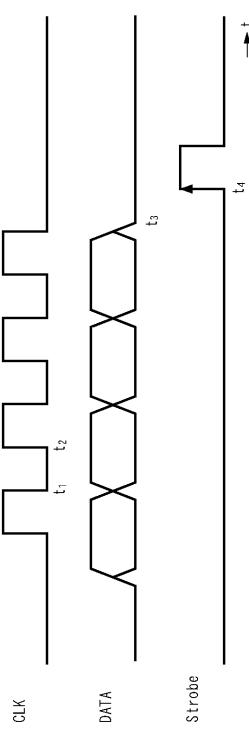

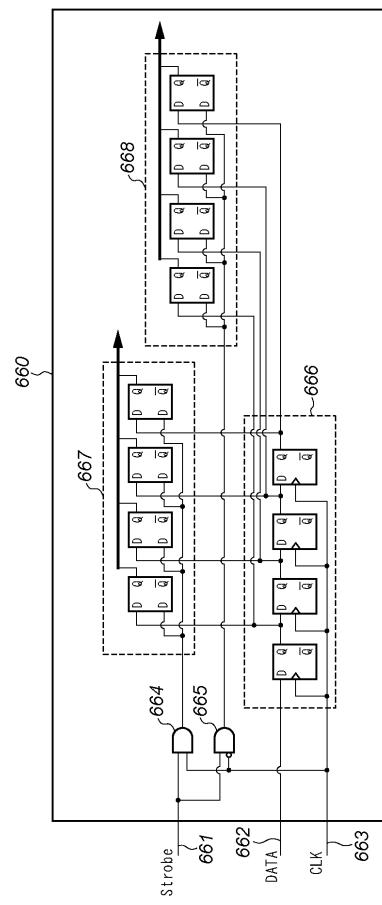

図8は実施例2に従うシリアルインターフェース回路660の構成を示す図である。

## 【0076】

図5と図8とを比較すると分かるように、この実施例に従うシリアルインターフェース回路660を構成する構成要素は実施例1の回路と同じである。従って、その構成要素には同じ参照番号を付してあり、その説明は省略する。

10

## 【0077】

実施例1と実施例2のシリアルインターフェース回路の構成で異なる点は、実施例1の構成では、データ信号(DATA)と反転されたデータ信号とが夫々、ANDゲート664と665に入力されていたのに対し、実施例2ではクロック信号(CLK)と反転されたクロック信号とが夫々、ANDゲート664と665に入力される点にある。

## 【0078】

この実施例では、シフトレジスタ666にデータ信号転送終了後、信号線661にストローブ信号(Strobe)を入力し、転送データ信号をラッチすることによりデータ信号(DATA)を有効にする。その際、ストローブ信号(Strobe)は、ANDゲート664を介してラッチ667に、ANDゲート665を介してラッチ668に入力される。そして、ANDゲート664にはクロック信号(CLK)が、ANDゲート665には、インバータを介して反転されたクロック信号が入力される。

20

## 【0079】

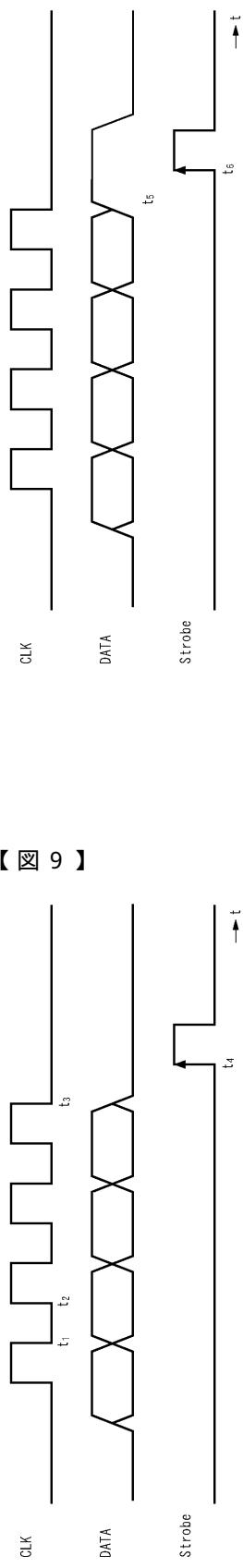

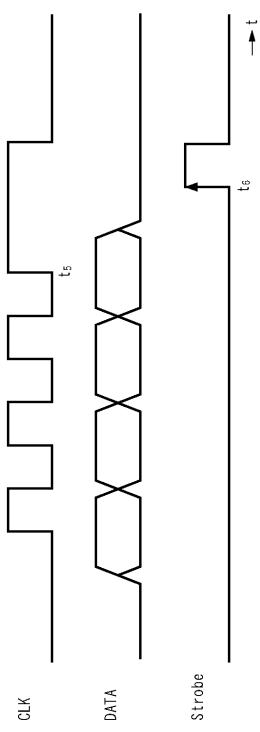

図9～図10は図8に示したインターフェース回路の動作を説明するために用いるシリアル転送される信号のタイムチャートである。

## 【0080】

図9に示す場合では、クロック信号(CLK)の立下りに同期して(例えば、 $t = t_1$ )、データ信号(DATA)を変化させ、クロック信号(CLK)の立上りに同期して(例えば、 $t = t_2$ )、シフトレジスタ666に格納するデータ信号をシフトさせる。所定ビット数(この実施例では4ビット)のデータ信号(DATA)をシフトレジスタ666に取込んだ後、クロック信号(CLK)はローレベル(Low)の信号を出力する( $t = t_3$ )。この状態で、ストローブ信号(Strobe)を発生させると( $t = t_4$ )、ANDゲート664からストローブ信号(Strobe)がラッチ667に入力され、シフトレジスタ666内のデータ信号がラッチ667にラッチされる。一方、ゲート665には、インバータを介して反転されたクロック信号が入力されている為、ANDゲート665の出力はローレベル(Low)に固定され、ラッチ668にストローブ信号(Strobe)は入力されない。

30

## 【0081】

また、図10に示す場合では、図9のタイムチャートと同様に、クロック信号(CLK)とデータ信号(DATA)の変化によりシフトレジスタ666内にデータ信号を取り込んだ後、クロック信号(CLK)はハイレベル(High)の信号を出力する( $t = t_5$ )。この状態で、ストローブ信号(Strobe)を発生させても( $t = t_6$ )、ANDゲート664の出力はローレベル(Low)に固定される。補足すると、ストローブ信号(Strobe)がハイレベル(High)からローレベル(Low)に変化するまで、クロック信号(CLK)はハイレベル(High)を維持する。一方、ANDゲート665にはインバータを介して反転されたクロック信号が入力されているため、ANDゲート665からストローブ信号(Strobe)がラッチ668に入力され、シフトレジスタ666内のデータ信号がラッチ668にラッチされる。

40

50

## 【0082】

従って以上説明した実施例によれば、3本の信号線によって供給されるクロック信号、データ信号、ストローブ信号の3つの信号により、異なる2つのラッチへのデータ書き込みの制御を行うことが可能になる。なお、図13を参照して説明したようにモード信号(mode)を用いて、モード信号がローレベルである場合には、クロック信号(CLK)はハイレベル(High)を維持するように制御しても構わない。

## 【実施例3】

## 【0083】

図11は実施例3に従うシリアルインターフェース回路の構成を示す図である。

## 【0084】

この実施例のシリアルインターフェース回路660にも、実施例1～2と同様に、ストローブ信号(Strobe)とデータ信号(DATA)とクロック信号(CLK)とを夫々入力する3本の信号線661～663が接続されている。そして、シリアルデータ転送時には、クロック信号(CLK)に同期して転送されるデータ信号(CLK)を切替えることにより、複数のフリップフロップで構成されるシフトレジスタ669にデータ信号(DATA)を入力する。なお、シフトレジスタ669は実施例1～2と同様に4ビットのシフトレジスタになっている。

## 【0085】

シフトレジスタ669にデータ信号を転送終了後、信号線661からストローブ信号(Strobe)を入力し、転送されたデータ信号をラッチすることによりデータを有効にする。

## 【0086】

図11に示すように、ストローブ信号(Strobe)は、ANDゲート671を介してラッチ675に、ANDゲート672を介してラッチ676に、ANDゲート673を介してラッチ677に、ANDゲート674を介してラッチ678に入力される。

## 【0087】

また、ANDゲート671にはデータ信号(DATA)とクロック信号(CLK)が、ANDゲート672にはデータ信号(DATA)とインバータを介して反転されたクロック信号(CLK)が、ANDゲート673にはインバータを介して反転されたデータ信号(DATA)とクロック信号(CLK)が、ANDゲート674にはインバータを介して反転されたデータ信号(DATA)とインバータを介して反転されたクロック信号(CLK)が入力される。

## 【0088】

これにより、信号線661からハイレベル(High)のストローブ信号(Strobe)が入力された場合、データ信号(DATA)とクロック信号(CLK)が共にハイレベル(High)の時にANDゲート671が、データ信号(DATA)がハイレベル(High)でクロック信号(CLK)がローレベル(Low)の時にANDゲート672が、データ信号(DATA)がローレベル(Low)でクロック信号(CLK)がハイレベル(High)の時にANDゲート673が、データ信号(DATA)とクロック信号(CLK)が共にローレベル(Low)の時にANDゲート674が、ストローブ信号(Strobe)を通過させて、各ANDゲートからの出力に接続されているラッチにシフトレジスタ669からのデータ信号がラッチされる。

## 【0089】

従って以上説明した実施例に従えば、3本の信号線によって供給されるクロック信号、データ信号、ストローブ信号の3つの信号により、制御信号線を追加することなく異なる4つのラッチへのデータ書き込みの制御を行うことが可能になる。

## 【実施例4】

## 【0090】

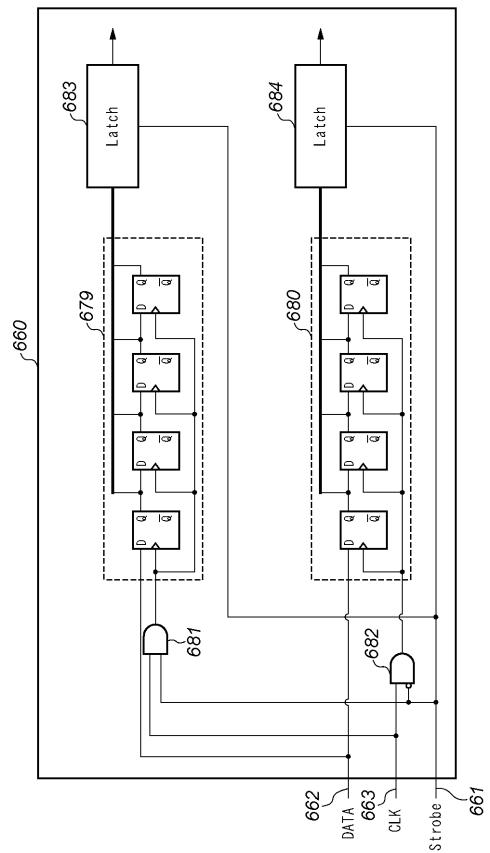

図12は実施例4に従うシリアルインターフェース回路の構成を示す図である。

## 【0091】

10

20

30

40

50

この実施例のシリアルインターフェース回路 660 にも、実施例 1 ~ 3 と同様に、ストローブ信号 (S t r o b e) とデータ信号 (D A T A) とクロック信号 (C L K) とを夫々入力する 3 本の信号線 661 ~ 663 が接続されている。

#### 【0092】

そして、図 12 に示されているように、ストローブ信号 (S t r o b e) はラッチ 683 とラッチ 684 に、データ信号 (D A T A) はシフトレジスタ 679 とシフトレジスタ 680 にそれぞれ共通に入力される。また、A N D ゲート 681 にはクロック信号 (C L K) とストローブ信号 (S t r o b e) が入力され、その出力はシフトレジスタ 679 を構成する 4 つのフリップフロップのクロックに入力される。一方、A N D ゲート 682 には、クロック信号 (C L K) とインバータを介して反転されたストローブ信号 (S t r o b e) が入力され、その出力はシフトレジスタ 680 を構成する 4 つのフリップフロップのクロックに入力される。10

#### 【0093】

このような構成によれば、信号線 663 からのクロック信号 (C L K) に同期して信号線 662 からデータ信号 (D A T A) をシリアル転送する際、ストローブ信号 (S t r o b e) がローレベル (L o w) の時、A N D ゲート 681 からの出力信号はローレベル (L o w) に固定され、その結果、シフトレジスタ 679 にはクロックが供給されず、データ信号のシフト転送は行われない。一方、A N D ゲート 682 からはクロック信号 (C L K) がそのまま出力されるので、クロック供給を受けたシフトレジスタ 680 はシリアル転送されたデータ信号 (D A T A) を取込むことができる。20

#### 【0094】

また、ストローブ信号 (S t r o b e) がハイレベル (H i g h) の時、A N D ゲート 681 からはクロック信号 (C L K) がそのまま出力され、クロック供給を受けたシフトレジスタ 679 はシリアル転送されたデータ信号 (D A T A) を取込むことができる。これに対して、A N D ゲート 682 からの出力信号はローレベル (L o w) レベルに固定され、その結果、シフトレジスタ 680 にはクロックが供給されず、データ信号のシフト転送は行われない。

#### 【0095】

その後、信号線 661 からストローブ信号 (S t r o b e) が入力されると、シフトレジスタ 679 のデータ信号はラッチ 683 で、シフトレジスタ 680 のデータ信号はラッチ 684 で夫々ラッチされる。なお、クロック供給を受けなかった側のシフトレジスタのデータ信号は、前回ラッチ動作を実施したデータ信号と基本的に同じであり、ストローブ信号の入力時には実質的に前回と同一データ信号を再ラッチすることになるため、動作上の問題はない。30

#### 【0096】

従って以上説明した実施例に従えば、3 本の信号線によって供給されるクロック信号、データ信号、ストローブ信号の 3 つの信号により、同一のタイミング (1 つのスロトープ信号入力) で異なる 2 つのシフトレジスト内のデータを夫々ラッチすることができる。

#### 【0097】

以上 4 つの実施例を説明したが、いずれの構成でも、3 本の信号線によって供給されるクロック信号、データ信号、ストローブ信号の 3 つの信号により、ラッチへの種々のデータ書き込み制御を行うことが可能になっている。従って、シリアルインターフェース回路の回路構成を少し変更し、A S I C 側からの信号送信シーケンスを多少変更するだけで、A S I C とモータドライバとの間のシリアル転送のための信号線の数や信号の種類を変更することなく種々の制御に柔軟に対応することができる。40

#### 【0098】

そして、以上のようにして取り込まれたデータ信号に従ってモータドライバに種々の設定が行われ、そして、その設定に従って、記録装置は D C モータとステッピングモータとを用いた 5 つのモータの駆動制御を行うことができる。

#### 【0099】

10

20

30

40

50

これは、記録装置全体として見ると、最小の設計変更や仕様変更で種々のモータ駆動制御を実現することにつながり、開発コストの削減、部品の共通化、回路基板上でのシリアル信号線の配線面積の最小化などに貢献する。

【0100】

なお、以上説明した実施例では、モータドライバを備えた装置として、インクジェット記録ヘッドを用いて記録を行う記録装置について説明したが、本発明はこれによって限定されるものではなく、例えば、複数のモータを駆動する他の機器に適用しても良い。

【0101】

また、記録装置が採用するモータの構成は、ここで説明した実施例に限定されるものではなく、排紙モータM5を搬送モータM2と兼用させて記録装置に搭載するモータの数を減らすようにした構成でも良いし、或いは、メンテナンスモータとしてDCモータを用いても良い。

【0102】

またさらに、以上説明したようなシリアルインターフェース回路は記録ヘッドとヘッドドライバとの間のシリアル転送にも適用可能である。例えば、このシリアルインターフェース回路を記録ヘッドの回路構成に適用すると、複数のラッチを用いた書き込み制御に複数のラッチ制御信号を必要とせず、そのための専用パッドも不要となる。従って、制御信号線を増やすことなく、即ち、FPCの配線数を増やすことなく、複雑な記録制御を実現することに貢献する。

【図面の簡単な説明】

【0103】

【図1】本発明の代表的な実施例であるインクジェット記録装置の全体構成の概要を示す外観斜視図である。

【図2】図1に示す記録装置の制御構成を示すブロック図である。

【図3】モータドライバと5つのモータとの関係を示すブロック図である。

【図4】モータドライバ642a(642b)の内部構造を示す図である。

【図5】実施例1に従うシリアルインターフェース回路の構成を示す図である。

【図6】図5に示すシリアルインターフェース回路の動作を説明するためのシリアル転送される信号のタイムチャートである。

【図7】図5に示すシリアルインターフェース回路の動作を説明するためのシリアル転送される信号の別のタイムチャートである。

【図8】実施例2に従うシリアルインターフェース回路の構成を示す図である。

【図9】図8に示すシリアルインターフェース回路の動作を説明するためのシリアル転送される信号のタイムチャートである。

【図10】図8に示すシリアルインターフェース回路の動作を説明するためのシリアル転送される信号の別のタイムチャートである。

【図11】実施例3に従うシリアルインターフェース回路の構成を示す図である。

【図12】実施例4に従うシリアルインターフェース回路の構成を示す図である。

【図13】図5に示すシリアルインターフェース回路の動作を説明するためのシリアル転送される信号の別のタイムチャートである。

【符号の説明】

【0104】

642、642a、642b モータドライバ

650 設定部

651a、651b 制御部

652a、652b、652c、652d Hブリッジ

660 シリアルインターフェース回路

661～663 信号線

664、665、671～674、681、682 ANDゲート

666、669、679、680 シフトレジスタ

10

20

30

40

50

6 6 7、6 6 8、6 7 5 ~ 6 7 8、6 8 3、6 8 4 ラッチ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

審査官 横山 佳弘

(56)参考文献 特開平08-265168 (JP, A)

特開平07-230418 (JP, A)

特開平04-101535 (JP, A)

特開平07-246723 (JP, A)

特開平09-207369 (JP, A)

特開2001-136076 (JP, A)

特開2002-009799 (JP, A)

特開2000-185423 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| G 06 F | 13 / 38 |

| B 41 J | 29 / 38 |

| H 03 M | 9 / 00  |

| G 06 F | 13 / 00 |

| B 41 J | 2 / 00  |