(19) 日本国特許庁(JP)

## (12) 特許公報(B1)

(11) 特許番号

特許第6013661号

(P6013661)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

(51) Int.Cl.

F 1

G06T 11/20 (2006.01)

G06T 15/80 (2011.01)G06T 11/20

G06T 15/80

請求項の数 26 (全 52 頁)

(21) 出願番号 特願2016-534976 (P2016-534976)

(86) (22) 出願日 平成26年7月2日 (2014.7.2)

(86) 国際出願番号 PCT/US2014/045299

(87) 国際公開番号 WO2015/030932

(87) 国際公開日 平成27年3月5日 (2015.3.5)

審査請求日 平成28年5月26日 (2016.5.26)

(31) 優先権主張番号 61/871,260

(32) 優先日 平成25年8月28日 (2013.8.28)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/321,309

(32) 優先日 平成26年7月1日 (2014.7.1)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】グラフィックス処理におけるターゲット独立ステンシル

## (57) 【特許請求の範囲】

## 【請求項 1】

グラフィックスデータをレンダリングする方法であって、

画像のパスの1つまたは複数のアンチエイリアスの各々についてのカバレージ値を決定

するためのステンシルサンプリングレートを決定することと、ここにおいて、前記ステン

シルサンプリングレートは、前記アンチエイリアス画素の各々について、前記ステンシル

サンプリングレートでサンプリングされる前記アンチエイリアス画素の各々のサンプルを

記憶するためのステンシルバッファにおけるメモリ割当てを示す。

前記ステンシルサンプリングレートとは別々に、前記ステンシルサンプリングレートよ

りも少ないと有するレンダターゲットパラメータを決定することと、ここにおいて、前

記レンダターゲットパラメータは、前記アンチエイリアス画素の各々について、前記パス

の各レンダリングされたアンチエイリアス画素を記憶するためのフレームバッファにお

けるメモリ割当てを示す。

前記ステンシルサンプリングレートと前記レンダターゲットパラメータとを使用して前

記パスをレンダリングすることと

を備える方法。

## 【請求項 2】

前記ステンシルサンプリングレートとは異なる値である深度パラメータを決定すること

をさらに備える、請求項 1 に記載の方法。

## 【請求項 3】

10

20

前記深度パラメータを決定することが、前記レンダターゲットパラメータに等しい深度パラメータを決定すること、ここにおいて、前記深度パラメータが、1つまたは複数の他の画素に対する前記パスの前記アンチエイリアス画素の各々の深度を示す、を備える、請求項2に記載の方法。

【請求項4】

前記レンダターゲットパラメータとは異なる値であるラスタライゼーションパラメータを決定すること、ここにおいて、前記ラスタライゼーションパラメータが、前記パスの前記アンチエイリアス画素の各々についてのラスタライゼーションサンプリングレートを示す、をさらに備える、請求項1に記載の方法。

【請求項5】

10

前記パスをレンダリングすることが、

前記ステンシルサンプリングレートを使用して前記ステンシルバッファに前記パスをレンダリングすることと、ここにおいて、前記ステンシルバッファが、シェーディングされることになる前記パスのアンチエイリアス画素を示す、

前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記パスをラスタライズすることと

を備える、請求項1に記載の方法。

【請求項6】

前記ステンシルバッファに前記パスをレンダリングする間に、前記パスのためのバウンディングボックスを決定すること、ここにおいて、前記バウンディングボックスを決定することが、前記パスの複数の最大境界点を決定することを備える、

20

をさらに備え、

前記パスをラスタライズすることが、前記パスのための前記バウンディングボックスを決定することと、前記パスをラスタライズすることとが、1つのレンダリングパスの中で実行されるように、前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記バウンディングボックスをラスタライズすることを備える、請求項5に記載の方法。

【請求項7】

前記パスの前記複数の最大境界点を決定することが、上部境界点、下部境界点、右境界点および左境界点を決定することを備える、請求項6に記載の方法。

30

【請求項8】

グラフィックスをレンディングするための装置であって、

ステンシルサンプリングレートでサンプリングされるアンチエイリアス画素のサンプルを記憶するように構成されたステンシルバッファと、前記アンチエイリアス画素は、少なくとも画像のパスの一部を形成する、

レンダリングされたアンチエイリアス画素を記憶するように構成されたフレームバッファと、

画像のパスの1つまたは複数のアンチエイリアス画素の各々についてのカバレージ値を決定するためのステンシルサンプリングレートを決定することと、ここにおいて、前記ステンシルサンプリングレートは、前記アンチエイリアス画素の各々について、前記ステンシルサンプリングレートでサンプリングされる前記アンチエイリアス画素の各々のサンプルを記憶するためのステンシルバッファにおけるメモリ割当てを示す、

40

前記ステンシルサンプリングレートとは別々に、前記ステンシルサンプリングレートよりも少ない値を有するレンダターゲットパラメータを決定することと、ここにおいて、前記レンダターゲットパラメータは、前記アンチエイリアス画素の各々について、前記パスの各レンダリングされたアンチエイリアス画素を記憶するためのフレームバッファにおけるメモリ割当てを示す、

前記ステンシルサンプリングレートと前記レンダターゲットパラメータとを使用して前記パスをレンダリングすることと

を行うように構成されたグラフィックス処理ユニット(GPU)と

50

を備える装置。

【請求項 9】

前記 G P U が、前記ステンシルサンプリングレートとは異なる値である深度パラメータを決定することを行うようにさらに構成された、請求項 8 に記載の装置。

【請求項 10】

前記深度パラメータを決定するために、前記 G P U が、前記レンダターゲットパラメータに等しい深度パラメータを決定すること、ここにおいて、前記深度パラメータが、1つまたは複数の他の画素に対する前記パスの前記アンチエイリアス画素の各々の深度を示す、を行うように構成された、請求項 9 に記載の装置。

【請求項 11】

前記 G P U が、前記レンダターゲットパラメータとは異なる値であるラスタライゼーションパラメータを決定すること、ここにおいて、前記ラスタライゼーションパラメータが、前記パスの前記アンチエイリアス画素の各々についてのラスタライゼーションサンプリングレートを示す、を行うように構成された、請求項 8 に記載の装置。

【請求項 12】

前記パスをレンダリングするために、前記 G P U が、

前記ステンシルサンプリングレートを使用して前記ステンシルバッファに前記パスをレンダリングすることと、ここにおいて、前記ステンシルバッファが、シェーディングされることになる前記パスのアンチエイリアス画素を示す、

前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記パスをラスタライズすることと

を行うように構成された、請求項 8 に記載の装置。

【請求項 13】

前記 G P U が、

前記ステンシルバッファに前記パスをレンダリングする間に、前記パスのためのバウンディングボックスを決定すること、ここにおいて、前記バウンディングボックスを決定することが、前記パスの複数の最大境界点を決定することを備える、

を行うようにさらに構成された、

前記パスをラスタライズするために、前記 G P U が、前記パスのための前記バウンディングボックスを決定することと、前記パスをラスタライズすることとが、1つのレンダリングパス中で実行されるように、前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記バウンディングボックスをラスタライズすることを行うように構成された、請求項 12 に記載の装置。

【請求項 14】

前記パスの前記複数の最大境界点を決定するために、前記 G P U が、上部境界点、下部境界点、右境界点および左境界点を決定することを行うように構成された、請求項 13 に記載の装置。

【請求項 15】

グラフィックスデータをレンダリングするための装置であって、

画像のパスの1つまたは複数のアンチエイリアス画素の各々についてのカバレージ値を決定するためのステンシルサンプリングレートを決定するための手段と、ここにおいて、前記ステンシルサンプリングレートは、前記アンチエイリアス画素の各々について、前記ステンシルサンプリングレートでサンプリングされる前記アンチエイリアス画素の各々のサンプルを記憶するためのステンシルバッファにおけるメモリ割当てを示す、

前記ステンシルサンプリングレートとは別々に、前記ステンシルサンプリングレートよりも少ない値を有するレンダターゲットパラメータを決定するための手段と、ここにおいて、前記レンダターゲットパラメータは、前記アンチエイリアス画素の各々について、前記パスの各レンダリングされたアンチエイリアス画素を記憶するためのフレームバッファにおけるメモリ割当てを示す、

前記ステンシルサンプリングレートと前記レンダターゲットパラメータとを使用して前

10

20

30

40

50

記パスをレンダリングするための手段と

を備える装置。

【請求項 16】

前記ステンシルサンプリングレートとは異なる値である深度パラメータを決定するための手段をさらに備える、請求項 15 に記載の装置。

【請求項 17】

前記深度パラメータを決定するための前記手段が、前記レンダターゲットパラメータに等しい深度パラメータを決定するための手段、ここにおいて、前記深度パラメータが、1つまたは複数の他の画素に対する前記パスの前記アンチエイリアス画素の各々の深度を示す、を備える、請求項 16 に記載の装置。 10

【請求項 18】

前記レンダターゲットパラメータとは異なる値であるラスタライゼーションパラメータを決定するための手段、ここにおいて、前記ラスタライゼーションパラメータが、前記パスの前記アンチエイリアス画素の各々についてのラスタライゼーションサンプリングレートを示す、をさらに備える、請求項 15 に記載の装置。 20

【請求項 19】

前記パスをレンダリングするための前記手段が、

前記ステンシルサンプリングレートを使用して前記ステンシルバッファに前記パスをレンダリングするための手段と、ここにおいて、前記ステンシルバッファが、シェーディングされることになる前記パスのアンチエイリアス画素を示す、 20

前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記パスをラスタライズするための手段と

を備える、請求項 15 に記載の装置。

【請求項 20】

前記ステンシルバッファに前記パスをレンダリングする間に、前記パスのためのバウンディングボックスを決定するための手段、ここにおいて、前記バウンディングボックスを決定することが、前記パスの複数の最大境界点を決定することを備える、

をさらに備え、

前記パスをラスタライズするための前記手段が、前記パスのための前記バウンディングボックスを決定することと、前記パスをラスタライズすることとが、1つのレンダリングパス中で実行されるように、前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記バウンディングボックスをラスタライズするための手段を備える、請求項 19 に記載の装置。 30

【請求項 21】

実行されたとき、グラフィックス処理ユニット (GPU) に、

画像のパスの1つまたは複数のアンチエイリアス画素の各々についてのカバレージ値を決定するためのステンシルサンプリングレートを決定することと、ここにおいて、前記ステンシルサンプリングレートは、前記アンチエイリアス画素の各々について、前記ステンシルサンプリングレートでサンプリングされる前記アンチエイリアス画素の各々のサンプルを記憶するためのステンシルバッファにおけるメモリ割当てを示す、 40

前記ステンシルサンプリングレートとは別々に、前記ステンシルサンプリングレートよりも少ない値を有するレンダターゲットパラメータを決定することと、ここにおいて、前記レンダターゲットパラメータは、前記アンチエイリアス画素の各々について、前記パスの各レンダリングされたアンチエイリアス画素を記憶するためのフレームバッファにおけるメモリ割当てを示す、

前記ステンシルサンプリングレートと前記レンダターゲットパラメータとを使用して前記パスをレンダリングすることと

を行わせる命令を記憶した非一時的コンピュータ可読媒体。

【請求項 22】

前記命令が、前記 GPU に、前記ステンシルサンプリングレートとは異なる値である深 50

度パラメータを決定することをさらに行わせる、請求項 2 1 に記載の非一時的コンピュータ可読媒体。

【請求項 2 3】

前記深度パラメータを決定するために、前記命令が、前記 G P U に、前記レンダターゲットパラメータに等しい深度パラメータを決定すること、ここにおいて、前記深度パラメータが、1 つまたは複数の他の画素に対する前記パスの前記アンチエイリアス画素の各々の深度を示す、を行わせる、請求項 2 2 に記載の非一時的コンピュータ可読媒体。

【請求項 2 4】

前記命令が、前記 G P U に、前記レンダターゲットパラメータとは異なる値であるラストライゼーションパラメータを決定すること、ここにおいて、前記ラストライゼーションパラメータが、前記パスの前記アンチエイリアス画素の各々についてのラストライゼーションサンプリングレートを示す、をさらに行わせる、請求項 2 1 に記載の非一時的コンピュータ可読媒体。

【請求項 2 5】

前記パスをレンダリングするために、前記命令が、前記 G P U に、

前記ステンシルサンプリングレートを使用して前記ステンシルバッファに前記パスをレンダリングすることと、ここにおいて、前記ステンシルバッファが、シェーディングされることになる前記パスのアンチエイリアス画素を示す、

前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記パスをラスタライズすることと

を行わせる、請求項 2 1 に記載の非一時的コンピュータ可読媒体。

【請求項 2 6】

前記命令が、前記 G P U に、

前記ステンシルバッファに前記パスをレンダリングする間に、前記パスのためのバウンディングボックスを決定すること、ここにおいて、前記バウンディングボックスを決定することが、前記パスの複数の最大境界点を決定することを備える、

を行わせる、

前記パスをラスタライズするために、前記 G P U が、前記パスのための前記バウンディングボックスを決定することと、前記パスをラスタライズすることとが、1 つのレンダリングパス中で実行されるように、前記レンダターゲットパラメータと前記ステンシルバッファとを使用して前記バウンディングボックスをラスタライズすることを行うように構成された、請求項 2 5 に記載の非一時的コンピュータ可読媒体。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

[0001] 本出願は、その内容全体が参照により本明細書に組み込まれる、2013年8月28日に出願された米国仮特許出願第61/871,260号の利益を主張する。

【0 0 0 2】

[0002] 本開示は、グラフィックス処理に関し、より詳細には、パスレンダリングのための技法に関する。

【背景技術】

【0 0 0 3】

[0003] パスレンダリングは、その各々が1つまたは複数のパスセグメントを含み得る、(あるいは、本明細書で「パス」と呼ばれる)2次元(2D)ベクタグラフィックスパス(vector graphics paths)のレンダリングを指す場合がある。パスが2つ以上のパスセグメントを含むとき、個々のパスセグメントは、同じタイプまたは異なるタイプのものであり得る。パスセグメントのタイプは、たとえば、線と、橒円弧と、2次ベジェ曲線と、3次ベジェ曲線とを含み得る。いくつかの例では、パスセグメントタイプは、たとえば、Open Vector Graphics(OpenVG)APIなど、標準ベクタグラフィックスアプリケーションプログラミングインターフェース(API)に従って定義

10

20

30

40

50

され得る。

#### 【0004】

[0004]バスレンダリングは、中央処理装置（CPU）で実装され得る。しかしながら、そのような手法は、CPU集中的であり得、したがって、他のCPUタスクに利用可能なCPU処理サイクルの量を制限する可能性がある。さらに、場合によっては、所望の詳細レベルでバスセグメントをレンダリングするために、比較的大量のデータがグラフィックス処理ユニット（GPU）に転送される必要があり得る。比較的大量のデータは、データを記憶するとき、かなりの量のメモリストレージスペースを消費する場合があり、データをGPUに転送するとき、かなりの量のメモリ帯域を消費する場合がある。

#### 【発明の概要】

10

#### 【0005】

[0005]本開示は、バスのファイル（filling）とダッシング（dashing）とを用いてグラフィックスデータを生成するための技法を含む。たとえば、バスをファイルするときに、本開示の態様によれば、GPUは、メモリが（レンダターゲットと呼ばれる）レンダリングされたデータに割り当てられるレートとは異なるレートでステンシル（stenciling）動作を実行することができる。すなわち、ステンシル動作を実行するためのステンシルパラメータは、レンダリングされたデータを記憶するためのレンダターゲットパラメータから独立して指定され得る。

#### 【0006】

[0006]さらに、ダッシングに関して、本開示の態様によれば、GPUは、ダッシュ特性を決定し、単一のレンダリングバスでダッシングを実行することができる。たとえば、GPUは、セグメントが決定されるときにセグメントの各々の長さを計算し、各ダッシュセグメントのための開始口けーション（たとえば、テクスチャ座標）を決定するために長さ情報を適用することができる。

20

#### 【0007】

[0007]一例では、グラフィックスデータをレンダリングする方法は、画像のバスの各アンチエイリアス画素のカバレージ値を決定するためのサンプリングレートを示すステンシルパラメータを決定することと、ステンシルパラメータとは別々に、バスの各アンチエイリアス画素のためのメモリ割当てを示すレンダターゲットパラメータを決定することと、ステンシルパラメータとレンダターゲットパラメータとを使用してバスをレンダリングすることとを含む。

30

#### 【0008】

[0008]別の例では、グラフィックスをレンディングするための装置は、画像のバスの各アンチエイリアス画素のカバレージ値を決定するためのサンプリングレートを示すステンシルパラメータを決定することと、ステンシルパラメータとは別々に、バスの各アンチエイリアス画素のためのメモリ割当てを示すレンダターゲットパラメータを決定することと、ステンシルパラメータとレンダターゲットパラメータとを使用してバスをレンダリングすることとを行うように構成されたグラフィックス処理ユニット（GPU）を含む。

#### 【0009】

[0009]別の例では、グラフィックスデータをレンダリングするための装置は、画像のバスの各アンチエイリアス画素のカバレージ値を決定するためのサンプリングレートを示すステンシルパラメータを決定するための手段と、ステンシルパラメータとは別々に、バスの各アンチエイリアス画素のためのメモリ割当てを示すレンダターゲットパラメータを決定するための手段と、ステンシルパラメータとレンダターゲットパラメータとを使用してバスをレンダリングするための手段とを含む。

40

#### 【0010】

[0010]別の例では、非一時的コンピュータ可読媒体は、実行されたとき、グラフィックス処理ユニット（GPU）に、画像のバスの各アンチエイリアス画素のカバレージ値を決定するためのサンプリングレートを示すステンシルパラメータを決定することと、ステンシルパラメータとは別々に、バスの各アンチエイリアス画素のためのメモリ割当てを示す

50

レンダターゲットパラメータを決定することと、ステンシルパラメータとレンダターゲットパラメータとを使用してパスをレンダリングすることとを行わせる命令を記憶する。

【0011】

[0011]別の例では、グラフィックスデータをレンダリングする方法は、グラフィックス処理ユニット( G P U )を用いて、破線の複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットを決定することと、ここにおいて、複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットが、現在のセグメントより順序が前のセグメントの長さの累積に基づく、現在のセグメントのロケーションを決定するために、テクスチャオフセットを適用することを含めて現在のセグメントをピクセルシェーディングすることとを含む。

10

【0012】

[0012]別の例では、グラフィックスデータをレンダリングするための装置は、破線の複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットを決定することと、ここにおいて、複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットが、現在のセグメントより順序が前のセグメントの長さの累積に基づく、現在のセグメントのロケーションを決定するために、テクスチャオフセットを適用することを含めて現在のセグメントをピクセルシェーディングすることとを行うように構成されたグラフィックス処理ユニット( G P U )を含む。

【0013】

[0013]別の例では、グラフィックスデータをレンダリングするための装置は、グラフィックス処理ユニット( G P U )を用いて、破線の複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットを決定するための手段と、ここにおいて、複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットが、現在のセグメントより順序が前のセグメントの長さの累積に基づく、現在のセグメントのロケーションを決定するために、テクスチャオフセットを適用することを含めて現在のセグメントをピクセルシェーディングするための手段とを含む。

20

【0014】

[0014]別の例では、非一時的コンピュータ可読媒体は、実行されたとき、構成されたグラフィックス処理ユニット( G P U )に、破線の複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットを決定することと、ここにおいて、複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットが、現在のセグメントより順序が前のセグメントの長さの累積に基づく、現在のセグメントのロケーションを決定するために、テクスチャオフセットを適用することを含めて現在のセグメントをピクセルシェーディングすることとを行わせる、命令を記憶する。

30

【0015】

[0015]本開示の1つまたは複数の例の詳細が、添付の図面および下記の説明に記載される。本開示の他の特徴、目的、および利点は、説明および図面、ならびに特許請求の範囲から明らかになろう。

【図面の簡単な説明】

【0016】

40

【図1】[0016]本開示の技法を実装するために使用され得る例示的なコンピューティングデバイスを示すブロック図。

【図2】[0017]図1のコンピューティングデバイスのC P U、G P U、およびメモリをより詳細に示すブロック図。

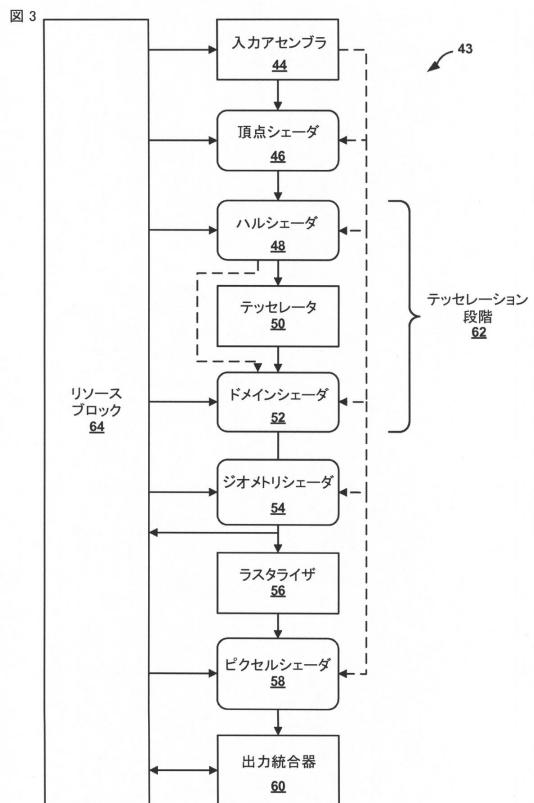

【図3】[0018]本開示の技法を実行するために使用され得る例示的なグラフィックスバイオペラインを示す概念図。

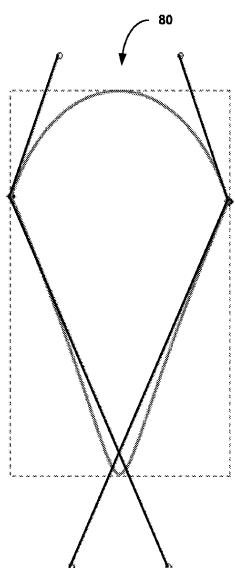

【図4】[0019]レンダリングされることになる例示的なパスの図。

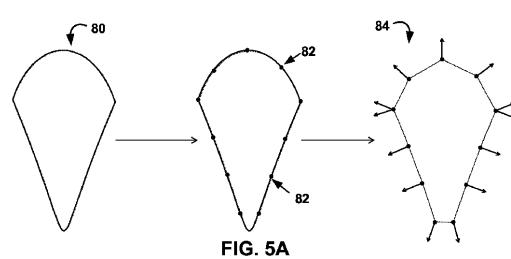

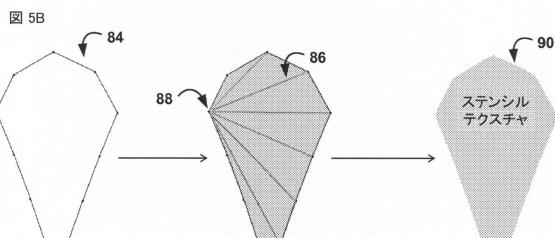

【図5 A】[0020]図4に示されるパスのためのフィル動作の例示的なシーケンスを示す図。

【図5 B】図4に示されるパスのためのフィル動作の例示的なシーケンスを示す図。

50

【図5C】図4に示されるパスのためのファイル動作の例示的なシーケンスを示す図。

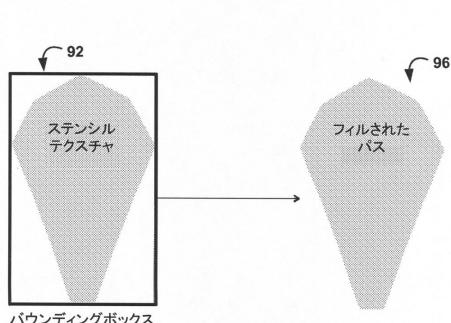

【図6】[0021]ステンシル動作を示す概念図。

【図7】[0022]本開示の態様による、例示的なファイル動作を示す概念図。

【図8】[0023]本開示の態様による、レンダリング中の帯域幅を示すグラフ。

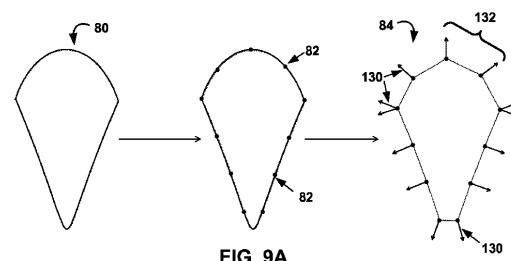

【図9A】[0024]図4に示されるパスのための例示的なダッシング動作を示す一連の図。

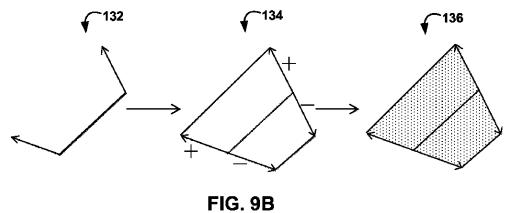

【図9B】図4に示されるパスのための例示的なダッシング動作を示す一連の図。

【図9C】図4に示されるパスのための例示的なダッシング動作を示す一連の図。

【図9D】図4に示されるパスのための例示的なダッシング動作を示す一連の図。

【図10】[0025]本開示の態様による、グラフィックスデータをレンダリングするための例示的なプロセスを示す流れ図。

【図11】[0026]本開示の態様による、ダッシングするための例示的なプロセスを示す流れ図。

【発明を実施するための形態】

【0017】

[0027]本開示は、GPUベースのパスレンダリングを実行するための技法に関する。パスレンダリングは、その各々が1つまたは複数のパスセグメントを含み得る（あるいは、本明細書で「パス」と呼ばれる）2次元（2D）ベクタグラフィックスパスのレンダリングを指す場合がある。パスが2つ以上のパスセグメントを含むとき、個々のパスセグメントは、同じタイプまたは異なるタイプのものであり得る。パスセグメントのタイプは、たとえば、線と、橢円弧と、2次ベジェ曲線と、3次ベジェ曲線とを含み得る。いくつかの例では、パスセグメントタイプは、たとえば、Open Vector Graphics（OpenVG）APIなど、標準ベクタグラフィックスアプリケーションプログラミングインターフェース（API）に従って定義され得る。

【0018】

[0028]GPUは、通常、1つまたは複数の3DグラフィックスAPIに対応するように設計された3次元（3D）グラフィックスライブラリを実装する。今日使用されている一般的な3DグラフィックスAPIは、対応デバイスがパスレンダリングコマンドをサポートすることを必要としないため、多くの場合、現代的なGPUがパスレンダリングコマンド用のハードウェアアクセラレーションを提供することはほとんどない。たとえば、現代的なGPUで実装される典型的な3Dグラフィックスライブラリは、（たとえば、点、線、および三角形など）低次の、湾曲していない3Dグラフィックスプリミティブをラスタライズするように設計されるが、（たとえば、橢円弧、およびベジェ曲線など）湾曲したパスレンダリングプリミティブを直接的にレンダリングすることができないラスタライザを含み得る。

【0019】

[0029]パスレンダリングに関する一手法は、パスレンダリングコマンドを実行する目的で部分的なGPUハードウェアアクセラレーションを提供するために3D GPUライブラリを使用することに関連し得る。この手法は、パスセグメントを、GPUによってラスタライズされ得る、1つまたは複数の低次の、湾曲していない3Dグラフィックスプリミティブに変換するために、中央処理装置（CPU）を用いてパスセグメントを前処理することに関連する。たとえば、CPUは、湾曲したパスセグメント（たとえば、橢円弧またはベジェ曲線）を、パスセグメントの曲率を近似する比較的小さな三角形のセットにテッセレートすることができ、GPUを使用して三角形のセットをレンダリングさせることができる。しかしながら、そのような手法は、CPU集中的であり得、したがって、他のCPUタスクに利用可能なCPU処理サイクルの量を制限する可能性がある。さらに、場合によっては、所望の詳細レベルでパスセグメントをレンダリングするために、比較的に多数の三角形が必要とされる場合がある。比較的に多数の三角形は、データを記憶するとき、かなりの量のメモリストレージスペースを消費する場合があり、データをGPUに転送するとき、かなりの量のメモリ帯域を消費する場合がある。

【0020】

10

20

30

40

50

[0030] パスレンダリングコマンドの実行に部分的 - 全体的 G P U ハードウェアアクセラレーションを提供するための別の手法は、専用の、ハードウェアアクセラレーションされたパスレンダリングパイプラインをサポートするように G P U のアーキテクチャを変更することを伴い得る。しかしながら、一般的な 3 D グラフィックス A P I (たとえば、 M i c r o s o f t (登録商標) D i r e c t X 1 1 ( D X ) A P I ) は、一般に、 G P U アーキテクチャが専用のパスレンダリングパイプラインを含むことを必要としないので、そのような手法は、特定の 3 D グラフィックス A P I (たとえば、 D X 1 1 A P I ) に準拠するすべての G P U によってサポートされることが保証されるであろうクロスプラットフォームな、ハードウェアアクセラレーションされたパスレンダリングソリューションを生じない。

10

### 【 0 0 2 1 】

[0031] いくつかの例では、受け取ったパスセグメントを複数のラインセグメントにテッセレートすることと、3 D グラフィックスパイプラインを使用してテッセレートされたラインセグメントをレンダリングすることとを行うように G P U が構成された G P U ベースのパスレンダリング技法が使用され得る。パスセグメントをラインセグメントにテッセレートするために G P U を使用することによって、パスセグメントを前処理する負担を C P U から取り除き、それによって、他の C P U タスクのために処理リソースを解放する。さらに、いくつかの例では、 G P U は、テッセレーション演算を実行するために、いくつかの例では、 G P U が、 C P U よりも効率的な形でパスセグメントをレンダリングするのを可能にする、高並列の現代的な G P U テッセレーションアーキテクチャを利用することができます。加えて、テッセレーションは、 C P U 内ではなく、 G P U 内で発生するため、多数のテッセレートされたプリミティブは、システムメモリ内に記憶される必要がなく、 C P U から G P U に渡される必要がなく、それによって、パスレンダリングに必要とされるメモリフットプリント、ならびに、パスレンダリングに必要とされるメモリ帯域幅を削減する。

20

### 【 0 0 2 2 】

[0032] いくつかの例では、 G P U は、アンチエイリアシングを実行するためにマルチサンプルアンチエイリアシング ( M S A A : multi-sample anti-aliasing ) 技法を使用することができる。たとえば、画素は、一様に着色され、常に同じ形状にあり、これにより、レンダリングされた画像の線の外観にジャギーが生じ得る。 M S A A では、単一の画素に対して複数のサンプルが生成され得る。サンプルは、次いで、最終画素値を決定するために、組み合わされ得る (たとえば、平均化され得る)。

30

### 【 0 0 2 3 】

[0033] したがって、いくつかの事例では、 G P U は、表示されている解像度よりも高い解像度で画像をレンダリングすることができる。 G P U は、次いで、表示より前に適切なサイズに画像をダウンサンプリングすることができる。結果は、オブジェクトの縁に沿って画素の 1 つの線から別の線へのよりスムーズな遷移であり得る。 M S A A は、 4 、 8 、 1 6 、または他の値の係数を使用して実行され得る。 M S A A を実行するとき、 G P U は、 M S A A レートで深度およびステンシル動作をサンプリングし、 M S A A レートでメモリを割り当て、 M S A A レートにおいて画素をラスタライズすることができる (たとえば、 1 6 × の M S A A は、画素ごとに 1 6 × の深度 / ステンシルサンプルと、画素ごとに 1 6 × のメモリ割当てと、画素ごとに 1 6 × のラスタライゼーションサンプルとを含む)。

40

### 【 0 0 2 4 】

[0034] 概して、「ターゲット」は、レンダリングされた画素に割り当てられるメモリを指す場合がある。一般に、アンチエイリアス画像に関して、レンダリングされたターゲットのためのラスタライゼーションおよびメモリ割当てなどのグラフィックス演算を実行するサンプリングレートは、互いに対応し、たとえば、 1 : 1 になる。したがって、説明のための一例では、 G P U は、ラスタライゼーションのために画素ごとに 1 6 × のサンプリングレートを使用し、画素ごとに 1 6 個のサンプルを記憶するようにメモリを割り当て得る。しかしながら、ターゲット独立ラスタライゼーション ( T I R : target independent

50

rasterization) では、ラスタライゼーションプロセスのサンプリングレートが、レンダリングされた画像に割り当てられるメモリから独立して指定され得る。たとえば、画素ごとに 4 つのサンプルのサンプリングレートがラスタライゼーションのために使用され得、一方、画像の画素の色を記憶するためのメモリ割当ては、画像中の画素ごとに 1 色になり得る。

#### 【 0 0 2 5 】

[0035] T I R により、ターゲットに割り当てられるメモリから独立してラスタライゼーションレートを指定することが可能になるが、他のレンダリング動作は、結び合わされたままであり得る。たとえば、(以下でより詳細に説明する) 深度およびステンシル動作は、一般に、レンダターゲットに関連付けられ得る。したがって、単一のレンダターゲットは、画素ごとに指定され、深度およびステンシル動作はまた、同じレート(すなわち、1 × のサンプリングレート) で実行され得る。 10

#### 【 0 0 2 6 】

[0036] 本開示の態様によれば、G P U は、ステンシル動作中に T I R の概念を活用することができる。たとえば、G P U は、特定の画素に割り当てられるメモリの量よりも高いレートでステンシルを実行することができる。すなわち、ステンシル動作がスーパーサンプリングされる (super sampled)、たとえば、各画素が 16 個のサンプルを有することになるプロセスでは、G P U は、(スーパーサンプリングされた画素のうちの) 画素のどのサンプルが、ステンシルテストにパスしたか、たとえば、特定のパスの内側にあったかに基づいて画素ごとにカバレージ値を計算することによってレンダリングすることができる。パフォーマンスの改善のために、レンダターゲットは、1 × でサンプリングされ得、一方、ステンシルは、16 × でサンプリングされ得る。G P U は、サンプルごとのステンシルテストに基づいて各画素にカバレージ値を割り当て得る。ターゲットとラスタライゼーションレートとから独立してステンシルサンプリングレートを指定することは、本明細書ではステンシル T I R と呼ばれる場合がある。 20

#### 【 0 0 2 7 】

[0037] ステンシル T I R プロセスは、パスレンダリング中に適用され得る。たとえば、パスレンダリング時に、G P U は、一般に、パスをフィルするために、ラインセグメントにパスをテッセレートし、ラインセグメントをピボット点に接続して三角形を形成し、(いくつかの事例では、深度テストを実行することを含めて) 三角形をステンシルバッファにレンダリングするという例示的な機能を実行し得、ここで、ステンシルバッファは、画像の可視画素インを示す。フィルプロセスの次の、場合によっては最後のステップは、ステンシルテストを有効化した状態でバウンディングボックスをレンダリングすることと、フレームバッファにステンシルバッファのコンテンツをコピーすることを行うことである。この手法は、2 つのレンダリングパス、たとえば、バウンディングボックスをレンダリングする 1 つのパスと、テクスチャをレンダリングする 1 つのパスとを必要とする。 30

#### 【 0 0 2 8 】

[0038] 本開示の態様によれば、G P U は、バウンディングボックスを前処理する必要なしに単一のレンダリングパスでパスをフィルすることができる。たとえば、いくつかの例では、G P U は、ラスタライザ段階において使用されるハードウェアを含み得るバウンディングボックスユニットを組み込み得る。たとえば、プリミティブがステンシルバッファにレンダリングされるとき、バウンディングボックスユニットは、所与のパスの最外座標点(たとえば、上極値、下極値、左極値、および右極値)を追跡することができる。最外座標点は、これらの点がパスの最外境界を示すという点で、最大境界点と呼ばれる場合もある。ステンシルが完了した後、バウンディングボックスユニットは、最外座標点に基づいて境界長方形を決定している。 40

#### 【 0 0 2 9 】

[0039] 上記の例では、パスのプリミティブがステンシルバッファにレンダリングされる(プリミティブはステンシルにのみ影響を及ぼす)ので、G P U は、パスのプリミティブをシェーディングしない。G P U は、次に、色を割り当てるためにステンシルバッファを 50

使用してバウンディングボックスをレンダリングすることができる。本開示の態様によれば、ステンシルを実行し、バウンディングボックスを決定した後に別の描画呼出しを必要としない。むしろ、G P Uは、単一のパスでステンシルT I Rを使用してバウンディングボックスをラスタライズする。

【0030】

[0040]このようにして、G P Uは、たとえば、G P Uにおいてプリミティブを決定すること、C P Uにおいてバウンディングボックスを決定すること、G P U上で着色動作を実行することを行うのではなく、単一のパスでフィルすることができる（たとえば、ステンシルおよび着色動作を実行することができる）。すなわち、本開示の技法は、G P Uが、ステンシルと着色の両方が単一のパスで実行され得るように、（たとえば、G P Uが次いでラスタライザにプッシュすることができるテッセレーション中に）バウンディングボックスを決定することを可能にするバウンディングボックス最適化を含む。10

【0031】

[0041]本開示の他の態様は、ダッシング（破線など）に関する。たとえば、ストロークされたパスをダッシングするとき、G P Uは、（セグメント順序と呼ばれる）順序でダッシュセグメントをレンダリングすることができ、前のセグメントが途切れた場所に1つのセグメントを生成することができる。すなわち、G P Uは、前のセグメントをシェーディングした後にのみ、ダッシュパターンの各セグメントのための開始口ケーションを決定する。そのような計算は、正しい開始口ケーションを決定するためにダッシュの各セクションのための口ケーションが処理される必要があるので、グラフィックス処理の並列性を低減し、2つ以上のレンダリングパスを実行することを必要とし得る。20

【0032】

[0042]本開示の態様によれば、G P Uは、ダッシュ特性を決定し、単一のパス、たとえば、単一のレンダリングパスでダッシングを実行することができる。たとえば、G P Uは、たとえば、ジオメトリシェーディング中にセグメントが決定されると、セグメントの各々の長さを計算することができる。すなわち、G P Uは、現在のセグメントの開始口ケーションを決定するために、セグメント、たとえば、セグメント順序で現在のセグメントの前のセグメントの長さを累積することができる。長さのこの累積は、本明細書では、「プレフィックス長さ」または「プレフィックス総和長さ」と呼ばれる場合がある。G P Uはまた、線の全長を決定することができる。30

【0033】

[0043]説明のための一例では、G P Uは、破線の第1のセグメントを決定することができる。G P Uはまた、破線の第2のセグメントを決定することができる。G P Uは、前のセグメントのプレフィックス総和長さに基づいて第2のセグメントのための開始口ケーションを決定することができる。すなわち、G P Uは、前のセグメント、すなわち、第1のセグメントの長さの累積に基づいて第2のセグメントのための開始口ケーションを決定することができる。G P Uはまた、破線の第3のセグメントを決定することができる。この場合も、G P Uは、前のセグメントのプレフィックス総和長さに基づいて第3のセグメントのための開始口ケーションを決定することができる。すなわち、G P Uは、前のセグメント、すなわち、第1のセグメントと第2のセグメントとの長さの累積に基づいて第3のセグメントのための開始口ケーションを決定することができる。G P Uは、線のセグメントの各々の開始口ケーションが決定されるまで、このようにして継続することができる。40

【0034】

[0044]いくつかの例では、破線は、可視セグメントと不可視セグメントとを含み得る。たとえば、G P U 1 2は、可視（たとえば、線のダッシュ）であるセグメントのための色を決定し、不可視（たとえば、着色ダッシュ間の破線の部分）であるセグメントを破棄することができる。G P U 1 2は、シェーディングされているセグメントの口ケーションに基づいて（たとえば、本明細書では、ピクセルシェーディング中のフラグメントと互換的に呼ばれる場合がある）セグメントを保持すべきかどうかを決定することができる。一例として上記で説明した3つのセグメントに関して、破線の第1および第3のセグメントを

仮定し、第2のセグメントは、着色されていない、第1のセグメントと第3のセグメントとを分離する不可視セグメントである。G P U 1 2は、セグメントのロケーションに基づいて、ピクセルシェーディング中にセグメントを保持（たとえば、色を用いてシェーディング）すべきか、または破棄すべきかを決定することができる。すなわち、G P U 1 2は、第1のセグメントのロケーションに基づいて第1のセグメントが保持されることを決定し、第2のセグメントのロケーションに基づいて第2のセグメントが破棄されることを決定し、第3のセグメントのロケーションに基づいて第3のセグメントが保持されることを決定する。

#### 【 0 0 3 5 】

[0045]本開示の態様によれば、G P Uは、レンダリング中に各セグメントのためのプレフィックス総和長さをテクスチャオフセットとして適用することができる。たとえば、セグメントをラスタライズした後に、G P Uは、テクスチャオフセット値としてピクセルシェーダにセグメントのためのプレフィックス総和長さの値を供給することができる。G P Uは、シェーディングされているセグメントのロケーションを決定するために、線の始端のテクスチャ座標にテクスチャオフセットを適用することができる。 10

#### 【 0 0 3 6 】

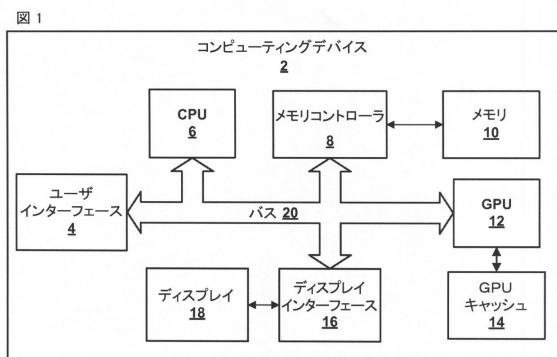

[0046]図1は、本開示の技法を実装するために使用され得る例示的なコンピューティングシステム2を示すプロック図である。コンピューティングデバイス2は、パーソナルコンピュータ、デスクトップコンピュータ、ラップトップコンピュータ、コンピュータワークステーション、ビデオゲームプラットフォームもしくはコンソール、（たとえば、モバイル電話、セルラー電話、衛星電話、および／もしくはモバイル電話ハンドセットなど）ワイヤレス通信デバイス、固定電話、インターネット電話、ポータブルビデオゲームデバイスもしくは携帯情報端末（P D A）などのハンドヘルドデバイス、パーソナル音楽プレーヤ、ビデオプレーヤ、ディスプレイデバイス、テレビジョン、テレビジョンセットトップボックス、サーバ、中間ネットワークデバイス、メインフレームコンピュータ、またはグラフィカルデータを処理および／もしくは表示する任意の他のタイプのデバイスを備えることができる。 20

#### 【 0 0 3 7 】

[0047]図1の例に示すように、コンピューティングデバイス2は、ユーザインターフェース4と、C P U 6と、メモリコントローラ8と、メモリ10と、グラフィックス処理ユニット（G P U）12と、G P Uキャッシュ14と、ディスプレイインターフェース16と、ディスプレイ18と、バス20とを含む。ユーザインターフェース4、C P U 6、メモリコントローラ8、G P U 1 2、およびディスプレイインターフェース16は、バス20を使用して互いに通信することができる。図1に示す異なる構成要素同士の間のバスおよび通信インターフェースの特定の構成は単なる例示であり、本開示の本技法を実装するために、同じもしくは異なる構成要素を備えたコンピューティングデバイスおよび／または他のグラフィックス処理システムの他の構成が使用され得ることに留意されたい。 30

#### 【 0 0 3 8 】

[0048]C P U 6は、コンピューティングデバイス2の動作を制御する汎用プロセッサまたは専用プロセッサを備えることができる。ユーザは、C P U 6に1つまたは複数のソフトウェアアプリケーションを実行させるための入力をコンピューティングデバイス2に与えることができる。C P U 6上で実行されるそれらのソフトウェアアプリケーションは、たとえば、オペレーティングシステム、ワードプロセッサアプリケーション、電子メールアプリケーション、スプレッドシートアプリケーション、メディアプレーヤアプリケーション、ビデオゲームアプリケーション、グラフィカルユーザインターフェースアプリケーション、または別のプログラムを含み得る。ユーザは、ユーザインターフェース4を介してコンピューティングデバイス2に結合される、キーボード、マウス、マイクロfon、タッチパッドまたは別の入力デバイスなど、1つもしくは複数の入力デバイス（図示せず）を介してコンピューティングデバイス2に入力を与えることができる。 40

#### 【 0 0 3 9 】

50

20

30

40

50

[0049] C P U 6 上で実行するソフトウェアアプリケーションは、グラフィックスデータをディスプレイ 18 にレンダリングせしめるよう G P U 1 2 に命令する、1 つまたは複数のグラフィックスレンダリング命令を含み得る。いくつかの例では、ソフトウェア命令は、たとえば、Open Graphics Library (OpenGL (商標登録)) API、Open Graphics Library Embedded System (OpenGL ES) API、Direct 3D API、Direct X API、RenderMan API、Web GL API、または任意の他の公的もしくは所有権を主張できる標準グラフィックス API など、グラフィックスアプリケーションプログラムインターフェース (API) に準拠し得る。グラフィックスレンダリング命令を処理するために、C P U 6 は、G P U 1 2 にグラフィックスデータのレンダリングのうちの一部またはすべてを実行せしめるよう G P U 1 2 に命令するための、1 つまたは複数のグラフィックスレンダリングコマンドを発行することができる。いくつかの例では、レンダリングされることになるグラフィックスデータは、たとえば、点、線、三角形、クアドララテラル (quadralaterals)、トライアングルストリップ (triangle strips)、パッチなど、グラフィックスプリミティブのリストを含み得る。さらなる例では、レンダリングされることになるグラフィックスデータは、たとえば、ラインセグメント、橙円弧、2 次ベジェ曲線、および 3 次ベジェ曲線など、1 つまたは複数のパスレンダリングプリミティブを含み得る。10

#### 【0040】

[0050] メモリコントローラ 8 は、メモリ 10 との間を行き来するデータの転送を容易にする。たとえば、メモリコントローラ 8 は、メモリ読み取り要求とメモリ書き込み要求とを C P U 6 および / または G P U 1 2 から受け取って、コンピューティングデバイス 2 内の構成要素にメモリサービスを提供するために、メモリ 10 に関するそのような要求にサービス提供することができる。メモリコントローラ 8 はメモリ 10 に通信可能に結合される。メモリコントローラ 8 は、図 1 の例示的なコンピューティングデバイス 2 内で、C P U 6 、 G P U 1 2 、およびメモリ 10 の各々とは別である処理モジュールとして示されているが、他の例では、メモリコントローラ 8 の機能の一部またはすべては、C P U 6 、 G P U 1 2 、およびメモリ 10 のうちの 1 つもしくは複数の上で実装され得る。20

#### 【0041】

[0051] メモリ 10 は、C P U 6 による実行のためにアクセス可能なプログラムモジュールおよび / もしくは命令、ならびに / または C P U 6 上で実行するプログラムによって使用するためのデータを記憶することができる。たとえば、メモリ 10 は、ユーザアプリケーションと、それらのアプリケーションと関連付けられたグラフィックスデータとを記憶することができる。メモリ 10 は、コンピューティングデバイス 2 の他の構成要素によって使用するため、および / または生成されるための情報を記憶することも可能である。たとえば、メモリ 10 は、G P U 1 2 のデバイスマモリとして機能することができ、G P U 1 2 によって演算されることになるデータ、ならびに G P U 1 2 によって実行される演算の結果生じるデータを記憶することができる。たとえば、メモリ 10 は、パステータ、パスセグメントデータ、表面、テクスチャバッファ、デプスバッファ、ステンシルバッファ、頂点バッファ、フレームバッファなどの任意の組合せを記憶することができる。加えて、メモリ 10 は、G P U 1 2 によって処理するためのコマンドストリームを記憶することができる。たとえば、メモリ 10 は、パスレンダリングコマンド、3 D グラフィックスレンダリングコマンド、および / または汎用 G P U コンピューティングコマンドを記憶することができる。メモリ 10 は、たとえば、ランダムアクセスメモリ (RAM) 、 static RAM (SRAM) 、ダイナミック RAM (DRAM) 、同期式ダイナミックランダムアクセスメモリ (SDRAM) 、読み取り専用メモリ (ROM) 、消去可能プログラマブル ROM (EPROM) 、電気的消去可能プログラマブル ROM (EEPROM (登録商標)) 、フラッシュメモリ、磁気データ媒体または光記憶媒体など、1 つもしくは複数の揮発性または不揮発性のメモリあるいは記憶デバイスを含み得る。3040

#### 【0042】

[0052] G P U 1 2 は、 C P U 6 によって G P U 1 2 に発行されたコマンドを実行するよう構成され得る。 G P U 1 2 によって実行されるコマンドは、 グラフィックスコマンド、 描画呼出し (draw call) コマンド、 G P U 状態プログラミングコマンド、 メモリ転送コマンド、 汎用コンピューティングコマンド、 カーネル実行コマンドなどを含み得る。

#### 【 0 0 4 3 】

[0053] いくつかの例では、 G P U 1 2 は、 ディスプレイ 1 8 に 1 つまたは複数のグラフィックスプリミティブをレンダリングするためのグラフィックス演算を実行するよう構成され得る。 そのような例では、 C P U 6 上で実行するソフトウェアアプリケーションの 1 つがグラフィックス処理を必要とするとき、 C P U 6 は、 ディスプレイ 1 8 にレンダリングするためのグラフィックスデータを G P U 1 2 に提供して、 G P U 1 2 に対する 1 つまたは複数のグラフィックスコマンドを発行することができる。 グラフィックスコマンドは、 たとえば、 描画呼出しコマンド、 G P U 状態プログラミングコマンド、 メモリ転送コマンド、 ブリッティング (blitting) コマンドなどを含み得る。 グラフィカルデータは、 頂点バッファ、 テクスチャデータ、 表面データなどを含み得る。 いくつかの例では、 C P U 6 は、 コマンドとグラフィックスデータとを G P U 1 2 によってアクセス可能なメモリ 1 0 に書き込むことによって、 コマンドとグラフィックスデータとを G P U 1 2 に提供することができる。

#### 【 0 0 4 4 】

[0054] さらなる例では、 G P U 1 2 は、 C P U 6 上で実行するアプリケーションについて、 汎用コンピューティングを実行するよう構成され得る。 そのような例では、 C P U 6 上で実行するソフトウェアアプリケーションのうちの 1 つが計算タスクを G P U 1 2 にオフロードすることを決定するとき、 C P U 6 は、 汎用コンピューティングデータを G P U 1 2 に提供して、 G P U 1 2 に対する 1 つまたは複数の汎用コンピューティングコマンドを発行することができる。 汎用コンピューティングコマンドは、 たとえば、 カーネル実行コマンド、 メモリ転送コマンドなどを含み得る。 いくつかの例では、 C P U 6 は、 コマンドとグラフィックスデータとを G P U 1 2 によってアクセス可能なメモリ 1 0 に書き込むことによって、 コマンドと汎用コンピューティングデータとを G P U 1 2 に提供することができる。

#### 【 0 0 4 5 】

[0055] G P U 1 2 は、 いくつかの例では、 ベクタ演算について C P U 6 よりも効率的な処理を行う高並列構造を用いて構築され得る。 たとえば、 G P U 1 2 は、 複数の頂点、 制御点、 画素および / または他のデータに関して並列な形で演算するよう構成された複数の処理要素を含み得る。 G P U 1 2 の高並列性質は、 いくつかの例では、 G P U 1 2 が、 C P U 6 を使用して画像をレンダリングするよりもより迅速にグラフィックス画像 ( たとえば、 G U I および 2 次元 ( 2 D ) ならびに / または 3 次元 ( 3 D ) のグラフィックスシーン ) をディスプレイ 1 8 上にレンダリングするのを可能にする。 加えて、 G P U 1 2 の高並列性質は、 G P U 1 2 が、 C P U 6 よりもより迅速に、 汎用コンピューティングアプリケーションについて、 ある種のタイプのベクトル演算および行列演算を処理するのを可能にし得る。

#### 【 0 0 4 6 】

[0056] いくつかの例では、 G P U 1 2 は、 コンピューティングデバイス 2 のマザーボードに統合され得る。 他の例では、 G P U 1 2 は、 コンピューティングデバイス 2 のマザーボードにおけるポートに設置されるグラフィックスカード上に存在し得るか、 または場合によっては、 コンピューティングデバイス 2 と相互運用するよう構成された周辺デバイス内に組み込まれ得る。 さらなる例では、 G P U 1 2 は、 システムオンチップ ( S o C ) を形成する C P U 6 と同じマイクロチップ上に配置され得る。 G P U 1 2 は、 1 つもしくは複数のマイクロプロセッサ、 特定用途向け集積回路 ( A S I C ) 、 フィールドプログラマブルゲートアレイ ( F P G A ) 、 デジタル信号プロセッサ ( D S P ) 、 あるいは他の等価な集積論理回路または個別論理回路など、 1 つもしくは複数のプロセッサを含み得る。

#### 【 0 0 4 7 】

10

20

30

40

50

[0057]いくつかの例では、GPU12はGPUキャッシュ14に直接結合され得る。したがって、GPU12は、必ずしもバス20を使用せずに、GPUキャッシュ14からデータを読み取り、GPUキャッシュ14にデータを書き込むことができる。言い換えれば、GPU12は、オフチップメモリの代わりに、ローカルストレージを使用してデータをローカルで処理することができる。これにより、GPU12は、大量のバストラフィックを受けることがある、バス20を介したデータの読み取りおよび書き込みの必要がなくなるので、より効率的な方法で動作できるようになる。しかしながら、いくつかの例では、GPU12は、別個のキャッシュを含まず、代わりに、バス20を介してメモリ10を利用することができる。GPUキャッシュ14は、たとえば、ランダムアクセスメモリ(RAM)、スタティックRAM(SRAM)、ダイナミックRAM(DRAM)、消去可能プログラマブルROM(EPROM)、電気消去可能プログラマブルROM(EEPROM)、フラッシュメモリ、磁気データ媒体または光学データ媒体など、1つもしくは複数の揮発性または不揮発性のメモリあるいは記憶デバイスを含み得る。10

#### 【0048】

[0058]CPU6および/またはGPU12は、レンダリングされた画像データをメモリ10内に割り振られたフレームバッファ内に記憶することができる。ベクタグラフィックスに関して、レンダリングされた画像データは、レンダリングされることになるパスセグメントに関してレンダリングされたフィル領域とストローク領域とを含み得る。ディスプレイインターフェース16は、データをフレームバッファから取り出して、レンダリングされた画像データによって表される画像を表示するようにディスプレイ18を構成することができる。いくつかの例では、ディスプレイインターフェース16は、フレームバッファから取り出されたデジタル値をディスプレイ18によって消費され得るアナログ信号に変換するように構成されたデジタルアナログ変換器(DAC)を含み得る。他の例では、ディスプレイインターフェース16は、処理のために、デジタル値をディスプレイ18に直接的に渡すことができる。20

#### 【0049】

[0059]ディスプレイ18は、モニタ、テレビジョン、投影デバイス、液晶ディスプレイ(LCD)、プラズマディスプレイパネル、発光ダイオード(LED)アレイ、陰極線管(CRT)ディスプレイ、電子ペーパー、表面伝導型電子放出素子ディスプレイ(SED)、レーザテレビジョンディスプレイ、ナノ結晶ディスプレイまたは別のタイプのディスプレイユニットを含み得る。ディスプレイ18はコンピューティングデバイス2内に統合され得る。たとえば、ディスプレイ18は、モバイル電話ハンドセットまたはタブレットコンピュータのスクリーンとすることができます。あるいは、ディスプレイ18は、ワイヤード通信リンクまたはワイヤレス通信リンクを介してコンピュータデバイス2に結合されるスタンドアロンデバイスとすることができます。たとえば、ディスプレイ18は、ケーブルリンクまたはワイヤレスリンクを介してパーソナルコンピュータに接続されるコンピュータモニタまたはフラットパネルディスプレイとすることができます。30

#### 【0050】

[0060]バス20は、第1世代、第2世代、および第3世代のバス構造ならびにバスプロトコルと、共有バス構造およびバスプロトコルと、ポイントツーポイントバス構造およびバスプロトコルと、一方向バス構造およびバスプロトコルと、双方向バス構造およびバスプロトコルとを含めて、バス構造およびバスプロトコルの任意の組合せを使用して実装され得る。バス20を実装するために使用され得る様々なバス構造およびバスプロトコルの例は、たとえば、HyperTransportバス、InfiniBandバス、Advanced Graphics Portバス、Peripheral Component Interconnect(PCI)バス、PCI Expressバス、Advanced Microcontroller Bus Architecture(AMBA)Advanced High-performance Bus(AHB)、AMBA Advanced Peripheral Bus(APB)、およびAMBA Advanced eXtensible Interface(AXI)バスを4050

含む。他のタイプのバス構造およびバスプロトコルも使用され得る。

#### 【0051】

[0061]いくつかの事例では、GPU12は、部分的 - 全体的 (partial-to-total) GPUベースの様々なバスレンダリングコマンドの実行を実現するように構成され得る。たとえば、CPU6は、GPU12に対する1つまたは複数のバスレンダリングコマンドを発行することができ、GPU12は、バスレンダリングコマンドを実行することができる。一例として、CPU6は、GPU12にバスファイル動作を実行するように命令する1つまたは複数のバスファイルコマンドをGPU12に発行することができ、GPU12は、バスファイルコマンドを実行することができる。別の例として、CPU6は、GPU12にバスストローク動作を実行するように命令する1つまたは複数のバスストロークコマンドをGPU12に発行することができ、GPU12は、バスストロークコマンドを実行することができる。10

#### 【0052】

[0062]いくつかの例では、GPU12は、レンダリングされることになるバスのバスセグメントを示すデータを受け取ることと、複数のプリミティブにバスセグメントをテッセレートすることと、複数のプリミティブに基づいてバスセグメントに関するフィル領域とストローク領域とのうちの少なくとも1つをレンダリングすることとを行なうように構成され得る。GPUは、フィル動作を実行するときにバスセグメントに関するフィル領域をレンダリングすることができ、ストローク動作を実行するときにバスセグメントに関するストローク領域をレンダリングすることができる。複数のプリミティブは、いくつかの例では、複数のラインセグメントであり得る。20

#### 【0053】

[0063]いくつかの例では、GPU12は、バスファイル動作を実行するために、2バスレンダリング手法を使用することができる。たとえば、第1のレンダリングバスの一部として、GPU12は、レンダリングされることになるバスのバスセグメントを示すデータを受け取り、複数のラインセグメントにバスセグメントをテッセレートし、複数のラインセグメントに基づいて複数の三角形プリミティブを生成することができる。GPU12は、複数のラインセグメントのそれぞれに基づいて複数の三角形プリミティブの各々を生成することができる。GPU12は、どの画素がバスセグメントに関するフィル領域の内側にあるかを示すデータを共通ステンシルバッファが記憶するように、共通のステンシルバッファに複数の三角形プリミティブの各々をレンダリングすることができる。共通のステンシルバッファにプリミティブをレンダリングした後に、GPU12は、第2のレンダリングバスを実行することができる。第2のレンダリングバス中に、GPU12は、バスセグメントに関するフィル領域のラスタライズされたバージョンを生成するために、ステンシルバッファに記憶されたデータとフィル色に基づいてバスセグメントに関するフィル領域の内側にある画素を包含する1つまたは複数のプリミティブをレンダリングすることができる。30

#### 【0054】

[0064]バスファイル動作のための複数の三角形プリミティブを生成するために、GPU12は、いくつかの例では、バスセグメントに関して生成される三角形プリミティブのすべてに対して同じである共通の頂点を三角形プリミティブの各々が有するように、複数の三角形プリミティブを生成することができる。そのような例では、GPU12は、複数のラインセグメントのそれぞれの終点に対応する2つの追加の頂点（すなわち、共通の頂点に加えて2つの頂点）を三角形プリミティブの各々が有するように、複数の三角形プリミティブを生成することができる。追加の各頂点は、対応するラインセグメントの終点のそれぞれに対応し得る。40

#### 【0055】

[0065]したがって、バスレンダリングを実行するとき、GPU12は、バスをフィルするために、ラインセグメントにバスをテッセレートし、ラインセグメントをピボット点に接続して三角形プリミティブを形成し、三角形をステンシルバッファにレンダリングする50

という以下の例示的な機能を実行することができる。フィルプロセスの次の、場合によつては最後のステップは、ステンシルテストを有効化した状態で（たとえば、図5Cに関してより詳細に説明するように）パスを包含するバウンディングボックスをレンダリングすることと、フレームバッファにステンシルコンテンツをコピーすることとを行うことである。いくつかの事例では、バウンディングボックスは、GPU6から受け取ったコマンドに基づいて決定され得る。上記のように、この手法は、バウンディングボックスを計算するために、2つのレンダリングパスとパスの前処理とを必要とする。

#### 【0056】

[0066]さらに、MSAAなどのアンチエイリアシングを実行するとき、GPU12は、レンダターゲットと同じレートでステンシルバッファをサンプリングすることができる。たとえば、ステンシルバッファとレンダターゲットとがどちらもMSAAレートでサンプリングされる場合、フレームバッファにステンシルバッファをコピーするときに消費されるメモリ帯域幅は、比較的大きくなり得る。GPU12がTIRを実行し、レンダターゲットのために比較的小さい割当てを使用する場合、ステンシルサンプリングレートも影響を受け、それによって、ステンシルバッファの精度を低減し得る。

10

#### 【0057】

[0067]本開示の態様によれば、GPU12は、ステンシルTIRを実行することができる。たとえば、GPU12は、画像のパスの各アンチエイリアス画素のカバレージ値を決定するためのサンプリングレートを示すステンシルパラメータを決定することができる。GPU12はまた、ステンシルパラメータとは別々に、パスの各アンチエイリアス画素のためのメモリ割当てを示すレンダターゲットパラメータを決定することができる。GPU12は、ステンシルパラメータとレンダターゲットパラメータとを使用してパスをレンダリングすることができる。

20

#### 【0058】

[0068]いくつかの例では、GPU12は、画素に割り当てられるメモリの量よりも高いレートでステンシルを実行することができる。たとえば、16×のMSAAに関して、GPU12は、スーパーサンプリングされる、たとえば、各画素が16個のサンプルを有するステンシル動作を実行することができる。GPU12は、ステンシルテストにパスした（たとえば、パスの内側にあると決定された）画素のサンプルの数に基づいて画素ごとにカバレージ値を計算することによって所与のパスをレンダリングすることができる。本開示の態様によれば、ステンシルが16×でサンプリングされ得るにもかかわらず、GPU12、画素のためのレンダターゲットは1×でサンプリングされ得る。

30

#### 【0059】

[0069]さらに、本開示の態様によれば、GPU12は、バウンディングボックスを前処理する必要なしに単一のレンダリングパスでパスをフィルすることができる。たとえば、GPU12は、ステンシル動作中にバウンディングボックスを決定することができる。この例では、GPU12が、（たとえば、画素をシェーディングすることなしに）ステンシル中にプリミティブをレンダリングするので、GPU12は、パスのプリミティブの最外点（たとえば、最外境界点）を決定することができる。いくつかの例では、GPU12は、（パスの相対上部にある）上位点と、（パスの相対下部にある）下位点と、（パスの右端点にある）右点と、（パスの左端点にある）左点とを決定することができる。GPU12は、ステンシル中に決定された最外点を使用してバウンディングボックスを決定することができる。すなわち、GPU12は、パスのプリミティブのすべてを包含するバウンディングボックスを決定することができる。いくつかの例では、バウンディングボックスは、2つの三角形から構成され得る。

40

#### 【0060】

[0070]バウンディングボックスを完了した後に、GPU12は、さらに、バウンディングボックスの上でステンシルTIRを実行することによって、（たとえば、同じレンダリングパス中で）バウンディングボックスを処理することができる。すなわち、上記のように、GPU12は、各画素のカバレージ値を決定し、ステンシル内に位置するとGPU1

50

2 が決定した画素をシェーディングすることができる。この例では、GPU12 は、画素に対して別個の深度テストを実行する必要がない。

#### 【0061】

[0071]ストロークに関して、GPU12 は、いくつかの事例では、ストロークされたパスをダッシングすることができる。すなわち、GPU12 は、ストロークしたパスのための複数のセグメントを決定することができ、したがって、レンダリングされたパスが破線として現れる。一般に、GPU12 は、順番にダッシングされたパスのセグメントを決定することができる。たとえば、GPU12 は、パスの次のセグメントに移る前に、1 つのセグメントをレンダリングするために CPU6 からコマンドを受け取ることができる。そのようなプロセスは、並列性（たとえば、特定の時間インスタンスにおいて 2 つ以上のセグメントをラスタライズおよび／またはシェーディングすること）を阻止し得、GPU12 がパスを単独でレンダリングするのを防ぎ得る。10

#### 【0062】

[0072]本開示の態様によれば、GPU12 は、パスの各セグメントのロケーション（ならびにパスの長さ）を決定し、レンダリング中に長さ情報を適用することができる。たとえば、GPU12 は、破線の複数の順序付きセグメントの各セグメントのためのテクスチャオフセットを決定することができる。いくつかの事例では、セグメント順序は、以下により詳細に説明するように、ジオメトリシェーディング中に決定され得る。この例では、複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットは、現在のセグメントより順序が前のセグメントの長さの累積に基づき得る。GPU12 はまた、セグメントのロケーションを決定するために、各セグメントにテクスチャオフセットを適用することを含めてセグメントをピクセルシェーディングすることができる。たとえば、たとえば、GPU12 は、セグメントのロケーションに基づいてセグメントが可視であるのか不可視であるのかを決定することができる。GPU12 は、可視のセグメントについて保持し（たとえば、色を決定し）、可視でない（たとえば、可視ダッシュ間の空間である）ダッシュのセグメントを破棄することができる。このようにして、GPU12 は、たとえば、CPU6 からダッシングコマンドを受け取ることなしに、破線のパスレンダリングを実行することができる。20

#### 【0063】

[0073]パスレンダリングに関して説明したが、上記で説明したプレフィックス総和動作はベクタグラフィックスに限定されない。たとえば、プレフィックス総和を決定するための技法は、GPU12 が累積値を追跡するあらゆる適用例において使用され得る。説明のための一例では、GPU12 は、勾配を決定するときに上記で説明したプレフィックス総和動作を実行することができる。たとえば、画像処理中に、勾配を作成することは、色を決定するために、何らかの長さ情報の累積を必要とし得る。この例では、GPU12 は、長さ情報を決定するために、上記で説明したプレフィックス総和動作を適用することができる。30

#### 【0064】

[0074]本開示で説明するパスレンダリング技法は、たとえば、CPU6 と、GPU12 と、メモリ10 とを含めて、図1に示されるコンピューティングデバイス2の構成要素のうちのいずれかの中で実装され得る。いくつかの例では、パスレンダリング技法は、（たとえば、図3に関して説明するように GPU12 のグラフィックスパイプラインにおいて）GPU12 によって完全にまたはほぼ完全に実装され得る。追加の例では、CPU6 は、本開示のパスレンダリング技法を実行する GPU12 内のパスレンダリングパイプラインを実装するために、グラフィックスパイプラインの状態を構成して、シェーダプログラムをグラフィックスパイプラインと結合させるための技法を実装することができる。さらなる例では、CPU6 は、レンダリングされることになるパスを示すデータを、1 つまたは複数のパスをレンダリングするために GPU12 によってアクセスされ得る 1 つまたは複数のバッファ（たとえば、1 つまたは複数の頂点バッファ）内に配置するように構成され得る。40

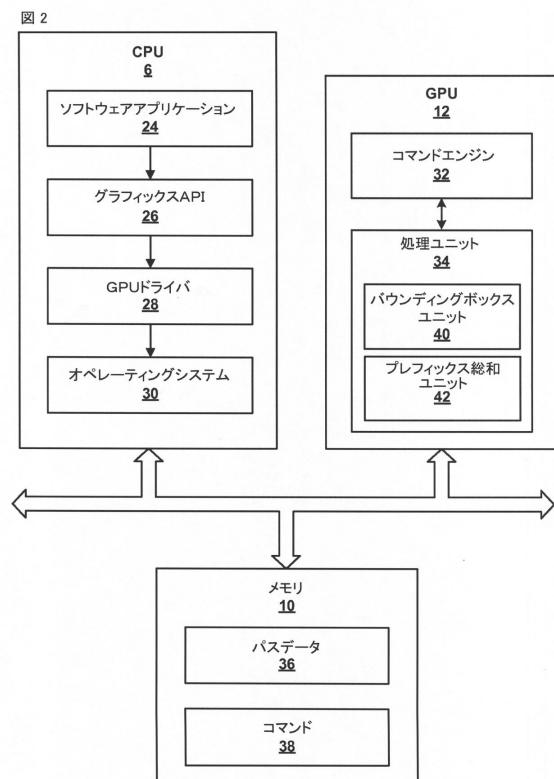

## 【0065】

[0075]図2は、図1のコンピューティングデバイス2のCPU6、GPU12、およびメモリ10をさらに詳細に示すブロック図である。図2に示すように、CPU6はGPU12とメモリ10とに通信可能に結合され、GPU12はCPU6とメモリ10とに通信可能に結合される。いくつかの例では、GPU12は、CPU6によってマザーボードに統合され得る。追加の例では、GPU12は、CPU6を含むマザーボードのポート内にインストールされたグラフィックスカード上で実装され得る。さらなる例では、GPU12は、CPU6と相互作用するように構成された周辺デバイス内に組み込まれることが可能である。追加の例では、GPU12は、システムオンチップ(SoC)を形成するCPU6と同じマイクロチップ上に配置され得る。

10

## 【0066】

[0076]CPU6は、ソフトウェアアプリケーション24と、グラフィックスAPI26と、GPUドライバ28と、オペレーティングシステム30とを実行するように構成される。ソフトウェアアプリケーション24は、グラフィックス画像を表示させる1つもしくは複数の命令および/または非グラフィックスタスク(たとえば、汎用コンピューティングタスク)をGPU12上で実行させる1つもしくは複数の命令を含み得る。ソフトウェアアプリケーション24は、グラフィックスAPI26に対する命令を発行することができる。グラフィックスAPI26は、ソフトウェアアプリケーション24から受け取った命令をGPUドライバ28によって消費され得るフォーマットに変換するランタイムサービスであり得る。GPUドライバ28は、グラフィックスAPI26を介して、ソフトウェアアプリケーション24から命令を受け取って、それらの命令にサービス提供するためにはGPU12の演算を制御する。たとえば、GPUドライバ28は、1つまたは複数のコマンド38を構築して、コマンド38をメモリ10内に配置して、コマンド38を実行するようにGPU12に命令することができる。いくつかの例では、GPUドライバ28は、コマンド38をメモリ10内に配置して、オペレーティングシステム30、たとえば、1つまたは複数のシステム呼出しを介してGPU12と通信することができる。

20

## 【0067】

[0077]GPU12は、コマンドエンジン32と、1つまたは複数の処理ユニット34とを含む。いくつかの例では、1つまたは複数の処理ユニット34は、3Dグラフィックスレンダリングパイプライン、たとえば、DX11グラフィックスレンダリングパイプライン(すなわち、DX11グラフィックスAPIに準拠する3Dグラフィックスパイプライン)を形成および/または実装することができる。

30

## 【0068】

[0078]コマンドエンジン32は、(たとえば、メモリ10を介して)CPU6からコマンドを受け取って、GPU12にそれらのコマンドを実行させるように構成される。状態コマンドを受け取ることに応答して、コマンドエンジン32は、状態コマンドに基づいて、GPU12内の1つもしくは複数の状態レジスタを特定の値に設定するように、および/または状態コマンドに基づいて、固定関数処理ユニット34のうちの1つもしくは複数を構成するように構成され得る。描画呼出コマンドを受け取ることに応答して、コマンドエンジン32は、処理ユニット34に、レンダリングされることになる1つまたは複数のパスセグメントのジオメトリを定義するデータに基づいて、およびレンダリングされることになるパスセグメントの各々のためのパスセグメントのタイプを示すデータに基づいて1つまたは複数のパスセグメントをレンダリングせしめるよう構成され得る。いくつかの例では、レンダリングされることになる1つまたは複数のパスセグメントのジオメトリを定義するデータと、パスセグメントの各々のためのパスセグメントのタイプを定義するデータとは、メモリ10中の1つまたは複数の頂点データ構造に記憶され得る。コマンドエンジン32は、シェーダプログラム結合コマンドを受け取って、それらのシェーダプログラム結合コマンドに基づいて、特定のシェーダプログラムをプログラマブル処理ユニット34のうちの1つまたは複数にロードすることも可能である。

40

## 【0069】

50

[0079]処理ユニット34は、その各々がプログラマブル処理ユニットまたは固定関数処理ユニットであり得る、1つもしくは複数の処理ユニットを含み得る。プログラマブル処理ユニットは、たとえば、CPU6からGPU12上にダウンロードされた1つまたは複数のシェーダプログラムを実行するように構成されたプログラマブルシェーダユニットを含み得る。いくつかの例では、シェーダプログラムは、たとえば、OpenGL Shading Language(GLSL)、High Level Shading Language(HLSL)、C for Graphics(Cg)シェーディング言語など、ハイレベルシェーディング言語で書き込まれたプログラムのコンパイルバージョンであり得る。

#### 【0070】

[0080]いくつかの例では、プログラマブルシェーダユニットは、並列して動作するよう構成された複数の処理ユニット、たとえば、 SIMDパイプラインを含み得る。プログラマブルシェーダユニットは、シェーダプログラム命令を記憶するプログラムメモリと、実行状態レジスタ、たとえば、実行されているプログラムメモリ内の現在の命令またはフェッチされることになる次の命令を示すプログラムカウンタレジスタとを有し得る。処理ユニット34中のプログラマブルシェーダユニットは、たとえば、頂点シェーダユニット、ピクセルシェーダユニット、ジオメトリシェーダユニット、ハルシェーダユニット、ドメインシェーダユニット、テッセレーション制御シェーダユニット、テッセレーション評価シェーダユニット、コンピュートシェーダユニット、および/またはユニファイドシェーダユニットを含み得る。図2に示されるように、処理ユニット34はまた、バウンディングボックスユニット40とプレフィックス総和ユニットとを含み得る。

#### 【0071】

[0081]固定関数処理ユニットは、ある種の機能を実行するために配線接続されたハードウェアを含み得る。固定関数ハードウェアは、1つまたは複数の制御信号を介して、たとえば、異なる機能を実行するように構成され得るが、固定関数ハードウェアは、通常、ユーザコンパイルプログラムを受け取ることができるプログラムメモリを含まない。いくつかの例では、処理ユニット34内の固定関数処理ユニットは、たとえば、デブステスト、シザーテスト、アルファブレンディングなど、ラスタ演算を実行する処理ユニットを含み得る。

#### 【0072】

[0082]メモリ10は、バスデータ36と、1つまたは複数のコマンド38とを記憶することができる。いくつかの例では、バスデータ36は、複数の頂点(すなわち、制御点)として、メモリ10内に割り当てられた1つまたは複数の頂点バッファ内に記憶され得る。いくつかの例では、バスデータは、パッチリストデータ構造(たとえば、4制御点パッチリスト)内に記憶され得る。コマンド38は、1つまたは複数のコマンドバッファ(たとえば、リングバッファ)内に記憶され得る。CPU6(たとえば、オペレーティングシステム30を介したGPUドライバ28)は、GPU12によって消費するために、バスデータ36とコマンド38とをメモリ10内に配置することができる。GPU12(たとえば、コマンドエンジン32)は、メモリ10内に記憶されたコマンド38を検索および実行することができる。

#### 【0073】

[0083]バスデータ36が頂点(たとえば、制御点)として記憶される例では、頂点はレンダリングされることになるバスセグメントを形状的に定義する1つまたは複数の属性を含み得る。たとえば、線の場合、パッチ制御リスト内の頂点は、線の終点に関する座標(たとえば、(x0, y0)および(x1, y1))を示すデータを含み得る。3次ベジェ曲線の場合、パッチ制御リスト内の頂点は、その曲線を定義する4つの制御点の座標(たとえば、(x0, y0)、(x1, y1)、(x2, y2)、(x3, y3))を示すデータを含み得る。2次ベジェ曲線の場合、パッチ制御リスト内の頂点は、4つの制御点の代わりに、3つの制御点に関する座標を示すデータを含み得る。橜円弧の場合、パッチ制御リスト内の頂点は、橜円弧の終点パラメータ表示を示すデータ、または橜円弧の中心パ

10

20

30

40

50

ラメータ表示を示すデータを含み得る。

【0074】

[0084] いくつかの例では、レンダリングされることになるパスセグメントを形状的に定義する 1 つまたは複数の属性は解像度と無関係であり得る。言い換えれば、パスセグメントを形状的に定義する属性は、パスセグメントをレンダリングするときに実行されることになるテッセレーションの量と無関係であり得、および / またはパスセグメントをレンダリングするときに生成されることになる頂点の数量と無関係であり得る。

【0075】

[0085] C P U 6 は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を頂点バッファ内の 1 つまたは複数の、場合によっては未使用の頂点属性内に配置することも可能である。いくつかの例では、異なるパスセグメントタイプは、ベクタグラフィックス A P I によって定義されたパスセグメントタイプのセットに対応し得、ソフトウェアアプリケーション 2 4 によって使用するために利用可能である。いくつかの例では、異なるパスセグメントタイプは、O p e n V G A P I によって定義されたパスセグメントタイプのセットに対応し得る。

10

【0076】

[0086] コマンド 3 8 は、1 つもしくは複数の状態コマンドおよび / または 1 つもしくは複数の描画呼出しコマンドを含み得る。状態コマンドは、たとえば、描画色、フィル色、ストローク色など、G P U 1 2 内の状態変数のうちの 1 つまたは複数を変更するように G P U 1 2 に命令することができる。いくつかの例では、状態コマンドは、パスをレンダリングすることと関連付けられた 1 つまたは複数の状態変数を設定するように構成されたパスレンダリング状態コマンドを含み得る。たとえば、状態コマンドは、レンダリングされることになるパスがフィルされるか、ストロークされるか、またはそれらの両方かを示すように構成されたペイントモードコマンドを含み得る。別の例として、状態コマンドは、フィル動作のために使用されることになる色を指定するフィル色コマンドおよび / またはストローク動作のために使用されることになる色を指定するストローク色コマンドを含み得る。さらなる例として、状態コマンドは、たとえば、ストローク幅、エンドキャップスタイル（たとえば、円形、方形）、ライン接合スタイル（たとえば、マイター、ラウンド、ベベル）、マイターリミットなど、ストローク動作に関する 1 つまたは複数のパラメータを指定することができる。いくつかの例では、1 つもしくは複数の状態パラメータを設定するために状態コマンドを使用することに加えて、またはその代わりに、描画呼出しコマンドを使用することによって、あるいはパスデータ 3 6 を含む頂点バッファ内に状態インジケータを配置することによって、状態パラメータのうちの 1 つもしくは複数が設定され得る。

20

【0077】

[0087] 描画呼出しコマンドは、メモリ 1 0 内に記憶された（たとえば、頂点バッファ内で定義された）1 つまたは複数の頂点のグループによって定義された形状をレンダリングするように G P U 1 2 に命令することができる。いくつかの例では、描画呼出しコマンドは、G P U 1 2 にメモリ 1 0 の定義されたセクション（たとえば、頂点バッファまたはパスデータ 3 6 ）内に記憶された頂点のすべてをレンダリングさせることができる。言い換えれば、G P U 1 2 が描画呼出しコマンドを受け取ると、メモリ 1 0 の定義されたセクション（たとえば、頂点バッファまたはパスデータ 3 6 ）内の頂点によって表された形状およびプリミティブをレンダリングするための制御が G P U 1 2 に渡される。

30

【0078】

[0088] 描写呼出しコマンドは、3 D 描写呼出しコマンドおよびパスレンダリング描写呼出しコマンドのうちの 1 つまたは両方を含み得る。3 D レンダリング描画呼出しコマンドの場合、頂点バッファ内の 1 つまたは複数の頂点のグループによって定義された形状は、レンダリングされることになる 1 つまたは複数の 3 D グラフィックスプリミティブ（たとえば、点、線、三角形、クアドララテラル（quadralaterals）、トライアングルストリップ、パッチなど）に対応し得、3 D レンダリング描画呼出しコマンドは、1 つまたは複数

40

50

の 3 D グラフィックスプリミティブをレンダリングするように G P U 1 2 に命令することができる。パスレンダリング描画呼出しコマンドの場合、頂点バッファ内の 1 つまたは複数の頂点のグループによって定義された形狀は、レンダリングされることになる 1 つまたは複数のパスプリミティブ（たとえば、ラインセグメント、橢円弧、2 次ベジェ曲線、および 3 次ベジェ曲線など）に対応し得、パスレンダリング描画呼出しコマンドは、1 つまたは複数のパスプリミティブをレンダリングするように G P U 1 2 に命令することができる。いくつかの例では、G P U 1 2 によってレンダリングされることが可能なパスプリミティブは、本開示で説明する異なるタイプのパスセグメントに対応し得る。

#### 【 0 0 7 9 】

[0089]いくつかの例では、本開示で説明するパスレンダリング技法は、たとえば、グラフィックス A P I 2 6 と、G P U ドライバ 2 8 と、コマンドエンジン 3 2 と、処理ユニット 3 4 とを含めて、図 2 に示す構成要素のうちのいずれかの内で実装され得る。さらなる例では、パスレンダリング技法のすべてまたは大部分は、処理ユニット 3 4 によって形成された G P U 1 2 内のグラフィカルパイプライン内で実装され得る。追加の例では、C P U 6 のソフトウェアアプリケーション 2 4 、グラフィックス A P I 2 6 および / または G P U ドライバ 2 8 は、本開示で説明するパスレンダリング技法を実行する G P U 1 2 内のパスレンダリングパイプラインを実装するために、グラフィックスパイプラインの状態を構成して、シェーダプログラムをグラフィックスパイプラインと結合させるための技法を実装することができる。さらなる例では、C P U 6 のソフトウェアアプリケーション 2 4 、グラフィックス A P I 2 6 および / または G P U ドライバ 2 8 は、レンダリングされることになるパスを示すデータを、1 つまたは複数のパスをレンダリングするために G P U 1 2 によってアクセスされ得る 1 つまたは複数のバッファ（たとえば、1 つまたは複数の頂点バッファ）内に配置するように構成され得る。

10

#### 【 0 0 8 0 】

[0090]本開示の態様によれば、処理ユニット 3 4 は、バウンディングボックスユニット 4 0 を含む。バウンディングボックスユニット 4 0 は、バウンディングボックスを決定するための 1 つまたは複数のプログラマブルおよび / または固定機能ユニットを含み得る。たとえば、本開示の技法は、（たとえば、以下の図 3 に関してより詳細に説明するように）バウンディングボックスを決定することと、単一のレンダリングパスでバウンディングボックスをレンダリングすることとを含む。G P U 1 2 がパスフィル動作を実行するとき、バウンディングボックスユニット 4 0 は、パスの境界を決定することを担当し得る。

20

#### 【 0 0 8 1 】

[0091]本開示の態様によれば、バウンディングボックスユニット 4 0 は、A P I 呼出しを使用して開始され得る。たとえば、グラフィックス A P I 2 6 は、パスのレンダリング中に、バウンディングボックスユニット 4 0 の使用をトリガするための 1 つまたは複数の命令を含み得る。A P I 呼出しにより、G P U 1 2 は、バウンディングボックスユニット 4 0 がバウンディングボックスを決定するまで、プリミティブのシェーディングをスキップすることが可能になり得る。G P U 1 2 は、次いで、上記のように、バウンディングボックスの上でステンシル T I R を実行することができる。さらに、バウンディングボックスユニット 4 0 を組み込むことによって、G P U 1 2 は、深度バッファを使用せずに単一のパスでパスをフィルすることができる。

30

#### 【 0 0 8 2 】

[0092]バウンディングボックスユニット 4 0 により、G P U 1 2 は、バウンディングボックスを前処理することなしにパスをフィルすることが可能になり得る。たとえば、バウンディングボックスユニット 4 0 は、たとえば、C P U 6 において、制御多角形を使用してバウンディングボックスを決定することができる。すなわち、バウンディングボックスユニット 4 0 は、生成されたプリミティブのすべての境界に基づいてバウンディングボックスを決定することができる。

40

#### 【 0 0 8 3 】

[0093]本開示の態様によれば、G P U 1 2 は、バウンディングボックスユニット 4 0 が

50

バウンディングボックスを決定するまで、プリミティブのシェーディングをスキップするように構成され得る。すなわち、バウンディングボックスの生成中に、GPU12は、プリミティブをシェーディングすることなしにGPU12のステンシルバッファにパスのプリミティブを書き込むことができる。バウンディングボックスユニット40を組み込むことによって、GPU12は、深度バッファを使用せずに单一のパスでパスをフィルすることができます。たとえば、GPU12は、バウンディングボックスの上でステンシルTIRを実行することができます。

#### 【0084】

[0094]説明のための一例では、バウンディングボックスユニット40によって決定されたバウンディングボックスをGPU12がラスタライズした後、GPU12は、バウンディングボックス中の各画素のカバレージ値を決定することができる。いくつかの例では、GPU12は、画素のクワッド(quad)(一度に4つの画素)のカバレージ値を決定することができる。そのような例では、処理するための画素波を形成する前に、GPU12は、クワッドの各画素のサンプルに対してステンシルテストを実行することができる。GPU12は、テストの結果に基づいて各画素のカバレージマスクを更新することができる。このカバレージ値は、`stencilied_TIR`属性と呼ばれる場合があり、その場合、GPU12は、シェーディング中に使用することができる。たとえば、各画素の`InputCoverage`値は、`stencilied_TIR`に基づき得る。たとえば、GPU12は、ステンシルテストをパスした各画素をピクセルシェーディングする(たとえば、着色する)ことができる(たとえば、ここで、画素のより多くのサンプルが可視である(シェーディングされている)とき、画素はステンシルテストをパスする)。すなわち、GPU12は、分散プロセッサ(`DP proc`)からサンプルに(`InputCoverage`のための)ステンシルテストの後に(中心についての)カバレージマスクとサンプルマスクの両方をパスすることができる。

#### 【0085】

[0095]本開示のいくつかの態様によれば、API呼出しは、レンダリングのステンシルTIRモードをサポートするために使用され得る。たとえば、グラフィックスAPI26は、パスのレンダリング中に、ステンシルTIRの使用をトリガするための1つまたは複数の命令を含み得る。ステンシルTIRがアクティブであるとき、(GPU12のメモリおよび/またはメモリ10中に割り当てられ得る)色バッファと深度/ステンシルバッファとは異なり得る。たとえば、MSAAを実行するとき、GPU12は、1xのMSAAである色バッファと16xのMSAAであるステンシルバッファとにレンダリングすることができる。

#### 【0086】

[0096]本開示の他の態様によれば、処理ユニット34はまた、ダッキングされたセグメントをレンダリングすること、たとえば、ダッキングされたパスをストロークすることを行うためのプレフィックス総和ユニット42を含む。プレフィックス総和ユニット42は、破線の複数の順序付きセグメントの各セグメントのためのテクスチャオフセットを決定することができる。いくつかの例では、テッセレーションまたはジオメトリシェーダ段階は、セグメントを生成するときにセグメント順序を決定することができる。複数の順序付きセグメントの現在のセグメントのためのテクスチャオフセットは、現在のセグメントより順序が前のセグメントの長さの累積に基づき得る。プレフィックス総和ユニット42は、ピクセルシェーダ段階などのシェーダ段階にテクスチャオフセットを与えることができる。シェーダ段階は、テクスチャオフセットを適用し、適切なロケーションでセグメントをレンダリングすることができる。

#### 【0087】

[0097]したがって、プレフィックス総和装置42は、破線のセグメントの長さを累積する1つまたは複数のプログラマブルまたは固定機能ユニットを含み得る。いくつかの例では、プレフィックス総和装置42は、ラスタライザ段階に組み込まれ得る。たとえば、GPU12は、パスをテッセレートすることができ、ジオメトリシェーダ段階は、パスの長

10

20

30

40

50

さを決定することができる。他の例では、長さは、1つまたは複数の他のシェーダユニットによって決定され得る。たとえば、本開示の態様によれば、プレフィックス総和装置42は、(点プリミティブのサイズを示す)属性 `points size` のシステム解釈値と同様の方法で `line length` 値を計算することができる。すなわち、`line length` は、ダッショングされたパターン中の(フラグメントとも呼ばれる場合がある)セグメントのロケーションを示すシステム解釈値であり得る。

#### 【0088】

[0098] GPU12の(たとえば、以下の図3に関して説明する)ピクセルシェーダが、プレフィックス総和した `line length` 値を受け取ると、ピクセルシェーダは、ダッシュパターン中でシェーディングされているフラグメントのロケーションを決定することができる。ピクセルシェーダは、次いで、決定されたロケーションに基づいて、(フラグメントが可視ダッシュの一部を形成する場合)フラグメントを保持するか、あるいは(フラグメントが可視ダッシュの一部でない場合)フラグメントを破棄することができる。いずれの場合も、プレフィックス総和ユニット42は、プレフィックス総和として長さ情報を累積し、ピクセルシェーダなどのダウンストリームシェーダ段階にテクスチャオフセットとしてプレフィックス総和を与えることができる。

#### 【0089】

[0099]レンダリング中に、GPU12は、`prefix_sum` パラメータをリセットするために(以下の図3に関してより詳細に説明するように、ハルシェーダ、テッセレータ、および/またはドメインシェーダを含み得る)テッセレーションエンジン(TSE)にイベント `presum_start` を送ることができる。プリミティブごとに、プレフィックス総和ユニット42は、新しい値として `prefix_sum` にプリミティブのスカラー値(たとえば、`points size` と同じフィールド)を追加することができる。プレフィックス総和ユニット42は、画素ごとの古いプレフィックス総和値をテクスチャオフセットとしてパスすることができる。

#### 【0090】

[0100]いくつかの例では、テッセレーションエンジンは、`prefix_sum` パラメータを累積するためにレジスタを組み込むことができる。プレフィックス総和ユニット42は、イベント `presum_start` によってレジスタをリセットすることができる。テッセレーションエンジンは、(テクスチャオフセットを送ることと同様であり得る)プリミティブフェイスネス(faceness)と同様の重心平面インターフェース中でバックエンド(RB)をレンダリングするためにプリミティブごとの属性として `prefix_sum` をパスする。この例では、属性は、このプリミティブごとの属性を表すインターフェースを高レベルシーケンサ(HLSQ)に与えるためにRBに追加され得る。

#### 【0091】

[0101]図3は、本開示のパスレンダリング技法を実行することができる例示的なグラフィックスパイプライン43を示す概念図である。いくつかの例では、グラフィックスパイプラインは、Microsoft(DirectX)11グラフィックスパイプラインに対応し得る。図3に示すように、グラフィックスパイプライン43は、入力アセンブラ(IA)44と、頂点シェーダ(VS)46と、ハルシェーダ(HS)48と、テッセレータ50と、ドメインシェーダ(DS)52と、ジオメトリシェーダ(GS)54と、ラスタライザ56と、ピクセルシェーダ(PS)58と、出力統合器60とを含む複数の処理段階を含む。ハルシェーダ48、テッセレータ50、およびドメインシェーダ52は、グラフィックスパイプライン43のテッセレーション段階62を形成し得る。さらに、パイプライン43はまた、リソースブロック64を含む。いくつかの例では、パイプライン43は、以下に述べるように、GPU12によって実装され、および/またはGPU12中に組み込まれ得る。

#### 【0092】

[0102]リソースブロック64は、たとえば、1つもしくは複数のテクスチャおよび/または1つもしくは複数のバッファなど、グラフィックスパイプライン43によって使用さ

10

20

30

40

50

れる 1 つもしくは複数のメモリリソースに対応し得る。リソースブロック 6 4 は、グラフィカルパイプライン 4 3 内の処理段階のうちの 1 つもしくは複数によって処理されることになる入力データおよび / またはグラフィックスパイプライン 4 3 内の処理段階のうちの 1 つもしくは複数からの出力データを記憶することができる。一例として、リソースブロック 6 4 は、本開示で説明するバスファイル動作を実行するために使用されるステンシルバッファを記憶することができる。別の例として、リソースブロック 6 4 は、本開示で説明するようにバスセグメントに関するフィル領域のラスタライズされたバージョンおよび / またはバスセグメントに関するストローク領域のラスタライズされたバージョンを保持するフレームバッファを記憶することができる。いくつかの例では、リソースブロック 6 4 を形成するメモリリソースは、コンピューティングデバイス 2 のメモリ 1 0 および / または G P U キャッシュ 1 4 内に存在し得る。

#### 【 0 0 9 3 】

[0103] 図 3 に示す直角の処理段階は固定関数処理段階を表し、図 3 に示す丸角の処理段階はプログラマブル処理段階を表す。たとえば、図 3 に示すように、入力アセンブラー 4 4 、テッセレータ 5 0 、ラスタライザ 5 6 、および出力統合器 6 0 は固定関数処理段階であり、頂点シェーダ 4 6 、ハルシェーダ 4 8 、ドメインシェーダ 5 2 、ジオメトリシェーダ 5 4 、およびピクセルシェーダ 5 8 はプログラマブル処理段階である。プログラマブル段階の各々は、特定のタイプのシェーダプログラムを実行するように構成され得る。たとえば、頂点シェーダ 4 6 は、頂点シェーダプログラムを実行するように構成され得、ハルシェーダ 4 8 は、ハルシェーダプログラムを実行するように構成され得る、等々である。異なるタイプのシェーダプログラムの各々は、G P U 1 2 の共通シェーダユニット上、または 1 つもしくは複数の特定のタイプのシェーダプログラムを実行するための専用である 1 つもしくは複数の専用シェーダユニット上のいずれかで実行することができる。

#### 【 0 0 9 4 】

[0104] 図 3 に示すように、入力アセンブラー 4 4 、頂点シェーダ 4 6 、ハルシェーダ 4 8 、ドメインシェーダ 5 2 、ジオメトリシェーダ 5 4 、ピクセルシェーダ 5 8 、および出力マージャ 6 0 はリソースブロック 6 4 に通信可能に結合される。入力アセンブラー 4 4 、頂点シェーダ 4 6 、ハルシェーダ 4 8 、ドメインシェーダ 5 2 、ジオメトリシェーダ 5 4 、ピクセルシェーダ 5 8 、および出力統合器 6 0 はリソースブロック 6 4 から入力データを検索ならびに / または受け取るように構成される。ジオメトリシェーダ 5 4 および出力統合器 6 0 は、出力データをリソースブロック 6 4 に書き込むように構成される。グラフィックスパイプライン 4 3 内の処理段階とリソースブロック 6 4 との間の通信の上述の構成は、グラフィックスパイプライン 4 3 の処理段階とリソースブロック 6 4 との間の通信がどのように構成され得るかの単なる一例である。他の例では、グラフィックスパイプライン 4 3 の処理段階とリソースブロック 6 4 との間により多くのもしくはより少ない一方で / または双方の通信チャネルが提供され得る。

#### 【 0 0 9 5 】

[0105] Direct X 11 グラフィックスパイプラインの一般的な動作に関する追加の背景情報は、<http://msdn.microsoft.com/en-us/library/windows/desktop/ff476882%28v=vs.85%29.aspx> にあり得る。Direct X 11 グラフィックスパイプラインの一般的な動作に関するさらなる情報は、Zink から、「 Practical Rendering & Computation with Direct3D 11 」、CRC Press (2011 年) に見出すことができる。

#### 【 0 0 9 6 】

[0106] 2 つの主要なバスレンダリング動作は、( 1 ) バスセグメントをフィルすることと、( 2 ) バスセグメントをストロークすることとを含み得るいくつかの事例では、フィル動作は、以下のステップを概して伴い得る 2 パス手法を利用することができる。

#### 【 0 0 9 7 】

1. 複数のラインセグメントにパスセグメントをテッセレートする。

【0098】

2. ラインセグメントごとに三角形プリミティブを生成する。

【0099】

3. ステンシルバッファに三角形プリミティブのすべてをレンダリングする。

【0100】

パス2

4. ステンシルバッファを使用してパスセグメントに関するバウンディングボックスをレンダリングする。

【0101】

10

[0107] 第1のパスの場合、CPU6は、レンダリングされることになるパスセグメントを示すデータを頂点バッファの1つまたは複数の頂点内に配置することができる。いくつかの例では、頂点バッファは図2に示すパスデータ36に対応し得る。頂点バッファ内の頂点に関するプリミティブポロジは、いくつかの例では、パッチ制御リストであり得る。線の場合、パッチ制御リスト内の頂点は、線の終点に関する座標（たとえば、(x0, y0) および (x1, y1)）を示すデータを含み得る。3次ベジェ曲線の場合、パッチ制御リスト内の頂点は、その曲線を定義する4つの制御点の座標（たとえば、(x0, y0)、(x1, y1)、(x2, y2)、(x3, y3)）を示すデータを含み得る。2次ベジェ曲線の場合、パッチ制御リスト内の頂点は、4つの制御点の代わりに、曲線を定義する3つの制御点に関する座標を示すデータを含み得る。楕円弧の場合、パッチ制御リスト内の頂点は、楕円弧の終点パラメータ表示を示すデータ、または楕円弧の中心パラメータ表示を示すデータを含み得る。CPU6は、レンダリングされることになるパスセグメントのタイプを示すデータをパッチ制御リストの、場合によっては未使用の頂点属性内に配置することも可能である。

【0102】

20

[0108] パスレンダリングを実行するためにGPU12によって受け取られ、使用されるパスデータ36の1つの例示的なフォーマットが次に説明される。これは、レンダリングされることになるパスおよび/またはレンダリングされることになるパスセグメントを示すデータがCPU6によってGPU12にどのように提供され得るかの単なる一例であり、他の例が可能であり、本開示の範囲内であることを理解されたい。この例では、GPU12は4(4)つの制御点パッチリストプリミティブとして各パスセグメントを受け取る。この例では、パッチリスト内の頂点（たとえば、制御点）の各々は、それぞれの頂点（たとえば、制御点）に関する属性を定義する3(3)つの浮動属性を含む。

【0103】

30

[0109] ラインパスセグメントの場合、入力パスデータは、以下の形または類似の形をとることができる。

【数1】

```

{ XMFLOAT3(    X0,    Y0, 2.0f ) },

{ XMFLOAT3(    X1,    Y1, 1.0f ) },

{ XMFLOAT3(  0.0f,  0.0f, 1.0f ) },

{ XMFLOAT3(  0.0f,  0.0f, 1.0f ) },

```

40

【0104】

この例では、各行は4つの制御点パッチリストの頂点すなわち制御点を表し、括弧内の各パラメータは、それぞれの頂点すなわち制御点の属性を表す。この例では、第1の制御点の最後の属性は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を記憶する。具体的には、この例で

50

は、パスセグメントタイプインジケータは、パスセグメントがラインパスセグメントであることを意味する  $2.0f$  である。 $X0$ 、 $Y0$ 、 $X1$ 、 $Y1$  はラインパスセグメントの終点に関する座標であり、この場合、 $(X0, Y0)$  は第 1 の終点を表し、 $(X1, Y1)$  は第 2 の終点を表す。

#### 【0105】

[0110] この例では、残りの頂点および属性は、パスセグメントに関する他の属性を示すために使用されなくよく、および / または使用されてもよい。パスセグメントに関する他の属性は、たとえば、パスセグメントがオープンパスの始端であるかまたは終端であるかと、そのパスに関してパスセグメントが表示されるべきかどうかと、エンドキャップがパスセグメントの両方の終端上に配置されるべきかどうかと、もしあれば、何のタイプのエンドキャップが使用されるべきかと、接合がパスセグメントのいずれかの終端上に配置されるべきかどうかと、もしあれば、何のタイプの接合を使用するかと、を含み得る。

10

#### 【0106】

[0111] 3 次ベジェパスセグメントに関する入力パステータは、以下の形または類似の形をとることができる。

#### 【数2】

```

{ XMFLOAT3( X0, Y0, 3.0f ),

{ XMFLOAT3( X1, Y1, 1.0f ),

{ XMFLOAT3( X2, Y2, 1.0f ),

{ XMFLOAT3( X3, Y3, 1.0f ),

```

20

#### 【0107】

この例では、各行は 4 つの制御点パッチリストの頂点すなわち制御点を表し、括弧内の各パラメータは、それぞれの頂点すなわち制御点の属性を表す。この例では、第 1 の制御点の最後の属性は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を記憶する。具体的には、この例では、パスセグメントタイプインジケータは、パスセグメントが 3 次ベジェパスセグメントであることを意味する  $3.0f$  である。 $X0 \sim X3$  および  $Y0 \sim Y3$  は、3 次ベジェパスセグメントに関する制御点の座標であり、この場合、 $(X0, Y0)$  は第 1 の制御点を表し、 $(X1, Y1)$  は第 2 の制御点を表す、等々である。この例では、残りの頂点および属性は、パスセグメントに関する他の属性を示すために使用されなくよく、および / または使用されてもよい。パスセグメントに関する他の属性は、いくつかの例では、ラインパスセグメントに関して上記で説明した属性と同様の属性を含み得る。

30

#### 【0108】

[0112] 4 つの制御点の代わりに、3 つの制御点が提供され得ることを除いて、類似の入力が 2 次ベジェパスセグメントに関して使用されてよく、パスセグメントタイプインジケータは 3 次ベジェパスセグメントからのプリミティブと区別するために異なってよい。

40

#### 【0109】

[0113] たとえば、2 次ベジェパスセグメントに関する入力パステータは、以下の形または類似の形をとることができる。

#### 【数3】

```

{ XMFLOAT3( X0, Y0, 1.0f ),

{ XMFLOAT3( X1, Y1, 1.0f ),

{ XMFLOAT3( X2, Y2, 1.0f ),

{ XMFLOAT3( 0.0f, 0.0f, 1.0f ),

```

50

## 【0110】

この例では、各行は4つの制御点パッチリストの頂点すなわち制御点を表し、括弧内の各パラメータは、それぞれの頂点すなわち制御点の属性を表す。この例では、第1の制御点の最後の属性は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を記憶する。具体的には、この例では、パスセグメントタイプインジケータは、パスセグメントが2次ベジェパスセグメントであることを意味する1.0fである。X0～X2およびY0～Y2は、2次ベジェパスセグメントに関する制御点の座標であり、この場合、(X0, Y0)は第1の制御点を表し、(X1, Y1)は第2の制御点を表す、等々である。この例では、残りの頂点および属性は、パスセグメントに関する他の属性を示すために使用されなくよく、および/または使用されてもよい。パスセグメントに関する他の属性は、いくつかの例では、ラインパスセグメントに関して上記で説明した属性と同様の属性を含み得る。

10

## 【0111】

[0114]いくつかの例では、橜円弧パスセグメントに関する入力パスデータは、橜円弧パスセグメントの中心パラメータ表示を示すデータを含み得る。たとえば、橜円弧パスセグメントに関する入力パスデータは、以下の形または類似の形をとることができる。

## 【数4】

```

{ XMFLOAT3(      X0,      Y0,  4.0f ) },

{ XMFLOAT3(      X1,      Y1,  1.0f ) },

{ XMFLOAT3(      c.x,      c.y,  1.0f ) },

{ XMFLOAT3( theta0, theta1, angle ) },

```

20

## 【0112】

この例では、各行は4つの制御点パッチリストの頂点すなわち制御点を表し、括弧内の各パラメータは、それぞれの頂点すなわち制御点の属性を表す。この例では、第1の制御点の最後の属性は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を記憶する。この例では、パスセグメントタイプインジケータは、それぞれ、大型時計回り(LCW)橜円弧、大型反時計回り(LCCW)橜円弧、小型時計回り(SCW)橜円弧、および小型反時計回り(SCCW)橜円弧に対応する4.0、4.1、4.2、または4.3のうちのいずれかであり得る。X0、X1およびY0、Y1は、橜円弧パスセグメントの終点座標であり、この場合、(X0, Y0)は弧の最初の終点を表し、(X1, Y1)は弧の最終の終点を表す。加えて、theta0は、(スケーリングされていない(unscaled)円上で測定された)橜円弧の初期点の角度を表し、theta1は、(スケーリングされていない円上で測定された)橜円弧の最終点の角度を表す。特に、上で指定された例示的な入力データ形式は中央パラメータ表示であるが、入力データ形式は、弧の最初の終点および最後の終点に関する座標（すなわち、(X0, Y0)、(X1, Y1)）を依然として含み得る。いくつかの例では、そのような座標は、結果として生じる形状の水密性を確実にするために使用され得る。

30

## 【0113】

[0115]さらなる例では、橜円弧パスセグメントに関する入力パスデータは、橜円弧パスセグメントの終点パラメータ表示を示すデータを含み得る。たとえば、橜円弧パスセグメントに関する入力パスデータは、以下の形または類似の形をとることができる。

40

## 【数5】

```

{ XMFLOAT3(    X0,    Y0, 4.0f ),

{ XMFLOAT3(    X1,    Y1, 1.0f ),

{ XMFLOAT3(    rH,    rV, 1.0f ),

{ XMFLOAT3( angle,  0.0f, 1.0f ),

```

## 【0114】

10

この例では、各行は4つの制御点パッチリストの頂点すなわち制御点を表し、括弧内の各パラメータは、それぞれの頂点すなわち制御点の属性を表す。この例では、第1の制御点の最後の属性は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を記憶する。この例では、パスセグメントタイプインジケータは、それぞれ、大型時計回り（L C W）橙円弧、大型反時計回り（L C C W）橙円弧、小型時計回り（S C W）橙円弧、および小型反時計回り（S C C W）橙円弧に対応する4.0、4.1、4.2、または4.3のうちのいずれかであり得る。X0、X1およびY0、Y1は、橙円弧パスセグメントの終点座標であり、この場合、（X0、Y0）は弧の最初の終点を表し、（X1、Y1）は弧の最終の終点を表す。加えて、angleは、（rH、rV）によるスケーリングに先立って測定されたx軸に対する橙円の反時計回り回転角度を表す。

## 【0115】

20

[0116]入力パステータが終点パラメータ形式で表される橙円弧を含む例では、CPU6は、いくつかの例では、レンダリングのためのGPU12に橙円弧を示すデータを送る前に、終点パラメータ形式から中心パラメトリック形式に橙円弧の表現を変換することができる。たとえば、CPU6は、橙円弧の終点パラメータ表示に基づいて、橙円弧の中心パラメータ表示を生成して、橙円弧の中央パラメータ表示をGPU12に送ることができる。橙円弧に関する中央パラメータ表示は、上に指定された例示的な入力データ形式に準拠し得る。中央パラメータ表示は、次に、GPU12によってレンダリングする目的で接合プリミティブを生成するためにCPU6によって使用され得る、橙円弧のための終点接線（tangents）および/または法線を見出すためにCPU6によって使用され得る。

30

## 【0116】

[0117]いくつかの例では、ストローク動作は、エンドキャップと、接合と、オープンパスとを処理するために頂点パステータ入力の3つの追加のフィールドを使用することができる。たとえば、ある種の頂点座標は、パスセグメントがオープンパスの始端であるか、オープンパスの終端であるか、およびパスセグメントが破棄され得る（たとえば、パスセグメントがオープンパスの終結パスセグメントである）かどうかを示すデータを記憶することができる。以下は、上述の頂点属性を含む例示的なテンプレートである。

## 【数6】

40

```

{ XMFLOAT3(    X0,    Y0, 2.0f ),

{ XMFLOAT3(    X1,    Y1, 2.0f ),

{ XMFLOAT3(  0.0f,  0.0f, 2.0f ),

{ XMFLOAT3(  0.0f,  0.0f, 2.0f ),

```

## 【0117】

このテンプレートでは、第2の頂点のz座標（たとえば、第3の座標、すなわち属性）に関する2.0fは、そのパスセグメントがオープンパスの始端であることを示し、そのパ

50

スセグメントの始端にエンドキャップ（すなわち、スタートキャップ）を入れるように GPU 12 に信号伝達することができる。第 3 の頂点の z 座標に関する 2.0f は、そのパスセグメントがオープンパスの終端であることを示し、そのパスセグメントの終端にエンドキャップを入れるように GPU 12 に信号伝達することができる。最後の頂点の z 座標の 2.0f は、現在のプリミティブが破棄される（たとえば、そのプリミティブがオープンパスの終結ラインまたはパスセグメントである）ことを示す。

#### 【0118】

[0118] パスファイル動作を実行するために、入力アセンブラー 4.4 は、パスデータ 3.6 をメモリ 10 から取得して、パスデータ 3.6 によって指定されたパスセグメント（たとえば、パスプリミティブ）をレンダリングするために、そのパスデータをグラフィックパイプライン 4.3 の後続の 1 つまたは複数の段階に渡す。たとえば、入力アセンブラー 4.4 は、複数の頂点をメモリ 10 内に記憶された頂点バッファから取得して、頂点シェーダ 4.6 にそれらの頂点を処理させることができる。いくつかの例では、入力アセンブラー 4.4 は、処理されることになる頂点を頂点シェーダ 4.6 に直接的に渡すことができる。追加の例では、入力アセンブラー 4.4 は、リソースブロック 6.4 内の頂点バッファから、処理のために特定の頂点を検索するように頂点シェーダ 4.6 に指示することができる。

#### 【0119】

[0119] 頂点シェーダ 4.6 は、入力アセンブラー 4.4 および / またはリソースブロック 6.4 から受け取った頂点を処理して、頂点シェーダ 4.6 によって処理された各入力頂点に関する出力頂点を生成するように構成される。たとえば、各入力頂点に関して、頂点シェーダ 4.6 は、GPU 12 のシェーダユニット上で頂点シェーダプログラムのインスタンスを実行することができる。いくつかの例では、頂点シェーダ 4.6 は、各入力頂点に対して「パススルーパス」頂点シェーダプログラムを実行することができる。「パススルーパス」頂点シェーダプログラムは、頂点シェーダ 4.6 に、入力頂点ごとに、入力頂点に対応する頂点を出力させることができる。この場合、出力頂点が入力頂点と同じ属性を有する場合、出力頂点は、入力頂点に対応し得る。「パススルーパス」頂点シェーダプログラムを実装するために、いくつかの例では、頂点シェーダ 4.6 は、同じ属性をもつ出力頂点を生成するために、各入力頂点に識別変換を適用することができる。頂点シェーダ 4.6 によって受け取られた入力頂点、および頂点シェーダ 4.6 によって生成された出力頂点は、あるいは、それぞれ、入力制御点および出力制御点と呼ばれる場合がある。

#### 【0120】

[0120] さらなる例では、頂点シェーダ 4.6 は、対応する入力頂点の入力属性と同一でない出力頂点に関する 1 つまたは複数の出力属性を生成することができる。たとえば、頂点シェーダ 4.6 は、出力頂点に関する 1 つまたは複数の属性を生成するために、入力頂点の属性のうちの 1 つまたは複数に関して実質的な処理を実行することができる。一例として、頂点シェーダ 4.6 は、出力頂点のための 1 つまたは複数の属性を生成するために、入力頂点の位置属性に対して世界変換、ビュー変換、投影変換、またはそれらの任意の組合せのうちの 1 つまたは複数を実行することができる。別の例として、頂点シェーダ 4.6 は、出力頂点に関する出力属性のセットを生成するために、入力属性のセットから追加および / または属性を削除することができる。

#### 【0121】

[0121] ション段階 6.2（すなわち、ハルシェーダ 4.8、テッセレータ 5.0、およびドメインシェーダ 5.2）は、テッセレーションエンジンを形成することができ、入力パスデータによって定義されたパスセグメントを複数のラインセグメントにテッセレートすることができる。複数のラインセグメントは、レンダリングされることになるパスセグメントの曲率を近似することができる。一般に、ハルシェーダ 4.8 は、さらなる処理のために、頂点シェーダ 4.6 から受け取った制御点をドメインシェーダ 5.2 に渡して、構成データをテッセレータ 5.0 に提供することができる。テッセレータ 5.0 は、特定のタイプのパスセグメントを表す 1 つもしくは複数のパラメータ式が評価されるべき値を決定することができる。ドメインシェーダ 5.2 は、テッセレータ 5.0 によって決定された値でパラメータ式を

10

20

30

40

50

評価して、各評価に関する頂点を出力することができる。いくつかの例では、ドメインシェーダ 5 2 によって出力された頂点の各々は、その頂点の位置を示す 1 つまたは複数の属性を含み得る。追加の例では、ドメインシェーダ 5 2 によって出力された頂点の各々は、その頂点と関連付けられたパスレンダリングプリミティブのタイプを示す 1 つまたは複数の属性を含み得る。

#### 【 0 1 2 2 】

[0122] いくつかの例では、ハルシェーダ 4 8 は、頂点シェーダ 4 6 および / またはリソースブロック 6 4 から受け取った制御点を処理することができる、ハルシェーダ 4 8 によって実行されたハルシェーダプログラムの各インスタンスに関する出力制御点を生成することができる。たとえば、ハルシェーダ 4 8 によって生成されることになる各出力制御点に関して、ハルシェーダ 4 8 は、GPU 1 2 のシェーダユニット上でハルシェーダプログラムのインスタンスを実行することができる。いくつかの例では、ハルシェーダ 4 8 は、各出力制御点に対して「パススルー」ハルシェーダプログラムを実行することができる。「パススルー」ハルシェーダプログラムは、ハルシェーダ 4 8 に、出力制御点ごとに、入力制御点のそれぞれに対応する制御点を出力させることができる。この場合、出力制御点が入力制御点と同じ属性を有する場合、出力制御点は、入力制御点に対応し得る。

#### 【 0 1 2 3 】

[0123] さらなる例では、ハルシェーダ 4 8 は、入力制御点のうちのそれぞれ 1 つの入力属性と同一でない出力制御点に関する 1 つまたは複数の出力属性を生成することができる。たとえば、ハルシェーダ 4 8 は、出力制御点に関する 1 つまたは複数の属性を生成するために、入力制御点の属性のうちの 1 つまたは複数に関して実質的な処理を実行することができる。別の例として、ハルシェーダ 4 8 は、出力制御点に関する出力属性のセットを生成するために、入力属性のセットから属性を追加および / または削除することができる。いくつかの例では、下でさらに詳細に説明するように、GPU 1 2 が終点パラメータ表示の形である、橙円弧に関するパスデータを受け取る場合、ハルシェーダ 4 8 は、その橙円弧の終点パラメータ表示をその橙円弧の中心パラメータ表示に変換することができる。

#### 【 0 1 2 4 】

[0124] 追加の例では、ハルシェーダ 4 8 は、特定のレンダリング動作に関して、レンダリングされるべきではないプリミティブを破棄することができる。プリミティブを破棄することは、プリミティブに対応するデータをグラフィックスパイプライン 4 3 のさらなる段階に渡させず、それによって、そのようなプリミティブをパイプラインの残りによって効果的にレンダリングさせないプロセスを指す場合がある。たとえば、グラフィックスパイプライン 4 3 がフィル動作を実行しているとき、ハルシェーダ 4 8 は、接合プリミティブとキャッププリミティブとを破棄することができる。別の例として、グラフィックスパイプライン 4 3 がストローク動作を実行しているとき、ハルシェーダ 4 8 は、オープンパスのためのクローズパスプリミティブを破棄することができる。クローズパスプリミティブは、ループを閉じるラインパスセグメントを表すプリミティブを指す場合がある。クローズパスプリミティブは、一般に、オープンパスではなくクローズパスであるパスのために使用される。いくつかの例では、クローズパスプリミティブは、パス中の他のラインパスセグメントを識別するために使用されるプリミティブタイプ識別子とは異なるプリミティブタイプ識別子によって識別され得る。たとえば、クローズパスプリミティブは、2 . 0 f の代わりに 2 . 1 f のプリミティブタイプ識別子によって識別され得る。

#### 【 0 1 2 5 】

[0125] ハルシェーダ 4 8 は、各パスセグメントに関するパッチ定数関数のインスタンスを実行することもできる。パッチ定数関数は、出力値を生成するとき、テッセレータ 5 0 によって使用されることになる構成パラメータを決定して、テッセレータ 5 0 に提供することができる。たとえば、パッチ定数関数は、ハルシェーダ 4 8 にテッセレーション係数をテッセレータ 5 0 に提供させることができる。テッセレーション係数は、テッセレータ 5 0 が特定のテッセレーションドメインに適用されるテッセレーションの程度（たとえば、ドメインがどの程度微細に再分割されるべきか、および / またはドメインが再分割され

10

20

30

40

50

るべきより小さなオブジェクトの数)を指定することができる。いくつかの例では、ハルシェーダ48は、テッセレータ50に、3次ベジェ曲線に対して4×のテッセレーションを実行することと、ラウンド接合および円形キャップに対して4×のテッセレーションを実行することと、ラインセグメントに対して1×テッセレーションを実行することを行わせることができる。

#### 【0126】

[0126]別の例として、パッチ定数関数は、ハルシェーダ48に、テッセレーション中に使用されることになるテッセレーションドメインのタイプをテッセレータ50に提供させることができる。テッセレーションドメインは、ドメインシェーダ52によって使用されるための複数の座標を生成するために、テッセレータ50によって使用されるオブジェクトを指す場合がある。概念的に、テッセレーションドメインは、テッセレータ50によって複数のより小さなオブジェクトに再分割されるオブジェクトに対応し得る。より小さなオブジェクトの頂点の位置座標は、次いで、さらなる処理のために、ドメインシェーダ52に送られる。いくつかの例では、テッセレーションドメインのタイプは、クワッド、トライ、および等値線のうちの1つになるように選択され得る。いくつかの例では、ドメインが再分割される先である、より小さいオブジェクトは、三角形、ラインセグメント、または点に対応し得る。いくつかの例では、ハルシェーダ48は、等値線テッセレーションドメインタイプを指定して、テッセレータ50が等値線ドメインをラインセグメントに再分割すべきであることを指定することができる。

#### 【0127】

[0127]テッセレータ50はまた、テッセレーション段階62によって処理される各パスセグメントに関する複数の出力値も生成することができる。出力値は、特定のタイプのパスセグメントを表す1つまたは複数のパラメータ式がドメインシェーダ52によって評価されるべき値を決定することができる。いくつかの例では、テッセレータ50は、ハルシェーダ48によってテッセレータ50に提供された1つもしくは複数のテッセレーション係数および/またはテッセレーションドメインタイプに基づいて、複数の出力値を生成することができる。たとえば、テッセレータ50は、等値線を複数のラインセグメントに再分割して、正規化された座標系内の複数のラインセグメントの各終点に関する出力値を生成することができる。

#### 【0128】

[0128]ドメインシェーダ52は、テッセレータ50から出力値を受け取り、ハルシェーダ48からパスセグメントに関する制御点を受け取り、パスセグメントの曲率および/または形状を近似する複数のテッセレートされたラインセグメントに対応する出力頂点を生成することができる。たとえば、テッセレータ50から受け取られた出力値の各々に関して、ドメインシェーダ52は、GPU12のシェーダユニット上でドメインシェーダプログラムのインスタンスを実行することができる。ドメインシェーダプログラムは、ドメインシェーダ52に、テッセレータ50から受け取った出力値の各々について、それぞれの出力値に対応する出力頂点に関する位置座標を生成するために、それぞれの出力値に基づいて決定された特定の値で、1つまたは複数のパラメータ式を評価させることができる。出力頂点座標を生成するために使用されるパラメータ式の係数のうちの1つまたは複数は、ハルシェーダ48から受け取った制御点のうちの1つまたは複数に基づいて定義され得る。各出力頂点は、複数のテッセレートされたラインセグメントのうちの1つの終点に対応し得る。2つの連続する出力頂点は、単一のテッセレートされたラインセグメントの終点に対応し得る。

#### 【0129】

[0129]追加の例では、ドメインシェーダプログラムは、ドメインシェーダ52に、テッセレータ50から受け取った出力値の各々に対応する出力頂点に関する正規座標を生成させることができる。たとえば、ドメインシェーダプログラムは、ドメインシェーダ52に、テッセレータ50から受け取った出力値の各々について、それぞれの出力値に対応する出力頂点に関する接線座標を生成するために、それぞれの出力値に基づいて決定された特

10

20

30

40

50

定の値で、1つまたは複数の追加のパラメータ式を評価させることができる。出力頂点に関する接線座標は、出力頂点においてパスセグメントと交差するパスセグメントの接線の方向を示すことができる。ドメインシェーダ52は、それぞれの出力頂点に対応する接線座標に基づいて出力頂点の各々に関する正規座標を生成することができる。特定の出力頂点のために生成された正規座標は、出力頂点においてパスセグメントと交差するパスセグメントの接線に対して直角である方向を示す法線ベクトルを示すことができる。

#### 【0130】

[0130]いくつかの例では、グラフィックスパイプライン43がフィル動作を実行しているとき、ドメインシェーダ52は、そのようなロケーションのためのいかなる法線も生成することなしに、テッセレートされたラインセグメントの終点のロケーションに対応する頂点を生成することができる。そのような例では、グラフィックスパイプライン43がストローク動作を実行しているとき、ドメインシェーダ52は、いくつかの例では、テッセレートされたラインセグメントの終点のロケーションに対応する頂点を生成し、そのようなロケーションに対応する法線を生成することができる。

10

#### 【0131】

[0131]ドメインシェーダ52は、隣接する頂点の各セットがテッセレートされたラインセグメントを表す、順序付けられた順番で頂点を出力することができる。ラインセグメントは、頂点バッファ内で定義されたパスセグメントを集合的に近似することができる。たとえば、ドメインシェーダ52は、以下のラインセグメント{0, 1}、{1, 2}、{2, 3}、{3, 4}、{4, 5}を定義する頂点の以下のセット{0, 1, 2, 3, 4, 5}を出力することができる。追加の例では、ドメインシェーダ52は、前の例で列挙されたのと同じラインセグメントを定義し得る頂点の以下のセット{0, 1, 1, 2, 2, 3, 3, 4, 4, 5}を出力することができる。

20

#### 【0132】

[0132]いくつかの例では、テッセレータ50およびドメインシェーダ52は、以下の技法に従って、パスセグメントを複数のラインセグメントに均一にテッセレートするように構成され得る。具体的には、テッセレータ50は、パラメータ評価のための座標を出力することができる（たとえば、 $t = 0 / T, 1 / T, 2 / T, \dots, T / T$ 、式中、Tはテッセレーション係数である）。プリミティブのタイプに応じて、ドメインシェーダ52は、テッセレータ50によって出力された値で1つまたは複数のパラメータ式を評価することができる。

30

#### 【0133】

[0133]ジオメトリシェーダ54は、テッセレートされたラインセグメントをドメインシェーダ52から受け取って、それらのテッセレートされたラインセグメントに基づいて、複数のプリミティブを生成することができる。このようにして、ジオメトリシェーダ54は、ラインセグメントのためのセグメント順序を決定することができる。テッセレートされたラインセグメントの各々に関して、ジオメトリシェーダ54は、GPU12のシェーダユニット上でジオメトリシェーダプログラムのインスタンスを実行して、それぞれのテッセレートされたラインセグメントに基づいて、テッセレートされたラインセグメントに関する三角形プリミティブを生成することができる。いくつかの例では、テッセレートされたラインセグメントの各々に関して、ジオメトリシェーダ54は、それぞれのテッセレートされたラインセグメントに対応する2つの頂点をドメインシェーダ52から受け取って、三角形プリミティブに対応する3つの頂点のセットを生成することができる。

40

#### 【0134】

[0134]いくつかの例では、三角形プリミティブの頂点のうちの2つは、2つの受け取った頂点と同じ頂点であり得る（たとえば、同じ位置座標を有し得る）。そのような例では、ジオメトリシェーダ54は、レンダリングされることになるパスセグメントと関連付けられたすべてのテッセレートされたラインセグメントに共通である共通の頂点に基づいて、第3の頂点を生成することができる。共通の頂点は、テッセレートされたラインセグメントの終点のうちの1つに対応してよく、または対応しなくてもよい。いくつかの例では

50

、共通の頂点は、レンダリングされることになるパスセグメントに関する、テッセレートされたラインセグメントに対応する頂点のセット内の第1の頂点に対応し得る。

#### 【0135】

[0135]ジオメトリシェーダ54は、ドメインシェーダ52によって作り出された、テッセレートされたラインセグメントの各々に関して一回度起動され得る。テッセレートされたラインセグメントの各々に関して、ジオメトリシェーダ54は、三角形の第1の頂点として共通の制御点を使用し、三角形の第2の頂点および第3の頂点として、それぞれのテッセレートされたラインセグメントの2つの終点を使用して、三角形プリミティブを生成することができる。たとえば、ドメインシェーダ52が、以下のラインセグメント $\{0, 1\}$ 、 $\{1, 2\}$ 、 $\{2, 3\}$ 、 $\{3, 4\}$ 、 $\{4, 5\}$ を定義する、以下の頂点のセット $\{0, 1, 2, 3, 4, 5\}$ を生成した例が上で提供された。上記の一連のラインセグメントの場合、ジオメトリシェーダ54は、以下の三角形、 $\{C, 0, 1\}$ 、 $\{C, 1, 2\}$ 、 $\{C, 2, 3\}$ 、 $\{C, 3, 4\}$ 、 $\{C, 4, 5\}$ 、 $\{C, 5, 0\}$ を生成することができ、式中、Cは三角形のすべてに共通する任意の単一の頂点である。

10

#### 【0136】

[0136]ラスタライザ56は、複数の3Dグラフィックスプリミティブ(たとえば、点、線、および三角形)をそれらの3Dグラフィックスプリミティブに対応する複数の画素に変換するように構成され得る。たとえば、ラスタライザ56は、三角形プリミティブに対応する3つの頂点を受け取って、それらの3つの頂点を、その三角形プリミティブによってカバーされたスクリーン画素位置に対応する複数の画素に変換することができる。三角形プリミティブによってカバーされたスクリーン画素位置は、三角形の頂点、三角形の縁、および三角形の内部に対応するスクリーン画素位置を含み得る。

20

#### 【0137】

[0137]ピクセルシェーダ58は、画素をラスタライザ56から受け取って、ピクセルシェーダプログラムに従って、受け取った画素に基づいて、影付き画素を生成することができる。たとえば、ラスタライザ56から受け取った各画素に関して、ピクセルシェーダ58は、GPU12のシェーダユニット上でピクセルシェーダプログラムのインスタンスを実行することができる。いくつかの例では、ピクセルシェーダ58は、各画素に対して「パススルー」ピクセルシェーダプログラムを実行することができる。「パススルー」ピクセルシェーダプログラムは、ピクセルシェーダ58に、画素ごとに、入力画素のそれぞれに対応する画素を出力させることができる。この場合、出力画素が入力画素と同じ属性を有する場合、出力画素は、入力画素に対応し得る。

30

#### 【0138】

[0138]さらなる例では、ピクセルシェーダ58は、入力画素のうちのそれぞれの1つの入力画素の入力属性と同一でない、出力画素に関する1つまたは複数の出力属性を生成することができる。たとえば、ピクセルシェーダ58は、出力画素に関する1つまたは複数の属性を生成するために、入力画素の属性のうちの1つまたは複数に関して実質的な処理を実行することができる。別の例として、ピクセルシェーダ58は、出力画素に関する出力属性のセットを生成するために、入力属性のセットから属性を追加および/または削除することができる。

40

#### 【0139】

[0139]出力統合器60は、ピクセルシェーダ58から受け取った画素データをレンダターゲット(たとえば、フレームバッファまたはステンシルバッファ)内に配置することができる。いくつかの例では、出力マージャ60は、ピクセルシェーダ58から受け取った画素データをラスタ演算に基づいてレンダターゲット内にすでに記憶されている画素データと併合することができる。

#### 【0140】

[0140]パスファイル動作を実行するために、ラスタライザ56は、共通のステンシルバッファ(たとえば、リソースロック64に記憶されたバッファ)にジオメトリシェーダ54によって受け取った三角形の各々をラスタライズすることができる。第1のパス中に、

50

ピクセルシェーダ 5 8 は、出力統合器 6 0 に入力画素を直接パスするために、無効化されるか、または「パススルー」モードに設定され得る。出力統合器 6 0 は、1 つまたは複数のステンシルバッファフィル技法に従ってパスセグメントに関するフィル領域を示す値をステンシルバッファが記憶するようにステンシルバッファをポピュレートするように構成され得る。

【0141】

[0141]本開示の態様によれば、上記のように、GPU 1 2 は、以下のステップを伴うステンシル TIR とバウンディングボックスとを使用する単一のパス手法を使用してフィル動作を実行することができる。

【0142】

1. 複数のラインセグメントにパスセグメントをテッセレートする。

【0143】

2. ラインセグメントごとに三角形プリミティブを生成する。

【0144】

3. ステンシルバッファに三角形プリミティブのすべてをレンダリングする。

【0145】

4. ステンシル中にバウンディングボックスを決定する。

【0146】

5. ステンシル TIR を用いてバウンディングボックスをレンダリングする。

【0147】

上記の例では、GPU 1 2 は、(本明細書ではテッセレーションエンジンと呼ばれる場合もある)テッセレーション段階 6 2 に、バウンディングボックスパラメータ(たとえば、`bb_box`)をリセットすべきであることを示すイベント(たとえば、`bb_start`)を送ることができる。GPU 1 2 は、次いで、上記で説明したプロセスを使用してステンシルバッファを更新しながら、三角形プリミティブを生成することができる。さらに、テッセレーション段階 6 2 は、最小~最大パラメータを頂点データと比較することによってバウンディングボックスパラメータ(`bb_box`)を更新する。すなわち、テッセレーション段階 6 2 は、たとえば、デカルト座標を使用して前に決定された頂点のさらに上、下、右側、左側に位置する口케ーションを頂点が有するかどうかを決定するために頂点の各々を検査することができる。頂点が他の頂点に対して最外口ケーションに位置する場合、テッセレーション段階 6 2 は、バウンディングボックスパラメータ(`bb_box`)を更新することができる。

【0148】

[0142]テッセレーション段階 6 2 がバウンディングボックス終了イベント(たとえば、`bb_end`)を受け取ると、テッセレーション段階は、たとえば、パスの三角形プリミティブを包含するバウンディングボックスを形成する決定されたバウンディングボックス座標に対応する`rectlist`を生成することができる。ラスタライザ 5 6 は、次いで、バウンディングボックスをラスタライズすることができる。本開示の態様によれば、ラスタライザ 5 6 は、レンダターゲットに対してステンシルされた画素をスーパーサンプリングするステンシル TIR を実行することができ、ピクセルシェーダ 5 8 は、ステンシルされた画素のみをシェーディングする。ピクセルシェーダ 5 8 が画素をシェーディングするとき、画素のステンシル値がステンシルバッファから消去され得る。

【0149】

[0143]したがって、上記で説明した例では、テッセレーション段階 6 2 は、バウンディングボックス開始イベント(`bb_start`)とバウンディングボックス終了イベント(`bb_end`)との間にバウンディングボックスパラメータ(`bb_box`)の累積を維持する。(たとえば、ジオメトリシェーダ 5 4、ラスタライザ 5 6、ピクセルシェーダ 5 8 および/または出力統合器 6 0 を含む)レンダバッケンドは、バウンディングボックス開始イベント(`bb_start`)とバウンディングボックス終了イベント(`bb_end`)との間に固定動作を予想する。すなわち、レンダバッケンドは、(GPU ドラ

10

20

30

40

50

イバ28(図2)などの)ドライバがレンダバックエンドレジスタをプログラムすることなしにバウンディングボックスを決定することに関連する動作を実行することができ、これはリソースブロック64中に割り当てられ得る。テッセレーション段階62に関して説明したが、上記の技法がグラフィックスパイプラインの1つまたは複数の他の段階によって実行され得ることを理解されたい。このようにして、GPU12は、別個のパス中にバウンディングボックスをレンダリングする必要なしに単一のパスでパスをフィルするためにはグラフィックスパイプライン43を使用することができる。

#### 【0150】

[0144]本開示の他の態様によれば、グラフィックスパイプライン43は、ストロークされたパスセグメントに関するダッショングを実行するように構成され得る。説明のための一例では、ジオメトリシェーダ54は、ドメインシェーダ52からテッセレートされたラインセグメントを受け取り、テッセレートされたラインセグメントに基づいて複数の三角形プリミティブを生成することができる。複数のプリミティブは、シェーディングされることになるダッシュセグメントを含み得、複数のプリミティブは、特定の順序、たとえば、セグメント順序であり得る。ジオメトリシェーダ54(またはグラフィックスパイプライン43の別の構成要素)はまた、ダッシュの各々の長さを決定することができる。

10

#### 【0151】

[0145]さらに、ジオメトリシェーダ54は、各ダッシュが生成されるとダッシュの長さを累積し、前のダッシュセグメント、たとえば、セグメント順序で現在のセグメントに先行するダッシュセグメントの長さのプレフィックス総和を各ダッシュセグメントに割り当てる。たとえば、第1のダッシュセグメントには、0のプレフィックス総和が割り当て得、第2のダッシュセグメントには、長さ優先ダッシュセグメントのプレフィックス総和が割り当てられ得、第3のダッシュセグメントには、第1のダッシュセグメントと第2のダッシュセグメントとの組合せの長さのプレフィックス総和が割り当てられ得、以下同様である。

20

#### 【0152】

[0146]ラスタライザ56は、一般に、ダッシュセグメントを受け取り、ラスタライゼーション中にプリミティブ順序に従い、ここで、プリミティブ順序は、レンダリングの順序を指す。ラスタライゼーションの後に、各ダッシュセグメントのためのプレフィックス総和が、ダッシュセグメントをシェーディングするときに使用するためにピクセルシェーダ58に送られ得る。たとえば、適切なロケーションにあるダッシュセグメントをシェーディングするために、ピクセルシェーダ58は、テクスチャオフセットとして各ダッシュセグメントのためのプレフィックス総和を適用することができる。テクスチャオフセットは、前のダッシュセグメントのロケーションを示し、それによって、ピクセルシェーダ58が、前のセグメントに対して適切なロケーションにある次のダッシュセグメントをシェーディングすることができる。

30

#### 【0153】

[0147]図4は、レンダリングされることになる例示的なパス80の図である。たとえば、パス80は、上部が丸く、下部が細長い「アイスクリームコーン」形状を表す。パス80は、2つの3次方程式からなるクローズパスであり得る。セグメントは、path4プリム(プリミティブ)にパックされ得る。たとえば、パス80に関する入力パスデータは、以下の形または類似の形をとることができる。

40

## 【数7】

```

{ XMFLOAT4(0.0f, 0.0f,      CUBIC, 0.0f) },

{ XMFLOAT4(0.4f, 1.2f,      0.0f, 0.0f) },

{ XMFLOAT4(1.4f, 1.2f,      0.0f, 0.0f) },

{ XMFLOAT4(1.8f, 0.0f,      0.0f, 0.0f) },

```

## 【数8】

10

```

{ XMFLOAT4(1.8f, 0.0f,      CUBIC, 0.0f) },

{ XMFLOAT4(0.5f,-3.0f,      0.0f, 0.0f) },

{ XMFLOAT4(1.3f,-3.0f,      0.0f, 0.0f) },

{ XMFLOAT4(0.0f, 0.0f,      0.0f, 0.0f) }

```

## 【0154】

20

この例では、各行は、頂点または制御点を表し、括弧内の各パラメータは、それぞれの頂点すなわち制御点の属性を表す。この例では、第1の制御点の最後の属性は、レンダリングされることになるパスセグメントのタイプを示すデータ（すなわち、「パスセグメントタイプインジケータ」）を記憶する。具体的には、この例では、パスセグメントタイプインジケータは、パスセグメントが3次ベジェパスセグメントであることを意味する0.0fである。パスセグメントに関する他の属性は、いくつかの例では、ラインパスセグメントに関して上記で説明した属性と同様の属性を含み得る。

## 【0155】

30

[0148]図5A～図5Cは、図4に示されるパス80のための例示的なフィル動作を示す一連の図である。パス80は、例示のために、図5A～図5Cの例においてテッセレートされている（たとえば、通常より少ないセグメントを有する）。さらに、説明のためにGPU12に関して説明したが、図5A～図5Cにおいて実行されるプロセスは、様々な他のプロセッサによって実行され得る。

## 【0156】

40

[0149]図5Aに示されるように、GPU12は、ラインストリップ方式84で接続されたいいくつかの頂点82を含めるためにパス80をテッセレートする。図5Bに示されるように、GPU12は、いくつかの三角形プリミティブを形成するためにピボット点88に接続されたいいくつかのラインセグメント86を生成する。図5Bの例では、パス80の相対的な第1の頂点は、ピボット点88として使用される。三角形の巻上げ順序が適切なステンシル動作を決定する。たとえば、あらゆる生成されたラインセグメントがピボット点88に接続される。三角形の得られた配向（たとえば、時計回りまたは反時計回り）は、三角形プリミティブの巻上げ順序を決定することができる。巻上げ順序は、様々な方法でステンシル値に影響を及ぼすことができる（たとえば、時計回りの巻上げ順序の場合にステンシル値を増分するか、または反時計回りの巻上げ順序の場合にステンシル値を減分する）。

## 【0157】

[0150]この例では、GPU12は、ステンシル中に図5Bに示される三角形プリミティブをシェーディングしない。むしろ、上記のように、ステンシル中にレンダリングされる三角形プリミティブは、ステンシルテクスチャ90にのみ影響を及ぼす。すなわち、ステンシルテクスチャ90は、画像中に現れる、たとえば、レンダリングされ、シェーディングされるパスの部分を示す。

50

## 【0158】

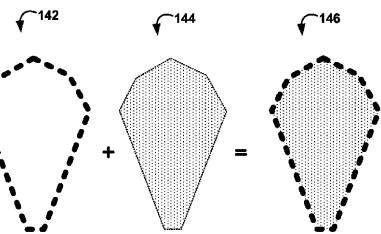

[0151]図5Cに示されるように、GPU12は、ステンシルテクスチャ90を包含するバウンディングボックス92を決定する。すなわち、バウンディングボックスは、フィルされることになるパスの全体をカバーする。GPU12は、次いで、フィルされたパス96を生成するためにバウンディングボックス92に対してステンシルTIRを実行する。このようにして、GPU12は、バウンディングボックス92を決定し、単一のレンダリングパスでパス80をフィルする。

## 【0159】

[0152]図6は、ステンシル動作を示す概念図である。たとえば、説明のために、GPU12が $16 \times$ のMSAAを使用してプリミティブ100をレンダリングすると仮定する。この例では、各方形は、画素102のサンプルを表す。

10

## 【0160】

[0153]本開示の態様によれば、GPU12は、ステンシルTIRを実行することができる。したがって、GPU12は、レンダターゲットパラメータ（たとえば、レンダリングされた画素のためのメモリ割当て）から独立してステンシルパラメータ（たとえば、ステンシルサンプリングレート）を決定することができる。この例では、GPU12は、画素がサンプルごとのステンシルテストをパスしたかどうかに基づいて画素をレンダリングするためのカバレージ値を決定することができる。

## 【0161】

[0154]いくつかの例では、GPU12は、サンプルが非ゼロ値を有するかどうかを決定するためにステンシルテストを実行することができる。たとえば、GPU12は、非ゼロのステンシル値を有するサンプルがレンダリングされるゼロ／非ゼロステンシルテストを実行することができる。別の例では、GPU12は、奇数の（または偶数の）値を有するサンプルがレンダリングされる奇数／偶数ステンシルテストを実行することができる。したがって、いくつかの例では、GPU12は、サンプルが奇数値を有するかどうかを決定するためにステンシルテストを実行することができる。さらに他の例では、GPU12は、サンプルが偶数値を有するかどうかを決定するためにステンシルテストを実行することができる。

20

## 【0162】

[0155]いずれの場合も、図6に示される例では、画素102の（この場合も、ボックスによって表される）16個サンプルのうちの10個がプリミティブ100内に位置する。したがって、プリミティブ100のためのカバレージマスクは画素102を含み得、GPU12は、レンダリング中に画素102をシェーディングすることができる。

30

## 【0163】

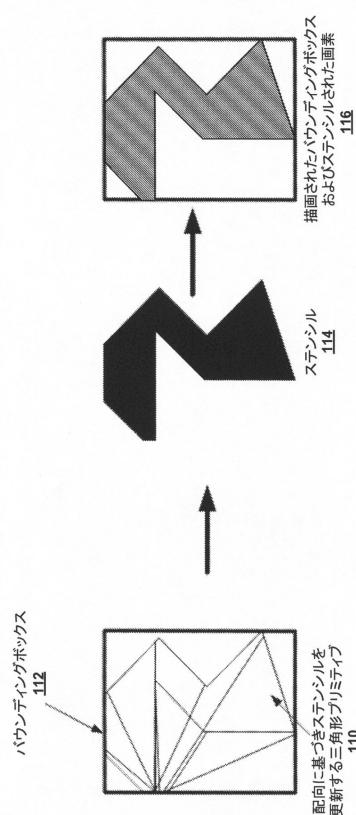

[0156]図7は、本開示の態様による、例示的なフィル動作を示す概念図である。たとえば、図7に、三角形プリミティブを決定し、プリミティブ110の配向に基づいてステンシルバッファを更新することと、プリミティブの最外点と、ステンシルバッファ114のコンテンツと、描画されたバウンディングボックスおよびステンシルされた画素116とに基づいてバウンディングボックス112を決定することとを示す。

## 【0164】

40

[0157]いくつかの例によれば、ステンシル中に含まれるプリミティブをステンシルし、レンダリングする間にバウンディングボックスを決定するシーケンスは、以下のAPI呼出しを使用してGPU12によって実行され得る。

## 【0165】

Draw\_BB() // 描画呼出し内のプリミティブのバウンディングボックスを計算する

// または、BeginQuery()...EndQuery()であり得る

// ピクセルシェーダの境界が画定されない場合、境界ボックスだけが

// 計算され、プリミティブはレンダリングされない

Render\_BB() // 以前に計算されたバウンディングボックスを

50

// レンダリングするか、またはプリミティブが送られずに、

// ピクセルシェーダおよび他のバックエンド状態が指定されることを除いて、描画呼

出しと同じ

// DrawIndirectのような方法であり得る

ここで、Draw\_BBは、GPU12に、(画素をレンダリングすることなしに)ステンシル中にバウンディングボックス112を決定するように命令し、Renderer\_BBは、GPU12に、バウンディングボックスの上でステンシルTIRを実行するように命令する。このようにして、GPU12は、バウンディングボックスを決定し、単一のレンダリングパスでパスのフィルを実行することができる。

【0166】

10

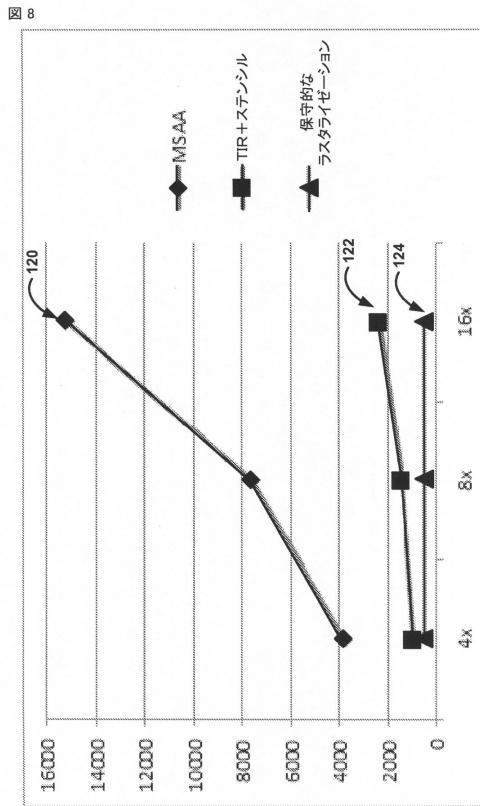

[0158]図8は、本開示の態様による、レンダリング中のメモリ帯域幅を示すグラフである。たとえば、図8に、3つの異なるアンチエイリアシングレート(4x、8x、16x)、ならびにテッセレーションおよびジオメトリシェーディングが実行されるMSAA方式120と、ステンシルTIR方式122と、保守的なラスタライゼーション方式124(たとえば、ループプリントプロセス)との3つのレンダリング方式の各々のためのレートに関連付けられた関連するデータ転送を示す。図8に示される帯域幅要件は、60フレーム毎秒(fps)および32ビットの色と、24ビットの深度と、8ビットのステンシルとを有するバッファフォーマットでレンダリングされる画像のテストシーケンスに関連付けられる。

【0167】

20

[0159]図8のグラフに示されるように、MSAA120のためのメモリ帯域幅要件は、ステンシルTIR122および保守的なラスタライゼーション124のためのメモリ帯域幅要件よりもかなり高い。以下に示される表1に、MSAA120と、保守的なラスタライゼーション124と、ステンシルTIR122との比較を示す。

【表1】

表1

|                  | MSAA                         | 保守的なラスタライゼーション           | ステンシルTIR                          |

|------------------|------------------------------|--------------------------|-----------------------------------|

| 品質               | 同様                           | わずかにより良好                 | 同様                                |

| メモリ帯域幅           | 高い                           | 低い<br>(サンプルごとに<br>1つの画素) | 低い(ステンシル+<br>サンプルごとに<br>1つの画素)    |

| 画素<br>シェーディング    | なし                           | 極めて高い                    | なし                                |

| HWの変更            | すでに存在                        | 小さい                      | 中程度                               |

| APIの変更           | すでに存在                        | 小さい                      | 中程度                               |

| ジオメトリ作業          | CPU<br>(テッセレーション<br>エンジンに移動) | CPU<br>(複雑なアルゴリズム)       | より少ないCPU<br>(テッセレーション<br>エンジンに移動) |

| 一般的なパス<br>レンダリング | はい                           | いいえ                      | はい                                |

| 重複パス             | はい                           | いいえ                      | はい                                |

30

【0168】

[0160]以下に示される表2に、MSAA120と、ステンシルTIR122と、保守的なラスタライゼーション124との間の追加の比較を示す。

50

【表2】

表2

|             | Nx MSAA: | NxTIR +<br>ステンシル: | 保守的な<br>ラストライゼーション        |

|-------------|----------|-------------------|---------------------------|

| サンプルテスト(HW) | Nx       | Nx                | 1x                        |

| 深度バッファ更新    | Nx       | なし                | なし                        |

| ステンシルバッファ更新 | Nx       | Nx                | なし                        |

| 色バッファ更新     | Nx       | 1x                | 1x                        |

| ピクセルシェーダ起動  | 1x       | 1x                | 1x(比較的複雑な画素<br>シェーディング段階) |

10

## 【0169】

[0161]図9A～図9Dは、図4に示されるパスのための例示的なダッキング動作を示す一連の図である。やはり、説明のために、図9A～図9Dの例では、パス80はテッセレートされている。さらに、説明のためにGPU12に関して説明したが、図9A～図9Dにおいて実行されるプロセスは、様々な他のプロセッサによって実行され得る。

20

## 【0170】

[0162]図9Aに示されるように、GPU12は、ラインストリップ84中で接続されたいいくつかの頂点82を含めるためにパス80をテッセレートする。さらに、GPU12は、(頂点から伸びる矢印として示されている)法線130の数を決定する。図9Aの例では、二重の法線130は、接合口ケーションを示す。接合を作成するには、ラインストリップ中の次のプリミティブの終点接線を必要とし得る。図9Aはまた、例示的なセグメント132を含む。

## 【0171】

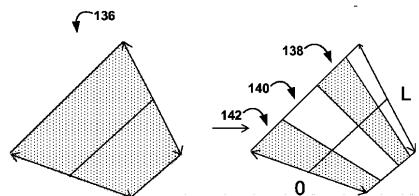

[0163]図9Bに、セグメント132がストローク幅/2だけ+/-法線方向に膨張される膨張動作をGPU12がセグメント132に対して実行することを示す。説明のために図9Bの例に追加の太いストロークが示される。図9Bに、膨張されたセグメント134と、ストロークされ膨張されたセグメント136とを示す。

30

## 【0172】

[0164]図9Cに、ダッキングし、ストロークされ、膨張されたセグメント136を示す。たとえば、GPU12は、第1のダッシュセグメント138と、第2のダッシュセグメント140と、第3のダッシュセグメント142とを決定することができる。この例では、第1のダッシュセグメント138と第3のダッシュセグメント142とは、可視セグメントであり、一方、第2のダッシュセグメント140は不可視ダッシュセグメントである。ダッキングのために、GPU12は、各ダッシュセグメント(線)138、140、および142のための開始口ケーションを決定する。上記のように、いくつかの例では、プレフィックス総和ユニット42は、ジオメトリシェーディング中にダッシュセグメント138～142の長さを累積することができる。

40

## 【0173】

[0165]GPU12は、テクスチャ座標のためのテクスチャオフセットとして0から線長さLまでの長さを適用することができる。たとえば、本開示の態様によれば、プレフィックス総和ユニット42は、セグメント138～142の各々の口ケーションを示すline length値を計算することができる。プレフィックス総和装置42は、ピクセルシェーダ段階にプレフィックス総和したline length値を送ることができ、これは、画素シェーディング中にセグメント138～142のそれぞれの口ケーションを決定す

50

る。GPU12は、可視ダッシュパターンの一部を形成するので可視セグメント138および142を(シェーディングされたフラグメントとして)保持し、ダッシュパターン中で不可視であるのでセグメント140を(シェーディングすることなしに)破棄する。

#### 【0174】

[0166]いくつかの例では、`pointsize`などのプリミティブごとのスカラー値を決定することをサポートするグラフィックスAPIは、スカラー長さを決定するようにGPU12に命令するために使用され得る。本開示の態様によれば、グラフィックスAPIは、`lineLength`値をサポートすることができる。この`lineLength`値は、プリミティブの同じフラット属性であり得るが、属性は、ピクセルシェーダ段階に与えられ得る。たとえば、GPU12は、画素シェーディング中にオフセット座標を決定するためにテッセレートされたプリミティブごとにプレフィックス総和パスを適用することができる。さらに、API呼出し(`query_start/end`と同様の)`prsum_start`、`prsum_end`は、破線の相対的な開始および終了を示す1つまたは複数の描画呼出しを括弧化することができる。

10

#### 【0175】

[0167]図9Dに、フィルされ、ダッシングされたパス146を生成するために、ダッシングされたストローク142のフィルされたパス144への追加を示す。

#### 【0176】

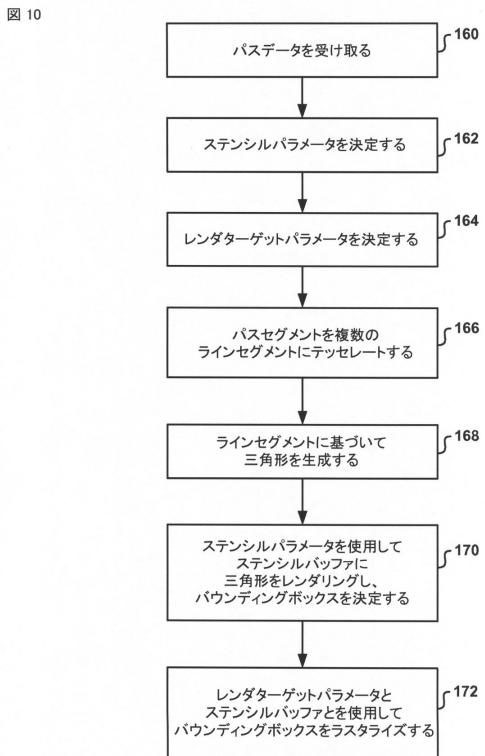

[0168]図10は、本開示による、フィル動作を実行するための例示的な技法を示す流れ図である。説明のためにGPU12によって実行されるものとして説明したが、図10に示される技法が、様々な他のプロセッサによって実行され得ることを理解されたい。さらに、本技法を実行するために、図示したステップよりも少ないステップ、それに追加のステップ、またはそれとは異なるステップが使用され得る。

20

#### 【0177】

[0169]図10の例では、GPU12は、パスデータを受け取る(160)。パスデータは、レンダリングされることになるパスの1つまたは複数のパスセグメントを示し得る。GPU12はまた、ステンシルパラメータを決定する(162)。いくつかの例では、ステンシルパラメータは、パスの各アンチエイリアス画素のカバレージ値を決定するためのサンプリングレートを示し得る。GPU12はまた、ステンシルパラメータとは別々に、レンダターゲットパラメータを決定する(164)。レンダターゲットパラメータは、パスの各アンチエイリアス画素のためのメモリ割当てを示し得る。

30

#### 【0178】

[0170]GPU12は、パスデータによって定義されたパスセグメントを複数のラインセグメントにテッセレートする(166)。たとえば、GPU12は、図5Aに示されるラインストリップなどのラインストリップにパスデータをテッセレートすることができる。GPU12は、次いで、複数のラインセグメントに基づいて複数の三角形プリミティブを生成する(168)。複数の三角形プリミティブの各々は、複数のラインセグメントのそれぞれに基づいて生成され得る。所与のパスセグメントに関する複数の三角形プリミティブの各々は、共通の頂点を共有することができる。三角形プリミティブの各々の他の2つの頂点は、複数のラインセグメントのそれぞれの終点に対応し得る。

40

#### 【0179】

[0171]GPU12は、ステンシルパラメータを使用して共通のステンシルバッファに複数の三角形プリミティブの各々をレンダリングし、バウンディングボックスを決定する(170)。たとえば、上記のように、GPU12は、ステンシル中に三角形プリミティブをシェーディングしない。しかしながら、GPU12は、プリミティブのためのバウンディングボックスを決定するために三角形プリミティブの最外点を決定することができる。いくつかの例では、GPU12は、各三角形プリミティブに関する座標を決定し、プリミティブが前の三角形プリミティブの最外点を越えて拡大するたびに、上部境界点、下部境界点、右境界点、および/または左境界点を上書きすることができる。

#### 【0180】

50

[0172]ステンシルバッファに三角形プリミティブのすべてをレンダリングした後に、ステンシルバッファは、どのピクセルがパスセグメントに関するフィル領域の内側にあるかを示すデータを記憶することができる。さらに、バウンディングボックスは、三角形プリミティブの各々を包含する。

【0181】

[0173]GPU12は、次いで、レンダターゲットパラメータとステンシルバッファとを使用してバウンディングボックスをラスタライズする(172)。たとえば、本開示の様によれば、GPU12は、パスデータの各画素の色値を決定するために、バウンディングボックスに対してステンシルTIRを実行する。ステンシルバッファ中のデータにより、フィル領域内の画素がフィル色を用いてシェーディングされ、フィル領域の外部にある画素がシェーディングなしのままにされるようになり得る。バウンディングボックスのレンダリングが完了すると、レンダターゲット(たとえば、フレームバッファ)は、レンダターゲットパラメータを使用してパスセグメントに関するフィル領域の、ラスタライズされたバージョンを記憶することができる。

【0182】

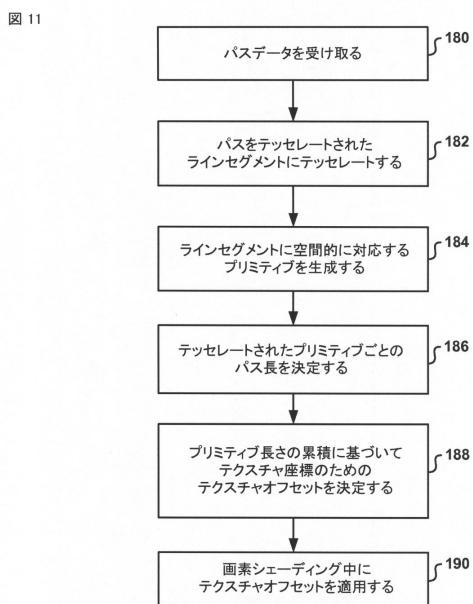

[0174]図11は、本開示による、ストローク動作を実行するための例示的な技法を示す流れ図である。この場合も、説明のためにGPU12によって実行されるものとして説明したが、図11に示される技法が、様々な他のプロセッサによって実行され得ることを理解されたい。さらに、本技法を実行するために、図示されるステップよりも少ないステップ、それに追加のステップ、またはそれとは異なるステップが使用され得る。

10

【0183】

[0175]GPU12は、パスデータを受け取る(180)。パスデータは、レンダリングされることになるパスの1つまたは複数のパスセグメントを示し得る。GPU12は、パスデータによって定義されたパスセグメントを複数のラインセグメントにテッセレートする(182)。たとえば、GPU12は、図9Aに示されるラインストリップなどのラインストリップにパスデータをテッセレートすることができる。

【0184】

[0176]GPU12は、パスセグメントに関するストローク領域に空間的に対応する複数のプリミティブを生成する(184)。たとえば、複数のテッセレートされたラインセグメントの各々について、GPU12は、それぞれのラインセグメントのためのストローク領域に空間的に対応する1つまたは複数のプリミティブを生成することができる。GPU12は、ラインセグメントのジオメトリシェーディング中にラインセグメントごとのテッセレートされたプリミティブの数を決定することができる。すなわち、ジオメトリシェーディング中に、GPU12は、(たとえば、ストロークの特定のセグメントをシェーディングすることなしに)「ダッシングなしの」ストロークを生成することができる。

20

【0185】

[0177]ダッシュするとき、GPU12は、テッセレートされたプリミティブごとのパス長を決定する(186)。たとえば、GPU12は、ジオメトリシェーディング中に生成された各ダッシュセグメント(プリミティブ)のための長さの累積を決定することができる。すなわち、ダッシュセグメントは、特定の順序(たとえば、テッセレーションおよび/またはジオメトリシェーディング中に決定された順序)で順序付けられ得る。プリミティブごとに、GPU12は、順序でそれに先行するプリミティブの長さを累積することができる。

30

【0186】

[0178]GPU12は、長さの累積に基づいてレンダリングされている各プリミティブのテクスチャ座標のためのテクスチャオフセットを決定することができる(188)。たとえば、上記のように、GPU12は、プリミティブの各々の始端のテクスチャ座標を決定するために長さ情報を使用することができる。GPU12は、画素シェーディング中にテクスチャオフセットを適用することができる(190)。たとえば、GPU12は、テクスチャオフセットを適用し、ストロークされたパスデータのための適切な色を使用してダ

40

50

ツシューのセグメントの各々をシェーディングする。

【0187】

[0179]いくつかの例では、本開示の技法により、Direct X 11ハードウェアのユーザは、Direct X 11ハードウェアを使用するか、または同様のパフォーマンス特性を有するハードウェアを用いてパスレンダリングを実行することが可能になり得る。さらなる例では、本開示の技法は、パスレンダリングに全GPUのレンダリングソリューションを与えることができる。

【0188】

[0180]本開示の技法について、主に、DX 11グラフィックスAPIによって定義されたハードウェアアーキテクチャに関して説明してきたが、本開示の技法はまた、たとえば、OpenGLグラフィックスAPI（たとえば、OpenGLバージョン4.0、4.1、4.2、4.3および以降のバージョン）など、他のオンチップのテッセレーション対応グラフィックスAPIに従って定義されたハードウェアアーキテクチャで実行され得る。本開示の技法が、OpenGLグラフィックスAPIに従って定義されたハードウェアアーキテクチャで実装される例では、本開示におけるハルシェーダ48に帰属する機能のうちの1つまたは複数は、テッセレーション制御シェーダによって実行され得、および/または本開示におけるドメインシェーダ52に帰属する機能のうちの1つまたは複数は、テッセレーション評価シェーダによって実行され得る。

【0189】

[0181]本開示で説明する技法は、少なくとも部分的に、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装され得る。たとえば、説明した技法の様々な態様は、1つもしくは複数のマイクロプロセッサ、デジタル信号プロセッサ（DSP）、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、あるいは任意の他の等価な集積回路またはディスクリート論理回路を含む、1つもしくは複数のプロセッサ内、ならびにそのような構成要素の任意の組合せ内で実装され得る。「プロセッサ」または「処理回路」という用語は、一般に、単独で、あるいは他の論理回路または、処理を実行する個別ハードウェアなどの他の等価回路との組合せで上記の論理回路のいずれかを指すことがある。

【0190】