(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4209108号

(P4209108)

(45) 発行日 平成21年1月14日(2009.1.14)

(24) 登録日 平成20年10月31日(2008.10.31)

(51) Int.Cl.

F 1

|                   |                  |            |       |

|-------------------|------------------|------------|-------|

| <b>G06F 3/06</b>  | <b>(2006.01)</b> | G06F 3/06  | 304 E |

| <b>G06F 12/16</b> | <b>(2006.01)</b> | G06F 3/06  | 540   |

| <b>G06F 13/10</b> | <b>(2006.01)</b> | G06F 12/16 | 310 J |

|                   |                  | G06F 13/10 | 340 B |

請求項の数 14 (全 11 頁)

(21) 出願番号

特願2001-388162 (P2001-388162)

(22) 出願日

平成13年12月20日 (2001.12.20)

(65) 公開番号

特開2003-186626 (P2003-186626A)

(43) 公開日

平成15年7月4日 (2003.7.4)

審査請求日

平成16年7月20日 (2004.7.20)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 110000176

一色国際特許業務法人

(74) 代理人 100094042

弁理士 鈴木 知

(72) 発明者 平野 正人

神奈川県小田原市中里322番地2号 株式会社日立製作所R A I Dシステム事業部内

(72) 発明者 中野 明良

神奈川県小田原市中里322番地2号 株式会社日立製作所R A I Dシステム事業部内

最終頁に続く

(54) 【発明の名称】記憶装置の制御方法およびこの方法に用いる記憶装置、ディスクアレイ装置、及びディスクコントローラ

## (57) 【特許請求の範囲】

## 【請求項 1】

上位装置に接続し、キャッシングメモリとこのキャッシングメモリを制御するデータコントローラと複数の記憶デバイスとの記憶デバイスを制御するデバイスコントローラとを含んで構成される記憶装置の制御方法であって、

記憶装置が、前記上位装置から送られてくる、データと記憶デバイスへの前記データの書き込み要求とを受信して、

前記データコントローラが、1つの前記キャッシングメモリ上の二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシングメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記デバイスコントローラに転送し、

前記デバイスコントローラが、前記受け取った各データを、前記各領域のそれぞれに対応する前記記憶デバイスに書き込むこと、

を特徴とする記憶装置の制御方法。

## 【請求項 2】

上位装置に接続し、キャッシングメモリとこのキャッシングメモリを制御するデータコントローラと複数のディスクドライブとのディスクドライブを制御するドライブコントローラとを含んで構成されるディスクアレイ装置の制御方法であって、

前記ディスクアレイ装置が、前記上位装置から送られてくる、データと前記ディスクドライブへの前記データの書き込み要求とを受信して、

10

20

前記データコントローラが、1つの前記キャッシュメモリ上の二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記ドライブコントローラに転送し、

前記ドライブコントローラが、前記受け取った各データを、前記各領域のそれに対応する前記ディスクドライブに書き込むこと、

を特徴とするディスクアレイ装置の制御方法。

#### 【請求項3】

前記ディスクアレイ装置が、前記上位装置から送られてくる前記キャッシュメモリ上の領域を指定する領域指定情報を受信して、

10

前記データコントローラが、前記領域指定情報に基づいて特定される前記キャッシュメモリ上の前記二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記ドライブコントローラに転送し、

前記ドライブコントローラが、前記受け取った各データを、前記各領域のそれに対応する前記ディスクドライブに書き込むこと、

を特徴とする請求項2に記載のディスクアレイ装置の制御方法。

#### 【請求項4】

上位装置に接続し、キャッシュメモリと、このキャッシュメモリを制御するデータコントローラと、このデータコントローラを制御する上位コントローラと、複数のディスクドライブと、このディスクドライブを制御するドライブコントローラとを含んで構成されるディスクアレイ装置の制御方法であって、

20

前記ディスクアレイ装置が、上位装置から送られてくる、データと前記ディスクドライブへの前記データの書き込み要求とを受信して、

前記上位コントローラが、前記キャッシュメモリ上の領域を指定する領域指定情報を前記データコントローラに送出して、

前記データコントローラが、前記領域指定情報に基づいて特定される、1つの前記キャッシュメモリ上の二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記ドライブコントローラに転送し、

30

前記ドライブコントローラが、前記受け取った各データを、前記各領域のそれに対応する前記ディスクドライブに書き込むこと、

を特徴とするディスクアレイ装置の制御方法。

#### 【請求項5】

前記領域指定情報が、前記キャッシュメモリ上の領域を指定するアドレスを少なくとも一つ含むことを特徴とする請求項3または4に記載のディスクアレイ装置の制御方法。

#### 【請求項6】

前記領域指定情報が、前記キャッシュメモリ上の領域を指定する第2の領域指定情報を格納している前記キャッシュメモリ上の領域を指定するポインタを、少なくとも一つ含むことを特徴とする請求項3から5のいずれかに記載のディスクアレイ装置の制御方法。

40

#### 【請求項7】

上位装置に接続し、キャッシュメモリと、このキャッシュメモリを制御するデータコントローラと、複数のディスクドライブと、このディスクドライブを制御するドライブコントローラとを含んで構成されるディスクアレイ装置の制御方法であって、

前記ディスクアレイ装置が、前記上位装置から送られてくる、データと前記ディスクドライブへの前記データの書き込み要求とを受信して、

前記データコントローラが、前記キャッシュメモリ上のアドレスと、このアドレスに基づいて算出される別のアドレスとによって指定される、1つの前記キャッシュメモリ上の二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記

50

データをそれぞれ読み出して前記ドライブコントローラに転送し、

前記ドライブコントローラが、前記受け取った各データを、前記各領域のそれに対応する前記ディスクドライブに書き込むこと、

を特徴とするディスクアレイ装置の制御方法。

**【請求項 8】**

前記ディスクアレイ装置が、前記キャッシュメモリ上の領域を指定するアドレスを少なくとも一つ含む領域指定情報を、前記上位装置から受信して、

前記データコントローラが、前記アドレスに基づいて、別のアドレスを算出し、これらのアドレスにより指定される前記キャッシュメモリ上の前記二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記ドライブコントローラに転送し、

前記ドライブコントローラが、前記受け取った各データを、前記各領域のそれに対応する前記ディスクドライブに書き込むこと、

を特徴とする請求項 7 に記載のディスクアレイ装置の制御方法。

**【請求項 9】**

上位装置に接続し、キャッシュメモリと、このキャッシュメモリを制御するデータコントローラと、このデータコントローラを制御する上位コントローラと、複数のディスクドライブと、このディスクドライブを制御するドライブコントローラとを含んで構成されるディスクアレイ装置の制御方法であって、

前記ディスクアレイ装置が、前記上位装置から送られてくる、データと前記ディスクドライブへの前記データの書き込み要求とを受信して、

前記上位コントローラが、前記キャッシュメモリ上の領域を指定するアドレスを少なくとも一つ含む領域指定情報を前記データコントローラに送出して、

前記データコントローラが、前記アドレスに基づいて、別のアドレスを算出し、これらのアドレスにより指定される、1つの前記キャッシュメモリ上の二つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記ドライブコントローラに転送し、

前記ドライブコントローラが、前記受け取った各データを、前記各領域のそれに対応する前記ディスクドライブに書き込むこと、

を特徴とするディスクアレイ装置の制御方法。

**【請求項 10】**

前記データコントローラが、前記アドレスに基づいて別のアドレスを算出する処理は、前記アドレスに前記データのデータ長を加算して別のアドレスを算出するか、前記アドレスを整数倍して別のアドレスを算出するか、前記アドレスにあらかじめ決められた所定値を加算するか、のいずれかであることを特徴とする請求項 7 ~ 9 のいずれかに記載のディスクアレイ装置の制御方法。

**【請求項 11】**

上位装置に接続し、

キャッシュメモリと、前記キャッシュメモリ上の二つの領域にデータを二重化して同時に直接書き込む手段を備えたデータコントローラと、複数の記憶デバイスと、

上位装置から送られてくる、データおよび前記記憶デバイスへの書き込み要求を受信する手段と、

前記キャッシュメモリ上の前記各領域に書き込まれた前記各データを前記記憶デバイスに書き込む手段と、

を備えることを特徴とする記憶装置。

**【請求項 12】**

上位装置に接続し、

キャッシュメモリと、1つの前記キャッシュメモリ上の二つの領域にデータを二重化し

10

20

30

40

50

て同時に直接書き込む手段を備えたデータコントローラと、複数のディスクドライブと、上位装置から送られてくる、データおよび前記ディスクドライブへの書き込み要求を受信する手段と、

前記キャッシュメモリ上の前記各領域に書き込まれた前記各データを前記ディスクドライブに書き込む手段と、

を備えることを特徴とするディスクアレイ装置。

**【請求項 1 3】**

上位装置と複数のディスクドライブに接続し、

キャッシュメモリと、1つの前記キャッシュメモリ上の二つの領域にデータを二重化して同時に直接書き込む手段を備えたデータコントローラと、

上位装置から送られてくるデータおよび前記ディスクドライブへの書き込み要求を受信する手段と、

前記キャッシュメモリ上の前記各領域に書き込まれた前記各データを前記ディスクドライブに書き込む手段と、

を備えることを特徴とするディスクコントローラ。

**【請求項 1 4】**

ホストコンピュータなどの上位装置に接続し、

マイクロプロセッサと、

キャッシュメモリと、

前記キャッシュメモリとキャッシュバスにより接続され、このキャッシュメモリを制御するデータコントローラと、

前記データコントローラとPCIバスにより接続され、前記上位装置や前記データコントローラとの間でデータの入出力制御を行う上位コントローラと、

複数のディスクドライブと、

前記データコントローラとPCIバスにより接続され、このディスクドライブを制御するドライブコントローラと、

を含んで構成されるディスクアレイ装置の制御方法であって、

前記上位コントローラが、前記上位装置から送られてくる、データと前記ディスクドライブへの前記データの書き込み要求とを受信して、

前記上位コントローラが、前記マイクロプロセッサに対して割り込み報告を行い、

前記マイクロプロセッサが、前記上位コントローラに対して、前記データと、このデータが書き込まれる、1つの前記キャッシュメモリ上の2つの領域に対応する領域指定情報と、を前記データコントローラに転送する指示、及び前記領域指定情報を送信し、

前記上位コントローラが、前記キャッシュメモリ上の領域を指定する領域指定情報を前記データコントローラに送出して、

前記データコントローラが、前記領域指定情報に基づいて特定される前記キャッシュメモリ上の前記2つの領域に前記データを二重化して同時に直接書き込み、

前記データコントローラが、前記2つの領域にそれぞれ書き込まれている前記データを読み出して前記ドライブコントローラに転送し、

前記ドライブコントローラが、前記キャッシュメモリ上の各領域に書き込まれた前記データを、前記各領域のそれぞれに対応する前記ディスクドライブに書き込むこと、

を特徴とするディスクアレイ装置の制御方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、記憶装置の制御方法およびこの方法に用いる記憶装置、ディスクアレイ装置、およびディスクコントローラに関する。

**【0002】**

**【従来の技術】**

ディスクアレイ装置などの記憶装置におけるデータセキュリティを確保する技術として、

10

20

30

40

50

例えば、R A I D 1 ( redundant array of inexpensive disks ) に代表されるように、データを複数の記憶デバイス（例えば、ディスクドライブ）に多重化して管理する技術が知られている。また、記憶装置の稼働状態を維持したまま、バックグラウンドでバックアップを行うといった目的で、データの多重化管理が行われることもある。

#### 【 0 0 0 3 】

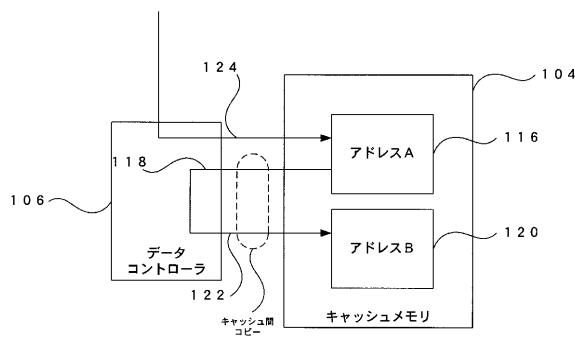

従来の記憶装置におけるこのようなデータの多重化管理において、複数の記憶デバイスにデータを書き込む際には、一旦、キャッシュメモリ上にデータを多重に書き込んでおいた後、ドライブコントローラなどのデバイスコントローラにより、それぞれのデータを対応する記憶デバイスに書き込む、といった仕組みが一般的である。

#### 【 0 0 0 4 】

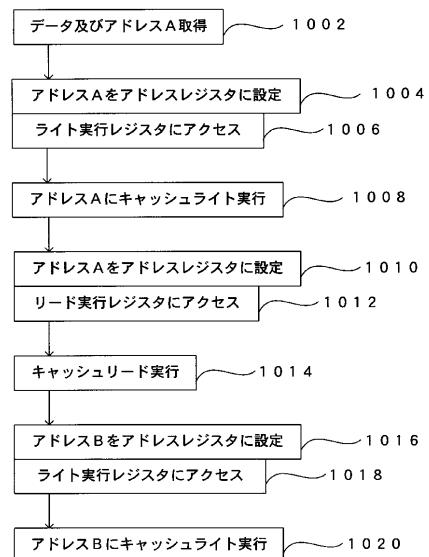

図9の概念ブロック図、図10のフローチャートは、前記の仕組みを具体的に説明したものである。すなわち、まず、データコントローラ106が、上位装置から、書き込み対象データとアドレスAとを取得し(S1002)、キャッシュメモリ104上のアドレスAで指定される領域116にデータを書き込む(S1004～S1008)。つぎに、データコントローラ106は、アドレスAで指定される領域に格納されているデータを読み出し(S1010～S1014)、読み出したデータをアドレスBで指定される領域120に書き込む(S1016～S1020)。

10

#### 【 0 0 0 5 】

**【発明が解決しようとする課題】**

ところで、図9に示しているように、この処理では、データコントローラ106とキャッシュメモリ104との間で、データの書き込み処理124、データの読み出し処理118、読み出したデータの書き込み処理122、という、計3回ものI/Oが発生する。そして、とくにこのうちのアドレスAからのアドレスBへのデータコピーに関連して必要となるデータの読み出し処理118により生じるI/Oは、データコントローラ106とキャッシュメモリ104との間のバス効率を低下させ、記憶装置自体の処理時間を増大させる要因ともなりうる。

20

#### 【 0 0 0 6 】

本発明は、このような課題に着目してなされたもので、データを多重化して管理する場合に、記憶デバイスへのデータの書き込み処理を効率よく行うことができる、記憶装置の制御方法およびこの方法に用いる記憶装置、ディスクアレイ装置、およびディスクコントローラを提供することを目的とする。

30

#### 【 0 0 0 7 】

##### 【課題を解決するための手段】

上記目的を達成するための本発明のディスク装置の制御方法は、上位装置に接続し、キャッシュメモリとこのキャッシュメモリを制御するデータコントローラと複数の記憶デバイスとこの記憶デバイスを制御するデバイスコントローラとを含んで構成される記憶装置の制御方法であって、記憶装置が、前記上位装置から送られてくる、データと記憶デバイスへの前記データの書き込み要求とを受信して、前記データコントローラが、1つの前記キャッシュメモリ上の二つの領域に前記データを二重化して同時に直接書き込み、前記データコントローラが、前記キャッシュメモリ上の前記各領域に書き込まれた前記データをそれぞれ読み出して前記デバイスコントローラに転送し、前記デバイスコントローラが、前記受け取った各データを、前記各領域のそれぞれに対応する前記記憶デバイスに書き込むことを特徴とする。

40

#### 【 0 0 0 8 】

##### 【発明の実施の形態】

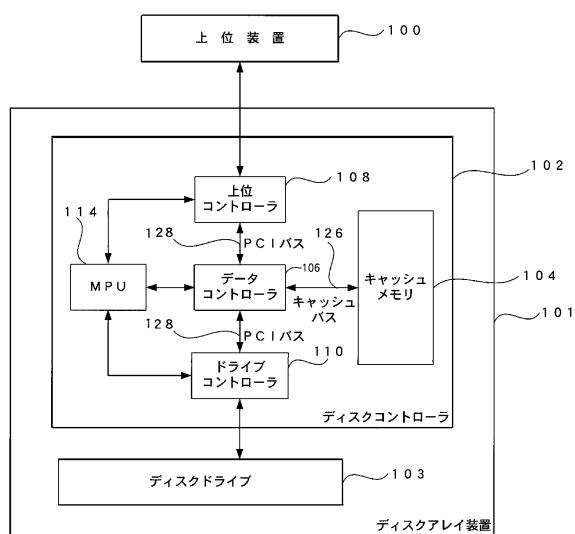

図1に、本発明による制御方法の一実施例に用いられるディスクアレイ装置101の構成を示す。ディスクアレイ装置101は、ホストコンピュータなどの上位装置100に接続し、ディスクコントローラ102と、このディスクコントローラ102によって制御される複数台のディスクドライブ103とを備える。また、ディスクコントローラ102は、マイクロプロセッサ(MPU)114、キャッシュメモリ104、このキャッシュメモリ

50

104を制御するデータコントローラ106、上位装置100やデータコントローラ106との間でのデータの入出力制御などを行う上位コントローラ108、各ディスクドライブ103を制御するドライブコントローラ110などを備える。データコントローラ106は、PCIバス128などにより、上位コントローラ108およびドライブコントローラ110に接続している。

#### 【0009】

以下、本発明の一実施例として、以上の構成のディスクアレイ装置101において、上位装置100から送られてくるデータが、ディスクドライブ103に書き込まれるまでの処理について詳述する。

#### 【0010】

10

##### <実施例1>

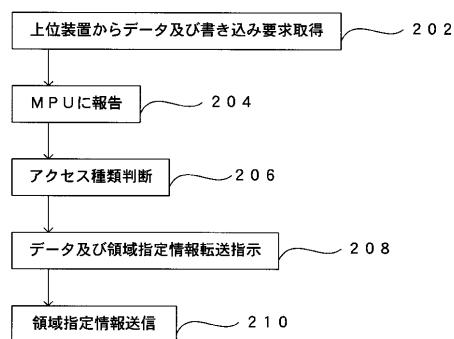

図2は、上位装置100から送信されてきた書き込み対象データが、データコントローラ106に送信されるまでのディスクアレイ装置101における処理を説明するフローチャートである。上位コントローラ108は、上位装置100から書き込み対象データとその書き込み要求とを受信すると(S202)、MPU114に対して割り込み報告を行う(S204)。MPU114は、割り込み信号をデコードしてアクセスの種類を判断し(S206)、上位コントローラ108に対して、書き込み対象データとこのデータが書き込まれるキャッシュメモリ104上の二つの領域に対応する領域指定情報をデータコントローラ106に転送する指示を送出し(S208)、前記領域指定情報を送信する(S210)。

#### 【0011】

20

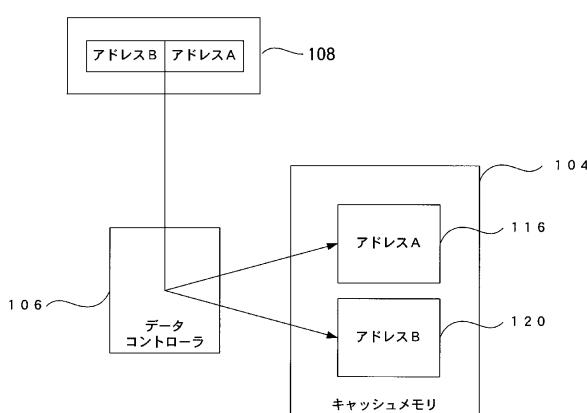

実施例1においては、この領域指定情報として、キャッシュメモリ104上の二つの領域を指定するアドレスを用いている。図3に、その場合のデータコントローラ106による書き込み処理の概念ブロック図を、図4に、データコントローラ106に送信されたデータが、キャッシュメモリ104上の所定の位置に書き込まれるまでのディスクアレイ装置101における処理を説明するフローチャートを示す。

#### 【0012】

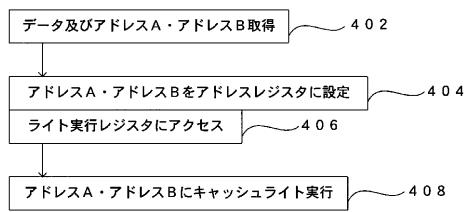

データコントローラ106は、MPU114からの指示により上位コントローラ108から送信されたアドレスAおよびアドレスBを取得する(S402)。データコントローラ106は、上位コントローラ108から送られてきたアドレスAおよびアドレスBを、アドレスレジスタ(図示しない)に設定し(S404)、ライト実行レジスタ(図示しない)にアクセスし(S406)、キャッシュメモリ104上の前記アドレスに対応する領域116, 120に、前記書き込み対象データを書き込む(S408)。そして、書き込みが終了した後、上位コントローラ108は、MPU114にデータ転送終了を報告し、キャッシュメモリ104へのデータの書き込み処理が完了する。

30

#### 【0013】

そして、このようにしてキャッシュメモリ104に二重に書き込まれたデータは、さらにつぎの手順を経て、それぞれ対応するディスクドライブ(記憶デバイス)に書き込まれる。

#### 【0014】

40

すなわち、まず、データコントローラ106は、アドレスAおよびアドレスBをアドレスレジスタに設定して、リード実行レジスタ(図示しない)にアクセスする。つぎに、データコントローラ106は、キャッシュメモリ104上のアドレスAおよびアドレスBで指定される領域に書き込まれているデータを読み出し、読み出したそれぞれのデータを、ドライブコントローラ110に転送する。データを受け取ったドライブコントローラ110は、各々のアドレスに対応するディスクドライブ103にデータを書き込む。ここで各アドレスとディスクドライブ103との対応づけの管理は、例えば、ディスクコントローラ102に実装されている制御メモリに前記対応づけを記載した管理テーブルを用意したり、MPUに対応づけを導出するアルゴリズムを実行させるといった方法で行う。

#### 【0015】

ところで、以上に説明した仕組みにおいては、データをキャッシュメモリ104上で二

50

重化する際に、データコントローラ 106 がキャッシュメモリ 104 上の二つの領域に同時にデータを書き込むようにしている。このため、従来のように、アドレス A からのアドレス B へのデータコピーに関連して必要となるデータの読み出し処理 118 が必要でなく、書き込み対象データを効率よくキャッシュメモリ 104 に書き込むことができる。

#### 【0016】

<実施例 2 >

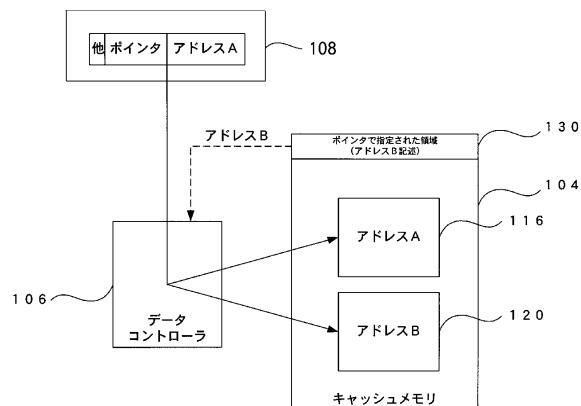

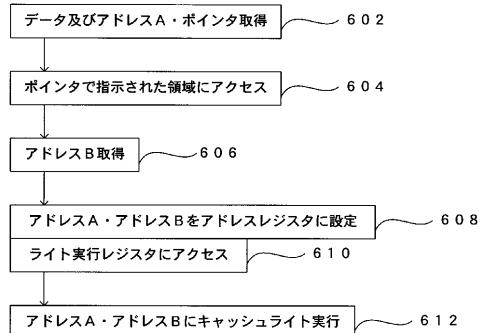

ここで説明する実施例は、データコントローラ 106 が、前記領域指定情報として、その全部または一部をポインタにより受領し、このポインタで指定される領域 130 に格納されているアドレス B をキャッシュメモリ 104 から読み出すことで、データコントローラ 106 が前記書込対象データが書き込まれるキャッシュメモリ 104 上の領域を認知する 10 ようにしたものである。以下、図 5 の概念ブロック図、図 6 のフローチャートとともにこの仕組みを説明する。

#### 【0017】

まず、データコントローラ 106 が、上位コントローラ 108 から送信されてくるアドレス A およびポインタを取得する(S602)。データコントローラ 106 は、送られてきたポインタ値に従い、指定されたキャッシュメモリ 104 上の領域 130 にアクセスし(S604)、そこに格納されているアドレス B を取得する(S606)。つぎに、データコントローラ 106 は、アドレス A と、ポインタによって得られたアドレス B とをアドレスレジスタに設定して(S608)、ライト実行レジスタにアクセスし(S610)、前記アドレスに対応するキャッシュメモリ 104 上の領域 116, 120 にデータを書き込む(S612)。そして、書き込みが終了した後、上位コントローラ 108 は、MPU 114 にデータ転送終了を報告し、キャッシュメモリ 104 へのデータの書き込み処理が完了する。なお、キャッシュメモリ 104 上のデータがディスクドライブ 103 に書き込まれるまでの処理は、実施例 1 と同様であるので、ここでは説明を省略する。 20

#### 【0018】

ところで、以上は二重に書き込まれる一方の領域指定情報のみがポインタで指定される場合についての説明であったが、双方ともポインタで指定される構成としてもよい。

#### 【0019】

<実施例 3 >

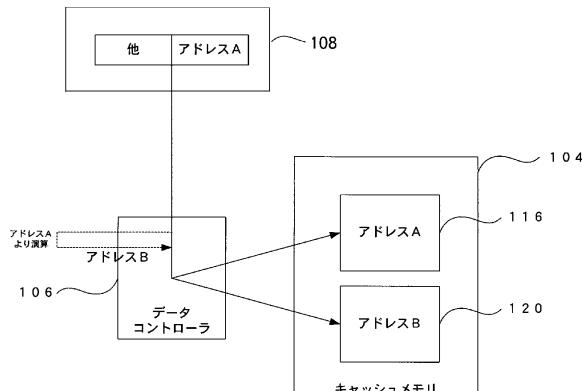

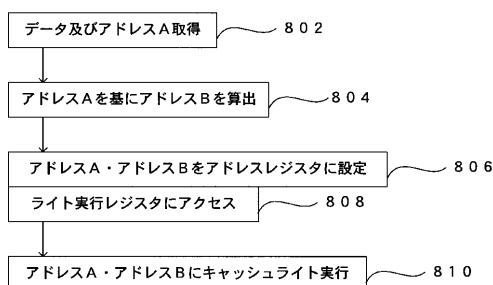

つぎに説明する実施例は、前記領域指定情報として、データコントローラ 106 が書き込み対象データが二重に書き込まれる一方のアドレスのみを上位装置 100 から受領し、受領した前記アドレスに所定のアルゴリズムを適用することでもう一方のアドレス B を決定するようにしたものである。以下、図 7 の概念ブロック図、図 8 のフローチャートとともにこの仕組みを説明する。 30

#### 【0020】

まず、データコントローラ 106 は、MPU 114 からの指示により上位コントローラ 108 から送信されたアドレス A を取得する(S802)。つぎに、データコントローラ 106 は、このアドレス A に所定のアルゴリズムを適用し、もう一方のアドレス B を決定する(S804)。 40

#### 【0021】

ここで所定のアルゴリズムとしては、例えば、アドレス A に書き込み対象データのデータ長を加算したものをアドレス B とする、アドレス A を整数倍したものをアドレス B とする、アドレス A にあらかじめ決められた所定値を加算する、といったようなものがあげられる。

#### 【0022】

そして、データコントローラ 106 は、送られてきたアドレス A と、これに基づいて決定されたアドレス B とをアドレスレジスタに設定し(S806)、ライト実行レジスタにアクセスし(S808)、キャッシュメモリ 104 上の前記アドレス A およびアドレス B に対応する領域 116, 120 にデータを書き込む(S810)。そして、書き込み終了後、上位コントローラ 108 は、MPU 114 にデータ転送終了を報告し、キャッシュメモリ 104 へのデータ 50

の書き込み処理が完了する。なお、キャッシュメモリ104上のデータがディスクドライブ103に書き込まれるまでの処理は、実施例1と同様であるので、ここでは説明を省略する。

#### 【0023】

ところで、以上に述べた実施例1乃至3においては、ディスクコントローラ102内に上位コントローラ108を設けているが、上位装置100が直接データをデータコントローラ106に送る構成であってもよい。また、上位装置100がキャッシュメモリ104上のデータ書き込み位置を決定する構成でもよい。

#### 【0024】

また、上位コントローラ108が上位装置100やMPU114から得た領域指定情報に基づいてキャッシュメモリ104上の領域を特定し、そのアドレスをデータコントローラ106に送るようにしてもよい。

10

#### 【0025】

また、以上に説明した実施例では、ディスクコントローラ102内において、MPU114が独立する構成としているが、上位コントローラ108やデータコントローラ106の機能をMPU114に実行させてもよい。

#### 【0026】

#### 【発明の効果】

本発明の記憶装置の制御方法およびこの方法に用いる記憶装置、ディスクアレイ装置、およびディスクコントローラにあっては、データを多重化して管理する場合に、記憶デバイスへのデータの書き込み処理を効率よく行うことができる。

20

#### 【図面の簡単な説明】

【図1】本発明の一実施例による、ハードウェアの全体構成を示す図である。

【図2】本発明の一実施例による、上位装置から送信されたデータがデータコントローラに送信されるまでの処理を説明するフローチャートを示す図である。

【図3】本発明の一実施例による、データコントローラに送信されたデータがキャッシュメモリ上に書き込まれるまでの処理を説明する概念ブロック図である。

【図4】本発明の一実施例による、データコントローラに送信されたデータがキャッシュメモリ上の所定の位置に書き込まれるまでの処理を説明するフローチャートを示す図である。

30

【図5】本発明の一実施例による、データコントローラに送信されたデータがキャッシュメモリ上に書き込まれるまでの処理を説明する概念ブロック図である。

【図6】本発明の一実施例による、データコントローラに送信されたデータがキャッシュメモリ上に書き込まれるまでの処理を説明するフローチャートを示す図である。

【図7】本発明の一実施例による、データコントローラに送信されたデータがキャッシュメモリ上に書き込まれるまでの処理を説明する概念ブロック図である。

【図8】本発明の一実施例による、データコントローラに送信されたデータがキャッシュメモリ上に書き込まれるまでの処理を説明するフローチャートである。

【図9】従来の記憶装置における、キャッシュメモリにデータを二重に書き込む際の処理を説明する概念ブロック図である。

40

【図10】従来の記憶装置における、キャッシュメモリにデータを二重に書き込む際の処理を説明するフローチャートである。

#### 【符号の説明】

100 上位装置

101 ディスクアレイ装置

102 ディスクコントローラ

103 ディスクドライブ

104 キャッシュメモリ

106 データコントローラ

110 ドライブコントローラ

50

## 128 PCIバス

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 八木沢 育哉

神奈川県川崎市麻生区王禅寺1099番地 株式会社日立製作所システム開発研究所内

審査官 木村 雅也

(56)参考文献 特開平08-036542(JP,A)

特開2001-175582(JP,A)

特開2001-273245(JP,A)

特開平08-263432(JP,A)

特開2001-166993(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 3/06

G06F 12/16

G06F 13/10