(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4281237号

(P4281237)

(45) 発行日 平成21年6月17日(2009.6.17)

(24) 登録日 平成21年3月27日(2009.3.27)

(51) Int.Cl.

F 1

|         |       |           |

|---------|-------|-----------|

| B 4 1 J | 2/44  | (2006.01) |

| B 4 1 J | 2/45  | (2006.01) |

| B 4 1 J | 2/455 | (2006.01) |

| H 0 1 L | 33/00 | (2006.01) |

|         |       |

|---------|-------|

| B 4 1 J | 3/21  |

| H 0 1 L | 33/00 |

|   |

|---|

| L |

| J |

請求項の数 11 (全 23 頁)

(21) 出願番号

特願2000-295553 (P2000-295553)

(22) 出願日

平成12年9月28日 (2000.9.28)

(65) 公開番号

特開2002-111063 (P2002-111063A)

(43) 公開日

平成14年4月12日 (2002.4.12)

審査請求日

平成18年6月23日 (2006.6.23)

(73) 特許権者 000005496

富士ゼロックス株式会社

東京都港区赤坂九丁目7番3号

(74) 代理人 100104880

弁理士 古部 次郎

(74) 代理人 100118201

弁理士 千田 武

(72) 発明者 大野 誠治

大阪府大阪市中央区道修町3丁目5番11

号 日本板硝子株式会社内

審査官 尾崎 俊彦

最終頁に続く

(54) 【発明の名称】自己走査型発光素子アレイチップ

## (57) 【特許請求の範囲】

## 【請求項 1】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給する2本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれ

10

20

それに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第1の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給する2本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれぞれに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される1本の電源ラインと；

を備えることを特徴とする自己走査型発光素子アレイチップ。

#### 【請求項2】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれ

10

20

30

40

50

それに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第1の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路へ一方の相のクロックパルスをそれぞれ供給する、互いに接続された2本のクロックパルスラインと；

前記第1および第2の自己走査型発光素子アレイ回路へ他方の相のクロックパルスをそれぞれ供給する、互いに接続された2本のクロックパルスラインと；

前記第1および第2の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される1本の電源ラインと；

を備えることを特徴とする自己走査型発光素子アレイチップ。

### 【請求項3】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給する2本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極と、前記2相のクロックパルスラインのいずれか一方とを、当該ダイオードと直列接続されるようにダイオードを介して接続し、当該クロックパルスラインに与えられた一方のクロックパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた他方の相のクロックパルスにより、当該転送素子をオンさせ、

前記他方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素

10

20

30

40

50

子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、前記一方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれぞれに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第1の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給する2本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極と、前記2相のクロックパルスラインのいずれか一方とを、当該ダイオードと直列接続されるようにダイオードを介して接続し、当該クロックパルスラインに与えられた一方のクロックパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた他方の相のクロックパルスにより、当該転送素子をオンさせ、

前記他方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、前記一方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれぞれに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される1本の電源ラインと；

を備えることを特徴とする自己走査型発光素子アレイチップ。

#### 【請求項4】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該

10

20

30

40

50

転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれぞれに対応させて一次元的に配列し、

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、 10

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第1の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、 20

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子多数個を、前記転送素子のそれぞれに対応させて一次元的に配列し、 30

前記転送素子の各ゲート電極を、当該転送素子に対応する前記発光素子のゲート電極に接続し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を印加する1本の書き込み信号ラインを設けた第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路へ一方の相のクロックパルスを、第1の電流制限抵抗R1を介して、供給する1本の第1のクロックパルスラインと；

前記第1および第2の自己走査型発光素子アレイ回路へ他方の相のクロックパルスを、第2の電流制限抵抗R2を介して、供給する1本の第2のクロックパルスラインと； 40

前記各転送素子のアノード電極またはカソード電極の一方と、前記第1または第2のクロックパルスラインとの間に挿入された第3の抵抗RAと；

前記第1および第2の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される1本の電源ラインと；

を備え、

第1の電流制限抵抗R1および第2の電流制限抵抗R2のそれぞれを流れる電流jが、

$$2(V_{th} - V_D) / R_A > j > (V_{th} - V_D) / R_A$$

(ここで、V<sub>D</sub>はpn接合順方向電位、V<sub>th</sub>は転送素子のしきい電圧)

を満たす

ことを特徴とする自己走査型発光素子アレイチップ。

## 【請求項 5】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ 1 素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から 2 相のクロックパルスのいずれか一方を供給する 2 本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子発光素子を、前記転送素子のそれぞれに 2 個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ 1 素子おきに印加する 2 本の書き込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する 2 個の前記発光素子のゲート電極にそれぞれ接続した第 1 の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ 1 素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から 2 相のクロックパルスのいずれか一方を供給する 2 本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子発光素子を、前記転送素子のそれぞれに 2 個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ 1 素子おきに印加する 2 本の書き込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する 2 個の前記発光素子のゲート電極にそれぞれ接続した第 2 の自己走査型発光素子アレイ回路と；

前記第 1 および第 2 の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、それぞれ負荷抵抗を介して接続される 1 本の電源ラインと；

を備えることを特徴とする自己走査型発光素子アレイチップ。

10

20

30

40

50

## 【請求項 6】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子を、前記転送素子のそれぞれに2個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ1素子おきに印加する2本の書き込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する2個の前記発光素子のゲート電極にそれぞれ接続した第1の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子を、前記転送素子のそれぞれに2個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ1素子おきに印加する2本の書き込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する2個の前記発光素子のゲート電極にそれぞれ接続した第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路へ一方の相のクロックパルスをそれぞれ供給する、互いに接続された2本のクロックパルスラインと；

前記第1および第2の自己走査型発光素子アレイ回路へ他方の相のクロックパルスをそ

10

20

30

40

50

れぞれ供給する、互いに接続された 2 本のクロックパルスラインと；

前記第 1 および第 2 の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される 1 本の電源ラインと；

を備えることを特徴とする自己走査型発光素子アレイチップ。

【請求項 7】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ 1 素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から 2 相のクロックパルスのいずれか一方を供給する 2 本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極と、前記 2 相のクロックパルスラインのいずれか一方とを、当該ダイオードと直列接続されるようにダイオードを介して接続し、当該クロックパルスラインに与えられた一方のクロックパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた他方の相のクロックパルスにより、当該転送素子をオンさせ、

前記他方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、前記一方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子発光素子を、前記転送素子のそれぞれに 2 個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ 1 素子おきに印加する 2 本の書き込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する 2 個の前記発光素子のゲート電極にそれぞれ接続した第 1 の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ 1 素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から 2 相のクロックパルスのいずれか一方を供給する 2 本のクロックパルスラインを設け、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極と、前記 2 相のクロックパルスラインのいずれか一方とを、当該ダイオードと直列接続されるようにダイオードを介して接続し、当該クロックパルスラインに与えられた一方のクロックパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた他方の相のクロックパルスにより、当該転送素子をオンさせ、

前記他方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、前記一方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する 3 端子発光素子を、前記転送素子のそれぞれに

10

20

30

40

50

2個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ1素子おきに印加する2本の書き込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する2個の前記発光素子のゲート電極にそれぞれ接続した第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される1本の電源ラインと；

を備えることを特徴とする自己走査型発光素子アレイチップ。

【請求項8】

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、 10

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、 20

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子を、前記転送素子のそれぞれに2個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書き込み信号を、それぞれ1素子おきに印加する2本の書き込み信号ラインを設け、 30

前記転送素子の各ゲート電極を、当該転送素子に対応する2個の前記発光素子のゲート電極にそれぞれ接続した第1の自己走査型発光素子アレイ回路と；

しきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子転送素子多数個を、一次元的に配列し、

隣接する転送素子のしきい電圧もしくはしきい電流を制御するゲート電極を、電圧もしくは電流の一方向性をもつダイオードが直列に接続されるように、当該ダイオードをそれぞれ介在させて互いに接続し、

前記ダイオードにより互いに接続された各転送素子のそれぞれ1素子おきに、当該転送素子のアノード電極またはカソード電極のうちの一方に、外部から2相のクロックパルスのいずれか一方を供給し、 40

転送素子のオン状態が順次転送される上流側の端の転送素子のゲート電極に加えられたスタートパルスにより、当該転送素子のしきい電圧もしくはしきい電流を変化させ、当該転送素子に加えられた一方の相のクロックパルスにより、当該転送素子をオンさせ、

前記一方の相のクロックパルスにより、前記転送素子がオンしているとき、当該転送素子に前記ダイオードを介して接続され、当該ダイオードを介してしきい電圧もしくはしきい電流が変化した転送素子を、他方の相のクロックパルスによりオンさせ、

前記一方の相のクロックパルスと前記他方の相のクロックパルスとで、一次元的に配列された転送素子のオン状態を転送させるとともに、

発光のためのしきい電圧もしくはしきい電流が外部から電気的に制御可能な、ゲート電極、アノード電極、カソード電極を有する3端子発光素子を、前記転送素子のそれぞれに 50

2個対応させて一次元的に配列し、

前記各発光素子のアノード電極またはカソード電極の一方に発光のための書込み信号を、それぞれ1素子おきに印加する2本の書込み信号ラインを設け、

前記転送素子の各ゲート電極を、当該転送素子に対応する2個の前記発光素子のゲート電極にそれぞれ接続した第2の自己走査型発光素子アレイ回路と；

前記第1および第2の自己走査型発光素子アレイ回路へ一方の相のクロックパルスを、第1の電流制限抵抗R1を介して、供給する1本の第1のクロックパルスラインと；

前記第1および第2の自己走査型発光素子アレイ回路へ他方の相のクロックパルスを、第2の電流制限抵抗R2を介して、供給する1本の第2のクロックパルスラインと；

前記各転送素子のアノード電極またはカソード電極の一方と、前記第1または第2のクロックパルスラインとの間に挿入された第3の抵抗RAと；

前記第1および第2の自己走査型発光素子アレイ回路の転送素子の各ゲート電極が、負荷抵抗を介して接続される1本の電源ラインと；

を備え、

第1の電流制限抵抗R1および第2の電流制限抵抗R2のそれを流れる電流jが、

$$2(V_{th} - V_D) / R_A > j > (V_{th} - V_D) / R_A$$

(ここで、V<sub>D</sub>はpn接合順方向電位、V<sub>th</sub>は転送素子のしきい電圧)

を満たす

ことを特徴とする自己走査型発光素子アレイチップ。

#### 【請求項9】

前記転送素子および発光素子は、pnpn構造の発光サイリスタにより構成されることを特徴とする請求項1～8のいずれかに記載の自己走査型発光素子アレイチップ。

#### 【請求項10】

請求項9に記載の自己走査型発光素子アレイチップを有することを特徴とする光書込みヘッド。

#### 【請求項11】

請求項10に記載の光書込みヘッドを備えることを特徴とする光プリンタ。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、自己走査型発光素子アレイチップ、特に、発光用クロックラインを2分割することにより、1チップ上で2つの発光点を同時に点灯できるようにした自己走査型発光素子アレイチップに関する。

##### 【0002】

##### 【従来の技術】

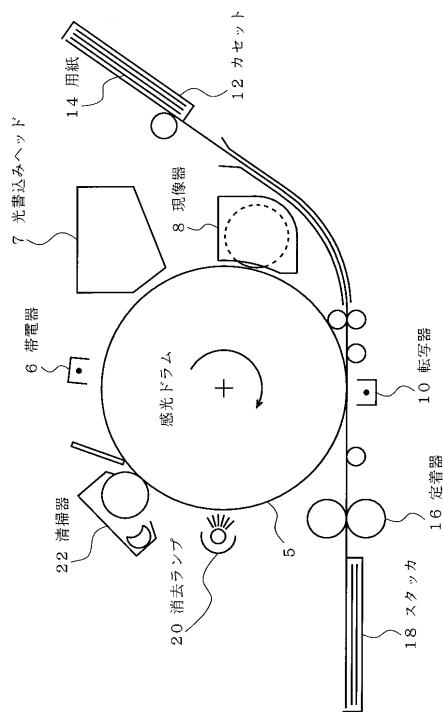

光プリンタの書込みヘッド（光書込みヘッド）は、感光ドラムに光を露光させるための光源であり、発光素子アレイを有している。光書込みヘッドを備える光プリンタの原理図を図1に示す。円筒形の感光ドラム5の表面に、アモルファスSi等の光導電性を持つ材料（感光体）が作られている。このドラムはプリントの速度で回転している。回転しているドラムの感光体表面を、帯電器6で一様に帯電させる。そして、光書込みヘッド7で、印字するドットイメージの光を感光体上に照射し、光の当たったところの帯電を中和し、潜像を形成する。続いて、現像器8で感光体上の帯電状態にしたがって、トナーを感光体上につける。そして、転写器10でカセット12中から送られてきた用紙14上に、トナーを転写する。用紙は、定着器16にて熱等を加えられ定着され、スタッカ18に送られる。一方、転写の終了したドラムは、消去ランプ20で帯電が全面にわたって中和され、清掃器22で残ったトナーが除去される。

##### 【0003】

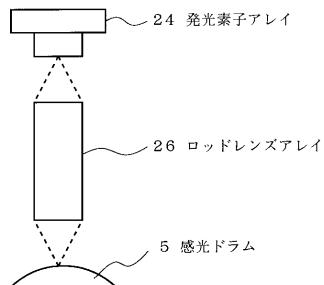

光書込みヘッド7の構造を図2に示す。光書込みヘッドは発光素子アレイ24と正立等倍光学系、例えばロッドレンズアレイ26で構成され、レンズの焦点が感光ドラム5上に結ぶようになっている。

10

20

30

40

50

## 【0004】

本発明者らは、自己走査型の発光素子アレイの構成要素として、p n p n構造を持つ3端子発光サイリスタに注目し、既に特許出願（特開平1-238962号公報、特開平2-14584号公報、特開平2-92650号公報、特開平2-92651号公報）し、光プリンタ用光源として実装上簡便となること、発光素子ピッチを細かくできること、コンパクトな自己走査型発光素子アレイを作製できること等を示した。

## 【0005】

さらに本発明者らは、転送素子アレイをシフト部として、発光部である発光素子アレイと分離した構造の自己走査型発光素子アレイを提案している（特開平2-263668号公報）。 10

## 【0006】

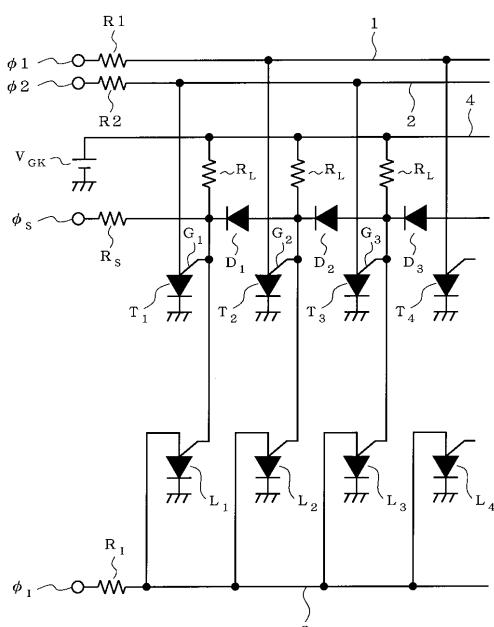

図3に、シフト部と発光部とを分離した構造の自己走査型発光素子アレイチップの等価回路図を示す。シフト部は、転送素子T<sub>1</sub>，T<sub>2</sub>，T<sub>3</sub>，…を有し、発光部は、書き込み用発光素子L<sub>1</sub>，L<sub>2</sub>，L<sub>3</sub>，…を有している。これら転送素子および発光素子は、3端子発光サイリスタにより構成される。シフト部の構成は、転送素子のゲートを互いに電気的に接続するのにダイオードD<sub>1</sub>，D<sub>2</sub>，D<sub>3</sub>，…を用いている。V<sub>GK</sub>は電源（通常5V）であり、負荷抵抗R<sub>L</sub>を経て各転送素子のゲート電極G<sub>1</sub>，G<sub>2</sub>，G<sub>3</sub>，…に接続されている。また、転送素子のゲート電極G<sub>1</sub>，G<sub>2</sub>，G<sub>3</sub>，…は、書き込み用発光素子のゲート電極にも接続される。転送素子T<sub>1</sub>のゲート電極にはスタートパルス<sub>s</sub>が加えられ、転送素子のアノード電極には、交互に転送用クロックパルス<sub>1</sub>，<sub>2</sub>が加えられ、書き込み用発光素子のアノード電極には、書き込み信号<sub>1</sub>が加えられている。 20

## 【0007】

なお図中、1は1ライン、2は2ライン、3は1ライン、4は電源ラインを示し、R<sub>1</sub>，R<sub>2</sub>，R<sub>1</sub>は、1ライン、2ライン、1ラインに挿入された電流制限抵抗を示している。

## 【0008】

動作を簡単に説明する。まず転送用クロックパルス<sub>1</sub>の電圧が、Hレベルで、転送素子T<sub>2</sub>がオン状態であるとする。このとき、ゲート電極G<sub>2</sub>の電位はV<sub>GK</sub>の5Vからほぼ0Vにまで低下する。この電位降下の影響はダイオードD<sub>2</sub>によってゲート電極G<sub>3</sub>に伝えられ、その電位を約1Vに（ダイオードD<sub>2</sub>の順方向立上り電圧（拡散電位に等しい））に設定する。しかし、ダイオードD<sub>1</sub>は逆バイアス状態であるためゲート電極G<sub>1</sub>への電位の接続は行われず、ゲート電極G<sub>1</sub>の電位は5Vのままとなる。発光サイリスタのオン電圧は、ゲート電極電位+p<sub>n</sub>接合の拡散電位（約1V）で近似されるから、次の転送用クロックパルス<sub>2</sub>のHレベル電圧は約2V（転送素子T<sub>3</sub>をオンさせるために必要な電圧）以上でありかつ約4V（転送素子T<sub>5</sub>をオンさせるために必要な電圧）以下に設定しておけば転送素子T<sub>3</sub>のみがオンし、これ以外の転送素子はオフのままにすることができる。従って2本の転送用クロックパルスでオン状態が転送されることになる。 30

## 【0009】

スタートパルス<sub>s</sub>は、このような転送動作を開示させるためのパルスであり、スタートパルス<sub>s</sub>をLレベル（約0V）にすると同時に転送用クロックパルス<sub>2</sub>をHレベル（約2～約4V）とし、転送素子T<sub>1</sub>をオンさせる。その後すぐ、スタートパルス<sub>s</sub>はHレベルに戻される。 40

## 【0010】

いま、転送素子T<sub>2</sub>がオン状態にあるとすると、ゲート電極G<sub>2</sub>の電位は、ほぼ0Vとなる。したがって、書き込み信号<sub>1</sub>の電圧が、p<sub>n</sub>接合の拡散電位（約1V）以上であれば、発光素子L<sub>2</sub>を発光状態とすることができます。

## 【0011】

これに対し、ゲート電極G<sub>1</sub>は約5Vであり、ゲート電極G<sub>3</sub>は約1Vとなる。したがって、発光素子L<sub>1</sub>の書き込み電圧は約6V、発光素子L<sub>3</sub>の書き込み電圧は約2Vとなる。これから、発光素子L<sub>2</sub>のみに書きめる書き込み信号<sub>1</sub>の電圧は、1～2Vの範囲となる。 50

発光素子  $L_2$  がオン、すなわち発光状態に入ると、発光強度は書込み信号  $I_1$  に流す電流量で決められ、任意の強度にて画像書込みが可能となる。また、発光状態を次の発光素子に転送するためには、書込み信号  $I_1$  ラインの電圧を一度 0 V までおとし、発光している発光素子をいったんオフにしておく必要がある。

#### 【0012】

自己走査型発光素子アレイは、上述のような構成のチップを配列することにより作製される。自己走査型発光素子アレイチップの価格は、通常の集積回路同様、1 ウエファから取れる個数によって決まる。このため、チップの幅を細くした方が安価になる。

#### 【0013】

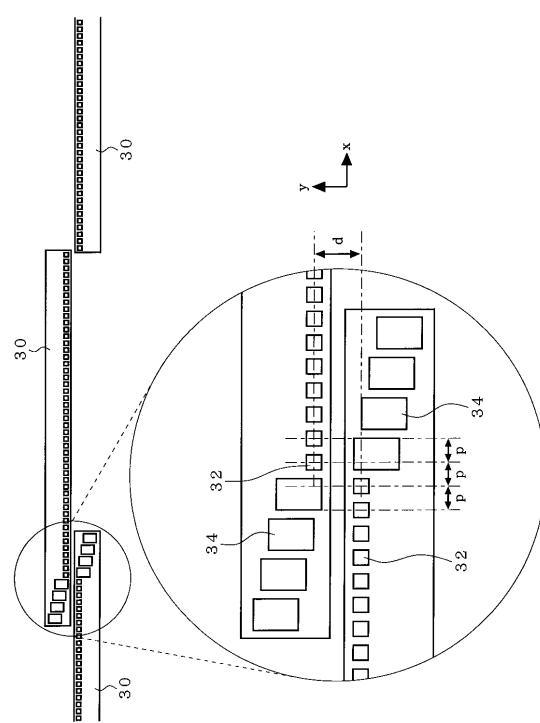

本出願人は、できる限り細幅のチップを実現する構成として、ボンディングパッドを両端（もしくは片端）に寄せたチップを千鳥状に配置することを提案している。ボンディングパッドを片端に寄せたチップを千鳥状に配置した様子を示す模式図を図 4 に示す。図 4 には、方向を示す x - y 軸を示す。10

#### 【0014】

自己走査型発光素子アレイチップ 30 を、発光点 32 が x 方向にピッチ P となるように配列し、y 方向のチップ間の距離 d を、y 方向解像度 r の整数倍にとる。なお図中、34 はボンディングパッドを示す。この発光点列の点 / 滅を、図 2 で示したように、ロッドレンズアレイを介して、感光ドラム上に投影して潜像を得る。ただし、このままでは、チップ間の発光点列は y 方向に距離 d だけ離れているので、d / r 本分だけ時間的にずれた画像のラインデータを使わなければならない。距離 d はある程度大きい方が、書込みヘッドの組立が容易であるが、距離 d が大きくなるにつれて、チップ間の光学系伝達効率や焦点位置のズレが大きくなるので、むやみと増やすことはできない。また、距離 d を大きくすることは、遅延させるデータ量が増加することとなり、必要メモリを増加させる。20

#### 【0015】

##### 【発明が解決しようとする課題】

上述した従来の書込みヘッドで、より高光出力のものを得たい場合、各発光点に流れる電流を増やすか、発光デューティを増加させるために同時に点灯できる発光点の数を増やす必要がある。電流値は、寿命に大きく影響するため、むやみに増やせない場合が多い。そこで、発光デューティを増加させるために同時に点灯できる発光点の数を 1 チップあたり 2 個にするために、 $I_1$  ラインを 2 本にすると、多層配線を使わない限り、発光素子の外側を  $I_1$  ラインが通ることになる。このため、発光素子とチップ長辺までの距離が遠くなってしまい、距離 d が大きくなってしまう。30

#### 【0016】

さらに、同時に発光できる点数を 3 個以上にするためには、多層配線を使わない限り実現できない。

#### 【0017】

本発明の目的は、チップ間の y 方向距離 d を大きくすることなく、同時に点灯できる発光点の数を 1 チップあたり 2 個にすることのできる自己走査型発光素子アレイチップを提供することにある。

#### 【0018】

本発明の他の目的は、多層配線を用いることなく、同時に点灯できる発光点の数を 1 チップあたり 4 個にすることのできる自己走査型発光素子アレイチップを提供することにある。

#### 【0019】

##### 【課題を解決するための手段】

本発明によれば、1 つのチップ上に、自己走査型発光素子アレイ回路を 2 個作り込む。この場合に、 $I_1$  ラインを各回路毎に独立に設け、それぞれの  $I_1$  ラインあたり、1 個の発光点が点灯できるようにした。

#### 【0020】

各自己走査型発光素子アレイ回路へ 2 相クロックパルスラインは、各回路毎に独立に設け50

ることもでき、あるいは各回路に共通に設けることもできる。2相クロックパルスラインを共通に設ける場合には、転送素子と各クロックパルスラインとの間に抵抗を設け、この抵抗の値および各クロックパルスラインに挿入された電流制限抵抗の値を、2個の転送素子が同時にオンとなるように選ぶ。

#### 【0021】

また、各自己走査型発光素子アレイ回路において、<sub>1</sub> ラインを2本設け、各<sub>1</sub> ラインに発光素子を交互に接続すれば、各回路毎に2個の発光点、合計4個の発光点を同時に点灯することが可能となる。

#### 【0022】

このように同時に点灯できる発光素子の数を増やすことにより、発光デューティを大きくできるので、光書き込みヘッドの光出力を増大させることが可能となる。 10

#### 【0023】

##### 【発明の実施の形態】

以下、本発明の実施の形態を、図面に基づいて説明する。

#### 【0024】

##### 【第1の実施例】

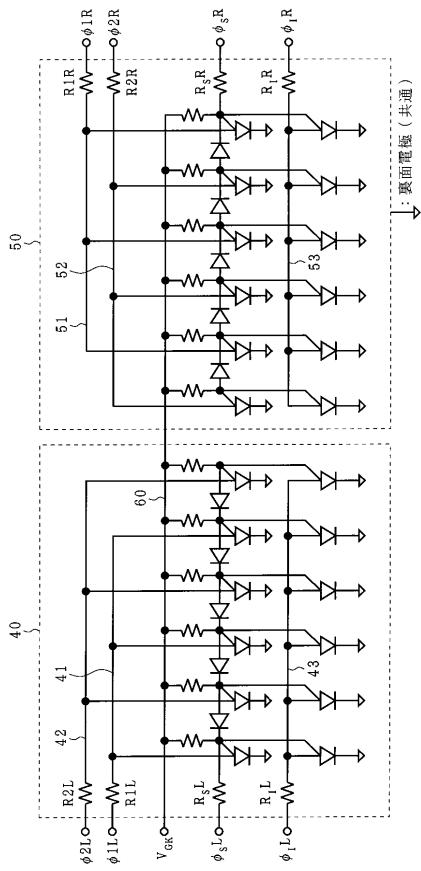

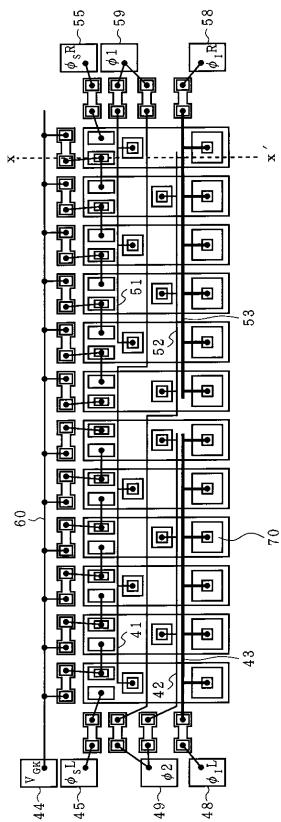

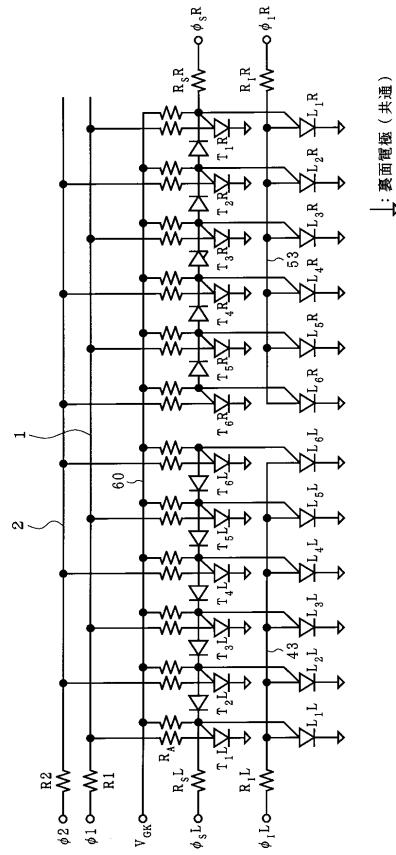

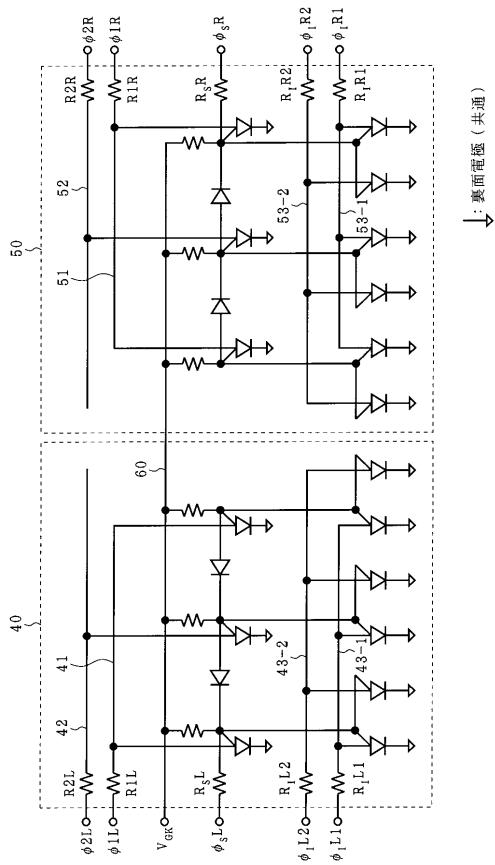

第1の実施例の自己走査型発光素子アレイチップの等価回路を図5に示す。1個のチップに2つの回路を作り込んだものである。図において、左右の回路40, 50は、図面を簡単にするためそれぞれ、各6個の発光素子を持った例を示している。 20

#### 【0025】

各回路40, 50は、図3に示した回路と同じであり、回路40は発光点が左から右へ転送され、回路50は発光が右から左へ転送される構成となっている。各回路を構成する素子は、図3で示した回路と同じである。左側回路40において、<sub>1L</sub>, <sub>2L</sub>はクロックパルス、<sub>sL</sub>はスタートパルス、<sub>1L</sub>は書き込み信号、41は<sub>1L</sub>ライン、42は<sub>2L</sub>ライン、43は<sub>1L</sub>ラインを示している。また、右側回路50において、<sub>1R</sub>, <sub>2R</sub>はクロックパルス、<sub>sR</sub>はスタートパルス、<sub>1R</sub>は書き込み信号、51は<sub>1R</sub>ライン、52は<sub>2R</sub>ライン、53は<sub>1R</sub>ラインを示している。

#### 【0026】

このように左右の回路ごとに、クロックパルス<sub>1</sub>, <sub>2</sub>、スタートパルス<sub>s</sub>、書き込み信号<sub>1</sub>をそれぞれ別系統とし、図示のように電源V<sub>GK</sub>のみは共通とする。共通のV<sub>GK</sub>ラインを60で示す。 30

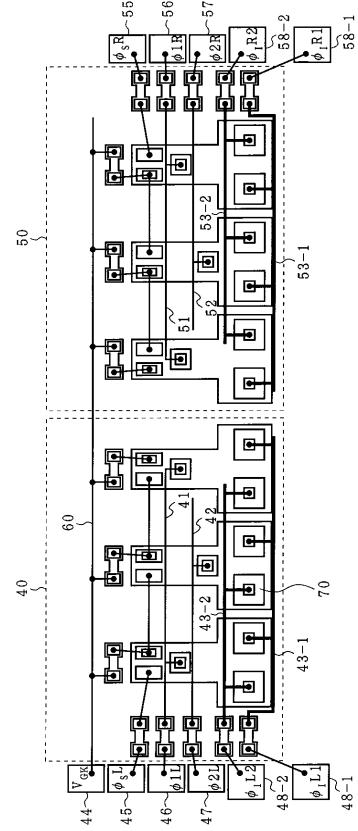

#### 【0027】

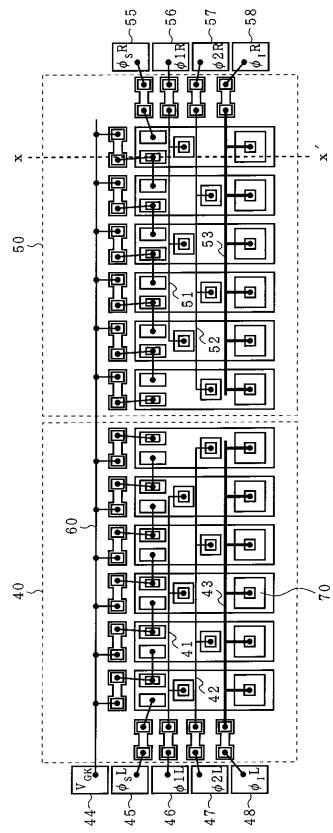

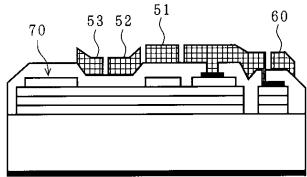

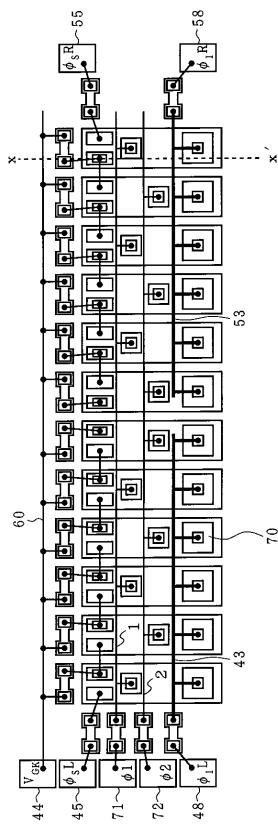

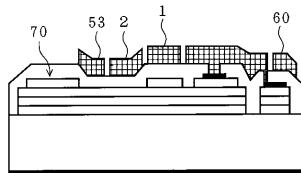

図6は、図5のチップの実際の構成の平面図であり、図7は、図6のX-X線断面図である。図6および図7において、図5と同じ要素には、同一の参照番号を付して示してある。

#### 【0028】

なお、図6において、44, 45, 46, 47, 48および55, 56, 57, 58は、ボンディングパッドを、70は発光部を示している。

#### 【0029】

図7の断面図に示すように、自己走査型発光素子アレイチップは、p n p n構造により作製される。p n p n構造は、n型半導体基板100上に、n型半導体層101, p型半導体層102, n型半導体層103, p型半導体層104が順次積層される。保護膜120上に、<sub>1</sub>ライン51, <sub>2</sub>ライン52, <sub>1</sub>ライン53, V<sub>GK</sub>ライン60が設けられている。また、n型半導体基板100の裏面には共通の裏面電極110が設けられている。 40

#### 【0030】

図5, 図6, 図7から明らかなように、本実施例の自己走査型発光素子アレイチップは、V<sub>GK</sub>ラインを共通としているが、回路40, 50毎に独立しており、2つの自己走査型発光素子アレイを1つのチップに作り込んだ構成となっている。

#### 【0031】

このような構成によれば、<sub>1</sub> ラインを左右2本に分割し、それぞれのラインあたり1個 50

の発光点を点灯できる。したがって、発光デューティを増加させることができ、高光出力が得られる。

#### 【0032】

なお、以上の実施例では、左右の回路の発光素子の数を同じにしているが、同じである必要は必ずしもない。

#### 【0033】

さらに、本実施例では、回路40は左から右へ、回路50は右から左へ発光点を転送しているが、必ずしもこの組み合わせである必要はない。しかし実際には、ボンディングパッドをチップの両端に置く構造をとる場合には、スタートパルス端子がチップ両端にあるため、チップの両端から中心に向かって発光点が転送する構成が作りやすい。

10

#### 【0034】

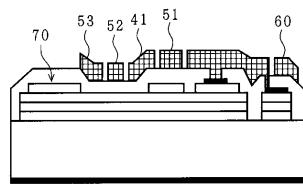

##### 【第2の実施例】

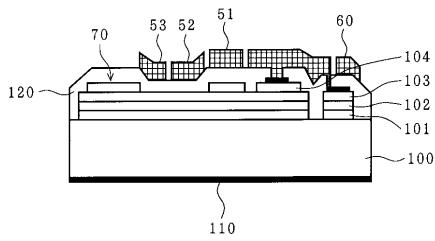

第1の実施例では、単純に2つの自己走査型発光素子アレイを1つのチップに作り込んだだけであったため、1ライン、2ラインが左右別々に存在するため、ボンディングパッドの数が増加し、チップ面積を増加させる。

#### 【0035】

そこで、本実施例では、図5の回路において、1Lラインと1Rラインと同じボンディングパッドに接続し、2Lラインと2Rラインと同じボンディングパッドに接続することで第1の実施例よりもボンディングパッドを2個減らす構成とした。

20

#### 【0036】

図8に、その回路構成を示す。1Lライン41と1Rライン51を右側のボンディングパッドに、2Lライン42と2Rライン52とを左側のボンディングパッドに接続する。

#### 【0037】

図9は、図8のチップの実際の構成の平面図であり、図10は、図9のX-X線断面図である。図9、図10において、図6、図7と同一の要素には、同一の参照番号を付して示してある。なお、49は2パッド、59は1パッドを示している。

#### 【0038】

第1の実施例に比べて、パッド数を、2個減らすことができ、したがってチップ面積を小さくすることができる。

30

#### 【0039】

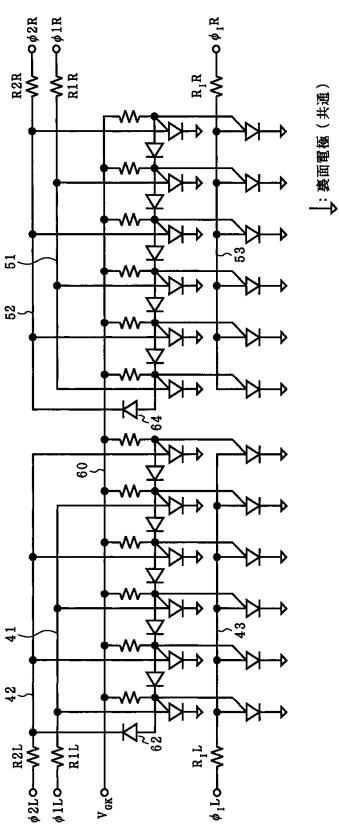

##### 【第3の実施例】

第1および第2の実施例では、スタートパルス端子を備えているが、ダイオードを用いて、スタートパルスをクロックパルスに兼ねさせることによって、スタートパルス端子を省略することができる。

#### 【0040】

図11に、その回路構成を示す。ダイオード62を、左側回路の左端の転送素子のゲートと、2Lライン42との間に挿入し、およびダイオード64を、右側回路の左端の転送素子のゲートと、2Rライン52との間に挿入する。

40

#### 【0041】

図12は、図11のチップの実際の構成の平面図であり、図13は、図12のX-X線断面図である。なお、図12の左側回路において、66、68は、ダイオード62のカソードおよびアノードをそれぞれ示している。

#### 【0042】

本実施例の回路によれば、<sub>s</sub>Lボンディングパッドおよび<sub>s</sub>Rボンディングパッドを省略できるので、チップの面積を小さくすることができる。さらに、本実施例の回路では、左側回路および右側回路において、共に発光点を左から右へ転送しているが、<sub>s</sub>ボンディングパッドの無いこの構成では、スタートする転送素子を自由に選ぶことができる。また、転送方向については自由な構成が可能となる。

#### 【0043】

50

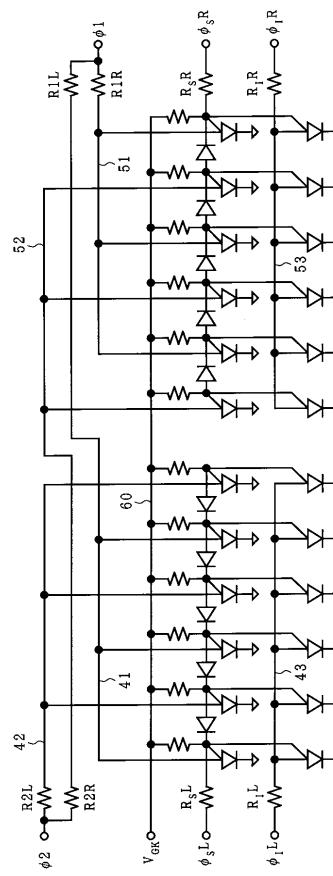

**【第4の実施例】**

第2の実施例では、1, 2のボンディングパッドは1チップあたり1個にできたが、図8を見ればわかるように、チップ表面を3本分のクロックラインが通るスペースが必要となる。このため、チップ面積が大きくなる問題点がある。そこで、本実施例では、シフト部の転送素子（サイリスタ）のアノードとクロックラインとの間に適当な抵抗 $R_A$ を設けることにより、2本のクロックライン1, 2で同時に2発光点が点灯できるようにした。

**【0044】**

図14に、その回路構成を示す。2本の1ライン1, 2ライン2を設け、転送素子（サイリスタ） $T_1 L, T_2 L, T_3 L, \dots, T_1 R, T_2 R, T_3 R, \dots$ の各アノードを、抵抗 $R_A$ を経て、それぞれ1ライン, 2ラインに接続する。その他の構成は、図5に同じである。10

**【0045】**

図15は、図14のチップの実際の構成の平面図であり、図16は、図15のX-X線断面図である。図15において、71は1ボンディングパッド、72は2ボンディングパッドである。

**【0046】**

抵抗 $R_A$ を設けることにより、同時に2点転送ができるメカニズムについて説明する。いま、図14の $s L$ 端子および $s R$ 端子が基板電位の場合を考える。この場合、サイリスタ $T_1 L, T_1 R$ のしきい電圧 $V_{th}$ は約 $V_D$ （pn接合順方向電位）である。クロックパルス1がHレベルになり、サイリスタ $T_1 L, T_1 R$ のいずれかがオンする。オンしたサイリスタのアノードは約 $V_D$ に固定される。このときのクロックパルス1の電圧は、アノード電圧（ $V_D$ ）よりも抵抗 $R_A$ の電圧降下分だけ高い値となる。このため、先にオンできなかったサイリスタも速やかにオンできる。すなわち、サイリスタ $T_1 L$ と $T_1 R$ とを同時にオンできる。これにより対応する発光素子（サイリスタ） $L_1 L, L_1 R$ を同時に点灯できる。20

**【0047】**

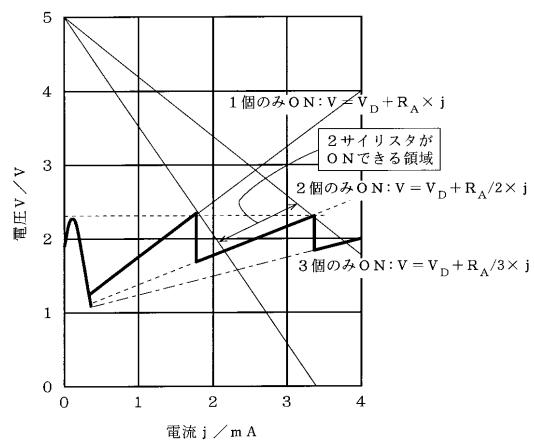

このとき、サイリスタ $T_2 L$ と $T_2 R$ のしきい電圧 $V_{th}$ は、約 $2V_D$ である。クロックパルス2がHレベルとなると、このどちらかがオンできる。このときのサイリスタの電流-電圧（I-V）特性を図17に示す。 $i = 3mA$ となるように抵抗 $R_A, R_2$ およびパルス電圧を選ぶと、2ラインの電圧は、オンできなかったサイリスタのしきい電圧（ $2V_D$ ）よりも低い値となり、1個しか点灯できない。しかし、電流を増やしていくと、2ラインの電圧は上昇していき、ついにはしきい電圧を超える。I-V特性は実線から破線に乗り移り、2つのサイリスタ $T_2 L$ と $T_2 R$ が同時にオンする。すなわち、 $R_A$ と $R_1, R_2$ の値を適当に選ぶことによって、1クロックラインあたり2個以上のサイリスタを同時にオンさせることができる。30

**【0048】**

アノード抵抗 $R_A$ および電流制限抵抗 $R_1, R_2$ は、2個のサイリスタがオン可能であり、かつ、3個が同時にオンしないように選ぶ（なお、3個目のサイリスタがオンしようとするのは、転送時に起こる）。40

**【0049】**

すなわち、電流 $j$ が2ラインに流れているとき、2個のサイリスタがオンするには、 $V_{th} < V_D + R_A \times j$

であり、3個以上のサイリスタがオンしないためには、

$$V_{th} > V_D + R_A / 2 \times j$$

である必要がある。これを $j$ について解くと、

$$2(V_{th} - V_D) / R_A > j > (V_{th} - V_D) / R_A$$

となる。この $j$ は、クロックパルスのHレベル電圧 $V_H$ と抵抗 $R_2$ の値とで決められ、

$$j = (V_{th} - V_D) + R_2$$

となる。この式の関係およびサイリスタの動作条件を考慮して、 $R_A$ および $R_1, R_2$ の50

値を決める。図17の負荷曲線の場合、 $R_A = 375$  のとき、 $411 < R_1, R_2 < 800$  となった。

#### 【0050】

抵抗 $R_A$ の作り方は、いろいろと考えられるが、ここでは、アノード層エピ膜の不純物濃度を低めに設定し、アノード電極とアノード層の間の接触抵抗が大きめになるように調整し、抵抗 $R_A$ として用いた。

#### 【0051】

なお、抵抗 $R_A$ はこのほかの作り方でもよく、例えば、アノード電極と金属配線の間に、抵抗層を設けたり、あるいは、半導体層や金属薄膜などを用いて独立した抵抗を作つて接続しても良い。

10

#### 【0052】

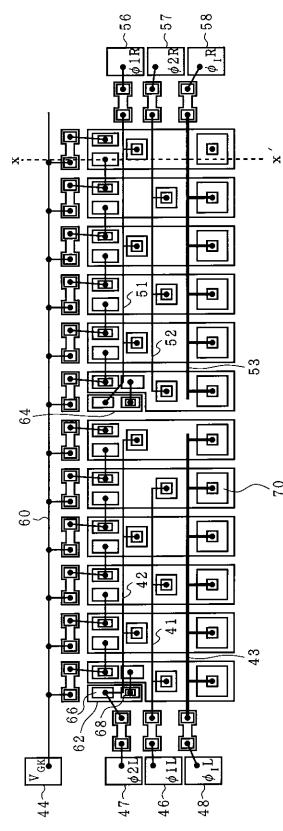

##### 【第5の実施例】

第1～第4の実施例は、 $\text{---}$  ラインを発光素子列の片側に置く構造について示した。しかし、更に光量が必要な場合、発光素子の両側に $\text{---}$  ラインを置き、それぞれを2分割することによって、1チップあたり4発光点を同時に点灯できる。

#### 【0053】

図18に、その回路構成を、図19に、チップの実際の構成を示す。なお、本実施例は、第1の実施例(図5, 図6)の構成において、 $\text{---}$  Lライン,  $\text{---}$  Rラインをそれぞれ2分割した例である。

20

#### 【0054】

1個の転送素子に対して、2個の発光素子を対応させ、左側回路40では、発光素子を2本の $\text{---}$  Lライン43-1,  $\text{---}$  Lライン43-2にそれぞれ交互に接続し、右側回路50では、発光素子を2本の $\text{---}$  Rライン53-1,  $\text{---}$  Rライン53-2にそれぞれ交互に接続する。

#### 【0055】

なお、図19において、48-1, 48-2は左側回路40の $\text{---}$  L1,  $\text{---}$  L2ラインのボンディングパッドを、58-1, 58-2は右側回路50の $\text{---}$  R1,  $\text{---}$  R2ラインのボンディングパッドを、それぞれ示す。

#### 【0056】

このような構成では、左側回路で2個の発光点と右側回路で2個の発光点とを同時に、すなわち4発光点を同時に点灯させることができる。

30

#### 【0057】

なお、このような4発光点を同時に点灯させる構成は、第2, 第3, 第4の実施例についても適用することができる。

#### 【0058】

##### 【発明の効果】

本発明によれば、チップ間のy方向距離を大きくすることなく、同時に点灯できる発光点の数を1チップあたり2個にすることができる。したがって、発光デューティを増大できるので、光書き込みヘッドとしての光出力を大きくすることができる。

#### 【0059】

さらに、本発明によれば、多層配線を用いることなく、同時に点灯できる発光点の数を1チップあたり4個にすることのできる自己走査型発光素子アレイチップを提供することが可能となる。

40

##### 【図面の簡単な説明】

【図1】光書き込みヘッドを備える光プリンタの原理を示す図である。

【図2】光書き込みヘッドの構造を示す図である。

【図3】シフト部と発光部とを分離した構造の自己走査型発光素子アレイチップの等価回路図である。

【図4】ボンディングパッドを片端に寄せたチップを千鳥状に配置した様子を示す模式図である。

50

【図5】第1の実施例の自己走査型発光素子アレイチップの等価回路を示す図である。

【図6】図5のチップの実際の構成の平面図である。

【図7】図6のX-X線断面図である。

【図8】第2の実施例の自己走査型発光素子アレイチップの等価回路を示す図である。

【図9】図8のチップの実際の構成の平面図である。

【図10】図9のX-X線断面図である。

【図11】第3の実施例の自己走査型発光素子アレイチップの等価回路を示す図である。 10

【図12】図11のチップの実際の構成の平面図である。

【図13】図12のX-X線断面図である。

【図14】第4の実施例の自己走査型発光素子アレイチップの等価回路を示す図である。 10

【図15】図14のチップの実際の構成の平面図である。

【図16】図15のX-X線断面図である。

【図17】サイリスタのI-V特性を示す図である。

【図18】第5の実施例の自己走査型発光素子アレイチップの等価回路を示す図である。

【図19】図18のチップの実際の構成の平面図である。

#### 【符号の説明】

4 1 1 L ライン

4 2 2 L ライン

4 3 1 L ライン

5 1 1 R ライン

5 2 2 R ライン

5 3 1 R ライン

6 0 V<sub>GK</sub> ライン

6 2 , 6 4 ダイオード

4 4 , 4 5 , 4 6 , 4 7 , 4 8 , 4 9 ボンディングパッド

5 5 , 5 6 , 5 7 , 5 8 , 5 9 ボンディングパッド

7 1 , 7 2 ボンディングパッド

1 0 0 n型半導体基板

1 0 1 n型半導体層

1 0 2 p型半導体層

1 0 3 n型半導体層

1 0 4 p型半導体層

1 1 0 裏面電極

1 2 0 保護膜

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開2000-164932(JP,A)

特開2000-168134(JP,A)

特開平09-150543(JP,A)

(58)調査した分野(Int.Cl., DB名)

B41J 2/44

B41J 2/45

B41J 2/455

H01L 33/00

H01S 5/00-5/50