(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5357706号

(P5357706)

(45) 発行日 平成25年12月4日(2013.12.4)

(24) 登録日 平成25年9月6日(2013.9.6)

(51) Int.Cl.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| HO1L 23/14 | (2006.01) | HO1L 23/14 | S    |

| HO1L 23/32 | (2006.01) | HO1L 23/32 | D    |

| HO1L 23/36 | (2006.01) | HO1L 23/36 | C    |

| HO1L 23/12 | (2006.01) | HO1L 23/12 | 501B |

| HO1L 23/28 | (2006.01) | HO1L 23/12 | J    |

請求項の数 5 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2009-257469 (P2009-257469)

(22) 出願日

平成21年11月10日(2009.11.10)

(65) 公開番号

特開2011-103358 (P2011-103358A)

(43) 公開日

平成23年5月26日(2011.5.26)

審査請求日

平成24年9月7日(2012.9.7)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100118924

弁理士 廣幸 正樹

(72) 発明者 東 和司

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 山本 雄一

最終頁に続く

(54) 【発明の名称】半導体実装構造体

## (57) 【特許請求の範囲】

## 【請求項1】

樹脂基板と、

側周面に凹部と、貫通し信号を伝達する複数の貫通電極と、貫通し熱を伝達するためだけの複数の放熱ビア電極とを含み、前記樹脂基板上に実装されたシリコン基板と、前記シリコン基板の上面に設けられ、前記放熱ビア電極と前記凹部とを結び、前記貫通電極と接触しない放熱パターンと、

前記シリコン基板の上に実装された半導体チップと、

前記半導体チップと前記放熱ビア電極と前記貫通電極と前記放熱パターンとまでに渡つて形成され、前記凹部には形成されない絶縁層とを備え、前記半導体チップの前記シリコン基板上の領域は、対向する2辺が前記複数の貫通電極の列で挟まれ、異なる対向する2辺が前記複数の放熱ビア電極の列で挟まれ、前記複数の放熱ビア電極の列と前記凹部間に前記複数の放熱ビア電極がさらに設けられた半導体実装構造体。

## 【請求項2】

前記凹部及び前記絶縁層を導電性放熱材料で覆う請求項1に記載の半導体実装構造体。

## 【請求項3】

前記貫通電極の直径は50~100μmであり、前記放熱ビア電極の直径は100~200μmである請求項1に記載の半導体実装構造体。

## 【請求項4】

10

20

前記凹部の表面は、金属膜で覆われていることを特徴とする請求項1に記載の半導体実装構造体。

**【請求項5】**

前記凹部は、前記シリコン基板の上下方向に所定長だけ延在する複数の溝を備え、前記溝は所定ピッチだけ離間していることを特徴とする請求項1に記載の半導体実装構造体。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、シリコン基板に実装および結線された半導体を絶縁樹脂で封止して構成され、当該半導体より発生される熱を効率的に放熱できる半導体実装構造体に関する。 10

**【背景技術】**

**【0002】**

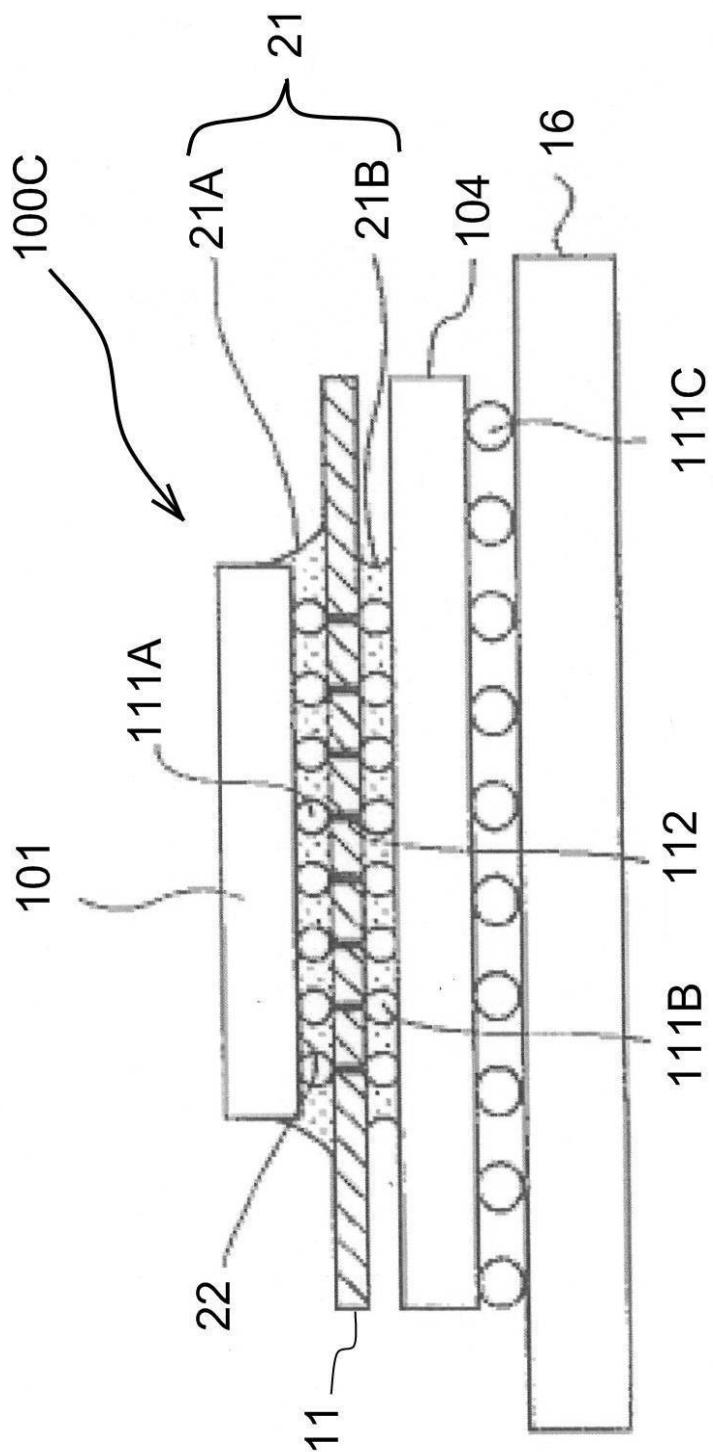

図8に半導体実装構造体の一例(例えば、特許文献1参照)を示す。半導体実装構造体100cは、LSI101、インターポーザ11、樹脂基板104、BGA111、アンダーフィル樹脂21、およびマザーボード16を含む。インターポーザ11は、LSI101の回路形成面22上の接続点に対応する複数の貫通電極112を含む。BGA111は複数のハンダボールがマトリックス状に配置されてなるボール・グリッド・アレイ(Ball Grid Array)であり、本例においては、LSI101とインターポーザ11との間に配される第1のBGA111Aと、インターポーザ11と樹脂基板104との間に配される第2のBGA111Bと、樹脂基板104とマザーボード16との間に配される第3のBGA111Cを含む。 20

**【0003】**

アンダーフィル樹脂21は、第1のアンダーフィル樹脂21Aと第2のアンダーフィル樹脂21Bとを含む。第1のアンダーフィル樹脂21Aは、LSI101と、第1のBGA111Aと、インターポーザ11(貫通電極112)との固定に用いられる。アンダーフィル樹脂21Bは、インターポーザ11と、第2のBGA111Bと、樹脂基板104との固定に用いられる。

**【0004】**

第1のBGA111Aは、そのハンダボールがLSI101の回路形成面22の接続点とインターポーザ11の貫通電極112の上端部とに接触して配置される。そして、LSI101とインターポーザ11との間に、第1のBGA111Aを内包するように、アンダーフィル樹脂21Aが充填されている。 30

**【0005】**

第2のBGA111Bは、インターポーザ11の貫通電極112の下端部と樹脂基板104の上端部に接続して配置される。インターポーザ11と樹脂基板104の間に、第2のBGA111Bを内包するようにアンダーフィル樹脂21Bが充填されている。

**【0006】**

上述の如く構成された半導体実装構造体100cにおいては、LSI101で発生した熱は、第1のBGA111A、インターポーザ11の貫通電極112、第2のBGA111Bを介して、樹脂基板104に伝導される。樹脂基板104に伝導された熱は、BGA111Cを介して、マザーボード16に伝導される。このようにして、LSI101で発生した熱は、半導体実装構造体100cの構成要素を伝導しながら放熱される。なお、半導体実装構造体100cにおいて、熱源であるLSI101を除く構成部材を、受熱体100rと呼ぶものとする。 40

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【特許文献1】特開2004-327951号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0008】**

半導体実装構造体100cにおいては、LSI101で発生した熱は、LSI101の表面から周囲の空気に伝導する第1の放熱経路と共に、アンダーフィル樹脂21A、およびBGA111を介して樹脂基板104およびマザーボード16へ伝導する第2の放熱経路と、それぞれ要素の表面から輻射と共に周囲の空気に伝導される第3の放熱経路を経て外部に放出される。

**【0009】**

LSI101の空気との接触（放熱）面積は、LSI101のほぼ片面と限られているうえに、空気は断熱材であるので、LSI101で発生した熱の第1及び第3の放熱経路を介しての熱伝導（熱排出）は効率的ではない。また、アンダーフィル樹脂21、インターポーザ11、樹脂基板104、及びマザーボード16は良熱伝導体とはいえず、LSI101から熱を迅速に奪い、効果的に外部に排出することは難しい。10

**【0010】**

LSI101から受熱体100rに伝導した熱は、半導体実装構造体100cの外部に排出され難く。さらに、LSI101の発熱量に対する、受熱体100r（アンダーフィル樹脂21、インターポーザ11、樹脂基板104、及びマザーボード16）のヒートマスが小さい。それゆえに、受熱体100rは容易に高温になり、LSI101と受熱体100rとの温度勾配がすぐに小さくなるために、LSI101から受熱体100rへの熱伝導が起こり難くなり、LSI101はより高温になってしまう。

**【0011】**

つまり、LSI101が発熱量の大きい半導体チップである場合、熱経路および熱経路の放熱能力が不足する。結果、LSI101の熱は、十分に放熱されずに半導体実装構造体100cに蓄積されてしまう。そして、半導体実装構造体100c（LSI101）は熱により劣化して、その信頼性が低下するという課題を有している。20

**【0012】**

本発明は、前記従来の課題を解決するもので、半導体素子で発生した熱を迅速に奪い、半導体素子の発熱量が大きい場合においても高い放熱性を確保できる半導体実装構造体を提供することを目的とする。

**【課題を解決するための手段】****【0013】**

上記の課題を解決する為に、本発明に係る半導体実装構造体は、樹脂基板と、側周面に凹部と、貫通し信号を伝達する複数の貫通電極と、貫通し熱を伝達するためだけの複数の放熱ビア電極とを含み、前記樹脂基板上に実装されたシリコン基板と、前記シリコン基板の上面に設けられ、前記放熱ビア電極と前記凹部とを結び、前記貫通電極と接触しない放熱パターンと、前記シリコン基板の上に実装された半導体チップと、前記半導体チップと前記放熱ビア電極と前記貫通電極と前記放熱パターンとまでに渡って形成され、前記凹部には形成されない絶縁層とを備え、前記半導体チップの前記シリコン基板上の領域は、対向する2辺が前記複数の貫通電極の列で挟まれ、異なる対向する2辺が前記複数の放熱ビア電極の列で挟まれ、前記複数の放熱ビア電極の列と前記凹部間に前記複数の放熱ビア電極がさらに設けられている。40

**【発明の効果】****【0014】**

半導体素子で発生した熱を迅速に奪い、半導体素子の発熱量が大きい場合においても高い放熱性を確保できる半導体実装構造体を提供できる。

**【図面の簡単な説明】****【0015】**

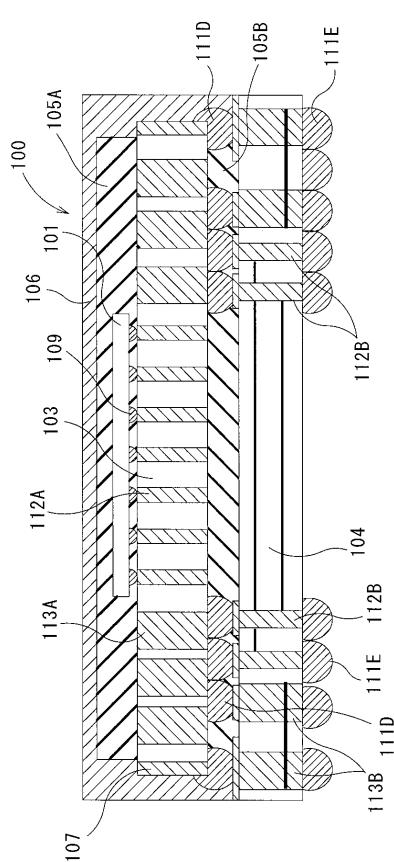

【図1】本発明の第1の実施の形態に係る半導体実装構造体の内部構造を示す縦断面図である。

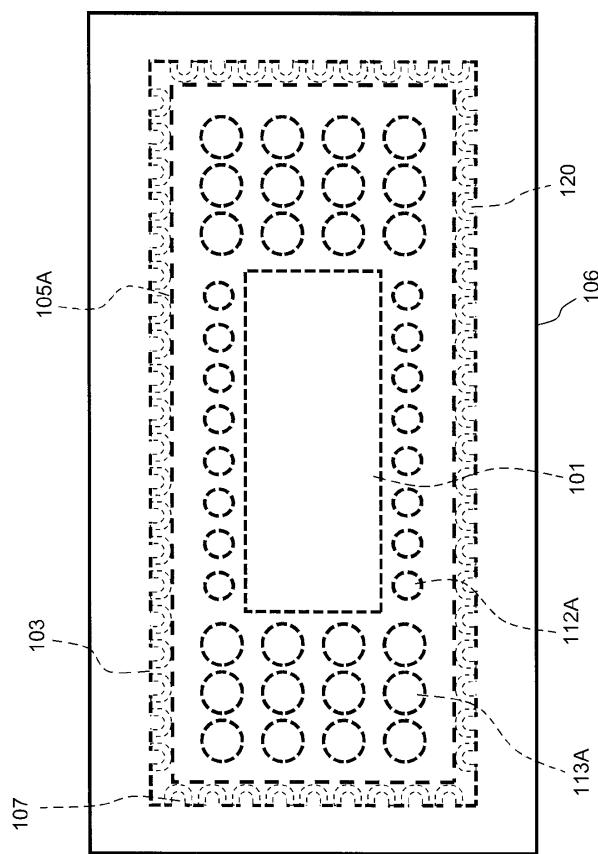

【図2】図1の半導体実装構造体を上面から見た平面図である。

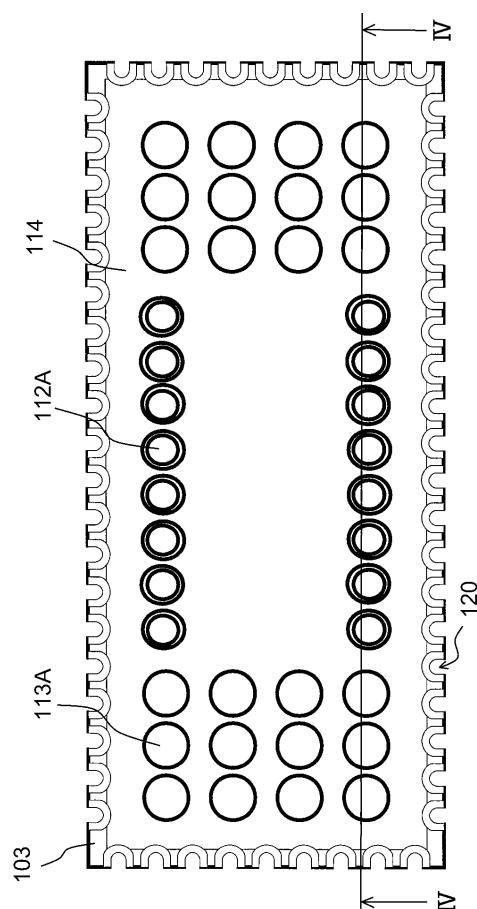

【図3】図1のシリコン基板の内部パターンを示す平面図である。

10

20

30

40

50

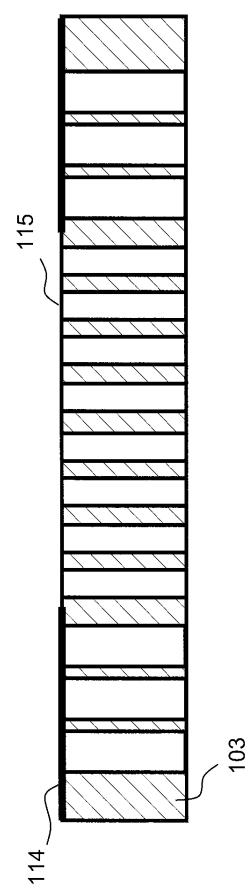

【図4】図3のシリコン基板のIV-IV断面図である。

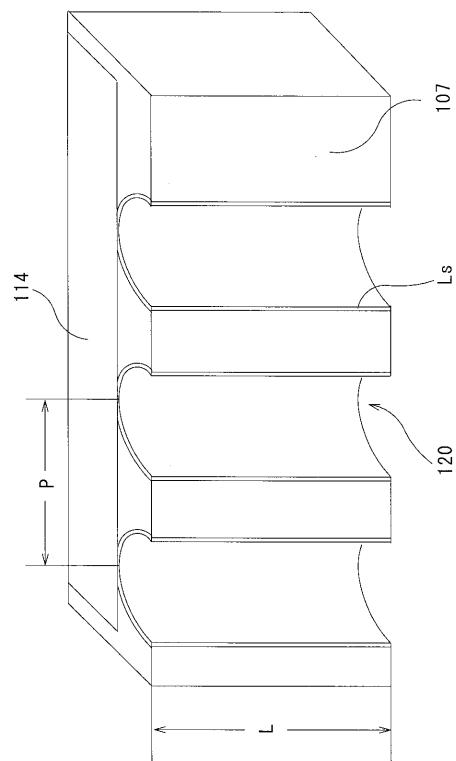

【図5】図3のシリコン基板の側端部に設けられている放熱部(凹凸部)を示す斜視図である。

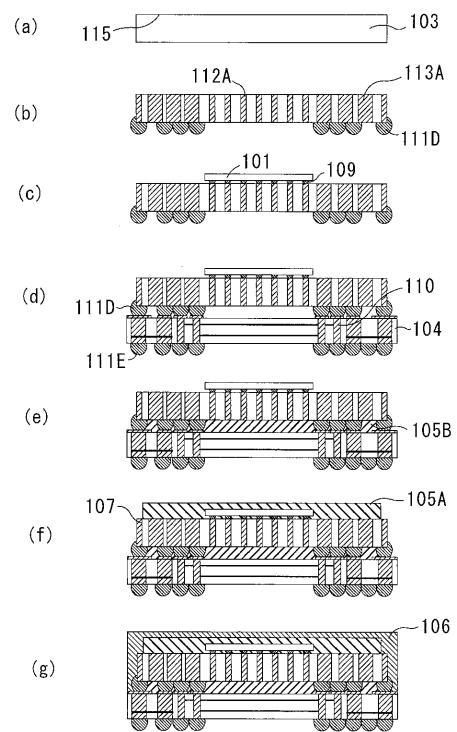

【図6】図1の半導体実装構造体の製造工程の説明図である。

【図7】本発明の第2の実施の形態に係る半導体実装構造体の内部構造を示す縦断面図である。

【図8】従来の半導体実装構造体の断面図である。

【発明を実施するための形態】

【0016】

以下に図面を参照して、本発明の実施の形態について説明する。なお、図8に示した上述の半導体実装構造体100cに於けるのと同じ構成要素については同じ符号を用い、説明を省略する。 10

【0017】

(第1の実施の形態)

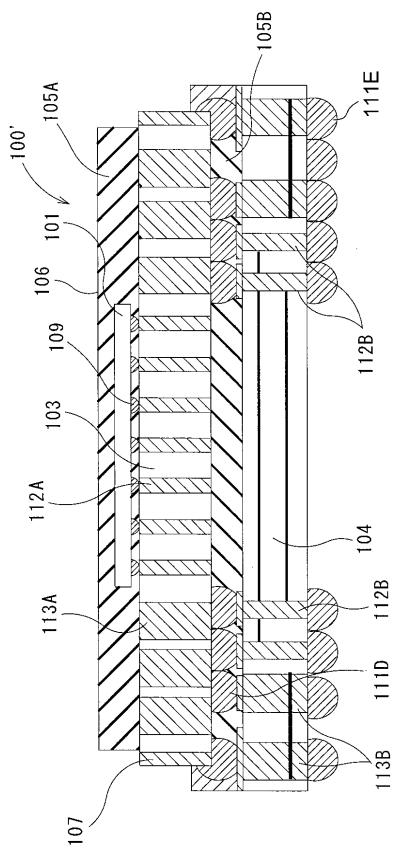

図1、図2、図3、図4、図5、及び図6を参照して、本発明の第1の実施の形態に係る半導体実装構造体について説明する。

【0018】

図1に示すように、半導体実装構造体100は、LSI101、複数のバンプ電極109、シリコン基板103、樹脂基板104、絶縁性高放熱材料105、および導電性高放熱材料106を含む。バンプ電極109は、LSI101の回路形成面22上の接続点上にそれぞれ配設されている。 20

【0019】

シリコン基板103には、LSI101の回路形成面22上の接続点に対応する複数の貫通電極112Aが中心部に設けられ、複数の放熱ビア電極113Aが複数の貫通電極112Aを挟んで周辺部に設けられている。LSI101は、バンプ電極109が貫通電極112Aの上端部に接触して配置される。この状態で、絶縁性高放熱材料105Aによって、LSI101はシリコン基板103に固定される。

【0020】

樹脂基板104には、複数の貫通電極112Bと、複数の放熱ビア電極113Bが設けられている。図1においては、上述の貫通電極112Aより外周部よりに2本ずつ、計4本の貫通電極112Bが示されている。また、貫通電極112Bおよび放熱ビア電極113Aより外周部に2本ずつ、計4本の放熱ビア電極113Bが示されている。また、貫通電極112Bは互いに連結され、放熱ビア電極113Bもまた互いに連結されている。 30

【0021】

貫通電極112Bおよび放熱ビア電極113Bの上部にはそれぞれBGA111Dのハンダボールが配されている。そして、貫通電極112B及び放熱ビア電極113Bの下端部にBGA111Eのハンダボールが配設されている。

【0022】

そして、シリコン基板103と樹脂基板104との間に、BGA111Dを内包するよう、絶縁性高放熱材料105Bが充填されている。この状態で、導電性高放熱材料106によって、シリコン基板103に固定されたLSI101は、さらに樹脂基板104に固定される。 40

【0023】

図2を参照して、半導体実装構造体100を上面から見た場合の、シリコン基板103、絶縁性高放熱材料105、および導電性高放熱材料106の平面的な位置関係について説明する。同図に示すように、半導体実装構造体100は、導電性高放熱材料106によって覆われており、その外形が導電性高放熱材料106によって決定されている。導電性高放熱材料106の輪郭の内側には、絶縁性高放熱材料105Bの輪郭が、その内側にはシリコン基板103の輪郭およびシリコン基板103に設けられた貫通電極112Aおよび放熱ビア電極113Aの輪郭と、シリコン基板103上に設けられたLSI101の輪 50

郭が示されている。

**【0024】**

図2に示す例においては、シリコン基板103にはLSI101を挟み8本/列×2列の計16本の貫通電極112Aと、3本/列×4列の計12本/側×2側の合計24本の放熱ビア電極113Aが設けられている。なお、シリコン基板103の外周側壁部には複数の凹凸部120が設けられているが、これらについては、後ほど図3を参照して詳述する。

**【0025】**

図3に、図2に示したシリコン基板103のみを示す。上述のように、本例においては、シリコン基板103の長手方向に、LSI101の載置位置を避けるように、8本/列×2列、計16本の貫通電極112Aと、3本/列×4列の計12本/組×2組の計24本の放熱ビア電極113Aがマトリックス上に設けられている。なお、貫通電極112Aおよび放熱ビア電極113Aの本数や位置は、これに限定されるものではなく、半導体実装構造体100毎に適正に定められるものである。また、貫通電極112はシリコン基板103の回路形成面22の接続点に対応する位置に設けられていることは上述のとおりである。同図におけるIV-IV断面図を図4に示す。

**【0026】**

凹凸部120は、シリコン基板103の側周面に、その厚み方向、つまりシリコン基板103の正面に対して概ね垂直に所定の間隔で平行して設けられている。図3に示すように、凹凸部120は内部に向かって湾曲、例えばU字状に形成されている。後ほど、図5を参照して、凹凸部120についてさらに説明する。

**【0027】**

図4を参照して、貫通電極112Aと放熱ビア電極113Aの役割について述べる。図3に例示された、16本の貫通電極112Aは、LSI101の回路形成面22に接続されて、LSI101の実装パターン115を形成している。24本の放熱ビア電極113A(図3)は、LSI101が発生した熱を絶縁性高放熱材料105Aを介して受けて、さらに絶縁性高放熱材料105Bに導いて放出させる放熱パターン114を形成している。なお、貫通電極112Aは、LSI101の熱をバンプ電極109を介して受けて、絶縁性高放熱材料105Bに導いて放出させる放熱パターンとしての機能も有していることは言うまでもない。

**【0028】**

図5に、図3に於ける凹凸部120を右斜め上方から見た状態を示す。シリコン基板端面107にドライエッチング加工などにより、ピッチPが $10\text{ }\mu\text{m}$ 以下で、長さLが $100\text{ }\mu\text{m}$ 以上の凹凸部120を形成する。凹凸部120には化学的気相成長法(CVD: Chemical Vapor Deposition)などで絶縁膜を形成した後にTi(チタニウム)やCu(銅)のスパッタなどで表面層Lsを成膜する。そして、Cuなどをメッキして、表面の金属膜を厚くして、表面層Lsを形成する。

**【0029】**

このように構成された半導体実装構造体100においては、LSI101で発生された熱は、LSI101の表面およびバンプ電極109を介して絶縁性高放熱材料105Aに伝達されると共に、バンプ電極109を介して貫通電極112Aに伝達される。絶縁性高放熱材料105Aに伝達された熱は、絶縁性高放熱材料105Aを包む導電性高放熱材料106と、絶縁性高放熱材料105Aに接する放熱ビア電極113Aに伝達される。

**【0030】**

放熱ビア電極113A及び貫通電極112Aに伝えられた熱は、絶縁性高放熱材料105BおよびBGA111Dを介して放熱ビア電極113Bおよび貫通電極112Bに伝えられ、BGA111Eに伝えられる。また、絶縁性高放熱材料105Bには、シリコン基板103から伝熱される。なお、絶縁性高放熱材料105Aからは、シリコン基板103のシリコン基材にも伝熱されるが、放熱ビア電極113Aに比べると伝熱量は小さい。

**【0031】**

10

20

30

40

50

シリコン基板 103 に伝えられた熱の一部は、凹凸部 120 を介して導電性高放熱材料 106 に伝導される。このようにして、LSI 101 で発生した熱は、導電性高放熱材料 106 から空気中に放熱されると共に、樹脂基板 104 側の BGA 111E を介して放熱される。なお、半導体実装構造体 100 のヒートマスは、その構成要素である導電性高放熱材料 106、絶縁性高放熱材料 105A、バンプ電極 109、シリコン基板 103（貫通電極 112A、および放熱ビア電極 113A）のヒートマスの合計であり、従来の半導体実装構造体 100c のヒートマスに比べて非常に大きい。

#### 【0032】

結果、LSI 101 から熱をより多く吸収でき、同じだけの熱量を吸収しても半導体実装構造体 100c に比べて温度上昇は小さい。さらに、LSI 101 は難伝熱材である空気ではなく、絶縁性高放熱材料 105A で囲まれているので、LSI 101 の熱は容易且つ迅速に導電性高放熱材料 105A に吸収される。そして、絶縁性高放熱材料 105A に吸収された熱は、シリコン基板 103（凹凸部 120）を介して、導電性高放熱材料 106 の表面から放熱される。なお、凹凸部 120 によってシリコン基板 103 の放熱面積を増すことによって、シリコン基板 103 から導電性高放熱材料 106 への放熱能力が強化されている。

#### 【0033】

そして、絶縁性高放熱材料 105A の表面から放出されない熱は、絶縁性高放熱材料 105B、BGA 111D、貫通電極 112B、放熱ビア電極 113B、樹脂基板 104、および BGA 111E を介して放出される。なお、絶縁性高放熱材料 105B、BGA 111D、貫通電極 112B、放熱ビア電極 113B、樹脂基板 104、および BGA 111E も半導体実装構造体 100 のヒートマスを増大させている。

#### 【0034】

上述のように、熱を半導体実装構造体 100 の外部に逃がすためには、他の物質と熱交換しながら最終的に大気、または実装基板に放熱する。熱伝達は物質の比熱と熱容量により決まり、熱交換を活発にするために熱交換界面の表面積を大きくすることが効果的である。シリコン基板 103 の端面 107 から導電性高放熱材料 106 に熱を移動させるために界面の面積を大きくしている。具体的には、ピッチ P が  $10 \mu m$  以下で長さ L が  $100 \mu m$  以上の凹凸部 120 を設けることで、シリコン基板 103 と導電性高放熱材料 106 との界面積を確保することにより、熱伝導効率が向上する。

#### 【0035】

放熱性は表面積、及び、熱交換性に比例するため、ピッチ P が細かく、長さ L が長いほど表面積が増大し、放熱効果が向上する。ピッチ P が半分になれば表面積 A は 2 倍になる。長さ L に比例し、表面積 A は増加する。この事実を踏まえて、シリコン基板 103 から導電性高放熱材料 106 への熱伝導効率を考慮して、ピッチ P および長さ L は適宜決定される。

#### 【0036】

上述の如く構成されたシリコン基板 103 に、LSI 101 とシリコン基板上のパターンとのアライメントを合わせてフリップ素子実装し、素子裏面上部から絶縁樹脂で封止して熱硬化させる。その後、Cu、Ag、及びCNT（カーボンナノチューブ）などの導電性樹脂で覆いオーブンで熱硬化する。

#### 【0037】

上述の放熱ビア電極 113A は、LSI 101 で発生した熱を他に導く放熱経路であり直径は  $100 \sim 200 \mu m$  である。一方、貫通電極 112A は、信号伝達用の導電経路であり、直径は  $50 \sim 100 \mu m$  である。シリコン基板 103 の上に LSI 101 がフリップ素子実装され、その上部にエポキシ系の絶縁性高放熱材料 105、その上部に Cu や Ag（銀）のペーストなどの熱伝導性が  $10 W / mK$  以上の導電性高放熱材料 106 が形成される。

#### 【0038】

図 3 に示すように、シリコン基板 103 の表層部の内部パターンに信号ラインとは独立

10

20

30

40

50

した放熱パターン 114 を Cu スパッタ、フォトリソエッティングなどにより形成する。放熱パターン 114 は、LSI 101 が駆動することにより発生した熱を半導体実装構造体 100 の外部に伝達するための放熱経路を構成している。図 4 に示すように放熱パターン 114 はシリコン基板 103 の表層に形成される。

#### 【0039】

図 5 に、放熱パターン 114 とシリコン基板 103 の端面 107 との位置関係を示す。放熱パターン 114 から、シリコン基板 103 の端面 107 へ熱が伝達され、熱が空気中に放熱される。シリコン基板下面に BGA 111D を形成し、チップの実装された樹脂基板 104 にハンダ実装した後、実装の隙間を絶縁性高放熱材料 105B で封止する。実装隙間は約 0.3 ~ 0.4 mm である。封止材は熱伝導が 0.2 W/mK 以上のものを用いる。

10

#### 【0040】

係る構成によれば LSI 101 が駆動することにより発生する熱は直接接觸しているバンプ電極 109 及び絶縁性高放熱材料 105A に伝達され、シリコン基板 103、放熱パターン 114、貫通電極 112A、放熱ビア電極 113A に伝達され、シリコン基板 103 の端面 107 に到達する。さらに導電性高放熱材料 106 に伝達され、周囲の空気に放熱される。同時にシリコン基板 103 と樹脂基板 104 を接続するためのハンダ材料で形成された BGA 111D とシリコン基板 103 と樹脂基板 104 の間に充填された絶縁性高放熱材料 105B に熱が伝達し、さらに樹脂基板 104 に形成された信号ライン 110 と放熱ビア電極 113D に伝達され、樹脂基板 104 の下部に形成されたマザ - 実装基板との接続用の BGA 111E を通して、マザ - 基板に伝達される。

20

#### 【0041】

材料個別の熱伝導率により熱伝導速度が決まる。関係する主な材料の熱伝導率は Cu : 398 W/m·K、Si : 168 W/m·K、導電ペースト : 10 ~ 15 W/m·K、エポキシ樹脂 : 0.21 W/m·K、空気 : 0.024 W/m·K であり、Cu で形成されているシリコン基板 103 内の放熱パターン 114、放熱ビア電極 113 が効果的に熱を伝達することがわかる。LSI 101、及び、シリコン基板 103 と接觸する材料としては絶縁性の高放熱材料を用いる。熱伝導率の高い AlN フィラ - などを分散したエポキシ系の材料が代表的なものである。導電経路と接觸しない部分には熱伝導率の高い導電性高放熱材料を用いるのが効果的である。このように LSI が駆動時に発生した熱は実装構造体に伝達され、導電性高放熱材料の外表面から空気中に効率よく放熱することができる。

30

#### 【0042】

LSI 101 などの素子を実装したシリコン基板をマザ - 基板などに実装する場合、接続部に及ぶ熱変化から生じる応力に対して持ちこたえることができず、破壊される危険性があるため、シリコン基板を樹脂製インタ - ポ - ザ基板に実装した後に樹脂製インタ - ポ - ザ基板をマザ - 基板に実装する。これによりマザ - 基板の実装部で生じる応力を樹脂製インタ - ポ - ザで吸収し、シリコン基板の接続部の劣化を防ぐことができる。

#### 【0043】

また、メモリ - I C などを複合的に 1 つの実装構造体に含む場合、LSI 101 の熱影響を受けにくくするために I C の厚みを BGA 高さよりも薄くして樹脂製インタ - ポ - ザ基板に実装する。

40

#### 【0044】

なお、本実施の形態において、高放熱材料として導電性樹脂を設けたが、金属板の貼付けによる放熱経路の形成としてもよい。

#### 【0045】

放熱ビア電極の径は熱伝達面積が大きいほど効果があるが信号ラインとの大小は放熱性に影響のない事項である。

#### 【0046】

さらに、導電性材料で表面を覆うことにより ESD による障害を防止する効果がある。なおビア電極は、丸型孔は四角形状であってもその他の形状であっても同様の効果を得る

50

ことができる。

#### 【0047】

次に、本発明の実施の形態に係る半導体実装構造体100の冷却能力について述べる。実施例1として、図1から図3の構造のものを用いた。つまり、シリコン基板103は、厚み0.5mm、3cm×4cm、LSI101は、2cm×3cm、貫通電極112は、直径80μmで20本、凹凸部120は、径50ミクロン、ピッチは50ミクロン、パンプ電極109は直径30～50μmで20個、絶縁性高放熱材料105は、厚み約0.5mm、放熱パターン114は、厚み15μm、放熱ビア電極113は、直径100～150μmで20本、導電性高放熱材料106は、厚み0.5mm、樹脂基板104は、厚み約0.4mm、BGA111は、直径50μm、マザー基板は、厚み約1mmのものを用いた。

10

#### 【0048】

実施例2として、上記実施例1で、シリコン基板103に、放熱ビア電極113がなく、導電性高放熱材料106がない場合とした。

#### 【0049】

実施例3として、上記実施例1で、シリコン基板103に、凹凸部120がなく、放熱パターン114がなく、導電性高放熱材料106がない場合とした。

#### 【0050】

比較例として、上記実施例で、凹凸部120がなく、貫通電極112がなく、絶縁性高放熱材料105がなく、放熱パターン114がなく、放熱ビア電極113がなく、導電性高放熱材料106がない場合とした。

20

#### 【0051】

LSI101を動作させ、比較例の構造で、LSI101の温度が、80で一定になった条件において、実施例1では、LSI101は、65、実施例2では、70、実施例3では75で一定となった。実施例2では、放熱パターン114と凹凸部120が主体的に放熱に寄与し、実施例3では、貫通電極112、放熱ビア電極113の効果が主体的に放熱に寄与したと考えられる。シリコン材料は熱伝導がよく、放熱ビア電極113や導電性高放熱材料106よりも放熱効果が高い。

#### 【0052】

図6を参照して、半導体実装構造体100の製造方法について説明する。

30

先ず図6(a)に示すように、シリコン基板103に、半導体素子実装用の実装パターン115が形成される。実装パターン115は、シリコン基板103上にシリコン酸化膜などの絶縁膜を形成し、スパッタでCuやAlなどの成膜を施し、フォトリソでパターンニングをした後に、ドライエッチング、またはウェットエッチングでパターン形成される。その上に、CVDなどで絶縁膜を形成し、スパッタ、フォトリソを繰り返し、多層パターンが形成される。シリコン基板103の表層の内部配線には、放熱パターン114(図4)を形成し、シリコン基板103の端面107と結合し、信号ラインとなる貫通電極112とは独立させる。

#### 【0053】

次に、図6(b)に示すように、シリコン基板103に貫通電極112A、放熱ビア電極113A、およびBGA111Dが形成されて、シリコン基板103が完成される。具体的には、貫通電極112Aおよび放熱ビア電極113Aは、シリコン基板(103)にドライエッチやレザ-などで孔を開け、CVDなどで絶縁処理した後に、Cu/Tiスパッタ、Cuメッキで導電経路および放熱経路が形成される。なお、BGA111Dは、ハンダボールが印刷搭載され、リフロ-を通して形成される。

40

#### 【0054】

次に、図6(c)に示すように、LSI101がシリコン基板103上にフリップチップ実装される。具体的には、フリップチップ接合は、シリコン基板103にハンダクリムが供給された、もしくはLSI101またはシリコン基板103にパンプ電極109が形成された、シリコン基板103にフラックスが供給した後に実装される。実装時に加熱

50

し、ハンダを溶融接合する場合と、実装後にリフロ - などを通してハンダを溶融接合する場合がある。また、シリコン基板 103 に、Auスパッタやメッキを施し、LSI101 側にAuバンプを形成したAu - Auの熱圧接接合や、樹脂を介在させた状態での圧接接合もフリップ素子実装手段として選択できる。

#### 【0055】

次に図6(d)に示すように、LSI101がフリップチップ実装されたシリコン基板103が樹脂基板104に実装される。具体的には、樹脂基板104にスクリ -ン印刷でハンダが供給され、樹脂基板104とシリコン基板103がアライメント後に、樹脂基板104にシリコン基板103(LSI101)を実装する。これをリフロ - に通すことによってハンダが溶融して、シリコン基板103と樹脂基板104とが接合する。

10

#### 【0056】

次に、図6(e)に示すように、シリコン基板103と樹脂基板104との実装間のギャップが絶縁性高放熱材料105Bで封止される。具体的には、絶縁性高放熱材料105BとしてはAlN(窒化アルミニウム)などのフィラ - を分散させた1W / mK以上の熱伝導率が高いものが用いられる。

#### 【0057】

次に、図6(f)に示すように、LSI101上が絶縁性高放熱材料105Aで封止される。封止材(絶縁性高放熱材料105A)は、AlNなどのフィラ - を分散させた熱伝導率が高いものが用いられる。

20

#### 【0058】

次に、図6(g)に示すように、絶縁性高放熱材料105A上が導電性高放熱材料106で封止される。導電性高放熱材料はCu、Ag、CNT(カ - ボンナノチュ - ブ)などをペ - スト状に分散させた熱伝導性の10WmK以上のものが用いられる。

#### 【0059】

##### (実施の形態2)

図7に第2の実施の形態に係る半導体実装構造体100'を示す。半導体実装構造体100'は、半導体実装構造体100における導電性高放熱材料106が導電性高放熱材料106'に置き換えられて構成されている。上述のように、半導体実装構造体100においては、導電性高放熱材料106によって、シリコン基板103、絶縁性高放熱材料105、およびBGA111Dが、樹脂基板104上に封止されている。つまり、絶縁性高放熱材料105およびシリコン基板103は、導電性高放熱材料106で覆われて周囲の空気と遮断されている。

30

#### 【0060】

半導体実装構造体100'においては、導電性高放熱材料106'は、絶縁性高放熱材料105およびシリコン基板103を覆うことなく、シリコン基板103の下部からBGA111Dを、樹脂基板104上に封止している。なお、シリコン基板103は絶縁性高放熱材料105に封止されているので、半導体実装構造体100'も、外気に対して封止されている。

#### 【0061】

つまり、シリコン基板103および絶縁性高放熱材料105は、導電性高放熱材料106に覆われることなく、周囲の空気に対して暴露されている。結果、シリコン基板103に伝導した熱は、凹凸部120の表面層Lsを介して導電性高放熱材料106ではなく、直接空気に放出される。

40

#### 【0062】

なお、上述のように、凹凸部120の放熱性は表面積、及び、熱交換性に比例するため、ピッチPが細かく、長さLが長いほど表面積が増大し、放熱効果が向上する。ピッチPが半分になれば表面積Aは2倍になる。長さLに比例し、表面積Aは増加する。しかしながらピッチPが小さすぎると空気の入れ替えが円滑にできなくなり、熱交換性が低下するため、放熱性が低下する。従って、ピッチPが10μm未満は用いることはできない。また、ピッチPを100μm以上にすると、現実の実装構造体の大きさが約数cmであるこ

50

とから、表面積が少なく、放熱性が小さい。

【産業上の利用可能性】

【0063】

本発明は、シリコン基板に実装および結線された半導体を絶縁樹脂で封止して構成された半導体実装構造体に利用することができる。

【符号の説明】

【0064】

100、100'、100c 半導体実装構造体

101 L S I

103 シリコン基板

10

104 樹脂基板

105 絶縁性高放熱材料

106 導電性高放熱材料

107 シリコン基板端面

109 バンプ電極

110 信号ライン

111、111A、111B、111C、111D、111E B G A

112、112A、112B 貫通電極

113、113A、113B 放熱ビア電極

114 放熱パターン

20

115 実装パターン

11 インタ - ポ - ザ

16 マザーボード

22 回路形成面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 23/28

(56)参考文献 特開2005-243763(JP,A)

特開平06-169029(JP,A)

特開2004-221248(JP,A)

特開2007-067407(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01L 23/12 - 23/15

H 01L 23/28

H 01L 23/32

H 01L 23/36