(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6324992号

(P6324992)

(45) 発行日 平成30年5月16日(2018.5.16)

(24) 登録日 平成30年4月20日(2018.4.20)

(51) Int.Cl.

H03F 3/24 (2006.01)

F 1

H03F 3/24

請求項の数 14 (全 18 頁)

(21) 出願番号 特願2015-549747 (P2015-549747)

(86) (22) 出願日 平成25年12月19日 (2013.12.19)

(65) 公表番号 特表2016-501502 (P2016-501502A)

(43) 公表日 平成28年1月18日 (2016.1.18)

(86) 國際出願番号 PCT/US2013/076748

(87) 國際公開番号 WO2014/100512

(87) 國際公開日 平成26年6月26日 (2014.6.26)

審査請求日 平成28年11月22日 (2016.11.22)

(31) 優先権主張番号 13/720,884

(32) 優先日 平成24年12月19日 (2012.12.19)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】マルチステージ増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電源電圧が閾値電圧より大きい場合に出力において出力信号を搬送するように構成された増幅器出力ステージの第1のパス、ここで前記第1のパスの少なくとも一部は、前記第1の電源電圧が前記閾値電圧と等しいまたはより小さい場合に前記出力から絶縁される、および、

前記第1の電源電圧が前記閾値電圧と等しいまたはより小さい場合に前記出力信号を前記出力に搬送するように構成された前記増幅器出力ステージの第2のパス、

を備え、前記第2のパスの少なくとも一部は、前記増幅器出力ステージにおいて受信された前記第1の電源電圧が前記閾値電圧より大きい場合に前記出力から絶縁され、前記増幅器は、前記第1のパスと前記第2のパスのうちの1つから前記出力信号を搬送することから他方のパスに前記出力信号を搬送することへの遷移を制御するためのバイアシング回路をさらに備える、装置。

## 【請求項 2】

前記第1のパスは、前記第1の電源電圧と前記出力の間に接続された第1のトランジスタと、第2の電源電圧と前記出力の間に接続された第2のトランジスタを含み、前記第2のパスは、前記第2のトランジスタと、前記第1の電源電圧と前記出力の間に接続された第3のトランジスタを含む、請求項1に記載の装置。

## 【請求項 3】

前記第3のトランジスタへフィードバックバイアス電流制御パスを提供するための少な

くとも 1 つのトランジスタ、および、

前記第 3 のトランジスタのゲートへ駆動信号を搬送するための少なくとも 1 つのトランジスタ、

をさらに備える、請求項 2 に記載の装置。

**【請求項 4】**

前記第 3 のトランジスタは、前記第 1 のトランジスタの第 1 の端子に接続された第 1 の端子と前記第 1 のトランジスタの第 2 の端子に接続された第 2 の端子を有し、かつ、前記第 1 の電源電圧が前記閾値電圧より小さいまたは等しい場合に導通するように構成された、請求項 2 に記載の装置。

**【請求項 5】**

前記第 3 のトランジスタと前記第 2 のトランジスタは、前記第 1 の電源電圧が実質的にゼロボルトの場合に導通状態で動作するように構成される、請求項 2 に記載の装置。

**【請求項 6】**

前記第 1 のトランジスタは、前記第 1 の電源電圧が前記閾値電圧より小さいまたは等しい場合に非導通状態になるように構成される、請求項 2 に記載の装置。

**【請求項 7】**

前記負の電源電圧と電流ソースの間に接続され、かつ、前記第 3 のトランジスタへフィードバックバイアス電流制御バスを提供するように構成された第 4 のトランジスタをさらに備える、請求項 2 に記載の装置。

**【請求項 8】**

前記第 3 のトランジスタのゲートへ駆動信号を搬送するように構成された複数のトランジスタをさらに備える、請求項 2 に記載の装置。

**【請求項 9】**

前記第 3 のトランジスタは、前記第 1 のトランジスタのソースと前記第 1 の電源電圧に接続されたドレイン、および、前記第 1 のトランジスタのドレインと前記出力に接続されたソースを有する、請求項 2 に記載の装置。

**【請求項 10】**

前記第 3 のトランジスタのゲートは、第 1 の駆動トランジスタのドレインと第 2 の駆動トランジスタのドレインの間に接続される、請求項 2 に記載の装置。

**【請求項 11】**

前記バイアシング回路は、前記增幅器出力ステージに静止電流を設定するように構成される、請求項 1 に記載の装置。

**【請求項 12】**

前記バイアシング回路は、第 1 のトランジスタを経由する電流をレプリケートする第 1 のスケールされた電流と、第 2 のトランジスタを経由する電流をレプリケートする第 2 のスケールされた電流と、第 3 のトランジスタを経由する電流をレプリケートする第 3 のスケールされた電流を生成するように構成される、請求項 11 に記載の装置。

**【請求項 13】**

前記バイアシング回路は、前記第 1 のスケールされた電流に基づく第 1 のバイアス電圧と、前記第 2 のスケールされた電流と前記第 3 のスケールされた電流に基づく第 2 のバイアス電圧を生成するように構成される、請求項 12 に記載の装置。

**【請求項 14】**

出力ステージの正の電源電圧が閾値電圧より大きい場合に增幅器の前記出力ステージの第 1 のパスを介して出力ノードにおいて出力信号を搬送すること、

前記出力ステージの前記正の電源電圧が前記閾値電圧より小さいまたは等しい場合に前記出力ノードから前記第 1 のパスの少なくとも一部を絶縁すること、

前記出力ステージの前記正の電源電圧が前記閾値電圧より小さいまたは等しい場合に前記出力ステージの第 2 の異なるパスを介して前記出力を前記出力に搬送すること、および、

前記出力ステージにおいて受信された前記正の電源電圧が前記閾値電圧より大きい場合

10

20

30

40

50

に前記出力ノードから前記第2の異なるパスの少なくとも一部を絶縁すること、

前記第1のパスと前記第2のパスのうちの1つから前記出力信号を搬送することから他方のパスに前記出力信号を搬送することへの遷移を制御すること、

を備える、方法。

【発明の詳細な説明】

【分野】

【0001】

[0001]本発明は、一般的に、電子増幅器に関する。さらに具体的に、本発明は、低電圧マルチステージ増幅器に関する実施例を含む。

【背景】

10

【0002】

[0002]無線通信システムは、音声、映像、データ、などの様々なタイプの通信コンテンツを提供するために広く展開されている。これらのシステムは、1つまたは複数の基地局と多数の無線通信デバイスの同時通信を支援することができる多元接続システムであり得る。

【0003】

[0003]無線通信デバイスは、一般にバッテリによって動作する。無線通信デバイスの機能がより複雑になるにつれて、バッテリの寿命を最大にする無線通信デバイスが望まれている。無線通信デバイスの電力消費量を低減することによって、バッテリの寿命が増大し得る。電力消費を低下するための1つの方法は、無線通信デバイス内でより効率の良い増幅器を使用することである。例えば、より低い電源電圧を使用する増幅器は、より高い電源電圧を使用する増幅器よりも効率が良いはずである。利益は、必要な利得を提供する一方で、より低い電源電圧を使用する増幅器によって実現され得る。

20

【0004】

[0004]マルチステージ増幅器の電力消費量を低減させることへのニーズが存在する。さらに具体的に、マルチステージ増幅器の出力ステージの電源電圧を低下させる実施例へのニーズが存在する。

【図面の簡単な説明】

【0005】

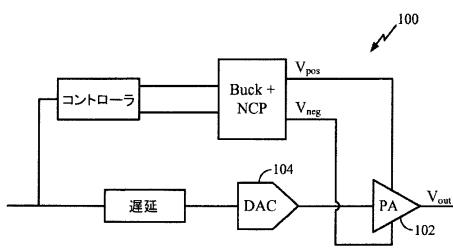

【図1】[0005]図1は、正の電源電圧と負の電源電圧を受けるように構成された増幅器を含むデバイスである。

30

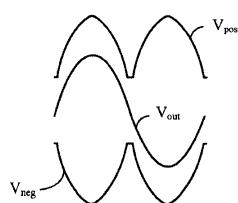

【図2】[0006]図2は、増幅器への正の電源電圧と該増幅器への負の電源電圧の波形を示すプロットである。

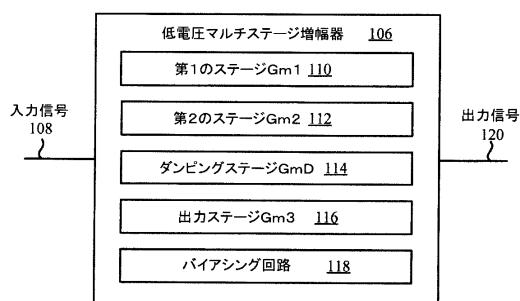

【図3】[0007]図3は、マルチステージ増幅器を示すブロック図である。

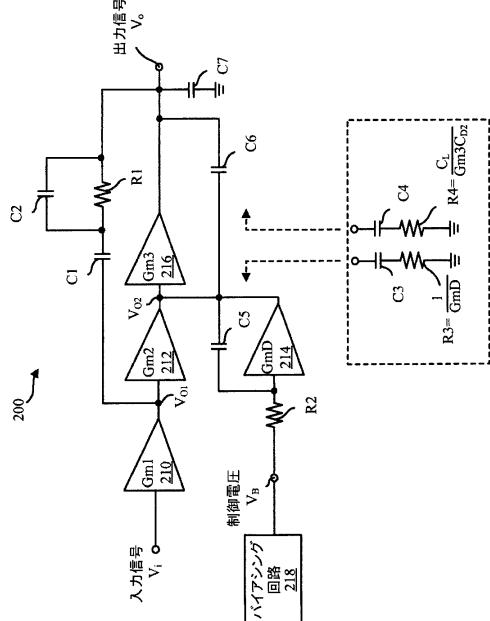

【図4】[0008]図4は、マルチステージ増幅器を示す。

【図5】[0009]図5は、本発明の例示的な実施例にしたがった低電圧マルチステージ増幅器を示す。

【図6】[0010]図6は、本発明の例示的な実施例にしたがった低電圧マルチステージ増幅器のバイアシング回路を示す。

【図7】[0011]図7は、低い電源電圧で動作するように構成された出力ステージを含むマルチステージ増幅器のシミュレーション結果を示すプロットである。

40

【図8】[0012]図8は、本発明の例示的な実施例にしたがった方法を示すフローチャートである。

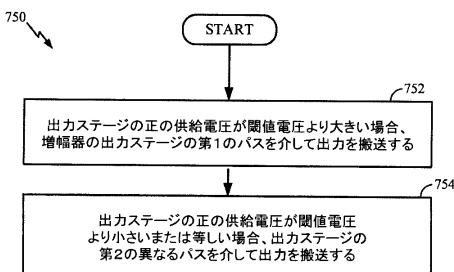

【図9】[0013]図9は、本発明の例示的な実施例にしたがった別の方法を示すフローチャートである。

【詳細な説明】

【0006】

[0014]添付の図面に関連して下記で説明される詳細な説明は、本発明の例示的な実施例の説明を意図しており、本発明が実施され得る実施例のみを表すことを意図するものではない。この説明を通じて用いられる用語「例示的な」は、「具体例、例、または例示とし

50

ての役割を果たすこと」を意味しており、他の例示的な実施例よりも好適または有利であると必ずしも解釈されるべきではない。詳細な説明は、本発明の例示的な実施例の全体を通じた理解を提供するための特定の詳細を含む。本発明の例示的な実施例がこれらの特定の詳細なしで実施されることは、当業者にとって明らかであろう。いくつかの例において、周知の構造およびデバイスは、ここで提示された例示的な実施例の新規性を曖昧にすることを回避するためにブロック図形式で示される。

#### 【0007】

[0015]例示的な実施例は、ここに記載されたように、マルチステージ増幅器の出力ステージの電源電圧を最小にするための実施例に関するものであり、よってマルチステージ増幅器の電圧効率を高める。本発明の様々な例示的な実施例にしたがって、マルチステージ増幅器は、低電源電圧（例えば、+ / - 0 . 1 ボルト）で動作するように構成された出力ステージを含み得る。例示のためだけに、出力ステージは、正の電源電圧と出力に接続された第1のトランジスタと負の電源電圧と出力に接続された第2のトランジスタを含み得る。出力ステージはまた、第1のトランジスタの第1の端子に接続された第1の端子と第1のトランジスタの第2の端子に接続された第2の端子を有し、正の電源電圧が閾値より下回る場合に作動されるように構成された第3のトランジスタを含み得る。

#### 【0008】

[0016]図1は、デジタル・アナログ・コンバータ（D A C）104からアナログ信号を受信するように構成された電力増幅器（P A）102を含むデバイス100のブロック図である。さらに、P A 102は、正の電源電圧 $V_{p.o.s}$ と負の電源電圧 $V_{n.e.g}$ を受け取り、ならびに出力電圧 $V_{o.u.t}$ を出力するように構成される。図2は、増幅器の正の電源電圧 $V_{p.o.s}$ 、負の電源電圧 $V_{n.e.g}$ 、および出力電圧 $V_{o.u.t}$ の波形を示す。当業者によって理解されるように、従来の増幅器（例えば、電力増幅器）の電力出力ステージは、およそ0 . 9 ボルトまたはそれより大きい正の電源電圧（例えば、正の電源電圧 $V_{p.o.s}$ ）とおよそ-0 . 9 ボルトまたはそれより小さい負の電源電圧（例えば、負の電源電圧 $V_{n.e.g}$ ）を必要とし得る。

#### 【0009】

[0017]図3は、クラスA B増幅器、クラスG増幅器、クラスH増幅器、レール切替え増幅器、無限可変電源レールを有する増幅器、またはそれらの任意の組み合わせを備え得るマルチステージ増幅器106を示すブロック図である。さらに、マルチステージ増幅器106は、演算増幅器、電力増幅器、分配増幅器、またはそれらの任意の組合せを備え得る。図1に示されたような、電力増幅器102は、マルチステージ増幅器106を備え得る。

#### 【0010】

[0018]マルチステージ増幅器106は複数の増幅ステージを含む。さらに具体的には、例えば、マルチステージ増幅器106は、第1のステージG m 1 110、第2のステージG m 2 112、ダンピングステージG m D 114、および出力ステージG m 3 116を含む。複数の増幅ステージは、入力信号108を増幅し、および最小限のひずみと最小限の電力消費量を用いて増幅出力信号120を生成することをマルチステージ増幅器106に可能にし得る。

#### 【0011】

[0019]クラスB増幅器は、入力信号108の波形サイクルの半分のみを増幅し得る。増大したひずみを犠牲にして、クラスB増幅器は高い効率を有し（すなわち、クラスB増幅器の増幅エレメントが半分の時間オフに切り替えられるため）、電力消費量が減少する結果となる。相補的な対を用いることによって、複数のクラスB増幅器は、入力信号の両半分を増幅するために用いられ得、その結果ひずみが減少する。しかし、クラスB増幅器の相補的な対は、クラスB増幅器のうちの1つがターンオフされかつ別のクラスB増幅器の電源がターンオンされる時にひずみの増大が認識されるクロスオーバひずみの影響を受ける可能性がある。

#### 【0012】

10

20

30

40

50

[0020]クロスオーバひずみを除去するための方法の1つにはクラスA B増幅器の使用がある。クラスA B増幅器において、各デバイスは、信号の半分を増幅し、他の半分の間に比較的少量導通し得る（すなわち、シャットオフするのではなく）。ひずみの量は、信号が無い（すなわち、静止電流（quiescent current））場合、両方のデバイスを経由するスタンディング電流に依存する。静止電流はバイアス電圧に直接依存する。クラスA B増幅器は、クラスB増幅器より低い効率を有するが、高められた直線性を有する。

#### 【0013】

[0021]クラスGおよびクラスH増幅器は、ひずみを増大することなく高められた効率を得ることによって、クラスA B出力ステージを拡張する。クラスG増幅器において、レールの切り替えは効率を高めるために用いられ、ならびに異なる電源電圧は、出力信号120における振幅に対応するために用いられ得る。一般に、出力ステージGm3 116が最大の電流振幅を認識すると、それによって最も高い効率を得ることができるので、レールの切り替えは、出力ステージGm3 116において用いられる。クラスG増幅器に関して、複数のディスクリート電源電圧が用いられ得る。クラスH増幅器に関して、無限可変電源電圧が出力信号120に電源電圧をマッチングすることによって用いられ得る。出力信号120に電源電圧をマッチングさせることはエンベロープトラッキングと称される場合もある。

#### 【0014】

[0022]マルチステージ増幅器106は、出力ステージGm3 116の静止電流を設定し得るバイアシング回路（circuitry）118をさらに含み得、それによって出力ステージGm3 116の適切な動作に必要な最小のヘッドルームを供給する。下記でさらに詳しく説明されるように、バイアシング回路118は、制御電圧を、ダンピングステージGmD114を介して出力ステージGm3 116へ提供し得る。

#### 【0015】

[0023]図4は、本発明の例示的な実施例にしたがったマルチステージ増幅器200を示すブロック図である。例示のみのために、マルチステージ増幅器200は、図3のマルチステージ増幅器106を備え得る。マルチステージ増幅器200は、バイアシング回路218、第1のステージGm1 210、第2のステージGm2 212、ダンピングステージGmD214、および出力ステージGm3 216を含み得る。第1のステージGm1 210は、入力信号V<sub>i</sub>を受信しおよび第2のステージGm2 212の入力に提供され得る電圧V<sub>o</sub>1を出力し得る。第2のステージGm2 212は、出力ステージGm3 216の入力に提供され得る電圧V<sub>o</sub>2を出力し得る。出力ステージGm3 216は、出力信号V<sub>o</sub>を出力し得る。出力ステージGm3 216の出力は基準電圧に接続され得、それはキャパシタC7を介して、負の電源電圧を備え得る。

#### 【0016】

[0024]第1のステージGm1 210の出力はまたキャパシタC1に接続され得、それは並列にレジスタR1とキャパシタC2の両方に接続され得る。さらに、レジスタR1とキャパシタC2は、出力ステージGm3 216の出力に接続され得る。第2のステージGm2 212の出力は、キャパシタC6を介する出力ステージGm3 216の出力ダンピングステージGmD214の出力のそれぞれにさらに接続され得る。第2のステージGm2 212の出力はまた、キャパシタC5を介してダンピングステージGmD214の入力にも接続され得る。

#### 【0017】

[0025]バイアシング回路218の出力は、レジスタR2を介してダンピングステージGmD214の入力に接続され得、および制御電圧V<sub>B</sub>を出力し得る。バイアシング回路218への追加のフィードバック（図4には図示されない）は、制御電圧V<sub>B</sub>の生成を容易にするために用いられ得、それは、レジスタR2とダンピングステージGmD214を通過し得、出力ステージGm3 216の動作に必要な適切な静止電流を生成し得る。

#### 【0018】

[0026]ダンピングステージGmD214の出力からダンピングステージGmD214の

10

20

30

40

50

入力へのインピーダンスはキャパシタ C 3 によって近似され得、それが負の電源電圧にさらに接続されるレジスタ R 3 に接続される。ダンピングステージ G m D 2 1 4 の出力からマルチステージ増幅器 2 0 0 の出力までのインピーダンスはキャパシタ C 4 によって近似され得、それが負の電源電圧にさらに接続されるレジスタ R 4 に接続される。ダンピングステージ G m D 2 1 4 、レジスタ R 2 、およびキャパシタ C 5 によって形成されたダンピング回路は、

【数 1】

$$R3 \approx \frac{1}{GmD}$$

10

【0019】

のダンピングレジスタンスと

【数 2】

$$C3 \approx GmD * R2 * C5$$

【0020】

の等価のブロッキングキャパシタンスをエミュレートする。

20

【0021】

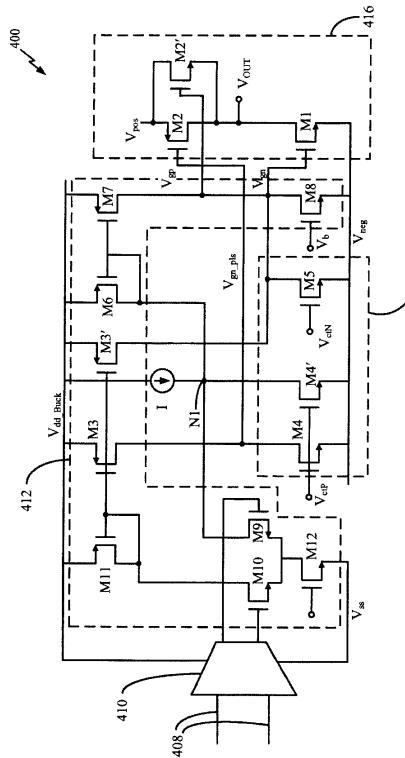

[0027]図 5 は、本発明の例示的な実施例にしたがったマルチステージ増幅器 4 0 0 を示す回路図である。マルチステージ増幅器 4 0 0 は、図 3 に示されたマルチステージ増幅器 1 0 6 を備え得る。マルチステージ増幅器 4 0 0 は、第 1 のステージ 4 1 0 、第 2 のステージ 4 1 2 、ダンピングステージ 4 1 4 、および出力ステージ 4 1 6 を含む。マルチステージ増幅器 4 0 0 はまた、バイアシング回路 5 0 0 を含み得る（図 5 には不図示、図 6 を参照のこと）。制御電圧 V<sub>c t p</sub> と制御電圧 V<sub>c t N</sub> は、バイアシング回路 5 0 0 から提供され得る（図 6 を参照のこと）。

【0022】

[0028]正の電源電圧 V<sub>d d \_ B u c k</sub> と負の電源電圧 V<sub>s s</sub> に接続される第 1 のステージ 4 1 0 は、入力信号 4 0 8 を受信し得る。1つの例示的な実施例にしたがって、正の電源電圧 V<sub>d d \_ B u c k</sub> と電源電圧 V<sub>s s</sub> （例えば、接地電圧または負の電源電圧）は、アナログ供給（すなわち、出力信号 V<sub>o u T</sub> によって変化しない）を構成し得る。第 1 のステージ 4 1 0 の出力は、p チャネルトランジスタ M 1 1 と n チャネルトランジスタ M 1 0 を含むカレントミラーに接続され得る。p チャネルトランジスタ M 1 1 のソースは正の電源電圧 V<sub>d d \_ B u c k</sub> に接続され得、ならびに p チャネルトランジスタ M 1 1 のゲートは、p チャネルトランジスタ M 1 1 のドレインに接続され得る。p チャネルトランジスタ M 1 1 のドレインはまた、n チャネルトランジスタ M 1 0 のドレインに接続され得る。さらに、n チャネルトランジスタ M 1 0 のソースは、n チャネルトランジスタ M 1 2 のドレインに接続され得、ならびに n チャネルトランジスタ M 1 0 のゲートは、第 1 のステージ 4 1 0 の出力に接続され得る。n チャネルトランジスタ M 1 2 のゲートはバイアス電圧を受信するように構成され、ならびに n チャネルトランジスタ M 1 2 のソースは負の電源電圧 V<sub>s s</sub> に接続される。さらに、増幅器 4 0 0 は、第 1 のステージ 4 1 0 の出力に接続されるゲート、ノード N 1 に接続されるドレイン、および n チャネルトランジスタ M 1 0 のソースと n チャネルトランジスタ M 1 2 のドレインに接続されるソースを有する n チャネルトランジスタ M 9 を含む。

30

【0023】

[0029]第 2 のステージ 4 1 2 は、p チャネルトランジスタ M 3 と p チャネルトランジスタ M 3' を含む。p チャネルトランジスタ M 3 のソースと p チャネルトランジスタ M 3' のソースはそれぞれ、正の電源電圧 V<sub>d d \_ B u c k</sub> に接続され得る。さらに、p チャネ

40

50

ルトランジスタM3のゲートとpチャネルトランジスタM3'のゲートはそれぞれ、pチャネルトランジスタM11のゲートに接続され得る。

#### 【0024】

[0030]ダンピングステージ414は、出力ステージ416のためのダンピングステージおよび電流源である。従って、ダンピングステージ414はまた、供給ステージと称され得る。マルチステージ増幅器400に必要なダンピングを提供し得るダンピングステージ414は、第2のステージ412のための電流源として再利用され得る。ダンピングステージ414は、nチャネルトランジスタM4、nチャネルトランジスタM4'、およびnチャネルトランジスタM5を含み得る。ダンピングステージ414はまた、nチャネルトランジスタM4、nチャネルトランジスタM4'、およびnチャネルトランジスタM5のうちの1つまたは複数に接続される様々なキャパシタおよび/またはレジスタを含み得ることが留意される。nチャネルトランジスタM4のゲートとnチャネルトランジスタM4'のゲートは、制御電圧 $V_{c_{tP}}$ に接続され得、ならびにnチャネルトランジスタM5のゲートは、制御電圧 $V_{c_{tN}}$ に接続され得る。バイアシング回路500(図6を参照のこと)によって提供され得る制御電圧 $V_{c_{tP}}$ と制御電圧 $V_{c_{tN}}$ は、出力ステージ416の適切な動作に必要とされる静止電流を設定し得る。

10

#### 【0025】

[0031]nチャネルトランジスタM4のドレインは、pチャネルトランジスタM3のドレインに接続され得、ならびにnチャネルトランジスタM4のソースは、可変負の電源電圧 $V_{n_{eg}}$ に接続され得る。nチャネルトランジスタM4'のドレインは電流源Iに接続され得、それは正の電源電圧 $V_{dd\_Buck}$ にさらに接続される。nチャネルトランジスタM4'のソースは、可変負の電源電圧 $V_{n_{eg}}$ に接続され得る。さらに、nチャネルトランジスタM5のドレインは、pチャネルトランジスタM3'のドレインに接続され得、ならびにnチャネルトランジスタM5のソースは、可変負の電源電圧 $V_{n_{eg}}$ に接続され得る。

20

#### 【0026】

[0032]出力ステージ416は、pチャネルトランジスタM2とnチャネルトランジスタM1を含む。pチャネルトランジスタM2のソースは、可変正の電源電圧 $V_{p_{os}}$ に接続され得、ならびにpチャネルトランジスタM2のドレインはnチャネルトランジスタM1のドレインに接続され得る。pチャネルトランジスタM2のドレインはまた、出力信号 $V_{out}$ に接続され得、ならびにpチャネルトランジスタM2のゲートは、ダンピングステージ414のnチャネルトランジスタM4のドレインに接続され得る。pチャネルトランジスタM2のゲートにおける電圧 $V_{g_p}$ は、バイアシング回路500(図6を参照のこと)に提供され得る。nチャネルトランジスタM1のソースは、可変負の電源電圧 $V_{n_{eg}}$ に接続され得、ならびにnチャネルトランジスタM1のゲートは、ダンピングステージ414のnチャネルトランジスタM5のドレインとpチャネルトランジスタM3'のドレインに接続され得る。nチャネルトランジスタM1のゲート電圧 $V_{g_n}$ は、バイアシング回路500(図6を参照)に提供され得る。

30

#### 【0027】

[0033]出力ステージ416は、可変正の電源電圧 $V_{p_{os}}$ に接続されたドレインおよび出力信号 $V_{out}$ とnチャネルトランジスタM1のドレインのそれぞれに接続されたソースを有するnチャネルトランジスタM2'をさらに含む。したがって、出力ステージ416は、pチャネルトランジスタM2とnチャネルトランジスタM1を含む出力バスとnチャネルトランジスタM2'とnチャネルトランジスタM1を含む別の出力バスを含み、ここにおいて、nチャネルトランジスタM2'はpチャネルトランジスタM2と並列である。

40

#### 【0028】

[0034]nチャネルトランジスタM2'のゲートは、pチャネルトランジスタM7のドレインとnチャネルトランジスタM8のドレインのそれぞれに接続される。さらに、nチャネルトランジスタM8のソースは、可変負の電源電圧 $V_{n_{eg}}$ に接続され、ならびにnチ

50

ヤネルトランジスタM 8 のゲートは、制御電圧  $V_b$  を受信するように構成される。さらに、p チャネルトランジスタM 7 のソースは、正の電源電圧  $V_{dd\_Buck}$  に接続され、ならびに p チャネルトランジスタM 7 のゲートは正の電源電圧  $V_{dd\_Buck}$  に接続されたソースを有する p チャネルトランジスタM 6 のゲートに接続される。P チャネルトランジスタM 6 は、ノードN 1 と p チャネルトランジスタM 6 のゲートに接続されたドレインをさらに含む。トランジスタM 6 、M 7 、M 8 、およびM 9 は、n チャネルトランジスタM 2' と n チャネルトランジスタM 1 を含む出力バスを駆動するように構成されることが留意される。n チャネルトランジスタM 4' は、n チャネルトランジスタM 2' へフィードバックバイアス電流制御バスを提供し、ならびに出力ステージ4 1 6 に静止電流を設定するように構成されることがさらに留意される。

10

## 【0029】

[0035]当業者によって理解されるように、電圧効率を実現するために、出力ステージ4 1 6 は最小の電源電圧を用いて動作されるべきである。さらに、平均比に対する高いピークが原因で、低およびミッドレンジの電圧における効率が非常に重要であり、そのため、非常に低い電圧動作が望まれる。当業者によって理解されるように、マルチステージ増幅器4 0 0 の p チャネルトランジスタM 2 と n チャネルトランジスタM 1 の適切な動作に必要とされる最小のヘッドルームは、

## 【数3】

20

$$V_{pos} - V_{neg} > Vgs_{M2} + Vdsat_{M4}$$

## 【0030】

であり、そこにおいて、

## 【数4】

$$Vgs_{M2}$$

30

## 【0031】

は、p チャネルトランジスタM 2 のゲートからソースまでの電圧であり、ならびに

## 【数5】

$$Vdsat_{M4}$$

## 【0032】

は、飽和動作に合わせるために必要とされる n チャネルトランジスタM 4 のドレインからソースまでの最小電圧であり、それによって n チャネルトランジスタM 4 が三極管領域で動作するのを防ぐ。

40

## 【0033】

[0036]本発明の例示的な実施例にしたがって、増幅器5 0 0 の電源電圧が閾値を超えて低下する場合（すなわち、p チャネルトランジスタM 2 が導通する値を超えて低下する）場合、n チャネルトランジスタM 2' が、増幅器5 0 0 の継続動作のために作動され得る。例えば、

## 【数6】

$$V_{pos} - V_{neg} < Vgs_{M2} + Vdsat_{M4}$$

## 【0034】

である場合、 $p$ チャネルトランジスタM2がターンオフされ得、 $n$ チャネルトランジスタM2'がターンオンされ得、それによって、出力ステージGm3 416は、最小電源電圧を用いて動作を継続し得る。1つの例として、 $n$ チャネルトランジスタM2' と  $n$ チャネルトランジスタM1は、可変正の電源電圧  $V_{pos}$  と可変負の電源電圧  $V_{neg}$  のそれぞれの絶対値が0.40ボルトより小さいときにそれぞれ導通し得る。さらにより具体的な例として、 $n$ チャネルトランジスタM2' と  $n$ チャネルトランジスタM1は、可変正の電源電圧  $V_{pos}$  が実質的に0.1ボルトに等しいかそれより大きく、および可変負の電源電圧  $V_{neg}$  が実質的に-0.1ボルトに等しいかそれより小さい時にそれぞれ導通し得る。 $n$ チャネルトランジスタM2' と  $n$ チャネルトランジスタM1のそれぞれは、可変正の電源電圧  $V_{pos}$  と可変負の電源電圧  $V_{neg}$  が実質的にゼロに等しい場合でさえも導通し得ることが留意される。従って、可変正の電源電圧  $V_{pos}$  と可変負の電源電圧  $V_{neg}$  に関する最小値は、バイアシングに必要とされない。当業者によって理解されるように、増幅器500における電力電源レールを減少させることによって、増幅器500の電力消費量が低減され得る。

## 【0035】

[0037]図2および5を参照して、増幅器400の電力出力ステージは、おおよそ0.1ボルトまたはそれより大きい正の電源電圧（例えば、正の電源電圧  $V_{pos}$ ）とおおよそ-0.1ボルトまたはそれより小さい負の電源電圧（例えば、負の電源電圧  $V_{neg}$ ）を必要とし得る。しかし、上述したとおり、 $n$ チャネルトランジスタM2' と  $n$ チャネルトランジスタM1を含む出力ステージ内のバスは、可変正の電源電圧  $V_{pos}$  と可変負の電源電圧  $V_{neg}$  が実質的にゼロに等しい場合でさえも導通し得る。

## 【0036】

[0038]当業者によって理解されるように、増幅器400は、出力ステージ416において最小電源電圧を必要とせず、それによって、+/-0.45ボルトの電源電圧を必要とし得る従来の増幅器と比較して、増幅器400は、出力ステージ416における実質的な（例えば、4.5X）電力削減を可能にし得る。

## 【0037】

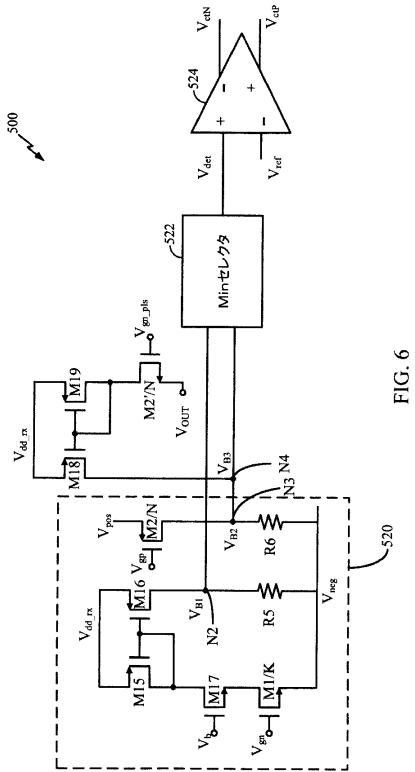

[0039]当業者によって理解されるように、マルチステージ増幅器をバイアシングするように構成された回路は、マルチステージ増幅器の出力ステージにおいて静止電流を保持するように構成され得る。図6は、本発明の例示的な実施例にしたがったバイアシング回路500を示す。バイアシング回路500は、 $n$ チャネルトランジスタM5（図5を参照のこと）のゲートまで搬送される制御電圧  $V_{ctN}$  および  $n$ チャネルトランジスタM4のゲートと  $n$ チャネルトランジスタM4'のゲートまで搬送される制御電圧  $V_{ctp}$  を生成するように構成される。バイアシング回路500は、出力ステージ416の静止電流を設定するため、および出力ステージ416における $p$ チャネルトランジスタM2と  $n$ チャネルトランジスタM2'の間の遷移を設定するために用いられ得ることが留意される。バイアシング回路518は、レプリカ（再現、replica）電流ステージ520、ミニマム・セレクタ522、および誤差増幅器524を含む。

## 【0038】

[0040]レプリカ電流ステージ520は、 $p$ チャネルトランジスタM15、 $p$ チャネルトランジスタM16、 $p$ チャネルトランジスタM2/N、 $n$ チャネルトランジスタM17、および  $n$ チャネルトランジスタM1/Kを含み得る。 $p$ チャネルトランジスタM2/Nのサイズは、整数Nによって分割された $p$ チャネルトランジスタM2（図5を参照のこと）のサイズに実質的に等しい。 $n$ チャネルトランジスタM1/Kのサイズは、整数Kによつ

10

20

30

40

50

て分割された n チャネルトランジスタ M 1 のサイズに実質的に等しい（図 5 を参照）。

【 0 0 3 9 】

[0041] p チャネルトランジスタ M 1 5 のソースと p チャネルトランジスタ M 1 6 のソースはそれぞれ正のレール電圧  $V_{d d\_r x}$  に接続され得る。同様に、 p チャネルトランジスタ M 1 5 のゲートは、第 2 の p チャネルトランジスタ M 1 6 のゲート、 p チャネルトランジスタ M 1 5 のドレイン、および n チャネルトランジスタ M 1 7 のドレインのそれぞれに接続され得る。 n チャネルトランジスタ M 1 7 のゲートは電圧  $V_b$  に接続され得、それは、 n チャネルトランジスタ M 1 / K のドレイン電圧を設定するために用いられる任意の電圧であり得る。電圧  $V_b$  は、 n チャネルトランジスタ M 1 / K のドレイン電圧がゼロ信号状態（例えば、 0 . 0 V ）における出力電圧に実質的に近いように設定され得ることが留意される。 n チャネルトランジスタ M 1 7 のソースは、 n チャネルトランジスタ M 1 / K のドレインに接続され得、ならびに n チャネルトランジスタ M 1 / K のゲートは、図 5 の電圧  $V_{g n}$  から構成され得る電圧  $V_{g n}$  に接続され得る。 n チャネルトランジスタ M 1 / K のソースは、可変負の電源レール  $V_{n e g}$  に接続され得る。

10

【 0 0 4 0 】

[0042] p チャネルトランジスタ M 1 6 のドレインは、レジスタ R 5 を介して可変負の電源電圧  $V_{n e g}$  に接続され得る。 p チャネルトランジスタ M 1 6 のドレインにおける電圧は、ノード N 2 におけるバイアス電圧  $V_{B 1}$  を備え得る。当業者によって理解されるように、トランジスタ M 1 （図 5 を参照のこと）を経由して搬送される電流のスケールされたバージョンである電流は、ノード N 2 においてバイアス電圧  $V_{B 1}$  を生成するためにレジスタ R 5 を経由して搬送される。

20

【 0 0 4 1 】

[0043] p チャネルトランジスタ M 2 / N のソースは、可変正の電源レール  $V_{p o s}$  に接続され得、ならびに p チャネルトランジスタ M 2 / N のゲートは、図 5 の電圧  $V_{g p}$  を備え得る電圧  $V_{g p}$  に接続され得る。 p チャネルトランジスタ M 2 / N のドレインは、レジスタ R 6 を介して可変負の電源レール  $V_{n e g}$  に接続され得る。 p チャネルトランジスタ M 2 / N のドレインにおける電圧は、ノード N 3 におけるバイアス電圧  $V_{B 2}$  を備え得る。当業者によって理解されるように、トランジスタ M 2 （図 5 を参照のこと）を経由して搬送される電流のスケールされたバージョンである電流は、ノード N 3 においてバイアス電圧  $V_{B 2}$  を生成するためにレジスタ R 6 を経由して搬送される。

30

【 0 0 4 2 】

[0044] さらに、本発明の例示的な実施例にしたがって、バイアシング回路 500 は、 n チャネルトランジスタ M 2' / N 、 p チャネルトランジスタ M 1 8 および p チャネルトランジスタ M 1 9 を含む。 p チャネルトランジスタ M 1 8 のドレインはノード N 4 に接続され、 p チャネルトランジスタ M 1 8 のソース 正のレール電圧  $V_{d d\_r x}$  に接続され。さらに、 p チャネルトランジスタ M 1 9 のソースは、正のレール電圧  $V_{d d\_r x}$  に接続され、および p チャネルトランジスタ M 1 9 のドレインは、 p チャネルトランジスタ M 1 9 のゲートと n チャネルトランジスタ M 2' / N のドレインのそれぞれに接続される。さらに、 n チャネルトランジスタ M 2' / N のゲートは、電圧  $V_{g n\_p 1 s}$  に接続され、および n チャネルトランジスタ M 2' / N のドレインは、出力電圧  $V_{o u t}$  に接続される。 p チャネルトランジスタ M 2' / N のサイズは、整数 N によって分割された p チャネルトランジスタ M 2' （図 5 を参照のこと）のサイズに実質的に等しくなり得る。

40

【 0 0 4 3 】

[0045] p チャネルトランジスタ M 1 8 のドレインにおける電圧は、ノード N 4 におけるバイアス電圧  $V_{B 3}$  を備え得る。当業者によって理解されるように、トランジスタ M 2' （図 5 を参照のこと）を経由して運ばれる電流のスケールされたバージョンであるレプリカ電流は、ノード N 4 においてバイアス電圧  $V_{B 3}$  を生成するためにレジスタ R 6 を経由して搬送され得る。図 4 の両方のトランジスタ M 2 および M 2' が導通している場合、 p チャネルトランジスタ M 2' / N を介して生成されたレプリカ電流は、ノード N 3 および N 4 に存在するバイアス電圧を生成するために p チャネルトランジスタ M 2 / N を介して

50

生成されたレプリカ電流に加えられ得ることが留意される。

#### 【0044】

[0046] n チャネルトランジスタ M<sub>2'</sub> / N を介する並列電流バスは、正側の静止電流（すなわち、n チャネルトランジスタ M<sub>2'</sub> と p チャネルトランジスタ M<sub>2</sub> のうちの 1 つまたは複数を経由する電流）が保持されることを確実にする。さらに、比較的大きい負の電圧の振幅（例えば V<sub>neg</sub> の絶対値が 0.5 V より大きい）で、正側の静止電流は、p チャネルトランジスタ M<sub>2</sub> によって設定される。中くらいの大きさの負の電圧の振幅で（すなわち、V<sub>neg</sub> の絶対値が 0.4 - 0.5 V である）、正側の静止電流は、p チャネルトランジスタ M<sub>2</sub> と n チャネルトランジスタ M<sub>2'</sub> の両方によって設定される。比較的低い負の電圧の振幅で（例えば、V<sub>neg</sub> の絶対値が 0.4 V より小さい）、正側の静止電流は、n チャネルトランジスタ M<sub>2'</sub> によって設定される。10

#### 【0045】

[0047] 生成されたバイアス電圧の両方（すなわち、バイアス電圧 V<sub>B1</sub> とバイアス電圧 V<sub>B2</sub>、バイアス電圧 V<sub>B1</sub> とバイアス電圧 V<sub>B3</sub>、または、バイアス電圧 V<sub>B1</sub> とバイアス電圧 V<sub>B2</sub> と V<sub>B3</sub> の組合せ）がミニマム・セレクタ 522 に提供され得る。ミニマム・セレクタ 522 は、決定された電圧 V<sub>det</sub> を出力し得、それは、2 つのバイアス電圧が比較的接近している（すなわち、ミニマム・セレクタ・トランジスタ飽和電圧と称されるミニマム・セレクタ 522 で使用されるトランジスタの飽和電圧より小さい）場合、2 つの受信されたバイアス電圧の平均値であり得る。1 つのバイアス電圧が他のバイアス電圧より非常に大きい（例えば、クラス A B 増幅器が高い電流を駆動している）場合、ミニマム・セレクタ 522 は、決定された電圧 V<sub>det</sub> として小さいほうのバイアス電圧を出力し得る。20

#### 【0046】

[0048] 決定された電圧 V<sub>det</sub> は誤差増幅器 460 に提供され得、それは、負のフィードバックに基づいて、制御電圧 V<sub>ctp</sub> と制御電圧 V<sub>ctn</sub> を設定するために、選択されたバイアス電圧（すなわち、決定された電圧 V<sub>det</sub>）を基準電圧 V<sub>ref</sub> と比較し得る。誤差増幅器 460 は、したがって、制御電圧 V<sub>ctp</sub> と制御電圧 V<sub>ctn</sub> を出力し得る。。

#### 【0047】

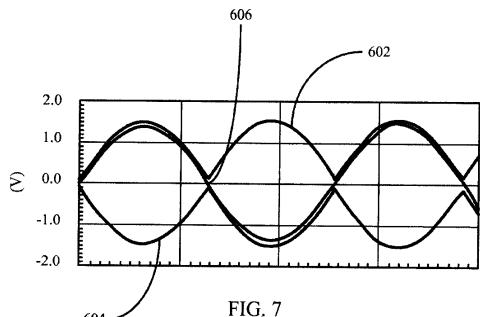

[0049] 図 7 は、0.1 ボルトのヘッドルームを使用する増幅器 400 のシミュレーション結果を示すプロット 600 である。波形 602 は、可変正の電源レール（例えば、図 5 の可変正の電源レール V<sub>pos</sub>）を表し、波形 604 は、可変負の電源レール（例えば、図 5 の可変負の電源レール V<sub>neg</sub>）を表し、および波形 606 は、出力電圧（例えば、図 5 の出力電圧 V<sub>out</sub>）を表す。プロット 600 で例示されたように、波形 602 は、正の電圧のための波形 606 を適切に辿り、ならびに波形 604 は、負の電圧のための波形 606 を適切に辿っている。30

#### 【0048】

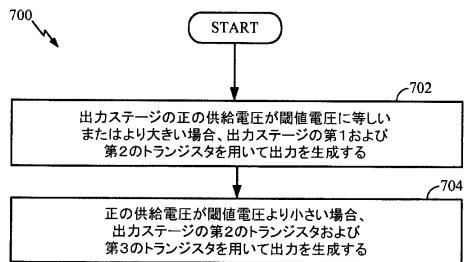

[0050] 図 8 は、1 つまたは複数の例示的な実施例にしたがった方法 700 を示すフローチャートである。方法 700 は、出力ステージの正の電源電圧が閾値電圧に等しいまたはより大きい場合、出力ステージの第 1 および第 2 のトランジスタを用いて出力を生成することを含み得る（参照番号 702 によって表される）。方法 900 はまた、正の電源電圧が閾値電圧より小さい場合、出力ステージの第 2 のトランジスタと第 3 のトランジスタを用いて出力を生成することを含み得る（参照番号 704 によって表される）。40

#### 【0049】

[0051] 図 9 は、1 つまたは複数の例示的な実施例にしたがった別の方法 750 を示すフローチャートである。方法 750 は、出力ステージの正の電源電圧が閾値電圧より大きい場合、増幅器の出力ステージの第 1 のバスを介して出力を搬送することを含み得る（参照番号 752 によって表される）。方法 750 はまた、出力ステージの正の電源電圧が閾値電圧より小さいまたは等しい場合、出力ステージの第 2 の異なるバスを介して出力を搬送することを含み得る（参照番号 754 によって表される）。50

## 【0050】

[0052] およそ0.45ボルトに等しい正の電源電圧 $V_{p..s}$ とおよそ-0.45ボルトに等しい負の電源電圧 $V_{n..g}$ を受信するように構成される電力増幅器の従来の出力ステージと比較して、本発明は、0.1ボルトにおおよそ等しいまたはそれより大きい正の電源電圧と-0.1ボルトにおおよそ等しいまたはそれより小さい負の電源電圧を受信する間に動作し得る電力増幅器を含み、したがって、かなりの電力量を節約する。

## 【0051】

[0053] 当業者は、情報および信号が様々な異なる技術および技法のいずれかを用いて表され得ることを理解するはずである。例えば、上記の説明を通じて言及され得るデータ、命令、コマンド、情報、信号、ビット、記号、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光場または光学粒子またはそれらの任意の組合せによって表され得る。

10

## 【0052】

[0054] 当業者はさらにここに開示された例示的な実施例に関連して記載された様々な例としての論理ブロック、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、またはその両方の組み合わせとして実装され得ることを理解するはずである。ハードウェアとソフトウェアのこの互換性を明確に示すために、様々な例としての構成部品、ブロック、モジュール、回路、およびステップが、一般に、それらの機能の観点から上で説明してきた。こういった機能が、ハードウェアまたはソフトウェアとして実装されるかどうかは、特定のアプリケーションおよび全体のシステムに課せられた設計の制限に依存する。当業者は、各特定のアプリケーションについて様々な方法で記載された機能を実装し得るが、こういった実装の決定は、本発明の例示的な実施例の範囲から逸脱させると解釈されるべきではない。

20

## 【0053】

[0055] ここで本開示された例示的な実施例に関連して記載された種々の例としての論理ブロック、モジュールおよび回路は、ここに記載された機能を実行するために設計された汎用目的プロセッサ、デジタル信号プロセッサ(DSP)、アプリケーション特定用途向け集積回路(ASIC)、フィールド・プログラマブル・ゲート・アレイ(FPGA)または他のプログラム可能な論理デバイス、ディスクリートゲートまたはトランジスタ論理、ディスクリートハードウェア構成要素、またはそれらの任意の組み合わせを実装するか、あるいはそれらと共に実行され得る。汎用プロセッサは、マイクロプロセッサであっても良いが、代替として、プロセッサは、従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンのいずれかであっても良い。プロセッサはまた、例えば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連結する1つまたは複数のマイクロプロセッサ、または任意の他のこういった構成であるコンピューティングデバイスの組み合わせとして実装され得る。

30

## 【0054】

[0056] 1つまたは複数の例示的な実施例において、記載された機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組み合わせに実装され得る。ソフトウェアに実装される場合、機能は、コンピュータ可読媒体上の1つまたは複数の命令またはコードとして記憶または送信され得る。コンピュータ可読媒体は、コンピュータ記憶媒体とある場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体との両方を含む。記憶媒体は、コンピュータによってアクセス可能な任意の入手可能な媒体であり得る。限定ではなく例として、こういったコンピュータ可読媒体は、命令またはデータ構造の形式で所望のプログラムコードを搬送または記憶するために用いられることが可能であり、およびコンピュータによってアクセス可能なRAM、ROM、EEPROM(登録商標)、CD-ROMまたは他の光学ディスク記憶装置、磁気ディスク記憶装置、他の磁気記憶装置、または任意の他の媒体を備えることが可能である。また、任意の接続はコンピュータ可読媒体と適切に称される。例えば、ソフトウェアが、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者線(DSL)、また

40

は赤外線、無線、および／またはマイクロ波のような無線技術を用いてウェブサイト、サーバ、または他の遠隔ソースから伝送される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、および／またはマイクロ波のような無線技術は媒体の定義に含まれる。ここで用いられたようなディスク（disk）およびディスク（disc）は、コンパクトディスク（CD）、レーザーディスク（登録商標）、光学ディスク、（CD）、デジタル多用途ディスク（DVD）、フロッピー（登録商標）ディスク、およびBlue-rayディスクを含み、そこにおいて、ディスク（disk）が、通常データを磁気的に再生する一方で、ディスク（disc）はレーザを用いて光学的にデータを再生する。上記の組み合わせはまた、コンピュータ可読媒体の範囲に含まれるべきである。

10

### 【0055】

[0057]開示された例示的な実施例の前の説明は、本発明を作成または使用することを当業者に可能にするために提供される。これらの例示的な実施例に対する種々の変更は、当業者にとって容易に明らかであり、ここで定義された一般的な原則は、本発明の精神または範囲から逸脱することなく他の実施例に適用され得る。従って、本発明は、ここに示された例示的な実施例に限定されることを意図するものではないが、ここに開示された原則および新規事項に調和する最も広い範囲に適合させるべきである。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

#### [C 1]

第1の電源電圧が閾値電圧より大きい場合に出力信号を搬送するように構成された増幅器出力ステージの第1のパス、および、

20

前記第1の電源電圧が前記閾値電圧と等しいまたはより小さい場合に前記出力信号を搬送するように構成された前記増幅器出力ステージの第2のパス、

を備える装置。

#### [C 2]

前記第1のパスは、前記第1の電源電圧と出力の間に接続された第1のトランジスタと第2の電源電圧と前記出力の間に接続された第2のトランジスタを含み、前記第2のパスは、前記第2のトランジスタと、前記第1の電源電圧と前記出力の間に接続された第3のトランジスタと、を含む、C 1に記載の装置。

#### [C 3]

前記第3のトランジスタへフィードバックバイアス電流制御バスを提供するための少なくとも1つのトランジスタ、および、

30

前記第3のトランジスタのゲートへ駆動信号を搬送するための少なくとも1つのトランジスタ、

をさらに備える、C 2に記載の装置。

#### [C 4]

前記第3のトランジスタは、前記第1のトランジスタの第1の端子に接続された第1の端子と前記第1のトランジスタの第2の端子に接続された第2の端子を有し、かつ、前記第1の電源電圧が前記閾値電圧より小さいまたは等しい場合に導通するように構成された、C 2に記載の装置。

40

#### [C 5]

前記第3のトランジスタと前記第2のトランジスタは、前記第1の電源電圧が実質的にゼロボルトの場合に導通状態になるように構成される、C 2に記載の装置。

#### [C 6]

前記第1のトランジスタは、前記第1の電源電圧が前記閾値電圧より小さいまたは等しい場合に非導通状態になるように構成される、C 2に記載の装置。

#### [C 7]

前記負の電源電圧と電流ソースの間に接続され、かつ、前記第3のトランジスタへフィードバックバイアス電流制御バスを提供するように構成された第4のトランジスタをさらに備える、C 2に記載の装置。

50

## [ C 8 ]

前記第3のトランジスタのゲートへ駆動信号を搬送するように構成された複数のトランジスタをさらに備える、C 2に記載の装置。

## [ C 9 ]

前記第3のトランジスタは、前記第1のトランジスタのソースと前記第1の電源電圧に接続されたドレイン、および、前記第1のトランジスタのドレインと前記出力に接続されたソースを有する、C 2に記載の装置。

## [ C 10 ]

前記第3のトランジスタのゲートは、第1の駆動トランジスタのドレインと第2の駆動トランジスタのドレインの間に接続される、C 2に記載の装置。

10

## [ C 11 ]

前記増幅器は、前記第1のパスと前記第2のパスのうちの1つから前記出力信号を搬送することから他方のパスに前記出力信号を搬送することへの遷移を制御するためのバイアシング回路をさらに備える、C 1に記載の装置。

## [ C 12 ]

前記増幅器は、前記出力ステージに静止電流を設定するためのバイアシング回路をさらに備える、C 1に記載の装置。

## [ C 13 ]

前記バイアシング回路は、前記第1のトランジスタを経由する電流をレプリケートする第1のスケールされた電流と、前記第2のトランジスタを経由する電流をレプリケートする第2のスケールされた電流と、前記第3のトランジスタを経由する電流をレプリケートする第3のスケールされた電流を生成するように構成される、C 1 2に記載の装置。

20

## [ C 14 ]

前記バイアシング回路は、前記第1のスケールされた電流に基づく第1のバイアス電圧と、前記第2のスケールされた電流と前記第3のスケールされた電流に基づく第2のバイアス電圧を生成するように構成される、C 1 3に記載の装置。

## [ C 15 ]

出力ステージの正の電源電圧が閾値電圧より大きい場合に増幅器の前記出力ステージの第1のパスを介して出力を搬送すること、および

30

前記出力ステージの前記正の電源電圧が前記閾値電圧より小さいまたは等しい場合に前記出力ステージの第2の異なるパスを介して前記出力を搬送すること、を備える、方法。

## [ C 16 ]

第2の異なるパスを介して前記出力を搬送することは、前記正の電源電圧が実質的に0.4ボルトまたはそれより小さい場合に前記第2の異なるパスを介して前記出力を搬送することを備える、C 1 5に記載の方法。

40

## [ C 17 ]

第1のパスを介して出力を前記搬送することは、前記出力ステージの第1および第2のトランジスタを用いて前記出力を生成することを備え、および第2の異なるパスを介して前記出力を前記搬送することは、前記出力ステージの前記第2のトランジスタと第3のトランジスタを用いて前記出力を生成することを備える、C 1 5に記載の方法。

## [ C 18 ]

出力ステージの正の電源電圧が閾値電圧より大きい場合に増幅器の前記出力ステージの第1のパスを介して出力を搬送するための手段、および、

前記正の電源電圧が前記閾値電圧より小さいまたは等しい場合に前記出力ステージの第2の異なるパスを介して前記出力を搬送するための手段、を備える、装置。

## [ C 19 ]

前記出力ステージへフィードバックバイアス電流制御パスを提供するための手段をさらに備える、C 1 8に記載の装置。

50

## 【C 2 0】

前記第2の異なるパスを経由する電流をレプリケートするスケールされた電流を生成するための手段を含む前記出力ステージに静止電流を設定するための手段をさらに備える、C 1 8に記載の装置。

【図 1】

図 1

FIG. 1

【図 3】

図 3

FIG. 3

【図 2】

図 2

FIG. 2

【 四 4 】

図 4

【 図 5 】

図 5

FIG. 5

【 図 6 】

図 6

【図7】

図 7

FIG. 7

## 【図8】

図8

FIG. 8

## 【図9】

図9

FIG. 9

---

フロントページの続き

(72)発明者 ダナセカラン、ビジャヤクマー

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 緒方 寿彦

(56)参考文献 特開2009-152680(JP,A)

米国特許出願公開第2009/0322420(US,A1)

特表2015-523821(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03F 3/24