(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-529894

(P2007-529894A)

(43) 公表日 平成19年10月25日(2007.10.25)

| (51) Int.CI.                 | F 1        |      | テーマコード (参考) |

|------------------------------|------------|------|-------------|

| <b>H01L 21/822</b> (2006.01) | H01L 27/04 | A    | 5B176       |

| <b>H01L 27/04</b> (2006.01)  | G06F 9/06  | 630A | 5FO38       |

| <b>G06F 11/00</b> (2006.01)  | H01L 21/82 | A    | 5FO64       |

| <b>H01L 21/82</b> (2006.01)  |            |      |             |

審査請求 未請求 予備審査請求 有 (全 18 頁)

|               |                              |          |                                                                                                  |

|---------------|------------------------------|----------|--------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2007-503893 (P2007-503893) | (71) 出願人 | 504204616<br>アーバー・カンパニー・リミテッド・ライ<br>アビリティ・パートナーシップ<br>アメリカ合衆国、89413 ネバダ州、<br>グレンブルック、サウス・メドウ、223 |

| (86) (22) 出願日 | 平成16年12月14日 (2004.12.14)     | (74) 代理人 | 100104156<br>弁理士 龍華 明裕                                                                           |

| (85) 翻訳文提出日   | 平成18年9月28日 (2006.9.28)       | (72) 発明者 | ハッペンタール、ジョン、エム<br>アメリカ合衆国、80908 コロラド州<br>、コロラド スプリングス、バージェス<br>ロード 10015                         |

| (86) 國際出願番号   | PCT/US2004/041791            | (72) 発明者 | グージー、ジェームス、ディ<br>アメリカ合衆国、89413 ネバダ州、<br>グレンブルック、ピーオー ボックス 1<br>28、サウス メドウ 223                    |

| (87) 國際公開番号   | W02005/094240                |          | 最終頁に続く                                                                                           |

| (87) 國際公開日    | 平成17年10月13日 (2005.10.13)     |          |                                                                                                  |

| (31) 優先権主張番号  | 10/802,067                   |          |                                                                                                  |

| (32) 優先日      | 平成16年3月16日 (2004.3.16)       |          |                                                                                                  |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                  |

(54) 【発明の名称】ダイ素子が積層された再構成可能なプロセッサモジュール

## (57) 【要約】

【課題】 集積回路(I C)ダイ素子が積層されたハイブリッド型の再構成可能なプロセッサモジュールを提供する。

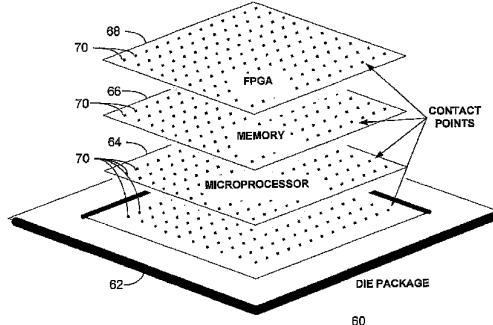

【解決手段】 本明細書に開示する一実施形態に係る再構成可能なプロセッサモジュールは、薄いマイクロプロセッサダイ素子、メモリダイ素子および/またはFPGAダイ素子が積層され、ダイの厚み方向に貫通しているコンタクトによりこれらのダイ素子が相互接続される構造を持つとしてもよい。このようなプロセッサモジュールは、マイクロプロセッサとFPGA間でのデータ共有化速度を大幅に上げることができ、完成アセンブリの歩留まりを改善すると同時に完成アセンブリの製造コストを削減するという効果を奏する。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

プロセッサモジュールであって、

プログラム可能なアレイを有する、少なくとも 1 つの第 1 集積回路機能素子、

前記第 1 集積回路機能素子の前記プログラム可能なアレイに積層され且つ電気的に接続

された、少なくとも 1 つの第 2 集積回路機能素子

を備えるプロセッサモジュール。

**【請求項 2】**

前記第 1 集積回路機能素子の前記プログラム可能なアレイはフィールド・プログラマブル・ゲート・アレイ (FPGA) を含む

請求項 1 に記載のプロセッサモジュール。

10

**【請求項 3】**

前記第 2 集積回路機能素子の前記プロセッサはマイクロプロセッサを含む

請求項 1 に記載のプロセッサモジュール。

**【請求項 4】**

前記第 2 集積回路機能素子はメモリを含む

請求項 1 に記載のプロセッサモジュール。

**【請求項 5】**

前記第 1 集積回路機能素子および前記第 2 集積回路機能素子のうち少なくとも一方に積

層され且つ電気的に接続された、少なくとも 1 つの第 3 集積回路機能素子

をさらに備える請求項 1 に記載のプロセッサモジュール。

20

**【請求項 6】**

前記第 3 集積回路機能素子はメモリを含む

請求項 5 に記載のプロセッサモジュール。

**【請求項 7】**

前記プログラム可能なアレイは、プロセッサ素子 (PE) として再構成可能である

請求項 1 に記載のプロセッサモジュール。

**【請求項 8】**

前記第 1 集積回路機能素子および前記第 2 集積回路機能素子は、両機能素子の表面全体

に配された複数のコンタクトポイントによって電気的に接続されている

請求項 1 に記載のプロセッサモジュール。

30

**【請求項 9】**

再構成可能なコンピュータシステムであって、

プロセッサ、

メモリ、

少なくとも 1 つのプロセッサモジュールであって、プログラム可能なアレイを含む少

なくとも 1 つの第 1 集積回路機能素子および前記第 1 集積回路機能素子の前記プログラム可

能なアレイに積層され且つ電気的に接続された少なくとも 1 つの第 2 集積回路機能素子を

有するプロセッサモジュール

を備えるコンピュータシステム。

40

**【請求項 10】**

前記第 1 集積回路機能素子の前記プログラム可能なアレイは FPGA を含む

請求項 9 に記載のコンピュータシステム。

**【請求項 11】**

前記第 2 集積回路機能素子の前記プロセッサはマイクロプロセッサを含む

請求項 9 に記載のコンピュータシステム。

**【請求項 12】**

前記第 2 集積回路機能素子はメモリを含む

請求項 9 に記載のコンピュータシステム。

**【請求項 13】**

50

前記第1集積回路機能素子および前記第2集積回路機能素子のうち少なくとも一方に積層され且つ電気的に接続された、少なくとも1つの第3集積回路機能素子をさらに備える請求項9に記載のコンピュータシステム。

**【請求項14】**

前記第3集積回路機能素子はメモリを含む請求項13に記載のコンピュータシステム。

**【請求項15】**

前記プログラム可能なアレイは、プロセッサ素子(PE)として再構成可能である請求項9に記載のコンピュータシステム。

**【請求項16】**

10

プロセッサモジュールであって、

プログラム可能なアレイを有する、少なくとも1つの第1集積回路機能素子、

前記第1集積回路機能素子の前記プログラム可能なアレイに積層され且つ電気的に接続されたプロセッサを有する、少なくとも1つの第2集積回路機能素子、

前記第1集積回路機能素子の前記プログラム可能なアレイおよび前記第2集積回路機能素子のプロセッサに積層され且つ電気的に接続されたメモリを有する、少なくとも1つの第3集積回路機能素子

を備えるプロセッサモジュール。

**【請求項17】**

前記第1集積回路機能素子の前記プログラム可能なアレイはFPGAを含む

請求項16に記載のプロセッサモジュール。

**【請求項18】**

前記第2集積回路機能素子の前記プロセッサはマイクロプロセッサを含む

請求項16に記載のプロセッサモジュール。

**【請求項19】**

前記第3集積回路機能素子の前記メモリはメモリアレイを含む

請求項16に記載のプロセッサモジュール。

**【請求項20】**

前記プログラム可能なアレイは、プロセッサ素子(PE)として再構成可能である

請求項16に記載のプロセッサモジュール。

**【請求項21】**

前記第1集積回路機能素子、前記第2集積回路機能素子および前記第3集積回路機能素子は、当該3つの機能素子の表面全体に配された複数のコンタクトポイントによって電気的に接続されている

請求項16に記載のプロセッサモジュール。

**【請求項22】**

40

プログラム可能アレイモジュールであって、

FPGAを有する、少なくとも1つの第1集積回路機能素子、

前記第1集積回路機能素子の前記FPGAに積層され且つ電気的に接続されたメモリアレイを有する、少なくとも1つの第2集積回路機能素子

を備えるプログラム可能アレイモジュール。

**【請求項23】**

前記FPGAは、プロセッサ素子(PE)としてプログラム可能である

請求項22に記載のプログラム可能アレイモジュール。

**【請求項24】**

前記メモリアレイは、前記FPGAのプロセッサ素子(PE)への再構成を加速する

請求項23に記載のプログラム可能アレイモジュール。

**【請求項25】**

前記メモリアレイは、外部メモリによる前記プロセッサ素子(PE)に対する参照動作を加速する

請求項 2 3 に記載のプログラム可能アレイモジュール。

【請求項 2 6】

前記メモリアレイは、前記プロセッサ素子( P E )用のブロックメモリとして機能する

請求項 2 3 に記載のプログラム可能アレイモジュール。

【請求項 2 7】

再構成可能なプロセッサモジュールであって、

プログラム可能なアレイを有する、少なくとも 1 つの第 1 集積回路機能素子、

前記第 1 集積回路機能素子の前記プログラム可能なアレイに積層され且つ電気的に接続

されたプロセッサを有する、少なくとも 1 つの第 2 集積回路機能素子、

前記第 1 集積回路機能素子の前記プログラム可能なアレイおよび前記第 2 集積回路機能

素子のプロセッサに積層され且つ電気的に接続されたメモリを有する、少なくとも 1 つの

第 3 集積回路機能素子

を備え、

前記プロセッサおよび前記プログラム可能なアレイは、両者間でデータを共有する

再構成可能なプロセッサモジュール。

【請求項 2 8】

前記メモリは、少なくとも一時的に前記データを格納する

請求項 2 7 に記載の再構成可能なプロセッサモジュール。

【請求項 2 9】

前記第 1 集積回路機能素子の前記プログラム可能なアレイは、F P G A を含む

請求項 2 7 に記載の再構成可能なプロセッサモジュール。

【請求項 3 0】

前記第 2 集積回路機能素子の前記プロセッサは、マイクロプロセッサを含む

請求項 2 7 に記載の再構成可能なプロセッサモジュール。

【請求項 3 1】

前記第 3 集積回路機能素子の前記メモリは、メモリアレイを含む

請求項 2 7 に記載の再構成可能なプロセッサモジュール。

【請求項 3 2】

プログラム可能アレイモジュールであって、

F P G A を有する、少なくとも 1 つの第 1 集積回路機能素子、

前記第 1 集積回路機能素子の前記 F P G A に積層され且つ電気的に接続されたメモリア

レイを有する、少なくとも 1 つの第 2 集積回路機能素子

を備え、

前記第 1 集積回路機能素子および前記第 2 集積回路機能素子は、両機能素子の表面全体

に配された複数のコンタクトポイントによって電気的に接続されている

プログラム可能アレイモジュール。

【請求項 3 3】

前記 F P G A は、プロセッサ素子( P E )としてプログラム可能である

請求項 3 2 に記載のプログラム可能アレイモジュール。

【請求項 3 4】

前記メモリアレイは、前記 F P G A のプロセッサ素子( P E )への再構成を加速する

請求項 3 3 に記載のプログラム可能アレイモジュール。

【請求項 3 5】

前記メモリアレイは、外部メモリによる前記プロセッサ素子( P E )に対する参照動作

を加速する

請求項 3 3 に記載のプログラム可能アレイモジュール。

【請求項 3 6】

前記メモリアレイは、前記プロセッサ素子( P E )用のブロックメモリとして機能する

請求項 3 3 に記載のプログラム可能アレイモジュール。

【請求項 3 7】

10

20

30

40

50

前記コンタクトポイントを介して、前記FPGAから前記第2集積回路機能素子に対して試験刺激が与えられる

請求項32に記載のプログラム可能アレイモジュール。

【請求項38】

前記第1集積回路機能素子および前記第2集積回路機能素子のうち少なくとも一方に積層され且つ電気的に接続された、少なくとも1つの第3集積回路機能素子をさらに備える請求項32に記載のプログラム可能アレイモジュール。

【請求項39】

前記第3集積回路機能素子はFPGAを有する

請求項38に記載のプログラム可能アレイモジュール。 10

【請求項40】

前記第3集積回路機能素子は、入出力(I/O)コントローラを有する

請求項38に記載のプログラム可能アレイモジュール。

【請求項41】

プログラム可能アレイモジュールを製造する方法であって、

ベースウェハ上に、FPGAおよび複数の金属パッドを有する少なくとも1つの第1集積回路機能素子を形成すること、

前記第1集積回路機能素子の上に、第1エピタキシャル層を形成すること、

前記第1エピタキシャル層に、メモリアレイを有する少なくとも1つの第2集積回路機能素子を形成すること 20

を備え、

前記第2集積回路機能素子は複数の金属パッドを有し、前記複数の金属パッドのうち少なくとも1つは前記第1集積回路機能素子の前記金属パッドと電気的に接続されている方法。

【請求項42】

前記第1集積回路機能素子の表面上に、第1二酸化シリコン層を形成することをさらに備える請求項41に記載の方法。

【請求項43】

前記第1二酸化シリコン層の表面上に、前記第1エピタキシャル層を形成することをさらに備える請求項42に記載の方法。 30

【請求項44】

前記第1エピタキシャル層の形成は、ポリシリコン層を形成することを含む請求項41に記載の方法。

【請求項45】

前記第1集積回路機能素子の前記金属パッドおよび前記第2集積回路機能素子の前記金属パッドの間に相互接続子が形成されるように、貫通するように前記第1エピタキシャル層にエッチングを行うこと

をさらに備える請求項41に記載の方法。

【請求項46】

前記第1集積回路機能素子の表面上に形成された第1二酸化シリコン層に対して、貫通するようにエッチングを行うこと 40

をさらに備える請求項45に記載の方法。

【請求項47】

第3機能素子が前記第1機能素子および前記第2機能素子と一体化した状態で形成されるように、前記第1エピタキシャル層上に第2エピタキシャル層を形成することをさらに備える請求項41に記載の方法。

【請求項48】

前記第3機能素子の形成は、I/Oコントローラ、メモリ、FPGAまたはマイクロプロセッサを形成することを含む

請求項47に記載の方法。 50

**【請求項 4 9】**

前記第2エピタキシャル層の表面上に、第2二酸化シリコン層を形成することをさらに備える請求項47に記載の方法。

**【請求項 5 0】**

前記第2エピタキシャル層の形成は、ポリシリコン層を形成することを含む請求項47に記載の方法。

**【請求項 5 1】**

プロセッサモジュールを製造する方法であって、

ベースウェハ上に、マイクロプロセッサなどである第1集積回路機能素子を少なくとも1つ形成すること、

ウェハ製造プロセスを用いて、前記第1集積回路機能素子上に、FPGAなどの第2集積回路機能素子を少なくとも1つ形成すること

を備える方法。

**【請求項 5 2】**

前記第1集積回路機能素子に対応する複数の金属パッドのうち少なくとも1つと前記第2集積回路機能素子に対応する複数の金属パッドのうち少なくとも1つの間を電気的に接続すること

をさらに備える請求項51に記載の方法。

**【請求項 5 3】**

前記第2集積回路機能素子の形成は、エピタキシャル層を形成することを含む請求項51に記載の方法。

**【請求項 5 4】**

前記エピタキシャル層の形成は、ポリシリコン層を形成することを含む請求項53に記載の方法。

**【請求項 5 5】**

前記第1集積回路機能素子の上面に、二酸化シリコン層を形成することをさらに備える請求項51に記載の方法。

**【請求項 5 6】**

前記第1集積回路機能素子と前記第2集積回路機能素子の間を電気的に接続するよう貫通するように前記第2集積回路機能素子にエッチングを行うこと

をさらに備える請求項51に記載の方法。

**【請求項 5 7】**

ウェハ製造プロセスを用いて、前記第1集積回路機能素子および前記第2集積回路機能素子と一体化された第3機能素子を形成すること

をさらに備える請求項51に記載の方法。

**【請求項 5 8】**

前記第3機能素子の形成は、エピタキシャル層を形成することを含む請求項57に記載の方法。

**【請求項 5 9】**

前記エピタキシャル層の形成は、ポリシリコン層を形成することを含む請求項58に記載の方法。

**【請求項 6 0】**

前記第3機能素子の形成は、I/Oコントローラ、メモリ、FPGAまたはマイクロプロセッサを形成することを含む

請求項57に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、再構成または適応可能なデータ処理用システムおよび方法に関する。本発明は特に、集積回路（IC）ダイ素子が積層された、ハイブリッド型の非常にコンパクトで

10

20

30

40

50

再構成可能なプロセッサモジュールに関する。また、本出願は米国特許出願第10/802,067号（出願日：2004年3月16日）に基づき優先権を主張する。当該米国出願は、米国特許出願第10/452,113号（出願日：2003年6月2日）の一部継続出願である。当該米国出願（第10/452,113号）は、現在米国特許第6,627,985号となっている、米国特許出願第10/012,057号（出願日：2001年12月5日）の継続出願である。上記出願に記載された内容はすべて参照により本出願に組み込んで本出願の記載の一部とするとともに、本出願の譲渡人に譲渡される。

#### 【背景技術】

##### 【0002】

現在普及しているICから構成されるマイクロプロセッサとは異なる種類のプロセッサ素子（PE）として、再構成可能なまたは適応可能なプロセッサと呼ばれるものがある。10 再構成可能なプロセッサは、一般的なマイクロプロセッサに比べ、さまざまな分野において多くの利点を有する。マイクロプロセッサは従来「ロード／保存」パラダイムに基づき所定の手段一式を用いてアプリケーションを実行するが、再構成可能なプロセッサは各アプリケーションの実行に当たりハードウェア内で必要な数の機能ユニットを生成する。このため、再構成可能なプロセッサの方がより多くの処理を並行して行えるようになり、多くのアプリケーションについてスループットを増やすことができる。再構成可能なプロセッサがハードウェア内の構成を変更できるのは通常、フィールド・プログラマブル・ゲート・アレイ（FPGA）を使用しているためである。FPGAは例えば、Altera Corporation社、Xilinx, Inc.社、Lucent Technologies, Inc.社などが製造している。20

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0003】

しかし、再構成可能なプロセッサ（マイクロプロセッサおよびFPGAの組み合わせから成るハイブリッドも含む）の利用範囲は限られている。その理由の1つは、FPGAのゲートカウントがマイクロプロセッサより密度が低いので、汎用の再構成可能なプロセッサ（GPRP）として使用するために必要な数のゲートやピンを有するパッケージ済みFPGAは、非常に大きくなってしまうためである。このようなサイズに関する問題だけをとっても、携帯用デバイスに再構成可能なプロセッサを用いるのは非常に難しいといえる。30

##### 【0004】

第二の理由は、チップを再構成するのに数百ミリ秒近くの時間が必要であり、現行のマイクロプロセッサ技術と組み合わせて使用した場合は、再構成完了までに数百万プロセッサクロックサイクルが必要になるためである。このため、GPRPは処理時間の大半をコンフィグレーションのロードに費やすこととなり、演算に必要な時間を最大限長くできるよう実行中のタスクは比較的長い時間存在しなければならない。このため、GPRPの使用はジョブのコンテキスト変更がない場合に限定されてしまう。ここで、コンテキスト変更とは、オペレーティングシステムが優先順位の高いジョブを処理するために現在実行中のジョブを一時的に終了する処理である。つまり、GPRPは再構成を繰り返し行うことになり、無駄な時間がさらに増えてしまう。40

##### 【0005】

さらに、マイクロプロセッサはキャッシュに格納されたデータを処理することによって実効動作速度を上げているので、ジョブの一部を付属のGPRPに移行させるとなると、マイクロプロセッサのフロントサイドバス（FSB）を介してキャッシュからFPGAにデータを移動させなければならない。しかし、FSBの動作速度はキャッシュバスの約25%にすぎないので、データの移動に多大な時間がかかるてしまう。このため、再構成可能なプロセッサの使用は実質的に、システム内のキャッシュ以外の場所にデータが格納されている場合に限定されることになる。

##### 【0006】

マイクロプロセッサの動作速度が増加の一途をたどっているため、上述した3つの理由が徐々に深刻な問題となってきた。既存の独立デバイスであるマイクロプロセッサとFPGAから構成されるハイブリッドシステムは、再構成が可能なことによりスループットを上昇させるという効果をもたらすが、そのような利点は必要とされなくなってしまうか高い有用性があるとは見なされなくなる可能性がある。

【課題を解決するための手段】

【0007】

本発明の代表実施例によれば、FPGA、マイクロプロセッサおよびキャッシュメモリを、近年開発されたウェハ製造プロセスを用いて組み合わせることによって、非常に有用性が高いハイブリッド型の再構成可能なプロセッサモジュールを実現することができる。10 このようなプロセッサモジュールは、独立した集積回路によって構成される現在のGPRPシステムが持つ問題点を解決するものである。本明細書で開示するこのような新型のプロセッサモジュールは、便宜上「ダイ積層ハイブリッド(SDH)プロセッサ」と呼ぶとしてもよい。

【0008】

米国カリフォルニア州サニーベールのTrue-Si Technologies社(<http://www.trusi.com>)は、金属コンタクトがウェハの厚み方向に貫通する状態まで半導体ウェハの厚みを薄くして、BGAパッケージのように、裏面に小さいバンプを形成する方法を開発した。このような技術を用いてマイクロプロセッサ、キャッシュメモリおよびFPGAのウェハを製造することによって、これら3種のダイ、もしくはそのうち2種類以上のダイを1つの非常にコンパクトな構造にまとめ、上述した現在の再構成可能なプロセッサが持つ問題点を解決するとしてもよい。20

【0009】

またこの場合、ダイ同士を接続するためにワイヤボンディングが必要なく、各ダイの周辺だけでなく、ダイに対応する領域全体に相互接続用パッドを配設することが可能となる。従って、公知の技術に比べてダイ間接続の数を増やすことができる。

【0010】

本明細書では特に、ペアダイ素子を積層および相互接続することによって構成された再構成可能なプロセッサモジュールを開示する。本明細書で開示する実施形態を一つ挙げると、再構成可能なプロセッサモジュールであって、厚みを薄くしたダイ素子を積層し、ダイの厚み方向に貫通しているコンタクトを用いて該ダイ素子を相互接続することによって構成されるプロセッサモジュールとしてもよい。このようなプロセッサモジュールは、マイクロプロセッサダイ、メモリダイおよびFPGAダイが積層され1つのブロックとして構成されているとしてもよい。30

【0011】

本明細書はまた、マイクロプロセッサとFPGA間のデータ共有を加速させるために、例えば、マイクロプロセッサダイ、メモリダイおよびFPGAダイが積層され1つのブロックとして構成された、再構成可能なプロセッサモジュールを開示している。このような構成を持つプロセッサモジュールブロックは、完成アセンブリの歩留まりを改善すると同時に完成アセンブリの製造コストを削減するという効果を奏する。40

【0012】

またさらに、FPGA再構成を加速させる目的で、積層技術を用いてメモリダイとFPGAモジュールを組み合わせる、FPGAモジュールを開示する。実施形態に係るFPGAモジュールによれば、積層技術を用いて該FPGAモジュールをメモリダイと組み合わせることによって、外部メモリの参照動作を加速させると共にオンチップブロックメモリを拡張するとしてもよい。

【0013】

またさらに、製造中に試験刺激を与えると共にFPGAの性能を向上させるために、積層技術を用いてほかのダイとFPGAモジュールを組み合わせる、FPGAモジュールを開示する。本発明に係る技術に基づき、メモリまたは入出力(I/O)コントローラとF50

P G A ダイが積層され 1 つのブロックとして構成された、再構成可能なメモリまたは I / O モジュールを提供するとしてもよい。

#### 【 0 0 1 4 】

本発明の別の実施形態に係る方法によれば、研削などの機械的工程が不要になり、ウェハ製造プロセスによって集積回路素子を「積層」することができる。本明細書で開示しているが、このような方法に基づいて製造された新型のプロセッサモジュールは便宜上、「集積回路機能積層（S I C F）プロセッサ」と呼ぶとしてもよい。

#### 【 0 0 1 5 】

まず、ベースウェハに従来と同様の処理を施して、例えばマイクロプロセッサを製造する。コンタクトはダイの表面全体に設けられる。ベースウェハ上にマイクロプロセッサダイを形成する処理を終えると、ベースウェハの表面は、別の機能を持つ半導体素子をさらに形成するための処理を行えるような状態にしておく。

#### 【 0 0 1 6 】

続いて、ベースウェハに対して F P G A を作成するために必要な処理をすべて施す。上述したとおり、物理的にダイの厚みを薄くして積層した場合と同様に、F P G A の I / O 用金属層はマイクロプロセッサの表面のコンタクトに接続される。こうして、上述した通り、2 つのダイ機能が積層され且つ接続される。しかしこの構造は、各々独立したダイの厚みを薄くして積層する機械的な方法ではなく、ウェハ製造プロセスによって実現される。

#### 【 0 0 1 7 】

本発明の実施形態に係る方法によれば、複数の異なるダイ機能を積層できる。さらに、各ダイの製造プロセスは前のダイ製造プロセスが完了してから開始されるので、別々のウェハ製造プロセスを用いるダイ機能同士を積層することもできる。各ウェハ製造が完了してから次のプロセスが開始されるので、別のダイ機能の積層処理を開始する前に、完成したダイ機能の試験をウェハ単位で行うことができる。このため、さらにダイ機能を積層してからダイ試験を行う場合に比べて試験時間を削減することができるという利点が得られる。これは、早い段階で形成された欠陥ダイはその時点で不良品とみなされるからである。また、欠陥がどのステップにおいて生じているのか簡単に特定できるので、プロセスの最適化という点からも有益である。

#### 【 図面の簡単な説明 】

#### 【 0 0 1 8 】

以下の部分において、本発明の特徴および目的、その実現方法ならびに本発明の内容について、最適な実施の形態に基づき添付の図面を参照しながら詳細に説明する。

#### 【 0 0 1 9 】

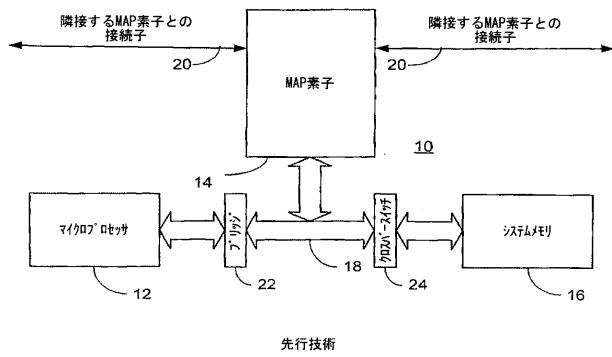

【図1】1 以上の M u l t i - a d a p t i v e p r o c e s s i n g ( M A P はコロラド州コロラド・スプリングの S R C C o m p u t e r s , I n c . , の商標) 素子を有する、先行技術に係るコンピュータシステムの一部を示す、簡略機能ブロック図である。

#### 【 0 0 2 0 】

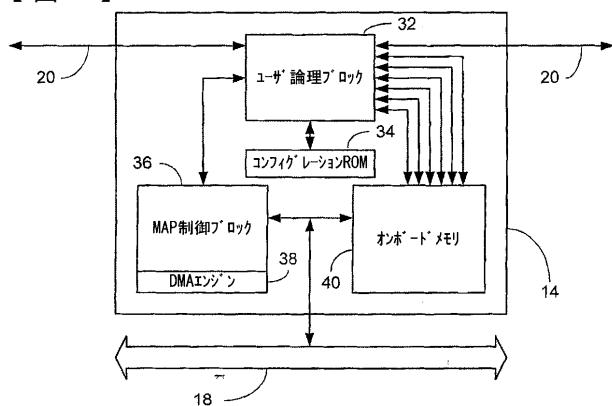

【図2】図1に示した M A P 素子をより詳細に説明する簡略機能ブロック図で、ユーザ論理ブロック ( F P G A を含むとしてもよい) および対応するコンフィグレーション R O M ( R e a d O n l y M e m o r y ) を示す。

#### 【 0 0 2 1 】

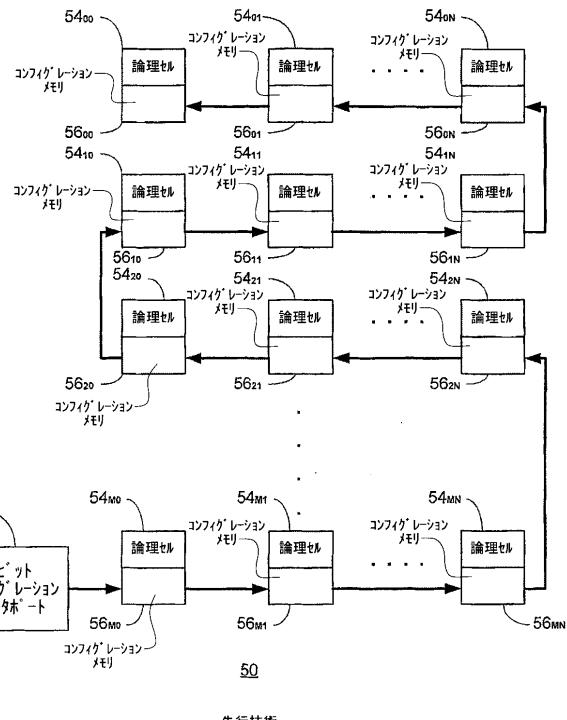

【図3】図2に示したユーザ論理ブロックを含む F P G A 全体に配設された複数の S R A M ( S t a t i c R a n d o m A c c e s s M e m o r y ) セルを含むコンフィグレーションデータバスの代表例を示す機能ブロック図である。

#### 【 0 0 2 2 】

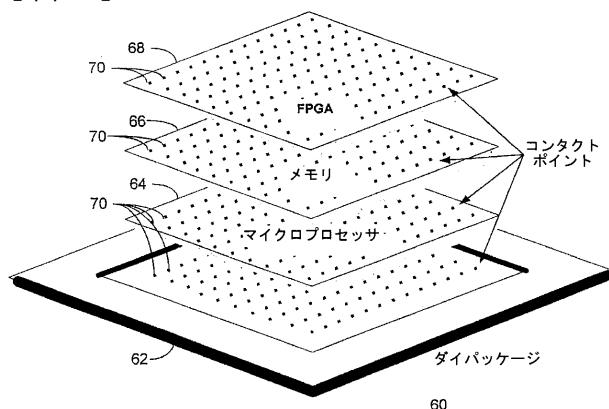

【図4】本発明の実施形態に係る、複数の集積回路ダイ素子が積層されたハイブリッドデバイスを含む再構成可能なプロセッサモジュールを示す、等角投影図法を用いて作成した簡略展開図である。

**【 0 0 2 3 】**

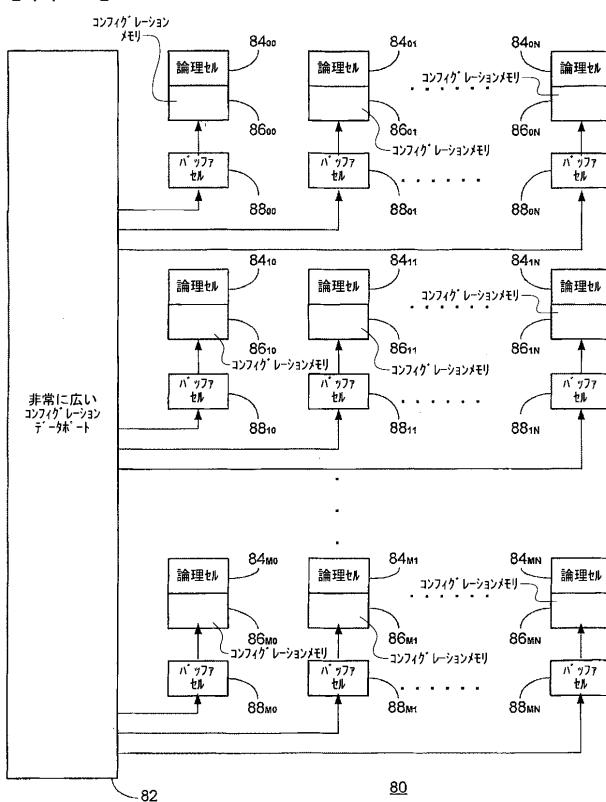

【図5】図4に示した再構成可能なプロセッサモジュールのコンフィグレーションセルを示す機能ブロック図であり、コンフィグレーションセルすべてを並行して更新することによって1クロックサイクル内でFPGAを完全に再構成する。

**【 0 0 2 4 】**

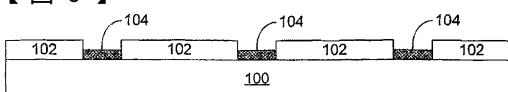

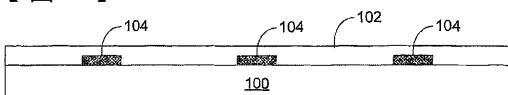

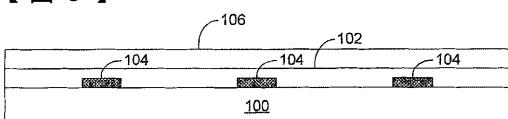

【図6】本発明の実施形態に係る処理方法に基づき、1つのベースウェハ上に2つの機能素子を製造する処理フローを示す断面図である。

**【 0 0 2 5 】**

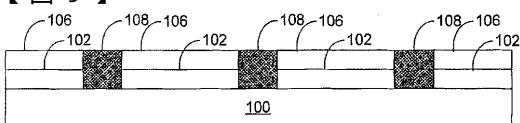

【図7】本発明の実施形態に係る処理方法に基づき、1つのベースウェハ上に2つの機能素子を製造する処理フローを示す断面図である。 10

**【 0 0 2 6 】**

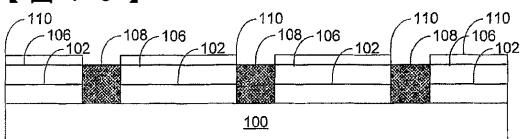

【図8】本発明の実施形態に係る処理方法に基づき、1つのベースウェハ上に2つの機能素子を製造する処理フローを示す断面図である。

**【 0 0 2 7 】**

【図9】本発明の実施形態に係る処理方法に基づき、1つのベースウェハ上に2つの機能素子を製造する処理フローを示す断面図である。

**【 0 0 2 8 】**

【図10】本発明の実施形態に係る処理方法に基づき、1つのベースウェハ上に2つの機能素子を製造する処理フローを示す断面図である。 20

**【 0 0 2 9 】**

【図11】本発明の実施形態に係る処理方法に基づき、1つのベースウェハ上に3つの機能素子を製造する処理フローを示す断面図である。

**【発明を実施するための最良の形態】****【 0 0 3 0 】**

図1は、先行技術に係る再構成可能なコンピュータシステム10の一部を示す、簡略機能ブロック図である。コンピュータシステム10の構成要素のうち関連するものを挙げると、1以上のマイクロプロセッサ12、1以上のMulti-adaptive Processing (MAP(商標))素子14、および対応するシステムメモリ16がある。システムバス18は、プリッジ22を介してマイクロプロセッサ12とMAP素子14を、クロスバースイッチ24を介してシステムメモリ16とMAP素子14を相互に接続する。さらに、同図に示す通り、各MAP素子14は隣接するMAP素子14に対する相互接続素子20を1以上有するとしてもよい。 30

**【 0 0 3 1 】**

図2は、図1のMAP素子14を詳細に示す簡略機能ブロック図である。MAP素子14の構成要素のうち関連するものを挙げると、ユーザ論理ブロック32がある。ユーザ論理ブロック32は、FPGAを備え、コンフィグレーションROM34と対応するとしてよい。MAP制御ブロック36と対応するダイレクトメモリアクセス(DMA)エンジン38およびオンボードメモリアレイ40は、ユーザ論理ブロック32およびシステムバス18と接続されている。

**【 0 0 3 2 】**

図3は、代表的なコンフィグレーションデータバス50を示す機能ブロック図である。コンフィグレーションデータバス50は、図2に示したユーザ論理ブロック32を含むFPGA全体に配設された複数のSRAMセルを備える。チップ機能をプログラムするコンフィグレーション情報は従来、図示した通りFPGA全体に配設されたSRAMセルに保持される。コンフィグレーションデータは、コンフィグレーションデータポート52を介してバイトシリアル伝送方式でロードされ、論理セル54と対応するコンフィグレーションメモリ56のアレイを順次構成していく必要がある。再構成に多大な時間がかかるのは、このコンフィグレーションデータを比較的狭い、例えば8ビットのポートを用いてロードしているためである。 40

**【 0 0 3 3 】**

図4は、本発明の実施形態に係る再構成可能なプロセッサモジュール60を示す、等角投影図法を用いて作成した簡略展開図である。再構成可能なプロセッサモジュール60は、複数の集積回路ダイ素子が積層されたハイブリッドデバイスを備える。同図に示す具体例によると、プロセッサモジュール60は、マイクロプロセッサダイ64、メモリダイ66およびFPGAダイ68が接続されたダイパッケージ62から構成される。ダイパッケージ62およびダイ64、66、68はすべて、複数の対応するコンタクトポイントまたは穴部70を全面にわたって有する。本発明の実施形態に係るプロセッサモジュール60は、マイクロプロセッサダイ64、メモリダイ66およびFPGAダイ78を自由に組み合わせてもよい。

## 【0034】

10

製造工程について、コンタクトポイント70はウェハの前面に形成され、酸化物から成る絶縁層が金属とシリコンの間に設けられる。前面の処理がすべて完了すると、ウェハの厚みを薄くして、Through-Siliconコンタクトを露出させる。Tru-Si Technologies社が開発したAtmospheric Downstream Plasma(ADP)エッチング処理を用いて、酸化物層をエッチングして金属を露出させる。このエッチング処理はシリコンの処理速度の方が速いため、シリコンはコンタクトから絶縁されたままとなる。

## 【0035】

20

図4に示すように、ダイ64、66および68を積層して、Through-Siliconコンタクトを設ける。このような構成とすると、キャッシュメモリダイ66は2つの役割を果たすことになる。一つには、従来と同じく高速アクセスが可能なメモリとしての機能が挙げられる。しかし上記構成によればさらに、マイクロプロセッサ64およびFPGA68が同等の速度でメモリ66にアクセスすることが可能となり、メモリ66がポートを3つ有する場合、システムの帯域幅をさらに増加させることができる。このような特徴によれば、従来の再構成可能なコンピュータシステムに関する多くの問題を解決することができる。また、メモリダイ66をほかの機能についても用いることができるようになれば、非常に大きな効果が得られると思われる。

## 【0036】

30

図5は、図4の再構成可能なプロセッサモジュール60のコンフィグレーションセル80を示す機能ブロック図である。ここで、全コンフィグレーションセルを並行して更新することによって、1クロックサイクル内にFPGA70の再構成を完了させることができるとてもよい。図3に示した従来技術とは異なり、広いコンフィグレーションデータポート82が使用され、対応するコンフィグレーションメモリ86およびバッファセル88を介して各論理セル84を更新するよう構成されている。ここで、バッファセル88はメモリダイ66(図4参照)の一部とすることが望ましい。このような構成とすることによって、論理セル84を有するFPGA68が動作中でもバッファセル88のロードが可能となる。このため、全コンフィグレーション論理セル84が並行して更新され、1クロックサイクル内でFPGA68の再構成を完了することができる。さらに、キャッシュメモリダイ66(図4参照)への接続ポイントが大幅に増えたことを生かして、FPGAダイ68上のコンフィグレーションビットストレージをすべてメモリダイ66で代わりに構成し、FPGAダイ68内で利用可能なものより大きなブロックRAM(Random Access Memory)を提供するとしてもよい。

## 【0037】

40

上記以外にも、必要な電力を削減し動作帯域幅を増加させるという利点がある。ダイ64、66および68(図4参照)間の電気経路が非常に短いので、信号レベルを低減させると同時に相互接続クロックスピードを増加させることができる。

## 【0038】

50

再構成可能なプロセッサモジュール60を組み込んだシステムの特徴としてさらに、製造途中およびモジュールのパッケージングが完了する前に、ダイパッケージ62の積層構造に含まれるマイクロプロセッサ64などのチップに試験刺激を与えることができるよう

に F P G A 6 8 を構成することができる。そして試験後に、所望の機能を有するように F P G A 6 8 を再構成することができる。このため、従来のパッケージ済み部品試験システムを用いる場合に比べて、製造工程のより早い段階でより充実した試験を行うことができ、製造コストを削減することができる。

#### 【 0 0 3 9 】

再構成可能なプロセッサモジュール 6 0 が備える F P G A ダイ 6 8 の数は 1 つとしているが、2 つ以上としてもよい。

#### 【 0 0 4 0 】

セル間の接続は、現在のところ 1 つのダイの 2 次元方向に限られているが、ダイを貫通するアレイ状に配置されたコンタクト 7 0 によって、積層構造内を 3 次元方向に上下に結ぶことが可能になるとしてもよい。公知の積層技術ではダイの周辺に積層用コンタクトを設ける必要があるので、このような構成を実現することはできない。このような構成を持つ本発明の実施形態によれば、所定の時間内にアクセス可能な F P G A ダイ 6 8 のセルの数が最高「 $4 V T / 3$ 」(V はウェハの伝播速度、T は所定の伝播時間)まで増加する。

#### 【 0 0 4 1 】

上述の技術は、上記以外の種類のダイが積層構造に含まれていたり、代わりに用いられても同様に利用できる。そのようなダイの例として、I / O 用の特定用途向け集積回路 (A S I C ) やメモリコントローラなどが挙げられる。

#### 【 0 0 4 2 】

本発明の実施形態に係るモジュールで用いられるダイ間接続技術は、ほかに比べて優れている。パッケージされていない構成要素を積層することは従来より可能であるが、構成要素間の I / O 接続性が大幅に低くなり、I / O 接続子の配設は構成要素の外周付近に限定されるため、本明細書で開示したダイ積層システムのような効果を達成できない。平面基板上に複数のダイを配設することもできるが、この方法についても、構成要素間の I / O 接続が限定され領域レベルの接続が出来ないという問題がある。また、マイクロプロセッサ、メモリおよび F P G A を備える 1 つのダイを作成するという方法もある。このようなダイは、3 つの機能素子間を接続するためにメタライゼーション層を用いており、ダイ積層方法とほぼ同じ効果を奏ることができる。しかし、サイズが非常に大きくなってしまい、積層技術で用いる 3 つの独立したダイに比べ、生産量が大幅に少なくなる。また、積層構造を用いることによって、各ダイの作成に異なる技術を用いたり、プロセッサおよび F P G A の数や種類を任意に設定することが可能となるが、このような構成を持つ单一の大きなダイを製造するには、各組み合わせに対して複数の異なるマスクセットが必要になり、コストが非常に高くなってしまう。

#### 【 0 0 4 3 】

本発明の実施形態に係る方法によれば、間に研削などの機械的工程を挟まずに、ウェハ製造プロセスで、複数の異なる「機能素子」を積層するとしてもよい。本発明の一実施形態に係る方法を具体的に図示すると共に説明するが、この方法には数多くの変形例があり、それらの変形例によっても、請求項に記載の通り、複数の機能素子を積層し相互に接続することができる。

#### 【 0 0 4 4 】

一例を挙げると、F P G A 機能素子がマイクロプロセッサ機能素子の上に積層された状態で、両機能素子間を接続することが望ましい。この順序で機能素子を積層する場合は、まずウェハに従来通りの処理を施して、図 6 に示すようにマイクロプロセッサを形成することから始める。ウェハ 1 0 0 の上面には二酸化シリコン層 1 0 2 と金属パッド 1 0 4 が配設されており、マイクロプロセッサ回路との電気接続に用いられる金属パッド 1 0 4 は露出している。金属パッド 1 0 4 は、ウェハ 1 0 0 の表面のどこに形成してもよい。次に、ウェハ 1 0 0 に第 2 ステップの処理が施される。

#### 【 0 0 4 5 】

第 2 ステップでは、通常のリソグラフィーとウェハ製造プロセスを用いて、金属コンタクト 1 0 4 以外をマスクするとともに酸化物層の上にシリコンから成るエピタキシャル層

10

20

30

40

50

を成長させる。図7に示した二酸化シリコン層102は、金属コントラクト104以外をマスクしてから形成されたものである。図8に、二酸化シリコン層上に成長させたエピタキシャル層106を示す。エピタキシャル層106は、酸化物層102上に成長するため、本質的には多結晶性を有する。現在では、通常のポリシリコン処理技術を用いて、このエピタキシャル層106にポリシリコントランジスタから成るFPGA機能素子を製造することが可能である。この処理によって、図9に示すように、FPGAの金属相互接続子108をマイクロプロセッサの金属パッドのうち少なくとも1つと電気的に接続する。具体的には、ポリシリコンから成るエピタキシャル層106とその下の二酸化シリコン層102にエッチングを施して、機能素子同士を相互接続する必要がある箇所に対応させて、両層を貫通するビアを形成し、該ビア内に相互接続子を形成する。このようにして、マイクロプロセッサとFPGAが物理的に接続され、本発明の実施形態に係る積層型プロセッサが形成される。FPGAに関連した工程がすべて完了すると、図10に示すように、最上面は二酸化シリコン層110と露出した金属パッド108で構成される。この金属パッド108は、通常の集積回路パッケージング技術を用いて、パッケージボンディングワイヤまたはフリップチップ用ハンダとの接続を行うこともできる。

10

20

30

#### 【0046】

または、金属パッド108以外にマスクを施し、その上にさらにエピタキシャル層を形成して、第3の機能素子を形成するとしてもよい。第3の機能素子は、例えばI/Oコントローラ、メモリ、FPGAまたはマイクロプロセッサなどで、既に形成した2つの機能素子と一体化するように設けられる。図11に、1つのベースウェハ上に3つの機能素子が形成されたモジュールを示す。このモジュールは、酸化物層102および110が間に設けられた機能素子100、106、112を備える。同図には、最上面に設けられた酸化物層114および3つの機能素子すべてを相互接続する金属パッド108も示す。

#### 【0047】

集積回路ダイ素子および特定の用途向けの構成を具体的に挙げて本発明の内容を説明したが、上記の説明は例示にすぎず本発明の範囲を限定するものではない。特に、当業者であれば上記の教示内容に基づきさまざまな変形例を得ることができるのは明らかである。そのような変形例は、既に公知となっている特徴や本明細書で開示した特徴と共にまたはそのような特徴に代わって用いることができるものを含むとしてもよい。本出願の請求項には特徴の組み合わせを具体的に記載したが、本明細書の開示範囲には、本出願の請求項にかかる発明に関係していてもいなくても、また本発明が解決に取り組む技術上の問題の解決方法に関係しようとしないと、当業者には明らかである、直接的または間接的に開示された新規性を有する特徴または新規性を有する特徴の組み合わせ、またはそれを一般化したものまたはその変形例が含まれる。出願人は、このような特徴および/または特徴の組み合わせに関して、本出願または派生する出願の審査過程において、新規の請求項を作成する権利を有するものである。

【図1】

【図2】

先行技術

【図3】

先行技術

【図4】

【図5】

82

80

【 四 6 】

〔 7 〕

【 8 】

〔 9 〕

【図10】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                             | International application No.<br>PCT/US04/41791         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC: H01L 23/02( 2006.01);H01L 21/50( 2006.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                             |                                                         |

| USPC: 257/686;438/109<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                             |                                                         |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 257/686, 777, 778; 438/109, 108                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                             |                                                         |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                             |                                                         |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>Please See Continuation Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                             |                                                         |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                             |                                                         |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the relevant passages                                                          | Relevant to claim No.                                   |

| X<br>--<br>Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 6,451,626 B1 (Lin) 17 September 2002 (17.09.2002), column 10, line 66 - column 11, line 23; and column 13, line 39 - column 14, line 40. | 1-23, 26-33, 36, 38-40,<br>51, 52, 56, 57, 60<br><br>55 |

| X<br>--<br>Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 6,072,233 (Corisis et al) 6 June 2000 (06.06.2000), column 3, line 51 - column 5, line 18; and column 6, line 10 - column 7, line 25     | 1-23, 26-33, 36, 38-40,<br>51, 52, 56, 57, 60<br><br>55 |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                             |                                                         |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                                             |                                                         |

| Date of the actual completion of the international search<br>23 March 2006 (23.03.2006)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date of mailing of the international search report<br>08 JUN 2006                                                                           |                                                         |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: ISA/US<br>Commissioner for Patents<br>P.O. Box 1450<br>Alexandria, Virginia 22313-1450<br>Facsimile No. (571) 273-3201                                                                                                                                                                                                                                                                                                                                                                                                                              | Authorized officer <i>Daniel D. Chang</i><br>Daniel D. Chang<br>Telephone No. (571) 272-1562                                                |                                                         |

**INTERNATIONAL SEARCH REPORT**

|                                                 |

|-------------------------------------------------|

| International application No.<br>PCT/US04/41791 |

|-------------------------------------------------|

Continuation of B. FIELDS SEARCHED Item 3:

EAST

search terms: silicon dioxide layer, epitaxial layer, stack, metal pad, fabiract, form, wafer, base wafer, FPGA, memory, processor