(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6300830号

(P6300830)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

(51) Int.Cl.

F 1

|             |               |                  |      |        |      |

|-------------|---------------|------------------|------|--------|------|

| <b>G06N</b> | <b>99/00</b>  | <b>(2010.01)</b> | G06N | 99/00  | 12 O |

| <b>H01L</b> | <b>39/22</b>  | <b>(2006.01)</b> | H01L | 39/22  | K    |

| <b>H03K</b> | <b>19/195</b> | <b>(2006.01)</b> | H03K | 19/195 |      |

| <b>B82Y</b> | <b>10/00</b>  | <b>(2011.01)</b> | B82Y | 10/00  |      |

請求項の数 23 (全 28 頁)

(21) 出願番号 特願2015-557134 (P2015-557134)

(86) (22) 出願日 平成26年2月7日 (2014.2.7)

(65) 公表番号 特表2016-515233 (P2016-515233A)

(43) 公表日 平成28年5月26日 (2016.5.26)

(86) 國際出願番号 PCT/US2014/015362

(87) 國際公開番号 WO2014/124295

(87) 國際公開日 平成26年8月14日 (2014.8.14)

審査請求日 平成29年1月30日 (2017.1.30)

(31) 優先権主張番号 61/762,704

(32) 優先日 平成25年2月8日 (2013.2.8)

(33) 優先権主張国 米国(US)

(73) 特許権者 507209207

ディーウェイブ システムズ、インコーポレイテッド

カナダ国、ブリティッシュ コロンビア州

ブイ5ジー 4エム9、バーナビー、ペータ アベニュー 3033

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(74) 代理人 100117189

弁理士 江口 昭彦

(74) 代理人 100134120

弁理士 内藤 和彦

最終頁に続く

(54) 【発明の名称】量子プロセッサの要素を較正するためのシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項1】

多数の素子の少なくとも第1の素子が決定可能なパラメータを有する多数の素子であって、多数のキューピットを含む多数の素子と、

前記多数の素子の前記少なくとも第1の素子と通信可能に結合できる較正信号源であって、較正信号を提供する較正信号源と、

前記多数の素子の前記少なくとも第1の素子と通信可能に結合できる読み出しシステムであって、前記第1の素子の前記決定可能なパラメータに対する値を決定するため、前記較正信号と前記第1の素子の前記決定可能なパラメータの両方に依存する信号を読み出す読み出しシステムと

を備える量子プロセッサ。

## 【請求項2】

前記較正信号源は、前記第1の素子と直接的に通信可能に結合できる、請求項1に記載の量子プロセッサ。

## 【請求項3】

前記多数の素子は、第2の素子を含み、前記第2の素子は、前記第1の素子と通信可能に結合でき、前記較正信号源は、前記第2の素子と直接的に通信可能に結合でき、また、前記第2の素子を介して、前記第1の素子と間接的に通信可能に結合でき、その結果、前記第2の素子は、前記較正信号源と前記第1の素子との間の通信可能な結合を仲介する、請求項1に記載の量子プロセッサ。

**【請求項 4】**

前記多数の素子は、少なくとも第3の素子を含み、前記少なくとも第3の素子は、前記第2の素子と前記第1の素子の両方と通信可能に結合でき、前記較正信号源は、前記第2の素子および前記少なくとも第3の素子を介して、前記第1の素子と間接的に通信可能に結合でき、その結果、前記第2の素子および前記少なくとも第3の素子は、前記較正信号源と前記第1の素子との間の通信可能な結合を仲介する、請求項3に記載の量子プロセッサ。

**【請求項 5】**

前記読み出しシステムは、前記第1の素子と直接的に通信可能に結合できる、請求項1に記載の量子プロセッサ。

10

**【請求項 6】**

前記多数の素子は、第2の素子を含み、前記第2の素子は、前記第1の素子と通信可能に結合でき、前記読み出しシステムは、前記第2の素子と直接的に通信可能に結合でき、また、前記第2の素子を介して、前記第1の素子と間接的に通信可能に結合でき、その結果、前記第2の素子は、前記読み出しシステムと前記第1の素子との間の通信可能な結合を仲介する、請求項1に記載の量子プロセッサ。

**【請求項 7】**

前記多数の素子は、少なくとも第3の素子を含み、前記少なくとも第3の素子は、前記第2の素子と前記第1の素子の両方と通信可能に結合でき、前記読み出しシステムは、前記第2の素子および前記少なくとも第3の素子を介して、前記第1の素子と間接的に通信可能に結合でき、その結果、前記第2の素子および前記少なくとも第3の素子は、前記読み出しシステムと前記第1の素子との間の通信可能な結合を仲介する、請求項6に記載の量子プロセッサ。

20

**【請求項 8】**

前記量子プロセッサは、超電導量子プロセッサを含み、前記多数の素子は、多数の超電導素子を含み、前記第1の素子は、第1の超電導素子であり、前記多数のキューピットは、多数の超電導キューピットを含み、前記較正信号源は、超電導電流経路によって形成された超電導較正線を含む、請求項1に記載の量子プロセッサ。

**【請求項 9】**

前記超電導較正線は、前記多数の超電導素子の少なくとも1つの超電導素子とガルバニック結合される、請求項8に記載の量子プロセッサ。

30

**【請求項 10】**

前記超電導較正線は、前記多数の超電導素子の少なくとも1つの超電導素子と誘導結合される、請求項8に記載の量子プロセッサ。

**【請求項 11】**

前記決定可能なパラメータは、前記第1の超電導素子の永久電流を含む、請求項8に記載の量子プロセッサ。

**【請求項 12】**

前記多数の超電導素子は、前記第1の超電導素子と誘導結合できる少なくとも第2の超電導素子を含み、前記第1の超電導素子の前記決定可能なパラメータは、前記第1の超電導素子と前記第2の超電導素子との間の相互インダクタンスを含む、請求項8に記載の量子プロセッサ。

40

**【請求項 13】**

前記多数の素子は、決定可能なパラメータを有する少なくとも第2の素子を含み、前記較正信号源は、前記少なくとも第2の素子と通信可能に結合でき、前記読み出しシステムは、前記少なくとも第2の素子と通信可能に結合でき、前記読み出しシステムは、前記少なくとも第2の素子の前記決定可能なパラメータに対する値を決定するため、前記較正信号と前記少なくとも第2の素子の前記決定可能なパラメータの両方に依存する信号を読み出す、請求項1に記載の量子プロセッサ。

**【請求項 14】**

50

量子プロセッサの少なくとも1つの素子を較正する方法であって、前記量子プロセッサは、少なくとも第1の決定可能なパラメータを有する少なくとも第1の素子を含む多数の素子と、前記少なくとも第1の素子と通信可能に結合できる較正信号源と、前記少なくとも第1の素子と通信可能に結合できる読み出しシステムとを含む、方法であり、

前記較正信号源を介して前記量子プロセッサに較正信号を印加するステップと、

前記較正信号の少なくとも一部分を前記較正信号源から前記第1の素子に通信可能に結合するステップと、

前記読み出しシステムを介して、前記較正信号と前記第1の素子の前記第1の決定可能なパラメータの両方に依存する信号を読み出すステップと、

前記読み出しシステムを介して読み出された前記信号に少なくとも部分的に基づいて、10 前記第1の素子の前記第1の決定可能なパラメータに対する値を決定するステップとを含む、方法。

#### 【請求項15】

前記較正信号源は、前記第1の素子と直接的に通信可能に結合でき、その結果、前記較正信号の少なくとも一部分を前記較正信号源から前記第1の素子に通信可能に結合するステップは、前記較正信号の少なくとも一部分を前記較正信号源から直接、前記第1の素子に通信可能に結合するステップを含む、請求項14に記載の方法。

#### 【請求項16】

前記量子プロセッサは、少なくとも第2の素子を含み、前記少なくとも第2の素子は、前記第1の素子と通信可能に結合でき、前記較正信号の少なくとも一部分を前記較正信号源から前記第1の素子に通信可能に結合するステップは、前記較正信号の少なくとも一部分を前記較正信号源から前記少くとも第2の素子に通信可能に結合し、また、前記較正信号の少なくとも一部分を前記少くとも第2の素子から前記第1の素子に通信可能に結合するステップを含み、その結果、前記少くとも第2の素子は、前記較正信号源と前記第1の素子との間の通信可能な結合を仲介する、請求項14に記載の方法。20

#### 【請求項17】

前記読み出しシステムは、前記第1の素子と直接的に通信可能に結合でき、その結果、前記読み出しシステムを介して、前記較正信号と前記第1の素子の前記第1の決定可能なパラメータの両方に依存する信号を読み出すステップは、前記読み出しシステムを介して、前記第1の素子から直接、前記信号の少なくとも一部分を読み出すステップを含む、請求項14に記載の方法。30

#### 【請求項18】

前記量子プロセッサは、少なくとも第2の素子を含み、前記少くとも第2の素子は、前記第1の素子と通信可能に結合でき、前記読み出しシステムを介して、前記較正信号と前記第1の素子の前記第1の決定可能なパラメータの両方に依存する信号を読み出すステップは、前記信号の少なくとも一部分を前記第1の素子から前記少くとも第2の素子に通信可能に結合し、また、前記読み出しシステムを介して、前記信号の少なくとも一部分を前記少くとも第2の素子から読み出すステップを含み、その結果、前記少くとも第2の素子は、前記第1の素子と前記読み出しシステムとの間の通信可能な結合を仲介する、請求項14に記載の方法。40

#### 【請求項19】

前記量子プロセッサは、超電導量子プロセッサを含み、前記第1の素子は、第1の超電導素子を含み、前記較正信号源は、超電導電流経路によって形成された超電導較正線を含み、前記量子プロセッサは、少なくとも第2の超電導素子を含み、前記第1の素子の前記第1の決定可能なパラメータは、前記第1の超電導素子と前記第2の超電導素子との間の相互インダクタンスを含み、

前記較正信号源を介して前記量子プロセッサに既知の値の較正信号を印加するステップは、前記超電導較正線を介して前記超電導量子プロセッサに既知の値の較正信号を印加するステップを含み、

前記較正信号の少なくとも一部分を前記較正信号源から前記第1の素子に通信可能に結50

合するステップは、前記較正信号の少なくとも一部分を前記超電導較正線から前記第1の超電導素子に通信可能に結合するステップを含み、

前記読み出しシステムを介して、前記較正信号と前記第1の素子の前記第1の決定可能なパラメータの両方に依存する信号を読み出すステップは、前記読み出しシステムを介して、前記較正信号と、前記第1の超電導素子と前記第2の超電導素子との間の前記相互インダクタンスの両方に依存する信号を読み出すステップを含み、

前記読み出しシステムを介して読み出された前記信号に少なくとも部分的に基づいて、前記第1の素子の前記第1の決定可能なパラメータに対する値を決定するステップは、前記読み出しシステムを介して読み出された前記信号に少なくとも部分的に基づいて、前記第1の超電導素子と前記第2の超電導素子との間の前記相互インダクタンスに対する値を决定するステップを含む、請求項1\_4に記載の方法。 10

#### 【請求項20】

前記量子プロセッサは、超電導量子プロセッサを含み、前記第1の素子は、第1の超電導素子を含み、前記較正信号源は、超電導電流経路によって形成された超電導較正線を含み、前記第1の素子の前記第1の決定可能なパラメータは、前記第1の超電導素子の永久電流を含み、

前記読み出しシステムを介して読み出された前記信号に少なくとも部分的に基づいて、前記第1の素子の前記第1の決定可能なパラメータに対する値を決定するステップは、前記読み出しシステムを介して読み出された前記信号に少なくとも部分的に基づいて、前記第1の超電導素子の前記永久電流に対する値を決定するステップを含む、請求項1\_4に記載の方法。 20

#### 【請求項21】

前記量子プロセッサは、第1の決定可能なパラメータを有する少なくとも第2の素子を含み、前記較正信号源は、前記少なくとも第2の素子と通信可能に結合でき、前記読み出しシステムは、前記少なくとも第2の素子と通信可能に結合できる、方法であって、

前記較正信号の少なくとも一部分を前記較正信号源から前記少なくとも第2の素子に通信可能に結合するステップと、

前記読み出しシステムを介して、前記較正信号と前記少なくとも第2の素子の前記第1の決定可能なパラメータの両方に依存する信号を読み出すステップと、

前記読み出しシステムを介して読み出された、前記較正信号と前記少なくとも第2の素子の前記第1の決定可能なパラメータの両方に依存する前記信号に少なくとも部分的に基づいて、前記少なくとも第2の素子の前記第1の決定可能なパラメータに対する値を決定するステップと 30

をさらに含む、請求項1\_4に記載の方法。

#### 【請求項22】

前記多数の素子の各素子は、少なくとも1つのそれぞれの決定可能なパラメータを有し、前記較正信号源は、前記多数の素子の各素子と通信可能に結合でき、前記読み出しシステムは、前記多数の素子の各素子と通信可能に結合できる、方法であって、

前記較正信号の少なくとも一部分を前記較正信号源から前記多数の素子の各素子に通信可能に結合するステップと、 40

前記読み出しシステムを介して、前記多数の素子の各素子からそれぞれの信号を読み出すステップであって、それぞれの信号の各々は、前記較正信号と前記信号が読み出された前記それぞれの素子の前記それぞれの決定可能なパラメータの両方に依存する、ステップと、

前記読み出しシステムを介して読み出されたそれぞれの信号の各々に少なくとも部分的に基づいて、それぞれの素子の各々の、前記それぞれの決定可能なパラメータに対するそれぞれの値を決定するステップと

をさらに含む、請求項1\_4に記載の方法。

#### 【請求項23】

前記少なくとも第1の素子は、第2の決定可能なパラメータを有する、方法であって、

50

前記少なくとも第1の素子の前記第1の決定可能なパラメータに対する前記値に少なくとも部分的に基づいて、前記少なくとも第1の素子の前記第2の決定可能なパラメータに対する値を決定するステップをさらに含む、請求項14に記載の方法。

## 【発明の詳細な説明】

## 【技術分野】

【 0 0 0 1 】

本システムおよび方法は、概して、量子プロセッサに関し、具体的には、量子プロセッサのコンポーネントのプログラミングおよび較正に関する。

10

【背景技术】

【 0 0 0 2 】

## 量子プロセッサーアーキテクチャ

量子プロセッサは、量子情報の処理において少なくとも1つの量子力学的な現象（重ね合わせ、もつれ、トンネル効果など）を活用するように設計されたいかなるコンピュータプロセッサでもある。量子プロセッサハードウェアのための多くの異なる設計が存在し、これらに限定されないが、フォトニック量子プロセッサ、超電導量子プロセッサ、核磁気共鳴量子プロセッサ、イオントラップ量子プロセッサ、位相量子プロセッサ、量子ドット量子プロセッサなどを含む。特定のハードウェア実装形態にかかわらず、すべての量子プロセッサは、量子ビットまたは「キュービット」と呼ばれる量子力学的な対象または素子における量子情報を符号化して操作する。すべての量子プロセッサは、キュービット間で情報を伝達するための構造または素子を使用し、すべての量子プロセッサは、少なくとも1つのキュービットの状態を読み出すための構造または素子を使用する。キュービットの物理的な形態は、量子プロセッサで使用されるハードウェアに依存する。例えば、フォトニック量子プロセッサは、光子ベースのキュービットを使用し、超電導量子プロセッサは、超電導キュービットを使用するなどが挙げられる。

20

〔 0 0 0 3 〕

量子プロセッサは、様々な異なる方法で動作するように構築することができる。例えば、量子プロセッサは、汎用プロセッサとしてまたは専用プロセッサとして構築することができる。さらに、量子プロセッサは、ゲート／回路ベースのアルゴリズムまたは断熱／アニーリングベースのアルゴリズムを含む、量子計算を実行するように設計することができる。量子プロセッサのための例示的なシステムおよび方法については、例えば、米国特許第7,135,701号明細書、米国特許第7,418,283号明細書、米国特許第7,533,068号明細書、米国特許第7,619,437号明細書、米国特許第7,639,035号明細書、米国特許第7,898,282号明細書、米国特許第8,008,942号明細書、米国特許第8,190,548号明細書、米国特許第8,195,596号明細書、米国特許第8,283,943号明細書および米国特許出願公開第2011-0022820号明細書（現在の米国特許第8,421,053号明細書）で説明され、その各々は、その全体が参照により本明細書に組み込まれる。

30

[ 0 0 0 4 ]

量子プロセッサは、大多数（例えば、数百、数千、数百万など）のプログラマブル要素を含み得、これらに限定されないが、キュービット、結合器、読み出し素子、ラッチ素子（例えば、量子磁束パラメトロンラッチ回路）、シフトレジスタ、デジタル／アナログ変換器および／またはデマルチプレクサツリー、ならびに、これらの要素のプログラマブルサブコンポーネント（補正素子非対称性のためのプログラマブルサブコンポーネント（例えば、インダクタンスチューナ、キャパシタンスチューナなど）、望ましくない信号ドリフトを補償するためのプログラマブルサブコンポーネントなど）を含む。上記に掲載されるプログラマブル要素のためのシステムおよび方法の例については、例えば、米国特許第7,876,248号明細書、米国特許第8,035,540号明細書、米国特許第8,098,179号明細書、米国特許第7,843,209号明細書、米国特許第8,01

10

8, 244号明細書、米国特許第8, 169, 231号明細書、米国特許出願公開第2011-0060780号明細書、米国特許出願公開第2011-0057169号明細書(現在の米国特許第8, 536, 566号明細書)および米国特許出願公開第2011-0065586号明細書(現在の米国特許第8, 611, 974号明細書)で説明され、その各々は、その全体が参照により本明細書に組み込まれる。

#### 【0005】

量子プロセッサの大多数のプログラマブル要素の中には、必然的に、a)理論的な設計仕様と実在する製造された素子の実際の物理的パラメータとの不一致、および/または、b)名目上同一の素子間の不調和がある。この理由のため、量子プロセッサは、通常、動作前に少なくとも何らかの較正を行うことが必要とされる。量子プロセッサの要素を較正するためのいくつかの例示的なシステムおよび方法については、米国特許出願公開第2011-0060780号明細書で説明されている。量子プロセッサの要素を較正するステップは、例えば、プロセッサ要素に信号を印加するステップと、印加信号に依存する応答、挙動および/またはパラメータを測定するステップと、後続の動作の間にどのように信号をプロセッサに印加するかに影響を及ぼすために測定の結果を使用するステップとを伴う場合がある。例えば、プロセッサ要素は、大きさXの信号でプログラムされると特定の応答を生成するように理論的に設計することができるが、理論的な設計仕様と実在する製造された素子の実際の物理的パラメータとの不一致に起因して、プロセッサ要素は、大きさ(X+d<sub>x</sub>)の信号でプログラムされると特定の応答を生成することが分かる。同様に、量子プロセッサの2つのプログラマブル要素は、グローバルに印加された信号に応答して同じように挙動するように理論的に設計することができるが、2つの要素の製作における不調和に起因して、それらの挙動は異なり得る。量子プロセッサの要素の較正は、そのような不調和を検出し、例えば、要素特有の静的バイアス信号の印加によって、それらの補正について通知することができる。量子プロセッサの要素の較正は、多大な量のデータの収集および分析を伴い得る、難易度の高い、時間のかかるタスクである。原則として、個々のプログラマブル要素の各々や、プログラマブル要素間の潜在的に対の相互作用について特徴付ける必要があり得る。それに従って、量子計算の技術は、量子プロセッサの較正手順を改善するためのシステムおよび方法により利益を得るようになる。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0006】

量子プロセッサは、多数の素子の少なくとも第1の素子が決定可能なパラメータを有する多数の素子であって、多数のキューピットを含む多数の素子と、多数の素子の少なくとも第1の素子と通信可能に結合できる較正信号源であって、較正信号を提供する較正信号源と、多数の素子の少なくとも第1の素子と通信可能に結合できる読み出しシステムであって、第1の素子の決定可能なパラメータに対する値を決定するため、較正信号と第1の素子の決定可能なパラメータの両方に依存する信号を読み出す読み出しシステムとを含むものとして要約することができる。較正信号源は、第1の素子と直接的に通信可能に結合できる。多数の素子は、第2の素子を含み得、第2の素子は、第1の素子と通信可能に結合でき、較正信号源は、第2の素子と直接的に通信可能に結合でき、また、第2の素子を介して、第1の素子と間接的に通信可能に結合でき、その結果、第2の素子は、較正信号源と第1の素子との間の通信可能な結合を仲介する。多数の素子は、少なくとも第3の素子を含み得、少なくとも第3の素子は、第2の素子と第1の素子の両方と通信可能に結合でき、較正信号源は、第2の素子および少なくとも第3の素子を介して、第1の素子と間接的に通信可能に結合でき、その結果、第2の素子および少なくとも第3の素子は、較正信号源と第1の素子との間の通信可能な結合を仲介する。

#### 【0007】

読み出しシステムは、第1の素子と直接的に通信可能に結合できる。多数の素子は、第2の素子を含み得、第2の素子は、第1の素子と通信可能に結合でき、読み出しシステムは、第2の素子と直接的に通信可能に結合でき、また、第2の素子を介して、第1の素子

10

20

30

40

50

と間接的に通信可能に結合でき、その結果、第2の素子は、読み出しシステムと第1の素子との間の通信可能な結合を仲介する。多数の素子は、少なくとも第3の素子を含み得、少なくとも第3の素子は、第2の素子と第1の素子の両方と通信可能に結合でき、読み出しシステムは、第2の素子および少なくとも第3の素子を介して、第1の素子と間接的に通信可能に結合でき、その結果、第2の素子および少なくとも第3の素子は、読み出しシステムと第1の素子との間の通信可能な結合を仲介する。

#### 【0008】

量子プロセッサは、超電導量子プロセッサを含み得、多数の素子は、多数の超電導素子を含み得、第1の素子は、第1の超電導素子であり得、多数のキューピットは、多数の超電導キューピットを含み得、較正信号源は、超電導電流経路によって形成された超電導較正線を含み得る。超電導較正線は、多数の超電導素子の少なくとも1つの超電導素子とガルバニック結合することができる。超電導較正線は、多数の超電導素子の少なくとも1つの超電導素子と誘導結合することができる。決定可能なパラメータは、第1の超電導素子の永久電流を含み得る。多数の超電導素子は、第1の超電導素子と誘導結合できる少なくとも第2の超電導素子を含み得、第1の超電導素子の決定可能なパラメータは、第1の超電導素子と第2の超電導素子との間の相互インダクタンスを含み得る。第2の超電導素子は、超電導キューピットであり得る。

10

#### 【0009】

多数の素子は、決定可能なパラメータを有する少なくとも第2の素子を含み得、較正信号源は、少なくとも第2の素子と通信可能に結合でき、読み出しシステムは、少なくとも第2の素子と通信可能に結合でき、読み出しシステムは、少なくとも第2の素子の決定可能なパラメータに対する値を決定するため、較正信号と少なくとも第2の素子の決定可能なパラメータの両方に依存する信号を読み出す。較正信号源は、多数の素子のあらゆる素子と通信可能に結合できる。第1の素子は、キューピットであり得る。多数の素子は、キューピット、ラッチ素子、結合素子、読み出し素子およびプログラミング素子の少なくとも1つを含み得、第1の素子は、キューピット、ラッチ素子、結合素子、読み出し素子およびプログラミング素子からなる群から選択することができる。

20

#### 【0010】

量子プロセッサの少なくとも1つの素子を較正する方法であって、量子プロセッサは、少なくとも第1の決定可能なパラメータを有する少なくとも第1の素子を含む多数の素子と、少なくとも第1の素子と通信可能に結合できる較正信号源と、少なくとも第1の素子と通信可能に結合できる読み出しシステムとを含む、方法は、較正信号源を介して量子プロセッサに較正信号を印加するステップと、較正信号の少なくとも一部分を較正信号源から第1の素子に通信可能に結合するステップと、読み出しシステムを介して、較正信号と第1の素子の第1の決定可能なパラメータに対する値を決定するステップとを含むものとして要約することができる。較正信号源は、第1の素子と直接的に通信可能に結合でき、その結果、較正信号の少なくとも一部分を較正信号源から第1の素子に通信可能に結合するステップは、較正信号の少なくとも一部分を較正信号源から直接、第1の素子に通信可能に結合するステップを含み得る。量子プロセッサは、少なくとも第2の素子を含み得、少なくとも第2の素子は、第1の素子と通信可能に結合でき、較正信号の少なくとも一部分を較正信号源から第1の素子に通信可能に結合するステップは、較正信号の少なくとも一部分を較正信号源から少なくとも第2の素子に通信可能に結合し、また、較正信号の少なくとも一部分を少なくとも第2の素子から第1の素子に通信可能に結合するステップを含み得、その結果、少なくとも第2の素子は、較正信号源と第1の素子との間の通信可能な結合を仲介する。読み出しシステムは、第1の素子と直接的に通信可能に結合でき、その結果、読み出しシステムを介して、較正信号と第1の素子の第1の決定可能なパラメータの両方に依存する信号を読み出すステップは、読み出しシステムを介して、第1の素子から直接、信号の少なくとも一部分を読み出すステップを含み得る。

30

40

50

## 【0011】

量子プロセッサは、少なくとも第2の素子を含み得、少なくとも第2の素子は、第1の素子と通信可能に結合でき、読み出しシステムを介して、較正信号と第1の素子の第1の決定可能なパラメータの両方に依存する信号を読み出すステップは、信号の少なくとも一部分を第1の素子から少なくとも第2の素子に通信可能に結合し、また、読み出しシステムを介して、信号の少なくとも一部分を少なくとも第2の素子から読み出すステップを含み得、その結果、少なくとも第2の素子は、第1の素子と読み出しシステムとの間の通信可能な結合を仲介する。

## 【0012】

量子プロセッサは、超電導量子プロセッサを含み得、第1の素子は、第1の超電導素子を含み得、較正信号源は、超電導電流経路によって形成された超電導較正線を含み得、量子プロセッサは、少なくとも第2の超電導素子を含み得、第1の素子の第1の決定可能なパラメータは、第1の超電導素子と第2の超電導素子との間の相互インダクタンスを含み得る。較正信号源を介して量子プロセッサに既知の値の較正信号を印加するステップは、超電導較正線を介して超電導量子プロセッサに既知の値の較正信号を印加するステップを含み得る。較正信号の少なくとも一部分を較正信号源から第1の素子に通信可能に結合するステップは、較正信号の少なくとも一部分を超電導較正線から第1の超電導素子に通信可能に結合するステップを含み得る。読み出しシステムを介して、較正信号と第1の素子の第1の決定可能なパラメータの両方に依存する信号を読み出すステップは、読み出しシステムを介して、較正信号と、第1の超電導素子と第2の超電導素子との間の相互インダクタンスの両方に依存する信号を読み出すステップを含み得る。読み出しシステムを介して読み出された信号に少なくとも部分的に基づいて、第1の素子の第1の決定可能なパラメータに対する値を決定するステップは、読み出しシステムを介して読み出された信号に少なくとも部分的に基づいて、第1の超電導素子と第2の超電導素子との間の相互インダクタンスに対する値を決定するステップを含み得る。第1の超電導素子および第2の超電導素子の少なくとも1つは、超電導キューピットであり得る。

10

20

## 【0013】

量子プロセッサは、超電導量子プロセッサを含み得、第1の素子は、第1の超電導素子を含み得、較正信号源は、超電導電流経路によって形成された超電導較正線を含み得、第1の素子の第1の決定可能なパラメータは、第1の超電導素子の永久電流を含み得る。読み出しシステムを介して読み出された信号に少なくとも部分的に基づいて、第1の素子の第1の決定可能なパラメータに対する値を決定するステップは、読み出しシステムを介して読み出された信号に少なくとも部分的に基づいて、第1の超電導素子の永久電流に対する値を決定するステップを含み得る。

30

## 【0014】

量子プロセッサは、第1の決定可能なパラメータを有する少なくとも第2の素子を含み得、較正信号源は、少なくとも第2の素子と通信可能に結合でき、読み出しシステムは、少なくとも第2の素子と通信可能に結合できる。次いで、方法は、較正信号の少なくとも一部分を較正信号源から少なくとも第2の素子に通信可能に結合するステップと、読み出しシステムを介して、較正信号と少なくとも第2の素子の第1の決定可能なパラメータの両方に依存する信号を読み出すステップと、読み出しシステムを介して読み出された、較正信号と少なくとも第2の素子の第1の決定可能なパラメータの両方に依存する信号に少なくとも部分的に基づいて、少なくとも第2の素子の第1の決定可能なパラメータに対する値を決定するステップとをさらに含み得る。

40

## 【0015】

多数の素子の各素子は、少なくとも1つのそれぞれの決定可能なパラメータを有し得、較正信号源は、多数の素子の各素子と通信可能に結合でき、読み出しシステムは、多数の素子の各素子と通信可能に結合できる。次いで、方法は、較正信号の少なくとも一部分を較正信号源から多数の素子の各素子に通信可能に結合するステップと、読み出しシステムを介して、多数の素子の各素子からそれぞれの信号を読み出すステップであって、それぞ

50

れの信号の各々は、較正信号と信号が読み出されたそれぞれの素子のそれぞれの決定可能なパラメータの両方に依存する、ステップと、読み出しシステムを介して読み出されたそれぞれの信号の各々に少なくとも部分的に基づいて、それぞれの素子の各々の、それぞれの決定可能なパラメータに対するそれぞれの値を決定するステップをさらに含み得る。

#### 【0016】

少なくとも第1の素子は、第2の決定可能なパラメータを有し得、方法は、少なくとも第1の素子の第1の決定可能なパラメータに対する値に少なくとも部分的に基づいて、少なくとも第1の素子の第2の決定可能なパラメータに対する値を決定するステップをさらに含み得る。

#### 【0017】

10

図面では、同一の参照番号は、同様の要素または行為を特定する。図面における要素のサイズおよび相対位置は、必ずしも原寸に比例することは限らない。例えば、様々な要素の形状および角度は原寸に比例しておらず、これらの要素のいくつかは、図面を読み易くするために任意に拡大および位置付けされる。さらに、描かれている要素の特定の形状は、特定の要素の実際の形状に関する情報を伝えることを意図せず、図面における認識を容易にするために、単に選択されただけである。

#### 【図面の簡単な説明】

#### 【0018】

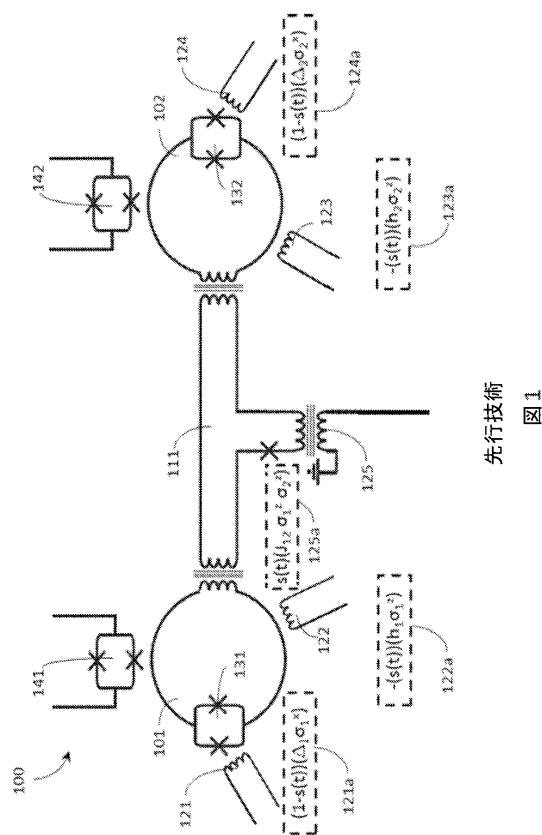

【図1】本システムおよび方法による、使用のために適合させることができるAQC（および/または量子アニーリング）のために設計された例示的な超電導量子プロセッサの一部分の概略図である。

20

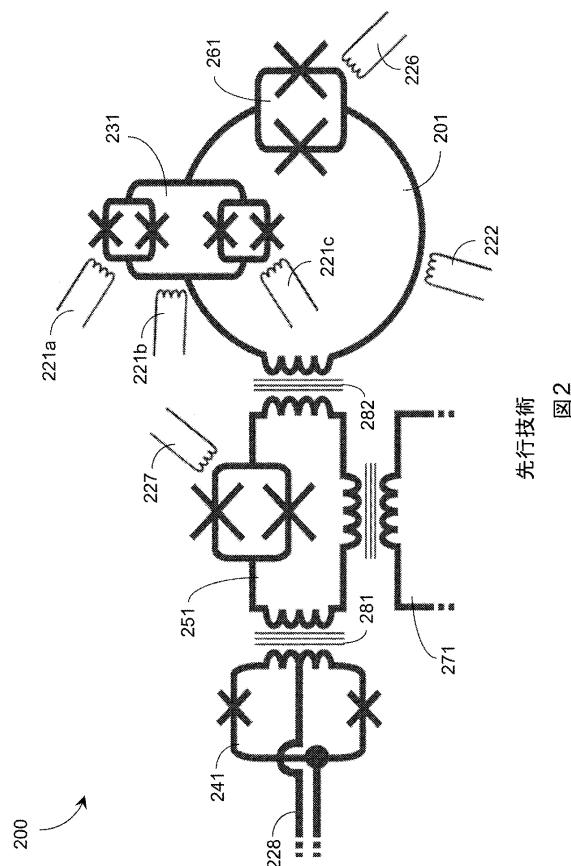

【図2】中間ラッチ素子を通じてDC-SQUID磁力計（読み出し素子）と結合された超電導磁束キューピットを含む量子プロセッサの一部分の概略図である。

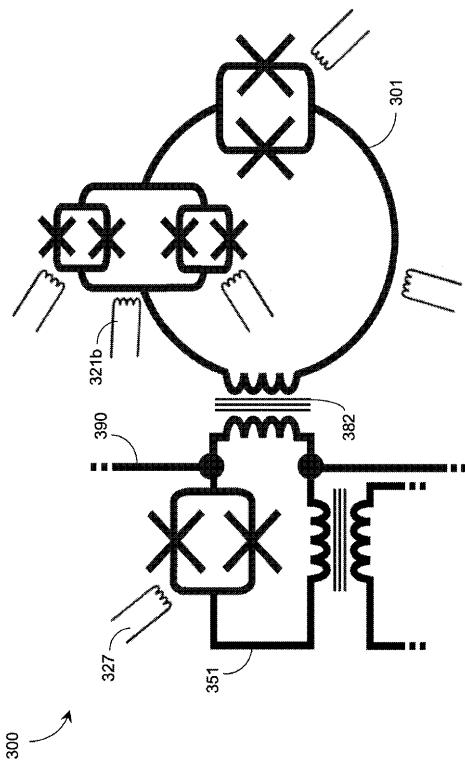

【図3】本システムおよび方法による、超電導磁束キューピットおよび専用較正信号源を含む量子プロセッサの一部分の概略図である。

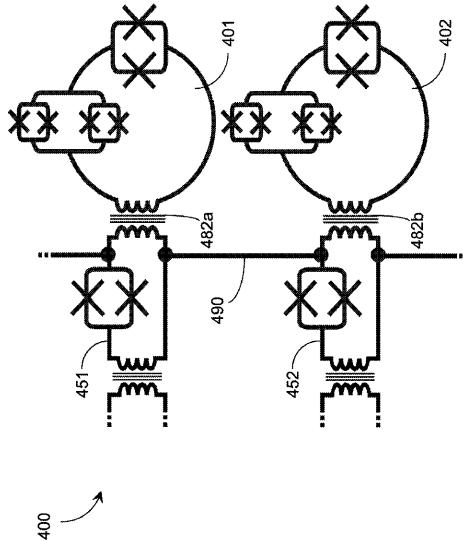

【図4】本システムおよび方法による、2つの超電導磁束キューピットおよび単一の専用較正信号源を含む量子プロセッサの一部分の概略図である。

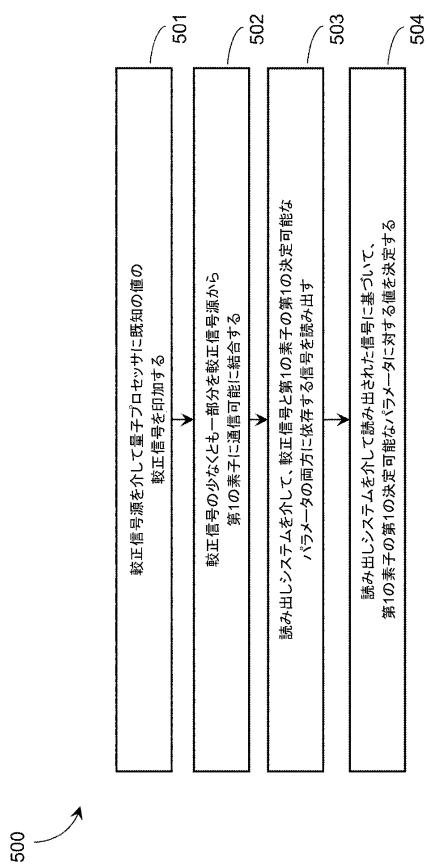

【図5】本システムおよび方法による、量子プロセッサの1つの要素のその較正を容易にするために較正信号源を使用する方法を示すフロー図である。

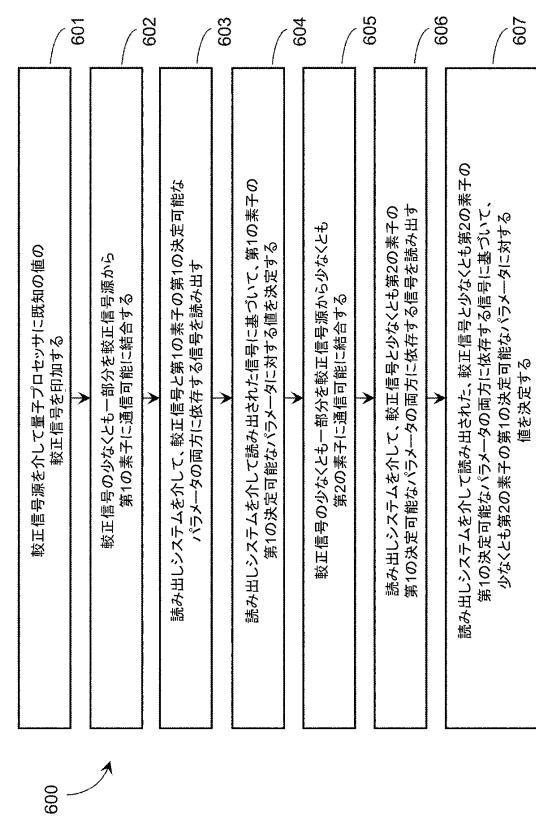

【図6】本システムおよび方法による、量子プロセッサの複数の要素のその較正を容易にするために較正信号源を使用する方法を示すフロー図である。

30

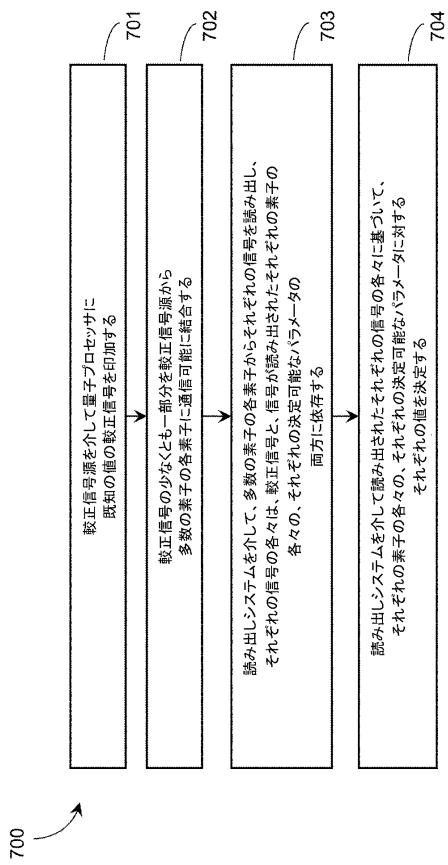

【図7】本システムおよび方法による、量子プロセッサの多数の素子の各々のその較正を容易にするために較正信号源を使用する方法を示すフロー図である。

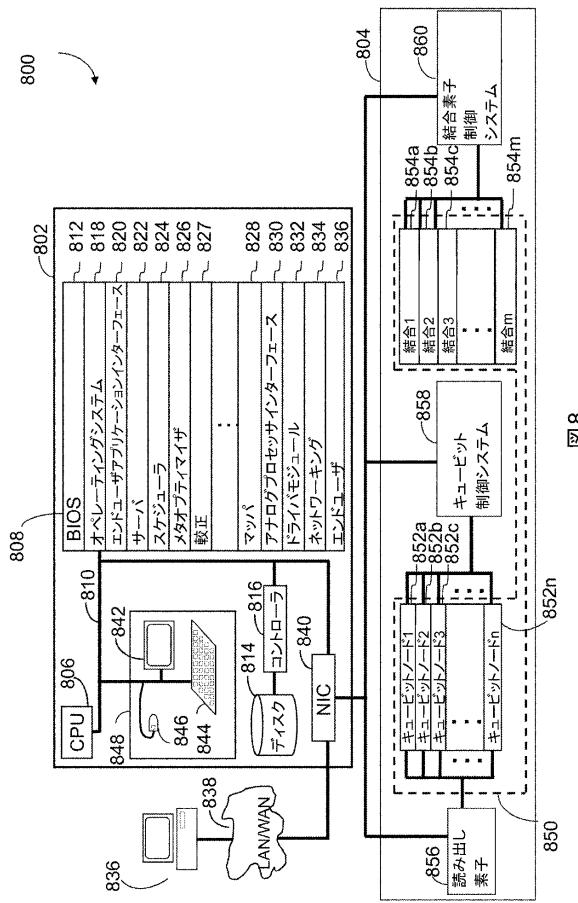

【図8】本システムおよび方法による、少なくとも1つの量子プロセッサを使用するコンピューティングシステムを示す機能ブロック図である。

#### 【発明を実施するための形態】

#### 【0019】

以下の説明では、開示される様々な実施形態の徹底的な理解を提供するため、いくつかの特定の詳細が含まれる。しかし、当業者であれば、これらの特定の詳細のうちの1つもしくは複数を用いることなく、または、他の方法、コンポーネント、材料などを用いて、実施形態を実践できることが認識されよう。他の例では、マイクロプロセッサ、駆動回路、および、非一時的なコンピュータまたはプロセッサ可読媒体（例えば、読み取り専用メモリ（ROM）、電気的消去・プログラム可能型ROM（EEPROM）もしくはFLASHメモリなどの不揮発性メモリ、または、例えば、スタティックもしくはダイナミックランダムアクセスメモリ（RAM）などの揮発性メモリなど）を含む、量子素子、結合素子および制御システムなどの量子プロセッサと関連付けられた周知の構造については、本システムおよび方法の実施形態の説明を必要に曖昧にすることを避けるため、詳細に示されることも説明されることもない。この明細書および添付の特許請求の範囲全体を通じて、「要素」および「1つまたは複数の要素」という用語は、これらに限定されないが、量子プロセッサと関連付けられたそのようなすべての構造、システムおよび素子ならびに

40

50

それらに関連するプログラマブルパラメータを包含するために使用される。

**【0020】**

文脈上他の意味に解すべき場合を除き、本明細書および以下の添付の特許請求の範囲全体を通じて、「備える、含む (comprise)」という用語ならびに「備える、含む (comprises)」および「備える、含む (comprising)」などのその变形語は、制限のない、包括的な意味で、すなわち、「これらに限定されないが、～を含む」として解釈されたい。

**【0021】**

この明細書全体を通じて、「一実施形態」、「実施形態」または「別の実施形態」への言及は、実施形態に関連して説明される特定の指示対象の特徴、構造または特性が少なくとも1つの実施形態に含まれることを意味する。したがって、この明細書全体を通じて、様々な場所での「一実施形態では」、「実施形態では」または「別の実施形態」という記載の出現は、必ずしもすべてが同じ実施形態を指すとは限らない。その上、特定の特徴、構造または特性は、1つまたは複数の実施形態において、適切ないかなる方法でも組み合わせることができる。

**【0022】**

この明細書および添付の特許請求の範囲で使用されるように、文脈上別段の明確な定めがない限り、単数形「a」、「a n」および「t h e」は、複数の指示対象を含むことに留意すべきである。したがって、例えば、「量子プロセッサ」を含む問題解決システムへの言及は、単一の量子プロセッサまたは2つ以上の量子プロセッサ（複数の量子プロセッサのグリッド状または分散型ネットワークを含む）を含む。また、文脈上別段の明確な定めがない限り、「または」という用語は、一般に、「および／または」を含む意味で使用されることにも留意すべきである。

**【0023】**

本明細書で提供される見出しあは、単に便宜を図るためのものであり、実施形態の範囲または意味を解釈するものではない。

**【0024】**

本明細書で説明される様々な実施形態は、量子プロセッサの要素を較正するためのシステムおよび方法を提供する。より具体的には、本明細書で説明される様々な実施形態は、較正精度の向上および／または総較正時間の削減を行うことができる専用較正構造を導入することによって、量子プロセッサの較正を改善するためのシステムおよび方法を提供する。

**【0025】**

説明に役立つ例として、断熱量子計算および／または量子アニーリングを実行するよう設計された超電導量子プロセッサが、以下の説明で使用される。しかし、以前に説明されるように、当業者であれば、本システムおよび方法は、量子アルゴリズム（例えば、断熱量子計算、量子アニーリング、ゲート／回路ベースの量子計算など）のいかなる形態をも実装する量子プロセッサハードウェア（例えば、超電導、フォトニック、イオントラップ、量子ドット、位相など）のいかなる形態にも適用できることが理解されよう。

**【0026】**

典型的な断熱発展は、方程式1によって表すことができる。

$$H_e = (1 - s) H_{In} + s H_f \quad (1)$$

式中、 $H_{In}$ は、初期ハミルトニアンであり、 $H_f$ は、最終または「問題」ハミルトニアンであり、 $H_e$ は、発展または瞬時ハミルトニアンであり、 $s$ は、発展速度を制御する発展係数である。一般に、 $s$ は、時間 $t$ と共に、 $s(t)$ として0から1まで様々である。例えば、Amin, M. H. S., “Effect of local minima on quantum adiabatic optimization”, Physical Review Letters Vol. 100, 130503 (2008)で説明されている断熱量子計算（「AQC」）の一般的な手法は、方程式2に示される形式の初期ハミルトニアンから始めることである。

10

20

30

40

50

【数1】

$$H_h = -\frac{1}{2} \sum_{i=1}^N \Delta_i \sigma_i^x \quad (2)$$

式中、Nは、キュービットの数を表し、

【数2】

$$\sigma_i^x$$

10

は、i番目のキュービットのパウリx行列であり、 $\Delta_i$ は、i番目のキュービットで誘発された単一のキュービットトンネル分裂量である。ここでは、

【数3】

$$\sigma_i^x$$

項は、「非対角」項の例である。この形式の初期ハミルトニアンは、例えば、以下の形式の最終ハミルトニアンに発展することができる。

【数4】

$$H_f = -\frac{\epsilon}{2} \left[ \sum_{i=1}^N h_i \sigma_i^z + \sum_{i,j=1}^N J_{ij} \sigma_i^z \sigma_j^z \right] \quad (3)$$

20

式中、Nは、キュービットの数を表し、

【数5】

$$\sigma_i^z$$

は、i番目のキュービットのパウリz行列であり、 $h_i$ および $J_{i,j}$ は、キュービットの無次元の局所場およびキュービット間の結合であり、 $\epsilon$ は、 $H_f$ の何らかの特性エネルギースケールである。ここでは、

【数6】

$$\sigma_i^z$$

30

および

【数7】

$$\sigma_i^z \sigma_j^z$$

40

項は、「対角」項の例である。この明細書全体を通じて、「最終ハミルトニアン」および「問題ハミルトニアン」という用語は、交換可能に使用される。方程式2および3のそれぞれの $H_{In}$ および $H_f$ などのハミルトニアンは、様々な異なる方法で物理的に実現することができる。特定の例は、超電導キュービットの実装によって実現される。

【0027】

図1は、本システムおよび方法による、使用のために適合させることができるAQC(および/または量子アニーリング)のために設計された例示的な超電導量子プロセッサ100の一部分の概略図である。図1に示される超電導量子プロセッサ100の一部分は、2つの超電導キュービット101、102と、超電導キュービット間の情報を結合する(

50

すなわち、キュービット 101 とキュービット 102 との間の対の結合を提供する)調整可能な ZZ 結合器 111 とを含む。図 1 に示される量子プロセッサ 100 の一部分は、2 つのキュービット 101、102 と、1 つの結合器 111 のみを含むが、当業者であれば、量子プロセッサ 100 は、いかなる数のキュービットも、キュービット間の情報を結合するいかなる数の結合素子も含み得ることが理解されよう。

#### 【0028】

図 1 に示される量子プロセッサ 100 の一部分は、方程式 2 によって説明されるハミルトニアンでシステムを初期化し、方程式 1 によって説明される発展に従って、方程式 3 によって説明されるハミルトニアンにシステムを発展させることによって、AQC および / または QA を物理的に実現するために実装することができる。量子プロセッサ 100 は、

量子プロセッサ 100 の状態の構成および制御に使用される多数のインターフェース 121 ~ 125 を含む。インターフェース 121 ~ 125 の各々は、プログラミングサブシステムおよび / または発展サブシステムの一部として、示されるような、それぞれの誘導結合構造によって実現することができる。そのようなプログラミングサブシステムおよび / または発展サブシステムは、量子プロセッサ 100 から分離することも、例えば、米国特許第 7,876,248 号明細書および米国特許第 8,035,540 号明細書で説明されているように、局所に含めること(すなわち、量子プロセッサ 100 内蔵)もできる。

10

#### 【0029】

量子プロセッサ 100 の動作において、インターフェース 121 および 124 の各々は、キュービット 101 および 102 のそれぞれの複合ジョセフソン接合 131、132 に磁束信号を送入して結合するために使用することができ、それにより、システムハミルトニアンの  $h_i$  項を実現することができる。この結合は、方程式 2 によって説明されるハミルトニアンの非対角  $\times$  項を提供し、これらの磁束信号は、「不規則化信号」の例である。同様に、インターフェース 122 および 123 の各々は、キュービット 101 および 102 のそれぞれのキュービットループに磁束信号を送入して結合するために使用することができ、それにより、システムハミルトニアンの  $h_i$  項を実現することができる。この結合は、方程式 3 の対角  $z$  項を提供する。その上、インターフェース 125 は、結合器 111 に磁束信号を送入して結合するために使用することができ、それにより、システムハミルトニアンの  $J_{ij}$  項を実現することができる。この結合は、方程式 3 の対角  $z_i$

20  $z_j$  項を提供する。図 1 では、システムハミルトニアンへのインターフェース 121 ~ 125 の各々の貢献は、ボックス 121a ~ 125a でそれぞれ示される。したがって、この明細書および添付の特許請求の範囲全体を通じて、「問題の公式化」および「多くのプログラマブルパラメータの構成」という用語は、例えばインターフェース 121 ~ 125 を介する、例えば超電導量子プロセッサのシステムハミルトニアンにおける  $h_i$  および  $J_{ij}$  項の特定の代入について言及するために使用される。

30

#### 【0030】

量子プロセッサ 100 の文脈では、「プログラミングサブシステム」という用語は、一般に、量子プロセッサ 100 のプログラマブル要素ならびに他の関連制御回路および / または命令にプログラマブルパラメータ(例えば、 $h_i$  および  $J_{ij}$  項)を適用するために使用されるインターフェース(例えば、「プログラミングインターフェース」122、123 および 125)について説明するために使用される。以前に説明されるように、プログラミングサブシステムのプログラミングインターフェースは、他のサブシステムと通信することができ、他のサブシステムは、量子プロセッサから分離することも、プロセッサ上の局所に含めることもできる。同様に、量子プロセッサ 100 の文脈では、「発展サブシステム」という用語は、一般に、量子プロセッサ 100 のプログラマブル要素ならびに他の関連制御回路および / または命令を発展させるために使用されるインターフェース(例えば、「発展インターフェース」121 および 124)について説明するために使用される。例えば、発展サブシステムは、アニーリング信号線およびそれらの対応するキュービット(101、102)に対するインターフェース(121、124)を含み得る。

40

#### 【0031】

50

また、量子プロセッサ 100 は、読み出し素子 141 および 142 も含み得、読み出し素子 141 は、キュービット 101 の状態を読み出すように構成され、読み出し素子 142 は、キュービット 102 の状態を読み出すように構成される。図 1 に示される実施形態では、読み出し素子 141 および 142 の各々は、対応するキュービット（キュービット 101 および 102 のそれぞれ）と誘導結合するように構成されたそれぞれの DC-SQUID を備える。量子プロセッサ 100 の文脈では、「読み出しサブシステム」という用語は、一般に、ビット列を生成するため、量子プロセッサにおけるキュービット（例えば、キュービット 101 および 102）の最終状態を読み出すために使用される読み出し素子 141 および 142 について説明するために使用される。また、読み出しサブシステムは、ルーティング回路（例えば、ラッチ要素、シフトレジスタまたはマルチプレクサ回路）などの他の要素を含むこと、ならびに／または、代替の構成（例えば、XYZ アドレス可能アレイ、XYZ アドレス可能アレイなど）で配置することもできる。また、キュービット読み出しは、PCT 特許出願国際公開第 2012-064974 号パンフレットで説明されているようなものなどの代替の回路を使用して実行することもできる。10

#### 【0032】

図 1 は、2 つの物理的なキュービット 101、102 と、1 つの結合器 111 と、2 つの読み出し素子 141、142 のみを示しているが、量子プロセッサ（例えば、プロセッサ 100）は、大多数（例えば、数百、数千またはそれ以上）のキュービット、結合器および／または読み出し素子を含む、いかなる数のキュービット、結合器および／または読み出し素子も使用することができる。異なる（例えば、より大きな）数の計算コンポーネントを有するプロセッサへの本明細書の教示の適用は、当業者であれば、容易に明らかであるはずである。20

#### 【0033】

図 1 に示される素子の少なくともいくつかは、明瞭さをさらによくするために簡易化されている。例として、キュービット（101、102）の構造および読み出し素子（141、142）に対するインターフェースは、図 1 では、混乱を低減するために簡易化されている。いくつかの応用では量子プロセッサ 100 の簡易化された回路で十分であるが、量子プロセッサは、図 1 で示されるものよりかなり複雑なキュービット回路および／または読み出しスキームを使用することができる。

#### 【0034】

図 2 は、中間ラッチ素子 251 を通じて DC-SQUID 磁力計（読み出し素子）241 と結合された超電導磁束キュービット 201 を含む量子プロセッサ 200 の一部分の概略図である。図 2 は、例えば、図 1 からのキュービット 101 および読み出し素子 141 とのそのインターフェースのより詳細な概略図を表し得る。キュービット 201 は、米国特許出願公開第 2011-0057169 号明細書の教示に従って、ジョセフソン接合の非対称性を補正するためのメカニズムを提供するために「複合ジョセフソン接合」まで拡大された複合ジョセフソン接合構造 231 を含む。その結果、図 1 からのプログラミングインターフェース 121 は、複合ジョセフソン接合構造 231 に印加される信号を制御するために 3 つのインターフェース 221a、221b および 221c まで拡大された。キュービット 201 は、以前に説明されるように、システムハミルトニアンの  $h_i$  項を実現するためにプログラミングインターフェース 222 と結合されるが、キュービット 201 は、米国特許出願公開第 2011-0057169 号明細書の教示に従って、キュービット 201 のインダクタンスを調整するためのメカニズムを提供するためにインダクタンスチューナ 261 も含む。インダクタンスチューナ 261 は、追加のプログラミングインターフェース 226 との結合によって制御される。キュービット 201 に含めることも、キュービット 201 と結合することもできる追加の素子（例えば、図 1 からの結合素子 111 などの他のキュービットと通信するための結合素子および／または米国特許出願公開第 2011-0060780 号明細書で教示されるようなアニーリングの間のキュービット永久電流の変化を補償するためのメカニズムなど）は、図 2 では、混乱を低減するために示されていない。304050

## 【0035】

キュービット201の状態は、キュービット201の永久電流によって定義される。キュービット201の永久電流は、米国特許第8,169,231号明細書で説明されているように、ラッチ素子251を通じてキュービット201をDC-SQUID磁力計241と結合することによって読み出される。ラッチ素子251は、米国特許第8,169,231号明細書の教示に従って、シフトレジスタ271と誘導結合されるものとして示されている。ラッチ素子251は、プログラミングインターフェース227によって制御され、磁力計241は、プログラミングインターフェース228によって制御される。キュービットパラメータおよび／またはキュービット挙動の特徴付けに関連する実験のために設計されているキュービットシステムは、システムの他のパラメータ（例えば、いくつかの／すべてのジョセフソン接合の臨界電流、キュービットインダクタンスなど）を直接測定するためのメカニズムを含み得るが、そのようなメカニズムは、実際の計算問題を解くように設計された量子プロセッサに圧倒的な複雑性を加え、最終的にはそのスケーラビリティを妨げる可能性がある。10 図1からのプロセッサ100などの量子プロセッサでは、計算の目的のためにキュービットの状態を読み出すように設計された単一の読み出しメカニズムは、利用可能なもののすべてであり得る（そのようなものは、例えば、プロセッサの要素の数を低減すること、プロセッサの物理的なサイズおよび／または面密度を低減すること、ならびに／あるいは、プロセッサとインターフェースを取るために必要なプログラミングチャネルの数を制限することによって、プロセッサーアーキテクチャの物理的なスケーラビリティを高める）。プロセッサのキュービットの他のすべてのパラメータならびにキュービット間およびキュービットと他の素子との間の相互作用を支配するパラメータの大部分は、一般に、様々なプログラミングインターフェースを通じて印加された信号に応答したキュービットの永久電流の測定から推測することができる。例えば、キュービット201のパラメータおよびキュービット201とラッチ素子231と磁力計241との間の相互作用を支配するパラメータの大部分は、一般に、プログラミングインターフェース221a、221b、221c、222、226、227および228を通じて印加された信号に応答したキュービット201の永久電流の測定から推測することができる。20 しかし、磁力計241によって実際に読み出されるキュービット201の永久電流の値は、キュービット201とラッチ素子251との間の結合（すなわち、示される誘導結合に対するキュービット201とラッチ素子251との間の相互インダクタンス）。しかし、当業者であれば、ガルバニック結合などの他の結合スキームも同様に使用できることが理解されよう）およびラッチ素子251と磁力計241との間の結合（すなわち、ラッチ素子251と磁力計241との間の相互インダクタンス）を含む、多くの介入パラメータに依存する。30 量子プロセッサの要素を較正する必要性の一部は、そのような介入パラメータ（例えば、素子間の相互インダクタンス）を特徴付ける必要性に起因し、本明細書で説明される様々な実施形態は、改善された較正手順のためのシステムおよび方法を提供する。

## 【0036】

ここでは、キュービット201の永久電流を較正するための例示的な手順について説明する。この説明の目的は、図2の回路および素子を使用する量子プロセッサーアーキテクチャにおけるキュービット201の永久電流を較正するために必要とされる中間較正ステップの数を強調することである。この説明は、单なる例示のために提供される。当業者であれば、代替の超電導アーキテクチャ、イオントラップアーキテクチャ、フォトニックアーキテクチャなどや、ゲート／回路ベースの量子アルゴリズムを実行するように設計されたアーキテクチャなど、他の量子プロセッサーアーキテクチャでも同様の状況が起こり得ることが理解されよう。40

## 【0037】

キュービット201の永久電流は、以下の一連の行為または動作において、プロセッサ200の回路および素子を使用して較正することができる。

1) DC-SQUID 241の永久電流

【数8】

$$|I_{ro}^p|$$

が較正される。独立して較正された電流が、プログラミングインターフェース228を介してDC-SQUID 241に印加され、DC-SQUID磁束バイアスの関数としてスイッチング電流が測定される。次いで、モデルを使用して、独立して較正された電流が解除された際（有限磁束バイアスの存在下で）の

【数9】

$$|I_{ro}^p|$$

10

が推定される。そのようなモデルの例は、スイッチング電流を臨界電流と同等と見なす。

2) DC-SQUID 241とラッチ素子251との間の相互インダクタンス281 ( $M_{281}$ ) が較正される。 $M_{281}$ を通じてDC-SQUID 241からラッチ素子251に信号が印加される。ラッチ素子251の磁束周期が独立して較正されているという条件で、プログラミングインターフェース227を介して印加される信号 $\phi_{227}$ によって、DC-SQUID 241からの信号をラッチ素子251でヌル値にする。次いで、 $M_{281}$ を以下の式の通り計算することができる。

【数10】

20

$$M_{281} = \phi_{227}/2|I_{ro}^p|$$

3) ラッチ素子251の永久電流

【数11】

$$|I_{qfp}^p|$$

30

が較正される。ラッチ素子251の状態をラッチするため、プログラミングインターフェース227を介してラッチ素子251に信号 $\phi_{227}$ が印加される。このラッチされた状態は、DC-SQUID 241を介して読み出され、プログラミングインターフェース228を通じて印加される信号 $\phi_{228}$ によってヌル値にする。次いで、

【数12】

$$|I_{qfp}^p|$$

を以下の式の通り計算することができる。

【数13】

40

$$|I_{qfp}^p| = \phi_{228}/2M_{281}$$

4) ラッチ素子251とキュービット201との間の相互インダクタンス282 ( $M_{282}$ ) が較正される。この場合もやはり、ラッチ素子251の状態をラッチするため、プログラミングインターフェース227を介してラッチ素子251に信号 $\phi_{227}$ が印加される。次いで、このラッチされた状態（すなわち、

【数14】

$$|I_{qfp}^p|$$

) は、M<sub>2 8 2</sub> を通じてキュービット201と結合される。キュービット201の周期が独立して較正されているという条件で、ラッチ素子251からの信号は、プログラミングインターフェース222を介して印加される信号 M<sub>2 2 2</sub> によって、キュービット201でヌル値にする。次いで、M<sub>2 8 2</sub> を以下の式の通り計算することができる。

【数15】

$$M_{282} = \Phi_{222}/2|I_{qfp}^p|$$

10

5) 次いで、キュービット201の永久電流

【数16】

$$|I_{\text{キュービット}}^p|$$

が較正される。トンネル障壁を作り、キュービット201の永久電流状態を局所化するため、プログラミングインターフェース221bを介して信号が印加される。この状態は、ラッチ素子251における磁束 M<sub>2 2 1</sub> の変化として検出される。ラッチ素子251の周期が既に較正されていることを前提として、

20

【数17】

$$|I_{\text{キュービット}}^p|$$

を以下の式の通り計算することができる。

【数18】

$$|I_{\text{キュービット}}^p| = \Delta\Phi/2M_{282}$$

30

【0038】

上記で概説される較正手順は、一部の人々によっては多少複雑であると見なされ得る。プロセッサ200の回路および素子を使用するキュービット201の永久電流

【数19】

$$|I_{\text{キュービット}}^p|$$

の較正は、キュービット201とラッチ素子251との間の相互インダクタンス M<sub>2 8 2</sub> の較正に依存し、相互インダクタンス M<sub>2 8 2</sub> の較正は、ラッチ素子251の永久電流

40

【数20】

$$|I_{qfp}^p|$$

の較正に依存し、ラッチ素子251の永久電流の較正は、ラッチ素子251とD C - S Q U I D 241との間の相互インダクタンス M<sub>2 8 1</sub> の較正に依存し、相互インダクタンス M<sub>2 8 1</sub> の較正は、D C - S Q U I D 241の永久電流

## 【数21】

$|I_{ro}^p|$

の較正に依存する。いくつかの実施形態では、依存性における誤差は、まるで誤差が独立しているかのように伝搬し、全誤差は、相対誤差の和の累乗根である。上記で概説される較正手順で行う必要がある測定は大多数あり、較正パラメータ間の一連の複雑な依存性をもたらす。測定誤差（小さな誤差でさえ）は必然的なものであり、較正パラメータのいずれか1つにおける誤差は、他のパラメータに終始伝搬され得る（そして、誤差は、伝搬される際および／または他の測定誤差と組み合わされる際に増大し得る）。その上、上記の較正手順におけるパラメータの少なくとも1つ（すなわち、

10

## 【数22】

$|I_{ro}^p|$

）は、現実との何らかの相違をほぼ常にもたらすモデル依存推定に依存する。上記で概説される手順は、時間のかかる、資源集約的なものであり（数百のキューピットを有するプロセッサの較正に数週間程度を要する）、結果として得られる較正パラメータの正確性／精度は、大多数の測定およびパラメータ間の依存性によって制限される。明らかに、当技術分野において、量子プロセッサの要素を較正するための改善されたシステムおよび方法の必要性がある。

20

## 【0039】

この明細書および添付の特許請求の範囲全体を通じて、較正手順の間に測定および／または較正された量子プロセッサの要素および／またはパラメータは、「決定可能なパラメータ」と呼ばれる。上記で概説される例示的な較正手順からの例示的な決定可能なパラメータは、キューピット永久電流

## 【数23】

$|I_{\text{キューピット}}^p|$

30

と、M<sub>2 8 1</sub>およびM<sub>2 8 2</sub>などの素子間の相互インダクタンスと、ラッチ素子永久電流

## 【数24】

$|I_{qfp}^p|$

と、DC-SQUID永久電流

## 【数25】

$|I_{ro}^p|$

40

とを含む。より一層確実にするため、この明細書および添付の特許請求の範囲全体を通じて、「決定可能なパラメータ」という用語は、直接測定を介しておよび／または測定に基づく計算を介して値を決定することができる量子プロセッサの任意の素子またはコンポーネントの任意のパラメータについて言及するために使用される。決定可能なパラメータは、例えば、特定の値を有するように設計されたパラメータを含み得るが、実在する物理的な素子の製作の不正確性により、量子プロセッサの適正な動作を確保するため、較正の間に決定されたその実際の値を有する必要がある。

## 【0040】

本明細書で説明される様々な実施形態は、量子プロセッサの要素を較正するための改善されたシステムおよび方法を提供する。例えば、上記で説明される較正手順は、量子プロ

50

セッサーアーキテクチャに専用較正信号源を導入することによって大幅に簡易化することができる。この簡易化により、重要なパラメータ（キュービット永久電流など）の較正に必要とされる測定の数を低減することができ、より高速なおよび／またはより正確な較正手順をもたらすことができる。説明に役立つ例として、専用較正信号源は、以下でさらに詳細に説明されるような超電導量子プロセッサーアーキテクチャにおける超電導信号線（すなわち、超電導電流経路）によって実現することができる。しかし、当業者であれば、専用較正信号源は、その特定のタイプの量子プロセッサに適切な、通信可能なハードウェアのどのような形式をも使用して、いかなる代替のタイプの量子プロセッサーアーキテクチャ（例えば、フォトニック量子プロセッサ、量子ドット量子プロセッサなど）でも同様に実装できることが理解されよう。

10

#### 【0041】

図3は、本システムおよび方法による、超電導磁束キュービット301および専用較正信号源390を含む量子プロセッサ300の一部分の概略図である。キュービット301は、図2からのプロセッサ200のキュービット201とラッチ素子251との間の結合と同様に、ラッチ素子351と誘導結合される。超電導プロセッサ300では、較正信号源390は、ラッチ素子351とガルバニック結合された超電導電流経路によって形成された超電導信号線である。較正信号源390は、例えば、量子プロセッサ300の外部にあり、室温で収納され得る、信号生成および制御電子機器（図3では図示せず）と結合される。較正信号源390は、量子プロセッサ300の要素を較正するために使用できる、独立して較正された電流を提供する。較正信号源390中の電流は、ラッチ素子351の臨界電流（ラッチ素子351におけるジョセフソン接合によって決定されるような）よりもかなり大きいものであり得、その結果、独立して較正された電流の圧倒的大部分は、ラッチ素子351とキュービット301との間の相互インダクタンス $M_{3\ 8\ 2}$ を通じてルーティングされる。したがって、較正信号源390を使用することにより、量子プロセッサ200のための以前に説明された例示的な較正手順の行為1～3を省略することができ、ラッチ素子351とキュービット301との間の相互インダクタンス $M_{3\ 8\ 2}$ を較正信号源390から直接較正することができる。これにより、例えば、キュービット201の永久電流の較正と比較して、キュービット301の永久電流の較正における測定および依存性（ならびに関連誤差および伝搬される誤差）の数が大幅に低減される。この低減を示すため、ここでは、プロセッサ300のキュービット301の永久電流を較正するための例示的な手順について説明する。

20

#### 【0042】

キュービット301の永久電流は、以下の一連の行為または動作において、プロセッサ300の回路および素子を使用して較正することができる。

1) ラッチ素子351とキュービット301との間の相互インダクタンス382（ $M_{3\ 8\ 2}$ ）が較正される。独立して較正された電流が超電導電流経路390を通じて伝送される。この電流の圧倒的大部分が相互インダクタンス $M_{3\ 8\ 2}$ を通じて流れることを保証するため、プログラミングインターフェース327を使用して、約1/2%の磁束信号でラッチ素子351の複合ジョセフソン接合に磁束バイアスを印加することができる。次いで、印加バイアスとして超電導電流経路390の電流を使用してキュービット301の磁束周期Pが測定される。次いで、 $M_{3\ 8\ 2}$ を以下の式の通り計算することができる。

30

$$M_{3\ 8\ 2} = I_0 / P$$

2) 次いで、キュービット301の永久電流

40

#### 【数26】

$$|I_{\text{キュービット}}^p|$$

が較正される。トンネル障壁を作り、キュービット301の永久電流状態を局所化するため、プログラミングインターフェース321bを介して信号が印加される。この状態は、ラッチ素子351における磁束の変化として検出される。ラッチ素子351の周期が

50

既に較正されていることを前提として、

【数27】

$$|I_{\text{キュービット}}^p|$$

を以下の式の通り計算することができる。

【数28】

$$|I_{\text{キュービット}}^p| = \Delta\Phi / 2M_{382}$$

10

【0043】

明らかに、較正信号源390を使用してプロセッサ300のキュービット301の永久電流を較正するための手順は、専用較正信号源なしでプロセッサ200のキュービット201の永久電流を較正するための手順よりはるかに簡単である。プロセッサ300に対して説明される較正手順は、プロセッサ200に対して説明される較正手順と比較して、より少ない測定、より少ない計算行為およびより少ないモデル依存推定（例えば、モデル依存推定なし）を含む。その結果、プロセッサ300における較正信号源390の追加により、プロセッサ要素のより高速なおよび／またはより高い精度／正確性の較正が可能になる。プロセッサ要素の精度／正確性の高い較正は少なくとも10倍は増加されると信じられている。

20

【0044】

上記で説明されるキュービット301の永久電流を較正するための例示的な手順は、単なる例示のために提供され、本システムおよび方法をキュービット永久電流の較正に限定することを意図しない。本システムおよび方法によれば、量子プロセッサは、多数の素子の少なくとも第1の素子が決定可能なパラメータを含む多数の素子（すなわち、任意の数の素子）であって、多数のキュービットを含む多数の素子と、多数の素子の少なくとも第1の素子と通信可能に結合できる較正信号源であって、既知の値の較正信号を提供する較正信号源と、多数の素子の少なくとも第1の素子と通信可能に結合できる読み出しシステムであって、第1の素子の決定可能なパラメータに対する値を決定するため、較正信号と第1の素子の決定可能なパラメータの両方に依存する信号を読み出す読み出しシステムとを備え得る。較正信号源は、較正信号源と直接的に通信可能に結合できる第1の素子および／または較正信号源と間接的に通信可能に結合できる第1の素子（例えば、較正信号源との通信可能な結合が少なくとも第2の素子によって仲介される第1の素子）を含む、量子プロセッサ内の任意の決定可能なパラメータに対する値を決定するために使用することができる。本システムおよび方法のさらなる利益は、単一の較正信号源を使用して、較正信号（例えば、独立して較正された電流）を量子プロセッサーアーキテクチャの複数の素子（例えば、第1の素子、第2の素子、第3の素子など）と通信可能に結合できることである。

30

【0045】

図4は、本システムおよび方法による、2つの超電導磁束キュービット401、402および単一の専用較正信号源490を含む量子プロセッサ400の一部分の概略図である。キュービット401は、ラッチ素子451と誘導結合され、キュービット402は、ラッチ素子452と誘導結合される。較正信号源490は、超電導電流経路によって形成された超電導較正線である。超電導電流経路490は、ラッチ素子451とラッチ素子452の両方と直列にガルバニック結合される。そのような直列結合は、超電導電流経路490を通じて電流が伝送される際、相互インダクタンスM<sub>482a</sub>と相互インダクタンスM<sub>482b</sub>の両方によって実質的に同じ電流が受信されることを意味する。

40

【0046】

典型的なアーキテクチャでは、量子プロセッサ300は、M<sub>482a</sub> = M<sub>482b</sub>となるように設計することができるが、実際には、製作プロセスにおける不均一性は、M<sub>48</sub>

50

$M_{2\ a}$  ～  $M_{4\ 8\ 2\ b}$  という状況を生み出し得る。 $M_{4\ 8\ 2\ a}$  および  $M_{4\ 8\ 2\ b}$  を較正する目的の少なくとも一部は、量子プロセッサ 400 の動作においてそのような不一致に対応／補償できるように、そのような不一致を特定することである。 $M_{4\ 8\ 2\ a}$  および  $M_{4\ 8\ 2\ b}$  や、キュービット 401 および 402 の各々の、それぞれの永久電流は、プロセッサ 300 の要素に対して以前に説明されたものと実質的に同じように、較正信号源 490 を使用して較正することができる。したがって、量子プロセッサ 400 のアーキテクチャ全体を通じて様々な要素と直接的に通信可能に結合できる単一の専用較正信号源 490 の追加は、図 2 からのプロセッサ 200 のような広範な一連の中間較正行為に依存することなく、プロセッサの要素の多く（例えば、すべて）を較正することができる絶対較正信号を提供する。較正信号源 490 を複数の素子と直接的に通信可能に結合することにより（プロセッサ 400 の一部分で示されるように）、図 2 からのプロセッサ 200 に対して概説される手順と比較して、より少ない数の行為または動作で各素子を較正することができるようになる。本システムおよび方法によれば、単一の較正信号源を使用して、量子プロセッサアーキテクチャのいかなる数の素子および／または要素との通信可能な結合および／または較正も行うことができる。

#### 【0047】

較正信号源が超電導電流経路の形態を取る超電導量子プロセッサアーキテクチャ（例えば、図 3 および 4 のそれぞれからの較正信号源 390 および 490）では、較正信号源の包含は、少なくとも 1 つの信号線をプロセッサに追加する。一般に、入力／出力システムを簡単にし、プロセッサ要素の面密度を低減するためにプロセッサの信号線の数を制限することが好ましい。しかし、較正信号源の包含は、量子プロセッサで使用される読み出しシステムの簡易化を可能にし得、したがって、使用される信号線の総数を低減することができる。例として、図 2 のプロセッサ 200（較正信号源を使用しない）は、ラッチ素子 251 を通じてキュービット 201 の状態を読み出すための D C - S Q U I D 241 とシフトレジスタ 271 の両方を含むが、図 3 からのプロセッサ 300（較正信号源 390 を含む）も、図 4 からのプロセッサ 400（較正信号源 490 を含む）も、同様の D C - S Q U I D 構造を含まない。いくつかのプロセッサアーキテクチャ（例えば、プロセッサ 100 および 200）では、読み出しシステムは、例えば、米国特許第 8,169,231 号明細書で説明されるような、個々のキュービットの状態をそれぞれ測定するための個々の読み出し素子（例えば、141、142 および 241）を使用することができる。

#### 【0048】

いくつかのプロセッサアーキテクチャ（例えば、プロセッサ 300 および 400）では、読み出しシステムは、例えば、米国特許第 8,169,231 号明細書および PCT 特許出願国際公開第 2012-064974 号パンフレットで説明されるような、キュービット状態をコピーし、コピーした状態を単一の読み出しメカニズム（または少数の読み出しメカニズム）にルーティングするシフトレジスタを使用することができる。シフトレジスタベースの読み出しシステムは、動作に必要な信号線がより少ないと有利であり得、キュービット特有の読み出し素子より動作が高速であり得るため計算の間の使用では有利であり得るが、シフトレジスタベースの読み出しシステムは、測定、依存性、誤差および伝搬される誤差の数を増加し得るため、いくつかの較正手順における使用では不利であり得る。計算の間にキュービットの状態を測定するためのシフトレジスタベースの読み出しシステムを使用する量子プロセッサは、依然として、プロセッサ要素の較正の間に使用するための個々のキュービット特有の読み出しメカニズムを含み得る。例えば、図 2 からの量子プロセッサ 200 は、D C - S Q U I D 241 とシフトレジスタ回路 271 の両方と結合されるラッチ素子 251 を含む。プロセッサ 200 では、計算の間にキュービット 201 の状態を読み出すためにシフトレジスタ 271 を使用することができるが、説明される例示的な較正手順を使用してキュービット 201 の永久電流を較正するために D C - S Q U I D 241 を使用することができる。言い換えれば、プロセッサ 200 は、計算の間に使用するためのシフトレジスタ 271 を有するだけでなく、較正の間だけ使用するための D C - S Q U I D 241 も含む。プロセッサ 200 の要素が較正された時点で、

DC - S Q U I D 241 はもはや使用されなくなるが、DC - S Q U I D 241 が使用中ではないときでさえ、DC - S Q U I D 241 のフットプリントがプロセッサ 200 上に残る（結果として得られる増加された面密度、回路要素間の潜在的なクロストーク、専用信号線などを含む）。本システムおよび方法によれば、専用較正信号源の包含は、較正目的でキュービット特有の読み出しメカニズムを含める必要もなく、シフトレジスタや、PCT 特許出願国際公開第 2012 - 064974 号パンフレットで説明される他のスキームなどのキュービット非特有の読み出しメカニズムの使用を可能にする。したがって、較正信号源の包含は、プロセッサアーキテクチャに信号線を追加するにもかかわらず、プロセッサアーキテクチャからキュービット特有の読み出しメカニズムを完全に取り除き、必要な信号線の総数の純減を生み出すことも可能にする。キュービット特有の読み出しメカニズム（例えば、DC - S Q U I D 241）を取り除くことにより、プロセッサアーキテクチャにおいてかなりの空間を開放し、プロセッサ要素のレイアウトを簡単にすることができる。

#### 【0049】

プロセッサ 300 とプロセッサ 400 の両方において、較正信号源（すなわち、390 および 490 のそれぞれ）は、ラッチ素子（すなわち、ラッチ素子 351 および ラッチ素子 451、452 のそれぞれ）とガルバニック結合され、ラッチ素子自体は、キュービット（すなわち、キュービット 301 および キュービット 401、402 のそれぞれ）と誘導結合される。しかし、これらの結合スキームは、単なる例示のために提供され、代替のプロセッサアーキテクチャは、代替の結合スキームを使用することができる。例えば、較正信号源は、ガルバニック結合とは対照的に、量子プロセッサの素子と誘導結合することができ、そのようなものには、対応する相互インダクタンスの較正が必要とされよう。同様に、較正信号源は、量子プロセッサのいかなる要素または素子とも通信可能に結合することができ、ラッチ素子と排他的に結合する必要はない。多くのアーキテクチャでは、誘導結合の相互インダクタンスを較正しなければならなくなることを避けるため、較正信号源を素子とガルバニック結合することが有利であり得、キュービットパラメータを較正する際に測定および依存性の数を最小限に抑えるため、較正信号源をキュービット「に近い」素子と結合することが有利であり得る。例えば、少ない行為または動作でキュービットパラメータを較正できるように、較正信号源をそれ自体がキュービットと直接的に通信可能に結合できる素子（ラッチ素子 351、451 および 452 の場合のように）と結合することが有利であり得る。較正信号源は、キュービットと直接結合することができますが、そのような構成では、較正信号源は、望ましくない形で、計算の間のキュービットへのノイズ源として機能し得る。多くのアーキテクチャでは、例えば、図 3 および 4 で描写されるように、較正信号源をそれ自体がキュービットと直接結合される素子と結合することによって、較正信号源とキュービットとの間にバッファを提供することが有利であり得る。

#### 【0050】

米国特許第 8,169,231 号明細書および PCT 特許出願国際公開第 2012 - 064974 号パンフレットで説明されるように、いくつかのアーキテクチャでは、ラッチ素子（例えば、ラッチ素子 351、451 および 452）は、キュービットとガルバニック結合することができる。ラッチ素子をキュービットとガルバニック結合することで、較正信号源は、依然として、ラッチ素子と結合することができるが、そのような構成では、較正信号源は、望ましくない形で、計算の間のキュービットへのノイズ源として機能し得る。しかし、ラッチ素子がキュービットとガルバニック結合される際、ラッチ素子は、シフトレジスタと誘導結合することもでき（例えば、図 2 ~ 4 に示されるように）、較正信号源は、依然として少なくとも 1 つの誘導結合によってキュービットから取り外されるよう、シフトレジスタと結合することができる。

#### 【0051】

本明細書で説明される様々な実施形態は、量子プロセッサアーキテクチャ内に 1 つまたは複数の専用較正信号源を導入することによって、量子プロセッサハードウェアにおける較正手順を容易にするためのシステムを提供する。また、本明細書で説明される様々な実

10

20

30

40

50

施形態は、これらのシステムを使用する改善された較正手順のための方法も提供する。

#### 【0052】

図5は、本システムおよび方法による、量子プロセッサの1つの要素のその較正を容易にするために較正信号源を使用する方法500を示すフロー図である。方法500は、4つの行為501、502、503および504を含むが、当業者であれば、代替の実施形態では、ある行為を省略することおよび／または追加の行為を追加することができるよう理解されよう。当業者であれば、示される行為の順番は、単なる例示を目的として示され、代替の実施形態では変更できることが理解されよう。

#### 【0053】

501では、較正信号源を介して量子プロセッサに（例えば、量子プロセッサの少なくとも1つの要素に）既知の値の較正信号が印加される。図3および4に示されるように、超電導量子プロセッサーアーキテクチャでは、較正信号源は、例えば、超電導電流経路によって形成された超電導較正線であり得る（例えば、図3からの390および図4からの490）。

10

#### 【0054】

502では、較正信号の少なくとも一部分が較正信号源から第1の素子に（例えば、量子プロセッサの第1の要素に）通信可能に結合される。第1の素子は、キュービット、キュービットと結合される素子（ラッチ素子または結合素子など）または量子プロセッサーアーキテクチャの他の任意の素子であり得る。較正信号源は、第1の素子と直接的に通信可能に結合できるか、または、較正信号源は、第1の素子と間接的に通信可能に結合できる。較正信号源が第1の素子と間接的に通信可能に結合できる場合、較正信号源は、第2の素子と直接的に通信可能に結合でき、第2の素子は、第1の素子と通信可能に結合でき、その結果、第2の素子は、較正信号源と第1の素子との間の通信可能な結合を仲介する。

20

#### 【0055】

503では、読み出しシステムを介して、較正信号と第1の素子の第1の決定可能なパラメータの両方に依存する信号が読み出される。以前に説明されるように、超電導量子プロセッサでは、第1の決定可能なパラメータは、相互インダクタンスまたは永久電流を含み得る。読み出しシステムは、第1の素子と直接的に通信可能に結合できるか、または、読み出しシステムは、第1の素子と間接的に通信可能に結合できる。読み出しシステムが第1の素子と間接的に通信可能に結合できる場合、読み出しシステムは、第2の素子と直接的に通信可能に結合でき、第2の素子は、第1の素子と通信可能に結合でき、その結果、第2の素子は、読み出しシステムと第1の素子との間の通信可能な結合を仲介する。

30

#### 【0056】

504では、読み出しシステムを介して読み出された信号に基づいて、第1の素子の第1の決定可能なパラメータに対する値が決定される。第1の決定可能なものに対する値は、読み出しシステムを介して読み出された信号の値であるか、または、読み出しシステムを介して読み出された信号の値から計算、推定もしくは推測された値であり得る。いくつかの事例では、第1の素子は、第2の決定可能なパラメータを含み得、方法500は、第1の素子の第1の決定可能なパラメータに対する値に少なくとも部分的にに基づいて、第1の素子の第2の決定可能なパラメータに対する値を決定するステップを含むように拡大することができる。例えば、図3からのプロセッサ300の文脈では、第1の素子は、キュービット301であり得、第1の素子の第1の決定可能なパラメータは、キュービット301とラッチ素子351との間の互インダクタンスM<sub>3 8 2</sub>であり得、キュービット301の第2の決定可能なパラメータは、キュービット301の永久電流

40

#### 【数29】

$$|I_{\text{キュービット}}^p|$$

であり得る。この例では、行為502に従って、較正信号の少なくとも一部分を較正信号源から第1の素子に通信可能に結合するステップは、キュービット301とラッチ素子3

50

51と間の相互インダクタンス  $M_{3\rightarrow 2}$  を介して、較正信号の少なくとも一部分を超電導電流経路 390 からキュービット 301 に間接的に通信可能に結合するステップを含む。

#### 【0057】

図4の文脈で以前に説明されるように、複数の素子の決定可能なパラメータを較正する目的で、単一の較正信号源は、量子プロセッサの複数の（すなわち、少なくとも2つの）素子と通信可能に結合することができる。

#### 【0058】

図6は、本システムおよび方法による、量子プロセッサの複数の要素のその較正を容易にするために較正信号源を使用する方法600を示すフロー図である。方法600は、7つの行為601、602、603、604、605、606および607を含むが、当業者であれば、代替の実施形態では、ある行為を省略することおよび／または追加の行為を追加することができることが理解されよう。当業者であれば、示される行為の順番は、單なる例示を目的として示され、代替の実施形態では変更できることが理解されよう。行為601～604は、図5からの方法500の行為501～504と本質的に同じである。

#### 【0059】

手短には、601では、較正信号源を介して量子プロセッサに（例えば、量子プロセッサの少なくとも1つの要素に）既知の値の較正信号が印加される。602では、較正信号の少なくとも一部分が較正信号源から第1の素子に（例えば、量子プロセッサの第1の要素に）通信可能に結合される。603では、読み出しシステムを介して、較正信号と第1の素子の第1の決定可能なパラメータの両方に依存する信号が読み出される。604では、読み出しシステムを介して読み出された信号に基づいて、第1の素子の第1の決定可能なパラメータに対する値が決定される。方法600は、行為605～607を続行し、行為605～607は、量子プロセッサの第2の素子の決定可能なパラメータに対する値を決定するために同じ較正信号源を使用することについて説明する。605では、較正信号の少なくとも一部分が較正信号源から少なくとも第2の素子に（例えば、量子プロセッサの少なくとも第2の要素に）通信可能に結合される。行為605は、行為602と並行して（すなわち、行為602と同時に）起こり得るか、または、行為602と連続して（すなわち、行為602の前後に）起こり得る。606では、読み出しシステムを介して、較正信号と少なくとも第2の素子の第1の決定可能なパラメータの両方に依存する信号が読み出される。行為606は、行為603と並行して（すなわち、行為603と同時に）起こり得るか、または、行為603と連続して（すなわち、行為603の前後に）起こり得る。607では、読み出しシステムを介して読み出された、較正信号と少なくとも第2の素子の第1の決定可能なパラメータの両方に依存する信号に基づいて、少なくとも第2の素子の第1の決定可能なパラメータに対する値が決定される。行為607は、行為604と並行して（すなわち、行為604と同時に）起こり得るか、または、行為604と連続して（すなわち、行為604の前後に）起こり得る。行為605～607のいずれかまたはすべては、行為601～604のいずれかまたはすべてと並行して（すなわち、行為601～604のいずれかまたはすべてと同時に）あるいは、行為601～604のいずれかまたはすべてと連続して（すなわち、行為601～604のいずれかまたはすべての前後に）起こり得る。

#### 【0060】

図6からの方法600は、量子プロセッサの少なくとも2つの素子を較正するために較正信号源を使用することについて説明する。いくつかの量子プロセッサーアーキテクチャは、多数の素子を含み得、各素子は、少なくとも1つのそれぞれの決定可能なパラメータを含み、較正信号源は、多数の素子の各素子と通信可能に結合できる。そのようなアーキテクチャでは、較正信号源は、多数の素子の各素子を較正するために使用することができる。

#### 【0061】

図7は、本システムおよび方法による、量子プロセッサの多数の素子の各々のその較正を容易にするために較正信号源を使用する方法700を示すフロー図である。方法700

10

20

30

40

50

は、4つの行為701、702、703および704を含むが、当業者であれば、代替の実施形態では、ある行為を省略することおよび／または追加の行為を追加することができる。当業者であれば、示される行為の順番は、単なる例示を目的として示され、代替の実施形態では変更できることが理解されよう。

#### 【0062】

701では、較正信号源を介して量子プロセッサに既知の値の較正信号が印加される。702では、較正信号の少なくとも一部分が較正信号源から多数の素子の各素子に通信可能に結合される。703では、読み出しシステムを介して、多数の素子の各素子からそれぞれの信号が読み出され、それぞれの信号の各々は、較正信号と、信号が読み出されたそれぞれの素子の各々の、それぞれの決定可能なパラメータの両方に依存する。704では、読み出しシステムを介して読み出されたそれぞれの信号の各々に基づいて、それぞれの素子の各々の、それぞれの決定可能なパラメータに対するそれぞれの値が決定される。方法700の目的のため、「多数の素子」は、量子プロセッサーアーキテクチャのすべての素子または量子プロセッサーアーキテクチャのすべての素子のサブセットを含み得る。例えば、図4に示されるスキームを使用すると、「多数の素子」は、キュービットと直接的に誘導結合される各ラッチ素子（すなわち、ラッチ素子451および452）を含み得るか、または、多数の素子は、各キュービット（すなわち、キュービット401および402）を含み得る。様々な量子プロセッサーアーキテクチャでは、較正信号源は、プロセッサーアーキテクチャの各要素およびあらゆる要素と、または、プロセッサーアーキテクチャの要素のサブセットと、通信可能に結合することができる。いくつかの量子プロセッサーアーキテクチャは、単一の較正信号源よりむしろ、複数の異なる較正信号源（すなわち、複数の独立して制御された較正信号源）によってより良好に機能が果たされ得る。10

#### 【0063】

大部分の量子プロセッサーアーキテクチャでは、較正信号源の導入は、それに伴う関連課題を抱える。例えば、図3および4の超電導量子プロセッサーアーキテクチャでは、超電導電流経路の形態の超電導較正線は、非意図的に、望ましくない形で、漂遊相互インダクタンスを通じて量子プロセッサの要素に結合され得る。超電導電流経路のレイアウトおよび量子プロセッサの要素のレイアウトは、公知の超電導集積回路設計の実践に従って（例えば、素子間の間隔および素子の幾何学を制御することによって、遮蔽構造を実装することによってなど）、漂遊相互インダクタンス（例えば、「クロストーク」）を通じるそのような望ましくない結合を最小限に抑えるように設計されるべきである。別の潜在的な課題は、較正信号源が、量子プロセッサの要素にノイズを送入して結合する導管を導入する場合があることである。以前に説明されるように、較正信号源は、プロセッサ要素の較正の間だけ使用することができるが、プロセッサが計算に使用される間は、量子プロセッサーアーキテクチャに物理的に埋め込まれたままの状態である。較正信号源が解除された場合でさえ、望ましくないノイズは、較正信号源から量子プロセッサの要素に結合され得る。そのようなノイズ（存在する場合）は、較正が完了した時点でその駆動メカニズムから較正信号源を電気的および／または物理的に減結合することによって、少なくとも部分的に低減することができる。例えば、較正信号源として室温電子機器によって制御された超電導電流経路を使用する超電導量子プロセッサでは、超電導電流経路は、較正手順が完了した後で、室温電子機器から少なくとも部分的に減結合することができる（例えば、室温電子機器回路の抵抗を開放することによって、またはそうでなければ、超電導電流経路の電流の流れを途絶するによって）。30

#### 【0064】

示される実施形態の上記の説明は、要約書で説明されるものも含めて、網羅的であることも、まさにその開示される形態に実施形態を限定することも意図しない。特定の実施形態および例は本明細書では例示を目的として説明されるが、当業者によって認識されるように、本開示の精神および範囲から逸脱することなく、様々な同等の変更を行うことができる。本明細書で提供される様々な実施形態の教示は、必ずしも上記で一般に説明される量子計算のための例示的な方法とは限らず、他の量子計算の方法に適用することができる4050

。

## 【0065】

上記で説明される様々な実施形態は、さらなる実施形態を提供するために組み合わせることができる。この明細書で言及されるおよび／または出願データシートに掲載される米国特許、米国特許出願公開、米国特許出願、国際（PCT）特許出願のすべて（米国仮特許出願第61/762,704号明細書を含む）は、その全体が参照により本明細書に組み込まれる。実施形態の様子は、さらなる実施形態を提供するため、様々な特許、出願および公開のシステム、回路および概念を使用するように、必要に応じて変更することができる。

## 【0066】

これらのおよび他の変更は、上記の詳細な説明を踏まえて実施形態に行うことができる。一般に、以下の特許請求の範囲では、使用される用語は、本明細書および特許請求の範囲で開示される特定の実施形態に特許請求の範囲を限定するものと解釈すべきではなく、そのような特許請求の範囲が権利付与する均等物の全範囲と共にすべての可能な実施形態を含むものと解釈すべきである。それに従って、特許請求の範囲は、本開示によって制限されない。

10

【図1】

【図2】

【図3】

FIGURE 3

【図4】

FIGURE 4

【図5】

図5

【図6】

図6

【四七】

## 【図8】

---

フロントページの続き

(72)発明者 ハリス , リチャード , ジー .

カナダ国 , ブリティッシュ コロンビア州 ブイ5シー 4エム9 , バーナビー , ベータ アベニ

ュー 3033

審査官 多胡 滋

(56)参考文献 国際公開第2009 / 143166 (WO , A2 )

(58)調査した分野(Int.Cl. , DB名)

G 06 N 99 / 00

H 01 L 39 / 22

H 03 K 19 / 195

B 82 Y 10 / 00