(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4065104号

(P4065104)

(45) 発行日 平成20年3月19日(2008.3.19)

(24) 登録日 平成20年1月11日(2008.1.11)

(51) Int.Cl.

**H01L 29/861 (2006.01)**

**H01L 21/8222 (2006.01)**

**H01L 27/06 (2006.01)**

**H01L 21/331 (2006.01)**

**H01L 29/73 (2006.01)**

F 1

H01L 29/91 L

H01L 27/06 1 O 1 D

H01L 29/72 Z

請求項の数 5 (全 14 頁)

(21) 出願番号 特願2000-392221 (P2000-392221)

(22) 出願日 平成12年12月25日 (2000.12.25)

(65) 公開番号 特開2002-198541 (P2002-198541A)

(43) 公開日 平成14年7月12日 (2002.7.12)

審査請求日 平成17年5月20日 (2005.5.20)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100131071

弁理士 ▲角▼谷 浩

(72) 発明者 大川 重明

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 大古田 敏幸

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

審査官 小野田 誠

最終頁に続く

(54) 【発明の名称】半導体集積回路装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

一導電型の半導体基板と、

該基板表面に積層されている逆導電型の第1のエピタキシャル層と、

前記基板と前記第1のエピタキシャルとの間に形成されている高濃度不純物拡散層からなる第1の逆導電型の埋め込み層と重畳して形成されている高濃度不純物拡散層からなる第1の一導電型の埋め込み層と、

前記第1のエピタキシャル層表面に積層されている逆導電型の第2のエピタキシャル層と、

前記第1のエピタキシャル層と前記第2のエピタキシャル層との間に形成されている高濃度不純物拡散層からなる第2の一導電型の埋め込み層および高濃度不純物拡散層からなる第2の逆導電型の埋め込み層と、

前記第2のエピタキシャル層表面から前記第2の一導電型の埋め込み層まで拡散して形成されている高濃度不純物拡散層からなる一導電型の拡散領域と、

前記第2のエピタキシャル層表面から前記第2の逆導電型の埋め込み層まで拡散して形成されている高濃度不純物拡散層からなる第1の逆導電型の拡散領域と、前記第2の一導電型の埋め込み層と前記一導電型の拡散領域とで挟まれる領域に配置されている高濃度不純物拡散層からなる第2の逆導電型の拡散領域とを有するダイオード素子を内蔵する半導体集積回路装置において、

前記第1の一導電型の埋め込み層と前記一導電型の拡散領域とは、前記第2の一導電型の

10

20

埋め込み層を介して連結して形成され、

前記第1の逆導電型の埋め込み層と前記第1の逆導電型の拡散領域とは、前記第2の逆導電型の埋め込み層を介して連結して形成され、

前記第1のエピタキシャル層と前記第2のエピタキシャル層の合計膜厚が8～16μm程度になるように形成され、

前記第1の一導電型の埋め込み層と前記第2の逆導電型の拡散領域とが、深さ方向に隔てて形成されていることを特徴とする半導体集積回路装置。

#### 【請求項2】

前記第2の逆導電型の拡散領域に重畠して逆導電型のウェル領域が形成されていることを特徴とする請求項1記載の半導体集積回路装置。 10

#### 【請求項3】

前記第1の逆導電型の拡散領域および前記一導電型の拡散領域はアノード導出領域として、前記第2の逆導電型の拡散領域はカソード導出領域として形成されていることを特徴とする請求項1記載の半導体集積回路装置。

#### 【請求項4】

一導電型の半導体基板を準備する工程と、該基板に不純物を拡散させ、ダイオード素子形成領域に第1の逆導電型の埋め込み層を形成する工程と、

前記基板上に不純物を拡散させ前記ダイオード素子形成領域に前記第1の逆導電型の埋め込み層と重畠して第1の一導電型の埋め込み層を形成する工程と、

前記基板上に逆導電型の第1のエピタキシャル層を積層する工程と、 20

該第1のエピタキシャル層上に不純物を拡散し、第2の逆導電型の埋め込み層を形成して、前記第1の逆導電型の埋め込み層と連結する工程と、

前記ダイオード素子形成領域に第2の一導電型の埋め込み層を形成する工程と、

前記第1のエピタキシャル層上に逆導電型の第2のエピタキシャル層を前記第1のエピタキシャル層と前記第2のエピタキシャル層の合計膜厚が8～16μm程度になるよう積層する工程と、

該第2のエピタキシャル層上に不純物を拡散し、前記ダイオード素子形成領域に第1の逆導電型の拡散領域を形成し、 25

前記第2の逆導電型の埋め込み層を介して前記第1の逆導電型の埋め込み層と連結する工程と、 30

該第2のエピタキシャル層上に不純物を拡散し、前記ダイオード素子形成領域に一導電型の拡散領域を形成し、前記第2の一導電型の埋め込み層を介して前記第1の一導電型の埋め込み層と連結する工程と、

前記ダイオード素子形成領域の該第2のエピタキシャル層上に逆導電型の拡散領域を形成する工程とを有することを特徴とする半導体集積回路装置の製造方法。

#### 【請求項5】

前記ダイオード素子形成領域の前記第2の一導電型の埋め込み層を形成する工程は、前記第1の一導電型の埋め込み層と前記一導電型の拡散領域とを連結させ、前記第1の一導電型の埋め込み層と前記逆導電型の拡散領域とを隔てて形成する工程であることを特徴とする請求項4記載の半導体集積回路装置の製造方法。 40

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、出力トランジスタ保護に適したスパークキラーダイオードを内蔵した半導体集積回路装置に関する。

##### 【0002】

##### 【従来の技術】

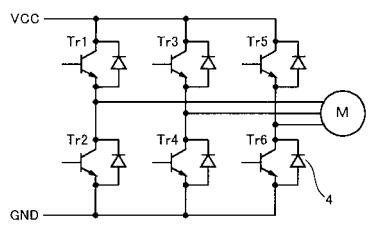

例えば、3相モータドライバは、図11のように直流電源VCC、GND間に直列接続されたトランジスタ(Tr1 Tr2、Tr3 Tr4、Tr5 Tr6)が並列接続され、Tr1 Tr2、Tr3 Tr4およびTr5 Tr6の間から取り出された出力端子

をモータMに接続した回路構成を採用する。

**【0003】**

このように負荷が誘導性負荷の場合、モータの回転／停止に伴う正／逆方向の起電力が発生する。従来は、IC化された直列接続トランジスタのコレクタ・エミッタ間に保護ダイオードを接続し、前記逆方向起電力によって出力端子がGND電位より低く又はVCC電位より高くなつた際にダイオード4がONする事で前記起電力を固定電位へ逃がし、直列接続されたトランジスタを含むICの内部を保護していた。特にダイオード4に数Aもの大電流を流す場合は、ダイオード4として個別部品を用いて構成していた。

**【0004】**

ここで、ユーザ側からすれば、機器の部品点数を減らす為にダイオード4もIC化したいとの要望もある。しかし、数Aもの大電流を流すダイオードを集積化すると、集積回路内で不可避的に発生する寄生トランジスタ効果によって寄生電流が流れ、無効電流が流れるほか最悪の場合はラッチアップに至るという危険性をはらんでいる。10

**【0005】**

そこで、寄生電流を防止する構造として例えば特開平6 100459号公報に記載された構造が提案された。

**【0006】**

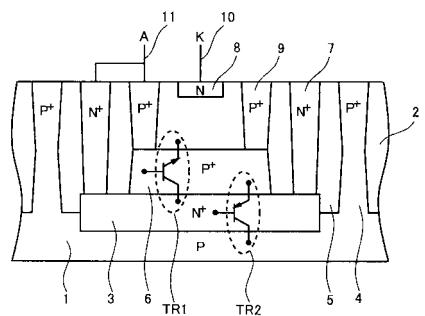

図12を参照して、P型半導体基板1とN型半導体基板2との間にN+型の埋め込み層3が設けられ、この埋め込み層3を囲むようにP+型の分離領域4が半導体層2表面から半導体基板1まで拡散され、1つのアイランド5を形成している。前記埋め込み層3の上には一部重なるようにP+型の埋め込み層6が形成されている。このP+型の埋め込み層6を囲み、半導体層2表面からN+型の埋め込み層3に到達するN+型の導出領域7が設けられ、この囲まれた領域にはN+型の拡散領域8が形成されている。更には導出領域7で囲まれた領域において、前記拡散領域8を囲み、半導体層2からP+型の埋め込み層6に到達するP+型の導出領域9が設けられている。更には、前記拡散領域8にはカソード電極10が、P+型の導出領域9にはアノード電極11が設けられ、この電極はN+型の導出領域7と電気的に接続されている。20

**【0007】**

つまりP+型の導出領域9とP+型の埋め込み層6がアノード領域、N+型の拡散領域8と導出領域9で囲まれたN型の半導体領域がカソード領域となり、ダイオードが構成されている。30

**【0008】**

斯かるダイオード素子においては、N+型の埋め込み層3をベース、P+型の埋め込み層6をエミッタ、P型の半導体基板1やP+型の分離領域4をコレクタとするPNP型の寄生トランジスタTr2が生じるが、アノード電極の接続によりこの寄生トランジスタTr2のベースとエミッタ間が同電位となるので、寄生PNPトランジスタTr2がON動作することを防止できる。

**【0009】**

**【発明が解決しようとする課題】**

上記したように従来の半導体集積回路装置では、図11に示したように、負荷が誘導性負荷の場合、モータの回転／停止に伴う正／逆方向の起電力が発生するため、IC化された直列接続トランジスタのコレクタ・エミッタ間に保護ダイオードを接続し、前記逆方向起電力によって出力端子がGND電位より低く又はVCC電位より高くなつた際にダイオード4がONする事で前記起電力を固定電位へ逃がし、直列接続されたトランジスタを含むICの内部を保護していた。特にダイオード4に数Aもの大電流を流す場合は、ダイオード4として個別部品を用いて構成していた。40

**【0010】**

そして、機器の部品点数を減らす為にダイオード4もIC化したいとの要望等により、数Aもの大電流を流すダイオードを集積化したが、集積回路内で不可避的に発生する寄生トランジスタ効果によって寄生電流が流れ、無効電流が流れる等の問題より、図12に示す50

ようなダイオードを I C の内部に取り入れた構造とした。

【 0 0 1 1 】

しかし、上記したように、ダイオード 4 を I C の内部に取り入れることはできたが、図 1 2 に示す構造において、ダイオード 4 が O F F の場合、すなわちカソード電極 1 0 がアノード電極 1 1 より高電圧となった場合、寄生トランジスタ T R 1 の P N 接合面におけるブレークダウン電流による半導体素子の破壊に対応するための耐圧が必要となる。したがって、従来の構造では寄生トランジスタ T R 1 のベース領域としての P + 型埋め込み層 6 の幅が狭く、電流増幅率 h f e が抑制することが困難であり寄生トランジスタ T R 1 の耐圧が確保することができないという課題が生じた。

【 0 0 1 2 】

10

【課題を解決するための手段】

本発明は、上記した従来の課題に鑑みてなされたもので、本発明である半導体集積回路装置では、一導電型の半導体基板と、該基板表面に積層されている逆導電型の第 1 のエピタキシャル層と、前記基板と前記第 1 のエピタキシャルとの間に形成されている高濃度不純物拡散層からなる第 1 の逆導電型の埋め込み層と重畠して形成されている高濃度不純物拡散層からなる第 1 の一導電型の埋め込み層と、前記第 1 のエピタキシャル層表面に積層されている逆導電型の第 2 のエピタキシャル層と、前記第 1 のエピタキシャル層と前記第 2 のエピタキシャル層との間に形成されている高濃度不純物拡散層からなる第 2 の一導電型の埋め込み層および高濃度不純物拡散層からなる第 2 の逆導電型の埋め込み層と、前記第 2 のエピタキシャル層表面から前記第 2 の一導電型の埋め込み層まで拡散して形成されている高濃度不純物拡散層からなる一導電型の拡散領域と、前記第 2 のエピタキシャル層表面から前記第 2 の逆導電型の埋め込み層まで拡散して形成されている高濃度不純物拡散層からなる第 1 の逆導電型の拡散領域と、前記第 2 の一導電型の埋め込み層と前記一導電型の拡散領域とで挟まれる前記第 2 のエピタキシャルに形成されている逆導電型のウェル領域と、前記ウェル領域に重畠して形成されている高濃度不純物拡散層からなる第 2 の逆導電型の拡散領域とを有する前記ダイオード素子において、前記第 1 の一導電型の埋め込み層と前記第 2 の逆導電型の拡散領域とが、深さ方向に隔てて形成されていることを特徴とする。

20

【 0 0 1 3 】

30

本発明の半導体集積回路装置は、好適には、前記ダイオード素子の前記第 1 の一導電型の埋め込み層と前記第 1 の逆導電型の埋め込み層とを重畠して形成し、また、前記第 1 の一導電型の埋め込み層と前記一導電型の拡散領域とを前記第 2 の一導電型の埋め込み層を介して連結する。そして、前記第 1 の一導電型の埋め込み層と前記第 2 の逆導電型の拡散領域とを深さ方向に隔てて形成している構造を有する。そのことにより、前記ダイオード素子が O F F の状態にある場合、前記ダイオード素子内の前記第 1 の一導電型の埋め込み層と前記第 1 のエピタキシャル層とを接面とする P N 接合において、N 型領域に空乏層形成領域を大幅に得ることができ前記空乏層で耐圧を確保することで逆方向バイアス状態に対処し、ブレークダウン電流による内部素子破壊を抑制することができる半導体集積回路装置を得ることができる。

【 0 0 1 4 】

40

本発明の半導体集積回路装置は、好適には、前記ダイオード素子の前記逆導電型のカソード導出領域と重畠して前記逆導電型のウェル領域を形成することに特徴を有する。そのことにより、前記ダイオード素子が O N の状態にある場合、P N 接合の N 型領域の抵抗値が下がることにより順方向電圧 ( V BEF ) が低減することで、順方向における電流 ( I f ) 能力を大幅に向上させる半導体集積回路装置を得ることができる。

【 0 0 1 5 】

上記した課題を解決するために、本発明の半導体集積回路装置の製造方法では、一導電型の半導体基板を準備する工程と、該基板に不純物を拡散させ、ダイオード素子、一導電タイプの縦型トランジスタ、および、逆導電タイプの縦型トランジスタ形成領域にそれぞれ逆導電型の埋め込み層を形成する工程と、前記基板上に不純物を拡散させ前記ダイオード

50

素子形成領域に前記逆導電型の埋め込み層と重畳して第1の一導電型の埋め込み層を形成する工程と、前記基板上に逆導電型の第1のエピタキシャル層を積層する工程と、該第1のエピタキシャル層上に不純物を拡散し、前記ダイオード素子および前記一導電タイプの縦型トランジスタ形成領域にそれぞれ第2の一導電型の埋め込み層を形成する工程と、前記第1のエピタキシャル層上に逆導電型の第2のエピタキシャル層を積層する工程と、該第2のエピタキシャル層上に不純物を拡散し、前記ダイオード素子形成領域に一導電型の拡散領域を形成し、前記第2の一導電型の埋め込み層を介して前記第1の一導電型の埋め込み層と連結する工程と、前記第2のエピタキシャル層上に不純物を拡散し、前記ダイオード素子および前記一導電タイプの縦型トランジスタ形成領域に逆導電型のウェル領域を同時に形成する工程と、前記ダイオード素子形成領域の前記ウェル領域に逆導電型の拡散領域を形成する工程とを有することを特徴とする。

#### 【0016】

本発明の半導体集積回路装置の製造方法は、好適には、前記第2の一導電型の埋め込み層を形成する工程は、前記第1の一導電型の埋め込み層と前記一導電型の拡散領域とを連結させる工程とすることで、前記第1の逆導電型の埋め込み層と前記逆導電型の拡散領域とを深さ方向に大幅に隔離し空乏層形成領域を増大させることができる工程であることを特徴とする。

#### 【0017】

##### 【発明の実施の形態】

以下に本発明の実施の形態について図面を参照しながら詳細に説明する。

#### 【0018】

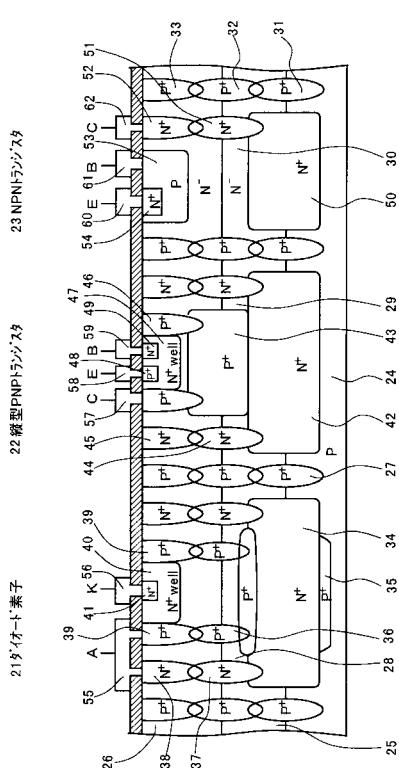

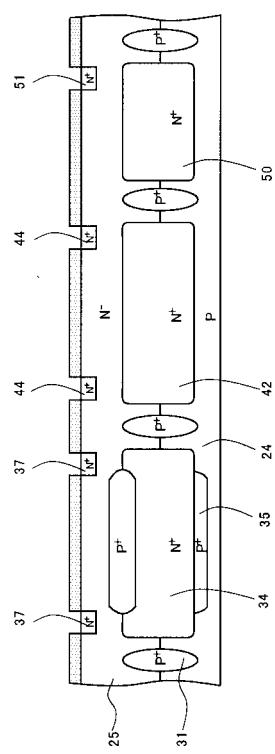

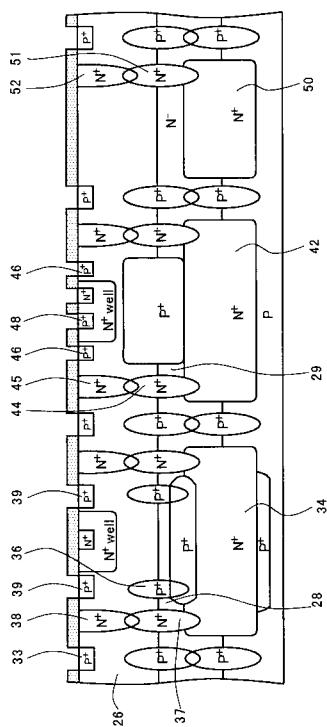

図1は、ダイオード素子21、縦型PNPトランジスタ22およびNPNトランジスタ23とを組み込んだ半導体集積回路装置の断面図である。

#### 【0019】

P型の単結晶シリコン基板24上には、厚さ2~10μmの第1のエピタキシャル層25および厚さ8~10μmの第2のエピタキシャル層26が、2層の合計膜厚が8~16μm程度になるように形成されている。そして、基板24と第1および第2のエピタキシャル層25、26は、それらを貫通するP+型分離領域27によってダイオード素子21を形成する第1の島領域28、縦型PNPトランジスタ22を形成する第2の島領域29およびNPNトランジスタ23を形成する第3の島領域30が電気的に分離され、形成されている。

#### 【0020】

この分離領域27は、基板24表面から上下方向に拡散した第1の分離領域31と、第1および第2エピタキシャル層25、26の境界から上下方向に拡散した第2の分離領域32と、第2エピタキシャル層26表面から形成した第3の分離領域33から成り、3者が連結することで第1および第2のエピタキシャル層25、26を島状に分離する。

#### 【0021】

第1の島領域28に形成されているダイオード素子21には、基板24と第1エピタキシャル層25との間にN+型の第1の埋め込み層34とP+型の第1の埋め込み層35とが重畳して形成されており、第1および第2のエピタキシャル層25、26の境界部分にP+型の第2の埋め込み層36が形成されており、第2のエピタキシャル層26表面からP+型の第2の埋め込み層36に達するP+型の拡散領域39がアノード導出領域として形成されている。そして、これらP+型領域36、39に挟まれたN-型の第1および第2のエピタキシャル層25、26がカソード領域として形成されることでPN接合ダイオードが構成されている。この時、第2のエピタキシャル層26にN+型拡散領域38をアノード領域として形成し、N+型拡散領域38とP+型拡散領域39とを短絡してアノード導出領域としても良い。これはNPNトランジスタでいえば、ベース、コレクタ間を短絡して形成したダイオードということになる。

#### 【0022】

上記の本実施形態の半導体集積回路装置によれば、基板24と第1エピタキシャル層25

10

20

30

40

50

との間にN+型の第1の埋め込み層34とP+型の第1の埋め込み層35とが重畠して形成されているが、例えば、N+型の第1の埋め込み層34はアンチモン(Sb)を使用し、また、P+型の第1の埋め込み層35はホウ素(B)を使用し形成されている。そのため、不純物の拡散速度及び不純物の使用濃度の違いにより、図1に示すように、N+型の第1の埋め込み層34の上下にP+型の第1の埋め込み層35が形成されている構造を有する。そして、第1エピタキシャル層25と第2エピタキシャル層26との間に形成されているP+型の第2の埋め込み層36はP+型の第1の埋め込み層35およびP+型の拡散領域39と連結する。この構造により、P+型の第1埋め込み層35をアノード領域として、また、第1および第2のエピタキシャル層25、26をカソード領域としたPN接合ダイオードが形成されている。

10

#### 【0023】

ここで、カソード領域として形成されている第2のエピタキシャル層26にはN+型の拡散領域41がカソード導出領域として形成されているが、上記したように、N+型の拡散領域41とP+型の第1の埋め込み層35とが深さ方向に隔てて形成されている構造となる。

#### 【0024】

よって、上記した構造を有することにより、ダイオード素子21がOFFの状態にある場合、つまり、P+型の第1の埋め込み層35とN-型の第1のエピタキシャル層25とで形成されているPN接合面に逆バイアス電圧がかかった場合、第1および第2のエピタキシャル層25、26からなるN型領域に空乏層形成領域を大幅に得ることができその形成された空乏層で耐圧を確保することでブレーキダウン電流による内部素子破壊を抑制することができる半導体集積回路装置を得ることができる。

20

#### 【0025】

更に、上記の本実施形態の半導体集積回路装置によれば、ダイオード素子がON時において、カソード領域として形成されているP+型領域36、39に挟まれたN-型の第2のエピタキシャル層26に、N+型ウェル領域40が形成されている。このN+型ウェル領域40により、PN接合のN型領域の抵抗値が下がることにより順方向電圧(VBEF)が低減することで、順方向における電流(If)能力を大幅に向上させることができる。

#### 【0026】

尚、第2のエピタキシャル層26の表面はシリコン酸化膜によって被覆され、酸化膜に形成されたコンタクトホールを介して各種のアルミ電極が設けられている。基板24には接合分離のための接地電位GNDが印加されている。

30

#### 【0027】

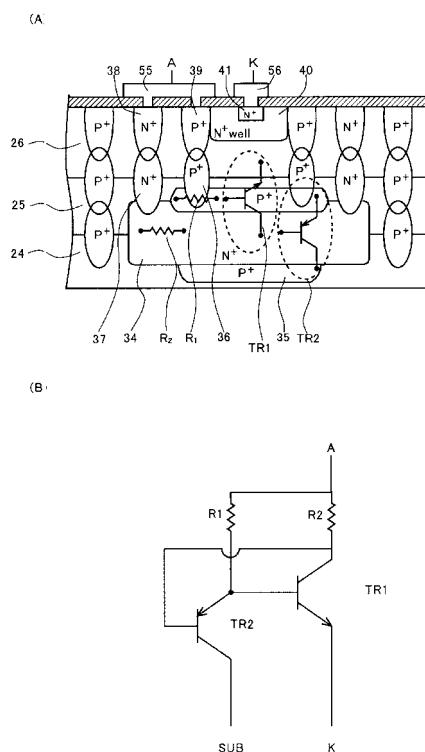

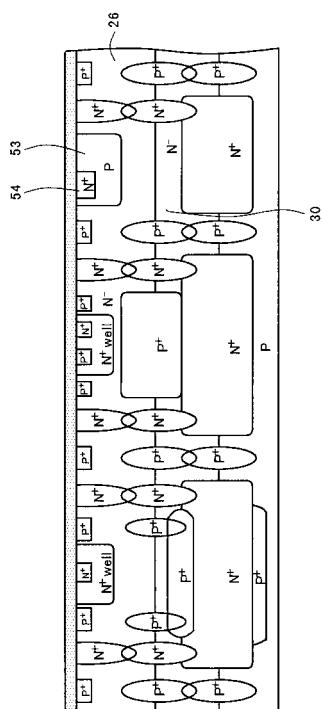

ここで、図2(A)はダイオード素子21の拡大断面図を表した図であり、図2(B)は寄生トランジスタを示す等価回路図である。以下、ダイオード素子21がON状態における基板24への漏れ電流を左右する寄生トランジスタの動作について説明する。

#### 【0028】

寄生NPNトランジスタTR1は、N+型の第1の埋め込み層34をコレクタ、P+型の埋め込み層35をベースおよび第1および第2のエピタキシャル層25、26をエミッタとして構成されている。一方、寄生PNPトランジスタTR2は、P型の基板24をコレクタ、N+型の第1の埋め込み層34をベース、P+型の埋め込み層35をエミッタとして構成されている。

40

#### 【0029】

図2(B)を参照にして、寄生NPNトランジスタTR1のベース・コレクタはアノード電極55によって短絡され、同じく寄生PNPトランジスタTR2のベース・エミッタ間が短絡される。このとき、寄生NPNトランジスタTR1のベース・コレクタ間にはP+型の拡散領域39とP+型の埋め込み層36とが持つ抵抗成分R1が接続され、寄生PNPトランジスタTR2のベース・エミッタ間にはN+型の拡散領域38、N+型の第2の埋め込み層37およびN+型の第1の埋め込み層34とが持つ抵抗成分R2が接続される。本発明のダイオード素子21の構造では、寄生NPNトランジスタTR1の抵抗成分R

50

1の場合は、P+型の拡散領域39、P+型の埋め込み層36およびP+型の第1の埋め込み層35との連結により構成されているため抵抗成分R1の値は極めて小さくなる。また、寄生PNPトランジスタTR2の抵抗成分R2の場合も、N+型の拡散領域38、N+型の第2の埋め込み層37およびN+型の第1の埋め込み層34との連結により抵抗成分R2の値は極めて小さくなる。

#### 【0030】

本発明はN+型ウェル領域40の形成によりカソード領域の抵抗を下げることができるので、順方向電流Ifの能力を向上することができる。

#### 【0031】

一方、寄生PNPトランジスタTR2のベース・エミッタ間に接続される抵抗成分R2の値は小さくできるので、寄生PNPトランジスタTR2のベース電位(N+型の第1の埋め込み層34の電位)をエミッタ電位(P+型の埋め込み層35、36の電位)より高く維持することができる。従って、寄生PNPトランジスタTR2のON動作を阻止し、基板24への漏れ電流を小さく保つことが可能になる。

10

#### 【0032】

その結果、上記した寄生PNPトランジスタTR2において、例えば、従来の構造では1Aを流したとき基板24への漏れ電流が100mAであったのに対して、本発明の構造(抵抗成分R2の抵抗値を8とした場合)では20mAまで低減することができる。

#### 【0033】

第2の島領域29に形成されている縦型PNPトランジスタ22において、基本的にダイオード素子21と同様の構造を具備している。具体的にいうと、第1および第2のエピタキシャル層25、26の境界部分にP+型の埋め込み層43がコレクタ領域として形成されており、第2のエピタキシャル層26表面からP+型の埋め込み層43に達するP+型拡散領域46がコレクタ導出領域として形成されている。そして、これらP+型領域に囲まれたN-型の第2のエピタキシャル層26にN+型のウェル領域47がベース領域として形成されており、N+型のウェル領域47にはP+型の拡散領域48がエミッタ領域として、また、N+型の拡散領域49がベース導出領域として形成されることで、縦型PNPトランジスタ22は構成されている。また、P+型拡散領域46を囲むようにN+型拡散領域45を形成し、N+型の第2の埋め込み層44を介して第1の埋め込み層42に連結し、図示せぬ電極により電源電位Vccあるいはエミッタ電極58の電位を印加した。これはP+型の拡散領域46をエミッタ、第2の島領域29をベース、P+型の分離領域27をコレクタとする寄生PNPトランジスタの発生を抑制するものであり、この縦型PNPトランジスタを大電流用途に適したPNPトランジスタとすることができる。

20

#### 【0034】

第3の島領域30に形成されているNPNトランジスタ23において、第3の島領域30をコレクタ領域としてP型の拡散領域53をベース領域として、N+型の拡散領域54をエミッタ領域として形成されていることで構成される。そして、基板24と第1のエピタキシャル層25との間に第1のN+型の埋め込み層50と第1および第2のエピタキシャル層25、26の境界部分にも第2のN+型の埋め込み層51とが連結して形成されている。更に、N+型の拡散領域52をコレクタ導出領域とし、N+型の拡散領域52も第2のN+型の埋め込み層51と連結して形成されている。このように、コレクタ電極62の下部に高濃度低抵抗領域を構成することによって、NPNトランジスタ23の飽和抵抗Vce(sat)を低減する。従って、このNPNトランジスタ23は高耐圧、大電流であり、モータドライバー等の回路用途に適している。

30

#### 【0035】

次に、図1に示した本発明の半導体集積回路装置の製造方法について図3～図10を参照にして説明する。

#### 【0036】

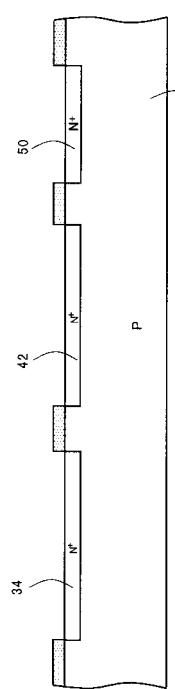

先ず、図3に示すように、P-型の単結晶シリコン基板24を準備し、この基板24の表面を熱酸化して酸化膜を形成し、N+型の第1の埋め込み層34、42、50に対応する

40

50

酸化膜をホトエッチングして選択マスクとする。そして、基板 2 4 表面に N + 型埋め込み層 3 4、4 2、5 0 を形成するアンチモン (Sb) を拡散する。

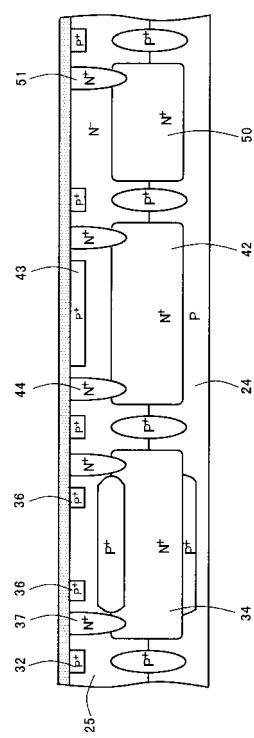

#### 【 0 0 3 7 】

次に、図 4 に示すように、P + 型の埋め込み層 3 5 および P + 型の分離領域 2 7 の第 1 分離領域 3 1 を形成するため、イオン注入を行う。図 3 において選択マスクとして用いた酸化膜を全て除去した後、公知のフォトリソグラフィ技術により P + 型の第 1 の分離領域 3 1 を形成する部分に開口部が設けられたフォトレジスト（図示せず）を選択マスクとして形成する。そして、P 型不純物、例えば、ホウ素 (B) をイオンエネルギー 1 6 0 k e V、導入量  $1.0 \times 10^{14} / \text{cm}^2$  でイオン注入する。その後、フォトレジストを除去する。

10

#### 【 0 0 3 8 】

次に、図 5 に示すように、酸化膜を全て除去した後、基板 2 4 をエピタキシャル成長装置のサセプタ上に配置し、ランプ加熱によって基板 2 4 に 1 1 4 0 度の高温を与えると共に反応管内に SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>ガスと H<sub>2</sub>ガスを導入することにより、低濃度エピ（ = 1.25 · cm）、厚さ 2.0 ~ 10.0 μm の第 1 のエピタキシャル層 2 5 を成長させる。そして、第 1 のエピタキシャル層 2 5 の表面を熱酸化して酸化膜を形成した後、N + 型の第 2 の埋め込み層 3 7、4 4、5 1 に対応する酸化膜をホトエッチングして選択マスクとする。

#### 【 0 0 3 9 】

ここで、同時に、基板 2 4 表面に N + 型埋め込み層 3 4、4 2、5 0 および P + 型の埋め込み層 3 1、3 5 を拡散する。このとき、P + 型の埋め込み層 3 5 を形成するホウ素 (B) は、N + 型埋め込み層 3 4 を形成するアンチモン (Sb) と比べて拡散速度が速く、また、不純物濃度が低いため、N + 型埋め込み層 3 4 の上下に形成領域が形成される。

20

#### 【 0 0 4 0 】

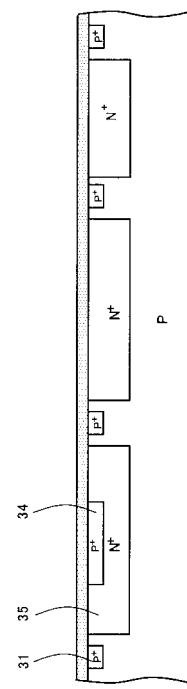

次に、図 6 に示すように、酸化膜を全て除去した後、再び、第 1 のエピタキシャル層 2 5 の表面を熱酸化して酸化膜を形成し、公知のフォトリソグラフィ技術により P + 型の埋め込み層 3 6、4 3 および P + 型の第 2 の分離領域 3 2 を形成する部分に開口部が設けられたフォトレジスト（図示せず）を選択マスクとして形成する。そして、P 型不純物、例えば、ホウ素 (B) をイオンエネルギー 4 0 k e V、導入量  $3.0 \times 10^{13} / \text{cm}^2$  でイオン注入する。その後、フォトレジストを除去する。このとき、第 2 の N + 型埋め込み層 3 7、4 4、5 1 は同時に拡散され、第 1 の N + 型埋め込み層 3 4、4 2、5 0 と連結する。

30

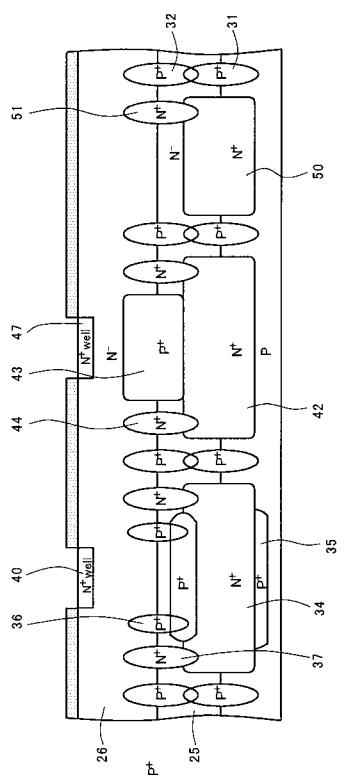

#### 【 0 0 4 1 】

次に、図 7 に示すように、酸化膜を全て除去した後、基板 2 4 をエピタキシャル成長装置のサセプタ上に配置し、ランプ加熱によって基板 2 4 に 1 1 4 0 度の高温を与えると共に反応管内に SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>ガスと H<sub>2</sub>ガスを導入することにより、低濃度エピ（ = 1.25 · cm）、厚さ 8.0 ~ 10.0 μm の第 2 のエピタキシャル層 2 6 を第 1 のエピタキシャル層 2 5 上に成長させる。そして、第 2 のエピタキシャル層 2 6 の表面を熱酸化して酸化膜を形成した後、公知のフォトリソグラフィ技術により N + 型ウェル領域 4 0、4 7 を形成する部分に開口部が設けられたフォトレジスト（図示せず）を選択マスクとして形成する。そして、N 型不純物、例えば、リン (P) をイオンエネルギー 1 6 0 k e V、導入量  $1.0 \times 10^{12} / \text{cm}^2$  でイオン注入する。その後、フォトレジストを除去する。

40

#### 【 0 0 4 2 】

このとき、P + 型の埋め込み層 3 6、4 3 および P + 型の第 2 の分離領域 3 2 は同時に拡散され、それぞれ第 1 の P + 型埋め込み層 3 5、第 1 の N + 型埋め込み層 4 2 および P + 型の第 1 の分離領域 3 1 と連結する。

#### 【 0 0 4 3 】

次に、図 8 に示すように、第 2 のエピタキシャル層 2 6 の表面を熱酸化して酸化膜を形成し、N + 型のコレクタ導出領域 3 8、4 5、5 2 およびベース導出領域 4 9 に対応する酸

50

化膜をホトエッチングして選択マスクとする。そして、第2のエピタキシャル層26表面にN+型拡散領域38、45、52およびベース導出領域49を形成するアンチモン(Sb)を拡散する。

#### 【0044】

次に、図9に示すように、酸化膜を全て除去した後、再び、第2のエピタキシャル層26の表面を熱酸化して酸化膜を形成し、公知のフォトリソグラフィ技術によりP+型の拡散領域39、46、P+型のエミッタ領域48およびP+型の第3の分離領域33を形成する部分に開口部が設けられたフォトレジスト(図示せず)を選択マスクとして形成する。そして、P型不純物、例えば、ホウ素(B)をイオンエネルギー40keV、導入量 $3.0 \times 10^{13} / \text{cm}^2$ でイオン注入する。その後、フォトレジストを除去し拡散する。

10

#### 【0045】

このとき、第2のN+型埋め込み層37、44、51は同時に拡散され、第1のN+型埋め込み層34、42、50と連結する。また、N+型の拡散領域38、45、52も同時に拡散され、それぞれ第2のN+型埋め込み層37、44、51と連結する。その結果、第1の島領域28にはダイオード素子21が完成し、第2の島領域29には縦型PNPトランジスタ22が完成する。

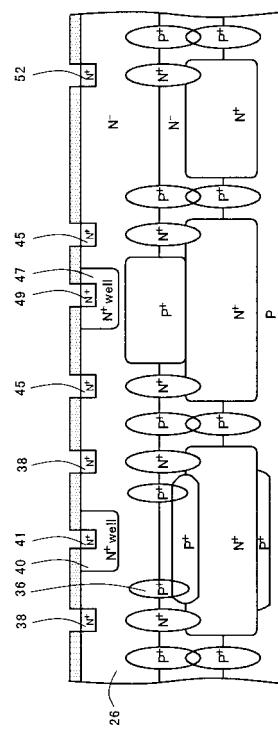

#### 【0046】

次に、図10に示すように、第3の島領域30にはP型のベース領域53およびN+型のエミッタ領域54を形成することで、NPNトランジスタ23が完成する。その後、図1に示すように、ダイオード素子21にはアノード電極55、カソード電極56が、縦型PNPトランジスタ22にはコレクタ電極57、エミッタ電極58、ベース電極59が、NPNトランジスタ23にはエミッタ電極60、ベース電極61、コレクタ電極62がアルミニ材料により形成されることで、外部電極と接続される。

20

#### 【0047】

##### 【発明の効果】

本発明によれば、半導体集積回路装置のダイオード素子において、基板と第1エピタキシャル層との間に形成されているP+型の第1の埋め込み層と、カソード電極と接続されているN+型の拡散領域とはPN接合を形成しているが、この両者は深さ方向に隔てて形成されている。そのことで、前記ダイオード素子がOFFの場合、つまり前記ダイオード素子に逆方向バイアス電圧がかかった場合、第1および第2のエピタキシャル層からなるN型領域に空乏層形成領域を大幅に得ることができその形成された空乏層で耐圧を確保することでブレークダウン電流による内部素子破壊を抑制することができる半導体集積回路装置を得ることができる。

30

#### 【0048】

更に、本発明によれば、半導体集積回路装置のダイオード素子において、ダイオード素子がONの状態にある場合、カソード領域として形成されているN-型の第2のエピタキシャル層に、N+型ウェル領域が形成されている。このN+型ウェル領域により、PN接合のN型領域の抵抗値が下がることにより順方向電圧(VBEF)が低減することで、順方向における電流(I<sub>f</sub>)能力を大幅に向上させることができる。

40

#### 【0049】

更に、本発明によるN+型ウェル領域形成により、ダイオード素子がONの状態にある場合、ダイオード素子内に形成される寄生トランジスタTR1の電流増幅率は向上し、寄生トランジスタTR2の電流増幅率は低減することができ、基板への漏れ電流の抑制効果が高まる。その結果、出力トランジスタ保護に適したスパークキラーダイオードを半導体集積回路装置に集積化でき、電子機器の小型化、高密度化に寄与することができる。

##### 【図面の簡単な説明】

【図1】本発明の半導体集積回路装置を説明する断面図である。

【図2】本発明の図1の半導体集積回路装置のダイオード素子を説明するための(A)拡大断面図(B)等価回路図である。

【図3】本発明の半導体集積回路装置の製造方法を説明する断図面である。

50

【図4】本発明の半導体集積回路装置の製造方法を説明する断図面である。

【図5】本発明の半導体集積回路装置の製造方法を説明する断面図である。

【図6】本発明の半導体集積回路装置の製造方法を説明する断図面である。

【図7】本発明の半導体集積回路装置の製造方法を説明する断面図である。

【図8】本発明の半導体集積回路装置の製造方法を説明する断図面である。

【図9】本発明の半導体集積回路装置の製造方法を説明する断面である。

【図10】本発明の半導体集積回路装置の製造方法を説明する断面図である。

【図1-1】従来の半導体集積回路装置を説明する回路図である。

【図1-2】従来の半導体集積回路装置のダイオード素子を説明するための断面図である。

【 义 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H01L 29/861

H01L 21/331

H01L 21/8222

H01L 27/06

H01L 29/73