(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

22 March 2012 (22.03.2012)

(10) International Publication Number

WO 2012/037133 A1

(51) International Patent Classification:

*H03F 3/45* (2006.01)      *H03M 1/12* (2006.01)

*H03K 17/62* (2006.01)

(74) Agents: **FRANZ, Warren, L.** et al.; Texas Instruments Incorporated, P.O. Box 655474, Mail Station 3999, Dallas, TX 75265-5474 (US).

(21) International Application Number:

PCT/US2011/051411

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(22) International Filing Date:

13 September 2011 (13.09.2011)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

12/880,311 13 September 2010 (13.09.2010) US

(63) Related by continuation (CON) or continuation-in-part (CIP) to earlier application:

US 12/880,311 (CON)

Filed on 13 September 2010 (13.09.2010)

(71) Applicant (for all designated States except US): **TEXAS INSTRUMENTS INCORPORATED** [US/US]; P.O. Box 655474, Mail Station 3999, Dallas, TX 75265-5474 (US).

(71) Applicant (for JP only): **TEXAS INSTRUMENTS JAPAN LIMITED** [JP/JP]; 24-1, Nishi-shinjuku 6-chome, Shinjuku-ku Tokyo, 160-8366 (JP).

(72) Inventor; and

(75) Inventor/Applicant (for US only): **PAYNE, Robert, F.** [US/US]; 1700 Briardale Drive, Lucas, TX 75002 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Declarations under Rule 4.17:

— as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

[Continued on next page]

(54) Title: MULTIPLEXED AMPLIFIER WITH REDUCED GLITCHING

FIG. 2C

(57) Abstract: A first multiplexer (216-1) is coupled to a first input terminal (INP1/INP2) and a second input terminal (INM1/INM2) of a folded cascode differential amplifier (210) which includes transistors (Q1 through Q4) and current sources (222-228). Switching between differential input signals (INP1/INM1) and (INP2/INM2) is controlled through a select signal SELECT provided by a controller (214). A reset mechanism includes a switch (Q5) coupled between output terminals (OUTP, OUTM) of amplifier (210) and controlled by a pulse generator (XOR gate 218 and delay circuit 220). On a rising or falling edge of the select signal SELECT, a pulse is provided to activate the switch (Q5) so as to briefly short the output terminals (OUTP, OUTM). This avoids glitching and results in faster settling times.

WO 2012/037133 A1

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

**Published:**

- with international search report (Art. 21(3))

## MULTIPLEXED AMPLIFIER WITH REDUCED GLITCHING

[0001] The invention relates generally to amplifiers and, more particularly, to residue amplifiers.

## BACKGROUND

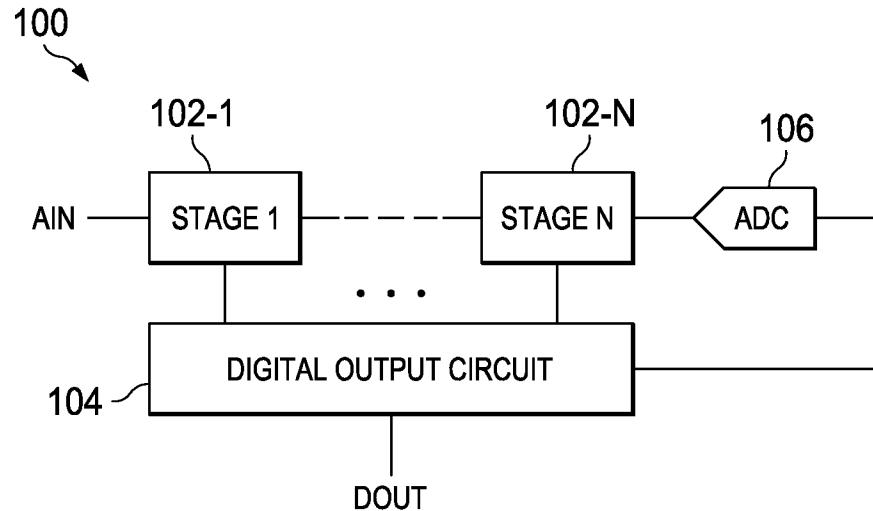

[0002] Referring to FIG. 1A of the drawings, reference numeral 100 generally designates a conventional analog-to-digital converter (ADC) 100. ADC 100 generally comprises several stages 102-1 to 102-N, an ADC 106 (which is typically a flash ADC), and a digital output circuit 104. The stages 102-1 to 102-N are generally coupled in series with one another in a sequence, where the first stage 102-1 receives the analog input signal and where each of the subsequent stages 102-2 to 102-N receives a residue signal from the previous stage 102-1 to 102-(N-1), respectively. ADC 106 is coupled to the last stage 102-N (receiving its residue signal). Based on its input signal (either a residue signal or the analog input signal), stages 102-1 to 102-N and ADC 106 are able to resolve a portion of the analog input signal, which is provided to digital output circuit 104. Digital output circuit 104 can then perform error correction or other digital processing to generate the digital output signal DOUT.

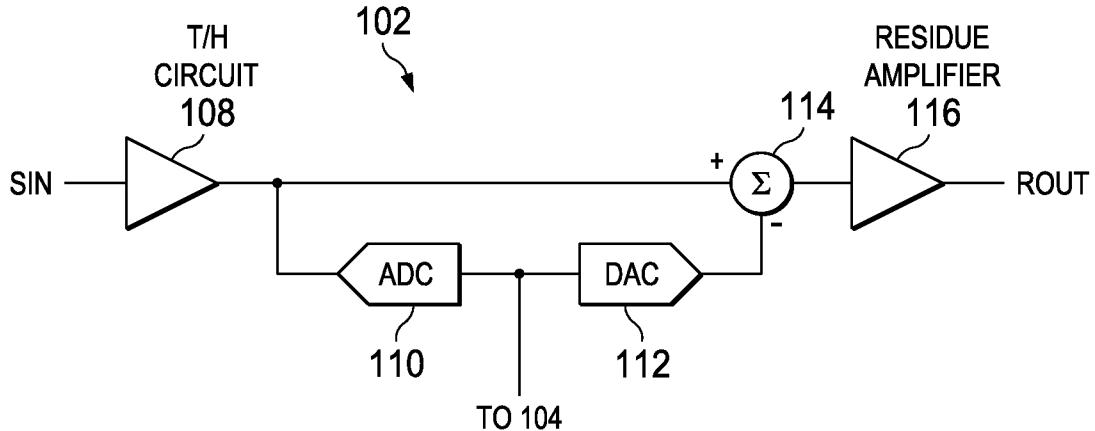

[0003] Turning now to FIGS. 1B and 1C, stages 102-1 to 102-N can be seen in greater detail (which are referred to hereinafter as stage 102 for the sake of simplicity). Stage 102 generally comprises a track-and-hold (T/H) circuit 108 (i.e., T/H amplifier), ADC 110, digital-to-analog converter (DAC) 112, adder 114, and a residue amplifier 116. In operation, the T/H circuit 110 enters a track phase T during the logic high state of the clock signal CLK and a hold phase H during the logic low state of the clock signal CLK. During the track phase T, the T/H circuit samples its analog input signal SIN (which may be the analog input signal AIN or the residue signal from the previous stage). During the hold phase H, the sampled signal is provided to ADC 110 and adder 114. The ADC 110 resolves a portion of the signal SIN, providing the resolved bits to digital output circuit 104 and DAC 112. DAC 112 converts the resolved bits to an analog signal which is provided to adder 114. Adder 114 determines the difference between the sampled signal and the analog signal from DAC, which is amplified by amplifier 116 and output as a residue signal ROUT.

**[0004]** There are some drawbacks to ADC 100. In particular, the residue amplifiers 116 for each stage 102-1 to 102-N are operating at less than 50% duty cycle, which consumes an excess amount of power. Therefore, it is desirable to have a residue amplifier that consumes less power.

5 **[0005]** Some examples of other conventional circuits are given in U.S. Patent Nos. 3,877,023; 5,180,932; 6,218,887; and 6,489,845.

## SUMMARY

10 **[0006]** An example embodiment of the invention, accordingly, provides an apparatus. The apparatus comprises an amplifier having a first input terminal, a second input terminal, a first output terminal, and a second input terminal; a first multiplexer that is coupled to the first input terminal of the amplifier; a second multiplexer that is coupled to the second input terminal of the amplifier; a switch that is coupled between the first and second output terminals of the amplifier; a pulse generator that is coupled to the switch so as to control the switch; and a controller that is coupled to the first multiplexer, the second multiplexer, and pulse generator, 15 wherein the controller provides a select signal to each of the first and second multiplexers, and wherein the controller activates the pulse generator when the first and second multiplexers are switched.

20 **[0007]** In accordance with an example embodiment of the invention, the pulse generator further comprises: a logic circuit that is coupled to the controller so as to receive the select signal and that is coupled to the switch; and a delay circuit that is coupled to the controller so as to receive the select signal and that is coupled to the switch.

**[0008]** In accordance with an example embodiment of the invention, the logic circuit further comprises a XOR gate.

25 **[0009]** In accordance with an example embodiment of the invention, the amplifier further comprises: a first transistor having a first passive electrode, a second passive electrode, and a control electrode, wherein the control electrode of the first transistor is coupled to the first multiplexer; a second transistor having a first passive electrode, a second passive electrode, and a control electrode, wherein the control electrode of the second transistor is coupled to the second multiplexer, and wherein the first passive electrode of the second transistor is coupled to the first passive electrode of the first transistor; a first current source that is coupled to the second passive electrode of the first transistor; a second current source that is coupled to the second passive

electrode of the second transistor; a first bias transistor that is coupled between the first currents source and the first output terminal; and a second bias transistor that is coupled between the second current source and the second output terminal.

[0010] In accordance with an example embodiment of the invention, the first and second

5 transistors are NPN transistors.

[0011] In accordance with an example embodiment of the invention, an apparatus is

provided. The apparatus comprises data converter circuitry; a first multiplexer that is coupled to

the data converter circuitry; a second multiplexer that is coupled to the data converter circuitry;

an amplifier having a first input terminal, a second input terminal, a first output terminal, and a

10 second input terminal, wherein the first multiplexer that is coupled to the first input terminal of

the amplifier, and wherein the second multiplexer that is coupled to the second input terminal of

the amplifier; a switch that is coupled between the first and second output terminals of the

amplifier; a pulse generator that is coupled to the switch so as to control the switch; and a

15 controller that is coupled to the first multiplexer, the second multiplexer, and pulse generator,

wherein the controller provides a select signal to each of the first and second multiplexers, and

wherein the controller activates the pulse generator when the first and second multiplexers are

switched.

[0012] In accordance with an example embodiment of the invention, the data converter

circuity further comprises: a first track-and-hold (T/H) circuit; a second T/H circuit; a first

20 analog-to-digital converter (ADC) that is coupled to the first T/H circuit; a second ADC that is

coupled to the second T/H circuit; a first digital-to-analog converter (DAC) that is coupled to the

first ADC; a second DAC that is coupled to the second ADC; a first adder that is coupled to the

first DAC, the first T/H circuit, and the first multiplexer, wherein the first adder determines the

difference between the outputs of the first T/H circuit and the first DAC; and a second adder that

25 is coupled to the second DAC, the second T/H circuit, and the second multiplexer, wherein the

second adder determines the difference between the outputs of the second T/H circuit and the

second DAC.

[0013] In accordance with an example embodiment of the invention, an apparatus is

provided. The apparatus comprises a plurality of stages that are coupled in series with one

30 another in a sequence, wherein each stage receives an analog input signal or a residue signal

from the previous stage, and wherein each stage includes: data converter circuitry; a first

multiplexer that is coupled to the data converter circuitry; a second multiplexer that is coupled to the data converter circuitry; an amplifier having a first input terminal, a second input terminal, a first output terminal, and a second input terminal, wherein the first multiplexer that is coupled to the first input terminal of the amplifier, and wherein the second multiplexer that is coupled to the second input terminal of the amplifier; a switch that is coupled between the first and second output terminals of the amplifier; a pulse generator that is coupled to the switch so as to control the switch; and a controller that is coupled to the first multiplexer, the second multiplexer, and pulse generator, wherein the controller provides a select signal to each of the first and second multiplexers, and wherein the controller activates the pulse generator when the first and second multiplexers are switched; an ADC that is coupled to the last stage of the sequence; and a digital output circuit that is coupled to the ADC and the data converter circuit for each stage.

[0014] The foregoing has outlined rather broadly the features and technical advantages of the invention in order that the detailed description of the invention that follows may be better understood. Additional features and advantages of the invention will be described hereinafter which form the subject of the claims of the invention. It should be appreciated by those skilled in the art that the conception and the specific embodiment disclosed may be readily utilized as a basis for modifying or designing other structures for carrying out the same purposes of the invention. It should also be realized by those skilled in the art that such equivalent constructions do not depart from the spirit and scope of the invention as set forth in the appended claims.

## 20 BRIEF DESCRIPTION OF THE DRAWINGS

[0015] Example embodiments are described with reference to accompanying drawings, wherein:

[0016] FIGS. 1A and 1B are circuit diagrams for an example of a conventional ADC;

[0017] FIG. 1C is a timing diagram for the ADC of FIGS. 1A and 1B;

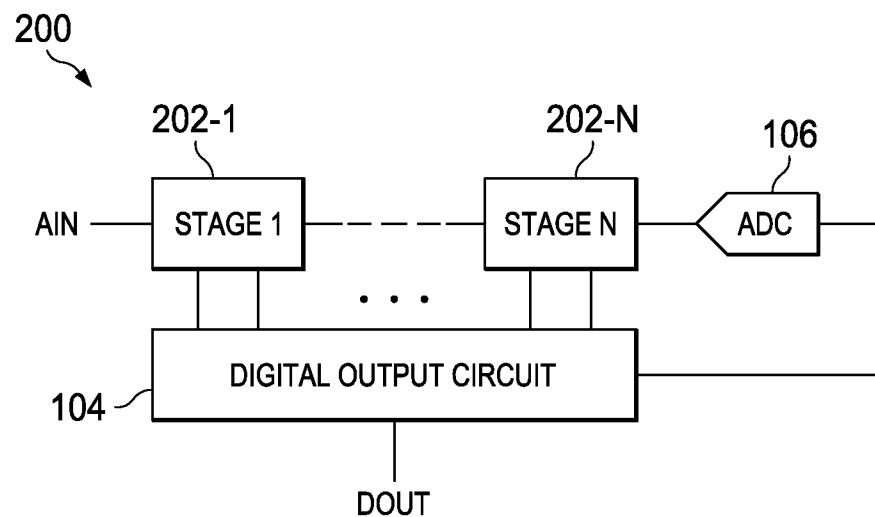

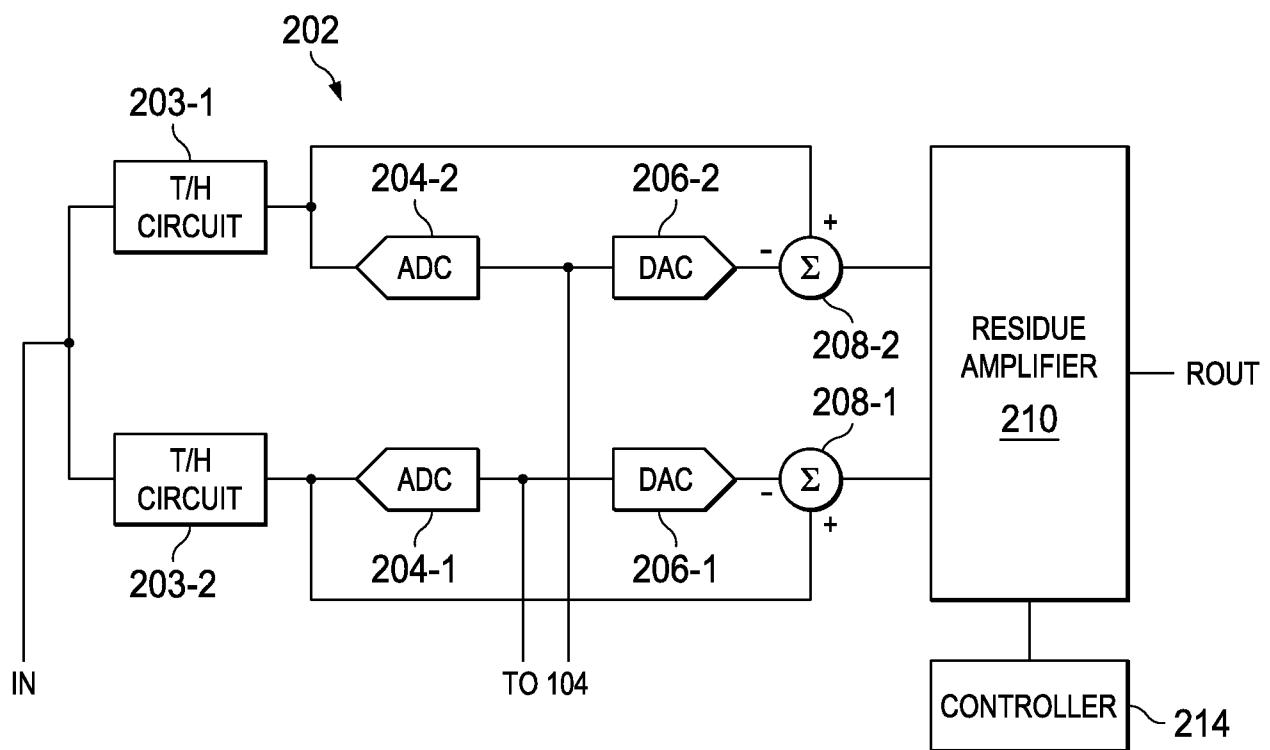

25 [0018] FIGS. 2A and 2B are circuit diagrams for an example of an ADC in accordance with an example embodiment of the invention; and

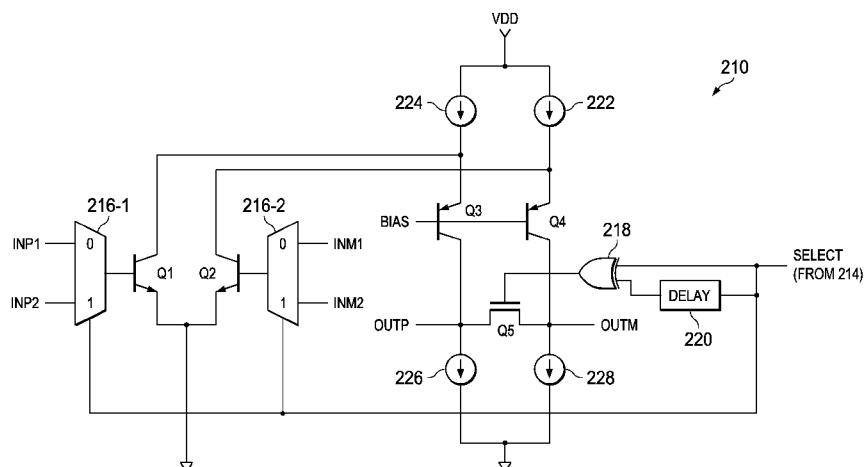

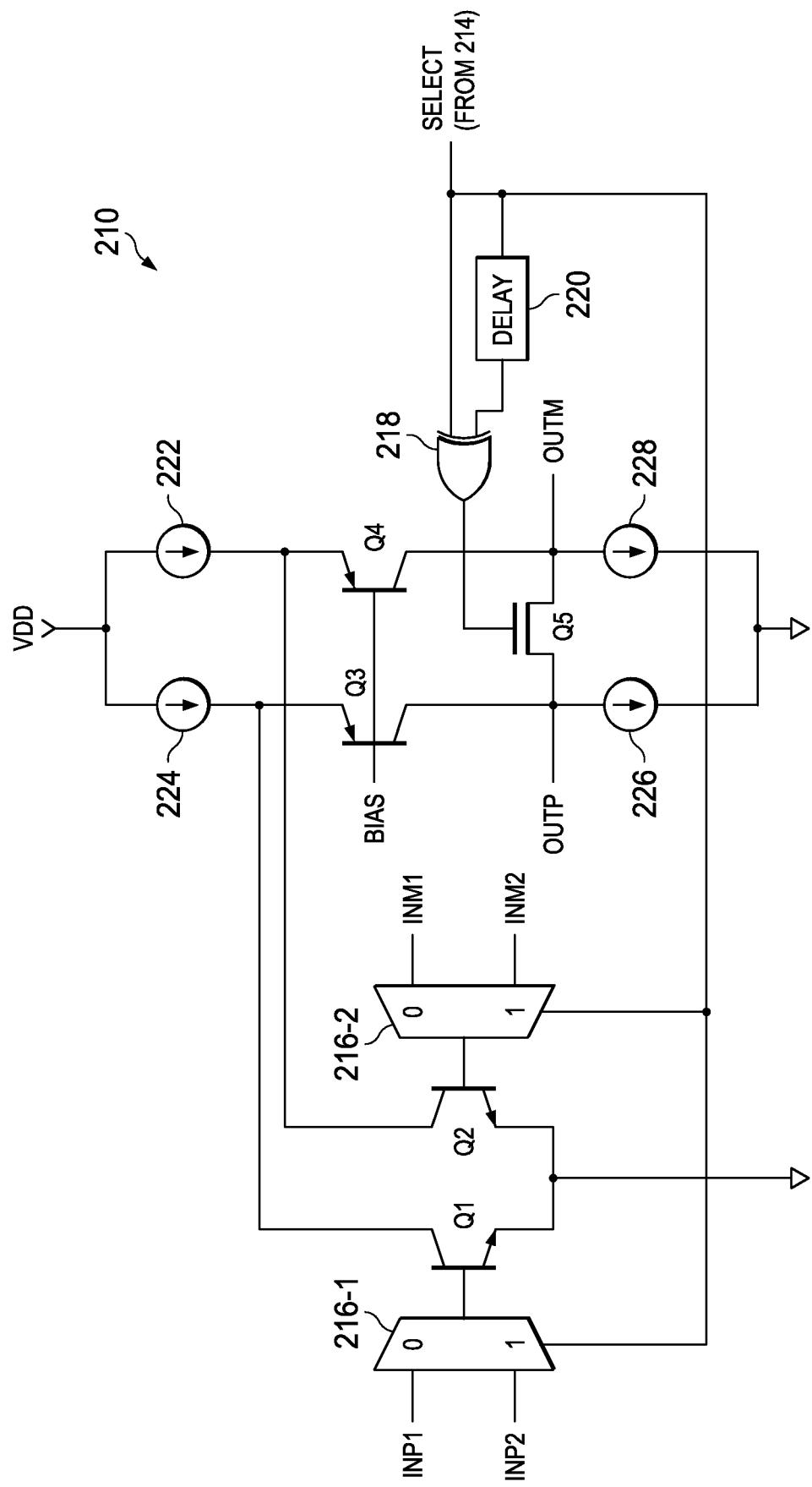

[0019] FIG. 2C is a circuit diagram of an example of a residue amplifier of FIG. 2B.

## DETAILED DESCRIPTION OF EXAMPLE EMBODIMENTS

[0020] FIG. 2A illustrates an example ADC 200 in accordance with principles of the invention. ADC 200 has the same general functionality as ADC 100. However, a difference

exists in the pipeline; namely, stages 102-1 to 102-N have been replaced by stages 202-1 to 202-N.

[0021] In FIG. 2B, stages 202-1 to 203-N (hereinafter 202) can be seen in greater detail. In operation, T/H circuit 203-1 and 203-2 are coupled to receive an analog input signal IN 5 (which is either the analog input signal AIN or a residue signal from the previous stage). Since these T/H circuits 203-1 and 203-2 are arranged in parallel with one another, T/H circuits 203-1 and 203-2 can be timed so as to sample on generally non-overlapping logic stages or phases of a clock signal. T/H circuits 203-1 and 203-2 are respectively coupled to ADC 204-1 and 204-2, and ADCs 204-1 and 204-2, DACs 206-1 and 206-2, adders 208-1 and 208-2, and residue 10 amplifier 210 can then perform analog processing to resolve sampled signals for digital output circuit 104 and to generate a residue signal ROUT.

[0022] Here, each of the data converter circuits (which respectively include ADCs 204-1 or 204-2, DAC 206-1 or 206-2, and adder 208-1 or 208-2) benefit from the use of a single amplifier. A reason is that duty cycle of an amplifier (for each data converter circuit) would be 15 less than 50%, which would consume an excessive amount of power. Therefore, amplifier 210 can be time multiplexed by controller 214 to process signals from each of the data converter circuits or data paths.

[0023] Turning to FIG. 2C, residue amplifier 210 can be seen in greater detail. In this example, a folded cascode differential amplifier (which generally comprises NPN transistors Q1 through Q4 and current sources 222, 224, 226, and 228) that is biased by a bias voltage BIAS is employed. Coupled to the input terminals of this amplifier are multiplexers 216-1 and 216-2. The switching between differential input signals INP1/INM1 and INP2/INM2 (which are provided by adders 208-1 and 208-2, respectively) are controlled through the select signal SELECT (which is provided by the controller 214). Additionally, multiplexers (not shown) that 20 are coupled to the output terminals of this amplifier (so as to receive output signals OUTP and OUTM) to direct the correct input and output signals to the amplifier at the correct instants in time for processing.

[0024] When multiplexers 216-1 and 216-2 are switched, however, the amplifier (which generally comprises NPN transistors Q1 through Q4 and current sources 222, 224, 226, and 228) 25 exhibits erratic behavior at the switching instant. This erratic behavior is referred to as a glitch, and if not addressed, the glitch can consume significant amounts of the amplifier's available

settling time or even lead to the amplifier output or interior nodes operating at voltages outside their desired ranges. In other words, this glitch can degrade performance. To combat this problem, a reset mechanism is provided at the output terminals of the amplifier. The resent mechanism generally comprises a switch Q5 that is coupled between the output terminals of the 5 amplifier and controlled by a pulse generator (which generally comprises an XOR gate and a delay circuit). Thus, on a rising or falling edge of the select signal SELECT, a pulse is provided to switch Q5 (which activates the switch Q5) so as to briefly short the output terminals of the amplifier together. Thus, glitching can be avoided, which results in faster settling times.

**[0025]** Those skilled in the art to which the invention relates will appreciate that 10 modifications may be made to the described example embodiments and other embodiments implemented within the scope of the claimed invention.

## CLAIMS

What is claimed is:

1. An apparatus comprising:

an amplifier having a first input terminal, a second input terminal, a first output terminal,

5 and a second input terminal;

a first multiplexer that is coupled to the first input terminal of the amplifier;

a second multiplexer that is coupled to the second input terminal of the amplifier;

a switch that is coupled between the first and second output terminals of the amplifier;

a pulse generator that is coupled to the switch so as to control the switch; and

10 a controller that is coupled to the first multiplexer, the second multiplexer, and pulse generator, wherein the controller provides a select signal to each of the first and second multiplexers, and wherein the controller activates the pulse generator when the first and second multiplexers are switched.

2. The apparatus of Claim 1, wherein the pulse generator further comprises:

15 a logic circuit that is coupled to the controller so as to receive the select signal and that is coupled to the switch; and

a delay circuit that is coupled to the controller so as to receive the select signal and that is coupled to the switch.

3. The apparatus of Claim 2, wherein the logic circuit further comprises a XOR gate.

20 4. The apparatus of Claim 3, wherein the amplifier further comprises:

a first transistor having a first passive electrode, a second passive electrode, and a control electrode, wherein the control electrode of the first transistor is coupled to the first multiplexer; a second transistor having a first passive electrode, a second passive electrode, and a control electrode, wherein the control electrode of the second transistor is coupled to the second multiplexer, and wherein the first passive electrode of the second transistor is coupled to the first passive electrode of the first transistor;

a first current source that is coupled to the second passive electrode of the first transistor;

a second current source that is coupled to the second passive electrode of the second transistor;

30 a first bias transistor that is coupled between the first currents source and the first output terminal; and

a second bias transistor that is coupled between the second current source and the second output terminal.

5. The apparatus of Claim 4, wherein the first and second transistors are NPN transistors.

6. An apparatus comprising:

5 data converter circuitry;

a first multiplexer that is coupled to the data converter circuitry;

a second multiplexer that is coupled to the data converter circuitry;

10 an amplifier having a first input terminal, a second input terminal, a first output terminal, and a second input terminal, wherein the first multiplexer that is coupled to the first input terminal of the amplifier, and wherein the second multiplexer that is coupled to the second input terminal of the amplifier;

a switch that is coupled between the first and second output terminals of the amplifier;

a pulse generator that is coupled to the switch so as to control the switch; and

15 a controller that is coupled to the first multiplexer, the second multiplexer, and pulse generator, wherein the controller provides a select signal to each of the first and second multiplexers, and wherein the controller activates the pulse generator when the first and second multiplexers are switched.

7. The apparatus of Claim 6, wherein the pulse generator further comprises:

20 a logic circuit that is coupled to the controller so as to receive the select signal and that is coupled to the switch; and

a delay circuit that is coupled to the controller so as to receive the select signal and that is coupled to the switch.

8. The apparatus of Claim 7, wherein the logic circuit further comprises a XOR gate.

9. The apparatus of Claim 8, wherein the amplifier further comprises:

25 a first transistor having a first passive electrode, a second passive electrode, and a control electrode, wherein the control electrode of the first transistor is coupled to the first multiplexer; a second transistor having a first passive electrode, a second passive electrode, and a control electrode, wherein the control electrode of the second transistor is coupled to the second multiplexer, and wherein the first passive electrode of the second transistor is coupled to the first passive electrode of the first transistor;

30 a first current source that is coupled to the second passive electrode of the first transistor;

a second current source that is coupled to the second passive electrode of the second transistor;

a first bias transistor that is coupled between the first currents source and the first output terminal; and

a second bias transistor that is coupled between the second current source and the second

5 output terminal.

10. The apparatus of Claim 9, wherein the first and second transistors are NPN transistors.

11. The apparatus of Claim 8, wherein the data converter circuitry further comprises:

a first track-and-hold (T/H) circuit;

a second T/H circuit;

10 a first analog-to-digital converter (ADC) that is coupled to the first T/H circuit;

a second ADC that is coupled to the second T/H circuit;

a first digital-to-analog converter (DAC) that is coupled to the first ADC;

a second DAC that is coupled to the second ADC;

15 a first adder that is coupled to the first DAC, the first T/H circuit, and the first

multiplexer, wherein the first adder determines the difference between the outputs of the first

T/H circuit and the first DAC; and

a second adder that is coupled to the second DAC, the second T/H circuit, and the second

multiplexer, wherein the second adder determines the difference between the outputs of the

second T/H circuit and the second DAC.

20

1/3

**FIG. 1A**

(PRIOR ART)

**FIG. 1B**

(PRIOR ART)

**FIG. 1C**

(PRIOR ART)

2/3

FIG. 2A

FIG. 2B

3/3

FIG. 2C

**INTERNATIONAL SEARCH REPORT**

International application No.

**PCT/US2011/051411**

**A. CLASSIFICATION OF SUBJECT MATTER**

**H03F 3/45(2006.01)i, H03K 17/62(2006.01)i, H03M 1/12(2006.01)i**

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H03F 3/45; H03F 1/56; H03M 1/00; H01P 9/00; H03M 1/14; H03M 1/38

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Korean utility models and applications for utility models

Japanese utility models and applications for utility models

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

eKOMPASS(KIPO internal) & Keywords:pipeline ADC, residue amplifier, folded cascode differential amplifier, multiplexer, glitch, pulse generator, XOR gate, delay

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                     | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 05530444 A (TICE, THOMAS E. et al.) 25 June 1996<br>See abstract, claims 1, 5-6, 9, 11-12, 14-16 and figures 2, 5, 8, 13-14                                                                                                                                         | 1-11                  |

| A         | J.H. et al. 'A 9.4-bit, 50-MS/s, 1.44-mW Pipelined ADC Using Dynamic Source Follower Residue Amplification', In: IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 44, NO. 4, APRIL 2009, pp. 1057-1066.<br>See abstract, figures 6-7 and corresponding detailed description. | 1-11                  |

| A         | B.M. et al. 'A 12-bit 75-MS/s Pipelined ADC Using Open-Loop Residue Amplification', In: IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 12, DECEMBER 2003, pp. 2040-2050.<br>See abstract, figures 6, 9, 13 and corresponding detailed description.                 | 1-11                  |

| A         | B.S.P. et al. 'A 10b 100MS/s 25.2mW 0.18 μm CMOS ADC with various circuit sharing techniques', In: 2009 International SoC Design Conference, 22-24 Nov. 2009, pp. 329-332.<br>See abstract, figures 1-2 and corresponding detailed description.                        | 1-11                  |

| A         | US 05867053 A (ENGLES, BRUCE E. et al.) 02 February 1999<br>See abstract, claim 1 and figures 2-5                                                                                                                                                                      | 1-11                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

|                                          |                                                                                                                                                                                                                                              |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents: |                                                                                                                                                                                                                                              |

| "A"                                      | document defining the general state of the art which is not considered to be of particular relevance                                                                                                                                         |

| "E"                                      | earlier application or patent but published on or after the international filing date                                                                                                                                                        |

| "L"                                      | document which may throw doubts on priority claim(s) or which is cited to establish the publication date of citation or other special reason (as specified)                                                                                  |

| "O"                                      | document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                     |

| "P"                                      | document published prior to the international filing date but later than the priority date claimed                                                                                                                                           |

| "T"                                      | later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "X"                                      | document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "Y"                                      | document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "&"                                      | document member of the same patent family                                                                                                                                                                                                    |

Date of the actual completion of the international search

16 JANUARY 2012 (16.01.2012)

Date of mailing of the international search report

**17 JANUARY 2012 (17.01.2012)**

Name and mailing address of the ISA/KR

Korean Intellectual Property Office

Government Complex-Daejeon, 189 Cheongsa-ro,

Seo-gu, Daejeon 302-701, Republic of Korea

Facsimile No. 82-42-472-7140

Authorized officer

Kang Hyun Il

Telephone No. 82-42-481-8268

**INTERNATIONAL SEARCH REPORT**

International application No.

**PCT/US2011/051411****C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 6323791 B1 (MURDEN, FRANK et al.) 27 November 2001<br>See abstract, claims 1,5 and figures 2-3 | 1-11                  |

| A         | US 2009-0243907 A1 (NAZEMI ALI et al.) 01 October 2009<br>See abstract, claim 1 and figure 3      | 1-11                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

**PCT/US2011/051411**

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                                                                                                                                                                                                                                                                                  | Publication date                                                                                                                                                                                                                                                                     |

|----------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| US 05530444 A                          | 25.06.1996       | WO 96-21271 A1                                                                                                                                                                                                                                                                                                                                                                                           | 11.07.1996                                                                                                                                                                                                                                                                           |

| US 05867053 A                          | 02.02.1999       | None                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                      |

| US 6323791 B1                          | 27.11.2001       | None                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                      |

| US 2009-0243907 A1                     | 01.10.2009       | EP 1941690 A2<br>EP 1972054 A2<br>US 2007-0133719 A1<br>US 2007-0133722 A1<br>US 2007-0176814 A1<br>US 2008-0240325 A1<br>US 2009-0096647 A1<br>US 2009-0185613 A1<br>US 2011-0058596 A1<br>US 2011-0081152 A1<br>US 7515084 B1<br>US 7576676 B2<br>US 7750835 B1<br>US 7778320 B2<br>US 7808417 B2<br>US 7852913 B2<br>WO 2007-041601 A2<br>WO 2007-041601 A3<br>WO 2007-092067 A2<br>WO 2007-092067 A3 | 09.07.2008<br>24.09.2008<br>14.06.2007<br>14.06.2007<br>02.08.2007<br>02.10.2008<br>16.04.2009<br>23.07.2009<br>10.03.2011<br>07.04.2011<br>07.04.2009<br>18.08.2009<br>06.07.2010<br>17.08.2010<br>05.10.2010<br>14.12.2010<br>12.04.2007<br>12.04.2007<br>16.08.2007<br>16.08.2007 |