(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6863980号

(P6863980)

(45) 発行日 令和3年4月21日(2021.4.21)

(24) 登録日 令和3年4月5日(2021.4.5)

(51) Int.CI.

G03F 7/20 (2006.01)

F 1

G03F 7/20 505

請求項の数 16 (全 28 頁)

(21) 出願番号 特願2018-522646 (P2018-522646)

(86) (22) 出願日 平成28年11月2日 (2016.11.2)

(65) 公表番号 特表2018-536190 (P2018-536190A)

(43) 公表日 平成30年12月6日 (2018.12.6)

(86) 國際出願番号 PCT/IL2016/051183

(87) 國際公開番号 WO2017/077532

(87) 國際公開日 平成29年5月11日 (2017.5.11)

審査請求日 令和1年10月29日 (2019.10.29)

(31) 優先権主張番号 62/249,971

(32) 優先日 平成27年11月3日 (2015.11.3)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 501005438

オルボテック リミテッド

イスラエル ヤブネ ピー. オー. ボック

ス 215

(73) 特許権者 501001500

レーザー・イメージング・システムズ ゲ

ーエムベーハー

ドイツ国, O 7745 イエナ, フリード

リッヒーフントーシュトラーセ 3

(74) 代理人 110001210

特許業務法人 Y K I 国際特許事務所

(72) 発明者 ルエッケル・シュテフェン

ドイツ国, デー-07751 グロースレ

ビハウ, ドルフシュトラーセ 61

最終頁に続く

(54) 【発明の名称】高解像度電子パターニングのためのステイチレス直接イメージング

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に直接に書込むための電気回路設計データを含む CAD ファイルであつて、上記基板上に生成される多数のダイについての CAD データを含む CAD ファイルを受信し、上記基板上の基準の画像を含む、上記基板の画像を生成し、

上記基板の画像に基づいて上記 CAD データに対する修正を算出することによって修正 CAD データを生成し、

上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査のそれぞれにおいて、上記基板上に上記修正 CAD データに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し、上記設定が、上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイについての上記直接書き込みデータを配置することを含み、これによって上記複数の走査の单一走査中に上記多数のダイのそれぞれの単層が書き込まれ、かつこれによって隣接する走査間の直接書き込みデータのステッチングを防止し、

上記直接書き込み装置を動作させて上記多数のダイを上記基板上に作成し、

上記自動的設定がさらに、

上記複数の走査の隣接するものの間にオーバーラップする継ぎ目を規定し、

上記継ぎ目のそれぞれが上記多数のダイのいずれにも位置しないことを保証し、

上記保証が、

上記多数のダイについての上記直接書き込みデータを、上記多数のダイのうちの複数のダ

10

20

イが上記複数の走査のそれぞれにおいて並んで書き込まれ，かつ上記複数のダイの隣接するものがストリートによって互いに分離される上記複数の走査の隣接するものによって書き込まれるように配置し，

上記直接書き込みデータを，上記継ぎ目が上記ストリートに沿って配置されかつ上記多数のダイのいずれにも重ならないように配置することを含む，

電気回路の製造方法。

**【請求項 2】**

上記基板の画像の生成が，上記基板の光学的イメージングを実行することを含む，請求項 1 に記載の電気回路の製造方法。

**【請求項 3】**

上記修正 C A D データの生成が，上記光学的イメージングに基づいてなされたときに，上記基板の構造における不正確さおよび歪みの少なくとも一方を考慮して上記 C A D データから修正データを導出することを含む，請求項 2 に記載の電気回路の製造方法。

**【請求項 4】**

上記直接書き込みデータが，2つ以上の走査によってダイが書き込まれないように設定されている，請求項 1 に記載の電気回路の製造方法。

**【請求項 5】**

上記ダイが複数層から形成されており，上記複数層が互いに位置決めされて順次書き込まれる，請求項 1 に記載の電気回路の製造方法。

**【請求項 6】**

上記自動的設定が，上記基板の幅よりも短い走査幅をそれぞれが有する上記複数の走査において，上記基板上に上記修正 C A D データに基づく上記複数層のそれぞれについて直接書き込みデータを直接に書込むものであり，上記複数の走査のそれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記複数層についての上記直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステッピングを防止するように上記直接書き込み装置を自動的に設定するものである，請求項 5 に記載の電気回路の製造方法。

**【請求項 7】**

上記直接書き込み装置が单一の読み／書きアセンブリを備え，上記複数の走査が上記読み／書きアセンブリによって順次実行される，請求項 1 に記載の電気回路の製造方法。

**【請求項 8】**

上記直接書き込み装置が2つ以上の読み／書きアセンブリを備え，上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによって実行される，請求項 1 に記載の電気回路の製造方法。

**【請求項 9】**

直接書き込み装置，

基板上の基準の画像を含む，基板の画像を生成するように動作可能なイメージング・サブシステム，および

上記基板上に直接に書込むための電気回路設計データを含む C A D ファイルであって，上記基板上に生成される多数のダイについての C A D データを含む C A D ファイルが記憶された一時的でないコンピュータ読み取り可能な媒体を備える自動直接書き込み装置設定( A D W M C )ユニットを備え，

上記 A D W M C が，

上記基板の上記画像に基づいて上記 C A D データに対する修正を算出することによって修正 C A D データを生成し，

複数の走査において，上記基板上に上記修正 C A D データに基づく直接書き込みデータを直接に書き込むように上記直接書き込み装置を自動的に設定し，

上記複数の走査のそれが，上記基板の幅よりも短い走査幅をそれぞれが有しており，上記複数の走査のそれにおいて上記走査幅内に並んで書き込まれるように上記多数のダイについての上記直接書き込みデータを配置することを含み，これによって上記複数の

10

20

30

40

50

走査の単一走査において上記多数のダイのそれぞれの単層が書き込まれ，かつ隣接する走査間の直接書込みデータのスティッチングが防止され，

上記 A D W M C がまた，

上記複数の走査の隣接するもの間にオーバーラップする継ぎ目を規定し，上記継ぎ目のそれぞれが上記多数のダイのいずれにも位置しないことを保証するように構成され，上記保証が，

上記多数のダイについての上記直接書込みデータを，上記多数のダイのうちの複数のダイが上記複数の走査のそれぞれにおいて並んで書き込まれ，上記複数のダイの隣接するものがストリートによって互いに分離される上記複数の走査の隣接するものによって書き込まれるように配置し，かつ

上記直接書込みデータを，上記継ぎ目が上記ストリートに沿って配置されかつ上記多数のダイのいずれにも重ならないように配置することによって行われる，

電気回路製造システム。

#### 【請求項 1 0】

上記イメージング・サブシステムが，上記基板の光学的イメージングを実行する光学イメージヤーをさらに備えている，請求項 9 に記載の電気回路製造システム。

#### 【請求項 1 1】

上記修正 C A D データが，上記光学的イメージングに基づいて作成されたときに，上記基板の構成における不正確さおよび歪みの少なくとも一つを考慮して導出される，請求項 1 0 に記載の電気回路製造システム。

#### 【請求項 1 2】

上記直接書込みデータが，2つ以上の走査によってダイが書き込まれないように設定されている，請求項 9 に記載の電気回路製造システム。

#### 【請求項 1 3】

上記ダイが複数層から形成されており，上記複数層が互いに位置決めされて順次書き込まれる，請求項 9 に記載の電気回路製造システム。

#### 【請求項 1 4】

上記 A D W M C ユニットが，上記直接書込み装置を自動的に設定して，上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記基板上に上記修正 C A D データに基づいて上記複数層のそれぞれについての直接書込みデータを直接に書き込むものであり，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記複数層の上記直接書込みデータを配置することを含み，これによって隣接する走査間の直接書込みデータのスティッチングを防止する，請求項 1 3 に記載の電気回路製造システム。

#### 【請求項 1 5】

上記直接書込み装置が单一の読み／書きアセンブリを備え，上記複数の走査が上記読み／書きアセンブリによって順次実行される，請求項 9 に記載の電気回路製造システム。

#### 【請求項 1 6】

上記直接書込み装置が2つ以上の読み／書きアセンブリを備え，上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによって実行される，請求項 9 に記載の電気回路製造システム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

##### (関連出願の参照)

この明細書は，2015年11月3日出願の米国特許出願第62/249,971号「STITCHLESS DIRECT IMAGING FOR HIGH RESOLUTION ELECTRONIC PATTERNING」(高解像電子パターニングのためのスティッチレス直接イメージング)を参照するもので，その開示内容をこの明細書に援用し，かつその優先権を37 CFR 1.78(a)(4)および(5)(i)にしたがって主張する。

**【 0 0 0 2 】**

この発明は直接イメージング（直接画像化）に関するもので，より詳細には，レーザ直接イメージング（レーザ直接画像化）電子パターニングに関する。

**【背景技術】****【 0 0 0 3 】**

さまざまなタイプの直接イメージング・システムが知られている。

**【発明の概要】****【 0 0 0 4 】**

この発明は，高解像度電子パターニングのための改良された直接イメージング・システムを提供するものである。 10

**【 0 0 0 5 】**

すなわち，この発明の好適な一実施形態によると，表面上に直接に書込む（描画する）ための電気回路設計データを含む C A D ファイルであって，上記表面上に生成される多数の対象物の C A D データを含む C A D ファイルを受信し，上記表面の幅よりも短い（狭い，小さい）走査幅（*a scan width less than a width of the surface*）をそれぞれが有する複数の走査において，C A D データに基づく直接書き込みデータを上記表面上に直接に書き込むように直接書き込み装置を自動的に設定し，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数の対象物の直接書き込みデータを配置すること（*arranging the direct writing data for the multiplicity of objects to be written in a side by side manner in each of the plural scans so as to be within the scan width*）を含み，これによって隣接する走査間の直接書き込みデータのステッチング（stitching）が防止され（予防され，不要にされ），上記直接書き込み装置を動作させて多数の対象物を表面上に作成する，対象物の製造方法が提供される。 20

**【 0 0 0 6 】**

好ましくは，この方法は，表面の光学的イメージングを実行するステップをさらに含む。 30

**【 0 0 0 7 】**

好ましくは，上記自動的設定は，上記光学的イメージングによって見つけられたときに，上記 C A D ファイルから導出されるデータを修正して上記表面の構成（configuration）および位置（location）の少なくとも一方における不正確さ（誤り）（inaccuracies）および歪み（distortions）の少なくとも一方を考慮することを含む。 30

**【 0 0 0 8 】**

好ましくは，上記直接書き込みデータは，2つ以上の走査によって対象物が書き込まれない（描画されない）ように（单一走査によって対象物が書き込まれる（描画される）ように）（no objection is written by more than a single scan）設定（構成）される。

**【 0 0 0 9 】**

この発明の好適な一実施形態によると，対象物が複数層に形成されており，上記複数層が互いに位置決め（位置合わせ）されて順次書き込まれ（the multi layers being sequentially written over each other in registration），上記自動設定は，上記直接書き込み装置を自動的に設定して，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上に上記 C A D データに基づいて上記複数層のそれぞれについての直接書き込みデータを直接に書き込むものであり，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数の対象物の複数層についての直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステッチングが防止される。 40

**【 0 0 1 0 】**

好ましくは，上記複数の走査の各走査の範囲（extent）が走査継ぎ目（*a scan seam*）によって規定され，上記直接書き込みデータは，上記走査継ぎ目のそれぞれが上記対象物の間に（between the objects）配置され，かつ上記対象物に重ならない（not overlying the objects）ように設定（構成）されている。 50

**【 0 0 1 1 】**

好ましくは，上記複数の走査のうちの隣接するものの走査継ぎ目は相互に離れている。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目は接している。さらにこれに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目はオーバーラップしている。

**【 0 0 1 2 】**

好ましくは，上記表面はフラットパネルディスプレイを含み，上記対象物は上記フラットパネルディスプレイのセル (cells) を含む。

**【 0 0 1 3 】**

これに代えて，上記表面はウェハを含み，上記対象物はダイ (dies) を含む。 10

**【 0 0 1 4 】**

好ましくは，上記直接書き込み装置は単一の読み／書きアセンブリを備え，上記複数の走査は上記読み／書きアセンブリによって順次実行される。

**【 0 0 1 5 】**

これに代えて，上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え，上記複数の走査は，少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリ (the read/write assemblies) によって実行される。

**【 0 0 1 6 】**

この発明の別の好適な実施形態によると，表面上に直接に書込む（描画する）ための電気回路設計データを含むCADファイルであって，上記表面上に生成される多数の対象物のCADデータを含むCADファイルを受信し，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上にCADデータに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し，上記設定が，上記複数の走査のそれが上記走査幅内に並んで書き込まれるように多数の対象物の直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステイッ칭が防止される直接書き込み装置の設定方法がさらに提供される。 20

**【 0 0 1 7 】**

好ましくは，上記直接書き込み装置の設定方法は表面の光学的イメージングを実行することをさらに含む。

**【 0 0 1 8 】**

好ましくは，上記自動的設定は，上記光学的イメージングによって見つけられたときにCADファイルから導出されるデータを修正して上記表面の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮することを含む。 30

**【 0 0 1 9 】**

好ましくは，上記直接書き込みデータは2つ以上の走査によって対象物が書き込まれないように設定（構成）されている。

**【 0 0 2 0 】**

この発明の直接書き込み装置の設定方法の好適な一実施形態によれば，上記対象物が複数層に形成されており，上記複数層が互いに位置決めされて順次書き込まれ，上記自動的設定は，上記直接書き込み装置を自動的に設定して，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上に上記CADデータに基づく複数層のそれぞれの直接書き込みデータを直接に書き込むものであり，上記設定が，上記複数の走査のそれが上記走査幅内に並んで書き込まれるように上記多数の対象物の複数層についての直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステイッ칭が防止される。 40

**【 0 0 2 1 】**

好ましくは，上記複数の走査の各走査の範囲が走査継ぎ目によって規定され，上記直接書き込みデータが，上記走査継ぎ目のそれぞれが上記対象物の間に配置され，かつ上記対象物に重ならないように設定されている。

**【 0 0 2 2 】**

50

好ましくは，上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目が接している。さらにこれに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。

**【0023】**

好ましくは，上記表面はフラットパネルディスプレイを含み，上記対象物は上記フラットパネルディスプレイのセルを含む。

**【0024】**

これに代えて，上記表面はウェハを含み，上記対象物はダイを含む。

**【0025】**

好ましくは，上記直接書き込み装置は単一の読み／書きアセンブリを備え，上記複数の走査が上記読み／書きアセンブリによって順次実行される。

**【0026】**

好ましくは，これに代えて，上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え，上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによって実行される。

**【0027】**

また，この発明の別の好適な実施形態によれば，直接書き込み装置，および表面上に直接に書込むための電気回路設計データを含むCADファイルであって，上記表面上に生成される多数の対象物のCADデータを含むCADファイルを受信し，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上にCADデータに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数の対象物についての直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステイッチングを防止する自動直接書き込み装置設定(an automatic direct writing machine configuration) (ADWMC) ユニットを備えている対象物製造システムがさらに提供される。

**【0028】**

好ましくは，上記システムは上記表面の光学的イメージングを実行する光学イメージャー(an optical imager)をさらに備えている。

**【0029】**

好ましくは，上記ADWMCユニットは，上記光学的イメージングによって見つけられたときに，上記CADファイルから導出されるデータを修正して上記表面の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮する。

**【0030】**

好ましくは，上記直接書き込みデータは，2つ以上の走査によって対象物が書き込まれないように設定(構成)されている。

**【0031】**

この発明の対象物製造システムの好適な実施形態によると，上記対象物が複数層から形成されており，上記複数層が互いに位置決めされて順次書き込まれ，上記ADWMCユニットは，上記直接書き込み装置を自動的に設定して，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上に上記CADデータに基づく複数層のそれについての直接書き込みデータを直接に書き込むものであり，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数の対象物の上記複数層についての上記直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステイッチングが防止される。

**【0032】**

好ましくは，上記複数の走査の各走査の範囲が走査継ぎ目によって規定され，上記直接書き込みデータが，上記走査継ぎ目のそれぞれが上記対象物の間に配置され，かつ上記対象物に重ならないように設定されている。

10

20

30

40

50

**【0033】**

好ましくは，上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目が接している。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。

**【0034】**

好ましくは，上記表面はフラットパネルディスプレイを含み，上記対象物は上記フラットパネルディスプレイのセルを含む。

**【0035】**

これに代えて，上記表面はウェハを含み，上記対象物はダイを含む。

**【0036】**

好ましくは，上記直接書き込み装置は単一の読み／書きアセンブリを備え，上記複数の走査が上記読み／書きアセンブリによって順次実行される。

10

**【0037】**

これに代えて，好ましくは，上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え，上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによって実行される。

**【0038】**

また，この発明のさらに別の好適な実施形態によれば，表面上に直接に書込むための電気回路設計データを含むCADファイルであって，上記表面上に生成される多数の対象物のCADデータを含むCADファイルを受信し，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上にCADデータに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数の対象物の直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのスティッキングを防止する自動直接書き込み装置設定(an automatic direct write machine configuration) (ADWMC) ユニットを備える直接書き込み装置設定システムも提供される。

20

**【0039】**

好ましくは，この発明の直接書き込み装置設定システムは，上記表面の光学的イメージングを実行する光学的イメージヤーも備えている。

**【0040】**

好ましくは，上記ADWMCユニットは，上記光学的イメージングによって見つけられたときに，上記CADファイルから導出されるデータを修正して上記表面の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮する。

30

**【0041】**

好ましくは，上記直接書き込みデータは，2つ以上の走査によって対象物が書き込まれないように設定されている。

**【0042】**

この発明の直接書き込み装置設定システムの好適な一実施形態によれば，上記対象物が複数層から構成されており，上記複数層が互いに位置決めされて順次書き込まれ，上記ADWMCユニットは，上記直接書き込み装置を自動的に設定して，上記表面の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記表面上に上記CADデータに基づいて複数層のそれぞれについての直接書き込みデータを直接に書き込むものであり，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数の対象物の上記複数層についての上記直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのスティッキングが防止される。

40

**【0043】**

好ましくは，上記複数の走査の各走査の範囲が走査継ぎ目によって規定され，上記直接書き込みデータが，上記走査継ぎ目のそれぞれが上記対象物の間に配置され，かつ上記対象物に重ならないように設定されている。

**【0044】**

50

上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。これに代えて、上記複数の走査のうちの隣接するものの走査継ぎ目が接している。これに代えて、上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。

**【0045】**

好ましくは、上記表面はフラットパネルディスプレイを含み、上記対象物は上記フラットパネルディスプレイのセルを含む。

**【0046】**

これに代えて、上記表面はウェハを含み、上記対象物はダイを含む。

**【0047】**

好ましくは、上記直接書き込み装置は単一の読み／書きアセンブリを備え、上記複数の走査が上記読み／書きアセンブリによって順次実行される。

10

**【0048】**

これに代えて、上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え、上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによって実行される。

**【0049】**

この発明のさらに好適な一実施形態によると、基板上に直接に書き込むための電気回路設計データを含むCADファイルであって、上記基板上に生成される多数のダイについてのCADデータを含むCADファイルを受信し、上記基板の幅よりも短い走査幅をそれぞれ有する複数の走査において、上記基板上に上記CADデータに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し、上記設定が、上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイについての上記直接書き込みデータを配置することを含み、これによって隣接する走査間の直接書き込みデータのスティッ칭が防止され、上記直接書き込み装置を動作させて上記多数のダイを基板上に作成する電気回路の製造方法がさらに提供される。

20

**【0050】**

好ましくは、この発明の電気回路の製造方法は、上記基板の光学的イメージングを実行することをさらに含む。

**【0051】**

好ましくは、上記自動的設定は、上記光学的イメージングによって見つけられたときに、上記CADファイルから導出されるデータを修正して上記基板の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮する。

30

**【0052】**

好ましくは、上記直接書き込みデータは、2つ以上の走査によってダイ(die)が書き込まれないように設定されている。

**【0053】**

この発明の電気回路の製造方法の好適な一実施形態によると、上記ダイが複数層から形成されており、上記複数層が互いに位置決めされて順次書き込まれ、上記自動的設定が、上記直接書き込み装置を自動的に設定して、上記基板の幅よりも短い走査幅をそれぞれが有する上記複数の走査において、上記基板上に上記CADデータに基づく複数層のそれぞれについての直接書き込みデータを直接に書き込むものであり、上記設定が、上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記複数層についての上記直接書き込みデータを配置することを含み、これによって隣接する走査間の直接書き込みデータのスティッ칭が防止される。

40

**【0054】**

好ましくは、上記複数の走査の各走査の範囲は走査継ぎ目によって規定され、上記直接書き込みデータは、上記走査継ぎ目のそれぞれが上記ダイの間(between the dies)に配置され、かつ上記ダイに重ならないように設定されている。

**【0055】**

好ましくは、上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。

50

これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目が接している。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。

【0056】

好ましくは，上記直接書き込み装置は単一の読み／書きアセンブリを備え，上記複数の走査が上記読み／書きアセンブリによって順次実行される。

【0057】

これに代えて，上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え，上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによって実行される。

【0058】

この発明のさらに別の好適な実施形態によれば，基板上に直接に書込むための電気回路設計データを含むCADファイルであって，上記基板上に生成される多数のダイのCADデータを含むCADファイルを受信し，上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記基板上に上記CADデータに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイについての上記直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステイッキングが防止される直接書き込み装置設定方法がさらに提供される。

【0059】

好ましくは，この発明の直接書き込み装置設定方法は，上記基板の光学的イメージングを実行することも含む。

【0060】

好ましくは，上記自動的設定は，上記光学的イメージングによって見つけられたときには，上記CADファイルから導出されるデータを修正して上記基板の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮する。

【0061】

好ましくは，上記直接書き込みデータは，2つ以上の走査によってダイが書き込まれないように設定されている。

【0062】

この発明の直接書き込み装置設定方法の好適な一実施形態によれば，上記ダイが複数層から形成されており，上記複数層が互いに位置決めされて順次書き込まれ，上記自動的設定が，上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査において，上記基板上に上記CADデータに基づく上記複数層のそれぞれについての直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し，上記設定が，上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記複数層についての直接書き込みデータを配置することを含み，これによって隣接する走査間の直接書き込みデータのステイッキングが防止される。

【0063】

好ましくは，上記複数の走査の各走査の範囲が走査継ぎ目によって規定され，上記直接書き込みデータが，上記走査継ぎ目のそれぞれが上記ダイの間に配置され，かつ上記ダイに重ならないように設定されている。

【0064】

好ましくは，上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目が接している。これに代えて，上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。

【0065】

好ましくは，上記直接書き込み装置は単一の読み／書きアセンブリを備え，上記複数の走査が上記読み／書きアセンブリによって順次実行される。

【0066】

これに代えて，上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え，上記複

10

20

30

40

50

数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによつて実行される。

【0067】

また、この発明のさらに別の好適な実施形態によれば、直接書込み装置と、基板上に直接に書込むための電気回路設計データを含むCADファイルであつて、上記基板上に生成される多数のダイのCADデータを含むCADファイルを受信し、上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査において、上記基板上に上記CADデータに基づく直接書込みデータを直接に書き込むように直接書込み装置を自動的に設定し、上記設定が、上記複数の走査それが上記走査幅内に並んで書き込まれるように上記多数のダイの上記直接書込みデータを配置することを含み、これによつて隣接する走査間の直接書込みデータのスティッ칭を防止する自動直接書込み装置設定(ADWMC)ユニットを備える電気回路製造システムが提供される。10

【0068】

好ましくは、請求項81に記載の電気回路製造システムは、上記基板の光学的イメージングを実行する光学的イメージヤーも備えている。

【0069】

好ましくは、上記ADWMCユニットは、上記光学的イメージングによって見つけられたときに、上記CADファイルから導出されるデータを修正して、上記基板の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮する。20

【0070】

好ましくは、上記直接書込みデータは、2つ以上の走査によつてダイが書き込まれないように設定されている。

【0071】

この発明に係る電気回路製造システムの好適な一実施形態によると、上記ダイが複数層から形成されており、上記複数層が互いに位置決めされて順次書き込まれ、上記ADWMCユニットは、上記直接書込み装置を自動的に設定して、上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査において、上記基板上に上記CADデータに基づいて複数層のそれについての直接書込みデータを直接に書き込むものであり、上記設定が、上記複数の走査のそれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記複数層の上記直接書込みデータを配置することを含み、これによつて隣接する走査間の直接書込みデータのスティッ칭が防止される。30

【0072】

好ましくは上記複数の走査の各走査の範囲が走査継ぎ目によつて規定され、上記直接書込みデータが、上記走査継ぎ目のそれが上記ダイの間に配置され、かつ上記ダイに重ならないように設定されている。

【0073】

好ましくは、上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。これに代えて、上記複数の走査のうちの隣接するものの走査継ぎ目が接している。これに代えて、上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。40

【0074】

好ましくは、上記直接書込み装置は单一の読み／書きアセンブリを備え、上記複数の走査は上記読み／書きアセンブリによつて順次実行される。

【0075】

これに代えて、上記直接書込み装置は2つ以上の読み／書きアセンブリを備え、上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み／書きアセンブリによつて実行される。

【0076】

また、この発明の別の好適な実施形態によると、基板上に直接に書込むための電気回路設計データを含むCADファイルであつて、上記基板上に生成される多数のダイについてのCADデータを含むCADファイルを受信し、上記基板の幅よりも短い走査幅をそれぞ50

れが有する複数の走査において、上記基板上に上記 C A D データに基づく直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し、上記設定が、上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記直接書き込みデータを配置することを含み、これによって隣接する走査間の直接書き込みデータのステイッキングを防止する自動直接書き込み装置設定（ A D W M C ）ユニットを備える、直接書き込み装置設定システムがさらに提供される。

**【 0 0 7 7 】**

好ましくは、この発明の直接書き込み装置設定システムは、上記基板の光学的イメージングを実行する光学的イメージヤーも備えている。

**【 0 0 7 8 】**

好ましくは、上記 A D W M C ユニットは、上記光学的イメージングによって見つけられたときに、上記 C A D ファイルから導出されるデータを修正して上記基板の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮する。

**【 0 0 7 9 】**

好ましくは、上記直接書き込みデータは、2つ以上の走査によってダイが書き込まれないように設定されている。

**【 0 0 8 0 】**

この発明の直接書き込み装置設定システムの好適な一実施形態によると、上記ダイが複数層から形成されており上記複数層が互いに位置決めされて順次書き込まれ、上記 A D W M C ユニットが、上記基板の幅よりも短い走査幅をそれぞれが有する複数の走査において、上記基板上に上記 C A D データに基づいて上記複数層のそれぞれについての直接書き込みデータを直接に書き込むように直接書き込み装置を自動的に設定し、上記設定が、上記複数の走査のそれぞれが上記走査幅内に並んで書き込まれるように上記多数のダイの上記複数層についての上記直接書き込みデータを配置することを含み、これによって隣接する走査間の直接書き込みデータのステイッキングが防止される。

**【 0 0 8 1 】**

好ましくは上記複数の走査の各走査の範囲が走査継ぎ目によって規定され、上記直接書き込みデータが、走査継ぎ目のそれぞれが上記ダイの間に配置され、かつ上記ダイに重ならないように設定されている。

**【 0 0 8 2 】**

好ましくは、上記複数の走査のうちの隣接するものの走査継ぎ目が相互に離れている。これに代えて、上記複数の走査のうちの隣接するものの走査継ぎ目が接している。これに代えて、上記複数の走査のうちの隣接するものの走査継ぎ目がオーバーラップしている。

**【 0 0 8 3 】**

好ましくは、上記直接書き込み装置は単一の読み／書きアセンブリを備え、上記複数の走査が上記読み／書きアセンブリによって順次実行される。

**【 0 0 8 4 】**

これに代えて、上記直接書き込み装置は2つ以上の読み／書きアセンブリを備え、上記複数の走査が少なくとも部分的に相互同時に動作する複数の上記読み書きアセンブリによって実行される。

**【 0 0 8 5 】**

この発明は、図面と併せた以下の詳細な説明によって、より深く理解されかつ認識されるであろう。

**【 図面の簡単な説明 】**

**【 0 0 8 6 】**

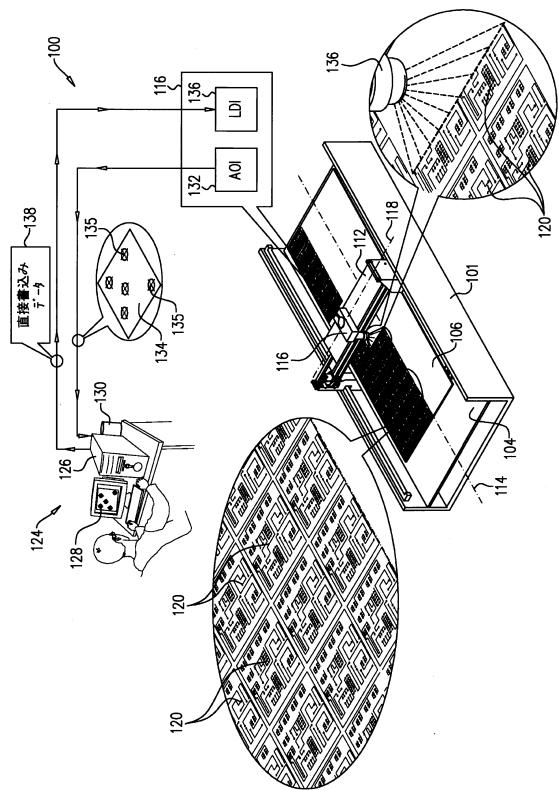

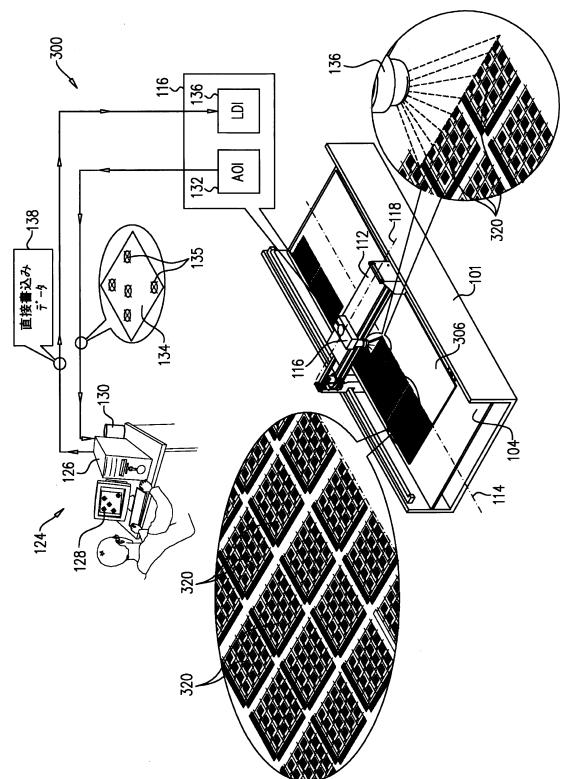

**【 図 1 A 】**この発明の好ましい一実施形態にしたがって構成されかつ動作可能とされる、コンピュータ化された直接書き込みシステムの簡略図である。

**【 図 1 B 】**この発明の好ましい一実施形態にしたがって構成されかつ動作可能とされる、コンピュータ化された直接書き込みシステムの簡略図である。

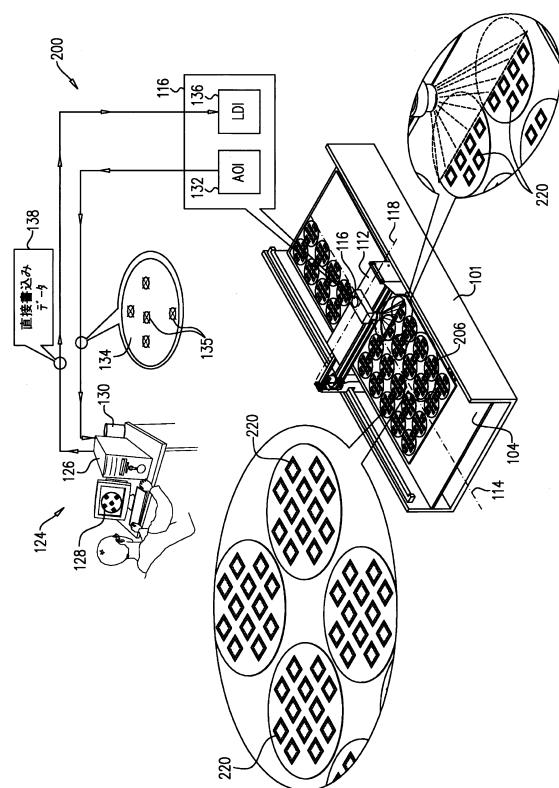

**【 図 2 A 】**この発明の他の好ましい実施形態にしたがって構成されかつ動作可能とされる

10

20

30

40

50

コンピュータ化された直接書き込みシステムの簡略図である。

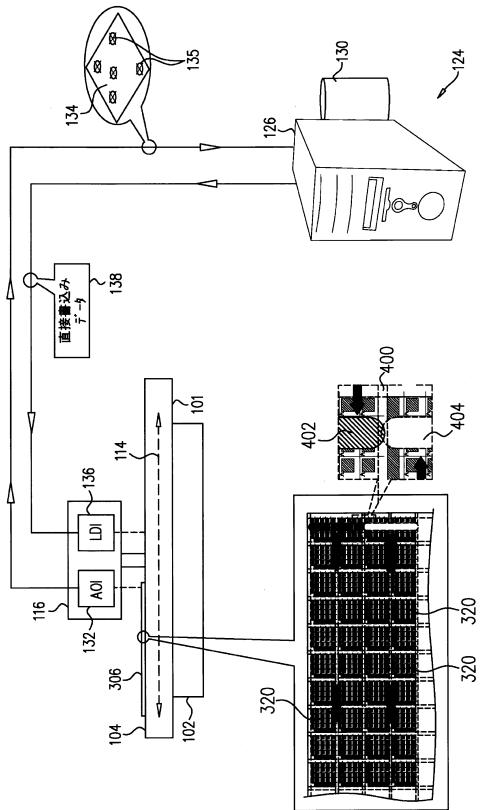

【図2B】この発明の他の好ましい実施形態にしたがって構成されかつ動作可能とされるコンピュータ化された直接書き込みシステムの簡略図である。

【図3A】この発明のさらに他の好ましい実施形態にしたがって構成されかつ動作可能とされるコンピュータ化された直接書き込みシステムの簡略図である。

【図3B】この発明のさらに他の好ましい実施形態にしたがって構成されかつ動作可能とされるコンピュータ化された直接書き込みシステムの簡略図である。

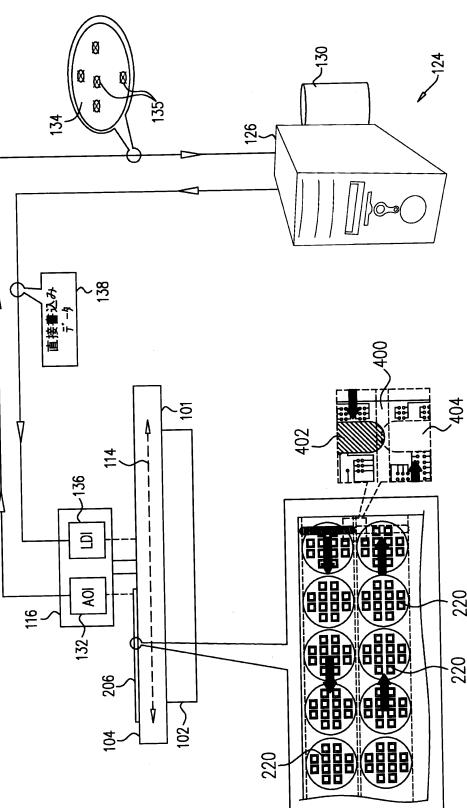

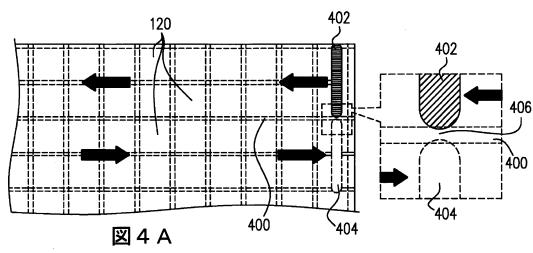

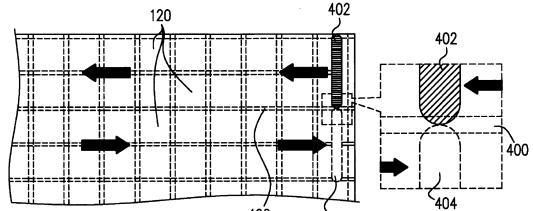

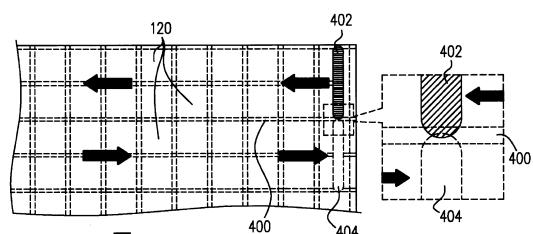

【図4】A, BおよびCは、この発明の好ましい一実施形態による、3つの考えられる走査パターンをそれぞれ示す、図1Aに示す代表的な対象物配置の簡略図である。

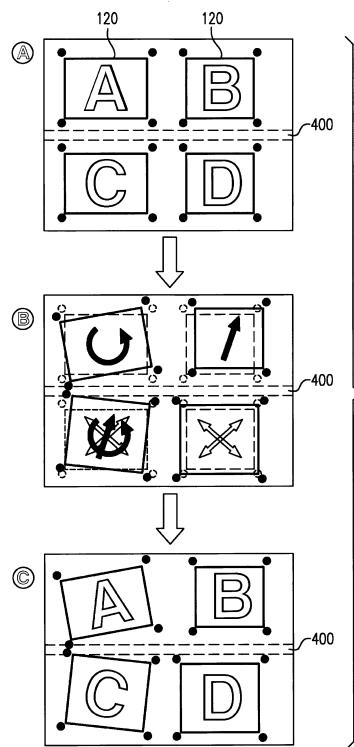

【図5】この発明の好ましい一実施形態による、直接書き込みのためのCADデータの適応する3つの連続状態を示す簡略図である。 10

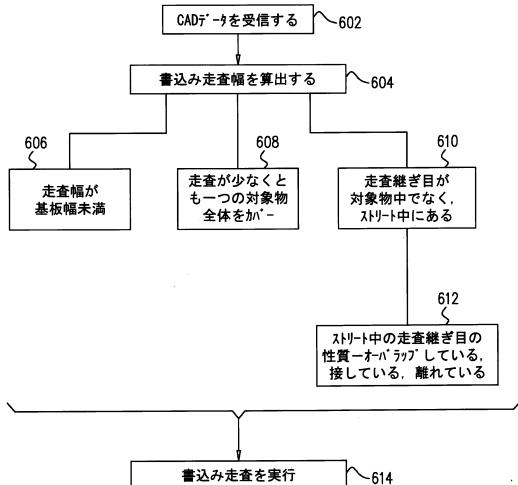

【図6A】直接書き込み装置の自動設定の2つの選択的方法を示す概略的なフローチャートである。

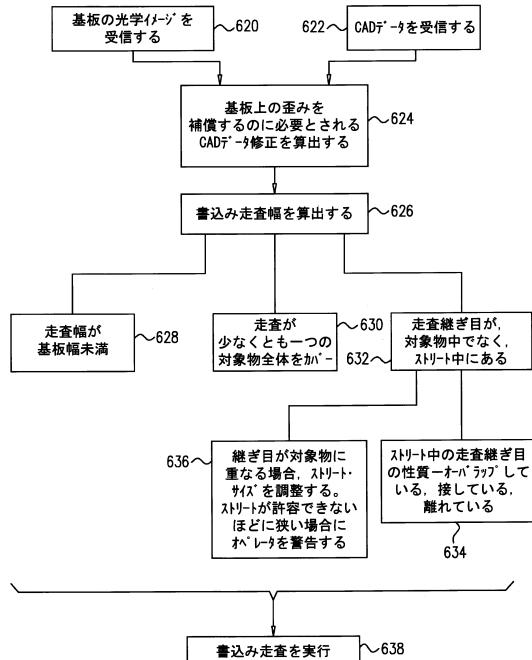

【図6B】直接書き込み装置の自動設定の2つの選択的方法を示す概略的なフローチャートである。

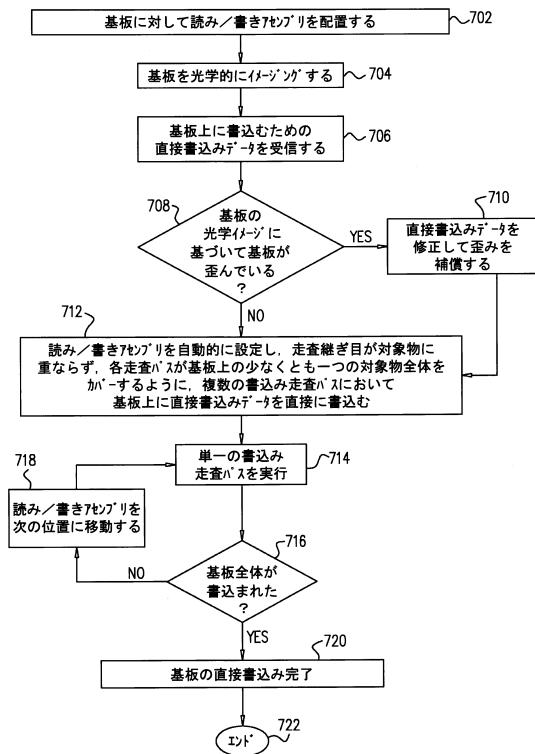

【図7A】この発明の2つの選択的な実施形態の動作をそれぞれ示す概略的なフローチャートである。

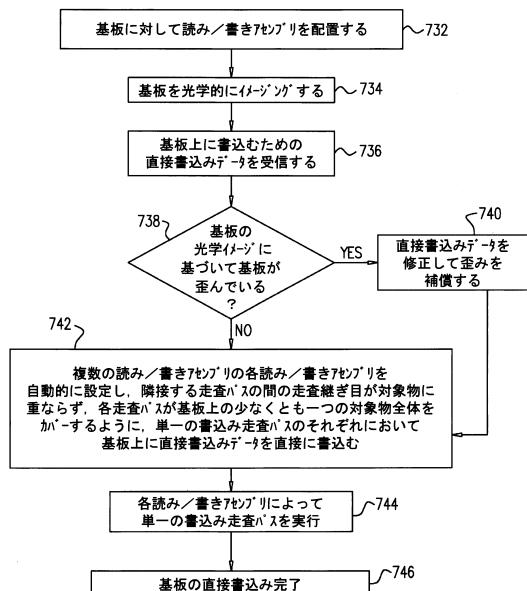

【図7B】この発明の2つの選択的な実施形態の動作をそれぞれ示す概略的なフローチャートである。

#### 【発明を実施するための形態】

##### 【0087】

はじめに図1Aおよび図1Bを参照して、図1Aおよび図1Bは、この発明の好ましい一実施形態にしたがって構成されかつ動作可能とされる、コンピュータ化された直接書き込みシステム(a system for computerized direct writing)の簡略図である。 20

##### 【0088】

図1Aおよび図1Bに示すように、好ましくは従来の光学支持テーブル102に搭載されたシャーシ(筐体)101を好ましくは備える、コンピュータ化直接書き込みシステム100が提供される。シャーシ101は好ましくは基板支持面104を規定し、その上にパターニング対象の基板106を載置することができる。上記基板106は基板上に実行されるコンピュータ化直接書き込みに適する任意の基板を含み、上記パターニングは、通常、基板106の少なくとも一方の表面上において、上記表面を覆うフォトレジストをレーザ光に露光することによって、対象物(物体)(objects)を規定する。この直接書き込み処理は好ましくは複数の対象物をプリントするものであり、上記対象物(複数)がこの発明の好ましい一実施形態にしたがって上記表面上に配置される。 30

##### 【0089】

この明細書において使用する用語「対象物」は、コンピュータ化直接書き込みによって基板106上にパターニング可能な任意のユニット(unit)を表すもので、典型的にはユニットは、基板上にパターニングされた他の隣り合うユニットから離れたものであることを理解されたい。このようなユニットとして、非限定的な例として、集積回路ダイ(集積回路チップ)(integrated circuit dies), ファンアウトダイ(fan out dies), フラットパネルディスプレイの一部を形成するセル、およびPCB上の電子回路モジュールを挙げることができる。 40

##### 【0090】

基板106は、典型的にはパネルまたはウェハであり、ガラス、ポリイミド、またはその他任意のプラスチック製の、剛性の、もしくは可撓性の材料製のものが含まれる。さらに、基板106は、作製中にガラス等の剛性支持層に貼り合わされて、作製後に取り外される可撓性基板であってもよい。これに加えてまたは代えて、基板106を、エポキシ化合物等の結合材料中に埋め込まれたダイのような埋込み対象物(embedded objects)によって構成してもよい。基板106およびその上にパターニングされた対応する対象物の様々な例示的実施形態については、図2A～図3Bを参照して以下に示す。 50

## 【0091】

シャーシ 101 に対して規定される第 1 の軸 114 に平行な軸に沿って、基板支持面 104 に対して直線運動するブリッジ 112 が配置されている。他の実施形態（図示略）においては、ブリッジを固定し、上記支持面およびその上に載置された基板と一緒に移動させる、またはブリッジおよび支持面の両方を相対的に移動させてもよい。好ましくは、少なくとも 1 つの読み／書きアセンブリがブリッジ 112 に沿って配置される。ここでは一例として、第 1 の軸 114 に垂直な第 2 の軸 118 に沿うブリッジ 112 に対して選択的に位置決めすることができる単一の読み／書きアセンブリ 116 が配置されており、これによって基板 106 上に複数の順次平行走査を実行することができ、走査のそれぞれが複数の対象物 120 を生成する。

10

## 【0092】

これに代えて、軸 118 に沿うブリッジ 112 上に複数の読み／書きアセンブリ 116 を並べて配置し、これによって複数のアセンブリ 116 のうちの対応するアセンブリによって基板 106 上において複数の走査を同時にまたは部分的に同時に実行できるようにしてもよく、走査のそれぞれが複数の対象物 120 を生成する。このような複数の走査は平行であるのが好ましいが、必ずしも平行でなくてもよい。

## 【0093】

対象物 120 は同一であるのが好ましいが、必ずしも同一でなくともよく、図 1A および図 1B に示すように、軸 114 と平行な方向に順々にかつ軸 118 と平行に並べて配置することができる。これに代えて、非直線の繰返しパターンまたは非繰返しパターン (non-linear repeating or non-repeating pattern) で対象物 120 を配置してもよい。

20

## 【0094】

また、システム 100 は好ましくは制御アセンブリ 124 を備え、制御アセンブリは好ましくはユーザインターフェース 128 を有するコンピュータ 126 を含む。コンピュータ 126 は、好ましくは読み／書きアセンブリ 116 を動作させるように動作するソフトウェアモジュールを含む。

## 【0095】

また、制御アセンブリ 124 は好ましくは書込み命令データベース 130 を含み、そこに、基板 106 の少なくとも 1 つの表面上に対象物 120 を書き込むために用いられる、この発明の一実施形態によるコンピュータ支援設計 (CAD) 命令が含まれている。

30

## 【0096】

この発明の好適な一実施形態によると、少なくとも 1 つの読み／書きアセンブリ 116 は、好ましくは基板 106 を光学的にイメージング（画像化、撮像）して基板 106 の光学画像 134 をコンピュータ 126 に提供するように動作する自動光学イメージング・サブシステム (automated optical imaging subsystem) (AOI) 132 を含む。この光学画像 134 は基板 106 上の基準 (fiducials) 135 の光学画像を含み、基準 135 はシステム 100 の位置決め（位置合わせ）(registration) および／または校正に有用である。

## 【0097】

読み／書きアセンブリ 116 はさらに、好ましくはレーザ直接イメージング・サブシステム (laser direct imaging subsystem) (LDI) 136 のような直接イメージング・サブシステムを含み、これは、コンピュータ 126 から受信した直接書込みデータ 138 に応答して基板 106 上にレーザ書込み（描画）するように動作して対象物 120 を生成する光学ライター（光学的書込み装置）(optical writer) を含む。この明細書において、AOI サブシステム 132 および LDI サブシステム 136 の両方がイメージング・サブシステムのタイプとして言及されているが、これらのサブシステムのそれぞれによって実行されるイメージングは相互に異なる性質のものであることを理解されたい。AOI サブシステム 132 は基板 106 の光学イメージングを実行してその光学イメージを取得するものであり、基板 106 上への直接書込み（直接描画）(direct writing) の実行に先立って行われるシステム 100 の位置決め（位置合わせ）および校正を目的とする。これ

40

50

に対してLDIサブシステム136は、基板106上へのパターンのレーザイメージングによって基板106上に直接書き込みを実行する。

#### 【0098】

一例として、LDI136は、この発明と同じ譲受人に譲渡された、米国特許第8,531,751号に記載されているタイプのレーザスキャナとすることができる。この発明とともに用いるのに適する直接イメージング・システムの他の例としては、日本国東京のSCREENセミコンダクターから販売されているDirect Imaging System、モデル番号DW-3000、およびドイツ・ハイデルベルグのHEIDELBERG Instrumentsから市販されているMaskless Aligner System、モデル番号MLA150が挙げられる。

#### 【0099】

制御アセンブリ124およびそのコンピュータ126は、好ましくは、基板106への直接書き込みのための電気回路設計データを含むCADファイルであって、基板106上に生成される多数の対象物120のためのCADデータを含むCADファイルを、データベース130から受信する。

#### 【0100】

好ましくは、制御アセンブリ124、より詳細にはコンピュータ126は、上記基板の幅よりも短い（狭い、小さい）走査幅（a scan width less than the width of the substrate）をそれぞれが有する複数の平行走査（plural parallel scans）において、上記基板106上にCADデータに基づく直接書き込みデータを直接に書き込むように、上記少なくとも一つの読み／書きアセンブリ116を自動的に設定する。この複数の平行走査は、本書に示すように単一の位置調整可能な読み／書きアセンブリによって順次実行してもよいし、複数の読み／書きアセンブリを用いて同時にまたは部分的に同時に実行してもよい。

#### 【0101】

少なくとも一つの読み／書きアセンブリ116は、このように、基板106上に直接書き込みデータを直接に書き込むように動作する直接書き込み装置（direct-write machine）の特に好適な一実施形態であることを理解されたい。コンピュータ126を備える制御アセンブリ124はさらに、それに相応して、基板106の少なくとも一つの表面への直接書き込みのための電気回路設計データを含むCADファイルを受信し、かつ複数の走査において基板106上にCADデータに基づく直接書き込みデータを直接に書き込むように、少なくとも一つの読み／書きアセンブリ116を備える上記直接書き込み装置を自動的に設定するように動作する自動直接書き込み装置設定（automatic direct write machine configuration：ADWMC）ユニットと呼ぶことができることを理解されたい。

#### 【0102】

この発明の好適な一実施形態の特定の特徴は、制御アセンブリ124、より詳細にはコンピュータ126が、複数の走査において一の対象物が書き込まれないようにし（no object is written in multiple scans），複数の走査のそれぞれにおいて、走査幅の範囲内で多数の対象物120が並んで書き込まれるように、多数の対象物120の直接書き込みデータを自動的に設定し、これによって隣接する走査間の直接書き込みデータのステッチングの必要性（the need for stitching of direct writing data between adjacent scans）を未然に排除することにある。

#### 【0103】

好ましくは、上記読み／書きアセンブリ116は、制御アセンブリ124によって動作されて、複数の走査バスにおいて基板106上に多数の対象物120を作成し、ここで隣接する走査バスの継ぎ目（seam）が対象物中に位置せず（the seam of adjacent scan passes is not located within an object），これによって隣接走査間の直接書き込みデータのステッチングの必要性が未然に排除される。隣接する走査バスの継ぎ目は、図4A～図4Cを参照して以下に説明するように、重なる配置であってもよく、接する配置であってもよく、または相互に離れた配置であってもよい。この発明の好適な一実施形態によると、存在する継ぎ目のタイプにかかわらず、上記継ぎ目は対象物の間（between objects

10

20

30

40

50

)に配置され、対象物には重ならない。

**【0104】**

L D I 1 3 6 によってもたらされる最大走査長 (maximum scan length) の固有限界に起因して、基板 1 0 6 の全幅を走査するためには典型的には複数の走査パスが必要であることを理解されたい。このような複数の走査パスは、単一の位置調整可能な走査ヘッドによって順次実行してもよく、並列に動作する複数の走査ヘッドを用いて少なくとも部分的に同時に実行してもよい。走査長の上記限界は、いくつかある因子のうち、基板表面への直接書き込みを実行する集束レーザ光線の所要サイズと L D I 1 3 6 の走査レンズの走査長との間において維持することが必要とされる臨界比 (critical ratio) によって決まる。

**【0105】**

この発明が提供するように、隣接する走査パスの継ぎ目が対象物 1 2 0 に重ならずには間に位置するように、走査のそれぞれにおいて、走査幅の範囲内となるように対象物 1 2 0 の直接書き込みデータが書き込まれないとすると、複数の所要走査の隣接する走査パスは典型的には対象物に重なるものになる。結果として、この発明による自動直接書き込み設定がなければ、対象物中の電気回路造形が必然的に 2 つ以上の走査パスによって露光されることになり、走査パス間におけるオーバーラップ箇所に集まる機械的かつ光学的誤差に起因するスティッチング効果が生じる。スティッチング効果、さらにはその影響を軽減するために典型的に必要とされる様々な複雑な技術が、走査パス間のオーバーラップの回避に起因して、この発明において効果的に防止される。

**【0106】**

基板 1 0 6 は、単層の対象物 1 2 0 のみがパターニングされた单層基板に限定されないことを理解されたい。むしろ、システム 1 0 0 は、付加的方法において、層ごとに基板を選択的に修正して 3 次元構造を作成することができる。このように対象物 1 2 0 は複数層に形成することができ、複数層を、読み / 書きアセンブリ 1 1 6 を用いて互いに位置決めして順次書き込むことができる。対象物 1 2 0 が複数層に形成されている場合、読み / 書きアセンブリ 1 1 6 は、好ましくは、上述したように複数の走査において複数層のそれについて直接書き込みデータを直接に書き込むように自動的に設定され、各走査は基板 1 0 6 の表面の幅よりも短い走査幅を持ち、複数の走査のそれらが走査幅の範囲内に並んで書き込まれるように対象物 1 2 0 の複数層の直接書き込みデータを配置することによって、隣接する走査間の直接書き込みデータのスティッチングが防止される。

**【0107】**

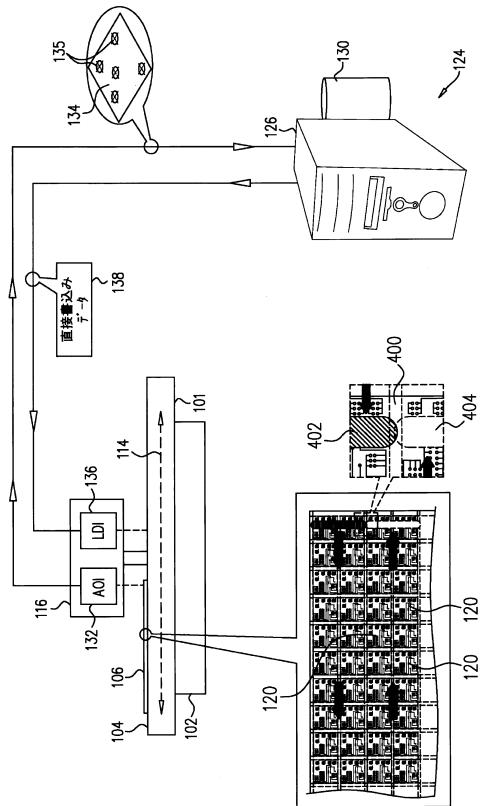

次に図 2 A および図 2 B を参照して、図 2 A および図 2 B は、この発明の別の好適な実施形態にしたがって構成され、かつ動作するコンピュータ化された直接書き込みシステムの簡略図である。

**【0108】**

図 2 A および図 2 B に示すように、好ましくは従来の光学支持テーブル 1 0 2 に搭載され、かつ好ましくはパターニング対象の基板をその上に載置可能な基板支持面 1 0 4 を規定するシャーシ 1 0 1 を好ましくは備える、コンピュータ化直接書き込みシステム 2 0 0 が提供される。ここで、一例として、パターニング対象の基板は、好ましくは半導体ウェハ 2 0 6 を含み、典型的には、上記パターニングは、ウェハ表面を覆うフォトレジストをレーザ光に露光することによってウェハ 2 0 6 の少なくとも 1 つの表面上にダイ (複数) (dies) を規定する。直接書き込み処理は好ましくは多数のダイをプリントし、このダイが、この発明の好適な実施形態にしたがって表面上に配置される。このようなダイは、一例にすぎないが、集積回路ダイまたはファンアウトダイとすることができます。

**【0109】**

シャーシ 1 0 1 に対して規定される第 1 の軸 1 1 4 に平行な軸に沿って、基板支持面 1 0 4 に対して直線運動するようにブリッジ 1 1 2 が配置されている。他の実施形態 (図示略) においては、ブリッジを固定し、上記支持面およびその上に載置された基板を一緒に移動させる、またはブリッジおよび支持面の両方を相対的に移動させてよい。第 1 の軸 1 1 4 に垂直な第 2 の軸 1 1 8 に沿うブリッジ 1 1 2 に対して選択的に位置決めすること

10

20

30

40

50

ができる少なくとも 1 つ の読み / 書きアセンブリ 1 1 6 が配置されており、これによってウェハ 2 0 6 上において複数の順次平行走査を実行することができ、走査のそれぞれが複数のダイ 2 2 0 を生成する。ダイ 2 2 0 は同一であることが好ましいが、必ずしも同一でなくともよく、好ましくは軸 1 1 4 と平行な方向に順々に軸 1 1 8 と平行に並んで配置される。

#### 【 0 1 1 0 】

これに代えて、軸 1 1 8 に沿うブリッジ 1 1 2 上に複数の読み / 書きアセンブリ 1 1 6 を並べて配置し、これによって複数のアセンブリ 1 1 6 のうちの対応するアセンブリによって、それぞれが多数のダイ 2 2 0 を生成する複数の走査を、ウェハ 2 0 6 上において同時にまたは部分的に同時に実行できるようにしてもよい。このような複数の走査は平行であるのが好ましいが、必ずしも平行でなくてもよい。10

#### 【 0 1 1 1 】

また、システム 2 0 0 は好ましくは制御アセンブリ 1 2 4 を備え、制御アセンブリは好ましくはユーザインターフェース 1 2 8 を有するコンピュータ 1 2 6 を含む。コンピュータ 1 2 6 は、好ましくは読み / 書きアセンブリ 1 1 6 を動作させるように動作するソフトウェアモジュールを含む。

#### 【 0 1 1 2 】

また、制御アセンブリ 1 2 4 は好ましくは書込み命令データベース 1 3 0 を含み、そこに、ウェハ 2 0 6 にダイ 2 2 0 を書き込むために用いられる、この発明の一実施形態によるコンピュータ支援設計（C A D）命令が含まれている。20

#### 【 0 1 1 3 】

この発明の好適な一実施形態によると、読み / 書きアセンブリ 1 1 6 は、好ましくはウェハ 2 0 6 をイメージングして画像 1 3 4 をコンピュータ 1 2 6 に提供するように動作する自動光学イメージング・サブシステム（A O I）1 3 2 を含む。この光学画像 1 3 4 はウェハ 2 0 6 上の基準 1 3 5 の光学画像を含み、基準 1 3 5 はシステム 2 0 0 の位置決めおよび / または校正に有用である。

#### 【 0 1 1 4 】

少なくとも 1 つ の読み / 書きアセンブリ 1 1 6 はさらに、好ましくはレーザダイレクトイメージング・サブシステム（L D I）1 3 6 のようなダイレクトイメージング・サブシステムを含み、これは、コンピュータ 1 2 6 から受信した直接書込みデータ 1 3 8 に応答してウェハ 2 0 6 にレーザ描画するように動作してダイ 2 2 0 を生成する光学ライターを含む。この明細書において、A O I サブシステム 1 3 2 および L D I サブシステム 1 3 6 の両方がイメージング・サブシステムのタイプとして言及されているが、これらのサブシステムのそれぞれによって実行されるイメージングは相互に異なる性質のものであることを理解されたい。A O I サブシステム 1 3 2 は光学イメージングを実行してその光学画像を取得するものであり、ウェハ 2 0 6 上への直接書込みの実行に先立って行われるシステム 2 0 0 の位置決めおよび校正を目的とする。これに対して L D I サブシステム 1 3 6 は、ウェハ 2 0 6 上へのパターンのレーザイメージングによってウェハ 2 0 6 上に直接書込みを実行する。30

#### 【 0 1 1 5 】

一例として、L D I 1 3 6 は、この発明と同じ譲受人に譲渡された、米国特許第 8 , 5 3 1 , 7 5 1 号に記載されているタイプのレーザスキャナとすることができます。この発明とともに用いるのに適するダイレクトイメージング・システムの他の例としては、日本国東京の S C R E E N セミコンダクターから販売されているDirect Imaging System、モデル番号 D W - 3 0 0 0 , およびドイツ・ハイデルベルグのHEIDELBERG Instrumentsから市販されているMaskless Aligner System、モデル番号 M L A 1 5 0 が挙げられる。40

#### 【 0 1 1 6 】

制御アセンブリ 1 2 4 およびそのコンピュータ 1 2 6 は、好ましくは、ウェハ 2 0 6 への直接書込みのための電気回路設計データを含む C A D ファイルであって、ウェハ 2 0 6 に生成される多数のダイ 2 2 0 のための C A D データを含む C A D ファイルを、データベ50

ース 130 から受信する。

**【0117】**

好ましくは、制御アセンブリ 124、より詳細にはコンピュータ 126 は、基板の幅より短い走査幅をそれぞれが有する複数の平行走査において、上記ウェハ 206 上に CAD データに基づく直接書き込みデータを直接に書き込むように、読み／書きアセンブリ 116 を自動的に設定する。少なくとも 1 つの読み／書きアセンブリ 116 は、このように、ウェハ 206 上に直接書き込みデータを直接に書き込むように動作する、直接書き込み装置の特に好適な一実施形態であることを理解されたい。コンピュータ 126 を備える制御アセンブリ 124 はさらに、それに相応して、ウェハ 206 の少なくとも 1 つの表面への直接書き込みのための電気回路設計データを含む CAD ファイルを受信し、かつ複数の走査においてウェハ 206 上に CAD データに基づく直接書き込みデータを直接に書き込むように、少なくとも 1 つの読み／書きアセンブリ 116 を備える上記直接書き込み装置を自動的に設定するように動作する、自動直接書き込み装置設定 (ADWMC) ユニットと呼ぶことができることを理解されたい。10

**【0118】**

この発明の好適な一実施形態の特定の特徴は、制御アセンブリ 124、より詳細にはコンピュータ 126 が、複数の走査中に一のダイが書き込まれないように、複数の走査のそれぞれにおいて、走査幅の範囲内で多数のダイが並んで書き込まれるように、多数のダイの直接書き込みデータを自動的に設定し、これによって隣接する走査間の直接書き込みデータのスティッ칭の必要性を未然に排除することにある。20

**【0119】**

好ましくは、上記読み／書きアセンブリ 116 は、制御アセンブリ 124 によって動作され、複数の走査バスにおいてウェハ 206 上に多数のダイ 220 を作成し、ここで隣接する走査バスの継ぎ目がダイ中に位置せず、これによって隣接する走査間の直接書き込みデータのスティッ칭の必要性が未然に排除される。隣接する走査バスの継ぎ目は、図 4 A ~ 図 4 C を参照して以下に説明するように、重なる配置であってもよく、接する配置であってもよく、または相互に離れた配置であってもよい。この発明の好適な一実施形態によると、存在する継ぎ目のタイプにかかわらず、上記継ぎ目はダイの間に配置され、ダイに重ならない。30

**【0120】**

L D I 136 によってもたらされる最大走査長の固有限界に起因して、ウェハ 206 の全幅を走査するには典型的には複数の走査バスが必要であることを理解されたい。このような複数の走査バスを、单一の位置調整可能な走査ヘッドによって順次実行してもよく、並列に動作する複数の走査ヘッドを用いて少なくとも部分的に同時に実行してもよい。走査長の上記限界は、いくつかある因子のうち、ウェハ表面への直接書き込みを実行する集束レーザ光線の所要サイズと L D I 136 の走査レンズの走査長との間において維持することが必要とされる臨界比によって決まる。一例として、ダイ 220 上に電気回路データを直接に書込むために必要とされる解像度を有するレーザスポットを提供するために、L D I 136 は、約 100mm の最大走査長をもたらすように制限される。これによって、300mm 幅のウェハは、その全幅を走査するために 3 つの走査バスを必要とする。40

**【0121】**

この発明が提供するように、隣接する走査バスの継ぎ目が多数のダイ 220 に重ならず、その間に位置するように、走査のそれぞれにおいて、走査幅の範囲内となるようにダイ 220 の直接書き込みデータが書き込まれないとすると、複数の所要走査の隣接する走査バスは典型的にはダイに重なるものとなる。結果として、この発明による自動直接書き込み設定がなければ、ダイ中の電気回路造形が必然的に 2 つ以上の走査バスによって露光されることになり、走査バス間におけるオーバーラップ箇所に集まる機械的かつ光学的誤差に起因するスティッ칭効果が生じる。スティッ칭効果、さらにはその影響を軽減するために典型的に必要とされる様々な複雑な技術が、走査バス間のオーバーラップの回避に起因して、この発明において効果的に防止される。50

**【0122】**

ウェハ206は、単層のダイ220のみがパターニングされた単層基板に限定されないことを理解されたい。むしろ、システム200は、付加的方法において、層ごとにウェハを選択的に修正して3次元構造を作成することができる。このように、ダイ220を複数層に形成することができ、複数層を、読み／書きアセンブリ116を用いて互いに位置決めして順次書き込むことができる。ダイ220が複数層に形成されている場合、読み／書きアセンブリ116は、好ましくは、上述したように複数の走査において複数層のそれぞれについて直接書き込みデータを直接に書き込むように自動的に設定され、各走査はウェハ206の表面の幅よりも短い走査幅を持ち、複数の走査のそれぞれが走査幅の範囲内となるように並んで書き込まれるようにダイ220の複数層の直接書き込みデータを配置することにより、隣接する走査間の直接書き込みデータのステイッキングが防止される。10

**【0123】**

次に図3Aおよび図3Bを参照して、図3Aおよび図3Bは、この発明の別の好適な実施形態にしたがって構成されかつ動作可能とされるコンピュータ化された直接書き込みシステムの簡略図である。

**【0124】**

図3Aおよび図3Bに示すように、好ましくは従来の光学支持テーブル102に搭載され、かつ好ましくはパターニング対象の基板106をその上に載置可能な基板支持面104を規定するシャーシ101を好ましくは備える、コンピュータ化直接書き込みシステム300が提供される。ここで、一例として、パターニング対象の基板は、好ましくはフラットパネルディスプレイ306を含み、上記パターニングは、典型的には、ディスプレイ表面を覆うフォトレジストをレーザ光に露光することによってディスプレイ306の少なくとも1つの表面上に素子(elements)を規定する。直接書き込み処理は好ましくはセルのマトリクスまたは多数のセルをプリントし、このセルが、この発明の好適な実施形態にしたがって表面上に配置される。20

**【0125】**

シャーシ101に対して規定される第1の軸114に平行な軸に沿って、基板支持面104に対して直線運動するようにブリッジ112が配置されている。他の実施形態(図示略)においては、ブリッジを固定し、上記支持面およびその上に載置された基板と一緒に移動させる、またはブリッジおよび支持面の両方を相対的に移動させててもよい。第1の軸114に垂直な第2の軸118に沿うブリッジ112に対して選択可能な位置決めすることができる少なくとも1つの読み／書きアセンブリ116が配置されており、これによってパネル306上において複数の順次平行走査を実行することができ、走査のそれぞれが複数のセル320を生成する。セル320は同一であることが好ましいが、必ずしも同一でなくてもよく、好ましくは軸114と平行な方向に順々に軸118と平行に並んで配置される。30

**【0126】**

これに代えて、軸118に沿うブリッジ112上に複数の読み／書きアセンブリ116を並べて配置し、これによって複数のアセンブリ116のうちの対応するアセンブリによって、それぞれが多数のセル320を生成する複数の走査を、パネル306上において同時または部分的に同時に実行できるようにしてもよい。このような複数の走査は平行であるのが好ましいが、必ずしも平行でなくてもよい。40

**【0127】**

また、システム300は好ましくは制御アセンブリ124を備え、制御アセンブリは好ましくはユーザインターフェース128を有するコンピュータ126を含む。コンピュータ126は、好ましくは読み／書きアセンブリ116を動作させるように動作するソフトウェアモジュールを含む。

**【0128】**

また、制御アセンブリ124は好ましくは書き込み命令データベース130を含み、そこに、パネル306にセル320を書き込むために用いられる、この発明の一実施形態によ50

るコンピュータ支援設計（C A D）命令が含まれている。

【0129】

この発明の好適な一実施形態によると、読み／書きアセンブリ116は、好ましくはパネル306をイメージングして画像134をコンピュータ126に提供するように動作する自動光学イメージング・サブシステム（A O I）132を含む。この光学画像134はパネル306上の基準135の光学画像を含み、基準135はシステム300の位置決めおよび／または校正に有用である。

【0130】

読み／書きアセンブリ116はさらに、好ましくはレーザダイレクトイメージング・サブシステム（L D I）136のようなダイレクトイメージング・サブシステムを含み、これは、コンピュータ126から受信した直接書き込みデータ138に応答してパネル306にレーザ描画するように動作してセル320を生成する光学ライターを含む。この明細書において、A O Iサブシステム132およびL D Iサブシステム136の両方がイメージング・サブシステムのタイプとして言及されているが、これらのサブシステムのそれぞれによって実行されるイメージングは相互に異なる性質のものであることを理解されたい。A O Iサブシステム132は光学イメージング実行してその光学画像を取得するものであり、パネル306への直接書き込みの実行に先立って行われるシステム300の位置決めおよび校正を目的とする。これに対してL D Iサブシステム136は、パネル306へのパターンのレザイメージングによってパネル306上に直接書き込みを実行する。

【0131】

一例として、L D I136は、この発明と同じ譲受人に譲渡された、米国特許第8,531,751号に記載されているタイプのレーザスキャナとすることができる。この発明とともに用いるのに適するダイレクトイメージング・システムの他の例としては、日本国東京のS C R E E Nセミコンダクターから販売されているDirect Imaging System、モデル番号D W - 3000、およびドイツ・ハイデルベルグのHEIDELBERG Instrumentsから市販されているMaskless Aligner System、モデル番号M L A 150が挙げられる。

【0132】

制御アセンブリ124およびそのコンピュータ126は、好ましくは、パネル306への直接書き込みのための電気回路設計データを含むC A Dファイルであって、パネル306に生成される多数のセル320のためのC A Dデータを含むC A Dファイルを、データベース130から受信する。

【0133】

好ましくは、制御アセンブリ124、より詳細にはコンピュータ126は、基板の幅よりも短い走査幅をそれぞれが有する複数の平行走査において、上記パネル306上にC A Dデータに基づく直接書き込みデータを直接書き込むように、少なくとも1つの読み／書きアセンブリ116を自動的に設定する。少なくとも1つの読み／書きアセンブリ116は、このように、パネル306上に直接書き込みデータを直接に書き込むように動作する、直接書き込み装置の特に好適な一実施形態であることを理解されたい。コンピュータ126を備える制御アセンブリ124はさらに、それに相応して、パネル306の少なくとも1つの表面への直接書き込みのための電気回路設計データを含むC A Dファイルを受信し、かつ複数の走査においてパネル306上にC A Dデータに基づく直接書き込みデータを直接に書き込むように、読み／書きアセンブリ116を備える上記直接書き込み装置を自動的に設定するように動作する、自動直接書き込み装置設定（A D W M C）ユニットと呼ぶことができる。

【0134】

この発明の好適な一実施形態の特定の特徴は、制御アセンブリ124、より詳細にはコンピュータ126が、複数の走査内に一のセルが書き込まれないように、複数の走査のそれぞれにおいて走査幅の範囲内に多数のセルが並んで書き込まれるように、多数のセル320の直接書き込みデータを自動的に設定し、これによって隣接する走査間の直接書き込みデータのスティッ칭の必要性を未然に排除することにある。

10

20

30

40

50

**【 0 1 3 5 】**

好ましくは，上記読み／書きアセンブリ 116 は，制御アセンブリ 124 によって動作され，複数の走査パスにおいてパネル 306 上に多数のセル 320 を作成し，ここで隣接する走査パスの継ぎ目がセル中に位置せず，これによって隣接する走査間の直接書込みデータのステイッチングの必要性が未然に排除される。隣接する走査パスの継ぎ目は，図 4 A ~ 図 4 C を参照して以下に説明するように，重なる配置であってもよく，接する配置であってもよく，または相互に離れた配置であってもよい。この発明の好適な一実施形態によると，存在する継ぎ目のタイプにかかわらず，上記継ぎ目は素子の間に配置され，素子に重ならない。

**【 0 1 3 6 】**

L D I 136 によってもたらされる最大走査長の固有限界に起因して，パネル 306 の全幅を走査するには典型的には複数の走査パスが必要であることを理解されたい。このような複数の走査パスを，単一の位置調整可能な走査ヘッドによって順次実行してもよく，並列に動作する複数の走査ヘッドを用いて少なくとも部分的に同時に実行してもよい。走査長の上記限界は，いくつかある因子のうち，パネル表面への直接書込みを実行する集束レーザ光線の所要サイズと L D I 136 の走査レンズの走査長との間で維持することが必要とされる臨界比によって決まる。一例として，セル 320 上に電気回路データ直接に書込むために必要とされる解像度を有するレーザスポットを提供するために，L D I 136 は，約 300 mm の最大走査長をもたらすように制限される。これによって，2400 mm 幅のパネルは，その全幅を走査するために約 8 つの走査パスを必要とする。

**【 0 1 3 7 】**

この発明が提供するように，隣接する走査パスの継ぎ目が多数のセル 320 に重ならずその間に位置するように，走査のそれぞれにおいて，走査幅の範囲内になるようにセル 320 の直接書込みデータが書き込まれないとすると，複数の所要走査の隣接する走査パスは典型的にはセルに重なるものとなる。結果として，この発明による自動直接書込み設定がなければ，セル中の電気回路造形が必然的に 2 つ以上の走査パスによって露光されることになり，走査パス間におけるオーバーラップ箇所に集まる機械的および光学的誤差に起因するステイッチング効果が生じる。ステイッチング効果，さらにはその影響を軽減するために典型的に必要とされる種々な複雑な技術が，走査パス間のオーバーラップの回避に起因して，この発明において効果的に防止される。

**【 0 1 3 8 】**

パネル 306 は，LCD，OLED，またはフレキシブルディスプレイ等，当該技術分野において既知の様々なタイプの任意のフラットパネルディスプレイであってもよいことを理解されたい。さらにパネル 306 は，単層セル 320 のみがパターニングされた単層基板に限定されない。むしろ，システム 300 は，付加的方法において，層ごとにパネルを選択的に修正して 3 次元構造を作成することができる。このように，セル 320 を複数層に形成することができ，複数層を，読み／書きアセンブリ 116 を用いて互いに位置決めして順次書き込むことができる。セル 320 が複数層に形成されている場合，読み／書きアセンブリ 116 は，好ましくは，上述したように複数の走査において複数層のそれについて直接書込みデータを直接に書き込むように自動的に設定され，各走査はパネル 306 の表面の幅よりも短い走査幅を持ち，複数の走査のそれらが走査幅の範囲内に並んで書き込まれるようにセル 320 の複数層の直接書込みデータを配置することにより，隣接する走査間の直接書込みデータのステイッチングが防止される。

**【 0 1 3 9 】**

次に図 4 A，図 4 B および図 4 C を参照して，図 4 A，図 4 B および図 4 C は，3 つの別々の複数順次走査パス配置 (plural sequential scan pass arrangements) の簡略図であり，この発明の一実施形態の特定の特徴によると，これらはすべて，図中において符号 400 を付す「ストリート」(streets) に沿う走査パス間の継ぎ目 (the seam between the scan passes) の存在を特徴とする。

**【 0 1 4 0 】**

10

20

30

40

50

複数順次走査パスは、図1A～図3Bを参照して上述した上記装置の動作によって生成されるもので、はじめに軸118に沿う第1の位置にある読み／書きアセンブリ116を用いて軸114に沿う符号402を付す第1の走査パスを生成し、次に上記読み／書きアセンブリ116を軸118に沿う第2の位置に位置調整して、第1の走査パス402に平行に、符号404で示す第2の走査パスを生成することを理解されたい。機械寸法および必要とされる解像度に応じて、3つ以上の走査パスを、所与の基板上にすべての対象物を直接に書き込むために利用することができる。対象物は、図2Aおよび図2Bに示すダイ220、図3Aおよび図3Bに示すフラットパネルディスプレイのセル320、または任意のその他の適切な対象物とすることができます。

## 【0141】

10

これに代えて、複数の読み／書きアセンブリ116のそれぞれを、好ましくは軸118に沿って並んで配置するようにして設けてもよい。上記複数の読み／書きアセンブリの個々の読み／書きアセンブリ116は好ましくは同時にまたは部分的に同時に動作して好ましくは平行な複数の走査パスが生成され、走査パスのそれぞれが、上記基板の幅よりも短い走査パスを持つ。このような構成において、読み／書きアセンブリ（複数）のうちの第1のアセンブリによって生成された第1の走査パス402を、読み／書きアセンブリ（複数）のうちの第2のアセンブリによって生成された第2の走査パス404と同時に実行することができる。

## 【0142】

20

図4Aは、各走査パス402および404がギャップ406によって分離されており、上記ギャップが対象物120の隣接する行の間のストリート400に重なっている構成を示している。ここでは隣接する走査パス402、404間の継ぎ目がギャップである。

## 【0143】

図4Bは、対象物120の隣接する行間のストリート400に重なる位置において各走査パス402および404が接している構成を示している。ここでは隣接する走査パス402、404間の継ぎ目が境界（butting）である（接している、突きあっている）。

## 【0144】

30

図4Cは、対象物120の隣接する行間のストリート400に重なる位置において各走査パス402および404が部分的に重なっている構成を示している。ここでは隣接する走査パス402、404間の継ぎ目は部分的なオーバーラップである。

## 【0145】

図4A～図4Cではストリート400が直線として示されているが、これは必須ではないことを理解されたい。これに代えて、当業者によって容易に理解されるように、被直線状のストリートによって対象物120を隔離するように配置してもよく、隣接する走査パス間の継ぎ目は、対象物120に重なるのではなく、上記のストリート内に位置付けられる。

## 【0146】

次に図5を参照して、図5はこの発明の好適な一実施形態による図1A～図3Bの任意のシステム100、200、300の動作における3段階の連続動作（three successive operative stages）を示している。

40

## 【0147】

この発明の好適な一実施形態によると、直接書き込みデータの自動設定は、上記CADファイルからのデータを修正して上記基板の構成および位置の少なくとも一方における不正確さおよび歪みの少なくとも一方を考慮することを含む。

## 【0148】

図5に戻って、Aは、CADデータの配置の描写を示しており、ストリート400によって分離された格子パターン中に対象物120が配置され、その1つまたは複数に沿って、隣接する走査パス間の継ぎ目が位置する。Bは、対象物120のそれぞれの位置における基板の歪みを示すAOIデータの描写を示している。Cは、Bにおける歪みを補償するとともに、走査パスの継ぎ目がストリート400に重なりかつ対象物120に重ならない

50

ように構成された直接書き込みデータの描写を示している。歪みに対応するために、上記ストリート400の幅を狭める必要があることを理解されたい。歪みが極端な場合、警告をオペレータに送り、上記オペレータに手動で上記基板を再配向させて(reorient)、上記継ぎ目が対象物120に重ならないようにしてもよい。

#### 【0149】

図5に関する上記説明は対象物120に言及するものであるが、この呼称は説明を簡素にしつつ一般化することを目的するに過ぎず、対象物120は、一例として、ダイ220またはセル320として具現化できることを理解されたい。

#### 【0150】

さらに、上記の歪みを補償する自動設定は、書き込み動作に先立って取得されるAOIデータに基づいて、または各走査後に動的に「オンザフライ」で取得されるAOIデータに基づいて、パネル全体についての書き込み動作に先立って行うことができることを理解されたい。10

#### 【0151】

また、設定変更は、たとえば支持面のシフトまたは回転に起因して（たとえば、支持面の不正確な平行移動を動的に補償するために）、基板全体の変化に応答して実行することができることを理解されたい。

#### 【0152】

次に図6Aおよび図6Bを参照して、図6Aおよび図6Bは、直接書き込み装置を自動的に設定する2つの別々の方法を示す、簡略フローチャートである。20

#### 【0153】

はじめに図6Aを参照して、第1のステップ602において、好ましくはCADデータが受信される。第1のステップ602で受信されたCADデータは好ましくは電気回路設計データを備え、かつ基板106、ウェハ206またはフラットパネルディスプレイ306といった基板上にパターニングされる対象物および境界ストリートの配置(an arrangement of objects and interfacing streets)を含む。第1のステップ602におけるCADデータの受信の後、第2のステップ604において、好ましくは走査幅が算出(計算)される。第2のステップ604において算出される走査幅はいくつかの要件を満たす必要があり、これには第1の要件606に示すように上記走査幅が上記基板の幅未満であること、第2の要件608に示すように各走査が一の対象物全体(a full object)をカバーすること、および第3の要件610に示すように各走査継ぎ目が対象物内ではなくストリートに重なるようになることが含まれる。また、第3の要件610は、図4A～図4Cを参照して詳述したように、ストリート内の走査継ぎ目の性質(nature)の算出を含み、かつ、第4の要件612に示すように、隣接する走査間であってストリート内の継ぎ目が、離れているか、接しているか、またはオーバーラップしているかの算出を含む。第2のステップ604における走査幅の算出の後、好ましくは第3のステップ614において書き込み走査が実行される。30

#### 【0154】

図6Aに示す方法は、上記基板のトポロジ中に存在することがある不正確さまたは歪み、および結果としてCADデータに求められる対応する修正を考慮していないことを理解されたい。この発明の好適な実施形態による、上記基板トポロジ中に生じうる歪みを考慮する直接書き込み装置の自動設定を含む例示的な方法が、図6Bに示されている。40

#### 【0155】

図6Bに示すように、第1のステップ620において上記基板の光学イメージが受信され、第2のステップ622においてCADデータが受信される。図6Bにおいてステップ620および622が並列に示されているが、ステップ620および622は同時に実行されてもよく、いずれか一方のステップが他方に先立つように順次実行されてもよいことを理解されたい。

#### 【0156】

上記光学イメージに基づいて上記基板中の歪みを考慮するために、第3のステップ6250

4において、上記C A Dデータに対する修正が算出される。この修正は、たとえば基板全体の位置における歪みに起因する上記C A Dデータの全体的な調整を含めることができ、および／または、たとえば上記基板上の個々の位置における反り(warping)に起因する上記C A Dデータの局所的な調整を含めることができることを理解されたい。この修正は、米国特許第7,508,515号および第8,769,471号に記載の方法、または当技術分野において知られている他の適当な方法にしたがって実行することができる。

#### 【0157】

次に第4のステップ626において、好ましくは走査幅が算出される。第4のステップ626において算出される走査幅はいくつかの要件を満たす必要があり、これには、第1の要件628に示すように上記走査幅が上記基板の幅未満であること、第2の要件630に示すように各走査が一の対象物全体をカバーすること、および第3の要件632に示すように各走査継ぎ目が対象物内ではなくストリートに重なるようになることが含まれる。

10

#### 【0158】

また、第3の要件632は、図4A～図4Cを参照して詳述したように、ストリート内の走査継ぎ目の性質の算出を含み、かつ、第4の要件634に示すように、隣接する走査間であってストリート内の継ぎ目が、離れているか、接しているか、またはオーバーラップしているかの算出を含む。第3の要件632を満たすために、第5のステップ636に示すように、ストリート・サイズおよび配向の調整が要求されることもある。調整されたストリート・サイズが許容できないほどに狭いことが分かった場合は、上記システムのオペレータに警告をもたらし、上記基板の正しい位置決めのために上記基板の手動による再配置が必要であることを示してもよい。

20

#### 【0159】

第4のステップ626における走査幅の算出の後、好ましくは第6のステップ638において書き込み走査が実行される。

#### 【0160】

次に図7Aおよび図7Bを参照して、図7Aおよび図7Bは、この発明の2つの別の実施形態の動作をそれぞれ示す簡略フローチャートである。

#### 【0161】

はじめに図7Aを参照して、第1のステップ702に示すように、好ましくは、読み／書きアセンブリがパターニング対象の基板に対して配置される。次に第2のステップ704に示すように、上記読み／書きアセンブリの光学イメージング構成要素を用いて上記基板が光学的にイメージングされる。この光学的イメージングは、好ましくは初期的な位置決めを目的とする上記基板上の基準の光学的イメージングを含み、かつ上記基板における局所的および／または全体的な歪みの存在を検出するための光学的イメージングを含む。第3のステップ706において、好ましくは読み／書きアセンブリによって上記基板上への直接書き込みのための直接書き込みデータが受信される。第4および第5のステップ708および710にそれぞれ示すように、上記基板の光学イメージが上記基板における歪みを示す場合、好ましくは直接書き込みデータが修正され、これらの歪みが考慮に入れられる。

30

#### 【0162】

次に、第6のステップ712において、好ましくは上記読み／書きアセンブリが自動的に設定され、複数の走査パスにおいて上記基板上に直接書き込みデータが直接書き込まれ、走査パスのそれぞれが、好ましくは図6Aおよび図6Bを参照して詳述した方法にしたがって、走査継ぎ目が上記対象物に重ならないようにして、上記基板上にパターニングされる少なくとも1つの対象物全体をカバーする。

40

#### 【0163】

このような自動設定に続いて、第7のステップ714において、好ましくは单一の走査パス(a single scan pass)が実行される。第8および第9のステップ716および718にそれぞれ示すように、上記基板の全幅をカバーするために追加の走査パスがさらに必要とされる場合には、好ましくは、上記基板に対して読み／書きアセンブリの場所が変えられ、必要に応じて追加の走査パスが実行される。第10および第11のステップ720

50

および 722 にそれぞれ示すように、直接書き込みが上記基板の全幅に実行されると、走査は完了したものとみなされる。

#### 【0164】

図 7 A を参照して概説した動作方法は、単一の読み / 書きアセンブリを含むシステムに対して適用可能なものであり、好ましくは、複数の順次走査パスを実行するために、読み / 書きアセンブリは、基板に対する場所が繰り返し変えられる。少なくとも部分的に同時に動作する複数の読み / 書きアセンブリを含むシステムに適用可能な、別の適切な動作方法については、図 7 B を参照して概説する。

#### 【0165】

次に図 7 B を参照して、第 1 のステップ 732 に示すように、好ましくは複数の読み / 書きアセンブリが、パターニング対象の基板に対して配置される。次に、第 2 のステップ 734 に示すように、上記基板が光学的にイメージングされる。この光学的イメージングには、初期的位置決めを目的とする上記基板上の基準の光学的イメージングを含み、かつ上記基板中の局所的および / または全体的な歪みの存在を検出するための光学的イメージングを含む。好ましくは、第 3 のステップ 736 において、読み / 書きアセンブリのそれぞれによって、上記基板上への直接書き込みのための直接書き込みデータが受信される。第 4 および第 5 のステップ 738 および 740 にそれぞれ示すように、好ましくは上記基板の光学イメージが上記基板中の歪みを示す場合は、上記直接書き込みデータが修正され、これらの歪みが考慮に入れられる。

#### 【0166】

次に第 6 のステップ 742 において、好ましくは上記複数の読み / 書きアセンブリの読み / 書きアセンブリのそれぞれが自動的に設定（構成）され、単一の走査パスにおいて上記基板上に直接書き込みデータが直接に書き込まれ、走査パスのそれぞれが、好ましくは図 6 A および図 6 B を参照して詳述した方法にしたがって、走査継ぎ目が上記対象物に重ならないようにして、上記基板上にパターニングされる少なくとも 1 つの対象物全体をカバーする。

#### 【0167】

このような自動設定に続いて、第 7 のステップ 744 において、好ましくは上記複数の読み / 書きアセンブリの読み / 書きアセンブリのそれぞれによって単一の走査パスが同時に実行され、好ましくは上記複数の読み / 書きアセンブリによって実行される走査パスの全体が上記基板の全幅をカバーし、第 8 のステップ 746 に示すように、基板の書き込みが完了する。

#### 【0168】

図 6 A および図 6 B に示す方法、ならびに図 7 A および図 7 B に示す動作形態は、かなり簡素化されたものであり、図示するステップの前、間、または後に、追加ステップを伴つてもよいことを理解されたい。さらに、図 6 A ~ 図 7 B に示すステップは、必ずしも図示しかつ説明した順番で実行されなくてもよく、順番を入れ替えてよい。

#### 【0169】

当業者にとって、この発明は、上記に特に図示しかつ説明したものによって限定されるものではないことを理解されたい。むしろ、この発明の範囲には、先行技術に含まれない、当業者が想到することができる、上述のさまざまな特徴のコンビネーションおよびサブコンビネーションの両方が含まれ、かつその変形が含まれる。

10

20

30

40

【図 1 A】

【図 1 B】

【図 2 A】

【図 2 B】

【図3A】

【 図 3 B 】

【 図 4 】

図 4 A

4 B

図 4 C

【 四 5 】

【図 6 A】

【図 6 B】

【図 7 A】

【図 7 B】

---

フロントページの続き

(72)発明者 ハイネマン・シュテファン

ドイツ国, デー- 0 7 7 4 5 イエナ, イン デン フィヒトレルスヴィーゼン 11

(72)発明者 エシュケ・ヴェルナー

ドイツ国, 0 7 7 4 3 イエナ, リカルダ- フッフ - ヴェーク 13 ア-

(72)発明者 グロス・アブラハム

イスラエル国 6 9 4 9 4 1 0 ラマト アヴィヴ リカナティ ストリート 10 アパートメント 40

審査官 今井 彰

(56)参考文献 特開2 0 1 2 - 1 8 1 2 8 5 (JP, A)

特開2 0 0 9 - 0 4 9 1 6 1 (JP, A)

特開2 0 1 3 - 1 9 0 5 0 5 (JP, A)

特開昭6 0 - 0 5 9 7 3 2 (JP, A)

特開2 0 1 2 - 0 9 3 7 0 1 (JP, A)

特開2 0 0 8 - 0 2 1 9 8 9 (JP, A)

米国特許出願公開第2 0 0 8 / 0 2 4 1 4 8 6 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 0 2 7、2 1 / 3 0

G 0 3 F 7 / 2 0 - 7 / 2 4、9 / 0 0 - 9 / 0 2

G 0 6 F 1 7 / 5 0