(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 600 31 881 T2 2007.07.05

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 234 335 B1

(21) Deutsches Aktenzeichen: 600 31 881.8

(86) PCT-Aktenzeichen: PCT/US00/17271

(96) Europäisches Aktenzeichen: 00 944 804.4

(87) PCT-Veröffentlichungs-Nr.: WO 2001/039273

(86) PCT-Anmeldetag: 23.06.2000

(87) Veröffentlichungstag

der PCT-Anmeldung: 31.05.2001

(97) Erstveröffentlichung durch das EPA: 28.08.2002

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 15.11.2006

(47) Veröffentlichungstag im Patentblatt: 05.07.2007

(51) Int Cl.<sup>8</sup>: H01L 29/10 (2006.01)

H01L 21/265 (2006.01)

(30) Unionspriorität:

168155 P 29.11.1999 US

497320 03.02.2000 US

(84) Benannte Vertragsstaaten:

DE, FR, GB, NL

(73) Patentinhaber:

Advanced Micro Devices, Inc., Sunnyvale, Calif.,

US

(72) Erfinder:

GHAEMMAGHAM, Ahmad, Gilroy, CA 95020, US;

KRIVOKAPIC, Zoran, Santa Clara, CA 95050, US;

SWANSON, Brian, San Jose, CA 95125, US

(74) Vertreter:

Grünecker, Kinkeldey, Stockmair &

Schwanhäusser, 80538 München

(54) Bezeichnung: VERFAHREN ZUR HERSTELLUNG EINER HALBLEITERBAUELEMENT MITTELS EINER HA-

LO-IMPLANTIERUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung betrifft Halbleiterbauelemente und betrifft insbesondere das Vorsehen einer Halo-Implantation beim Herstellen von Halbleiterbauelementen.

**Hintergrund der Erfindung**

**[0002]** Eine Halo-Implantation wird typischerweise eingesetzt, um Dotiermittel in ein Halbleiterbauelement zu implantieren. Es wird typischerweise Photolack für die I-Linienlithographie oder DUV (tiefes Ultraviolett) eingesetzt, um den Halo-Implantationsprozess zu maskieren. Typischerweise wird die gleiche Maske (leicht dotiertes Drain) (LDD) für die Halo-Implantation eingesetzt, da die Halo-Implantation nach der LDD-Implantation stattfindet. Auf Grund der Chemie des Photolacks tritt das Problem der Implantationsabschattung häufig ein, wenn konventionelle Prozesse (Maske und Photolack) angewendet werden, wodurch Ausbeute und Leistungsverhalten der Bauelemente negativ beeinflusst werden, wenn die Fertigungsprozesse sich in Richtung kleinerer Strukturgeometrien ändern.

**[0003]** Das erste Problem besteht darin, dass die Photolackdicke in dem Bereich der Implantation eine Dicke derart aufweist, dass eine Implantation, die bei einem 45 Grad Winkel ausgeführt wird, zu einem asymmetrischen und leckstrombehafteten Transistor führen kann. Ein zweites Problem besteht darin, dass die Dicke des Photolacks mit dem Grabenoxidationsgebiet des Bauelements in Beziehung steht. Wenn daher ein dicker Photolack (0,55 µm oder mehr) über dem Grabenoxidationsgebiet angeordnet wird, wird der Photolack häufig auf Bereiche absinken und diese abdecken, die zu implantieren sind auf Grund der weichen verformbaren Natur des Photolacks. Selbst wenn der Photolack nahe zu senkrecht bei kleineren Prozesstechnologien vorliegt, erreicht die Halo-Implantation nicht die gewünschten Bereiche. Des Weiteren wird in konventionellen Prozessen typischerweise nicht der Notwendigkeit Rechnung getragen, dass der Source/Drain-Bereich selektiv zu dotieren ist.

**[0004]** Es sind daher ein System und ein Verfahren erforderlich, um die oben genannten Probleme bei kleineren Prozessgeometrien zu überwinden. Die vorliegende Erfindung hat diese Problematik zum Gegenstand.

**Überblick über die Erfindung**

**[0005]** Es ist ein Verfahren zum Bereitstellen einer Halo-Implantation für ein Halbleiterbauelement offenbart. Das Verfahren umfasst das Bereitstellen einer dünnen Photolackschicht zwischen 0,1 bis 0,2 µm Di-

cke auf einem Halbleiterbauelement. Das Verfahren umfasst ferner das Bereitstellen der Halo-Implantation für das Halbleiterbauelement, wobei die dünne Photolackschicht als eine Maske für die Halo-Implantation verwendet wird. Folglich wird in dem erfindungsgemäßen Verfahren ein Photolack verwendet, der in der Lage ist, ein dünneres Profil zu bieten, d. h. ein DUV-Photolack. Dies ermöglicht es, die Dicke des Photolacks auf die vorgeschlagenen 100 nm (in der Fertigung) oder weniger zu reduzieren, wenn der Prozess dies ermöglicht. Mit dieser Photolackdicke können bei Berücksichtigung anderer Höhenvariablen das Source- und Drain-Gebiet entsprechend nach Bedarf geöffnet werden.

**[0006]** Bei einem 45 Grad Winkel kann die Implantation alle Transistoren in der Schaltung in dem gewünschten Bereich erreichen, wobei eine große Dosis lediglich am Transistorrand deponiert wird (bis zu  $\frac{1}{4}$  der Dosis), die dann am Grabenrand vorhanden ist. Dies minimiert auch die Gegendotierung des Source/Drain-Gebiets mit der inversen Dotierstoffsorte, wie dies für den Halo-Prozess erforderlich ist.

**[0007]** Bei kleineren Geometrien von 0,8 µm und darunter besitzt die Gatehöhe eine vorteilhafte Auswirkung und unterstützt das Verringern einer unerwünschten Gegendotierung des Source/Drain-Bereichs. Auf diese Weise kann die Gegendotierung auf einem absoluten Minimum gehalten werden. Der letztlich erreichte Vorteil besteht darin, dass mit dem dünneren Photolack die Möglichkeit verbessert wird, die Implantation bei kleineren Geometrien vorzusehen.

**[0008]** Folglich liefert der erfindungsgemäße Prozess eine Verbesserung im Fertigungsprozess sowie eine Verbesserung der Prozessmöglichkeiten, des Bauteilleistungsverhaltens und der Geschwindigkeit.

**[0009]** In den begleitenden Zeichnungen zeigen beispielhaft:

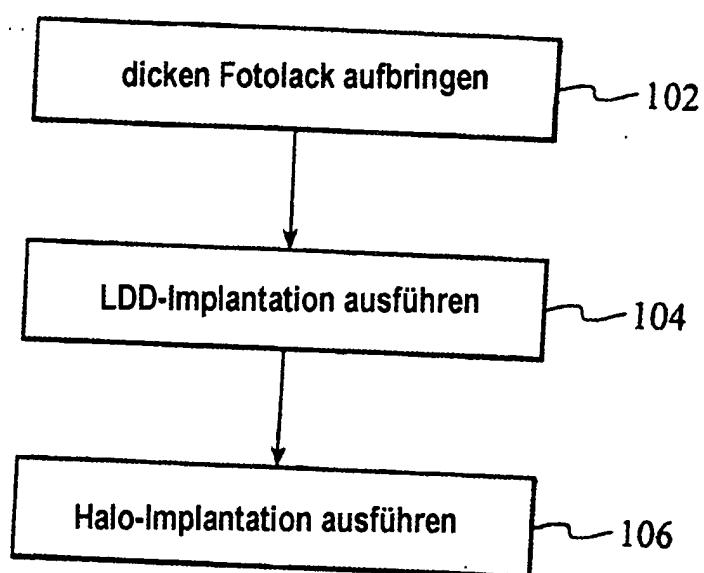

**[0010]** [Fig. 1](#) ein Flussdiagramm zur Darstellung eines konventionellen Prozesses zur Bereitstellung einer Halo-Implantation;

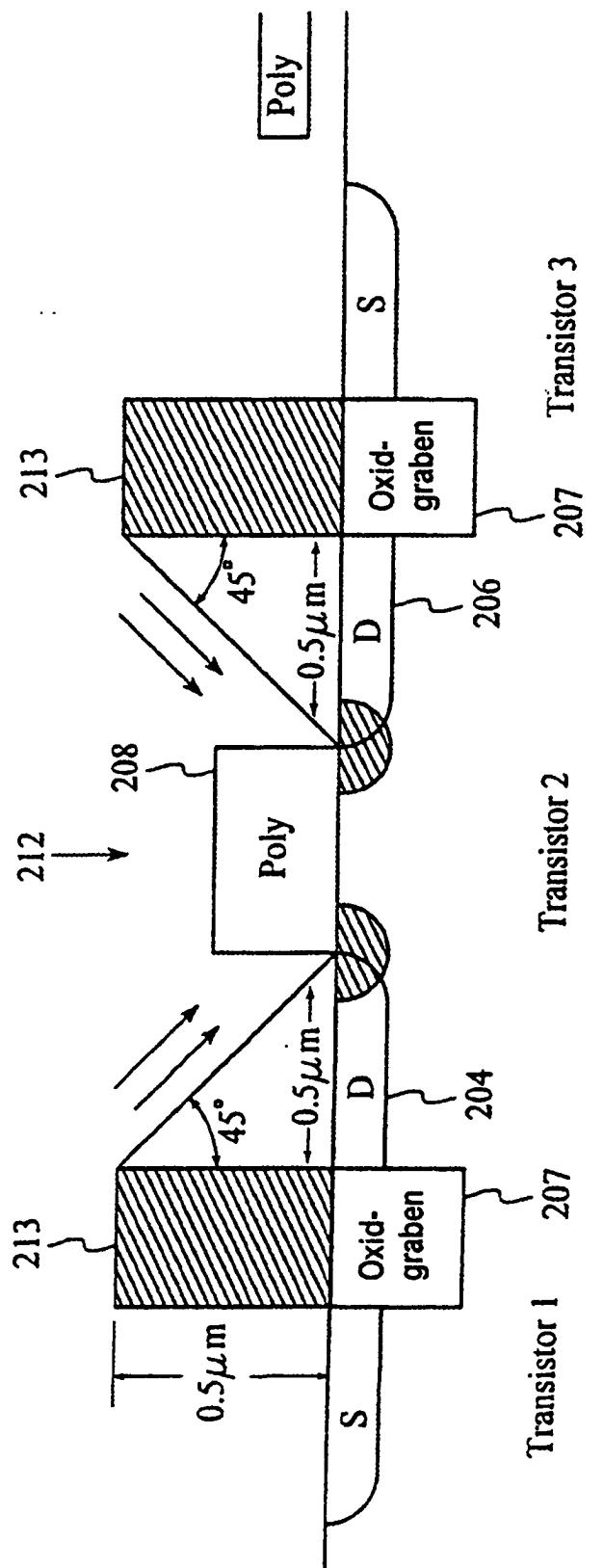

**[0011]** [Fig. 2](#) eine Ansicht, die das Halbleiterbauelement nach einer konventionellen Halo-Implantation zeigt;

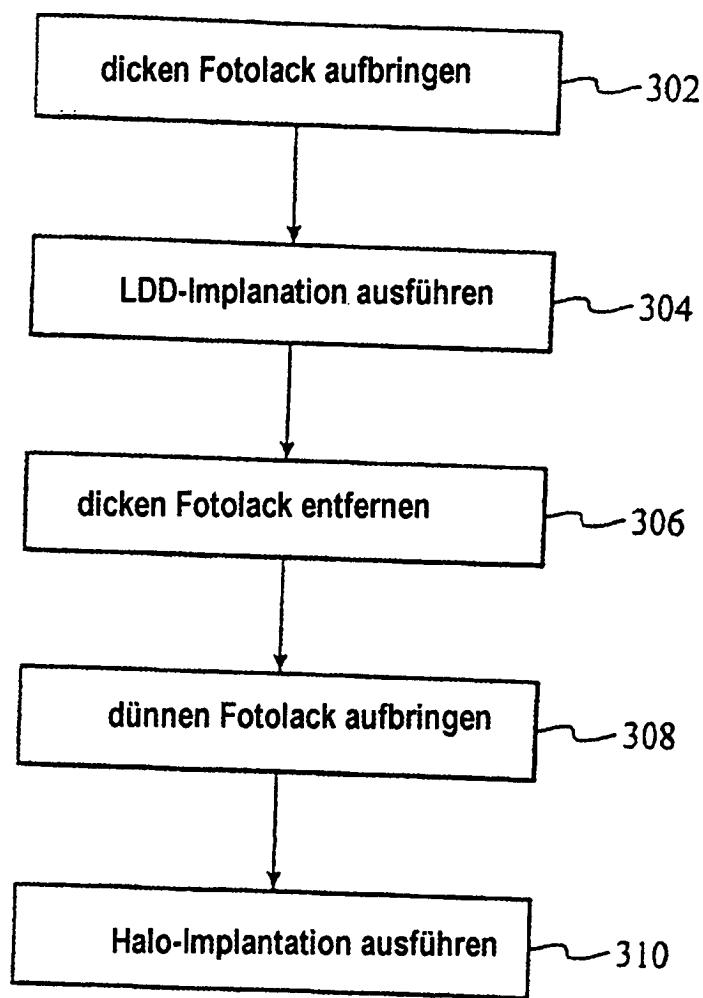

**[0012]** [Fig. 3](#) ein Flussdiagramm eines Verfahrens gemäß der vorliegenden Erfindung zur Bereitstellung einer Halo-Implantation;

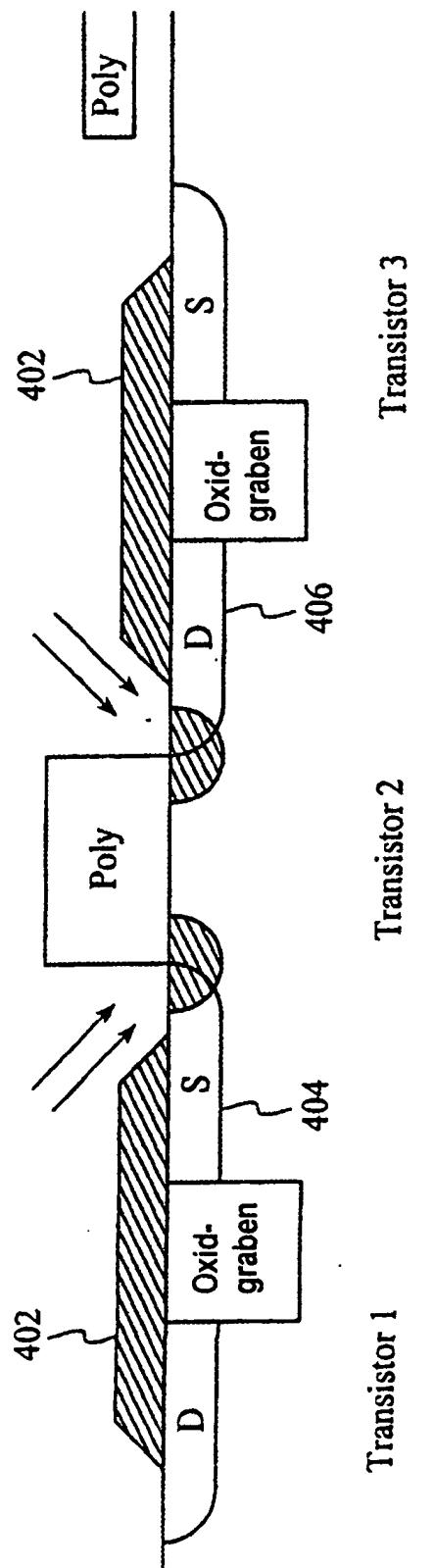

**[0013]** [Fig. 4](#) eine Ansicht, die das Halbleiterbauelement nach einer Halo-Implantation gemäß der vorliegenden Erfindung zeigt.

**[0014]** Fig. 1 ist ein Flussdiagramm, das einen konventionellen Prozessablauf zur Bereitstellung einer Halo-Implantation zeigt. Typischerweise wird in dem konventionellen Prozess zunächst eine dicke Photolackschicht im Schritt **102** vorgesehen. Anschließend wird eine LDD-Implantation im Schritt **104** durchgeführt. Der dicke Photolack oder die LDD-Maske in einem konventionellen Prozess ist typischerweise ein Photolack, der 0,55 µm hoch ist. Nach der LDD-Implantation wird eine Implantation im Schritt **106** durchgeführt, die als Halo-Implantation bezeichnet wird. Die Halo-Implantation wird typischerweise bei einem Winkel von 45 Grad durchgeführt, um unterhalb des Gatebereichs zu implantieren. Um bei einer Scheibe bei einer 45 Grad-Implantation entsprechend den gewünschten Bereich zu implantieren, wird eine LDD-Maske verwendet, die die Source- oder Drain-Gebiete nicht abdeckt. Beispiele konventioneller Halo-Implantationsprozesse sind in den Patentzusammenfassungen aus Japan, 1998, Nr. 03, 27. Februar 1998 und JP-09-289 315 und in EP-A-0 899 793 offenbart.

**[0015]** Fig. 2 ist eine Ansicht, die das Halbleiterbauelement **200** nach einem konventionellen Halo-Implantationsprozess zeigt. Folglich endet die Halo-Implantation **102** derart, dass ein Dotiermittel im gesamten Source-Gebiet **204** und Drain-Gebiet **206** vorhanden ist. Da lediglich der Bereich direkt unterhalb des Gate **208** für die Halo-Implantation von Interesse ist, sind somit Leckstrom und andere Probleme damit verknüpft. Somit ist der gesamte aktive Bereich **212** geöffnet, hauptsächlich deswegen, weil die Dicke der Photolackmaske **212** derart ist, dass bei einem 45 Grad Winkel die Ultravioletstrahlung nicht in präziser Weise unterhalb des Gatebereichs bereitgestellt werden kann.

**[0016]** Wie zu erkennen ist, ist es bei einer Photolackmaske **212** mit einer Dicke von 0,5 µm beim 45 Grad Winkel erforderlich ist, dass ein großer Teil der Ultravioletstrahlung nicht den interessierenden Bereich erreicht, da unter diesem Winkel dies bei einer dicken Photolackschicht nicht möglich ist. Wenn ferner ein dicker Photolack von (0,5 µm oder mehr) über der Grabenoxidation **207** angeordnet wird, sinkt der Photolack auf Grund der weichen nachgiebigen Natur des Photolacks häufig auf den Grabenoxidationsbereich und bedeckt Bereiche, die zu implantieren sind. Selbst wenn der Photolack bei kleineren Prozesstechnologien mit schärferen Profil vorgesehen ist, kann die Halo-Implantation die gewünschten Bereiche nicht erreichen.

**[0017]** In einem Verfahren gemäß der vorliegenden Erfindung wird der Implantationsbereich selektiv ausgewählt, anstatt eine ganzflächige Implantation auszuführen. Dies wird durch die Verwendung einer dünnenen Photolackmaske mit einer Dicke von 0,1 µm bis 0,2 µm anstelle von 0,5 µm bis 0,8 µm, wie sie im

konventionellen Prozess eingesetzt wird, erreicht. Zur genaueren Beschreibung der Merkmale der vorliegenden Erfindung wird auf die folgende Erläuterung in Verbindung mit den Figuren verwiesen.

**[0018]** Fig. 3 ist ein Flussdiagramm eines Systems gemäß der vorliegenden Erfindung. Wie typischerweise im konventionellen Prozess wird zunächst dem Schritt **302** ein dicker Photolack vorgesehen. Anschließend wird eine LDD-Implantation im Schritt **304** ausgeführt. Als nächstes wird der dicke Photolack im Schritt **306** entfernt. Danach wird ein dünner Photolack im Schritt **308** vorgesehen. Danach wird eine Halo-Implantation im Schritt **310** durchgeführt. Die Halo-Implantation wird typischerweise unter einem Winkel von 45 Grad durchgeführt, um unterhalb des Gatebereichs zu dotieren. Um in einer Scheibe bei einem 45 Grad-Halo-Implantationsprozess zuverlässig den beabsichtigten Bereich zu implantieren, wird eine LDD-Maske eingesetzt, die einen wesentlichen Anteil des Source-Gebiets oder Drain-Gebiets abdeckt.

**[0019]** Fig. 4 ist eine Ansicht, in der ein Halbleiterbauelement **400** nach einer Halo-Implantation gemäß der vorliegenden Erfindung gezeigt ist. Wie dargestellt ist, besitzt die Photolackmaske **402** eine geringere Höhe (0,1 µm bis 0,2 µm) im Vergleich zum konventionellen Prozess, wodurch es möglich ist, einen größeren Anteil der Source- und Drain-Gebiete **404** und **406** durch den Photolack **402** zu maskieren.

**[0020]** Daher wird in einem Verfahren gemäß der vorliegenden Erfindung ein Photolack eingesetzt, der ein dünneres Profil ermöglicht, d. h. ein DUV-Photolack. Dies macht es möglich, die Photolackdicke auf die vorgeschlagenen 100 nm (in der Produktion) oder weniger abzusenken, wenn es der Prozess zulässt. Mit dieser Photolackdicke unter Berücksichtigung anderer Höhenaspekte können die Source- und Draingebiete entsprechend dem Bedarf geöffnet werden. Bei einem 45 Grad Winkel kann die Implantation an allen Transistoren in der Schaltung in dem angestrebten Bereich durchgeführt werden, wobei lediglich eine große Menge der Dosis (bis zu  $\frac{1}{4}$  der Dosis) am Transistorrand auftritt, der an dem Grabenrand angeordnet ist. Dies minimiert auch die Gegendotierung des Source/Drain-Bereichs mit der inversen Dotierstoffsorte, wie sie für die Bildung des Halo-Gebiets erforderlich ist.

**[0021]** Bei kleineren Geometrien von 0,18 µm und weniger führt die Gatehöhe vorteilhafterweise zu einer Verringerung der unerwünschten Gegendotierung des Source-Gebiets und des Drain-Gebiets. Auf diese Weise kann die Gegendotierung bei einem absoluten Minimum gehalten werden. Der Vorteil liegt letztendlich darin, dass mit der dünnenen Photolackschicht die Möglichkeit geschaffen wird, die Implantation auf kleinere Geometrien anzuwenden. Daher be-

inhaltet der erfindungsgemäße Prozess eine Verbesserung der Fertigungsmöglichkeiten sowie der Prozessgrenzen, des Bauteilverhaltens und der Geschwindigkeit.

### Patentansprüche

1. Verfahren zur Bereitstellung einer Halo-Implantation in einem Halbleiterbauelement (**400**), **dadurch gekennzeichnet**, dass das Verfahren die Schritte umfasst:

- (a) Bereitstellen (**308**) einer dünnen Photolackschicht (**402**) mit einer Dicke von ungefähr 0,1 bis 0,2 µm auf dem Halbleiterbauelement; und

- (b) Bereitstellen (**310**) der Halo-Implantation in dem Halbleiterbauelement, wobei die dünne Photolackschicht als eine Maske für die Halo-Implantation verwendet wird.

2. Verfahren nach Anspruch 1, wobei die Photolackschicht (**402**) eine im tiefen Ultraviolettbereich (DUV) empfindliche Schicht umfasst.

3. Verfahren nach Anspruch 1 oder Anspruch 2, wobei die Photolackschicht einen wesentlichen Anteil des aktiven Bereichs des Halbleiterbauelements (**400**) abdeckt.

4. Verfahren nach Anspruch 3, wobei der aktive Bereich das Sourcegebiet (S) und das Draingebiet (D) des Halbleiterbauelements umfasst.

5. Verfahren nach einem der Ansprüche 1 bis 4, wobei die Halo-Implantation bei ungefähr einem Winkel von 45 Grad erfolgt.

6. Verfahren nach einem der Ansprüche 1 bis 5, das ferner den Schritt (**304**) aufweist: Bereitstellen einer leicht dotierenden Drainimplantation vor dem Schritt (b) zur Bereitstellung der Halo-Implantation.

Es folgen 4 Blatt Zeichnungen

FIG. 1

FIG. 2

FIG. 3

400

FIG. 4