(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-94407

(P2007-94407A)

(43) 公開日 平成19年4月12日(2007.4.12)

| (51) Int.C1.                 | F 1            | テーマコード (参考) |

|------------------------------|----------------|-------------|

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36      | 2 H 092     |

| <b>G02F 1/133 (2006.01)</b>  | G02F 1/133 570 | 2 H 093     |

| <b>G02F 1/1343 (2006.01)</b> | G02F 1/133 575 | 5 C 006     |

| <b>G09G 3/20 (2006.01)</b>   | G02F 1/1343    | 5 C 080     |

|                              | GO9G 3/20 631B |             |

審査請求 未請求 請求項の数 20 O L (全 28 頁) 最終頁に続く

|              |                              |          |                                                                                  |

|--------------|------------------------------|----------|----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2006-259928 (P2006-259928) | (71) 出願人 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区梅灘洞416 |

| (22) 出願日     | 平成18年9月26日 (2006.9.26)       | (74) 代理人 | 100094145<br>弁理士 小野 由己男                                                          |

| (31) 優先権主張番号 | 10-2005-0090493              | (74) 代理人 | 100106367<br>弁理士 稲積 朋子                                                           |

| (32) 優先日     | 平成17年9月28日 (2005.9.28)       | (72) 発明者 | 倉 學 ▲スン▼<br>大韓民国京畿道龍仁市豊徳川洞東部アパート103棟203号                                         |

| (33) 優先権主張国  | 韓国 (KR)                      |          |                                                                                  |

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその駆動方法

## (57) 【要約】

【課題】液晶の寿命や画面の視野角を損なうことなく液晶の応答を速くすることにより、動画表示での画質を向上できる液晶表示装置を提供する。

【解決手段】本発明による液晶表示装置では、映像信号補正部が、直前のフレームの映像信号と現在のフレームの映像信号とに基づいて第1補正映像信号を生成し、第1補正映像信号と次のフレームの映像信号とに基づいて第2補正映像信号を生成する。データ駆動部は、映像信号補正部から出力される第2補正映像信号をデータ電圧に変えて画素に供給する。特に、画素電圧の目標値の下限が画素電圧の実際の下限より高い。

【選択図】図12A

**【特許請求の範囲】****【請求項 1】**

複数の副領域を含む複数の画素；

直前のフレームの映像信号と現在のフレームの映像信号とに基づいて第1補正映像信号を生成し、前記第1補正映像信号と次のフレームの映像信号とに基づいて第2補正映像信号を生成する映像信号補正部；及び、

前記映像信号補正部から出力された第2補正映像信号をデータ電圧に変えて画素に供給するデータ駆動部；

を有する液晶表示装置であり、

データ電圧と共に電圧との間の差である画素電圧の目標値の下限が画素電圧の実際の下限より高い、液晶表示装置。 10

**【請求項 2】**

画素電圧の目標値の下限がブラック階調に対応し、その範囲が1.5V～2.0Vである、請求項1に記載の液晶表示装置。

**【請求項 3】**

直前のフレームの映像信号の示す階調値が第1設定値以上であり、かつ現在のフレームの映像信号の示す階調値が、第1設定値より低い第2設定値以下であれば、現在のフレームでは画素電圧の実際の下限を画素に対して印加する、請求項1に記載の液晶表示装置。

**【請求項 4】**

画素電圧の実際の下限が0.5V～1.2Vである、請求項3に記載の液晶表示装置。 20

**【請求項 5】**

前記第1補正映像信号と直前のフレームの映像信号との間での階調値の差が、現在のフレームの映像信号と直前のフレームの映像信号との間での階調値の差以上である、請求項1に記載の液晶表示装置。

**【請求項 6】**

前記第1補正映像信号の示す階調値が第3設定値以下であり、かつ次のフレームの映像信号の示す階調値が、第3設定値より高い第4設定値以上であれば、現在のフレームでは予備傾斜電圧を画素に対して印加する、請求項5に記載の液晶表示装置。

**【請求項 7】**

前記予備傾斜電圧が2.5V～3.0Vである、請求項6に記載の液晶表示装置。 30

**【請求項 8】**

ホワイト階調に対応する画素電圧の目標値の上限が画素電圧の実際の上限より低い、請求項1に記載の液晶表示装置。

**【請求項 9】**

ホワイト階調に対応する画素電圧の目標値の上限が画素電圧の実際の上限と実質的に等しい、請求項1に記載の液晶表示装置。

**【請求項 10】**

画素の副領域が、互いに隣接する第1副領域と第2副領域との対を複数含む、請求項1に記載の液晶表示装置。

**【請求項 11】**

前記第1副領域の幅が30μm以上であり、前記第2副領域の幅が20μm～30μmである、請求項10に記載の液晶表示装置。 40

**【請求項 12】**

画素の副領域を区画して液晶分子の傾斜方向を決める複数の傾斜方向決定部材、をさらに有する、請求項1に記載の液晶表示装置。

**【請求項 13】**

前記傾斜方向決定部材が、切開部、突起部、及び陥没部のうち、少なくとも一つを含む、請求項12に記載の液晶表示装置。

**【請求項 14】**

一対の平行な斜辺、を各々含む第1電極部と第2電極部、を有する画素電極；

50

前記画素電極と対向する共通電極；

前記画素電極と前記共通電極との間に入っている液晶層；

前記第1電極部と前記第2電極部との各々に備えられ、前記第1電極部と前記第2電極部との各斜辺と実質的に平行な斜線部を含む第1切開部、を有し、前記液晶層の液晶分子の傾斜方向を決める第1傾斜方向決定部材；及び、

前記共通電極に備えられ、前記第1電極部と前記第2電極部との各斜辺と実質的に平行な斜線部を含む複数の第2切開部、を有し、前記第1電極部と前記第2電極部との各斜辺の間、前記第1電極部の斜辺と前記第1傾斜方向決定部材との間、または前記第2電極部の斜辺と前記第1傾斜方向決定部材との間に配置され、前記液晶層の液晶分子の傾斜方向を決める複数の第2傾斜方向決定部材；

10

を備えた液晶表示装置であり、

前記画素電極と前記共通電極との間に印加されるブラック電圧が1.5V～2.0Vである液晶表示装置。

【請求項15】

前記第1切開部の斜線部と前記第2切開部の斜線部との間の距離が20μm～30μmであり、前記第2電極部の斜辺と前記第2切開部の斜線部との間の距離が30μm以上である、請求項14に記載の液晶表示装置。

【請求項16】

複数の画素を含む液晶表示装置の駆動方法であって、

20

直前のフレームの映像信号、現在のフレームの映像信号、及び次のフレームの映像信号を読み込む段階；

前記直前のフレームの映像信号と前記現在のフレームの映像信号とに基づいて第1補正映像信号を生成する段階；

前記第1補正映像信号と前記次のフレームの映像信号とに基づいて第2補正映像信号を生成する段階；並びに、

前記第2補正映像信号に対応する画素電圧を画素に対して印加する段階；

を含み、

ブラック階調に対応する画素電圧の目標値の下限を画素電圧の実際の下限より高く設定する、液晶表示装置の駆動方法。

30

【請求項17】

直前のフレームの映像信号の示す階調値が第1設定値以上であり、かつ現在のフレームの映像信号の示す階調値が、第1設定値より低い第2設定値以下であれば、画素電圧の実際の下限を画素に対して印加する、請求項16に記載の液晶表示装置の駆動方法。

【請求項18】

前記第1補正映像信号を生成する段階では、前記第1補正映像信号と前記直前のフレームの映像信号との間での階調値の差が、前記現在のフレームの映像信号と前記直前のフレームの映像信号との間での階調値の差以上になるように前記第1補正映像信号が生成され、

40

前記第1補正映像信号の示す階調値が第3設定値以下であり、かつ前記次のフレームの映像信号の示す階調値が、第3設定値より高い第4設定値以上であれば、予備傾斜電圧が画素に対して印加される、

請求項16に記載の液晶表示装置の駆動方法。

【請求項19】

ホワイト階調に対応する画素電圧の目標値の上限を画素電圧の実際の上限より低く設定する、請求項16に記載の液晶表示装置の駆動方法。

【請求項20】

ホワイト階調に対応する画素電圧の目標値の上限を画素電圧の実際の上限と実質的に等しく設定する、請求項16に記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

50

**【0001】**

本発明は液晶表示装置に関し、特にその駆動方法に関する。

**【背景技術】****【0002】**

一般的な液晶表示装置は、画素電極と共通電極とが備えられている二枚の表示パネル、及びそれらの間に挟まれている、誘電率異方性を示す液晶層を含む。画素電極は二枚の表示パネルの一方にマトリックス状に配列され、それぞれが薄膜トランジスタ（TFT）などのスイッチング素子に連結されている。各スイッチング素子のオンオフにより、画素電極のマトリックスに対して一行ずつ順番にデータ電圧が印加される。共通電極は二枚の表示パネルの他方の全面を覆っている。共通電極に対しては共通電圧が印加される。画素電極、共通電極、及びそれらの間の液晶層は、電気回路としてはキャパシタと等価である（以下、液晶キャパシタという）。液晶キャパシタと、それに連結されたスイッチング素子との対が、一つの画素を構成する基本単位である。各画素では、画素電極に対して印加されるデータ電圧の高さが調節されることにより液晶キャパシタの両端電圧（画素電圧）が調節され、液晶層に生成される電場の強さが調節される。その結果、液晶層での光透過率が画素ごとに調節されるので、液晶表示装置の画面には所望の画像が再現される。

10

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

一般的な液晶表示装置は、映像信号のフレームごとに、画素マトリックスの行ごとに、または画素ごとに、共通電圧に対するデータ電圧の極性を反転させる。それにより、各画素の液晶層では、一方向の電場が持続する時間が制限されるので、劣化が防止される。しかし、その反面、連続する二つのフレーム間では液晶分子の傾斜角（チルト角）の変化が一般に大きい。例えばノーマリブラックの液晶表示装置では、暗い映像のフレームが連続する状態では液晶分子の傾斜角の変化が小さいが、明るい映像のフレームが連続する状態では液晶分子の傾斜角の変化が大きい。

20

**【0004】**

近年、液晶表示装置は、テレビなどの画面にも広く使用されている。それらの用途では動画表示での画質が重要である。しかし、特に暗い映像と明るい映像との間でのフレームの切換時では液晶分子の傾斜角の変化が大きいので、液晶層に生成される電場の変化に対する液晶の応答が一般に遅い。その結果、動画表示での画質を更に向上させることが難しい。

30

**【0005】**

液晶表示装置の中には、各画素が傾斜方向決定部材（例えば、画素電極や共通電極の切開部）により複数の副領域に分けられているものがある。傾斜方向決定部材が副領域の液晶層ごとに液晶分子を異なる方向に傾斜させることにより、画面の視野角が大きく維持される。ここで、傾斜方向決定部材によって仕切られた、各副領域に含まれる画素電極や共通電極の部分が広いほど、各画素の開口率が一般に高く、かつ大画面化に有利である。しかし、その反面、各副領域に含まれる液晶分子全体を特定の方向に予め傾斜させるのに必要な時間の更なる短縮が困難である。その上、その時間の短縮を目的として、各副領域に対して予め印加される予備傾斜電圧（プレチルト電圧）を過剰に上昇させれば、各副領域に対して続いて印加されるデータ電圧とその副領域の光透過率の目標値との間の関係（特にコントラスト比）が過剰に歪むので、動画表示での画質を却って損ないかねない。

40

**【0006】**

本発明の技術的課題は、液晶の寿命や画面の視野角を損なうことなく液晶の応答を速くすることにより、特に動画表示での画質を更に向上できる液晶表示装置、及びその駆動方法を提供することにある。

**【課題を解決するための手段】****【0007】**

本発明の一つの観点による液晶表示装置は、

50

複数の副領域を含む複数の画素、

直前のフレームの映像信号と現在のフレームの映像信号とに基づいて第1補正映像信号を生成し、その第1補正映像信号と次のフレームの映像信号とに基づいて第2補正映像信号を生成する映像信号補正部、

映像信号補正部から出力された第2補正映像信号をデータ電圧に変えて画素に供給するデータ駆動部、を有する。この液晶表示装置では特に、データ電圧と共通電圧との間の差である画素電圧の目標値の下限が、画素電圧の実際の下限より高い。好ましくは、画素電圧の目標値の下限がブラック階調に対応し、その範囲が1.5V～2.0Vである。好ましくは、直前のフレームの映像信号の示す階調値が第1設定値以上であり、かつ現在のフレームの映像信号の示す階調値が第2設定値以下であれば、画素電圧の実際の下限を画素に対して印加する。ここで、第2設定値は第1設定値より低い。更に好ましくは、画素電圧の実際の下限が0.5V～1.2Vである。第1補正映像信号と直前のフレームの映像信号との間での階調値の差は好ましくは、現在のフレームの映像信号と直前のフレームの映像信号との間での階調値の差以上である。こうして、現在のフレームの映像が直前のフレームの映像より急に暗くなる場合、現在のフレームの映像を表示するときの画素電圧の実際の下限が目標値の下限（好ましくはブラック階調に対応するブラック電圧）より低く設定されるので、フレーム間での画素電圧の変化にアンダーシュートが生じる。

10

#### 【0008】

本発明による上記の液晶表示装置では、好ましくは、第1補正映像信号の示す階調値が第3設定値以下であり、かつ次のフレームの映像信号の示す階調値が第4設定値以上であれば、予備傾斜電圧が画素に対して印加される。ここで、第4設定値は第3設定値より高い。更に好ましくは、予備傾斜電圧が2.5V～3.0Vである。その他に、ホワイト階調に対応する画素電圧の目標値の上限が画素電圧の実際の上限より低く、若しくは、実質的に同一であってもよい。こうして、次のフレームの映像が現在のフレームの映像より急に明るくなる場合、現在のフレームでは予備傾斜電圧が一旦印加される。更に、次のフレームの映像を表示するときの画素電圧の実際の上限が目標値の上限（ホワイト階調に対応するホワイト電圧）より高く設定されるので、フレーム間での画素電圧の変化にはオーバーシュートが生じる。

20

#### 【0009】

各画素の副領域は好ましくは、互いに隣接する第1副領域と第2副領域との対を複数含む。更に好ましくは、第1副領域の幅が30μm以上であり、第2副領域の幅が20μm～30μmである。その液晶表示装置が好ましくは、画素の副領域を区画して液晶分子の傾斜方向を決める複数の傾斜方向決定部材、をさらに含んでも良い。更に好ましくは、傾斜方向決定部材が、切開部、突起、及び陥没部のうち、少なくとも一つを含む。

30

#### 【0010】

本発明の他の観点による液晶表示装置は、

一対の平行な斜辺、を各々含む第1電極部と第2電極部、を含む画素電極、

その画素電極と対向する共通電極、

画素電極と共通電極との間に入っている液晶層、

各画素電極の第1電極部と第2電極部との各々に備えられ、第1電極部と第2電極部との各斜辺と実質的に平行な斜線部を含む第1切開部、を有し、液晶層の液晶分子の傾斜方向を決める第1傾斜方向決定部材、及び、

40

共通電極に備えられ、第1電極部と第2電極部との各斜辺と実質的に平行な斜線部を含む複数の第2切開部、を有し、第1電極部と第2電極部との各斜辺の間、第1電極部の斜辺と第1傾斜方向決定部材との間、または第2電極部の斜辺と第1傾斜方向決定部材との間に配置され、液晶層の液晶分子の傾斜方向を決める複数の第2傾斜方向決定部材、を備える。その液晶表示装置では特に、画素電極と共通電極との間に印加されるブラック電圧が1.5V～2.0Vである。好ましくは、第1切開部の斜線部と第2切開部の斜線部との間の距離が20μm～30μmであり、第2電極部の斜辺と第2切開部の斜線部との間の距離が30μm以上である。

50

## 【0011】

本発明による液晶表示装置の駆動方法は、複数の画素を含む液晶表示装置を対象とする。その駆動方法は、好ましくは、

直前のフレームの映像信号、現在のフレームの映像信号、及び次のフレームの映像信号を読み込む段階、

読み込まれた直前のフレームの映像信号と現在のフレームの映像信号とに基づいて第1補正映像信号を生成する段階、

第1補正映像信号と次のフレームの映像信号とに基づいて第2補正映像信号を生成する段階、並びに、

第2補正映像信号に対応する画素電圧を画素に対して印加する段階、を含む。その駆動方法は好ましくは、ブラック階調に対応する画素電圧の目標値の下限を画素電圧の実際の下限より高く設定する。 10

## 【発明の効果】

## 【0012】

本発明による液晶表示装置では、上記の通り、連続する二つのフレーム間で階調値が大きく上昇する場合、前のフレームではブラック電圧を一旦予備傾斜電圧まで高める。それにより、液晶分子を予め傾斜させることで、次のフレームでの液晶の応答速度を高める。更に、次のフレームでは画素電圧の実際の上限を目標値の上限より高くし、フレーム間での画素電圧の変化にオーバーシュートを形成しても良い。それにより、前のフレームでの予備傾斜電圧の印加に伴うブラック電圧の上昇が、次のフレームでの画素電圧のオーバーシュートで相殺されるので、各副領域に対して印加される画素電圧とその副領域の光透過率の目標値との間の関係（特にコントラスト比）が良好に保たれる。逆に、連続する二つのフレーム間で階調値が大きく下降する場合、後のフレームでは画素電圧の実際の下限を目標値の下限より低くし、フレーム間での画素電圧の変化にアンダーシュートを形成する。それにより、後のフレームでは画素電圧の変化が十分に大きいので、液晶の応答速度を更に高めることができる。こうして、画質を高く維持したままで液晶の応答速度を更に高め得るので、本発明による液晶表示装置は、（特に動画表示の）更なる高画質化、及び、各副領域に含まれる電極部の拡大による画素の開口率の向上や更なる大画面化に有利である。 20

## 【発明を実施するための最良の形態】

## 【0013】

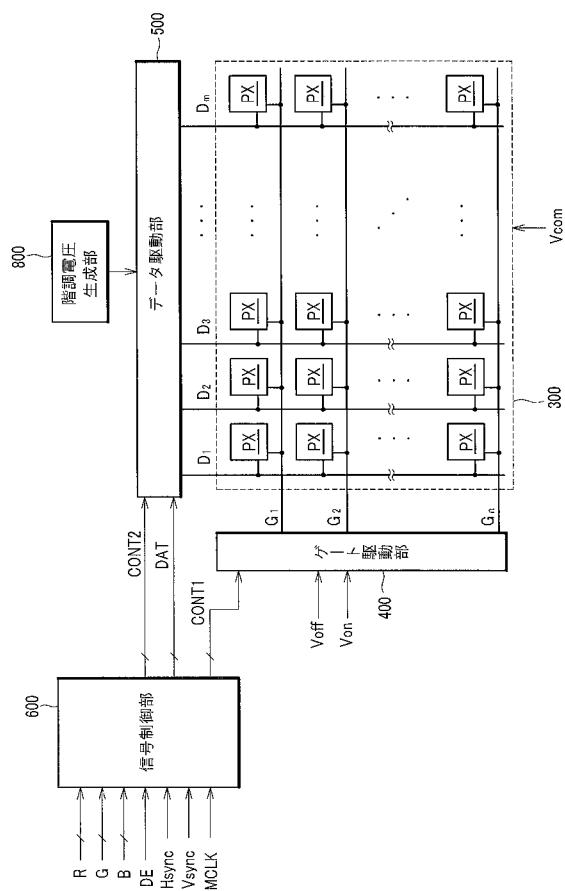

まず、図1及び図2を参照して、本発明の一つの実施例による液晶表示装置について詳細に説明する。

図1は本発明の一つの実施例による液晶表示装置のブロック図であり、図2は図1に示されている液晶表示装置に含まれる一つの画素の等価回路図である。

図1に示したように、本発明の一つの実施例による液晶表示装置は、液晶表示パネルアセンブリ300、それに連結されたゲート駆動部400とデータ駆動部500、データ駆動部500に連結された階調電圧生成部800、及びそれらを制御する信号制御部600を含む。

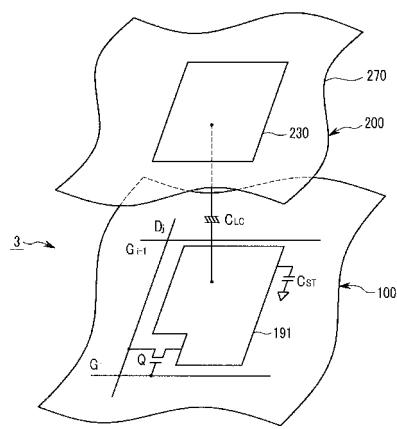

## 【0014】

液晶表示パネルアセンブリ300は、複数の信号線 $G_1 \sim G_n$ 、 $D_1 \sim D_m$ と、それらに連結され、かつマトリックス状に配列された複数の画素PXを含む。一方、図2に示したように、液晶表示パネルアセンブリ300は、互いに対向する薄膜トランジスタ表示パネル100と共に通電極表示パネル200、及びそれらの間に挟まれている液晶層3を含む。 40

信号線 $G_1 \sim G_n$ 、 $D_1 \sim D_m$ は、ゲート信号（“走査信号”とも言う）を伝達する複数のゲート線 $G_1 \sim G_n$ と、データ電圧を伝達する複数のデータ線 $D_1 \sim D_m$ とを含む。ゲート線 $G_1 \sim G_n$ は互いにほとんど平行に、ほぼ行方向に延びている。データ線 $D_1 \sim D_m$ は互いにほとんど平行に、ほぼ列方向に延びている。

## 【0015】

例えば、i番目（ $i = 1, 2, \dots, n$ ）のゲート線 $G_i$ とj番目（ $j = 1, 2, \dots, m$ ）のデータ線 $D_j$ とに連結された画素PXは、各信号線 $G_i$ 、 $D_j$ に連結されたスイッチング素子Q、及び、そ 50

れに連結された液晶キャパシタC1cとストレージキャパシタCstとを含む。ストレージキャパシタCstは必要に応じて省略できる。スイッチング素子Qは好ましくは、薄膜トランジスタ表示パネル100に備えられている薄膜トランジスタなどの三端子素子であり、制御端子はゲート線G<sub>i</sub>と連結され、入力端子はデータ線D<sub>j</sub>と連結され、出力端子は液晶キャパシタC1c及びストレージキャパシタCstと連結されている。液晶キャパシタC1cは、薄膜トランジスタ表示パネル100の画素電極191と共通電極表示パネル200の共通電極270とを二つの端子として含み、二つの電極191、270の間の液晶層3を誘電体として含む。画素電極191はスイッチング素子Qと連結され、共通電極270は共通電極表示パネル200の全面に形成されていて共通電圧Vcomの印加を受ける。図2とは異なり、共通電極270が薄膜トランジスタ表示パネル100に備えられる場合もあり、この時には二つの電極191、270の少なくとも一方が線状または棒状であってもよい。液晶キャパシタC1cの補助的な役割を果たすストレージキャパシタCstは、薄膜トランジスタ表示パネル100に備えられた別の信号線（維持電極線。図1、2には示されていない）と画素電極191とが絶縁体を間に置いて重なったものである。維持電極線に対しては共通電圧Vcomなどの決められた電圧が印加される。その他に、ストレージキャパシタCstは、画素電極191が絶縁体を間においてゲート線と重なったものであっても良い。

#### 【0016】

色表示を実現するためには、各画素PXが基本色のうちの一つを固有に表示し（空間分割方式）、又は、一つの画素PXが所定時間ごとに基本色を交互に表示する（時間分割方式）。それにより、基本色の空間的分布の割合、又は表示時間の割合に応じて所望の色相が画面に再現される。基本色の例としては、赤色、緑色、青色の三原色がある。図2は空間分割方式の一例であり、各画素PXが、画素電極191に対向する共通電極表示パネル200の領域に、基本色の一つを示す色フィルター230を備えている。図2とは異なり、色フィルター230は薄膜トランジスタ表示パネル100の画素電極191の上または下に形成されてもよい。

液晶表示パネルアセンブリ300の外側には、光を偏光させる少なくとも一つの偏光子（図示せず）が接着されている。

#### 【0017】

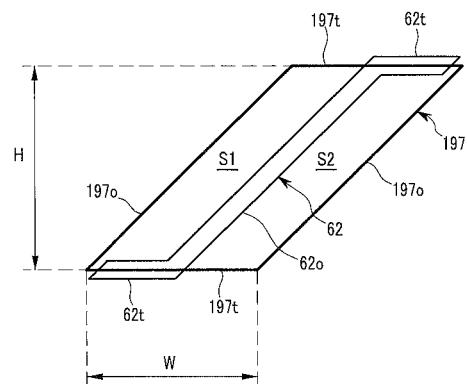

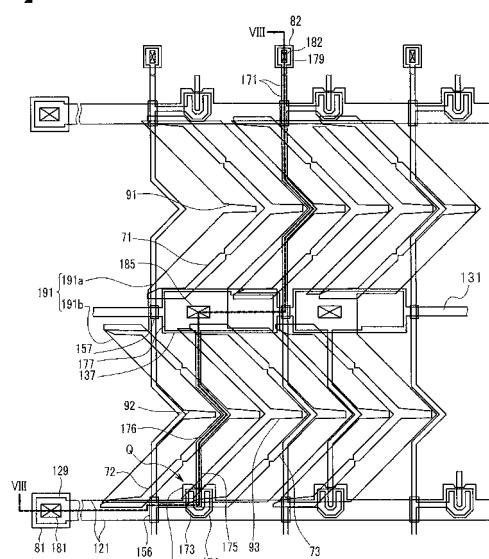

図3A～図4を参照し、上記の液晶表示パネルアセンブリの画素電極及び共通電極の詳細構造について説明する。

図3A～図3Cは本発明の一つの実施例による液晶表示装置の各画素電極の基本となる電極片の平面図である。図4は本発明の一つの実施例による液晶表示パネルアセンブリの画素電極と共通電極との配置図である。

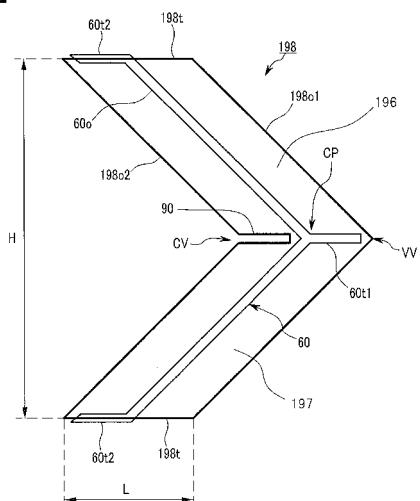

各画素電極191は少なくとも、図3Aに示した平行四辺形の電極片196と、図3Bに示した平行四辺形の電極片197とを一つずつ含む。図3A及び図3Bに示した電極片196、197を上下に連結すれば、図3Cに示した基本電極198が形成される。各画素電極191はこのような基本電極198を根幹とする。

#### 【0018】

図3A及び図3Bに示したように、電極片196、197の各々は一対の斜辺196o、197o及び一対の横辺196t、197tを有し、ほぼ平行四辺形である。各斜辺196o、197oは横辺196t、197tに対して斜角を成す。その斜角の大きさは好ましくは、ほぼ45°～135°である。以下では、底辺196t、197tに対し、図3Aのように左側に傾いた場合を“左傾斜”と言い、図3Bのように右側に傾いた場合を“右傾斜”と言う。

各電極片196、197の幅（すなわち、各横辺196t、197tの長さ）Wと高さ（すなわち、二つの横辺196t、197tの間の距離）Hとは液晶表示パネルアセンブリ300の大きさに応じて自由に決められる。また、各電極片196、197の横辺196t、197tは、他の部分との関係を考慮して様々に変形可能である（例えば、折れ曲がっても良く、突出していても良い）。以下では、それらの変形も全て含んだ意味で、各電極片196、197の周の形状を平行四辺形と称する。

#### 【0019】

共通電極270には電極片196、197と対向する切開部61、62が形成されており、電極片196

10

20

30

40

50

、197は切開部61、62を境に二つの副領域S1、S2に区画される。切開部61、62は、電極片196、197の斜辺196o、197oに対して平行な斜線部61o、62o、及び、斜線部61o、62oと鈍角を成し、かつ電極片196、197の横辺196t、197tと重なる横部61t、62tを含む。各副領域S1、S2は、切開部61、62の斜線部61o、62o及び電極片196、197の斜辺196t、197tに沿った二つの主辺を有する。二つの主辺間の距離、つまり、副領域の幅は好ましくは約25μm以上である。二つの副領域S1、S2の幅は互いに異なってもよい。

#### 【0020】

図3Cに示した基本電極198は、左傾斜電極片196と右傾斜電極片197との結合から成り、全体が山形または不等号(>)の形状を成す。左傾斜電極片196と右傾斜電極片197とが成す角度は好ましくはほぼ直角である。二つの電極片196、197間では、山形の頂上付近の部分が互いに連結され、その反対側の部分が連結されずに残されて切開部90を構成する。尚、切開部90は省略されてもよい。二つの電極片196、197の外側の横辺196t、197tは基本電極198の横辺198tを成し、二つの電極片196、197の同じ側の斜辺196o、197oは互いに連結されて基本電極198の屈曲辺198o1、198o2を成す。屈曲辺の一方(以下、凸辺と言う)198o1は横辺198tと鈍角(好ましくは約135°)を成し、屈曲辺の他方(以下、凹辺と言う)198o2は横辺198tと鋭角(好ましくは約45°)を成す。二つの電極片196、197の斜辺196o、197oがほぼ直交するので、屈曲辺198o1、198o2はほぼ直角に折れ曲がっている。切開部90は、凹辺198o2上の頂点(以下、凹頂点と言う)CVから凸辺198o1上の頂点(以下、凸頂点と言う)VVに向かって基本電極198のほぼ中心まで延びている。

#### 【0021】

共通電極270の切開部61、62は互いに連結されて一つの切開部60を成す。この時、二つの切開部61、62の間では各横部61t、62tが重なって一つの横部60t1を構成する。切開部60は、屈曲点CPを含む屈曲部60o、屈曲部60oの屈曲点CPに連結されている中央横部60t1、及び、屈曲部60oの各端に一つずつ連結されている一対の横部60t2を含む。屈曲部60oは、直角を成す一対の斜線部から成り、基本電極198の屈曲辺198o1、198o2に対してほぼ平行に延び、基本電極198を左半部と右半部とに二等分する。中央横部60t1は屈曲部60oと鈍角(好ましくは約135°)を成し、基本電極198の凸頂点VVに向かって延びている。横部60t2は基本電極198の横辺198tと重なり、屈曲部60oと鈍角(好ましくは約135°)を成す。基本電極198と共通電極の切開部60とは、基本電極198の凸頂点VVと凹頂点CVとの間を連結する仮想的な直線(以下、“横中心線”と言う)に対してほぼ反転対称である。

#### 【0022】

次に、図4に示した画素電極の特徴について具体的に説明する。

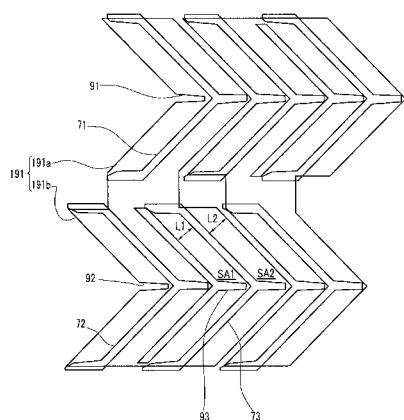

図4に示した各画素電極191は、第1電極部191aと第2電極部191bとの対、及び二つの電極部191a、191bの間を連結する連結部を含む。第1電極部191aと第2電極部191bとは列方向に連結されていて、切開部91、92、93を有する。第2電極部191bの電極片の数は第1電極部191aの電極片の数より多い。共通電極270は各電極部191a、191bと対向する切開部71、72、73を有する。

第1電極部191aは左傾斜電極片196と右傾斜電極片197とから成り、図3Cに示した基本電極198と実質的に同一な構造を有する。第2電極部191bは二つの左傾斜電極片196と二つの右傾斜電極片197との組み合わせから成り、一対の基本電極198が行方向に連結されている構造と実質的に同一な構造を有する。

#### 【0023】

図4に示した電極部191a、191b及び切開部91~93の配置は、図3Cに示した基本電極198及び切開部60、90の配置が行方向及び列方向に繰り返されて作られる。第2電極部191bでは、二つの基本電極198が一方の凹辺198o2を他方の凸辺198o1に隣接させて配置され、各基本電極198の上端間と下端間とが連結されている。それら二つの基本電極198の間の間隙と、この間隙に連結される切開部90とが一つの切開部93を構成する。この切開部93は、第2電極部191bを左半部と右半部とに二等分する屈曲部、及びそれに連結された横部を含む。図3Cに示したように、基本電極198の横辺198tの長さLをその基本電極の長さとし、二つの横辺198tの間の距離Hをその基本電極の高さと定義する。基本電極198から成る第1

10

20

30

40

50

電極部191aと第2電極部191bとの各々の長さと高さとも同様に定義する。図4では、第2電極部191bの高さが第1電極部191aの高さと実質的に同一であり、第2電極部191bの長さが第1電極部191aの長さのほぼ2倍以下である。したがって、第2電極部191bの面積が第1電極部191aの面積のほぼ2倍以下である。

## 【0024】

図4では、第1電極部191aと第2電極部191bとが行方向及び列方向のそれぞれで交互に配置されている。電極部191a、191bの行方向の配置では、第1電極部191aの横中心線と第2電極部191bの横中心線とが同一直線上に置かれ、第1電極部191aの凸辺と第2電極部191bの凹辺とが隣接し、第1電極部191aの凹辺と第2電極部191bの凸辺とが隣接している。一方、第1電極部191aと第2電極部191bとでは長さが異なるので、電極部191a、191bの列方向の配置は多様な形態があり得る。好ましくは、列方向で隣接する二つの電極部191a、191b間では各々の屈曲辺の端点が行方向にずれ、図4に示したように、第1電極部191aと第2電極部191bの中央とが列方向に整列している。

## 【0025】

第1電極部191aを二等分するように重なっている共通電極の切開部71が、第2電極部191bを二等分する切開部93と列方向に並ぶ。一方、第1電極部191aの凹辺及び凸辺は各々、第2電極部191bに含まれる二つの基本電極の各々を二等分する切開部72、73と列方向に並ぶ。それとは異なり、第1電極部191aが第2電極部191bに含まれる二つの基本電極のいずれか一つと列方向に整列しても良い。

## 【0026】

第2電極部191b上の副領域の大きさは一定でない。具体的には、第2電極部191b上の複数の副領域間では幅が異なる。図4を見れば、一つの第2電極部191b上で行方向に配列された四つの副領域では、その第2電極部191bの内側にある二つの副領域SA1の幅L1が、外側にある二つの副領域SA2の幅L2より狭い。好ましくは、第2電極部191bの内側にある各副領域SA1の幅L1は約20μm～30μmであり、外側にある各副領域SA2の幅L2が約30μm以上である。

## 【0027】

以上の配置では、行方向及び列方向のそれぞれで第1電極部191aと第2電極部191bとが交互に配置されているので、全体的なバランスが良く、かつ電極部191a、191bが薄膜トランジスタ表示パネルの表示領域に余すところなく配置され得る。更に、各副領域では電極部の幅L1、L2が十分に広いので、画素全体の開口率が高い。

## 【0028】

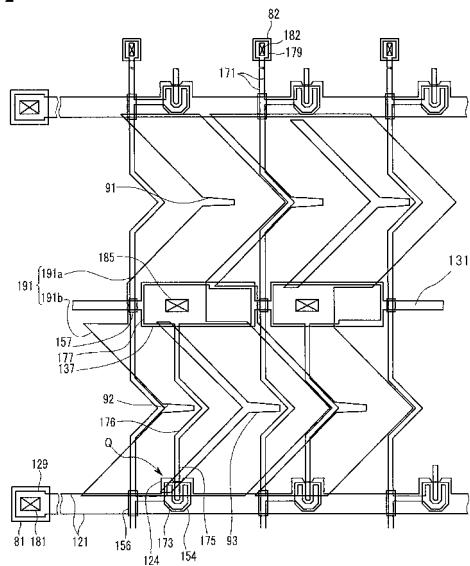

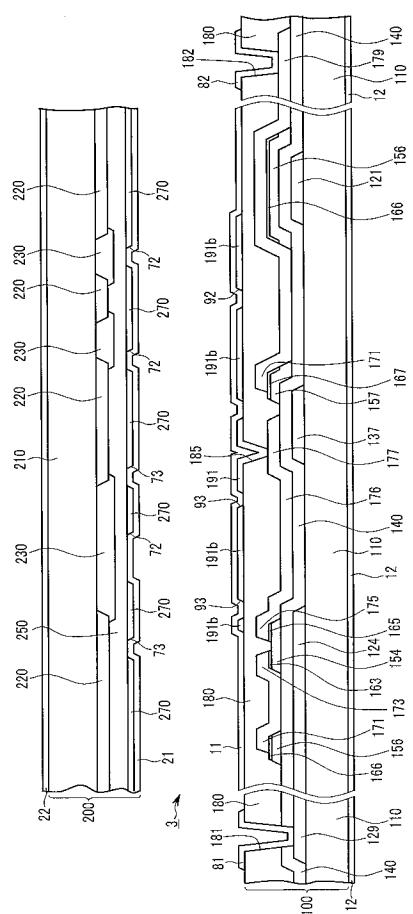

図5は本発明の一つの実施例による液晶表示パネルアセンブリの薄膜トランジスタ表示パネルの配置図であり、図6は本発明の一つの実施例による液晶表示パネルアセンブリの共通電極表示パネルの配置図であり、図7は図5に示した薄膜トランジスタ表示パネルと図6に示した共通電極表示パネルとを含む液晶表示パネルアセンブリの配置図である。図8は図7の液晶表示装置を折れ線VIII-VIIIに沿って切断したときの断面図である。図5～図8に示されているように、本実施例による液晶表示装置は、互いに対向する薄膜トランジスタ表示パネル100と共通電極表示パネル200、及び、それら二つの表示パネル100、200の間に挟まれている液晶層3を含む。

## 【0029】

まず、図5、図7、及び図8を参照して薄膜トランジスタ表示パネル100について説明する。

透明なガラスまたはプラスチックなどで作られた絶縁基板110上に、複数のゲート線121と複数の維持電極線131とを含む複数のゲート導電体が形成されている。ゲート線121は主に横方向に延び、ゲート信号を伝達する。各ゲート線121は、縦方向に突出した複数のゲート電極124と、他の層またはゲート駆動部400との接続のための広い端部129を含む。ゲート駆動部400が基板110上に集積化されている場合、ゲート線121が延びてゲート駆動部400と直結されても良い。維持電極線131は主に横方向に延び、共通電圧Vcomなどの所定の電圧の印加を受ける。各維持電極線131は、隣接する二つのゲート線121の間で、それぞ

10

20

30

40

50

のゲート線121からほとんど同じ距離に位置している。各維持電極線131は縦方向に拡張された複数の維持電極137を含む。尚、維持電極137をはじめ、維持電極線131の模様及び配置はその他にも多様な形態に変更できる。

【0030】

ゲート導電体121、131は好ましくは、アルミニウム(Al)やアルミニウム合金などのアルミニウム系金属、銀(Ag)や銀合金などの銀系金属、銅(Cu)や銅合金などの銅系金属、モリブデン(Mo)やモリブデン合金などのモリブデン系金属、クロム(Cr)、タンタル(Ta)、又はチタニウム(Ti)から成る。ゲート導電体は更に、物理的性質の異なる二つの導電膜(図示せず)を含む多重膜構造を有してもよい。このうちの一つの導電膜は、信号遅延や電圧降下を減らせるように比抵抗の低い金属、例えば、アルミニウム系金属、銀系金属、銅系金属などで作られる。一方、他の導電膜は他の物質、特にITO(酸化インジウムスズ)又はIZO(酸化インジウム亜鉛)との物理的、化学的、電気的接触特性に優れた物質、例えばモリブデン系金属、クロム、タンタル、チタニウムなどで作られる。このような組み合わせの良い例としては、クロム下部膜とアルミニウム(合金)上部膜との組み合わせ、及びアルミニウム(合金)下部膜とモリブデン(合金)上部膜との組み合わせがある。尚、ゲート導電体121、131はそれらの他にも多様な金属または導電体で作ることができる。ゲート導電体121、131の側面は基板110の表面に対して傾いており、その傾斜角は好ましくは約30°～約80°である。

10

20

30

【0031】

ゲート導電体121、131上には、窒化シリコン(SiNx)または酸化シリコン(SiOx)などで作られたゲート絶縁膜140が形成されている。ゲート絶縁膜140上には、水素化非晶質シリコン(a-Si:H)または多結晶シリコンなどで作られた島形の半導体154、156、157が複数形成されている。半導体154はゲート電極124上に位置する。半導体154上には一対の島形の抵抗性接触部材163、165が形成され、半導体156、157の上にも島形の抵抗性接触部材166、167が各々形成されている。抵抗性接触部材163、165、166、167は好ましくは、リンなどのn型不純物が高濃度でドーピングされているn+水素化非晶質シリコンなどの物質で作られている。その他に、シリサイドで作られてもよい。半導体154、156、157と抵抗性接触部材163、165、166、167との各側面は基板110の表面に対して傾いており、傾斜角は30°～80°程度である。

40

【0032】

抵抗性接触部材163、165、166、167及びゲート絶縁膜140の上には、複数のデータ線171と複数のドレイン電極175とを含むデータ導電体が形成されている。データ線171は主に縦方向に延びてゲート線121及び維持電極線131と交差し、データ電圧を伝達する。各データ線171は、右側に突出した複数の屈曲部を含む。各屈曲部は、互いに連結されて山形を成す一対の斜線部を含む。各斜線部はゲート線121と約45°の角度を成す。各データ線171は更に、ゲート電極124に向かって延びた複数のソース電極173と、他の層またはデータ駆動部500との接続のために面積の広い端部179を含む。データ駆動部500が基板110上に集積化されている場合、データ線171がデータ駆動部500と直結されても良い。

50

【0033】

ドレイン電極175はデータ線171から分離され、ゲート電極124の上でソース電極173と対向している。ドレイン電極175は屈曲部176及び拡張部177を含む。屈曲部176の一端はゲート電極124の上で、屈曲したソース電極173に囲まれており、他端は拡張部177に連結されている。屈曲部176は、互いに連結されて山形または不等号(>)の形状を成す一対の斜線部を含む。斜線部はゲート線121と約45°の角度を成す。拡張部177は屈曲部176に連結されており、維持電極137と重なっている。ゲート電極124、ソース電極173、及びドレイン電極175は半導体154と共に薄膜トランジスタ(TFT)Qを構成している。薄膜トランジスタQのチャンネルは、ソース電極173とドレイン電極175との間の半導体154の部分に形成される。

【0034】

データ導電体171、175は好ましくは、モリブデン、クロム、タンタル、若しくはチタニ

50

ウムなどの耐熱性金属、またはこれらの合金で作られる。更に好ましくは、耐熱性金属膜(図示せず)と低抵抗導電膜(図示せず)とを含む多重膜構造を有する。多重膜構造の例としては、クロムまたはモリブデン(合金)下部膜とアルミニウム(合金)上部膜との二重膜、及び、モリブデン(合金)下部膜とアルミニウム(合金)中間膜とモリブデン(合金)上部膜との三重膜がある。尚、データ導電体171、175はそれらの他にも多様な金属または導電体で作ることができる。データ導電体171、175の側面は好ましくは、基板110の表面に対して30°～80°程度の角度で傾いている。

#### 【0035】

抵抗性接触部材163、165、166、167はその下の半導体154、156、157とその上のデータ導電体171、175との間に存在し、それらの間の接触抵抗を下げる。半導体154、156、157には、ソース電極173とドレイン電極175との間の部分をはじめ、データ導電体171、175で覆われずに露出した部分がある。半導体156、157は、ゲート線121と維持電極線131との各々がデータ線171と交差する部分に位置し、ゲート線121及び維持電極線131の表面のプロファイルを滑らかにしてデータ線171の断線を防止する。

#### 【0036】

データ導電体171、175及び半導体154、156、157の露出部分の上には保護膜180が形成されている。保護膜180は無機絶縁物または有機絶縁物などで作られ、表面が平坦である。有機絶縁物は好ましくは4.0以下の誘電常数を有し、感光性を有してもよい。保護膜180は下部無機膜と上部有機膜との二重膜構造を有しても良い。その場合、有機膜の優れた絶縁特性が生かされ、かつ半導体154の露出部分が保護される。保護膜180には、データ線171の端部179とドレイン電極175の拡張部177とを各々露出させる複数の接触孔182、185が形成されている。保護膜180とゲート絶縁膜140とには、ゲート線121の端部129を露出させる複数の接触孔181が形成されている。

#### 【0037】

保護膜180上には複数の画素電極191及び複数の接触補助部材81、82が形成されている。これらは好ましくは、ITOまたはIZOなどの透明な導電物質、又は、アルミニウム、銀、クロム、若しくはそれらの合金などの反射性金属から成る。各画素電極191は、第1電極部191a、第2電極部191b、及びそれら二つの電極部191a、191bを連結する連結部を含む。各電極部191a、191bは切開部91、92、93を有している。画素電極191の模様及び配置については上述の説明を援用する。画素電極191は接触孔185を通じてドレイン電極175と物理的にかつ電気的に連結されており、ドレイン電極175からデータ電圧の印加を受ける。データ電圧が印加された画素電極191は、共通電圧Vcomが印加された共通電極表示パネル200の共通電極270と共に、液晶層3に電場を生成する。それにより、二つの電極191、270の間の液晶層3では液晶分子の方向が変化する。つまり、液晶キャパシタC1cの両端に電位差が生じれば、表示パネル100、200の表面に対してほとんど垂直な電場(主電場)が液晶層3に生成される(以下、画素電極191及び共通電極270と共に“電場生成電極”と言う)。その後、液晶層3の液晶分子の長軸が主電場により主電場の方向から傾く。液晶分子の傾斜角度に応じた角度だけ、液晶層3を透過する光の偏光方向が変わる。この偏光方向の変化が偏光子によって透過率の変化として現れる。その結果、液晶表示装置の画面には映像が表示される。画素電極191と共通電極270とは液晶キャパシタC1cを構成し、薄膜トランジスタが遮断された後も、印加された画素電圧を維持する。

#### 【0038】

液晶分子の傾斜方向は主に、電場生成電極191、270の切開部71～73、91～93と電極部191a、191bの辺とが主電場を歪曲して作り出す水平成分によって決定される。この主電場の水平成分は、切開部71～73、91～93の辺と電極部191a、191bの辺とに対してほぼ垂直である。切開部71～73、91～93によって分けられた各副領域では液晶分子が境界の各辺に対して垂直な方向で傾く。図4及び図7では、液晶分子の傾斜方向がほぼ四つの方向に分かれている。このように、液晶分子の傾斜方向を多様にすれば、液晶表示装置の基準視野角が大きくなる。更に、隣接する二つの電極部191a、191bの間の電圧差によって副次的に生成される電場(副電場)の方向が各副領域の主辺に対して垂直である。したがって、副電場

10

20

30

40

50

の方向が主電場の水平成分の方向と一致するので、電極部191a、191bの間では副電場が液晶分子の傾斜方向を、主電場で決まる方向に揃える。

【0039】

画素電極191に連結されたドレイン電極175の拡張部177はゲート絶縁膜140を間に置いて維持電極137と重なり、ストレージキャパシタCstを構成する。ストレージキャパシタCstは液晶キャパシタC1cの電圧維持能力を補う。

データ線171の一部は画素電極191の屈曲辺と交差し、特に、データ線171の屈曲部が画素電極191の屈曲辺に沿って折れている。このようにデータ線171を画素電極191の境界に沿って延びるようすれば、画素の高い開口率を確保できるのはもちろん、データ線171と電極部191a、191bとの間に生成される電場の水平成分が主電場の水平成分と同じ方向であるので、液晶分子の傾斜方向が更に揃う。

【0040】

維持電極線131とドレイン電極175の拡張部177とは、画素電極191に含まれる二つの電極部191a、191b間の連結部の下地に位置している。ドレイン電極175は接触孔185を通して画素電極191の連結部に接続されている。画素電極191の連結部は、列方向に隣接する二つの副領域間の境界であるので、この部分では液晶分子の配列が乱れやすく、テクスチャが現れやすい。しかし、維持電極線131とドレイン電極175の拡張部177とを上記のように配置すれば、画素の開口率が向上するのはもちろん、それらでテクスチャを覆うことができる。

接触補助部材81、82は各々接触孔181、182を通じてゲート線121の端部129及びデータ線171の端部179に連結される。接触補助部材81、82はゲート線121の端部129及びデータ線171の端部179と外部装置との接着性を補完し、これらを保護する。

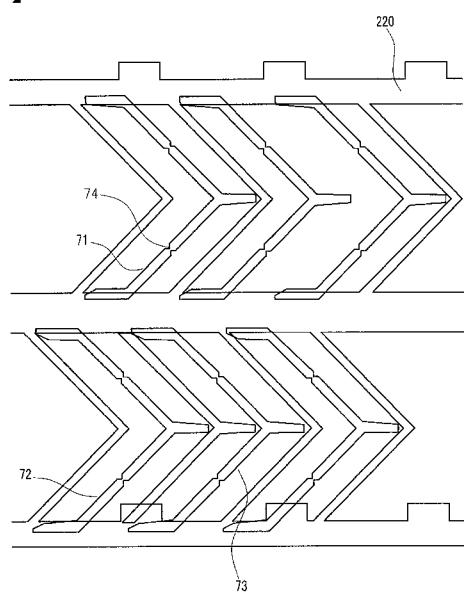

【0041】

次に、図6～図8を参照しながら、共通電極表示パネル200について説明する。

透明なガラスまたはプラスチックなどで作られた絶縁基板210上に遮光部材220が形成されている。遮光部材220は、ゲート線121と維持電極線131とのそれぞれに対向する一対の横部、画素電極191の屈曲辺に対向する屈曲部、及び、薄膜トランジスタQに対向する広い部分を含む。遮光部材220は画素電極191と対向する開口領域を区切り、隣接する二つの画素電極191の間からの光漏れを防止する。

基板210及び遮光部材220上には複数の色フィルター230が形成されている。色フィルター230は、遮光部材220で囲まれた開口領域のほとんどを覆う。各色フィルター230が画素電極191の列に沿って長く延びても良い。各色フィルター230は、赤色、緑色、及び青色の三原色など、基本色のいずれか一つを呈する。

色フィルター230及び遮光部材220の上には蓋膜250が形成されている。蓋膜250は好ましくは(有機)絶縁物から成り、色フィルター230の露出を防止し、かつその表面を平坦化させる。尚、蓋膜250は省略されても良い。

【0042】

蓋膜250上には共通電極270が形成されている。共通電極270は好ましくはITO、IZOなどの透明な導電体から成り、複数の切開部71、72、73を有する。切開部71～73の斜線部には三角形状の切り欠き74が形成されている。切り欠き74の形状はその他に、四角形、台形、または半円形であっても良い。更に、切り欠き74に代え、凸部が形成されていても良い。切り欠き74は、各切開部71～73により生じる副領域間の境界で液晶分子の傾斜方向を決める。共通電極270の切開部71～73の模様及び配置については上述の説明を援用する。電場生成電極の切開部71～73、91～93の数は設計要素に応じて変更可能である。尚、遮光部材220が切開部71～73、91～93と重なり、切開部71～73、91～93付近からの光漏れを遮断する。

【0043】

表示パネル100、200の各内面には配向膜11、21が形成されている。配向膜11、21は好ましくは垂直配向膜である。表示パネル100、200の各外面には偏光子12、22が備えられている。二つの偏光子12、22の偏光軸は互いに直交し、好ましくは、一方の偏光軸はゲート線

10

20

30

40

50

121に対して平行である。反射型液晶表示装置の場合、二つの偏光子12、22のいずれか一つが省略できる。液晶表示装置は更に、液晶層3の位相を補償する位相遅延膜（図示せず）、表示パネル100、200と液晶層3とに光を供給する照明部（バックライト部。図示せず）を含んでいても良い。液晶層3は好ましくは負の誘電率異方性を示す。その場合、液晶層3の液晶分子の長軸が、電場のない状態では二つの表示パネルの表面に対して垂直である。

尚、電場生成電極の切開部71～73、91～93は、突起（図示せず）や陥没部（図示せず）で代替可能である。突起は有機物または無機物で作ることができ、電場生成電極191、270の上または下に配置される。

#### 【0044】

10

図1に示されている階調電圧生成部800は、各画素PXの透過率に対応する階調電圧の集合（または基準階調電圧の集合）を二組生成する。二組の階調電圧の集合うち、一方では階調電圧の値が共通電圧Vcomに対して正であり、他方では負である。

ゲート駆動部400は液晶表示パネルアセンブリ300のゲート線G<sub>1</sub>～G<sub>n</sub>に連結され、ゲートオン電圧Vonとゲートオフ電圧Voffとの組み合わせから成るゲート信号をゲート線G<sub>1</sub>～G<sub>n</sub>に対して印加する。

データ駆動部500は液晶表示パネルアセンブリ300のデータ線D<sub>1</sub>～D<sub>m</sub>に連結され、階調電圧生成部800により生成される階調電圧の一つを選択し、データ電圧としてデータ線D<sub>1</sub>～D<sub>m</sub>に対して印加する。尚、階調電圧生成部800が基準階調電圧を提供する場合、データ駆動部500は基準階調電圧を分圧して全階調に対する階調電圧を生成し、それらの中からデータ電圧を選択する。

20

信号制御部600はゲート駆動部400及びデータ駆動部500を制御する。

#### 【0045】

20

駆動装置400、500、600、800の各々は好ましくは、少なくとも一つの集積回路チップの形態で液晶表示パネルアセンブリ300上に直接実装される。その他に、可撓性印刷回路膜（図示せず）上に実装されてTCP（tape carrier package）の形態で液晶表示パネルアセンブリ300に接着されても良い。更に、別の印刷回路基板（図示せず）上に実装されても良い。駆動装置400、500、600、800が信号線G<sub>1</sub>～G<sub>n</sub>、D<sub>1</sub>～D<sub>m</sub>及び薄膜トランジスタQと共に液晶表示パネルアセンブリ300に集積化されても良い。また、駆動装置400、500、600、800は単一のチップに集積化されても良い。その場合、駆動装置400、500、600、800のうち、少なくとも一つ、またはそれらを構成する少なくとも一つの回路素子が、上記のチップに外付けされても良い。

30

#### 【0046】

30

次に、上記の液晶表示装置の動作について詳細に説明する。

信号制御部600は外部のグラフィックコントローラ（図示せず）から、入力映像信号R、G、B、及び入力制御信号を受信する。入力映像信号R、G、Bは各画素PXの輝度情報を含んでいる。そこでは、各画素PXの輝度が、所定数（例えば、1024（=2<sup>10</sup>）、256（=2<sup>8</sup>）、または64（=2<sup>6</sup>））の階調のいずれかの値で表されている。入力制御信号の例としては、垂直同期信号Vsync、水平同期信号Hsync、メインクロックMCLK、データイネーブル信号DEなどがある。信号制御部600は入力映像信号R、G、Bと入力制御信号とに基づいて入力映像信号R、G、Bを、液晶表示パネルアセンブリ300及びデータ駆動部500の動作条件に合わせて適切に処理する。信号制御部600は更に、ゲート制御信号CONT1及びデータ制御信号CONT2を生成し、ゲート制御信号CONT1をゲート駆動部400に出力し、データ制御信号CONT2と処理された映像信号DATとをデータ駆動部500に出力する。出力映像信号DATはデジタル信号であり、特に、各画素PXの輝度に対応する階調値を示す。ゲート制御信号CONT1は、走査開始を指示するための走査開始信号STVと、ゲートオン電圧Vonの出力タイミングを示すクロック信号とを含む。ゲート制御信号CONT1は、ゲートオン電圧Vonの持続時間を限定するための出力イネーブル信号OEをさらに含んでいても良い。データ制御信号CONT2は、画素PXのマトリックスの各行に対して映像データの伝送開始を知らせるための水平同期開始信号、データ線D<sub>1</sub>～D<sub>m</sub>に対するデータ電圧の印加を命令するためのロード信号、及び、データ

40

50

タクロック信号HCLKを含む。データ制御信号CONT2は、共通電圧Vcomに対するデータ電圧の極性（以下、単に“データ電圧の極性”と言う）を反転させるための反転信号をさらに含んでも良い。

#### 【0047】

信号制御部600からのデータ制御信号CONT2に従い、データ駆動部500は画素PXのマトリックスの各行に対するデジタル映像信号DATを受信し、各デジタル映像信号DATの示す階調値に対応する階調電圧を選択する。それにより、デジタル映像信号DATをアナログ信号であるデータ電圧に変換する。その後、データ駆動部500はデータ電圧を目標のデータ線D<sub>1</sub>～D<sub>m</sub>に対して印加する。ゲート駆動部400は信号制御部600からのゲート制御信号CONT1に従い、ゲートオン電圧Vonをゲート線G<sub>1</sub>～G<sub>n</sub>に対して印加する。それにより、そのゲート線G<sub>1</sub>～G<sub>n</sub>に連結されたスイッチング素子Qが導通する。そのとき、データ線D<sub>1</sub>～D<sub>m</sub>に対して印加されたデータ電圧が、導通したスイッチング素子Qを通じて画素PXに対して印加される。画素PXに対して印加されたデータ電圧と共通電圧Vcomとの間の差が液晶キャパシタClcの両端電圧、つまり、画素電圧を定める。液晶分子の傾斜方向が画素電圧の大きさに応じて変化するので、液晶層3を透過する光の偏光方向が変化する。この偏光方向の変化が、液晶表示パネルアセンブリ300に接着された偏光子によって光透過率の変化として現れる。こうして、各画素PXが、映像信号DATの示す階調値に相当する輝度で光る。

#### 【0048】

1水平周期1H（水平同期信号Hsync及びデータイネーブル信号DEの一周期と等しい）を単位として上記の過程が繰り返されることにより、全てのゲート線G<sub>1</sub>～G<sub>n</sub>に対して順番にゲートオン電圧Vonが印加され、かつ全ての画素PXに対してデータ電圧が印加される。こうして、一つのフレームの映像が画面に表示される。一つのフレームの表示が終われば次のフレームの表示が始まる。そのとき、好ましくは、各画素PXに対して印加されるデータ電圧の極性が、直前のフレームにおける極性と反対になるように、データ駆動部500に対して印加される反転信号の状態が制御される（“フレーム反転”）。更に、一つのフレーム内でも反転信号の状態が制御されることにより、一つのデータ線に対して印加されるデータ電圧の極性が反転し（例：行反転、点反転）、又は画素マトリックスの行ごとに、印加されるデータ電圧の極性が反転しても良い（例：列反転、点反転）。

#### 【0049】

液晶キャパシタClcの両端に対して電圧が印加された時点から液晶層では液晶分子の再配列が開始され、それらの配向状態が、印加電圧の大きさによって定まるある安定な状態に向かって変化し始める。しかし、液晶分子の応答速度が低いので、その安定な状態に至るまでにはある程度の時間がかかる。液晶キャパシタClcに対して印加される電圧が維持されていれば、液晶分子の配向状態が安定な状態に至るまで液晶分子が動き続ける。それに併せて画素の光透過率もまた変化し続ける。液晶分子の配向状態が安定な状態に至れば、液晶分子が動かないで、液晶層の光透過率は一定になる。ここで、安定な配向状態での画素電圧の値を“画素電圧の目標値（以下、目標画素電圧と言う）”とし、かつ画素の光透過率の値を“光透過率の目標値（以下、目標光透過率と言う）”とすれば、目標画素電圧と目標光透過率との間には一対一の対応関係がある。

#### 【0050】

各画素PXのスイッチング素子Qを導通状態に維持してその画素PXに対してデータ電圧を印加し続けられる時間は限られている。更に、その限られた時間では、液晶分子の配向状態を安定な状態にまで至らせるのは一般に難しい。一方、スイッチング素子Qが遮断された後でも、液晶キャパシタClcの両端電圧は依然として維持されるので、液晶分子が安定な配向状態に向かって動き続ける。ここで、液晶分子の配向状態が変われば液晶層3の誘電率が変わるので、液晶キャパシタClcの静電容量が変化する。スイッチング素子Qが遮断された状態では液晶キャパシタClcの一つの端子が浮遊（フローティング）状態にあるので、（漏洩電流が無視できれば）液晶キャパシタClcに貯蔵された電荷は一定量に保たれる。したがって、液晶キャパシタClcの静電容量の変化は、液晶キャパシタClcの両端電圧、つまり、画素電圧の変化を招く。それ故、液晶層が安定な配向状態にあることを前提と

10

20

30

40

50

して目標画素電圧を定め、それに対応するデータ電圧の目標値（以下、“目標データ電圧”と言う）をそのまま画素PXに対して印加しても、液晶層がその安定な配向状態に実際に到達したときでは画素電圧の実際の値（以下、実際画素電圧と言う）が目標画素電圧とは異なる。その結果、目標光透過率が得られない。特に、目標データ電圧の印加直前でのその画素PXの光透過率と目標光透過率との間の差が大きいほど、実際画素電圧と目標画素電圧との間の差が大きい。

#### 【0051】

以上の考察から明らかな通り、画素PXに対して実際に印加すべきデータ電圧を目標データ電圧とは異なる値に調節する必要がある。その調節のための方法の一つがDCC (dynamic capacitance compensation) である。本実施例では、DCCが信号制御部600または別の映像信号補正部で行われる。DCCでは、任意の画素PXに対する現在のフレーム（N番目のフレーム）の映像信号の示す階調値 $g_N$ が、その画素PXに対する直前のフレーム（(N-1)番目のフレーム）の映像信号の示す階調値 $g_{N-1}$ に基づいて補正される。そのとき補正された階調値 $g_N'$ を示す映像信号を以下、“第1補正映像信号”と言う。ここで、補正前の階調値 $g_N$ と第1補正映像信号の示す階調値 $g_N'$ との間の関係は基本的には実験によって予め決められている。特に、第1補正映像信号の示す階調値 $g_N'$ と直前のフレームの映像信号の示す階調値 $g_{N-1}$ との間の差は一般に、補正前の階調値 $g_N$ と直前のフレームの映像信号の示す階調値 $g_{N-1}$ との間の差より大きい。但し、現在のフレームの映像信号の示す階調値 $g_N$ と直前のフレームの映像信号の示す階調値 $g_{N-1}$ とが同一であるとき、又は両方の階調値間の差が小さいときは、第1補正映像信号の示す階調値 $g_N'$ が現在のフレームの映像信号の示す階調値 $g_N$ と同一である（つまり、階調値が補正されないことがある）。

#### 【0052】

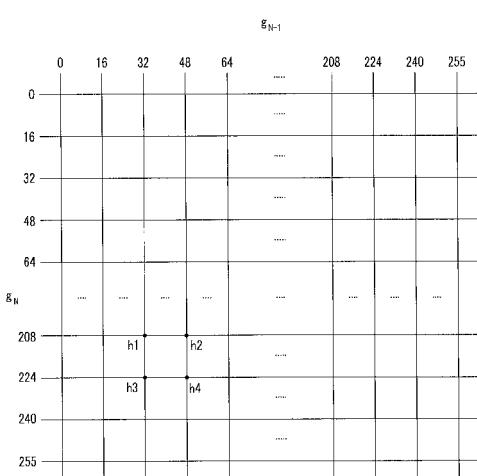

第1補正映像信号の示す階調値 $g_N'$ は、現在のフレームと直前のフレームとの各映像信号の示す階調値 $g_N$ 、 $g_{N-1}$ の関数F1として表される： $g_N' = F1(g_N, g_{N-1})$ 。特に、第1補正映像信号の示す階調値 $g_N'$ に対応するデータ電圧は、現在のフレームの映像信号の示す階調値 $g_N$ に対応する目標データ電圧とは異なる。表1には、階調の総数が256である場合を例として、直前のフレームと現在のフレームとの各映像信号の示す階調値 $g_{N-1}$ 及び $g_N$ の対ごとに、第1補正映像信号の示す階調値 $g_N'$ が示されている。

#### 【0053】

##### 【表1】

|                |     | g <sub>N-1</sub> |     |     |     |     |     |     |     |     |

|----------------|-----|------------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                |     | 0                | 32  | 64  | 96  | 128 | 160 | 192 | 224 | 255 |

| g <sub>N</sub> | 0   | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|                | 32  | 115              | 32  | 22  | 20  | 15  | 15  | 15  | 15  | 15  |

|                | 64  | 169              | 103 | 64  | 50  | 34  | 27  | 22  | 20  | 16  |

|                | 96  | 192              | 146 | 118 | 96  | 87  | 70  | 54  | 36  | 29  |

|                | 128 | 213              | 167 | 156 | 143 | 128 | 121 | 105 | 91  | 70  |

|                | 160 | 230              | 197 | 184 | 179 | 174 | 160 | 157 | 147 | 129 |

|                | 192 | 238              | 221 | 214 | 211 | 205 | 199 | 192 | 187 | 182 |

|                | 224 | 250              | 245 | 241 | 240 | 238 | 238 | 224 | 224 | 222 |

|                | 255 | 255              | 255 | 255 | 255 | 255 | 255 | 255 | 255 | 255 |

#### 【0054】

この映像信号補正を行うためには、直前のフレームの映像信号 $g_{N-1}$ を記憶しておく記憶空間が必要であり、好ましくはフレームメモリがその役割を果たす。また、表1を記憶

10

20

30

40

50

しておくルックアップテーブルが必要である。しかし、現在のフレーム及び直前のフレームの各映像信号の示す階調値の対  $g_{N-1}, g_N$  の可能な組み合わせの全てについて第1補正映像信号の示すべき階調値  $g_N'$  を記憶しておくためには、ルックアップテーブルが非常に大きくなければならない。従って、好ましくは、表1に示されている組み合わせの数程度の階調値の対  $g_{N-1}, g_N$  について、第1補正映像信号の示すべき階調値  $g_N'$  を基準補正階調値として記憶しておく。一方、記憶された組み合わせ以外の階調値の対  $g_{N-1}, g_N$  については、好ましくは補間法による演算で第1補正映像信号の示すべき階調値  $g_N'$  を求める。すなわち、任意の階調値の対  $g_{N-1}, g_N$  に対しては、まず、その対  $g_{N-1}, g_N$  と近い対  $g_{N-1}', g_N'$  に対する基準補正階調値  $g_{N-1}', g_N'$  を表1から検索する。次に、元の対  $g_{N-1}, g_N$  とそれに近い対  $g_{N-1}', g_N'$  との間の差、及び検索された基準補正階調値  $g_{N-1}', g_N'$  に基づき、元の階調値の対  $g_{N-1}, g_N$  に対する第1補正映像信号の示すべき階調値  $g_N'$  を補間法で算出する。更に具体的には、例えば、映像信号の示す階調値（バイナリ値）を上位ビットと下位ビットとに分け、ルックアップテーブルには、下位ビットが0である階調値の対  $g_{N-1}', g_N'$  に対する基準補正階調値を記憶しておく。任意の階調値の対  $g_{N-1}, g_N$  に対しては、まず、各階調値の上位ビットに基づいて基準補正階調値  $g_{N-1}', g_N'$  をルックアップテーブルから検索する。次に、階調値の対  $g_{N-1}, g_N$  の各下位ビットと、ルックアップテーブルから検索された基準補正階調値  $g_{N-1}', g_N'$  とを利用し、第1補正映像信号の示すべき階調値  $g_N'$  を補間法で算出する。

#### 【0055】

以上のような方法によっても目標光透過率を得ることが難しいことがある。その場合には、例えば、直前のフレームでの目標画素電圧と現在のフレームでの目標画素電圧との中间の画素電圧を直前のフレームで予め画素に対して印加し、その画素に含まれる液晶分子を予め傾けておく（これを予備傾斜と言う）。その上で、現在のフレームで目標画素電圧をその画素に対して印加すれば、液晶分子は既にある程度傾いているので、安定な配向状態が速やかに実現される。実際にその効果を得るためにには、信号制御部600（または別の映像信号補正部）は、現在のフレームの映像信号  $g_N$  を補正する時、直前のフレームの映像信号  $g_{N-1}$  だけでなく、次のフレーム（(N+1)番目のフレーム）の映像信号の示す階調値  $g_{N+1}$  をも考慮し、補正された階調値  $g_N''$  を示す映像信号（以下、第2補正映像信号と言う）を作り出す。例えば、現在のフレームの映像信号の示す階調値  $g_N$  が直前のフレームの映像信号の示す階調値  $g_{N-1}$  とは同一であっても、次のフレームの映像信号の示す階調値  $g_{N+1}$  とは大きく異なれば、現在のフレームの映像信号の示す階調値  $g_N$  が補正される。第2補正映像信号の示す階調値  $g_N''$  は、第1補正映像信号の示す階調値  $g_N'$  と次のフレームの映像信号の示す階調値  $g_{N+1}$  との関数F2で表される： $g_N'' = F2(g_N', g_{N+1})$ 。従って、直前のフレームの映像信号  $g_{N-1}$  と現在のフレーム映像信号  $g_N$  とを記憶するフレームメモリに加え、直前のフレーム及び現在のフレームの各映像信号の示す階調値の対  $(g_{N-1}, g_N)$  に対する補正階調値を記憶するルックアップテーブルが必要である。場合によっては、現在のフレーム及び次のフレームの各映像信号の示す階調値の対  $(g_N, g_{N+1})$  に対する補正階調値を記憶するルックアップテーブルが必要であることもある。

#### 【0056】

以上のような映像信号及びデータ電圧の補正是、映像信号の示す階調値の上限または下限に対しては行われなくてもよい。一方、階調値の上限または下限に対する補正を行うためには、階調電圧生成部800により生成される階調電圧の範囲を、映像信号の示す階調値の範囲に対応する目標輝度の範囲（または目標光透過率の範囲）を得るために必要な目標データ電圧の範囲より広げる方法が使用可能である。

#### 【0057】

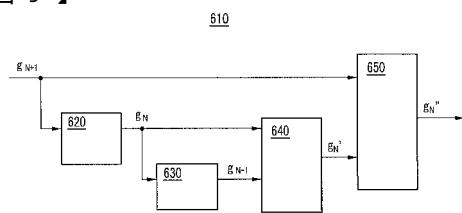

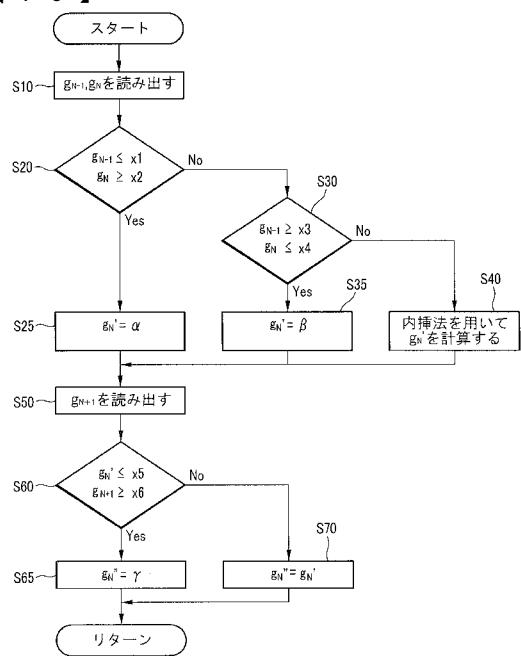

以下では、上記のような映像信号補正を実現する、本発明の一つの実施例による液晶表示装置の映像信号補正部について、図9～図11を参照しながら詳細に説明する。

図9は本発明の一つの実施例による液晶表示装置の映像信号補正部のブロック図であり、図10は図9に示した映像信号補正部の動作を示す流れ図の一例であり、図11は本発明の一つの実施例による映像信号補正方法を説明するための図である。

#### 【0058】

10

20

30

40

50

図9に示したように、本発明の一つの実施例による映像信号補正部610は、次のフレームの映像信号 $g_{N+1}$ が入力される第1メモリ620、第1メモリ620に連結されている第2メモリ630、第1メモリ620と第2メモリ630との両方に連結されている第1補正部640、及び、次のフレームの映像信号 $g_{N+1}$ が入力され、かつ第1補正部640に連結されている第2補正部650を含む。映像信号補正部610の全体または一部が図1に示した信号制御部600に含まれてもよく、別の装置で実現されてもよい。

#### 【0059】

第1メモリ620は、記憶されている現在のフレームの映像信号 $g_N$ を第2メモリ630と第1補正部640とに出力する一方、新たに入力される次のフレームの映像信号 $g_{N+1}$ を記憶する。第2メモリ630は、記憶されている直前のフレームの映像信号 $g_{N-1}$ を第1補正部640に出力する一方、第1メモリ620から現在のフレームの映像信号 $g_N$ を入力して記憶する。尚、ここでは、第1メモリ620と第2メモリ630とが分離されている。その他に、一つのメモリが、記憶されている直前のフレームの映像信号 $g_{N-1}$ 及び現在のフレームの映像信号 $g_N$ を第1補正部640に出力する一方、新たに入力される次のフレームの映像信号 $g_{N+1}$ を記憶しても良い。

#### 【0060】

第1補正部640はルックアップテーブル(図示せず)を含み、第2メモリ630から入力した直前のフレームの映像信号 $g_{N-1}$ 、及び、第1メモリ620から入力した現在のフレームの映像信号 $g_N$ に基づいて第1補正映像信号の示すべき階調値 $g_N'$ を算出し、第1補正映像信号 $g_N'$ を第2補正部650に出力する。ここで、ルックアップテーブルは上述したように、直前のフレームの映像信号の示す階調値 $g_{N-1}$ 及び現在のフレームの映像信号の示す階調値 $g_N$ の対に対する基準補正階調値 $g_{N-1}^0$ を記憶している。第2補正部650は、次のフレームの映像信号 $g_{N+1}$ と第1補正部640から入力した第1補正映像信号 $g_N'$ に基づいて第2補正映像信号の示すべき階調値 $g_N''$ を算出し、第2補正映像信号 $g_N''$ を出力する。

#### 【0061】

以下では、第1補正部640及び第2補正部650の各動作について、より詳細に説明する。

図10に示したように、まず、第1補正部640が第1メモリ620から現在のフレームの映像信号 $g_N$ を読み込み、第2メモリ630から直前のフレームの映像信号 $g_{N-1}$ を読み込む(S10)。次に、第1補正部640は直前のフレームの映像信号の示す階調値 $g_{N-1}$ と設定値( $x1$ 、 $x3$ )とを比較し、現在のフレームの映像信号の示す階調値 $g_N$ と設定値( $x2$ 、 $x4$ )とを比較する(S20、S30)。段階S20で比較した結果、直前のフレームの映像信号の示す階調値 $g_{N-1}$ が設定値 $x1$ 以下であり、かつ現在のフレームの映像信号の示す階調値 $g_N$ が設定値 $x2$ ( $> x1$ )以上であれば、第1補正映像信号の示すべき階調値 $g_N'$ が補正值に設定される(S25)。段階S30で比較した結果、直前のフレームの映像信号の示す階調値 $g_{N-1}$ が設定値 $x3$ 以上であり、かつ現在のフレームの映像信号の示す階調値 $g_N$ が設定値 $x4$ ( $< x3$ )以下である場合、第1補正映像信号の示すべき階調値 $g_N'$ が補正值に設定される(S35)。ここで、設定値 $x1$ 、 $x2$ は、階調値の対 $g_{N-1}$ 、 $g_N$ に対してオーバーシュート電圧(後述参照)の適用条件を与えるために設定されたしきい値である。特に、設定値 $x1$ は直前のフレームの映像信号の示す階調値 $g_{N-1}$ に対して設定された上限しきい値であり、設定値 $x2$ は現在のフレームの映像信号の示す階調値 $g_N$ に対して設定された下限しきい値である。一方、設定値 $x3$ 、 $x4$ は、階調値の対 $g_{N-1}$ 、 $g_N$ に対してアンダーシュート電圧(後述参照)の適用条件を与えるために設定されたしきい値である。特に、設定値 $x3$ は直前のフレームの映像信号の示す階調値 $g_{N-1}$ に対して設定された下限しきい値であり、設定値 $x4$ は現在のフレームの映像信号の示す階調値 $g_N$ に対して設定された上限しきい値である。補正值、 $x1$ 、 $x2$ は各々、映像信号の示し得る階調値の上限値及び下限値である。例えば、映像信号が8ビットである場合、補正值 $x1$ が“255”であり、補正值 $x2$ が“0”である。

#### 【0062】

以下の説明では簡単のため、映像信号が8ビットである場合を想定する。補正值 $x1$  = “255”は目標データ電圧の上限より高い電圧(以下、“オーバーシュート電圧”と言う)に対応し、補正值 $x2$  = “0”は目標データ電圧の下限より低い電圧(以下、“アンダーシュート電圧”と言う)に対応する。

10

20

30

40

50

ト電圧”と言う)に対応する。オーバーシュート電圧及びアンダーシュート電圧は各々、階調電圧生成部800により生成可能な階調電圧の上限及び下限である。オーバーシュート電圧及びアンダーシュート電圧を画素に対して印加するために、信号制御部600は、三原色の各階調で色感を一致させる色補正を通じ、入力映像信号の示す階調値の範囲を予め縮少する。つまり、データ駆動部500に入力される映像信号の示す階調値の範囲が0~255から、色補正を通じて1~254の範囲に変換される。変換された階調値の下限“1”が目標データ電圧の下限に相当し、変換された階調値の上限“254”が目標データ電圧の上限に相当する。ノーマリーブラックの液晶表示装置の場合、変換された階調値の下限“1”がブラック階調であり、変換された階調値の上限“254”がホワイト階調である。ノーマリーホワイトの液晶表示装置の場合は反対である。以下の説明では液晶表示装置がノーマリーブラックモードである場合を想定する。尚、必要に応じてはオーバーシュート電圧が適用されることもある。その場合、補正值“255”が目標データ電圧の上限に相当し、かつホワイト階調である。また、映像信号の示す階調値の範囲は1~255に変換される。

#### 【0063】

段階S20、S30で比較した結果、段階S25、S35に相当する場合でなければ、第1補正部640は、読み込んだ直前のフレーム及び現在のフレームの各映像信号の示す階調値の対( $g_{N-1}$ 、 $g_N$ )に対応する複数の基準補正階調値をルックアップテーブルから検索し、検索された基準補正階調値と読み込んだ階調値の対( $g_{N-1}$ 、 $g_N$ )に基づいて補間法により第1補正映像信号の示すべき階調値 $g_N'$ を算出する(S40)。好ましくは、図11に示されているように、直前のフレーム及び現在のフレームの各映像信号の示す階調値の対( $g_{N-1}$ 、 $g_N$ )の可能な組み合わせのうち、16階調刻みで選別された $17 \times 17$ の組み合わせに対する基準補正階調値が、ルックアップテーブルには記憶されている。読み込んだ階調値の対( $g_{N-1}$ 、 $g_N$ )が例えば(36、218)であれば、第1補正部640はまず、ルックアップテーブルに記憶された四つの対(32、208)、(48、208)、(32、224)、(48、224)のそれぞれに対する基準補正階調値 $h1$ 、 $h2$ 、 $h3$ 、 $h4$ をルックアップテーブルから抽出する。次に、抽出された基準補正階調値 $h1$ 、 $h2$ 、 $h3$ 、 $h4$ を基準として線形補間を行い、第1補正映像信号の示すべき階調値 $g_N'$ を算出する。尚、基準補正階調値 $h1$ 、 $h2$ 、 $h3$ 、 $h4$ は好ましくは実験によって予め決められる。

#### 【0064】

第2補正部650は次のフレームの映像信号 $g_{N+1}$ を読み込む(S50)。第2補正部650は更に、第1補正部640から入力した第1補正映像信号の示す階調値 $g_N'$ と設定値 $x5$ とを比較し、次のフレームの映像信号の示す階調値 $g_{N+1}$ と設定値 $x6$ とを比較する(S60)。段階S60で比較した結果、第1補正映像信号の示す階調値 $g_N'$ が設定値 $x5$ 以下であり、かつ次のフレームの映像信号 $g_{N+1}$ が設定値 $x6$ 以上であれば、第2補正映像信号の示すべき階調値 $g_N''$ が補正值に設定される(S65)。段階S60で比較した結果、段階S65に相当する場合でなければ、第2補正映像信号 $g_N''$ が第1補正映像信号 $g_N'$ と同一の階調値を示すように設定される(S70)。このように第2補正映像信号 $g_N''$ が決められれば、処理が最初の段階S10に戻される。ここで、補正值は第1補正映像信号の示す階調値 $g_N'$ より大きく、液晶分子の予備傾斜に必要な画素電圧(予備傾斜電圧)に相当する。設定値 $x5$ 、 $x6$ は、階調値の対 $g_N'$ 、 $g_{N+1}$ に対して予備傾斜の適用条件を与えるために設定されたしきい値である。特に、設定値 $x5$ は第1補正映像信号の示す階調値 $g_N'$ に対して設定された上限しきい値であり、設定値 $x6$ は次のフレームの映像信号の示す階調値 $g_{N+1}$ に対して設定された下限しきい値である。上記の設定値 $x1$ ~ $x6$ 、及び補正值は、液晶表示装置の特性及び設計要素によって変更可能であり、実験によって決められても良い。

#### 【0065】

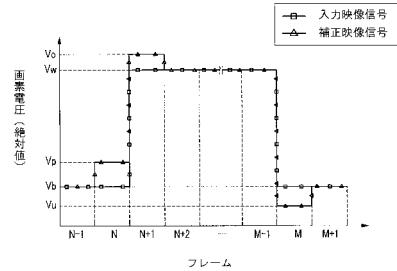

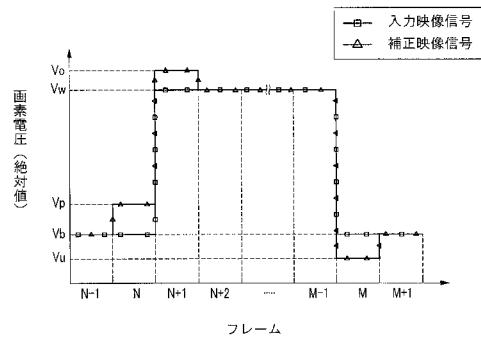

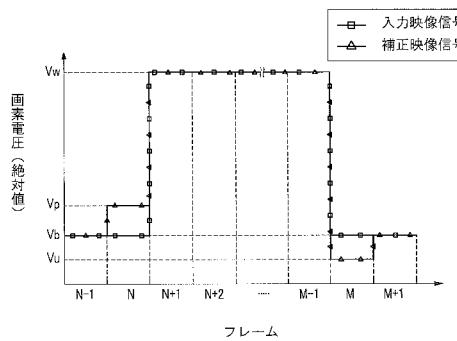

本発明の一つの実施例による映像信号補正部610が入力映像信号について第2補正映像信号を生成する一例を図12A及び図12Bを参照しながら説明する。図12A及び図12Bは、本発明の一つの実施例によって補正された信号の波形図である。図12A及び図12Bの波形図において、横軸はフレームの順番を示し、縦軸は絶対値で表示した画素電圧を示す。図12Aの波形図はオーバーシュート電圧を適用した場合の波形図である。前

10

20

30

40

50

述の通り、画素電圧の上限はオーバーシュート電圧 $V_o$ であり、下限はアンダーシュート電圧 $V_u$ である。一方、図12Bの波形図はオーバーシュート電圧を適用していない場合の波形図である。図12Bでは図12Aとは異なり、画素電圧の上限がホワイト電圧 $V_w$ である。ここで、ブラック階調に対応する画素電圧をブラック電圧 $V_b$ とし、ホワイト階調に対応する画素電圧をホワイト電圧 $V_w$ とする。

#### 【0066】

入力映像信号が、第(N-1)フレーム及び第Nフレームでブラック階調を示し、第(N+1)フレーム及び第(N+2)フレームでホワイト階調を示し、第(M-1)フレームでホワイト階調を示し、第Mフレーム及び第(M+1)フレームでブラック階調を示す場合を想定する(N+1 < M)。

10

#### 【0067】

図12Aでは、第Nフレーム及び第(N+1)フレームの各入力映像信号の示す階調値が上記のオーバーシュート電圧の適用条件を満たすので、第1補正部640が、第(N+1)フレームの第1補正映像信号をオーバーシュート電圧 $V_o$ に設定する。一方、第(M-1)フレーム及び第Mフレームの各入力映像信号の示す階調値が上記のアンダーシュート電圧の適用条件を満たすので、第1補正部640が、第Mフレームの第1補正映像信号をアンダーシュート電圧 $V_u$ に設定する。更に、第Nフレーム、第(N+2)フレーム、及び第(M+1)フレームの各入力映像信号が、それぞれの直前のフレームの入力映像信号と同一であるので、第1補正部640が、第Nフレーム、第(N+2)フレーム、及び第(M+1)フレームの各第1補正映像信号を各入力映像信号と同一に設定する。第Nフレーム及び第(N+1)フレームの各入力映像信号の示す階調値はまた、段階S60での予備傾斜の適用条件を満たすので、第2補正部650は、第Nフレームの第2補正映像信号を補正值、すなわち、予備傾斜電圧 $V_p$ に設定する。一方、他のフレームの第2補正映像信号を各フレームの第1補正映像信号と同一に設定する。その結果、最終的に出力される第2補正映像信号は、第(N-1)フレームから順に、ブラック電圧 $V_b$ 、予備傾斜電圧 $V_p$ 、オーバーシュート電圧 $V_o$ 、ホワイト電圧 $V_w$ になり、第(M-1)フレームからは順に、ホワイト電圧 $V_w$ 、アンダーシュート電圧 $V_u$ 、ブラック電圧 $V_b$ になる。第Nフレームでは第2補正映像信号を予備傾斜電圧 $V_p$ として画素に対して印加することで、液晶分子が予め傾くので、第(N+1)フレームでは画素の実際の光透過率が、ホワイト電圧 $V_w$ に対応する目標光透過率に速かに接近する。

20

#### 【0068】

図12Bでは、第1補正部640及び第2補正部650がいずれも第(N+1)フレームにおける補正映像信号をホワイト電圧 $V_w$ に設定する。他のフレームにおける第1補正部640及び第2補正部650の各動作は図12Aと同一である。すなわち、階調電圧生成部800により生成可能な階調電圧の上限がオーバーシュート電圧 $V_o$ の代わりにホワイト電圧 $V_w$ として使用される。それにより、ホワイト階調に対応する画素の実際の輝度を高めることができる。一方、その場合では、オーバーシュート電圧を適用する場合(図12A)に比べて液晶の応答速度が低下することがある。しかし、予備傾斜電圧 $V_p$ を適切に調節することで、十分に高い応答速度を確保できる。

30

#### 【0069】

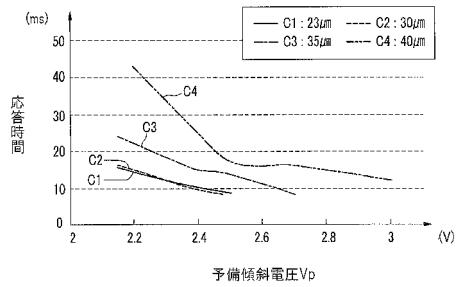

以下では、上述した液晶表示パネルアセンブリ300について、各副領域に含まれる電極部の幅L1、L2、ブラック電圧 $V_b$ 、予備傾斜電圧 $V_p$ 、及びアンダーシュート電圧 $V_u$ のそれぞれの変化に応じた液晶の応答速度の変化を、図13～図16を参照しながら詳細に説明する。

40

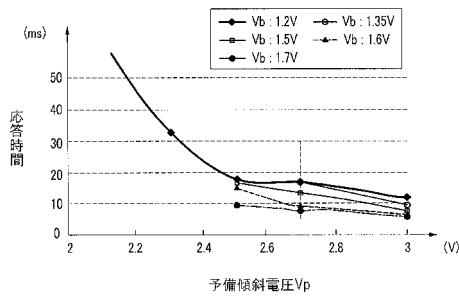

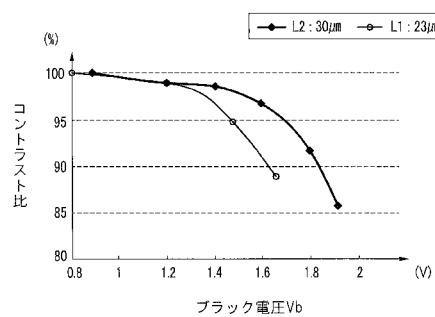

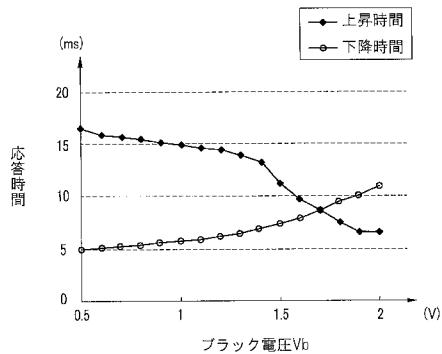

図13は本発明の一つの実施例による液晶表示装置において、各副領域に含まれる電極部の幅、及び予備傾斜電圧ごとに液晶の応答速度を示したグラフである。図14は本発明の一つの実施例による液晶表示装置において、ブラック電圧及び予備傾斜電圧ごとに液晶の応答速度を示したグラフである。図15は本発明の一つの実施例による液晶表示装置において、各副領域に含まれる電極部の幅及びブラック電圧ごとにコントラスト比を示したグラフである。図16は本発明の一つの実施例による液晶表示装置において、ブラック電圧ごとに液晶の応答速度を示したグラフである。図13及び図14のグラフにおいて、横

50

軸は予備傾斜電圧  $V_p$  を示し、縦軸は液晶の応答速度として上昇時間を示す。ここで、上昇時間は、「入力映像信号の示す階調がブラック階調からホワイト階調に変わる場合、画素の光透過率がホワイト階調に対応する目標光透過率の10%に達した時点から90%になる時点までの時間」を言う。尚、「入力映像信号の示す階調がホワイト階調からブラック階調に変わる場合、画素の光透過率がホワイト階調に対応する目標光透過率の90%に達した時点から10%になる時点までの時間」は下降時間と呼ばれる。図15のグラフでは、横軸はブラック電圧  $V_b$  を示し、縦軸はコントラスト比を示す。図16のグラフでは、横軸はブラック電圧  $V_b$  を示し、縦軸は液晶の応答速度を示す。

#### 【0070】

図13では、曲線C1が、副領域SA2を覆い、かつ副領域SA1の電極部の幅L1を23  $\mu m$ とした上で、予備傾斜電圧  $V_p$  を変化させながら、それぞれの印加時に測定された上昇時間をプロットしたものである。曲線C2、C3、C4はそれぞれ、副領域SA1を覆い、かつ副領域SA2の電極部の幅L2を30  $\mu m$ 、35  $\mu m$ 、40  $\mu m$ とした上で、予備傾斜電圧  $V_p$  を変化させながら、それぞれの印加時に測定された上昇時間をプロットしたものである。ここで、ブラック電圧  $V_b$  を1.2Vとし、ホワイト電圧  $V_w$  を7.0Vとする一方、オーバーシュート電圧  $V_o$  を適用していない。曲線C1と曲線C2とはほとんど一致しているので、電極部の幅L1、L2の変化は液晶の応答速度には変化を与えない。特に、電極部の幅L2が30  $\mu m$ である副領域SA2と、電極部の幅L1が23  $\mu m$ である副領域SA1とは、同様な液晶制御力を有する。この時、予備傾斜電圧  $V_p$  を2.5Vにすれば、上昇時間は10ms以下となる。しかし、曲線C3と曲線C4とから分かるように、測定に使用された予備傾斜電圧  $V_p$  の範囲では、電極部の幅L2が大きいほど、液晶の応答速度が全体的に低下した。従って、さらに高い予備傾斜電圧  $V_p$  を印加しなければ液晶の応答速度は更に高くならない。一方、画素の光透過率を更に上昇させるためには、各副領域に含まれる電極部の幅を更に広くする必要がある。また、液晶表示装置が大型化するほど、電極部の幅はさらに広くなる。例えば40インチの画面の場合、平均的な電極部の幅がほぼ42  $\mu m$ になる。したがって、電極部の幅が大きい液晶表示装置では、高い予備傾斜電圧  $V_p$  を使用しなければ液晶の応答速度を十分に高くできない。しかし、高過ぎる予備傾斜電圧  $V_p$  は画素の光透過率の歪曲を招いて動画表示での画質を悪くすることがある。したがって、予備傾斜電圧  $V_p$  を適度に高め、かつ液晶の応答速度を高くする必要がある。

#### 【0071】

図14では、各曲線が、ブラック電圧  $V_b$  のレベルを変化させながら測定された液晶の応答速度をプロットしたものである。図14に示されている通り、ブラック電圧  $V_b$  のレベルが高いほど応答速度が高い。特に、ブラック電圧  $V_b$  が1.6V以上であれば、予備傾斜電圧  $V_p$  が2.7Vである場合、上昇時間が10  $\mu m$ 以下となる。ここで、副領域SA2に含まれる電極部の幅L2は40  $\mu m$ とした。このように、ブラック電圧  $V_b$  のレベルを高めれば、各副領域SA1、SA2で液晶制御力が大きくなるので、液晶の応答速度が高くなる。しかし、ブラック電圧  $V_b$  が高くなれば、コントラスト比が低くなるので、下降時間が長くなることがある。したがって、高いブラック電圧  $V_b$  を使用しながら、コントラスト比の低下を抑え、下降時間の延長を防止する必要がある。

#### 【0072】

図15では、二つの曲線の各々が、各副領域に含まれる電極部ごとに測定された、ブラック電圧とコントラスト比との間の関係をプロットしたものである。図15に示されている通り、電極部の幅が大きいほど、ブラック電圧の上昇に伴うコントラスト比の低下が抑えられる。例えば、電極部の幅L1が23  $\mu m$ である場合、ブラック電圧  $V_b$  が1.6Vであるときのコントラスト比が、ブラック電圧  $V_b$  が1Vであるときのコントラスト比の約90%程度である。一方、電極部の幅L2が30  $\mu m$ である場合、前者のコントラスト比が後者のコントラスト比の約96%となる。ブラック電圧  $V_b$  が印加される時、電極部の幅が大きいほど、副領域の中央部ではほとんど横にならない液晶分子の割合が増えるので、大きく傾いた液晶分子を通じた光漏れが減ってコントラスト比の低下が抑えられる。また、電極部の幅が大きいほど、それに隣接する画素電極の開口部（切開部）の面積が相対的に減少するので、開口部を通じた光漏れが減ってコントラスト比の低下が抑えられる。

10

20

30

40

50

## 【0073】

図16では、ブラック電圧 $V_b$ ごとに測定された上昇時間と下降時間とをプロットしたものである。図16に示されている通り、ブラック電圧 $V_b$ が高いほど上昇時間は短く、下降時間は長い。ここで、図16に示されている下降時間の測定では、アンダーシュート電圧 $V_u$ を適用していない。一方、0.5V～1.2Vの範囲に収まるアンダーシュート電圧 $V_u$ を適用した上で、ブラック電圧 $V_b$ を1.5V～2.0Vの範囲で変化させながら下降時間を測定した結果では、下降時間がほぼ6ms程度を示した。結論として、ブラック電圧 $V_b$ を高めてもアンダーシュート電圧 $V_u$ を適用すれば、下降時間の延長を防止できる。

## 【0074】

以上の測定結果を整理すれば、副領域SA1に含まれる電極部の幅 $L1$ が20μm～30μmであり、かつ副領域SA2に含まれる電極部の幅 $L2$ が30μm以上である場合、ホワイト電圧 $V_w$ が7.0Vである時、ブラック電圧 $V_b$ を1.5V～2.0Vにし、予備傾斜電圧 $V_p$ を2.5V～3.0Vにし、更に、アンダーシュート電圧 $V_u$ を0.5V～1.2Vにすれば、画質を低下させることなく、液晶の応答速度を更に高めることができる。尚、上記の数値は一例に過ぎず、液晶表示装置の特性によって変わり得る。本発明の上記の実施例による映像信号補正は、図3A～図8に示した液晶表示パネルアセンブリだけでなく、画素電極の模様がほぼ長方形である場合にも同一に適用できる。

以上、本発明の好ましい実施例について詳細に説明した。しかし、本発明の技術的範囲は上記の実施例には限定されない。特許請求の範囲で定義されている本発明の基本概念を利用した当業者の多様な変形及び改良もまた、本発明の技術的範囲に属すると解されるべきである。

## 【図面の簡単な説明】

## 【0075】

【図1】本発明の一つの実施例による液晶表示装置のブロック図である。

【図2】図1に示されている液晶表示装置に含まれる一つの画素の構造と等価回路とを示す模式図である。

【図3A】本発明の一つの実施例による液晶表示装置の画素電極を構成する一部分を示す平面図である。

【図3B】本発明の一つの実施例による液晶表示装置の画素電極を構成する別の一部分を示す平面図である。

【図3C】図3Aに示されている一部分と図3Bに示されている別の一部分とを連結して得られる、画素電極の基本構成部分を示す平面図である。

【図4】本発明の一つの実施例による液晶表示パネルアセンブリの画素電極と共通電極の切開部との配置を示す平面図である。

【図5】本発明の一つの実施例による液晶表示パネルアセンブリの薄膜トランジスタ表示パネルの平面図である。

【図6】本発明の一つの実施例による液晶表示パネルアセンブリの共通電極表示パネルの平面図である。

【図7】図5に示した薄膜トランジスタ表示パネルと図6に示した共通電極表示パネルとを重ねたときの液晶表示パネルアセンブリの平面図である。

【図8】図7の液晶表示装置を折れ線VIII-VIIIに沿って切断した断面の展開図である。

【図9】本発明の一つの実施例による液晶表示装置の映像信号補正部のブロック図である。

【図10】図9に示した映像信号補正部の動作を示す流れ図の一例である。

【図11】本発明の一つの実施例による第1補正部により記憶されたルックアップテーブルの構成を模式的に示す図である。

【図12A】本発明の一つの実施例によって補正された画素電圧のフレームごとの変化を示す波形図である。

【図12B】本発明の別の実施例によって補正された画素電圧のフレームごとの変化を示す波形図である。

10

20

30

40

50

【図13】本発明の一つの実施例による液晶表示装置において、副領域に含まれる電極部の幅ごとに、予備傾斜電圧の変化に伴う液晶の応答速度の変化を示したグラフである。

【図14】本発明の一つの実施例による液晶表示装置において、ブラック電圧ごとに予備傾斜電圧の変化に伴う液晶の応答速度の変化を示したグラフである。

【図15】本発明の一つの実施例による液晶表示装置において、副領域に含まれる電極部の幅ごとに、ブラック電圧の変化に伴うコントラスト比の変化を示したグラフである。

【図16】本発明の一つの実施例による液晶表示装置において、ブラック電圧の変化に伴う液晶の応答速度の変化を示したグラフである。

【符号の説明】

【0076】

10

3 液晶層

12、22 偏光子

60o、176 屈曲部

60t1 中央横部

60t2 縦断横部

61、62、71、72、73、90、91、92、93 切開部

61o、62o 斜線部

81、82 接触補助部材

100 薄膜トランジスタ表示パネル

110 絶縁基板

20

121 ゲート線

124 ゲート電極

129 端部

131 維持電極線

137 維持電極

140 ゲート絶縁膜

154、156、157 島形半導体

163、165、166、167 抵抗性接触部材

171 データ線

30

173 ソース電極

175 ドレイン電極

177 拡張部

180 保護膜

182、185 接触孔

191 画素電極

191a 第1電極部

191b 第2電極部

196、197 電極片

196o、197o 斜辺

196t、197t 横辺

40

198 基本電極

198o1 凸辺

198o2 凹辺

200 共通電極表示パネル

210 基板

220 遮光部材

230 色フィルター

250 蓋膜

270 共通電極

300 液晶表示パネルアセンブリ

50

|                                 |             |    |

|---------------------------------|-------------|----|

| 400                             | ゲート駆動部      |    |

| 500                             | データ駆動部      |    |

| 600                             | 信号制御部       |    |

| 610                             | 映像信号補正部     |    |

| 620                             | 第1メモリ       |    |

| 630                             | 第2メモリ       |    |

| 640                             | 第1補正部       |    |

| 650                             | 第2補正部       |    |

| 800                             | 階調電圧生成部     |    |

| C1c                             | 液晶キャパシタ     | 10 |

| CONT1                           | ゲート制御信号     |    |

| CONT2                           | データ制御信号     |    |

| Cst                             | ストレージキャパシタ  |    |

| CV                              | 凹頂点         |    |

| DAT                             | デジタル映像信号    |    |

| DE                              | データインターブル信号 |    |

| D <sub>1</sub> ~ D <sub>m</sub> | データ線        |    |

| G <sub>1</sub> ~ G <sub>n</sub> | ゲート線        |    |

| Hsync                           | 水平同期信号      |    |

| L1, L2                          | 電極部の幅       | 20 |

| PX                              | 画素          |    |

| Q                               | スイッチング素子    |    |

| S1, S2, SA1, SA2                | 副領域         |    |

| V <sub>b</sub>                  | ブラック電圧      |    |

| V <sub>p</sub>                  | 予備傾斜電圧      |    |

| V <sub>o</sub>                  | オーバーシュート電圧  |    |

| V <sub>w</sub>                  | ホワイト電圧      |    |

| VV                              | 凸頂点         |    |

【図1】

【図2】

【図3 B】

【図3 C】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12A】

【図12B】

【図13】

【図14】

【図15】

【図16】

## フロントページの続き

| (51)Int.Cl. | F I     | テーマコード(参考)   |

|-------------|---------|--------------|

|             | G 0 9 G | 3/20 6 1 2 R |

|             | G 0 9 G | 3/20 6 2 3 A |

|             | G 0 9 G | 3/20 6 8 0 H |

|             | G 0 9 G | 3/20 6 4 1 C |

|             | G 0 9 G | 3/20 6 2 1 F |

|             | G 0 9 G | 3/20 6 3 2 F |

(72)発明者 嚴允成

大韓民国京畿道龍仁市上 ヒョン 洞サンヒョンマウル雙龍アパート216棟1702号

(72)発明者 柳承厚

大韓民国京畿道城南市盆唐区藪内洞ロイヤルパレスハウスビルビー棟1202号

(72)発明者 金賢ウック

大韓民国京畿道龍仁市器興区農書洞山24番地

(72)発明者 都熙旭

大韓民国京畿道水原市八達区仁溪洞1007-5番地1階

(72)発明者 金康佑

大韓民国ソウル市江南区道谷洞941-8番地503号

F ターム(参考) 2H092 GA12 GA14 GA29 JA26 JA36 JA46 JB05 JB13 JB24 JB32

JB61 JB69 KA04 KA05 KA12 KB04 MA27 NA01 NA05 PA06

2H093 NA16 NA53 NC13 NC29 NC34 NC52 ND03 ND04 ND06 ND33

NE03

5C006 AA16 AC01 AC21 AF03 AF04 AF44 AF45 AF46 AF50 BB16

BC06 BC16 BF02 FA12

5C080 AA10 BB05 DD08 EE29 FF11 GG15 GG17 JJ02 JJ04 JJ05

JJ06 JJ07