(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-189190

(P2016-189190A)

(43) 公開日 平成28年11月4日(2016.11.4)

(51) Int.Cl.

**G06F 3/041** (2006.01)

**H01L 21/336** (2006.01)

**H01L 29/786** (2006.01)

**G02F 1/1333** (2006.01)

**G06F 3/044** (2006.01)

F 1

G06F 3/041

H01L 29/786

G02F 1/1333

G06F 3/044

テーマコード(参考)

2H189

5F110

審査請求 未請求 請求項の数 6 O L (全 91 頁)

(21) 出願番号 特願2016-58073 (P2016-58073)

(22) 出願日 平成28年3月23日 (2016.3.23)

(31) 優先権主張番号 特願2015-66887 (P2015-66887)

(32) 優先日 平成27年3月27日 (2015.3.27)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2015-81398 (P2015-81398)

(32) 優先日 平成27年4月13日 (2015.4.13)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 2H189 JA14 LA03 LA10 LA28 LA31

最終頁に続く

(54) 【発明の名称】タッチパネル

## (57) 【要約】

【課題】厚さの薄いタッチパネルを提供する。または、構成が簡素化したタッチパネルを提供する。または、電子機器に組み込みやすいタッチパネルを提供する。

【解決手段】第1の基板と、第2の基板と、第1の導電層と、第2の導電層と、第3の導電層と、第4の導電層と、液晶と、FPCと、を備えるタッチパネルとする。第1の導電層は、画素電極としての機能を有する。第2の導電層は、共通電極としての機能を有する。第3の導電層及び第4の導電層は、タッチセンサの電極としての機能を有する。FPCは第4の導電層と電気的に接続する。第1の導電層、第2の導電層、第3の導電層、第4の導電層、及び液晶は、第1の基板と第2の基板の間に位置し、第1の導電層、第2の導電層、及び第3の導電層は、第1の基板に設けられ、FPCが第1の基板に設けられている。

【選択図】図7

**【特許請求の範囲】****【請求項 1】**

第1の基板と、第2の基板と、第1の導電層と、第2の導電層と、第3の導電層と、第4の導電層と、液晶と、FPCと、を備えるタッチパネルであって、

前記第1の導電層は、画素電極としての機能を有し、

前記第2の導電層は、共通電極としての機能を有し、

前記第3の導電層及び前記第4の導電層は、タッチセンサの電極としての機能を有し、

前記FPCは前記第4の導電層と電気的に接続し、

前記第1の導電層、前記第2の導電層、前記第3の導電層、前記第4の導電層、及び前記液晶は、前記第1の基板と前記第2の基板の間に位置し、

前記第1の導電層、前記第2の導電層、及び前記第3の導電層は、前記第1の基板に設けられ、

前記FPCが前記第1の基板に設けられた、

タッチパネル。

**【請求項 2】**

請求項1において、

第5の導電層と、接続体と、を有し、

前記第5の導電層は前記第1の基板に設けられ、

前記第4の導電層は、前記第2の基板に設けられ、

前記第5の導電層と前記第4の導電層とは、前記接続体を介して電気的に接続する、

タッチパネル。

**【請求項 3】**

請求項1において、

前記第4の導電層は前記第1の基板に設けられ、

前記第3の導電層及び前記第4の導電層のいずれか一方が、前記第2の導電層と同一面上に設けられた、

タッチパネル。

**【請求項 4】**

請求項1において、

前記第4の導電層は前記第1の基板に設けられ、

前記第3の導電層は、前記第1の導電層または前記第2の導電層と同一面上に設けられ、

前記第4の導電層は、前記第1の導電層または前記第2の導電層と同一面上に設けられた、

タッチパネル。

**【請求項 5】**

請求項1において、

前記第4の導電層は前記第1の基板に設けられ、

前記第2の導電層が、前記第3の導電層または前記第4の導電層のいずれか一方と一体に設けられた、

タッチパネル。

**【請求項 6】**

請求項1において、

前記第4の導電層は前記第1の基板に設けられ、

前記第1の導電層が、前記第3の導電層または前記第4の導電層のいずれか一方と一体に設けられた、

タッチパネル。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の一態様は、入力装置に関する。本発明の一態様は、表示装置に関する。本発明の一態様は、入出力装置に関する。本発明の一態様は、タッチパネルに関する。

#### 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様は、物、方法、又は、製造方法に関する。本発明の一態様は、プロセス、マシン、マニュファクチャ、又は、組成物（コンポジション・オブ・マター）に関する。そのため、より具体的に本明細書等で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、電子機器、照明装置、入力装置、入出力装置、それらの駆動方法、又は、それらの製造方法、を一例として挙げることができる。

#### 【0003】

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、入力装置、入出力装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、半導体装置を有している場合がある。

10

#### 【背景技術】

#### 【0004】

近年、位置入力手段としてタッチセンサを搭載した表示装置（または表示モジュール）が実用化されている。タッチセンサを搭載した表示装置（または表示モジュール）は、タッチパネル、またはタッチスクリーンなどと呼ばれている（以下、これを単に「タッチパネル」とも呼ぶ）。なお、表示装置を有しておらず、タッチセンサのみで構成されている部材に対して、そのような部材のことをタッチパネルと呼ぶ場合もある。または、タッチセンサを搭載した表示装置は、タッチセンサ付表示装置、表示装置付タッチパネル、または、表示モジュール、などとも呼ばれる場合がある。また、表示装置の内部にタッチセンサが組み込まれている場合には、インセル型タッチセンサ（またはインセル型タッチセンサ付表示装置）、または、オンセル型タッチセンサ（またはオンセル型タッチセンサ付表示装置）などとも呼ばれる場合がある。インセル型タッチセンサは、例えば、液晶素子で用いられる電極をタッチセンサ用の電極としても用いているものである。一方、オンセル型タッチセンサは、例えば、対向基板の上側（表示素子が設けられていない面側）に、タッチセンサ用の電極が形成されているものである。例えば、これらのタッチパネルなどを備える携帯情報端末としては、スマートフォン、タブレット端末などがある。

20

#### 【0005】

表示装置の一つとして、液晶素子を備える液晶表示装置がある。例えば、画素電極をマトリクス状に配置し、画素電極の各々に接続するスイッチング素子としてトランジスタを用いたアクティブマトリクス型液晶表示装置が注目を集めている。

30

#### 【0006】

例えば、画素電極の各々に接続するスイッチング素子として、金属酸化物をチャネル形成領域とするトランジスタを用いるアクティブマトリクス型液晶表示装置が知られている（特許文献1及び特許文献2）。

40

#### 【0007】

また特許文献3乃至6には、液晶素子が適用されたタッチパネルが記載されている。

#### 【0008】

液晶表示装置には大きく分けて透過型と反射型の二種類のタイプが知られている。

#### 【0009】

透過型の液晶表示装置は、冷陰極蛍光ランプやLEDなどのバックライトを用い、液晶の光学変調作用を利用して、バックライトからの光が液晶を透過して液晶表示装置外部に出力される状態と、出力されない状態とを選択し、明と暗の表示を行わせ、さらにそれらを組み合わせることで、画像表示を行うものである。

#### 【0010】

また、反射型の液晶表示装置は、液晶の光学変調作用を利用して、外光、即ち入射光が

50

画素電極で反射して装置外部に出力される状態と、入射光が装置外部に出力されない状態とを選択し、明と暗の表示を行わせ、さらにそれらを組み合わせることで、画像表示を行うものである。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【特許文献3】特開2011-197685号公報

【特許文献4】特開2014-44537号公報

10

【特許文献5】特開2014-178847号公報

【特許文献6】米国特許第7920129号明細書

【発明の概要】

【発明が解決しようとする課題】

【0012】

表示パネル（表示装置、または、表示モジュール）に、ユーザーインターフェースとして画面に指やスタイルス等で触れることで入力する機能を付加したタッチパネルが望まれている。

【0013】

また、タッチパネルが適用された電子機器の薄型化、軽量化が求められている。そのため、タッチパネル自体の薄型化、軽量化が求められている。

20

【0014】

例えば、タッチパネルは、表示パネルの視認側（表示面側）、つまり、人の指やペンが触る側にタッチセンサを設ける構成とすることができます。

【0015】

例えばタッチパネル（または表示モジュール）の構成として、表示パネルの表示面側にタッチセンサを有する基板を貼り付ける構成とすることができる。つまり、タッチパネル（または表示モジュール）の構成として、表示パネルとタッチセンサとが別々の部品として構成されており、表示パネルとタッチセンサと貼り合わせるような構成とすることができる。しかしながら、このような構成の場合、表示パネル用の基板とは別に、タッチセンサ用の基板が必要であるため、タッチパネル（または表示モジュール）の厚さを薄くできない、部品点数が多くなる、などの問題があった。

30

【0016】

本発明の一態様は、厚さの薄いタッチパネル（またはタッチセンサ付表示装置）などを提供することを課題の一とする。または、構成が簡素化したタッチパネル（またはタッチセンサ付表示装置）などを提供することを課題の一とする。または、電子機器に組み込みやすいタッチパネル（またはタッチセンサ付表示装置）などを提供することを課題の一とする。または、部品点数の少ないタッチパネル（またはタッチセンサ付表示装置）などを提供することを課題の一とする。または、軽量なタッチパネル（またはタッチセンサ付表示装置）などを提供することを課題の一とする。

40

【0017】

または、新規な入力装置を提供することを課題の一とする。または、新規な入出力装置を提供することを課題の一とする。または、新規な表示装置を提供することを課題の一とする。なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの課題の全てを解決する必要はない。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0018】

本発明の一態様は、第1の基板と、第2の基板と、第1の導電層と、第2の導電層と、

50

第3の導電層と、第4の導電層と、液晶と、FPCと、を備えるタッチパネルである。第1の導電層は、画素電極としての機能を有する。第2の導電層は、共通電極としての機能を有する。第3の導電層及び第4の導電層は、タッチセンサの電極としての機能を有する。FPCは第4の導電層と電気的に接続する。第1の導電層、第2の導電層、第3の導電層、第4の導電層、及び液晶は、第1の基板と第2の基板の間に位置し、第1の導電層、第2の導電層、及び第3の導電層は、第1の基板に設けられ、FPCが第1の基板に設けられている。

#### 【0019】

また、上記において、第5の導電層と、接続体と、を有し、第5の導電層は第1の基板に設けられ、第4の導電層は、第2の基板に設けられ、第5の導電層と第4の導電層とは、接続体を介して電気的に接続する構成とすることが好ましい。10

#### 【0020】

または、第4の導電層は第1の基板に設けられていることが好ましい。

#### 【0021】

このとき、第3の導電層及び第4の導電層のいずれか一方が、第2の導電層と同一面上に設けられていることが好ましい。

#### 【0022】

または、第3の導電層は、第1の導電層または第2の導電層と同一面上に設けられ、第4の導電層は、第1の導電層または第2の導電層と同一面上に設けられていることが好ましい。20

#### 【0023】

または、第2の導電層が、第3の導電層または第4の導電層のいずれか一方と一体に設けられていることが好ましい。

#### 【0024】

または、第1の導電層が、第3の導電層または第4の導電層のいずれか一方と一体に設けられていることが好ましい。

#### 【発明の効果】

#### 【0025】

本発明の一態様によれば、厚さの薄いタッチパネル（またはタッチセンサ付表示装置）などを提供できる。または、構成が簡素化したタッチパネル（またはタッチセンサ付表示装置）などを提供できる。または、電子機器に組み込みやすいタッチパネル（またはタッチセンサ付表示装置）などを提供できる。または、部品点数の少ないタッチパネル（またはタッチセンサ付表示装置）などを提供できる。または、軽量なタッチパネル（またはタッチセンサ付表示装置）などを提供できる。または、新規な入力装置を提供できる。または、新規な入出力装置を提供できる。または、新規な表示装置を提供できる。なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。30

#### 【図面の簡単な説明】

#### 【0026】

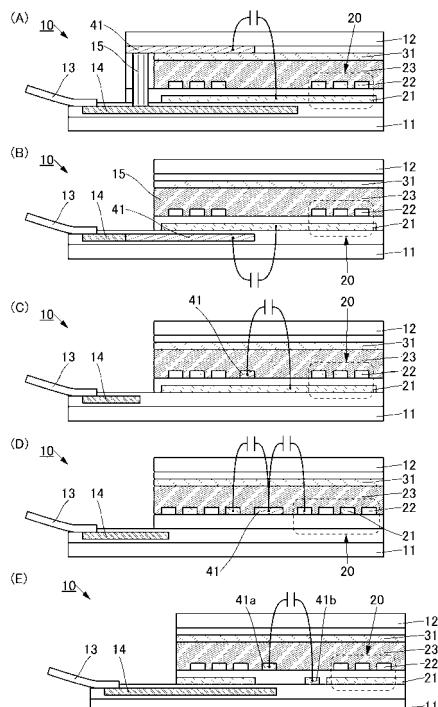

【図1】実施の形態に係る、タッチセンサのブロック図及びタイミングチャート図。

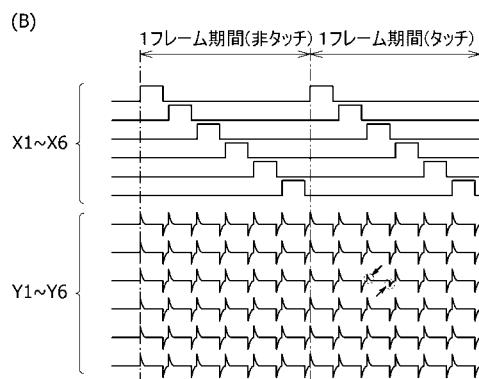

【図2】実施の形態に係る、タッチセンサを備える画素を説明する図。

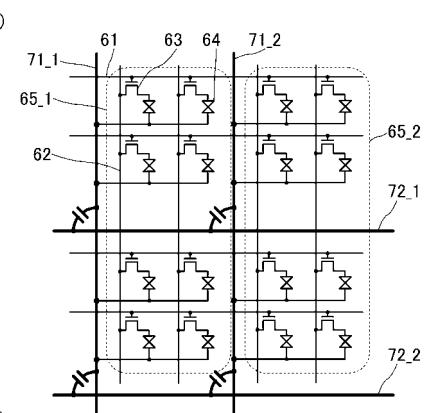

【図3】実施の形態に係る、タッチセンサを備える画素を説明する図。

【図4】実施の形態に係る、タッチセンサを備える画素を説明する図。

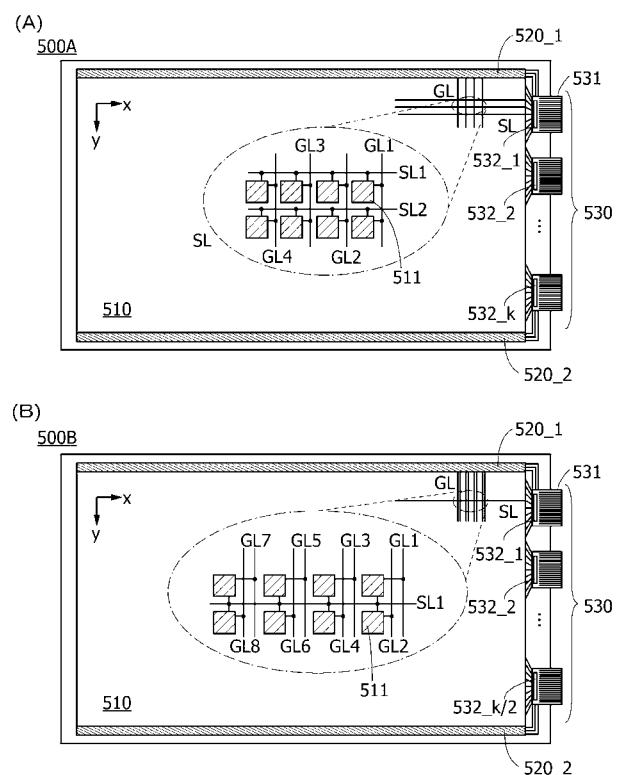

【図5】実施の形態に係る、タッチセンサを備える画素を説明する図。

【図6】実施の形態に係る、タッチセンサ及び画素の動作を説明する図。

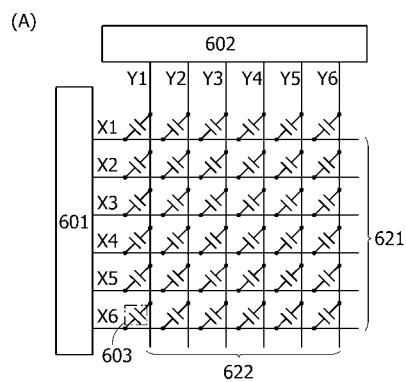

【図7】実施の形態に係る、タッチパネルの構成例。

【図8】実施の形態に係る、タッチパネルの構成例。

【図9】実施の形態に係る、タッチパネルの構成例。

10

20

30

40

50

- 【図 6 0】実施の形態に係る、タッチパネルの構成例。

【図 6 1】実施の形態に係る、タッチパネルの構成例。

【図 6 2】実施の形態に係る、タッチパネルの構成例。

【図 6 3】実施の形態に係る、タッチパネルの構成例。

【図 6 4】実施の形態に係る、タッチパネルの構成例。

【図 6 5】実施の形態に係る、タッチパネルの構成例。

【図 6 6】実施の形態に係る、タッチパネルの構成例。

【図 6 7】実施の形態に係る、タッチパネルの構成例。

【図 6 8】実施の形態に係る、タッチパネルの構成例。

【図 6 9】実施の形態に係る、タッチパネルの構成例。

【図 7 0】実施の形態に係る、タッチパネルの構成例。

【図 7 1】実施の形態に係る、タッチパネルの構成例。

【図 7 2】実施の形態に係る、タッチパネルの構成例。

【図 7 3】実施の形態に係る、タッチパネルの構成例。

【図 7 4】実施の形態に係る、タッチパネルの構成例。

【図 7 5】実施の形態に係る、タッチパネルの構成例。

【図 7 6】実施の形態に係る、タッチパネルの構成例。

【図 7 7】実施の形態に係る、タッチパネルの構成例。

【図 7 8】実施の形態に係る、タッチパネルの構成例。

【図 7 9】実施の形態に係る、タッチパネルの構成例。

【図 8 0】表示装置の一例を説明するための模式図。

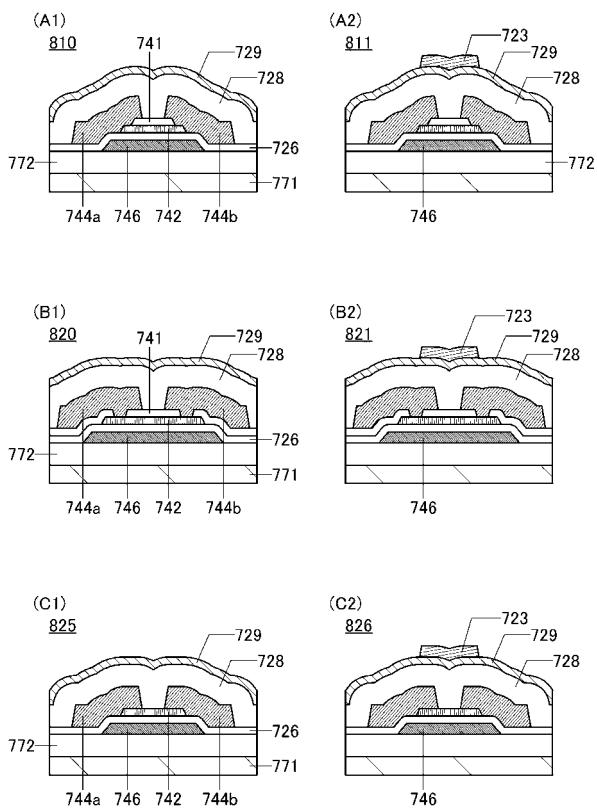

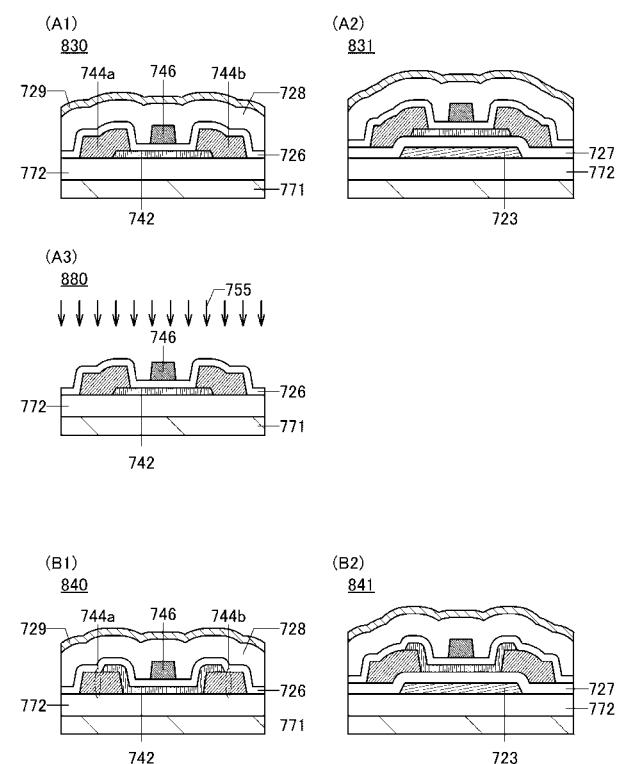

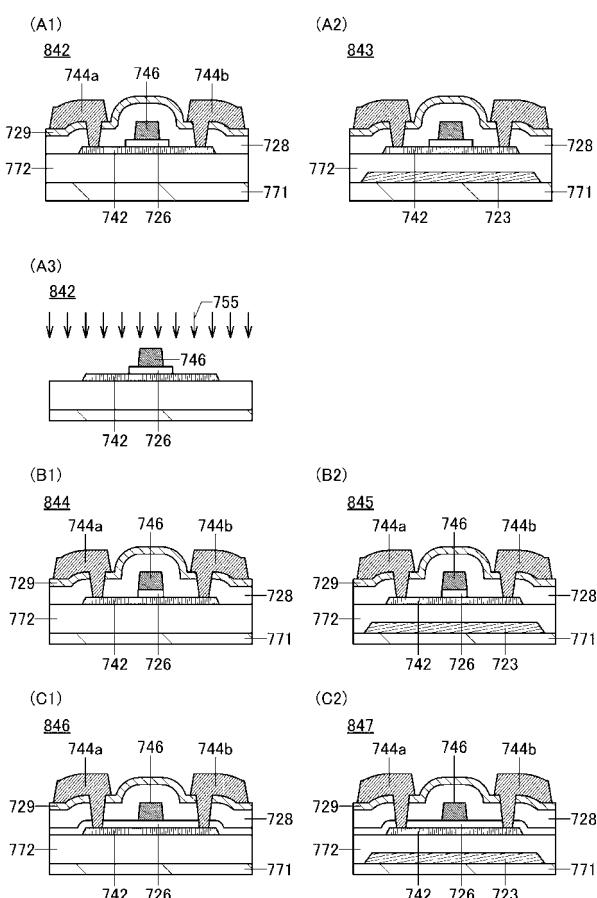

【図 8 1】トランジスタの一形態を説明する断面図。

【図 8 2】トランジスタの一形態を説明する断面図。

【図 8 3】トランジスタの一形態を説明する断面図。

【図 8 4】トランジスタの一形態を説明する平面図および断面図。

【図 8 5】トランジスタの一形態を説明する平面図および断面図。

【図 8 6】トランジスタの一形態を説明する平面図および断面図。

【図 8 7】トランジスタの一形態を説明する平面図および断面図。

【図 8 8】トランジスタの一形態を説明する平面図および断面図。

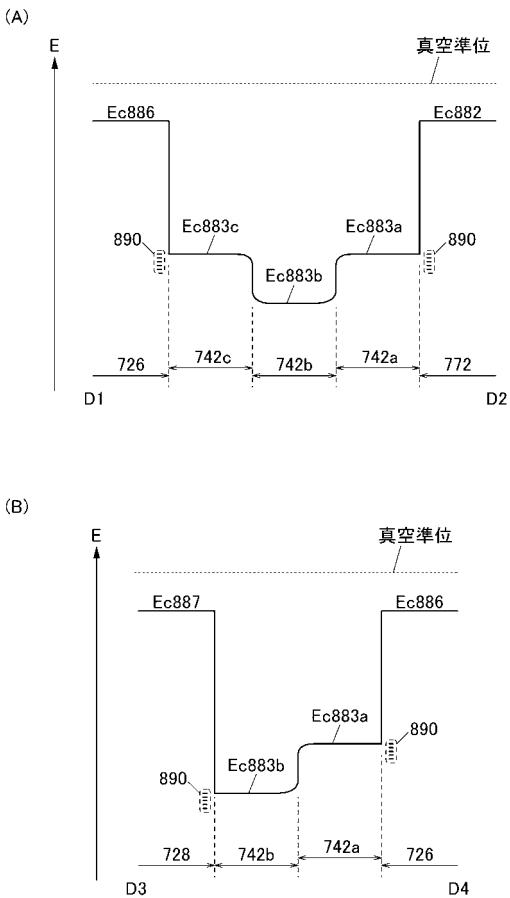

【図 8 9】エネルギーバンド構造を説明する図。

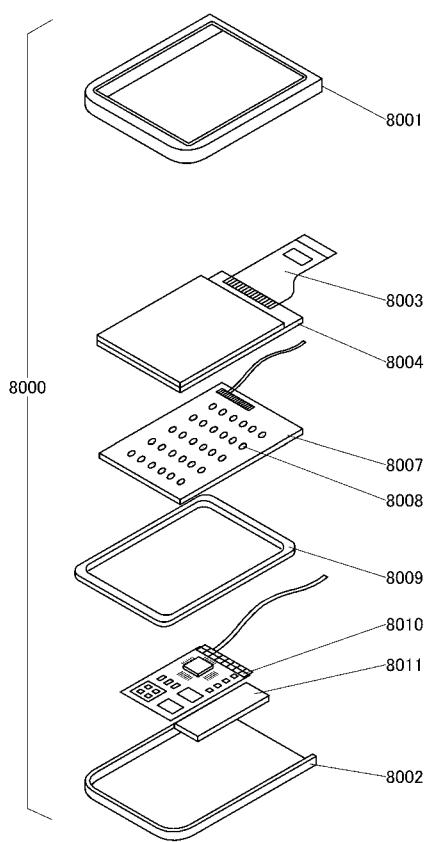

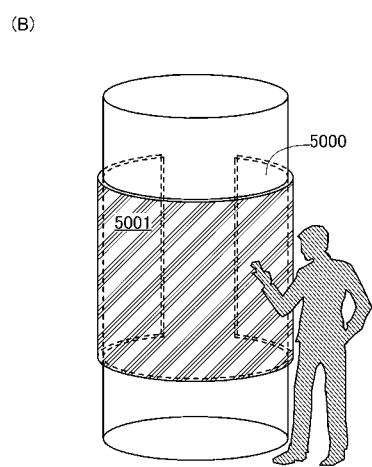

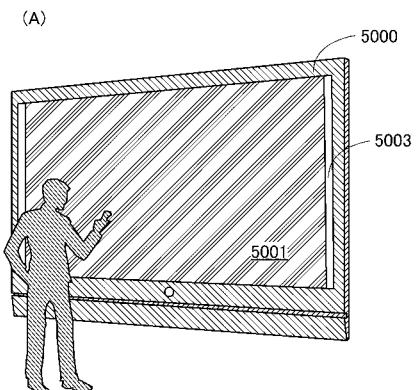

【図 9 0】実施の形態に係る表示モジュールを説明する図。

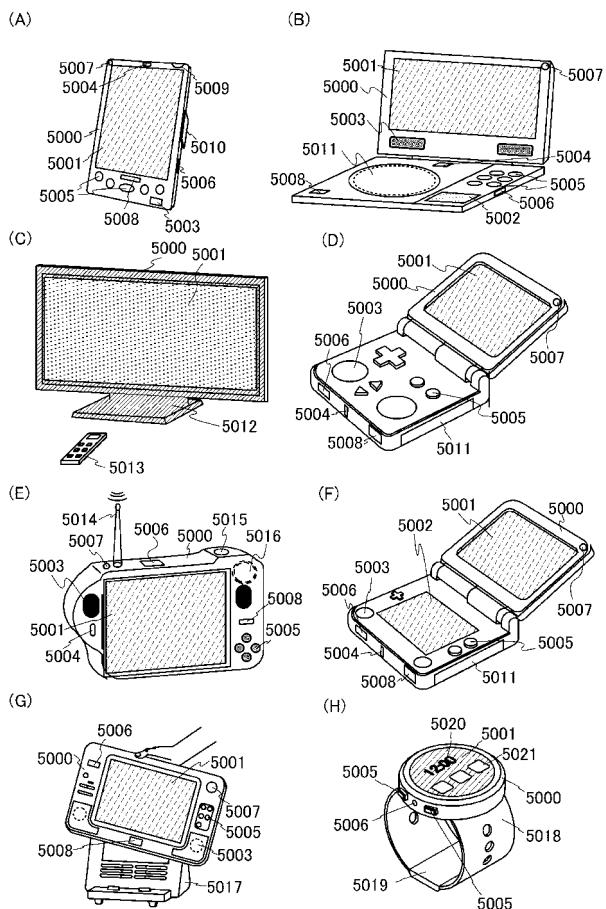

【図 9 1】実施の形態に係る電子機器を説明する図。

【図 9 2】実施の形態に係る電子機器を説明する図。

【発明を実施するための形態】

【0027】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0028】

なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0029】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0030】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

10

20

30

40

50

## 【0031】

なお、「膜」という言葉と、「層」という言葉とは、互いに入れ替えることが可能である場合がある。例えば、「導電層」という用語を、「導電膜」という用語に変更することや、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

## 【0032】

## (実施の形態1)

本実施の形態では、本発明の一様の入力装置または入出力装置の駆動方法、モード、及び構成例について図面を参照して説明する。

## 【0033】

10

## [センサの検知方法の例]

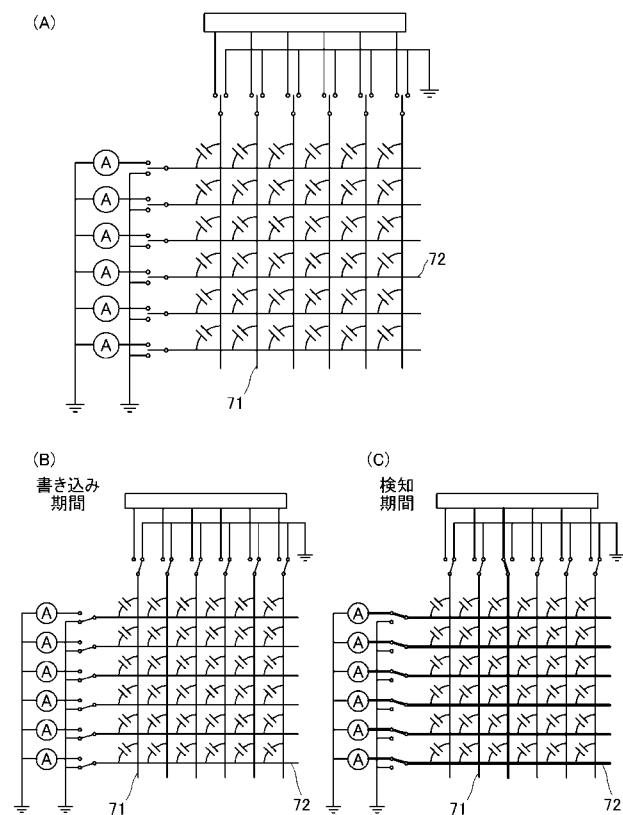

図1(A)は、相互容量方式のタッチセンサの構成を示すブロック図である。図1(A)では、パルス電圧出力回路601、電流検知回路602を示している。なお図1(A)では、一例として、パルス電圧が与えられる電極621、電流の変化を検知する電極622をそれぞれ、X1-X6、Y1-Y6のそれぞれ6本の配線として示している。なお、電極の数は、これに限定されない。また図1(A)は、電極621および電極622が重畳すること、または、電極621および電極622が近接して配置されることで形成される容量603を図示している。なお、電極621と電極622とはその機能を互いに置き換えてよい。

## 【0034】

20

パルス電圧出力回路601は、一例としては、X1-X6の配線に順にパルス電圧を印加するための回路である。X1-X6の配線にパルス電圧が印加されることで、容量603を形成する電極621および電極622の間では、電界が生じる。そして、パルス電圧により、容量603に電流が流れる。この電極間に生じる電界が、指やペンなどのタッチによる遮蔽等により変化する。つまり、指やペンなどのタッチなどにより、容量603の容量値が変化する。このように、指やペンなどのタッチなどにより、容量値に変化を生じさせることを利用して、被検知体の接近、または接触を検出することができる。

## 【0035】

30

電流検知回路602は、容量603の容量値の変化による、Y1-Y6の配線での電流の変化を検知するための回路である。Y1-Y6の配線では、被検知体の接近、または接触がないと検知される電流値に変化はないが、検出する被検知体の接近、または接触により容量値が減少する場合には電流値が減少する変化を検知する。なお電流の検知は、電流量の総和を検知してもよい。その場合には、積分回路等を用いて検知を行えばよい。または、電流のピーク値を検知してもよい。その場合には、電流を電圧に変換して、電圧値のピーク値を検知してもよい。

## 【0036】

次いで図1(B)には、図1(A)で示す相互容量方式のタッチセンサにおける入出力波形のタイミングチャートを示す。図1(B)では、1フレーム期間で各行列での被検知体の検出を行うものとする。また図1(B)では、被検知体を検出しない場合(非タッチ)と被検知体を検出する場合(タッチ)との2つの場合について示している。なおY1-Y6の配線については、検知される電流値に対応する電圧値とした波形を示している。なお、表示パネルにおいても、表示動作が行われている。この表示動作のタイミングと、タッチセンサのタイミングとは、同期させて動作することが望ましい。なお、図1(B)では、表示動作とは同期させていない場合の例を示す。

40

## 【0037】

X1-X6の配線には、順にパルス電圧が与えられ、該パルス電圧にしたがってY1-Y6の配線での波形が変化する。被検知体の接近または接触がない場合には、X1-X6の配線の電圧の変化に応じてY1-Y6の波形が一様に変化する。一方、被検知体が接近または接触する箇所では、電流値が減少するため、これに対応する電圧値の波形も変化する。

50

## 【0038】

このように、容量値の変化を検知することにより、被検知体の接近または接触を検出することができる。なお、指やペンなどの被検知体は、タッチセンサやタッチパネルに接触せず、接近した場合でも、信号が検知される場合がある。

## 【0039】

またパルス電圧出力回路601及び電流検知回路602は、一例としては、1個のICチップの中に、形成されていることが望ましい。そして、そのICチップは、例えば、タッチパネルに実装されること、若しくは電子機器の筐体内の基板に実装されることが好ましい。また可撓性を有するタッチパネルとする場合には、曲げた部分では寄生容量が増大し、ノイズの影響が大きくなってしまう恐れがあるため、ノイズの影響を受けにくい駆動方法が適用されたICチップを用いることが好ましい。例えばシグナル・ノイズ比(S/N比)を高める駆動方法が適用されたICチップを用いることが好ましい。

10

## 【0040】

また、図1(A)ではタッチセンサとして配線の交差部に容量603のみを設けるパッシブマトリクス型のタッチセンサの構成を示したが、トランジスタと容量とを備えたアクティブマトリクス型のタッチセンサとしてもよい。

## 【0041】

## [インセル型のタッチパネルの構成例]

ここでは、表示素子やトランジスタ等が設けられる基板上に、タッチセンサを構成する電極の少なくとも一方を配置する例について説明する。

20

## 【0042】

以下では、複数の画素を有する表示部にタッチセンサを組み込んだタッチパネル(いわゆるインセル型)の構成例について説明する。ここでは、画素に設けられる表示素子として、液晶素子を適用した例を示す。ただし、本発明の一態様は、これに限定されず、様々な表示素子を適用することができる。

## 【0043】

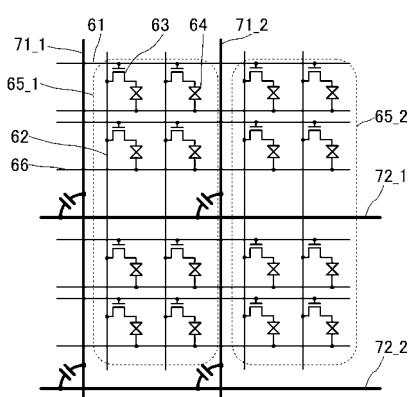

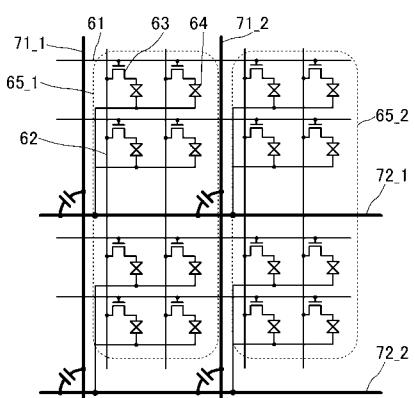

図2(A)は、本構成例で例示するタッチパネルの表示部に設けられる画素回路の一部における等価回路図である。

## 【0044】

一つの画素は少なくともトランジスタ63と液晶素子64を有する。なお、画素は、さらに、保持容量を有する場合もある。またトランジスタ63のゲートに配線61が、ソースまたはドレインの一方には配線62が、それぞれ電気的に接続されている。

30

## 【0045】

画素回路は、X方向に延在する複数の配線(例えば、配線72\_1、配線72\_2)と、Y方向に延在する複数の配線(例えば、配線71\_1、配線71\_2)を有し、これらは互いに交差して設けられている。そして、配線の間に容量が形成される。

## 【0046】

また、一例としては、画素回路に設けられる画素のうち、一部の隣接する複数の画素は、それぞれに設けられる液晶素子の一方の電極が電気的に接続され、一つのブロックを形成する。ここで、例えば、Y方向に延在するライン状の複数のブロック(例えば、ブロック65\_1、65\_2)が形成される。なお、図2(A)では、画素回路の一部のみを示しているが、実際にはこれらのブロックがX方向に繰り返し配置される。ここで、液晶素子の一方の電極としては、一例としては、コモン電極、または、対向電極などがあげられる。一方、液晶素子の他方の電極としては、一例としては、画素電極などがあげられる。

40

## 【0047】

このような構成とすることで、タッチセンサを構成する電極と、画素回路が有する液晶素子の一方の電極とを兼ねることができる。図2(A)では、配線71\_1、配線71\_2は、液晶素子の一方の電極と、タッチセンサを構成する電極とを兼ねている。一方、配線72\_1、配線72\_2は、タッチセンサを構成する電極として機能している。そのためタッチパネルの構成を簡略化できる。なお、図2(A)では、Y方向に延在する複数の

50

配線（例えば、配線 7\_1\_1、配線 7\_1\_2）が、液晶素子の一方の電極と、タッチセンサを構成する電極とを兼ねていたが、本発明の一態様は、これに限定されない。例えば、X 方向に延在する複数の配線（例えば、配線 7\_2\_1、配線 7\_2\_2）が、液晶素子の一方の電極と、タッチセンサを構成する電極とを兼ねていてもよい。その場合の回路図の例を、図 3 に示す。

#### 【0048】

なお、図 2 (A) および図 3 では、配線が、液晶素子の一方の電極と、タッチセンサを構成する電極とを兼ねている場合の例を示したが、本発明の一態様は、これに限定されない。液晶素子の一方の電極と、タッチセンサを構成する電極とは、それぞれ、別の配線で構成してもよい。例えば、図 2 (B) に示すように、液晶素子 6\_4 の一方の電極と電気的に接続する配線 6\_6 を有する構成としてもよい。このとき配線 6\_6、液晶素子 6\_4 を構成する一方の電極、または、液晶素子 6\_4 を構成する他方の電極の少なくとも一つと、X 方向に延在する配線または Y 方向に延在する配線の少なくとも一つと、を同一の導電膜を加工して同時に形成することで、タッチパネルの作製工程を簡略化できる。例えば、配線 6\_6 と配線 7\_1\_1 及び配線 7\_1\_2 を同時に形成してもよいし、または配線 6\_6 と配線 7\_2\_1 及び配線 7\_2\_2 などを同時に形成してもよい。

10

#### 【0049】

なお、図 2 (A)、図 2 (B) および図 3 では、表示素子として、液晶素子を適用した例を示したが、本発明の一態様は、これに限定されない。表示素子として、発光素子を適用した場合の例を、図 4 および図 5 に示す。

20

#### 【0050】

図 6 (A) は、X 方向に延在する複数の配線 7\_2 と、Y 方向に延在する複数の配線 7\_1 の接続構成を示した等価回路図である。なお、タッチセンサが、投影型であり、相互容量方式である場合を示している。Y 方向に延在する配線 7\_1 の各々には、入力電圧（または、選択電圧）または共通電位（または、接地電位、もしくは、基準となる電位）を入力することができる。また、X 方向に延在する配線 7\_2 の各々には接地電位（または、基準となる電位）を入力する、または配線 7\_2 と検知回路と電気的に接続することができる。なお、配線 7\_1 と配線 7\_2 とは入れ替えることが可能である。つまり、配線 7\_1 と検知回路とを接続してもよい。

30

#### 【0051】

以下、図 6 (B)、(C) を用いて、上述したタッチパネルの動作について説明する。

#### 【0052】

ここでは、一例として、1 フレーム期間を、書き込み期間と検知期間とに分ける。書き込み期間は画素への画像データの書き込みを行う期間であり、図 2 等で示す配線 6\_1（ゲート線、または走査線ともいう）が順次選択される。一方、検知期間は、タッチセンサによるセンシングを行う期間であり、Y 方向に延在する配線 7\_1 が順次選択され、入力電圧が入力される。

40

#### 【0053】

図 6 (B) は、書き込み期間における等価回路図である。書き込み期間では、X 方向に延在する配線 7\_2 と、Y 方向に延在する配線 7\_1 の両方に、共通電位が入力される。

#### 【0054】

図 6 (C) は、検知期間のある時点における等価回路図である。検知期間では、X 方向に延在する配線 7\_2 の各々は、検知回路と導通する。また、Y 方向に延在する配線 7\_1 のうち、選択されたものには入力電圧が入力され、それ以外のものには共通電位が入力される。

#### 【0055】

なお、ここで例示した駆動方法は、インセル方式だけでなく上記で例示したタッチパネルにも適用することができる。

#### 【0056】

このように、画像の書き込み期間とタッチセンサによるセンシングを行う期間とを、独

50

立して設けることが好ましい。例えば、表示の帰線期間にセンシングを行うことが好ましい。これにより、画素の書き込み時のノイズに起因するタッチセンサの感度の低下を抑制することができる。

#### 【0057】

##### [タッチパネルの方式について]

以下では、本発明の一態様のタッチパネルに適用可能いくつかの方式について説明する。

#### 【0058】

なお、本明細書等において、タッチパネルは表示面に画像等を表示（出力）する機能と、表示面に指やスタイルスなどの被検知体が触れる、または接近することを検出するタッチセンサとしての機能と、を有する。したがってタッチパネルは入出力装置の一態様である。10

#### 【0059】

また、本明細書等では、タッチパネルの基板に、例えばFPC（Flexible Print Circuit）もしくはTCP（Tape Carrier Package）などのコネクターが取り付けられたもの、または基板にCOG（Chip On Glass）方式によりIC（集積回路）が実装されたものを、タッチパネルモジュール、表示モジュール、または単にタッチパネルと呼ぶ場合がある。

#### 【0060】

本発明の一態様に適用できる静電容量方式のタッチセンサは、一対の導電層を備える。一対の導電層間には容量が形成されている。一対の導電層に被検知体が触れる、または接近することにより一対の導電層間の容量の大きさが変化することを利用して、検出を行うことができる。20

#### 【0061】

静電容量方式としては、表面型静電容量方式、投影型静電容量方式等がある。投影型静電容量方式としては、主に駆動方式の違いから、自己容量方式、相互容量方式などがある。相互容量方式を用いると、同時多点検出が可能となるため好ましい。ただし、自己容量方式を用いることも可能である。

#### 【0062】

また、本発明の一態様のタッチパネルが有する表示素子としては、液晶素子（縦電界方式、または、横電界方式）、MEMS（Micro Electro Mechanical System）を利用した光学素子、有機EL（Electro Luminescence）素子や発光ダイオード（LED：Light Emitting Diode）等の発光素子、電気泳動素子など、様々な表示素子を用いることができる。30

#### 【0063】

ここで、一例として、タッチパネルに表示素子として横電界方式が適用された液晶素子を用いた透過型の液晶表示装置を適用することが好ましい。

#### 【0064】

本発明の一態様のタッチパネルは、一対の基板の間にタッチセンサを構成する一対の電極（導電層または配線ともいう）を挟持することにより、表示パネルとタッチセンサとが一体となった構成を有する。つまり、別の基板などにタッチセンサを形成するのではなく、表示素子やトランジスタが設けられている一対の基板に、タッチセンサを形成する。そのため、タッチパネルの厚さが低減され、軽量なタッチパネルを実現できる。40

#### 【0065】

また、本発明の一態様のタッチパネルは、画素を駆動する信号を供給するFPC（Flexible Print Circuit）と、タッチセンサを駆動するFPCの両方を、一方の基板側に配置する。これにより、電子機器に組み込みやすく、また部品点数を削減することが可能となる。

#### 【0066】

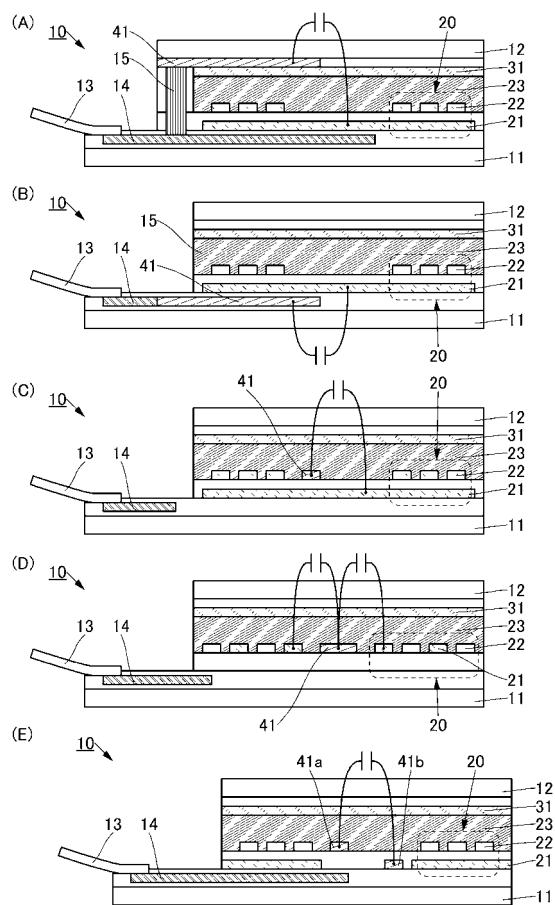

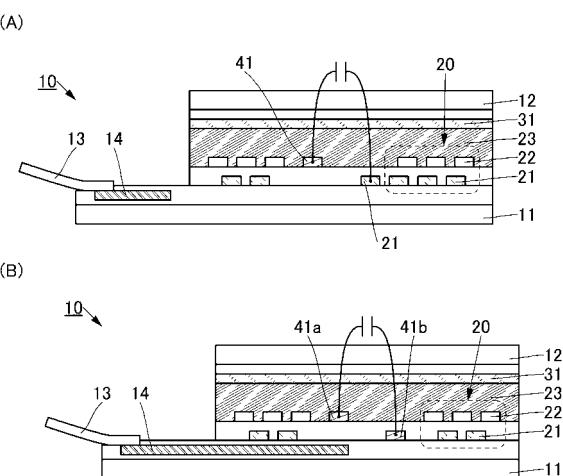

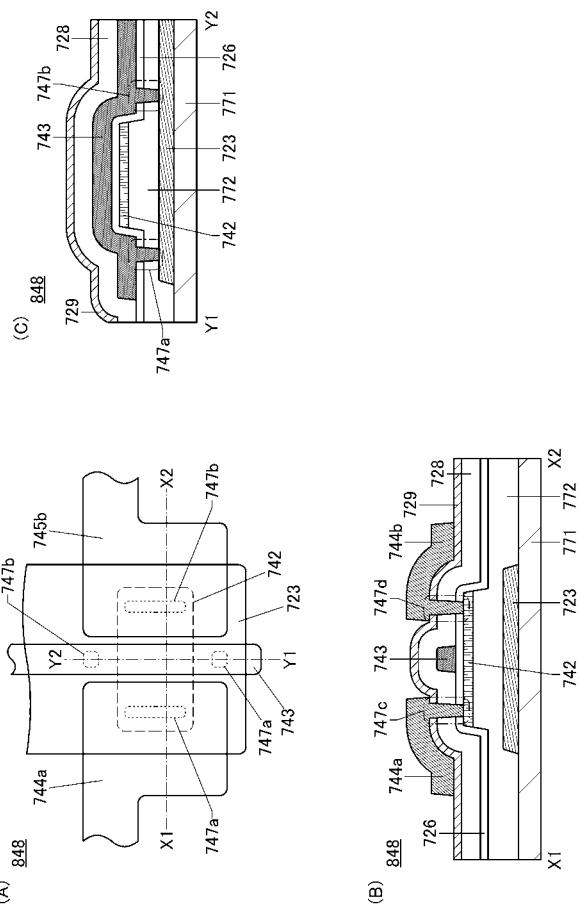

図7(A)は、本発明の一態様のタッチパネル10の方式を説明する断面概略図である

10

20

30

40

50

。

### 【0067】

タッチパネル10は、基板11、基板12、FPC13、導電層14、液晶素子20、着色層31、導電層41等を有する。

### 【0068】

液晶素子20は、導電層21、導電層22及び液晶23により構成される。ここでは液晶素子20にFFS(Fringe Field Switching)モードが適用された液晶素子を用いた場合の例を示している。導電層21上には絶縁層を介して導電層22が配置されている。導電層22は、一例としては、櫛歯状の上面形状、またはスリットが設けられた上面形状(平面形状ともいう)を有する。導電層21および導電層22は、一方が共通電極として機能し、他方が画素電極として機能する。なお、表示素子として、発光素子などを用いる場合には、一例としては、導電層22は、櫛歯状の上面形状、または、スリットが設けられた上面形状を、有していない。

### 【0069】

タッチセンサは、基板12側に設けられた導電層41と、液晶素子20の一対の電極の一方として機能する導電層21との間に形成される容量を利用して検出することができる。ここで、一例としては、導電層41は基板12の基板11側の面(つまり、基板12の下側の面)に設けられていることが好ましい。

### 【0070】

基板12側に設けられた導電層41は、接続層15により基板11側に設けられた導電層14と電気的に接続する。導電層14は基板11側に取り付けられたFPC13と電気的に接続する。このような構成とすることで、1つの基板にタッチセンサを駆動するためのFPCと、液晶素子20を駆動するためのFPCの両方を配置することができる。

### 【0071】

ここで、タッチパネルの構成として、例えば基板12の基板11側とは反対側の面(つまり、基板12の上側の面)にタッチセンサの電極として機能する導電層を配置した場合、これと電気的に接続するFPCを基板12に取り付ける必要がある。また図7(A)で示した接続層15を用いない場合であっても、導電層41と電気的に接続するFPCは、基板12に取り付ける必要がある。また、基板11及び基板12とは異なる基板に、タッチセンサの電極として機能する導電層を配置する場合も、当該基板にFPCを取り付ける必要がある。したがってこのような構成では部品点数が増加する、また電子機器に組み込む際にFPCの位置により制限が生じてしまう場合がある。一方、本発明の一態様では、一対の基板の一方にのみFPCを配置することが可能であるため、部品点数を低減し、電子機器に組み込みやすい構成とすることができます。

### 【0072】

また、液晶素子20の一方の電極を、タッチセンサとして機能する一対の電極の少なくとも一方と兼ねることにより、工程を簡略化することができるため歩留りの向上できまた製造コストを低減することができる。

### 【0073】

図7(B)では、タッチセンサの電極として機能する導電層41を、基板11側に配置した例を示している。導電層41は、導電層14と電気的に接続する。タッチセンサは、導電層41と、液晶素子20の一対の電極の一方(例えば、共通電極)として機能する導電層21との間に形成される容量を利用して検出することができる。このような構成とすることでも、FPC13を基板11側に配置することができる。またこのとき、基板11側の面をタッチ面とすると、より検出感度を高めることができます。

### 【0074】

図7(C)に示す構成では、導電層41を導電層22と同一面上に配置した例を示している。また導電層41は図示しない領域で導電層14と電気的に接続している。ここで、導電層41と導電層22とを同一の導電膜を加工して同時に形成されていることが好ましい。タッチセンサは、導電層41と導電層21の間に形成される容量を利用して検出する

10

20

30

40

50

ことができる。導電層 21 は、例えば、液晶素子 20 の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

【0075】

図 7 (D) に示す構成は、液晶素子 20 に IPS (In-Plane-Switching) モードを適用した場合の例を示している。

【0076】

液晶素子 20 を構成する導電層 21 と導電層 22 とは同一面上に設けられている。導電層 21 と導電層 22 とは、それぞれ櫛歯状の形状を有しており、これらが噛み合うように配置されている。タッチセンサは、導電層 41 と導電層 21 の間に形成される容量を利用して検出することができる。導電層 21 は、例えば、液晶素子 20 の共通電極としての機能と、タッチセンサの電極として機能とを有している。

10

【0077】

またタッチセンサの一方の電極として機能する導電層 41 は、導電層 21 及び導電層 22 と同一面上に配置されている。また導電層 41 は図示しない領域で導電層 14 と電気的に接続している。ここで導電層 41 、導電層 21 及び導電層 22 は、これらが同一の導電膜を加工して同時に形成されていることが好ましい。

【0078】

図 7 (E) に示す構成では、FFS モードが適用された液晶素子 20 を適用した他の例を示している。タッチセンサは、導電層 41a と導電層 41b との間に形成される容量を利用して検出することができる。導電層 21 及び導電層 22 は、一方が液晶素子 20 の共通電極としての機能を有し、他方が液晶素子 20 の画素電極としての機能を有している。

20

【0079】

導電層 41a は導電層 22 と同一面上に設けられている。また導電層 41b は導電層 21 と同一面上に設けられている。ここで導電層 41a と導電層 22 とを同一の導電膜を加工して同時に形成することが好ましい。同様に導電層 41b と導電層 21 とを同一の導電膜を加工して同時に形成することが好ましい。このような構成とすることで、液晶素子 20 の一対の電極を形成する工程で、同時にタッチセンサを構成する一対の電極を形成することができるため、製造工程を増やすことなくタッチセンサとしての機能を有するタッチパネル 10 を作製することができる。

30

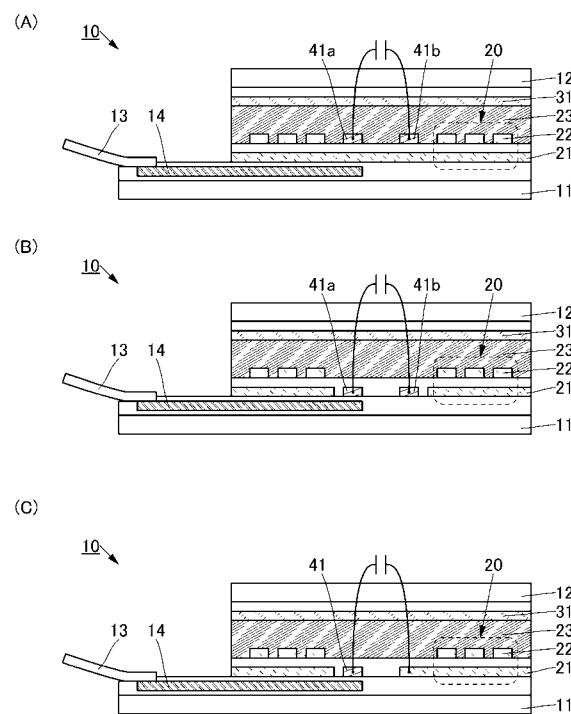

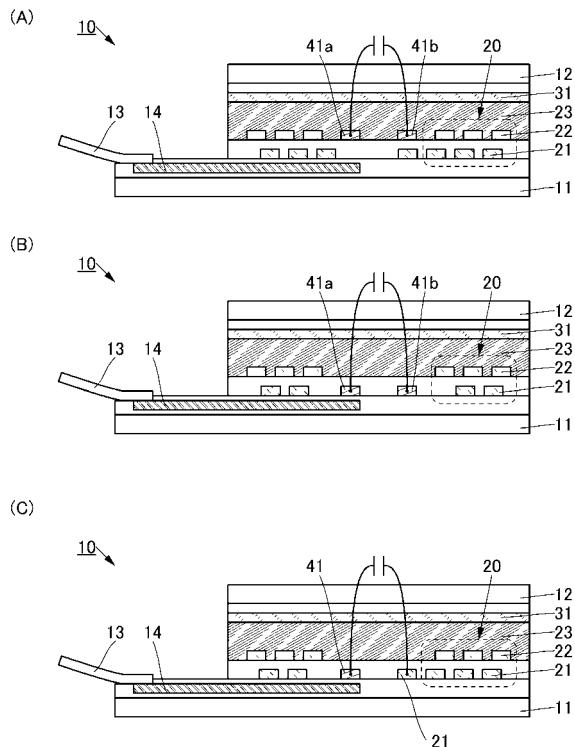

【0080】

図 8 (A) に示す構成では、FFS モードが適用された液晶素子 20 を適用した他の例を示している。タッチセンサは、導電層 41a と導電層 41b との間に形成される容量を利用して検出することができる。導電層 21 は、例えば、液晶素子 20 の共通電極としての機能を有している。

【0081】

導電層 41a および導電層 41b は導電層 22 と同一面上に設けられている。ここで導電層 41a と導電層 41b と導電層 22 とを同一の導電膜を加工して同時に形成することが好ましい。このような構成とすることで、液晶素子 20 の一方の電極を形成する工程で、同時にタッチセンサを構成する一対の電極を形成することができるため、製造工程を増やすことなくタッチセンサとしての機能を有するタッチパネル 10 を作製することができる。

40

【0082】

なお、導電層 41a は、導電層 21 と重なるように設けられているが、本発明の一態様は、これに限定されない。導電層 21 は、導電層 41a と重ならないように設けてもよい。その結果、導電層 41a の寄生容量を低減することができる。なお、導電層 41b の場合も同様に、導電層 21 は、導電層 41b と重ならないように設けてもよい。

【0083】

図 8 (B) に示す構成では、FFS モードが適用された液晶素子 20 を適用した他の例を示している。タッチセンサは、導電層 41a と導電層 41b との間に形成される容量を利用して検出することができる。導電層 21 及び導電層 22 は、一方が液晶素子 20 の共

50

通電極としての機能を有し、他方が液晶素子 20 の画素電極としての機能を有している。

【0084】

導電層 41a および導電層 41b は導電層 21 と同一面上に設けられている。ここで導電層 41a と導電層 41b と導電層 21 とを同一の導電膜を加工して同時に形成することが好ましい。このような構成とすることで、液晶素子 20 の一方の電極を形成する工程で、同時にタッチセンサを構成する一対の電極を形成することができるため、製造工程を増やすことなくタッチセンサとしての機能を有するタッチパネル 10 を作製することができる。

【0085】

図 8 (C) に示す構成では、FFS モードが適用された液晶素子 20 を適用した他の例を示している。タッチセンサは、導電層 41 と、液晶素子 20 の一対の電極の一方として機能する導電層 21 との間に形成される容量を利用して検出することができる。導電層 21 は、例えば、液晶素子 20 の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

10

【0086】

導電層 41 は、導電層 21 と同一面上に設けられている。ここで導電層 41 と導電層 21 とを同一の導電膜を加工して同時に形成することが好ましい。このような構成とすることで、液晶素子 20 の一方の電極を形成する工程で、同時にタッチセンサを構成する一対の電極を形成することができるため、製造工程を増やすことなくタッチセンサとしての機能を有するタッチパネル 10 を作製することができる。

20

【0087】

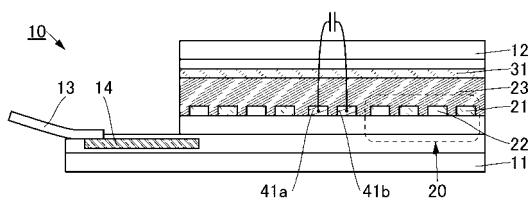

図 9 に示す構成は、液晶素子 20 に IPS モードを適用した場合の例を示している。

【0088】

液晶素子 20 を構成する導電層 21 と導電層 22 とは同一面状に設けられている。導電層 21 と導電層 22 とは、それぞれ櫛歯状の形状を有しており、これらが噛み合うように配置されている。導電層 21 及び導電層 22 は、一方が液晶素子 20 の共通電極としての機能を有し、他方が液晶素子 20 の画素電極としての機能を有している。

【0089】

またタッチセンサの電極として機能する導電層 41a と導電層 41b は、導電層 21 及び導電層 22 と同一面上に配置されている。ここで導電層 41a と導電層 41b と導電層 21 と導電層 22 とは、同一の導電膜を加工して同時に形成されていることが好ましい。タッチセンサは、導電層 41a と導電層 41b の間に形成される容量を利用して検出することができる。

30

【0090】

なお、FFS モードが適用された場合については、導電層 21 を、櫛歯状、または、スリットが設けられた上面形状とすることにより、IPS モードに変更することができる。

【0091】

例えば、図 7 (C) を IPS モードに変更した場合を、図 10 (A) に示す。導電層 21 は、例えば、液晶素子 20 の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

40

【0092】

同様に、図 7 (E) を IPS モードに変更した場合を、図 10 (B) に示す。導電層 21 及び導電層 22 は、一方が液晶素子 20 の共通電極としての機能を有し、他方が液晶素子 20 の画素電極としての機能を有している。

【0093】

同様に、図 8 (A)、図 8 (B) を IPS モードに変更した場合を、それぞれ、図 11 (A)、図 11 (B) に示す。導電層 21 及び導電層 22 は、一方が液晶素子 20 の共通電極としての機能を有し、他方が液晶素子 20 の画素電極としての機能を有している。

【0094】

同様に、図 8 (C) を IPS モードに変更した場合を、図 11 (C) に示す。導電層 21

50

1は、例えば、液晶素子20の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

**【0095】**

なお、上側の電極が液晶素子20の画素電極であり、下側の電極が液晶素子20の共通電極である場合の例を多く示したが、本発明の一態様は、これに限定されない。上側の電極が液晶素子20の共通電極であり、下側の電極が液晶素子20の画素電極となる構成としてもよい。

**【0096】**

例えば、図7(C)において、上側の電極が液晶素子20の共通電極となるようにした例を、図12に示す。導電層21は、例えば、液晶素子20の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

10

**【0097】**

同様に、図8(A)において、上側の電極が液晶素子20の共通電極となるようにした例を、図13(A)に示す。導電層21は、例えば、液晶素子20の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

10

**【0098】**

同様に、図8(C)において、上側の電極が液晶素子20の共通電極となるようにした例を、図13(B)に示す。導電層21は、例えば、液晶素子20の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

20

**【0099】**

同様に、図11(C)において、上側の電極が液晶素子20の共通電極となるようにした例を、図14に示す。導電層21は、例えば、液晶素子20の共通電極としての機能と、タッチセンサの電極としての機能とを有している。

20

**【0100】**

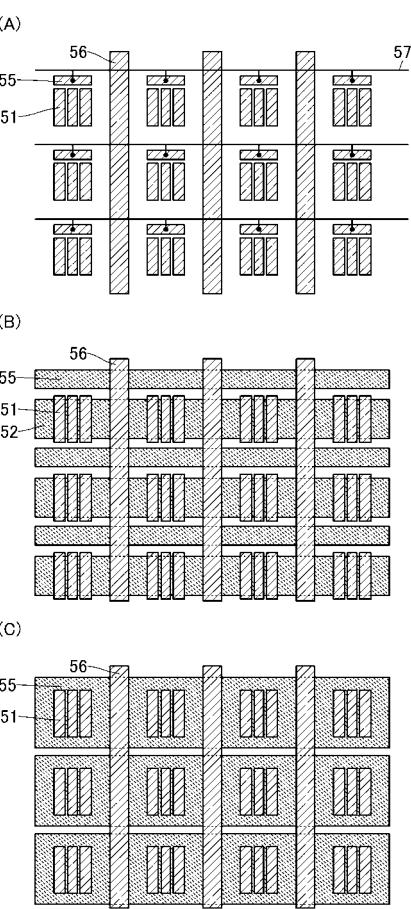

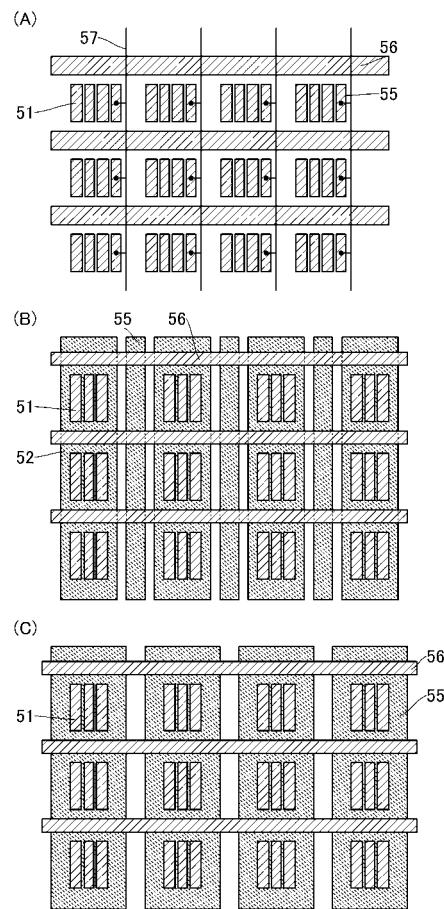

図15(A)(B)(C)は、上面から見た本発明の一態様のタッチパネルの概念図である。したがって、タッチセンサ以外の部分については、大幅に省略して示している。また、画素電極51において、櫛歯状の上面形状、またはスリットが設けられた上面形状を有している場合があるが、ここでは、省略している。

30

**【0101】**

図15(A)に示す構成では、タッチセンサはセンサ電極55とセンサ電極56とを有する。ここで、センサ電極55及びセンサ電極56は、画素電極51と同一の導電膜により形成されている。または、センサ電極55及びセンサ電極56は、画素電極51と同一面上に設けられている。X方向に配列する複数のセンサ電極55は電気的に接続された構成を有する。このとき、センサ電極55は、配線57により、接続されている。また、センサ電極56は、Y方向に延在して設けられている。つまり、図15(A)は、図8(A)の平面図を示しているとも言える。なお、センサ電極55及びセンサ電極56は、画素電極ではなく、コモン電極と同一の導電膜により形成されてもよい。

30

**【0102】**

図15(B)に示す構成では、共通電極52とセンサ電極55が同一の導電膜により形成されている例を示している。または、共通電極52とセンサ電極55は、同一面上に設けられている。ここで共通電極52及びセンサ電極55はX方向に伸びた帯状の形状を有し、各センサ電極56と交差する構成を有する。つまり、図15(B)は、図8(C)の平面図を示しているとも言える。

40

**【0103】**

図15(C)では、図15(B)で示した共通電極52が、センサ電極55を兼ねる構成の例を示している。つまり、図15(C)は、図7(C)の平面図を示しているとも言える。

40

**【0104】**

なお、センサ電極56は、Y方向に延在して設けられている場合の例を示したが、X方向に延在して設けられてもよい。図15(A)、図15(B)、図15(C)において、

50

X 方向に延在した場合の例を、図 16 (A)、図 16 (B)、図 16 (C) にそれぞれ示す。

#### 【0105】

なお、図 15 (B) および図 15 (C) では、上側の電極（液晶層に近い側の電極、つまり、指やペンなどの被検知体に近い側の電極）が画素電極であり、下側の電極（液晶層から遠い側の電極、つまり、指やペンなどの被検知体から遠い側の電極）が共通電極である場合の例を示したが、本発明の一態様は、これに限定されない。上側の電極（液晶層に近い側の電極、つまり、指やペンなどの被検知体に近い側の電極）が共通電極であり、下側の電極（液晶層から遠い側の電極、つまり、指やペンなどの被検知体から遠い側の電極）が画素電極となるような構成としてもよい。このような構成を図 15 (B) および図 15 (C) に適用した場合の例を、それぞれ、図 17 (A) および図 17 (B) に示す。なお、共通電極 52 において、櫛歯状の上面形状、またはスリットが設けられた上面形状を有している場合があるが、ここでは、省略している。10

#### 【0106】

以上がタッチパネルの方式についての説明である。

#### 【0107】

#### [構成例 1]

以下では、タッチパネルのより具体的な構成例について説明する。

#### 【0108】

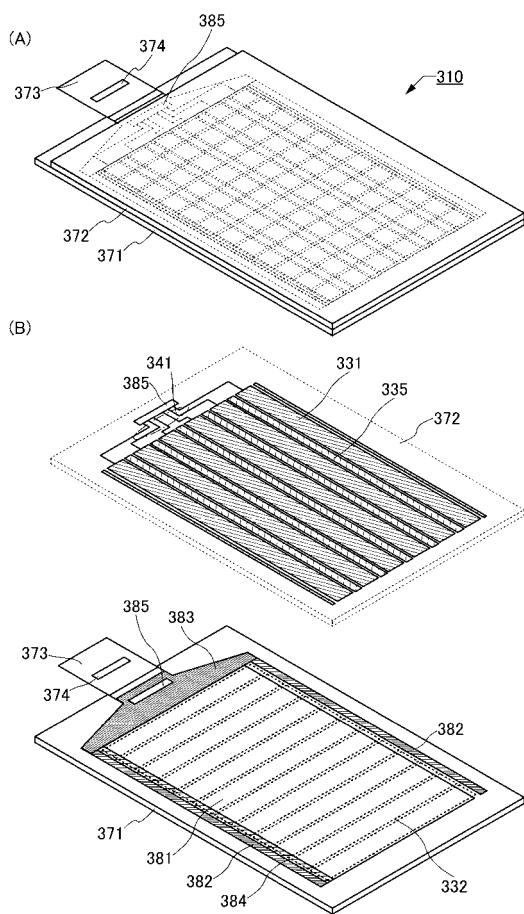

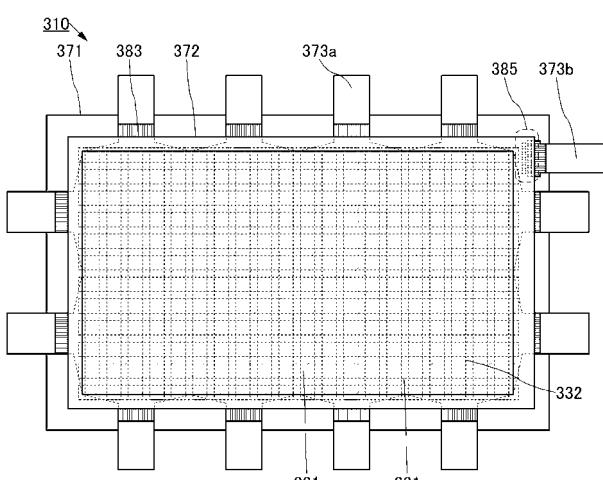

図 18 (A) は、本発明の一態様のタッチパネル 310 の斜視概略図である。また図 18 (B) は、図 18 (A) を展開した斜視概略図である。なお明瞭化のため、代表的な構成要素のみを示している。また図 18 (B) では、一部の構成要素（基板 372）を破線で輪郭のみ明示している。20

#### 【0109】

タッチパネル 310 は、対向して設けられた基板 371 と基板 372 とを有する。

#### 【0110】

基板 371 上には、表示部 381、駆動回路 382、配線 383、駆動回路 384 等が設けられている。また表示部 381 には、導電層 332 が形成されている。基板 371 には、配線 383 と電気的に接続される FPC 373 が設けられている。また図 18 (A) (B) では、FPC 373 上に IC 374 が設けられている例を示している。30

#### 【0111】

また基板 372 の基板 371 と対向する面側には、複数の導電層 331、複数の導電層 335、複数の導電層 341 等が形成されている。導電層 341 は複数の導電層 331 のいずれかと電気的に接続する。また複数の導電層 341 は接続部 385 を介して基板 371 に設けられた FPC 373 と電気的に接続する。

#### 【0112】

導電層 335 は、2 つの導電層 331 の間に配置される。導電層 335 を設けることで導電層 331 が設けられている領域と設けられていない領域の間で透過率に差が生じることを抑制する機能を有する。また導電層 335 は電気的にフローティングであることが好ましい。こうすることで、導電層 335 を介して、導電層 331 及び導電層 332 の一方の電位の変化を他方に効率よく伝達することができ、検出感度を高めることができる。なお導電層 335 は不要である場合には設けなくてもよい。40

#### 【0113】

表示部 381 は、少なくとも複数の画素を有する。画素は、少なくとも一つの表示素子を有する。また、画素は、トランジスタ及び表示素子を備えることが好ましい。表示素子としては、代表的には有機 EL 素子などの発光素子や液晶素子などを用いることができる。

#### 【0114】

駆動回路 382 は、例えば走査線駆動回路、信号線駆動回路等として機能する回路を用いることができる。

## 【0115】

配線383は、表示部381や駆動回路382に信号や電力を供給する機能を有する。当該信号や電力は、FPC373を介して外部、またはIC374から配線383に入力される。

## 【0116】

駆動回路384は、導電層332を順次選択する機能を有する。または、導電層332ではなく導電層331を順次選択することによりタッチセンサを駆動する場合には、駆動回路384は、固定電位とセンシングに用いる信号とを切り替えて導電層332に供給する機能を有する。なお、IC374や外部によりタッチセンサを駆動する信号が供給される場合には、駆動回路384を設けなくてもよい。

10

## 【0117】

また、図18(A)(B)では、FPC373上にCOF(Chip On Film)方式により実装されたIC374が設けられている例を示している。IC374は、例えば走査線駆動回路、または信号線駆動回路などとしての機能を有するICを適用できる。なおタッチパネル310が走査線駆動回路及び信号線駆動回路として機能する回路を備える場合や、走査線駆動回路や信号線駆動回路として機能する回路を外部に設け、FPC373を介して表示部381を駆動するための信号を入力する場合などでは、IC374を設けない構成としてもよい。また、IC374を、COG(Chip On Glass)方式等により、基板371に直接実装してもよい。

20

## 【0118】

タッチセンサは、基板372に設けられた導電層331と、基板371に設けられた導電層332と、により構成される。導電層331と導電層332の間に形成される容量を利用して、タッチセンサは検出することができる。

## 【0119】

このような構成とすることで、タッチパネル310に接続するFPCを1つの基板側(ここでは基板371側)にのみ配置することができる。また、図18(A)、(B)に示すように、タッチパネル310には1つのFPC373を設け、当該FPC373が、表示パネルとタッチセンサの両方に信号を供給する機能を有する構成とすると、より構成を簡略化できるため好ましい。

30

## 【0120】

またこのとき、IC374はタッチセンサを駆動する機能を有していてもよいし、タッチセンサを駆動するICをさらに設けてもよい。または、タッチセンサを駆動するICを基板371上に実装してもよい。

## 【0121】

図19は、図18とは異なる構成を有するタッチパネル310の上面概略図を示している。

## 【0122】

図19に示すタッチパネルは、基板371に複数のFPC373aと、FPC373bとを有している場合の例を示している。FPC373aは表示部381を駆動するための信号を供給する機能を有する。またFPC373bは基板372側に配置された導電層331に信号等を供給する機能を有する。

40

## 【0123】

このように、タッチパネル310の表示部381の2以上の辺に沿ってFPC373aを配置することで、多くの信号をタッチパネル310に供給できる。例えば表示部381が高解像度である場合には、このように表示部381の2以上の辺から信号を供給する構成とすることで、配線の密度が高まるによる配線間の寄生容量を低減できる。また大型の表示装置とする場合には、このような構成とすることで配線の長さを短くできるため、配線抵抗を削減し、信号の遅延などの影響を抑制することができる。

## 【0124】

[断面構成例1]

50

以下では、本発明の一態様のタッチパネルの断面構成の例について、図面を参照して説明する。

【0125】

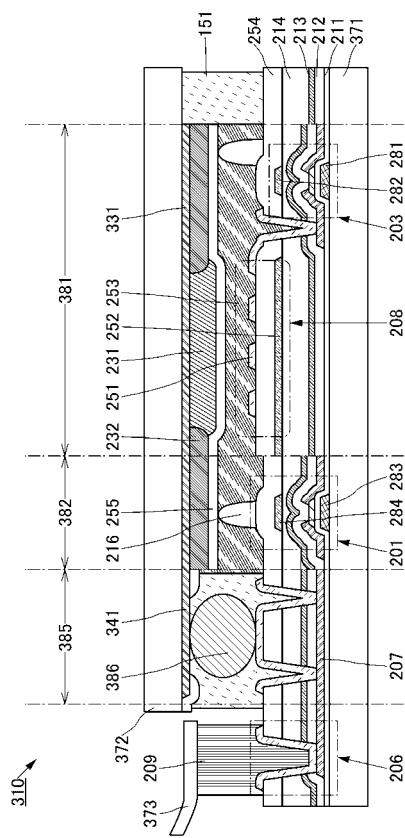

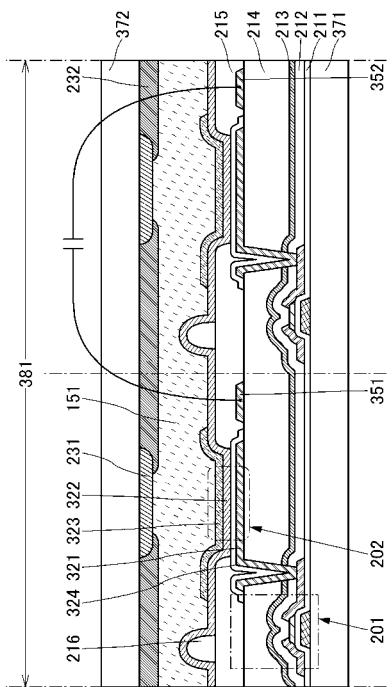

〔断面構成例1-1〕

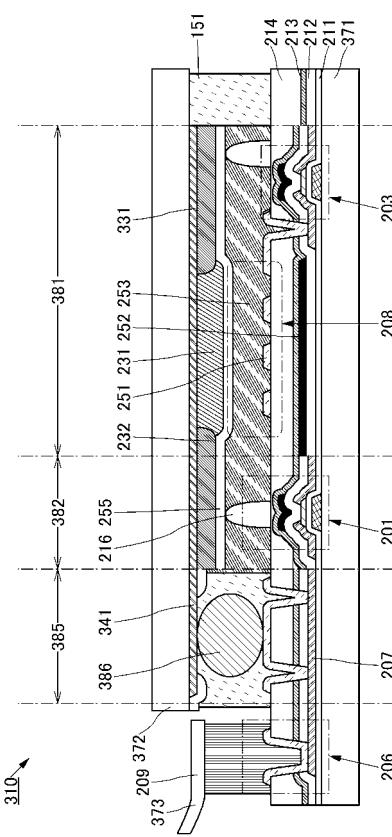

図20はタッチパネル310の断面概略図である。図20では、図18(A)におけるFPC373を含む領域、駆動回路382を含む領域、表示部381を含む領域のそれぞれの断面を示している。

【0126】

基板371と、基板372とは、接着層151によって貼り合わされている。また基板371、基板372、及び接着層151に囲まれた領域に、液晶253が封止されている。

10

【0127】

基板371上には、トランジスタ201、トランジスタ203、接続部206、導電層207、液晶素子208を構成する導電層251及び導電層252等が設けられている。

【0128】

基板371上には、絶縁層211、絶縁層212、絶縁層213、絶縁層214、絶縁層254、スペーサ216等が設けられている。絶縁層211は、その一部が各トランジスタのゲート絶縁層として機能する。絶縁層212、絶縁層213、及び絶縁層214は、各トランジスタ等を覆って設けられている。絶縁層214は、一例としては、平坦化層としての機能を有する。なお、ここではトランジスタ等を覆う絶縁層として、絶縁層212、絶縁層213、及び絶縁層214の3層を有する場合を示しているが、これに限られず4層以上であってもよいし、単層、または2層であってもよい。また平坦化層として機能する絶縁層214は不要であれば設けなくてもよい。

20

【0129】

図20では、表示部381の例として、1つの副画素の断面を示している。例えば、副画素は赤色を呈する副画素、緑色を呈する副画素、青色を呈する副画素のいずれかとすることで、フルカラーの表示を行うことができる。例えば図20に示す副画素は、トランジスタ203と、液晶素子208と、着色層231と、を有する。

【0130】

また図20では、駆動回路382の例としてトランジスタ201が設けられている例を示している。

30

【0131】

図20では、トランジスタ201及びトランジスタ203の例として、チャネルが形成される半導体層をゲート電極283及びゲート電極284、または、ゲート電極281及びゲート電極282で挟持する構成を適用した例を示している。このようなトランジスタは、ゲート電極281とゲート電極282とが接続されている場合や、ゲート電極283とゲート電極284とが接続されている場合には、他のトランジスタと比較して電界効果移動度を高めることができ、オン電流を増大させることができる。その結果、高速動作が可能な回路を作製することができる。さらには回路部の占有面積を縮小することができる。オン電流の大きなトランジスタを適用することで、表示パネルまたはタッチパネルを大型化、または高精細化したときに配線数が増大したとしても、各配線における信号遅延を低減することが可能であり、表示ムラを抑制することが可能である。

40

【0132】

なお、駆動回路382が有するトランジスタと、表示部381が有するトランジスタは、同じ構造であってもよい。また駆動回路382が有する複数のトランジスタは、全て同じ構造であってもよいし、異なる構造のトランジスタを組み合わせて用いてもよい。また、表示部381が有する複数のトランジスタは、全て同じ構造であってもよいし、異なる構造のトランジスタを組み合せて用いてもよい。

【0133】

各トランジスタを覆う絶縁層212、絶縁層213のうち少なくとも一方は、一例とし

50

ては、水や水素などの不純物が拡散しにくい材料を用いることが好ましい。すなわち、絶縁層212または絶縁層213はバリア膜として機能させることができる。このような構成とすることで、トランジスタに対して外部から不純物が拡散することを効果的に抑制することが可能となり、信頼性の高いタッチパネルを実現できる。

#### 【0134】

図20には、液晶素子208にFFS(Fringe Field Switching)モードが適用された液晶素子を用いた場合の例を示している。液晶素子208は、導電層251、液晶253、及び導電層252を有する。導電層251と導電層252との間に生じる電界により、液晶253の配向を制御することができる。

#### 【0135】

絶縁層214上に導電層252が設けられている。また導電層252を覆って絶縁層254が設けられ、絶縁層254上に導電層251が設けられている。導電層251は絶縁層254、絶縁層214、絶縁層213、絶縁層212に設けられた開口を介してトランジスタ203のソース又はドレインの一方と電気的に接続されている。導電層251と導電層252として透光性を有する導電性材料を用いると、タッチパネル310を透過型の液晶表示装置とすることができます。

#### 【0136】

導電層251は、櫛歯状の上面形状、またはスリットが設けられた上面形状(平面形状ともいう)を有する。また、導電層252は導電層251と重ねて配置されている。また着色層231等と重なる領域において、導電層252上に導電層251が配置されていない部分を有する。

#### 【0137】

図20では、導電層251が画素電極として機能し、導電層252が共通電極として機能する。なお、上層に設けられ、櫛歯状またはスリット状の上面形状を有する導電層251を共通電極とし、下層に設けられる導電層252を画素電極として用いることもできる。その場合には、導電層252をトランジスタ203のソース又はドレインの一方と電気的に接続すればよい。

#### 【0138】

基板371の端部に近い領域には、接続部206が設けられている。接続部206は、接続層209を介してFPC373と電気的に接続されている。図20では、導電層207の一部と、導電層251と同一の導電膜を加工して形成した導電層とを積層することで接続部206を構成している例を示している。

#### 【0139】

基板372の基板371側の面には、導電層331、導電層341、着色層231、遮光層232、絶縁層255等が設けられている。

#### 【0140】

図20では、導電層331と導電層341とが同一面上に形成されている場合を示している。ここで、導電層331と導電層341とは同一の導電膜を加工して同時に形成されていることが好ましい。また、導電層331と導電層341とが一体であってもよい。このとき、少なくとも表示部381と重なる部分が、タッチセンサの一方の電極として機能する導電層331に相当し、それ以外の部分を導電層341と呼ぶこともできる。つまり、図20は、図7(A)の場合の断面図の一例を示していると言える。

#### 【0141】

接続部385において、導電層341は絶縁層255に覆われない領域を有する。導電層341は接続体386を介して、基板371側に設けられた導電層207と電気的に接続している。これにより、FPC373と導電層331とが電気的に接続する。図20では、接続体386が導電層341に接する部分と、導電層251と同一面上に形成され、導電層207と電気的に接続する導電層と接する部分と、を有する場合の例を示している。

#### 【0142】

10

20

30

40

50

接続体 386 としては、例えば導電性の粒子を用いることができる。導電性の粒子としては、有機樹脂またはシリカなどの粒子の表面を金属材料で被覆したものを用いることができる。金属材料としてニッケルや金を用いると接触抵抗を低減できるため好ましい。またニッケルをさらに金で被覆するなど、2種類以上の金属材料を層状に被覆させた粒子を用いることが好ましい。また接続体 386 として弾性変形、または塑性変形する材料を用いることが好ましい。このとき導電性の粒子は図 20 に示すように上下方向に潰れた形状となる場合がある。こうすることで接続体 386 と、これと電気的に接続する導電層との接触面積が増大し、接触抵抗が低減できるほか、接続不良などの不具合の発生を抑制できる。

## 【0143】

接続体 386 は接着層 151 に覆われるよう配置することが好ましい。例えば接着層 151 となるペースト等を塗布した後に、接続部 385 に接続体 386 を配置すればよい。例えば固体封止構造の表示装置や中空封止構造の表示装置等のような、接着層 151 を周辺に用いる構成に、接着層 151 が設けられる部分に接続部 385 を配置する構成を適用することができる。

## 【0144】

着色層 231 及び遮光層 232 は、導電層 331 上に設けられている。また着色層 231 や遮光層 232 を覆って絶縁層 255 が設けられている。

## 【0145】

絶縁層 255 は、着色層 231 や遮光層 232 等に含まれる不純物が液晶 253 に拡散することを防ぐオーバーコートとしての機能を有する。

## 【0146】

スペーサ 216 は、絶縁層 254 上に設けられ、基板 371 と基板 372 との距離が一定以上近づくことを防ぐ機能を有する。図 20 ではスペーサ 216 と基板 372 側の構造物（例えば絶縁層 255 等）とが接触している例を示すが、これらが接していなくてもよい。またここではスペーサ 216 が基板 371 側に設けられている例を示したが、基板 372 側に設けてもよい。例えば、隣接する 2つの副画素の間に配置すればよい。または、スペーサ 216 として粒状のスペーサを用いてもよい。粒状のスペーサとしては、シリカなどの材料を用いることもできるが、有機樹脂やゴムなどの弾性を有する材料を用いることが好ましい。このとき、粒状のスペーサは上下方向に潰れた形状となる場合がある。

## 【0147】

なお、導電層 251、絶縁層 254、絶縁層 255 等において、液晶 253 と接する面には液晶 253 の配向を制御するための配向膜が設けられていてもよい。

## 【0148】

導電層 331 の、少なくとも着色層 231 と重なる部分には透光性を有する材料を用いることが好ましい。

## 【0149】

また、透過型の液晶素子 208 の場合、例えば図示しない偏光板を、表示部を挟むように 2つ配置する。偏光板よりも外側に配置されたバックライトからの光は偏光板を介して入射される。このとき、導電層 251 と導電層 252 の間に与える電圧によって液晶 253 の配向を制御し、光の光学変調を制御することができる。すなわち、偏光板を介して射出される光の強度を制御することができる。またバックライトから入射される光は着色層 231 によって特定の波長領域以外の光が吸収され、射出される光は例えば赤色、青色、または緑色を呈する光となる。

## 【0150】

また偏光板に加えて、例えば円偏光板を用いることができる。円偏光板としては、例えば直線偏光板と 1/4 波長位相差板を積層したものを用いることができる。円偏光板により、視野角依存を低減することができる。

## 【0151】

なお、ここでは液晶素子 20 として FFS モードが適用された素子を用いたが、これに

10

20

30

40

50

限られず様々なモードが適用された液晶素子を用いることができる。例えばVA(Vertical Alignment)モード、TN(Twisted Nematic)モード、IPS(In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード等が適用された液晶素子を用いることができる。

## 【0152】

10

また、タッチパネル310にノーマリーブラック型の液晶表示装置、例えば垂直配向(VA)モードを採用した透過型の液晶表示装置を適用してもよい。垂直配向モードとしては、MVA(Multi-Domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モードなどを用いることができる。

## 【0153】

なお、液晶素子は、液晶の光学変調作用によって光の透過または非透過を制御する素子である。なお、液晶の光学的変調作用は、液晶にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む)によって制御される。なお、液晶素子に用いる液晶としては、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLC:Polymer Dispersed Liquid Crystal)、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

20

## 【0154】

また、液晶材料としては、ポジ型の液晶、またはネガ型の液晶のいずれを用いてもよく、適用するモードや設計に応じて最適な液晶材料を用いればよい。

## 【0155】

30

また、横電界方式を採用する場合、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために数重量%以上のカイラル剤を混合させた液晶組成物を液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が短く、光学的等方性である。また、ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。

## 【0156】

本構成例において、導電層331と、導電層252の間に形成される容量を利用して、タッチ動作等を検出することができる。すなわち導電層252は、液晶素子208の一対の電極の一方と、タッチセンサの一対の電極の一方との両方を兼ねる。

40

## 【0157】

ここで、導電層251、導電層252、または導電層331として、可視光を透過する導電性材料を用いることが好ましい。例えば金属酸化物を含む導電性材料を含んで構成される。例えば、後述する透光性を有する導電性材料のうち、金属酸化物を用いることができる。

## 【0158】

または、導電層251、導電層252、または導電層331は、例えば、他の導電層や半導体層と同一の金属元素を含む金属酸化物を用いることが好ましい。特に、タッチパネル310が有するトランジスタの半導体層に酸化物半導体を用いた場合、これに含まれる金属元素を含む導電性酸化物を適用することが好ましい。特に、絶縁層254において、

50

水素を含む窒化珪素膜を用いてもよい。その場合には、導電層 252 として、酸化物半導体を用いる場合、絶縁層 254 から供給される水素によって、導電率を向上させることができる。つまり、酸化物半導体が N+ 化された状態とすることができる。

#### 【0159】

また、状況によっては、導電層 331 に固定電位が与えられていてもよい。その場合には、外部から電磁的なノイズを遮蔽することができる。例えばセンシングを行っていないとき、導電層 331 には液晶 253 のスイッチングに影響しない定電位を供給すればよい。例えば接地電位、共通電位、または任意の定電位を用いることができる。また例えば、導電層 331 と導電層 252 とを同電位としてもよい。

#### 【0160】

また、導電層 331 に適切な電位を与えることにより、導電層 251 と導電層 252 との間に生じる電界の向き（電気力線の向き）のうち、厚さ方向の成分を低減し、より効果的に厚さに対して概略垂直な方向（横方向）に電界が向くようにすることができます。こうすることで、液晶 253 の配向欠陥を抑制し、光漏れなどの不具合が生じることを防ぐことができる。

#### 【0161】

ここで、基板 372 よりも上部に、指またはスタイルスなどの検知体が直接触れる基板を設けてもよい。またこのとき、基板 372 と当該基板との間に偏光板または円偏光板を設けることが好ましい。その場合、当該基板上に保護層（セラミックコート等）を設けることが好ましい。保護層は、例えば酸化シリコン、酸化アルミニウム、酸化イットリウム、イットリア安定化ジルコニア（YSZ）などの無機絶縁材料を用いることができる。また、当該基板に強化ガラスを用いてもよい。強化ガラスは、イオン交換法や風冷強化法等により物理的、または化学的な処理が施され、その表面に圧縮応力を加えたものを用いることができる。

#### 【0162】

##### [各構成要素について]

以下では、上記に示す各構成要素について説明する。

#### 【0163】

##### {基板}

タッチパネルが有する基板には、平坦面を有する材料を用いることができる。表示素子からの光を取り出す側の基板には、該光を透過する材料を用いる。例えば、ガラス、石英、セラミック、サファイヤ、有機樹脂などの材料を用いることができる。また、シリコンや炭化シリコンからなる単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板として用いてもよい。

#### 【0164】

なお、基板として、ガラス基板を用いる場合、第 6 世代（1500 mm × 1850 mm）、第 7 世代（1870 mm × 2200 mm）、第 8 世代（2200 mm × 2400 mm）、第 9 世代（2400 mm × 2800 mm）、第 10 世代（2950 mm × 3400 mm）等の大面積基板を用いることで、大型の表示装置を作製することができる。また、基板として、可撓性基板を用い、可撓性基板上に直接、トランジスタや容量素子等を形成してもよい。

#### 【0165】

厚さの薄い基板を用いることで、タッチパネルの軽量化、薄型化を図ることができる。さらに、可撓性を有する程度の厚さの基板を用いることで、可撓性を有するタッチパネルを実現できる。

#### 【0166】

ガラスとしては、例えば、無アルカリガラス、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス等を用いることができる。

#### 【0167】

10

20

30

40

50

可撓性及び可視光に対する透過性を有する材料としては、例えば、可撓性を有する程度の厚さのガラスや、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）等のポリエステル樹脂、ポリアクリロニトリル樹脂、ポリイミド樹脂、ポリメチルメタクリレート樹脂、ポリカーボネート（P C）樹脂、ポリエーテルスルホン（P E S）樹脂、ポリアミド樹脂、シクロオレフィン樹脂、ポリスチレン樹脂、ポリアミドイミド樹脂、ポリ塩化ビニル樹脂、ポリテトラフルオロエチレン（P T F E）樹脂等が挙げられる。特に、熱膨張係数の低い材料を用いることが好ましく、例えば、ポリアミドイミド樹脂、ポリイミド樹脂、P E T等を好適に用いることができる。また、ガラス纖維に有機樹脂を含浸した基板や、無機フィラーを有機樹脂に混ぜて熱膨張係数を下げた基板を使用することもできる。このような材料を用いた基板は、重量が軽いため、該基板を用いたタッチパネルも軽量にすることができる。

10

## 【0168】

また、発光を取り出さない側の基板は、透光性を有していないために、上記に挙げた基板の他に、金属材料や合金材料を用いた金属基板、セラミック基板、または半導体基板等を用いることもできる。金属材料や合金材料は熱伝導性が高く、封止基板全体に熱を容易に伝導できるため、タッチパネルの局所的な温度上昇を抑制することができ、好ましい。可撓性や曲げ性を得るために、金属基板の厚さは、10 μm以上200 μm以下が好ましく、20 μm以上50 μm以下であることがより好ましい。

20

## 【0169】

金属基板を構成する材料としては、特に限定はないが、例えば、アルミニウム、銅、ニッケル、又はアルミニウム合金もしくはステンレス等の金属の合金などを好適に用いることができる。

## 【0170】

また、導電性の基板の表面を酸化する、又は表面に絶縁膜を形成するなどにより、絶縁処理が施された基板を用いてもよい。例えば、スピンドルコート法やディップ法などの塗布法、電着法、蒸着法、又はスパッタリング法などを用いて絶縁膜を形成してもよいし、酸素雰囲気で放置する又は加熱するほか、陽極酸化法などによって、基板の表面に酸化膜を形成してもよい。

30

## 【0171】

可撓性を有する基板としては、上記材料を用いた層が、タッチパネルの表面を傷などから保護するハードコート層（例えば、窒化シリコン層など）や、押圧を分散可能な材質の層（例えば、アラミド樹脂層など）等と積層されて構成されていてもよい。また、水分等による表示素子の寿命の低下等を抑制するために、窒化シリコン膜、酸化窒化シリコン膜等の窒素と珪素を含む膜や、窒化アルミニウム膜等の窒素とアルミニウムを含む膜等の透水性の低い絶縁膜を有していてもよい。

## 【0172】

基板は、複数の層を積層して用いることもできる。特に、ガラス層を有する構成とすると、水や酸素に対するバリア性を向上させ、信頼性の高いタッチパネルとすることができます。

40

## 【0173】

例えば、表示素子に近い側からガラス層、接着層、及び有機樹脂層を積層した基板を用いることができる。当該ガラス層の厚さとしては20 μm以上200 μm以下、好ましくは25 μm以上100 μm以下とする。このような厚さのガラス層は、水や酸素に対する高いバリア性と可撓性を同時に実現できる。また、有機樹脂層の厚さとしては、10 μm以上200 μm以下、好ましくは20 μm以上50 μm以下とする。このような有機樹脂層を設けることにより、ガラス層の割れやクラックを抑制し、機械的強度を向上させることができる。このようなガラス材料と有機樹脂の複合材料を基板に適用することにより、極めて信頼性が高いフレキシブルなタッチパネルとすることができます。

## 【0174】

{トランジスタ}

50

トランジスタは、ゲート電極として機能する導電層と、半導体層と、ソース電極として機能する導電層と、ドレイン電極として機能する導電層と、ゲート絶縁層として機能する絶縁層と、を有する。上記では、ボトムゲート構造のトランジスタを適用した場合を示している。

#### 【0175】

なお、本発明の一態様のタッチパネルが有するトランジスタの構造は特に限定されない。例えば、プレーナ型のトランジスタとしてもよいし、スタガ型のトランジスタとしてもよいし、逆スタガ型のトランジスタとしてもよい。また、トップゲート型又はボトムゲート型のいずれのトランジスタ構造としてもよい。または、チャネルの上下にゲート電極が設けられていてもよい。トランジスタに用いる半導体材料は特に限定されず、例えば、酸化物半導体、シリコン、ゲルマニウム等が挙げられる。10

#### 【0176】

トランジスタに用いる半導体材料の結晶性についても特に限定されず、非晶質半導体、結晶性を有する半導体（微結晶半導体、多結晶半導体、単結晶半導体、又は一部に結晶領域を有する半導体）のいずれを用いてもよい。結晶性を有する半導体を用いると、トランジスタ特性の劣化を抑制できるため好ましい。

#### 【0177】

また、トランジスタに用いる半導体材料としては、例えば、第14族の元素、化合物半導体又は酸化物半導体を半導体層に用いることができる。代表的には、シリコンを含む半導体、ガリウムヒ素を含む半導体又はインジウムを含む酸化物半導体などを適用できる。20

#### 【0178】

特に、トランジスタのチャネルが形成される半導体に、酸化物半導体を適用することが好ましい。特にシリコンよりもバンドギャップの大きな酸化物半導体を適用することが好ましい。シリコンよりもバンドギャップが広く、且つキャリア密度の小さい半導体材料を用いると、トランジスタのオフ状態における電流を低減できるため好ましい。

#### 【0179】

例えば、上記酸化物半導体として、少なくともインジウム（In）もしくは亜鉛（Zn）を含むことが好ましい。より好ましくは、In-M-Zn酸化物（MはAl、Ti、Ga、Ge、Y、Zr、Sn、La、Ce、HfまたはNd等の金属）で表記される酸化物を含む。30

#### 【0180】

特に、半導体層として、複数の結晶部を有し、当該結晶部はc軸が半導体層の被形成面、または半導体層の上面に対し概略垂直に配向し、且つ隣接する結晶部間には粒界が確認できない酸化物半導体膜を用いることが好ましい。

#### 【0181】

このような酸化物半導体は、結晶粒界を有さないために表示パネルを湾曲させたときの応力によって酸化物半導体膜にクラックが生じてしまうことが抑制される。したがって、可撓性を有し、湾曲させて用いるタッチパネルなどに、このような酸化物半導体を好適に用いることができる。

#### 【0182】

また半導体層としてこのような結晶性を有する酸化物半導体を用いることで、電気特性的変動が抑制され、信頼性の高いトランジスタを実現できる。

#### 【0183】

また、シリコンよりもバンドギャップの大きな酸化物半導体を用いたトランジスタは、その低いオフ電流により、トランジスタと直列に接続された容量に蓄積した電荷を長期間に亘って保持することが可能である。このようなトランジスタを画素に適用することで、各表示領域に表示した画像の階調を維持しつつ、駆動回路を停止することも可能となる。その結果、極めて消費電力の低減された表示装置を実現できる。

#### 【0184】

半導体層は、例えば少なくともインジウム（In）、亜鉛（Zn）及びM（Al、Ti40

10

20

30

40

50

、 Ga、 Y、 Zr、 La、 Ce、 Sn または Hf 等の金属 ) を含む In - M - Zn 酸化物で表記される膜を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

#### 【 0185 】

スタビライザーとしては、上記 M で記載の金属を含め、例えば、ガリウム ( Ga ) 、スズ ( Sn ) 、ハフニウム ( Hf ) 、アルミニウム ( Al ) 、またはジルコニウム ( Zr ) 等がある。また、他のスタビライザーとしては、ラントノイドである、ラントン ( La ) 、セリウム ( Ce ) 、プラセオジム ( Pr ) 、ネオジム ( Nd ) 、サマリウム ( Sm ) 、ユウロピウム ( Eu ) 、ガドリニウム ( Gd ) 、テルビウム ( Tb ) 、ジスプロシウム ( Dy ) 、ホルミウム ( Ho ) 、エルビウム ( Er ) 、ツリウム ( Tm ) 、イッテルビウム ( Yb ) 、ルテチウム ( Lu ) 等がある。

10

#### 【 0186 】

半導体層を構成する酸化物半導体として、例えば、In - Ga - Zn 系酸化物、In - Al - Zn 系酸化物、In - Sn - Zn 系酸化物、In - Hf - Zn 系酸化物、In - La - Zn 系酸化物、In - Ce - Zn 系酸化物、In - Pr - Zn 系酸化物、In - Nd - Zn 系酸化物、In - Sm - Zn 系酸化物、In - Eu - Zn 系酸化物、In - Gd - Zn 系酸化物、In - Tb - Zn 系酸化物、In - Dy - Zn 系酸化物、In - Ho - Zn 系酸化物、In - Er - Zn 系酸化物、In - Tm - Zn 系酸化物、In - Yb - Zn 系酸化物、In - Lu - Zn 系酸化物、In - Sn - Ga - Zn 系酸化物、In - Hf - Ga - Zn 系酸化物、In - Al - Ga - Zn 系酸化物、In - Sn - Al - Zn 系酸化物、In - Sn - Hf - Zn 系酸化物、In - Hf - Al - Zn 系酸化物を用いることができる。

20

#### 【 0187 】

なお、ここで、In - Ga - Zn 系酸化物とは、In と Ga と Zn を主成分として有する酸化物という意味であり、In と Ga と Zn の比率は問わない。また、In と Ga と Zn 以外の金属元素が入っていてもよい。

#### 【 0188 】

また、半導体層と、導電層は、上記酸化物のうち、同一の金属元素を有していてもよい。半導体層と、導電層を同一の金属元素とすることで、製造コストを低減させることができる。例えば、同一の金属組成の金属酸化物ターゲットを用いることで製造コストを低減させることができる。また同一の金属組成の金属酸化物ターゲットを用いることによって、半導体層と、導電層を加工する際のエッチングガスまたはエッチング液を共通して用いることができる。ただし、半導体層と、導電層は、同一の金属元素を有していても、組成が異なる場合がある。例えば、トランジスタ及び容量素子の作製工程中に、膜中の金属元素が脱離し、異なる金属組成となる場合がある。

30

#### 【 0189 】

なお、半導体層が In - M - Zn 酸化物であるとき、Zn および O を除いての In と M の原子数比率は、In および M の和を 100 atomic % としたとき、好ましくは In が 25 atomic % より高く、M が 75 atomic % 未満、さらに好ましくは In が 34 atomic % より高く、M が 66 atomic % 未満とする。

40

#### 【 0190 】

半導体層は、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタのオフ電流を低減することができる。

#### 【 0191 】

半導体層の厚さは、3 nm 以上 200 nm 以下、好ましくは 3 nm 以上 100 nm 以下、さらに好ましくは 3 nm 以上 50 nm 以下とする。

#### 【 0192 】

半導体層が In - M - Zn 酸化物 ( M は Al、Ti、Ga、Ge、Y、Zr、Sn、La、Ce、Hf または Nd ) の場合、In - M - Zn 酸化物を成膜するために用いるスパ

50

ツタリングターゲットの金属元素の原子数比は、In - M、Zn - Mを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In : M : Zn = 1 : 1 : 1、In : M : Zn = 1 : 1 : 1.2、In : M : Zn = 3 : 1 : 2、4 : 2 : 3が好ましい。なお、成膜される半導体層の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。

#### 【0193】

半導体層としては、キャリア密度の低い酸化物半導体膜を用いる。例えば、半導体層は、キャリア密度が $1 \times 10^{17}$ 個/cm<sup>3</sup>以下、好ましくは $1 \times 10^{15}$ 個/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{13}$ 個/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{11}$ 個/cm<sup>3</sup>以下の酸化物半導体膜を用いる。10

#### 【0194】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、半導体層のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0195】

半導体層において、第14族元素の一つであるシリコンや炭素が含まれると、半導体層において酸素欠損が増加し、n型化してしまう。このため、半導体層におけるシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18}$ atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$ atoms/cm<sup>3</sup>以下とする。20

#### 【0196】

また、半導体層において、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$ atoms/cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、半導体層のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

#### 【0197】

また、半導体層に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。従って、当該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>以下にすることが好ましい。30

#### 【0198】

また、半導体層は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、後述するC AAC - OS (C Axis Aligned Crystaline Oxide Semiconductor)、多結晶構造、後述する微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、C AAC - OSは最も欠陥準位密度が低い。40

#### 【0199】

半導体層は、例えば非晶質構造でもよい。非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

#### 【0200】

なお、半導体層が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、C AAC - OSの領域、単結晶構造の領域の二種以上を有する混合膜であってもよい。また、混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、C AAC - OSの領域、単結晶構造の領域のいずれか二種以上の領域の積層構造を有する場合がある50

。

### 【0201】

または、トランジスタのチャネルが形成される半導体に、シリコンを用いることが好ましい。シリコンとしてアモルファスシリコンを用いてもよいが、特に結晶性を有するシリコンを用いることが好ましい。例えば、微結晶シリコン、多結晶シリコン、単結晶シリコンなどを用いることが好ましい。特に、多結晶シリコンは、単結晶シリコンに比べて低温で形成でき、且つアモルファスシリコンに比べて高い電界効果移動度と高い信頼性を備える。このような多結晶半導体を画素に適用することで画素の開口率を向上させることができる。また極めて高精細に画素を有する場合であっても、ゲート駆動回路とソース駆動回路を画素と同一基板上に形成することが可能となり、電子機器を構成する部品数を低減することができる。10

### 【0202】

#### {導電層}

トランジスタのゲート、ソースおよびドレインのほか、タッチパネルを構成する各種配線および電極などの導電層に用いることのできる材料としては、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタンクステンなどの金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タンクステン膜上にアルミニウム膜を積層する二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タンクステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。また、マンガンを含む銅を用いると、エッチングによる形状の制御性が高まるため好ましい。20

### 【0203】

また、透光性を有する導電性材料としては、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などの導電性酸化物またはグラフェンを用いることができる。または、金、銀、白金、マグネシウム、ニッケル、タンクステン、クロム、モリブデン、鉄、コバルト、銅、パラジウム、またはチタンなどの金属材料や、該金属材料を含む合金材料を用いることができる。または、該金属材料の窒化物（例えば、窒化チタン）などを用いてもよい。なお、金属材料、合金材料（またはそれらの窒化物）を用いる場合には、透光性を有する程度に薄くすればよい。また、上記材料の積層膜を導電層として用いることができる。例えば、銀とマグネシウムの合金とインジウムスズ酸化物の積層膜などを用いると、導電性を高めることができるため好ましい。30

### 【0204】

または、導電層として、半導体層と同様の酸化物半導体を用いることが好ましい。このとき導電層が、半導体層のチャネルが形成される領域よりも低い電気抵抗を呈するように、形成されていることが好ましい。40

### 【0205】

例えばこのような導電層を、トランジスタの第2のゲート電極として機能する導電層に適用することができる。または、透光性を有する他の導電層にも適用することができる。

### 【0206】

#### {酸化物半導体の抵抗率の制御方法}

半導体層及び導電層に用いることのできる酸化物半導体膜は、膜中の酸素欠損及び/又は膜中の水素、水等の不純物濃度によって、抵抗率を制御することができる半導体材料である。そのため、半導体層及び導電層へ酸素欠損及び/又は不純物濃度が増加する処理、50

または酸素欠損及び／又は不純物濃度が低減する処理を選択することによって、それぞれの酸化物半導体膜の抵抗率を制御することができる。

#### 【0207】

具体的には、導電層に用いる酸化物半導体膜にプラズマ処理を行い、該酸化物半導体の膜中の酸素欠損を増加させる、および／または酸化物半導体の膜中の水素、水等の不純物を増加させることによって、キャリア密度が高く、抵抗率が低い酸化物半導体膜とすることができる。また、酸化物半導体膜に水素を含む絶縁膜を接して形成し、該水素を含む絶縁膜から酸化物半導体膜に水素を拡散させることによって、キャリア密度が高く、抵抗率が低い酸化物半導体膜とすることができます。

#### 【0208】

一方、トランジスタのチャネル領域として機能する半導体層は、水素を含む絶縁膜と接しない構成とする。半導体層と接する絶縁膜の少なくとも一つに酸素を含む絶縁膜、別言すると、酸素を放出することが可能な絶縁膜を適用することで、半導体層に酸素を供給することができる。酸素が供給された半導体層は、膜中または界面の酸素欠損が補填され抵抗率が高い酸化物半導体膜となる。なお、酸素を放出することが可能な絶縁膜としては、例えば、酸化シリコン膜、または酸化窒化シリコン膜を用いることができる。

#### 【0209】

また、抵抗率が低い酸化物半導体膜を得るために、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて、水素、ボロン、リン、または窒素を酸化物半導体膜に注入してもよい。

#### 【0210】

また、抵抗率が低い酸化物半導体膜を得るために、該酸化物半導体膜にプラズマ処理を行ってもよい。例えば、該プラズマ処理としては、代表的には、希ガス（He、Ne、Ar、Kr、Xe）、水素、及び窒素の中から選ばれた一種以上を含むガスを用いたプラズマ処理が挙げられる。より具体的には、Ar雰囲気下でのプラズマ処理、Arと水素の混合ガス雰囲気下でのプラズマ処理、アンモニア雰囲気下でのプラズマ処理、Arとアンモニアの混合ガス雰囲気下でのプラズマ処理、または窒素雰囲気下でのプラズマ処理などが挙げられる。

#### 【0211】

上記プラズマ処理によって、酸化物半導体膜は、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損は、キャリアを発生する要因になる場合がある。また、酸化物半導体膜の近傍、より具体的には、酸化物半導体膜の下側または上側に接する絶縁膜から水素が供給されると、上記酸素欠損と水素が結合することで、キャリアである電子を生成する場合がある。

#### 【0212】

一方、酸素欠損が補填され、水素濃度が低減された酸化物半導体膜は、高純度真性化、又は実質的に高純度真性化された酸化物半導体膜といえる。ここで、実質的に真性とは、酸化物半導体膜のキャリア密度が、 $8 \times 10^{11}$  個 / cm<sup>3</sup> 未満、好ましくは $1 \times 10^{11}$  個 / cm<sup>3</sup> 未満、さらに好ましくは $1 \times 10^{10}$  個 / cm<sup>3</sup> 未満であることを指す。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度を低減することができる。

#### 【0213】

また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6$  μmでチャネル長が $10$  μmの素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が $1$  Vから $10$  Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$  A以下という特性を得ることができる。したがって、上述した高純度真性または実質的に高純度真性である酸化物半導体膜を用いる半導体層をチャネル領域に用いるトランジスタは、電気

10

20

30

40

50

特性の変動が小さく、信頼性の高いトランジスタとなる。

【0214】

導電層として用いる酸化物半導体膜と接する絶縁膜として、例えば、水素を含む絶縁膜、別言すると水素を放出することが可能な絶縁膜、代表的には窒化シリコン膜を用いることで、導電層に水素を供給することができる。水素を放出することが可能な絶縁膜としては、膜中の含有水素濃度が  $1 \times 10^{-2}$  atoms / cm<sup>3</sup> 以上であると好ましい。このような絶縁膜を導電層に接して形成することで、導電層に効果的に水素を含有させることができ。このように、半導体層及び導電層に接する絶縁膜の構成を変えることによって、酸化物半導体膜の抵抗率を制御することができる。

【0215】

酸化物半導体膜に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損を形成する。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。したがって、水素が含まれている絶縁膜と接して設けられた導電層は、半導体層よりもキャリア密度の高い酸化物半導体膜となる。

【0216】

トランジスタのチャネル領域が形成される半導体層は、水素ができる限り低減されていることが好ましい。具体的には、半導体層において、二次イオン質量分析法 (S I M S : Secondary Ion Mass Spectrometry) により得られる水素濃度を、 $2 \times 10^{-2}$  atoms / cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{-1}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{-1}$  atoms / cm<sup>3</sup> 以下、 $5 \times 10^{-1}$  atoms / cm<sup>3</sup> 未満、好ましくは  $1 \times 10^{-1}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $5 \times 10^{-1}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{-1}$  atoms / cm<sup>3</sup> 以下とする。

【0217】

一方、導電層は、半導体層よりも水素濃度及び / 又は酸素欠損量が多く、抵抗率が低い酸化物半導体膜である。導電層に含まれる水素濃度は、 $8 \times 10^{-1}$  atoms / cm<sup>3</sup> 以上、好ましくは  $1 \times 10^{-2}$  atoms / cm<sup>3</sup> 以上、より好ましくは  $5 \times 10^{-2}$  atoms / cm<sup>3</sup> 以上である。また、半導体層と比較して、導電層に含まれる水素濃度は 2 倍以上、好ましくは 10 倍以上である。また、導電層の抵抗率が、半導体層の抵抗率の  $1 \times 10^{-8}$  倍以上  $1 \times 10^{-1}$  倍未満であることが好ましく、代表的には  $1 \times 10^{-3}$  cm 以上  $1 \times 10^{-4}$  cm 未満、さらに好ましくは、抵抗率が  $1 \times 10^{-3}$  cm 以上  $1 \times 10^{-1}$  cm 未満であるとよい。

【0218】

{ 絶縁層 }

各絶縁層、オーバーコート、スペーサ等に用いることのできる絶縁材料としては、例えば、アクリル、エポキシなどの樹脂、シロキサン結合を有する樹脂の他、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウムなどの無機絶縁材料を用いることもできる。

【0219】

{ 接着層 }

接着層としては、熱硬化樹脂や光硬化樹脂、2液混合型の硬化性樹脂などの硬化性樹脂を用いることができる。例えば、アクリル、ウレタン、エポキシなどの樹脂、またはシリコーンなどのシロキサン結合を有する樹脂などの樹脂を用いることができる。

【0220】

{ 接続層 }

接続層としては、異方性導電フィルム (A C F : Anisotropic Conductive Film) や、異方性導電ペースト (A C P : Anisotropic Conductive Paste) などを用いることができる。

10

20

30

40

40

50

## 【0221】

## {着色層}

着色層に用いることのできる材料としては、金属材料、樹脂材料、顔料または染料が含まれた樹脂材料などが挙げられる。

## 【0222】

以上が各構成要素についての説明である。

## 【0223】

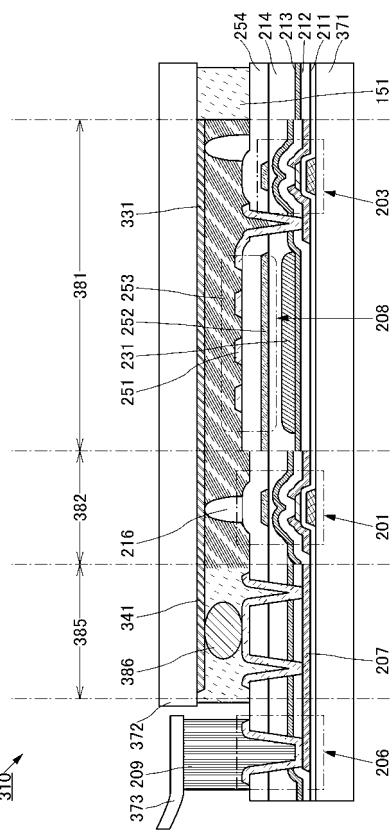

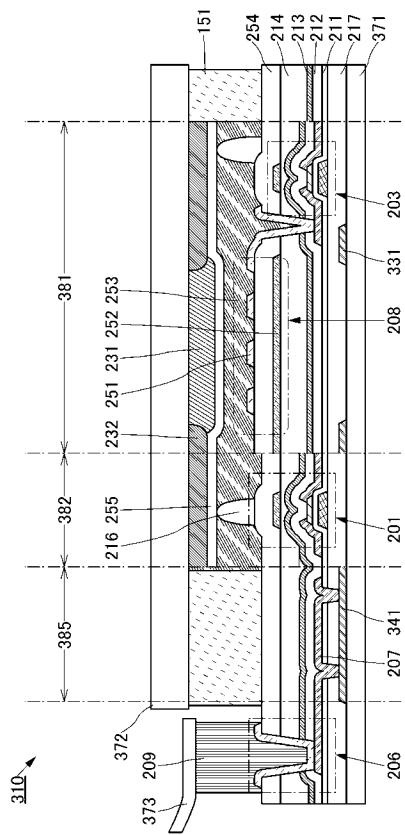

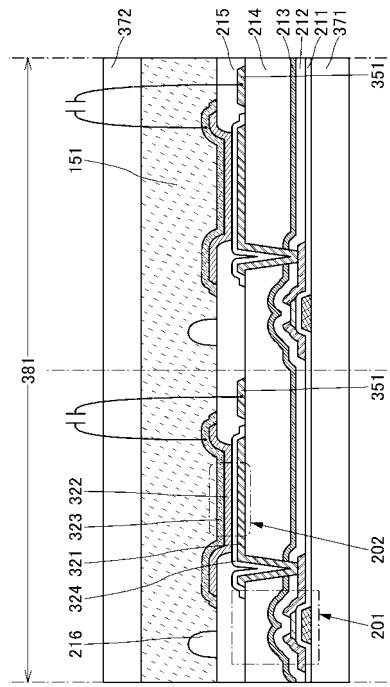

## 〔断面構成例1-2〕

図21には、上記とは一部の構成の異なるタッチパネルの断面構成例について示している。なお、上記と重複する部分については説明を省略し、相違点について説明する。

10

## 【0224】

図21では、着色層231が基板371側に配置されている例を示している。具体的には、着色層231が絶縁層213の上面に接して設けられている。また着色層231を覆って平坦化層として機能する絶縁層214が設けられている。

## 【0225】

このような構成とすることで、基板372の構成をより簡略化することができる。例えば図21では、基板372上には導電層331及び導電層341のみが形成されている例を示している。なお、基板372上には必要であれば配向膜等が設けられていてもよい。

20

## 【0226】

## 〔断面構成例1-3〕

図22では、図20におけるトランジスタ201及びトランジスタ203に、トップゲート型のトランジスタを適用した場合の例を示している。

## 【0227】

各トランジスタは半導体層を有し、半導体層上に絶縁層211を介してゲート電極が設けられている。また半導体層は低抵抗化された領域を有していてもよい。当該領域は、ソースまたはドレインとして機能する。

## 【0228】

トランジスタのソース電極及びドレイン電極は、絶縁層213上に設けられ、絶縁層213、絶縁層212、絶縁層211に設けられた開口を介して、半導体層の低抵抗化された領域と電気的に接続している。

30

## 【0229】

半導体層の低抵抗化された領域は、例えばトランジスタのチャネルが形成される領域よりも不純物を多く含む領域、キャリア濃度の高い領域、または結晶性が低い領域、などとすることができます。導電性を高める効果を奏する不純物は、半導体層に適用される半導体によって異なるが、代表的にはリンなどのn型の導電性を付与しうる元素、ホウ素などのp型の導電性を付与しうる元素、ヘリウム、ネオン、アルゴンなどの希ガスの他、水素、リチウム、ナトリウム、マグネシウム、アルミニウム、窒素、フッ素、カリウム、カルシウムなどが挙げられる。そのほかチタン、鉄、ニッケル、銅、亜鉛、銀、インジウム、スズなども、半導体の導電性に影響する不純物として機能する。例えば領域262や領域263は、トランジスタのチャネルが形成される領域よりも上記不純物を多く含む。

40

## 【0230】

## 〔断面構成例1-4〕

図23では、図20等と比較して導電層252の位置が異なる場合の例を示している。具体的には導電層252が絶縁層212と絶縁層213の間に位置する構成の例を示している。

## 【0231】

導電層252には、一例としては、上述した透光性の導電性材料を用いることができる。

## 【0232】

また、一例としては、導電層252が低抵抗化された酸化物半導体を含んで構成されて

50

いることが好ましい。特に、タッチパネル310が有するトランジスタの半導体層に酸化物半導体を用いた場合、これよりも抵抗率の低い酸化物半導体を適用することが好ましい。

**【0233】**

例えば、上述した酸化物半導体の抵抗率の制御方法により、導電層252を低抵抗化させることができる。

**【0234】**

またこのとき、導電層252を覆う絶縁層213としては、上述した水素を多く含む絶縁層を用いることが好ましい。特に、窒化シリコンを含む絶縁膜を含むことが好ましい。

**【0235】**

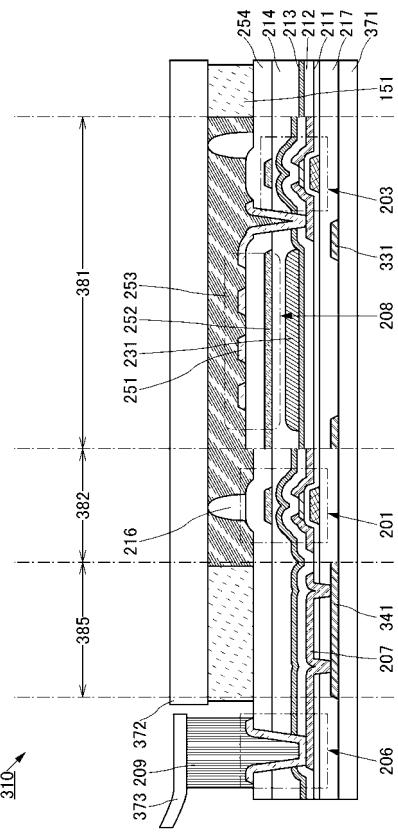

**[断面構成例2]**

以下では、上記断面構成例とは一部の構成が異なるタッチパネルの断面構成例について説明する。

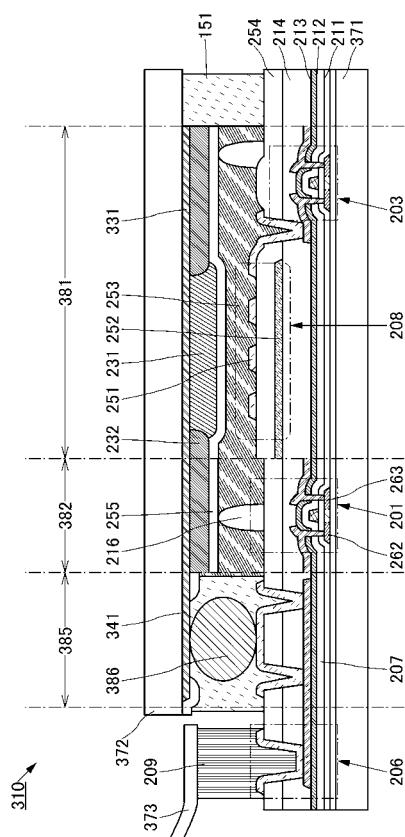

**【0236】**

**[断面構成例2-1]**

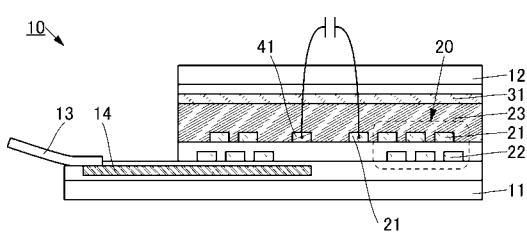

図24は、導電層331及び導電層341を基板371側に配置している点で、上記断面構成例と相違している。

**【0237】**

導電層331及び導電層341は、基板371上に設けられている。また導電層331及び導電層341を覆って絶縁層217が設けられている。また絶縁層217上に、トランジスタ201やトランジスタ203等が設けられている。

**【0238】**

また接続部385において、絶縁層217に設けられた開口を介して、導電層341と導電層207とが電気的に接続している。

**【0239】**

ここで、導電層331と導電層252との間に生じる容量を利用して、タッチ動作を検出することができる。

**【0240】**

このような構成とすることで、基板372の構成を簡略化することができる。

**【0241】**

なお、このとき導電層331及び導電層341には耐熱性の高い導電性材料を用いることが好ましい。また、導電層331として、金属などの遮光性を有する材料を用いる場合には、図24に示すように着色層231と重なる部分に開口を設けることが好ましい。

**【0242】**

また図24に示すように、導電層331はトランジスタ203等と重ならないように配置することが好ましい。または、導電層331のトランジスタ203等と重なる部分に開口を有する構成とすることが好ましい。こうすることで、導電層331の電位の変化に起因してトランジスタ203等が誤動作してしまうことを抑制できる。

**【0243】**

**[断面構成例2-2]**

図25は、図24で示した構成に、図21と同様に着色層231を基板371側に配置した例を示している。

**【0244】**

このように、導電層331、導電層341、及び着色層231を基板371側に設けることで、基板372上になにも形成しない構成とすることができます。なお、基板372及び基板371の液晶層と接する領域には、配向膜を設けてもよい。

**【0245】**

**[構成例2]**

以下では、上記構成例1とは一部の構成が異なるタッチパネルの構成例について図面を参照して説明する。

10

20

30

40

50

## 【0246】

以下で説明する本発明の一態様のタッチパネルは、タッチセンサを構成する一対の導電層の少なくとも一つを、液晶素子が有する一対の導電層の少なくとも一つと同一の導電膜で形成される。タッチセンサを構成する一対の導電層の少なくとも一つと、液晶素子が有する一対の導電層の少なくとも一つとは、同一面上に配置される。または、タッチセンサを構成する一対の導電層の少なくとも一つは、液晶素子が有する一対の導電層の少なくとも一つを兼ねて設けられる。つまり、一つの導電膜が、タッチセンサを構成する一対の導電層の少なくとも一つとしての機能と、液晶素子が有する一対の導電層の少なくとも一つとしての機能とを、両方を併せ持つ。これにより、タッチパネルの作製工程が簡略化され、より作製コストを低減することができる。

10

## 【0247】

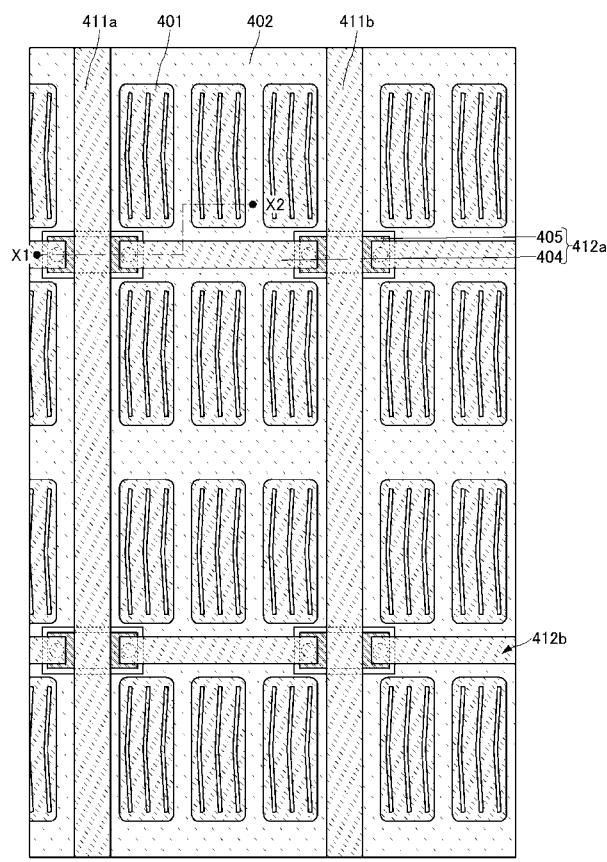

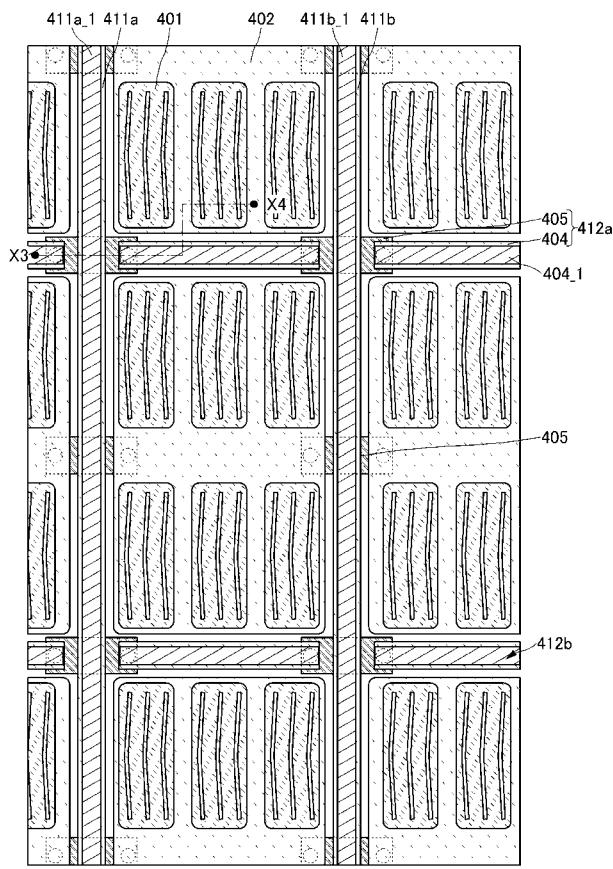

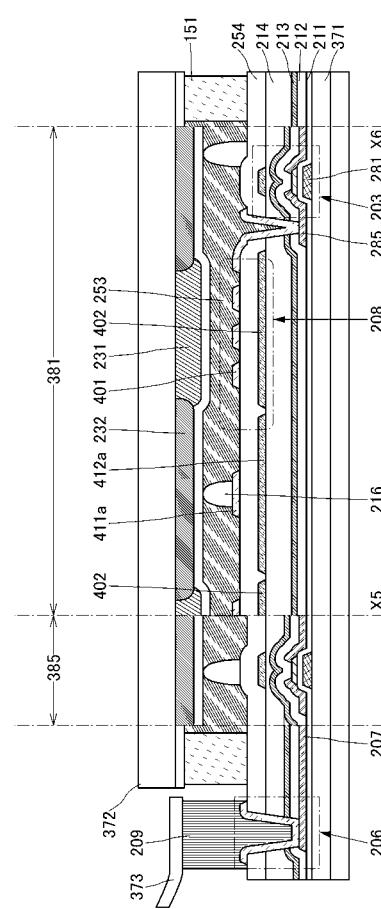

## 〔構成例2-1〕

図26は、液晶素子の電極として機能する一対の導電層と、タッチセンサを構成する一対の導電層のレイアウトの例を示す上面概略図である。ここでは、FFSモードが適用された液晶素子を例に挙げて説明する。

## 【0248】

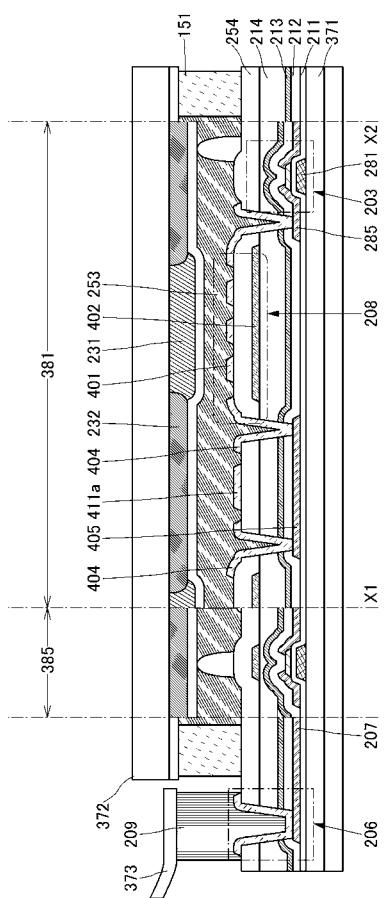

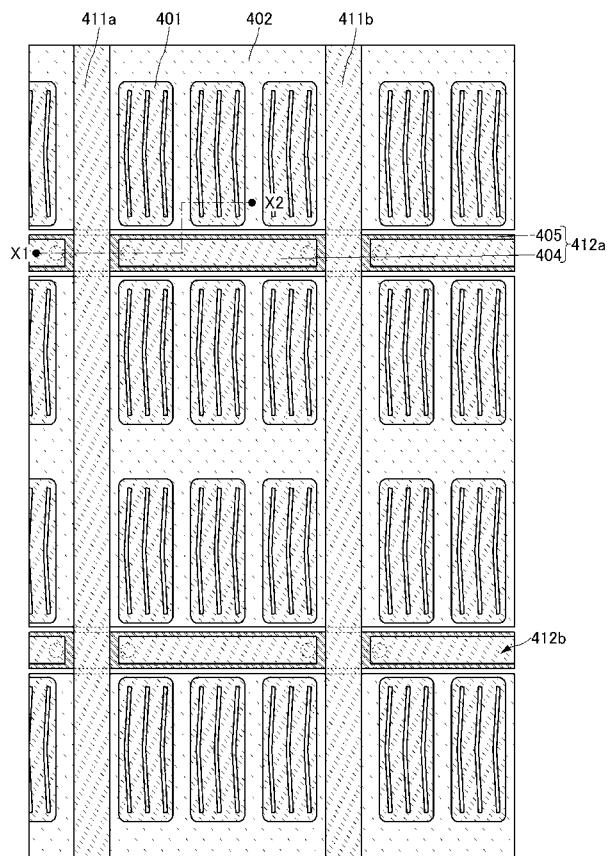

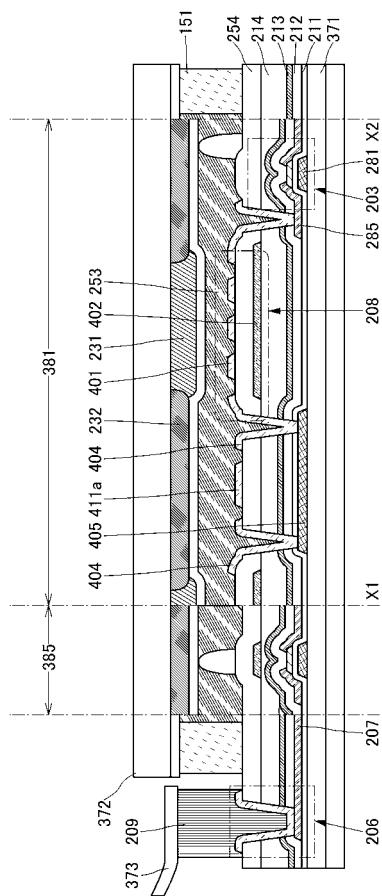

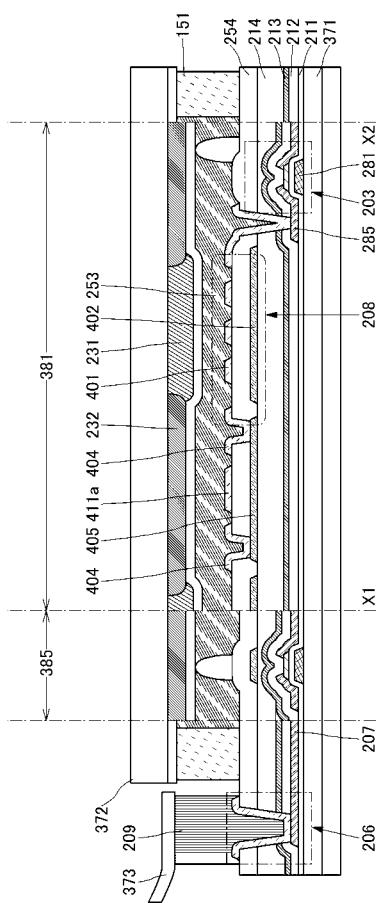

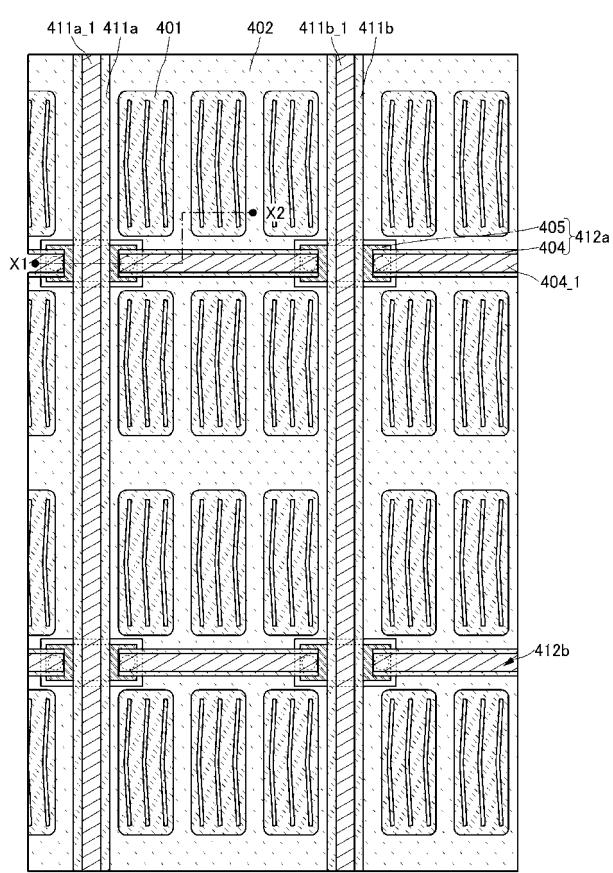

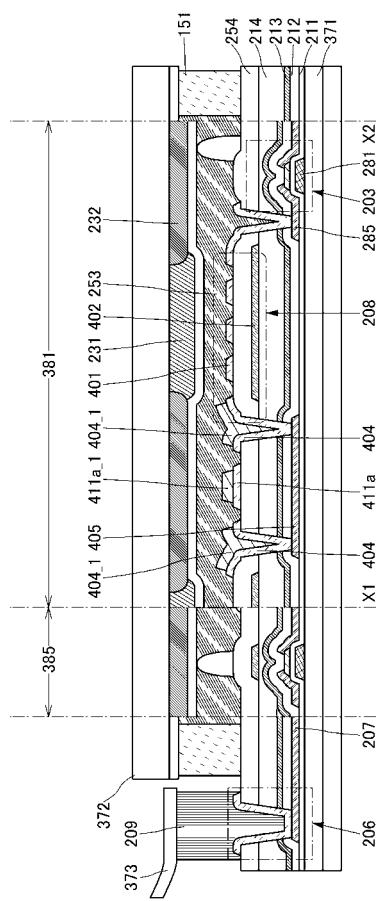

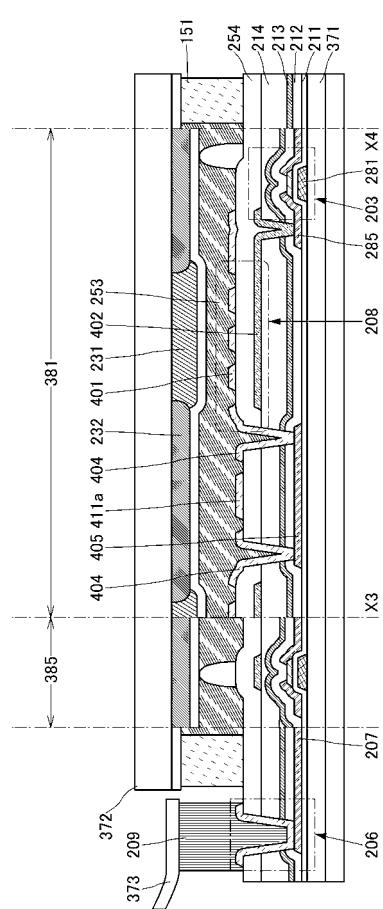

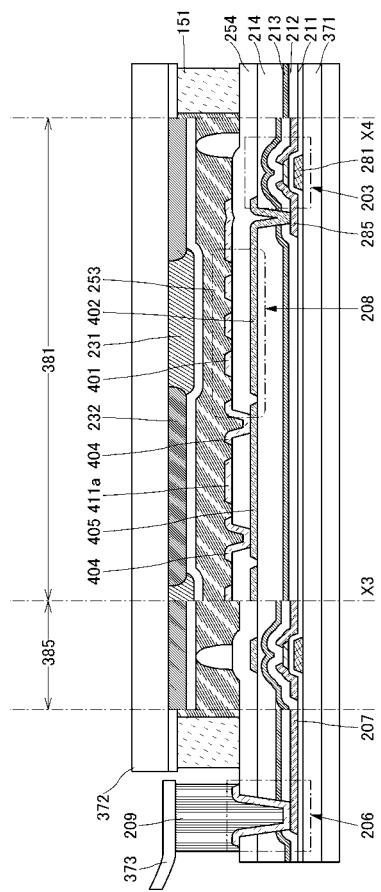

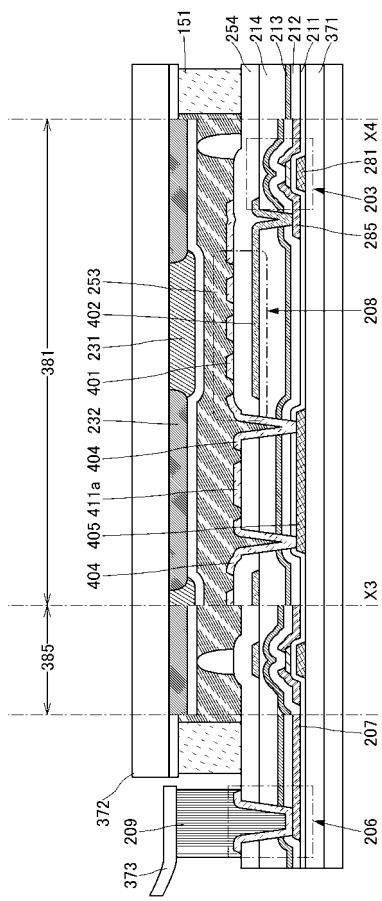

また図27には、図26中の切断線X1-X2に対応する部分の断面を含む、タッチパネルの断面概略図を示す。図26および図27は、図8(A)に対応している。

20

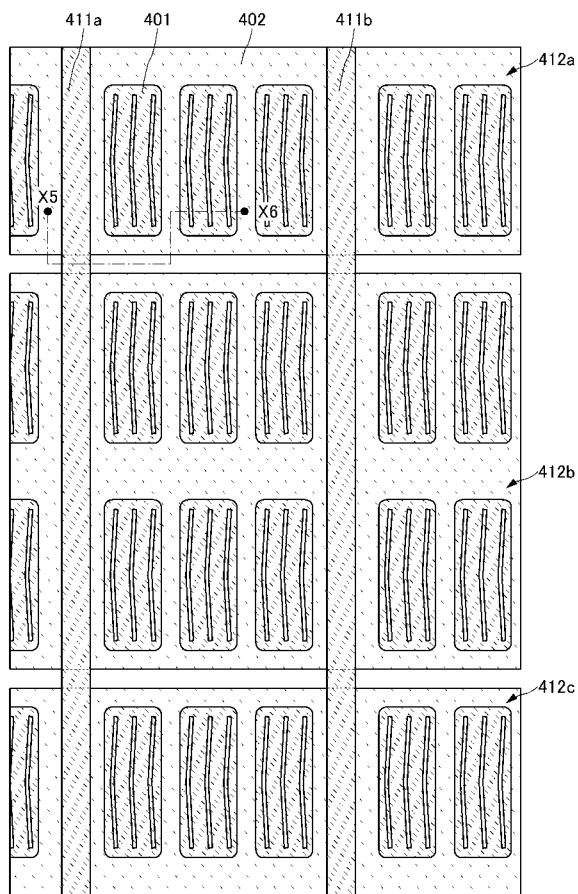

## 【0249】

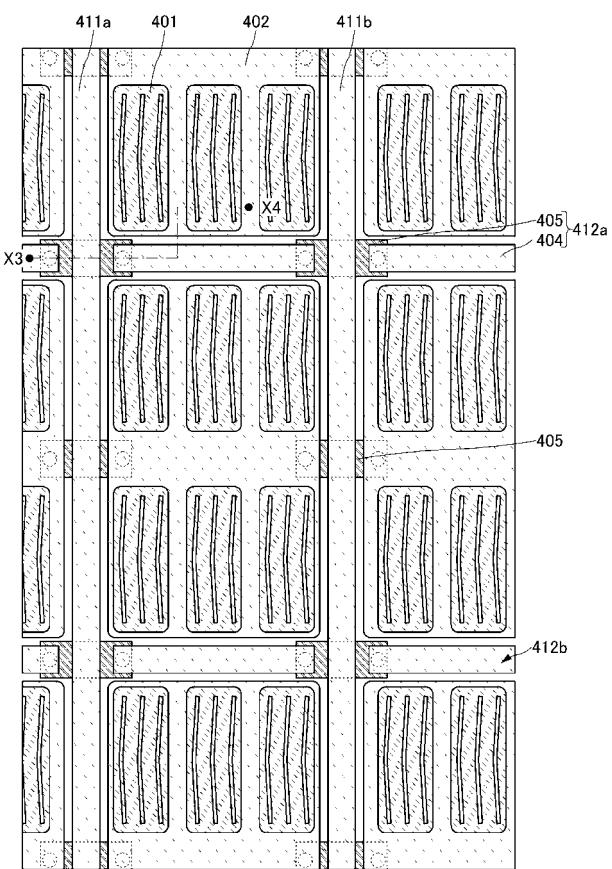

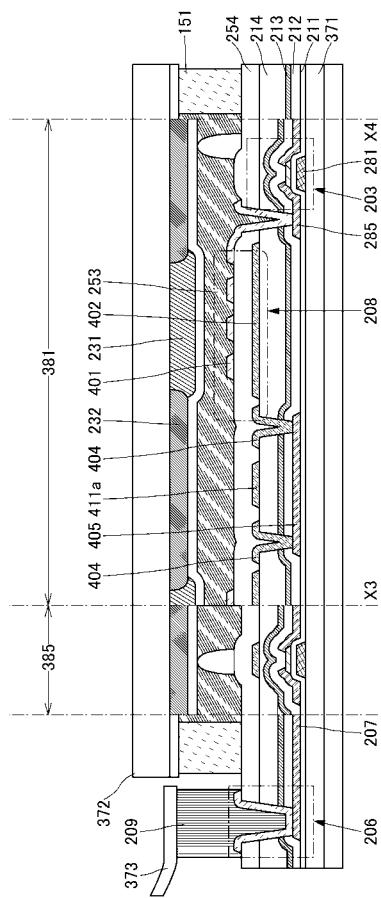

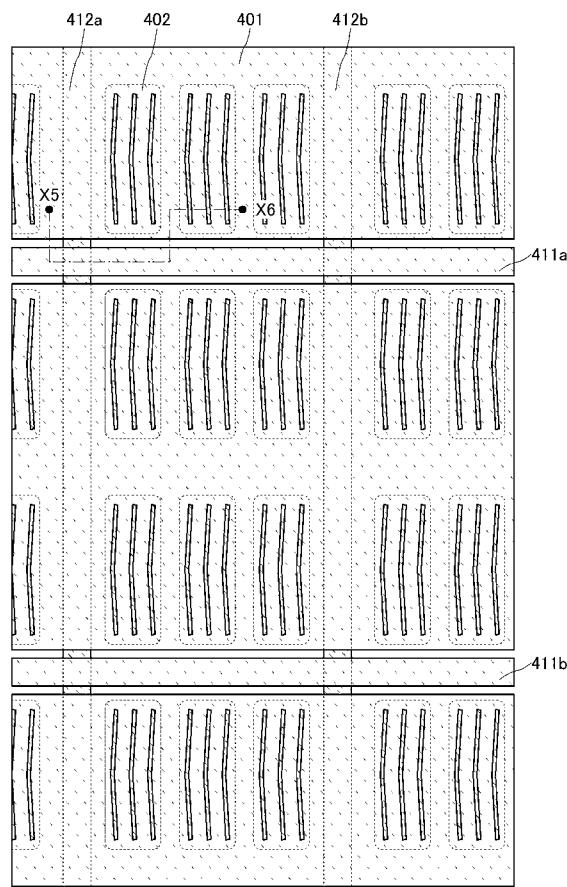

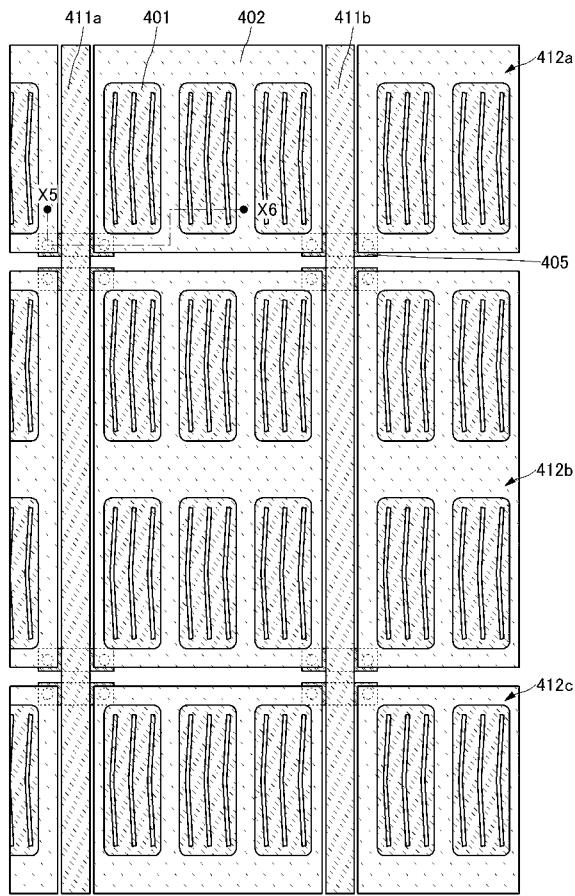

導電層401は島状の形状を有し、X方向及びY方向にマトリクス状に配列している。そして、導電層401にスリットが設けられている。導電層402は各導電層401と重なるように配置されている。ここで導電層401が画素電極として機能し、導電層402が共通電極として機能する。なお、ここでは上側の導電層401が画素電極であり、下側の導電層402が共通電極である場合について説明するが、これらの関係を逆転させてもよい。

20

## 【0250】

Y方向に延在する導電層411a及び導電層411bは、それぞれ隣接する2つの導電層401の間に位置するように配置されている。

## 【0251】

X方向に延在する導電層412aは、導電層404と導電層405により構成されている。導電層404は長辺方向がX方向と平行な帯状の形状を有し、例えば、導電層411aと導電層411bとの間に設けられている。また導電層405は、導電層411aまたは導電層411bと重なる部分を有し、導電層411aまたは導電層411bを挟む2つの導電層404を、コントクトホールを介して、電気的に接続する。導電層405と導電層411aまたは導電層411bとは、図示しない絶縁層を介して重なっている。なお、導電層405は、図28に示すように、X方向に延在して配置されていてもよい。このようにすることにより、導電層404の配線抵抗を実質的に低減することができる。

30

## 【0252】

なお、図26または図28において、導電層411a及び導電層411bは、X方向に延在するように配置し、導電層412a及び導電層412bは、Y方向に延在するように配置してもよい。

40

## 【0253】

ここで、導電層411a、導電層411b、導電層404、及び導電層401は、それぞれ同一の導電膜を加工することにより形成されている。したがって、導電層411a、導電層411b、導電層404、及び導電層401は、同一面上に配置されていることとなる。

## 【0254】

なお、ここでは導電層405としてトランジスタのソース電極及びドレイン電極285と同一の導電膜を加工して形成した構成とした。この場合には、導電層405の下に、ゲート電極などが配置されていても、問題なくレイアウトすることができる。よって、導電

50

層405は、ゲート電極や、ゲート電極と同一の導電膜を加工して形成された膜と、重ねて配置することができる。ただし、本発明の一態様は、これに限られず、トランジスタのゲート電極281、半導体層、またはそのほかの導電層と同一の導電膜を加工して導電層405を形成することができる。

#### 【0255】

一例として、導電層405を、ゲート電極と同一の導電膜を加工して形成した場合を図29に示す。この場合には、導電層405の上に、ソース電極及びドレイン電極285などが配置されていても、問題なくレイアウトすることができる。よって、導電層405は、ソース電極及びドレイン電極285や、ソース電極及びドレイン電極285と同一の導電膜を加工して形成された膜と、重ねたり、交差させて配置することができる。つまり、ソース信号線（映像信号を各画素に伝達する機能を有する配線）と、導電層411aまたは導電層411bとを、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。

10

#### 【0256】

または、導電層405を、導電層402と同一の導電膜を加工して形成した場合を図30に示す。この場合には、導電層405の下に、ソース電極及びドレイン電極285やゲート電極などが配置されていても、問題なくレイアウトすることができる。よって、導電層405は、ゲート電極や、ソース電極及びドレイン電極285や、ゲート電極と同一の導電膜を加工して形成された膜や、ソース電極及びドレイン電極285と同一の導電膜を加工して形成された膜と、重ねたり、交差させて配置することができる。つまり、ソース信号線（映像信号を各画素に伝達する機能を有する配線）と、導電層411aまたは導電層411bとを、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。または、ゲート信号線（各画素を選択する信号を伝達する機能を有する配線）と導電層404または導電層405と、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。

20

#### 【0257】

なお、図26または図28において、導電層411a及び導電層411bは、X方向に延在するように配置し、導電層412a及び導電層412bは、Y方向に延在するように配置する場合には、配置される方向が異なるため、導電層412a及び導電層412bをゲート信号線と重ねて配置するのではなくソース信号線と重ねて配置し、導電層411a及び導電層411bをソース信号線と重ねて配置するのではなくゲート信号線と重ねて配置することとなる。

30

#### 【0258】

なお、導電層411a、導電層411b、および、導電層404の抵抗を下げたい場合には、導電層411a、導電層411bおよび導電層404の上または下に、抵抗の低い導電層411a\_1、411b\_1、404\_1を設けてもよい。例えば、アルミニウム、銅、チタン、モリブデン、タングステン、または、それらの積層を、導電層411a、導電層411bおよび導電層404の上または下に設けてもよい。または、導電層411a\_1、411b\_1、404\_1の少なくとも一つは、メッッシュ状に加工された金属膜で構成されていてもよい。または、導電層411a\_1、411b\_1、404\_1の少なくとも一つは、金属ナノワイヤ、またはカーボンナノチューブなどで構成されていてもよい。ただし、導電層401は、透光性を有することが望ましい。したがって、導電層401の上または下には、抵抗の低い導電層を設けないことが望ましい。その場合の例を、図31と、図32に示す。

40

#### 【0259】

なお、導電層411a、導電層411bの抵抗値を実質的に下げたい場合には、導電層411aa、導電層411bbを配置してもよい。導電層411a（導電層411b）と、導電層411aa（導電層411bb）とは、コンタクトホールを介して、接続されている。その場合の例を、図33と、図34に示す。

50

**【0260】**

なお、導電層405のみを別途形成してもよいが、他の導電層と同時に形成することが好ましい。

**【0261】****[構成例2-2]**

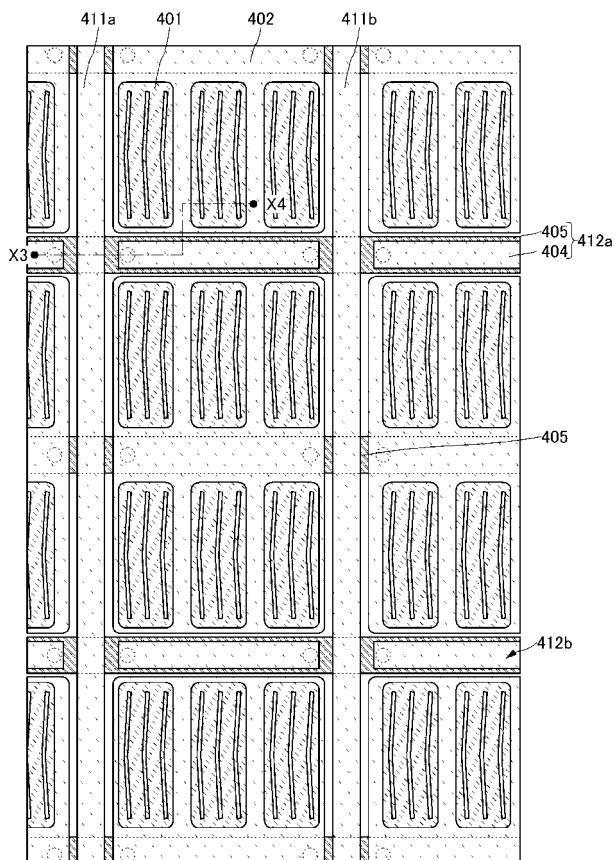

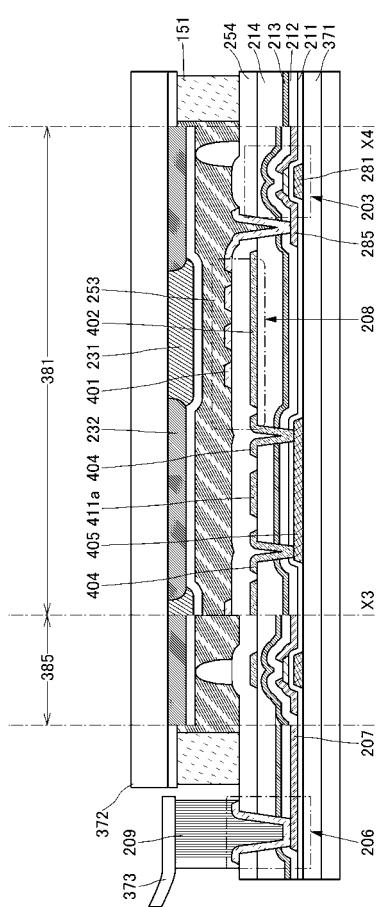

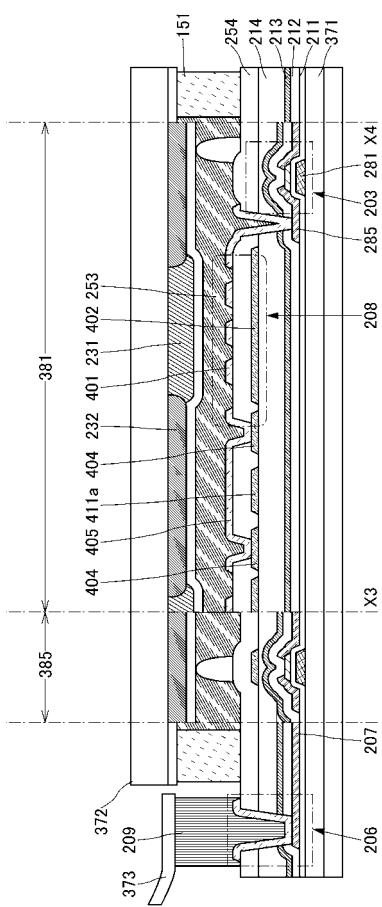

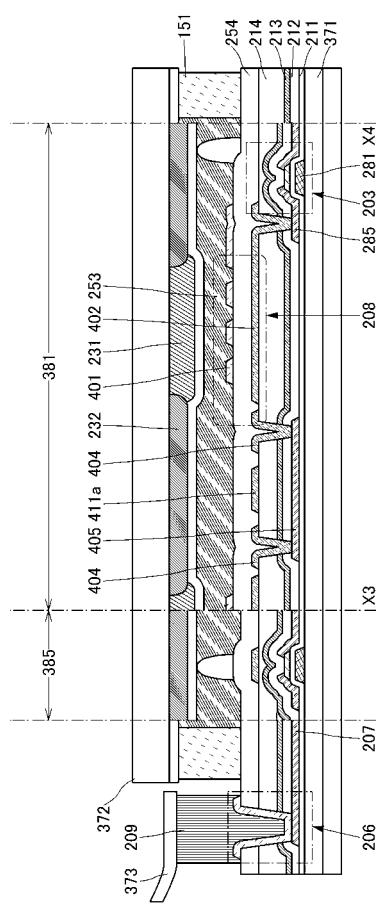

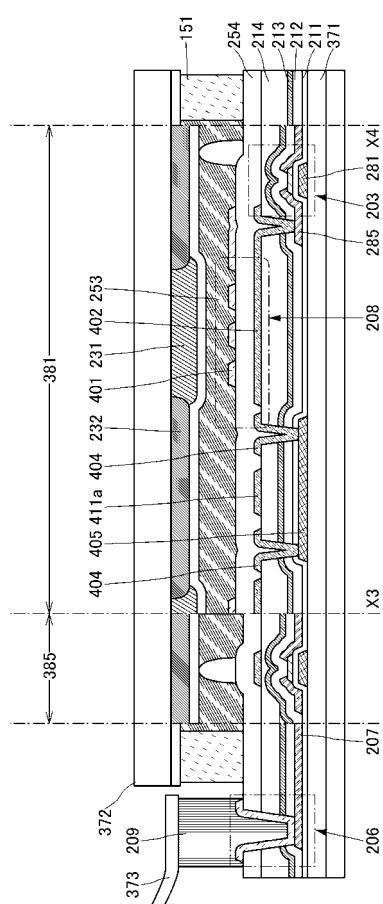

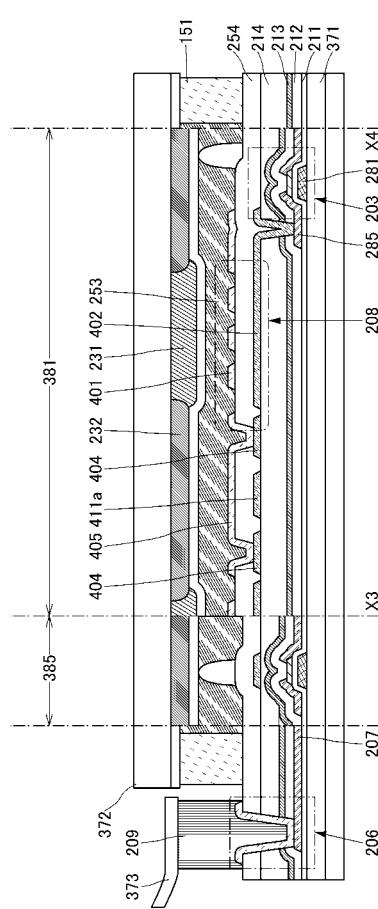

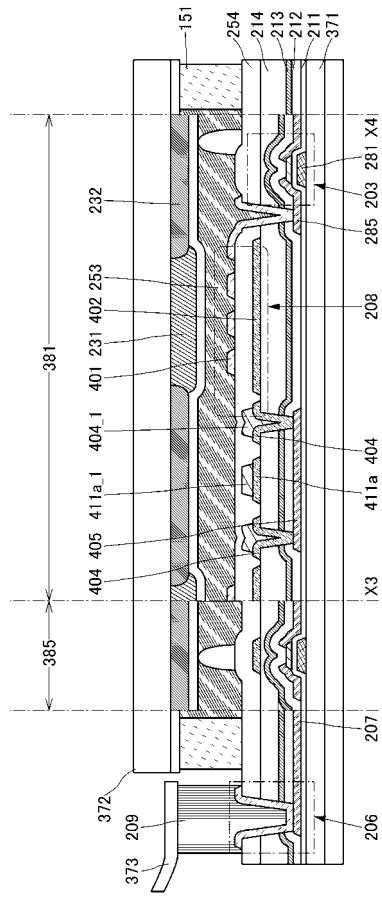

図35は、導電層411a、導電層411b及び導電層404を、導電層402と同一の導電膜を加工して形成した場合の例を示している。したがって、導電層411a、導電層411b、導電層404、及び導電層402は、同一面上に配置されていることとなる。また図36に、図35中の切断線X3-X4に対応する部分の断面を含む、タッチパネルの断面概略図を示す。図35および図36は、図8(B)に対応している。

10

**【0262】**

図35に示すように、導電層402は島状の形状を有する。また導電層411aまたは導電層411bを挟んで隣接する2つの導電層402は、導電層412aと同様に導電層405によって電気的に接続されている。なお、ここではY方向に隣接する2つの導電層402が電気的に接続されていない場合の例を示したが、複数の導電層402がY方向に導電層405を介して電気的に接続してもよいし、X方向とY方向のいずれも導電層405を介して電気的に接続してもよい。なお、ここでは上側の導電層401が画素電極であり、下側の導電層402が共通電極である場合について説明するが、これらの関係を逆転させてもよい。

20

**【0263】**

なお、導電層405は、図37に示すように、X方向に延在して配置されていてよい。このようにすることにより、導電層404の配線抵抗を実質的に低減することができる。

**【0264】**

なお、図35または図37において、導電層411a及び導電層411bは、X方向に延在するように配置し、導電層412a及び導電層412bは、Y方向に延在するように配置してもよい。

**【0265】**

なお、図36では導電層405としてトランジスタのソース電極及びドレイン電極285と同一の導電膜を加工して形成した構成とした。この場合には、導電層405の下に、ゲート電極などが配置されていても、問題なくレイアウトすることができる。よって、導電層405は、ゲート電極や、ゲート電極と同一の導電膜を加工して形成された膜と、重ねて配置することができる。ただし、本発明の一態様は、これに限られず、トランジスタのゲート電極281、半導体層、またはそのほかの導電層と同一の導電膜を加工して導電層405を形成することができる。

30

**【0266】**

一例として、導電層405を、ゲート電極281と同一の導電膜を加工して形成した場合を図38に示す。この場合には、導電層405の上に、ソース電極及びドレイン電極285などが配置されていても、問題なくレイアウトすることができる。よって、導電層405は、ソース電極及びドレイン電極285や、ソース電極及びドレイン電極285と同一の導電膜を加工して形成された膜と、重ねたり、交差させて配置することができる。つまり、ソース信号線と、導電層411aまたは導電層411bとを、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。

40

**【0267】**

または、導電層405を、導電層401と同一の導電膜を加工して形成した場合を図39に示す。この場合には、導電層405の下に、ソース電極及びドレイン電極285やゲート電極などが配置されていても、問題なくレイアウトすることができる。よって、導電層405は、ゲート電極や、ソース電極及びドレイン電極285や、ゲート電極と同一の導電膜を加工して形成された膜や、ソース電極及びドレイン電極285と同一の導電膜を

50

加工して形成された膜と、重ねたり、交差させて配置することができる。つまり、ソース信号線と、導電層411aまたは導電層411bとを、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。または、ゲート信号線と導電層404または導電層405と、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。

#### 【0268】

なお、図35または図37において、導電層411a及び導電層411bは、X方向に延在するように配置し、導電層412a及び導電層412bは、Y方向に延在するように配置する場合には、配置される方向が異なるため、導電層412a及び導電層412bをゲート信号線と重ねて配置するのではなくソース信号線と重ねて配置し、導電層411a及び導電層411bをソース信号線と重ねて配置するのではなくゲート信号線と重ねて配置することとなる。

10

#### 【0269】

なお、図36、図38、図39において、上側の導電層401が画素電極であり、下側の導電層402が共通電極である場合の例を示した。ただし、本発明の一態様は、これに限定されない。上側の導電層401を共通電極とし、下側の導電層402を画素電極としてもよい。その場合の例を、図40、図41、図42に示す。

20

#### 【0270】

なお、図40、図41、図42などでは、導電層411a、導電層411b及び導電層404を、導電層402と同一の導電膜を加工して形成した場合の例を示している。ただし、本発明の一態様は、これに限定されない。導電層411a、導電層411b及び導電層404を、導電層401と同一の導電膜を加工して形成してもよい。したがって、導電層411a、導電層411b、導電層404、及び導電層401は、同一面上に配置されていてもよい。その場合の例を、図43、図44、図45に示す。

20

#### 【0271】

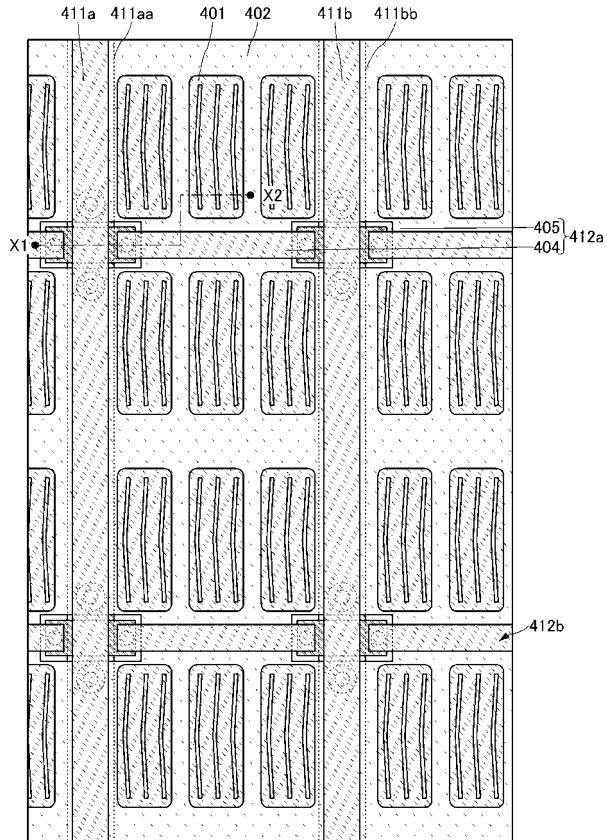

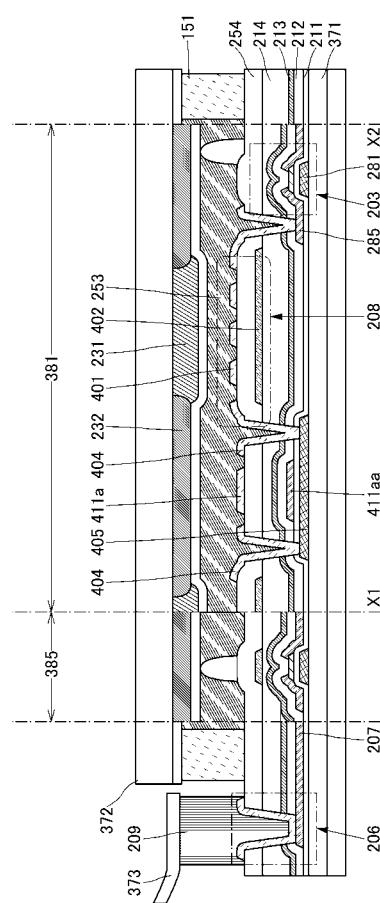

なお、導電層411a、導電層411b、および、導電層404の抵抗を下げたい場合には、導電層411a、導電層411bおよび導電層404の上または下に、抵抗の低い導電層411a\_1、411b\_1、404\_1を設けてもよい。例えば、アルミニウム、銅、チタン、モリブデン、タングステン、または、それらの積層を、導電層411a、導電層411bおよび導電層404の上または下に設けてもよい。または、導電層411a\_1、411b\_1、404\_1の少なくとも一つは、メッッシュ状に加工された金属膜で構成されていてもよい。または、導電層411a\_1、411b\_1、404\_1の少なくとも一つは、金属ナノワイヤ、またはカーボンナノチューブなどで構成されていてもよい。ただし、導電層402は、透光性を有することが望ましい。したがって、導電層402の上または下には、抵抗の低い導電層を設けないことが望ましい。その場合の例を、図46と、図47に示す。

30

#### 【0272】

なお、導電層411a、導電層411bの抵抗値を実質的に下げたい場合には、導電層411aa、導電層411bbを配置してもよい。導電層411a（導電層411b）と、導電層411aa（導電層411bb）とは、コンタクトホールを介して、接続されている。その場合の例を、図48と、図49に示す。

40

#### 【0273】

##### 〔構成例2-3〕

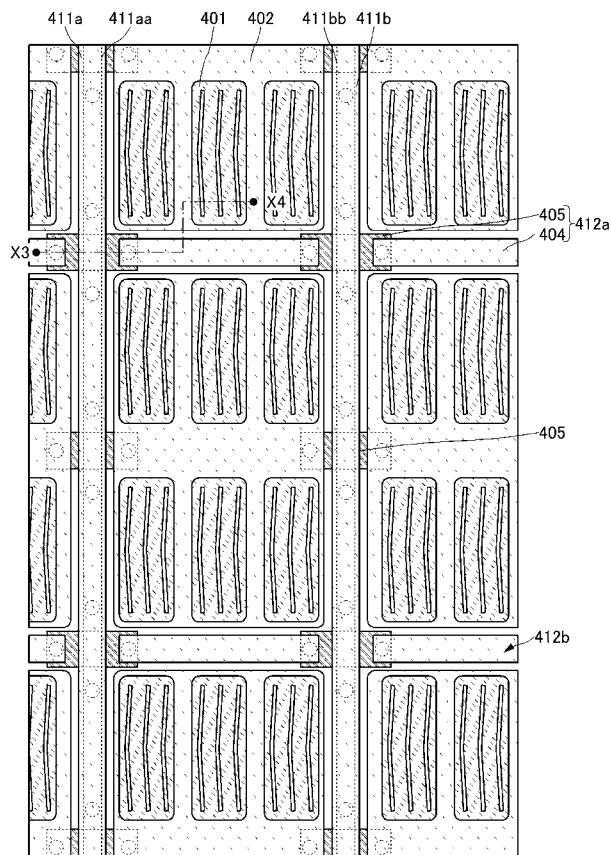

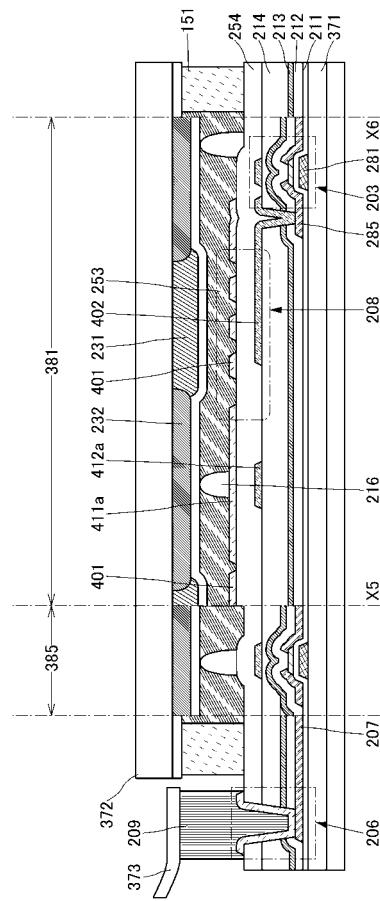

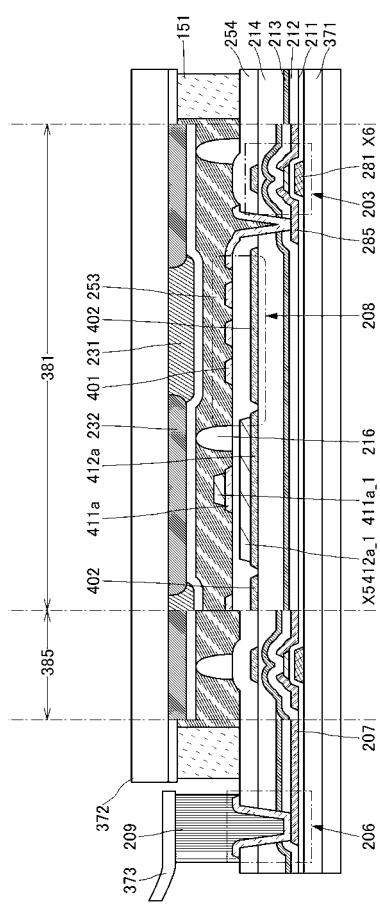

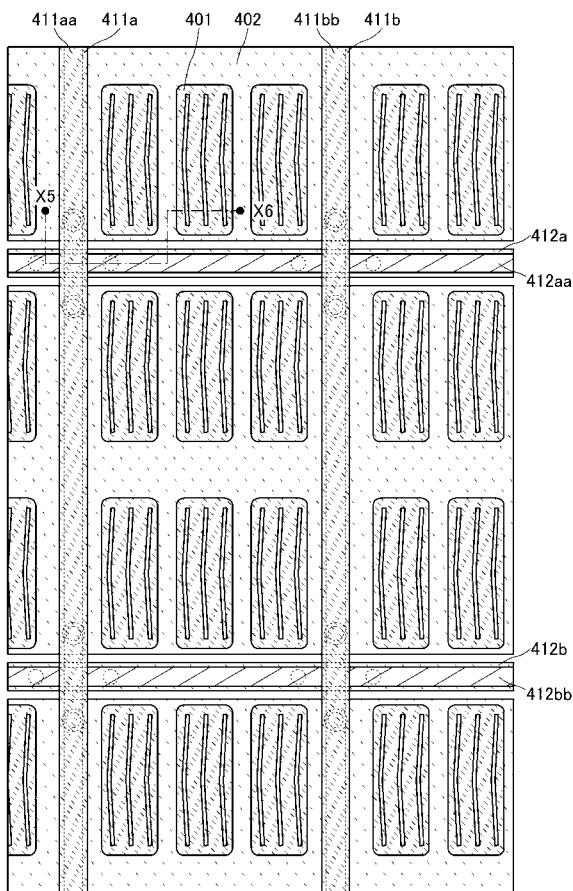

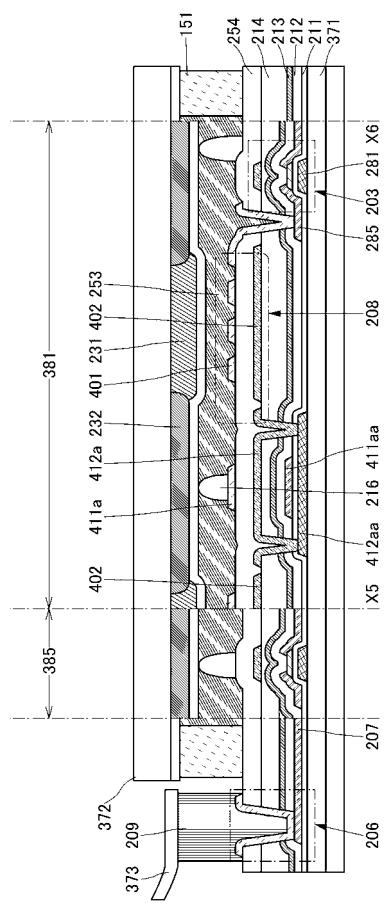

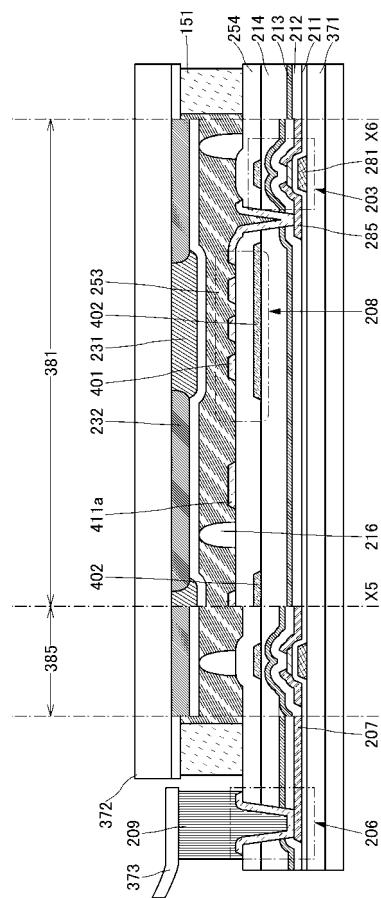

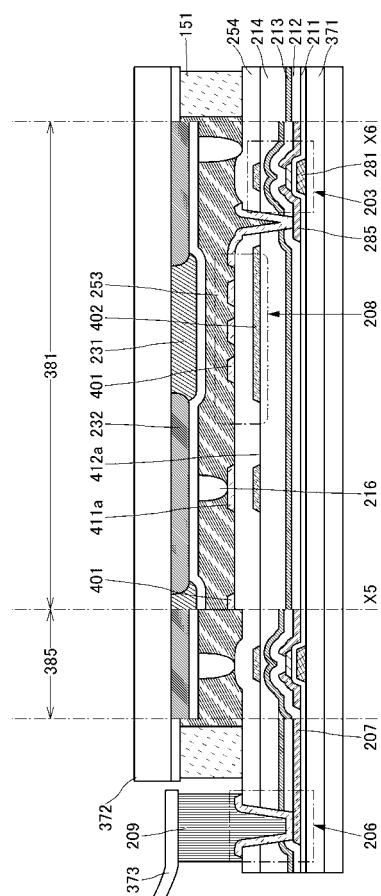

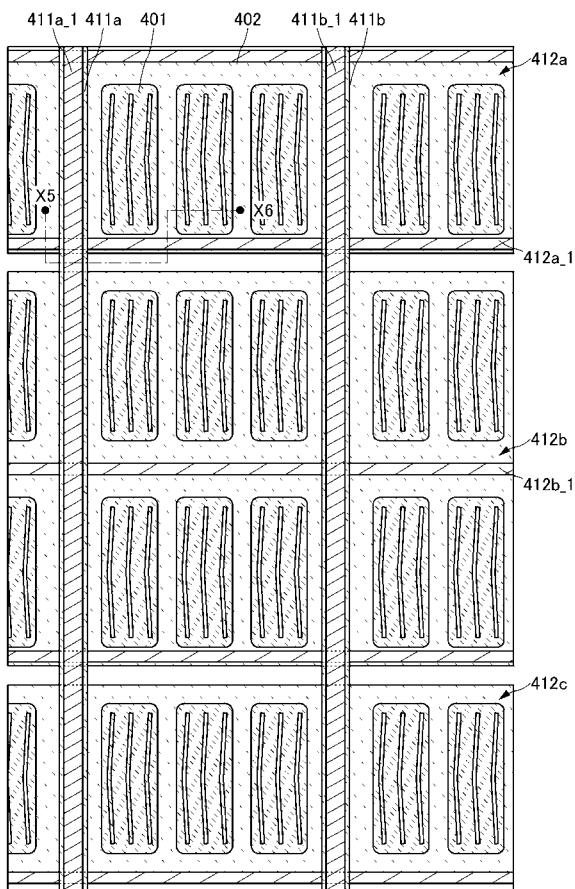

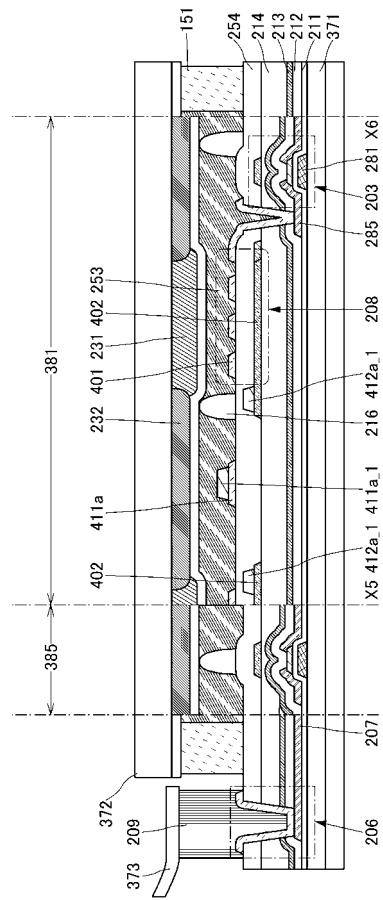

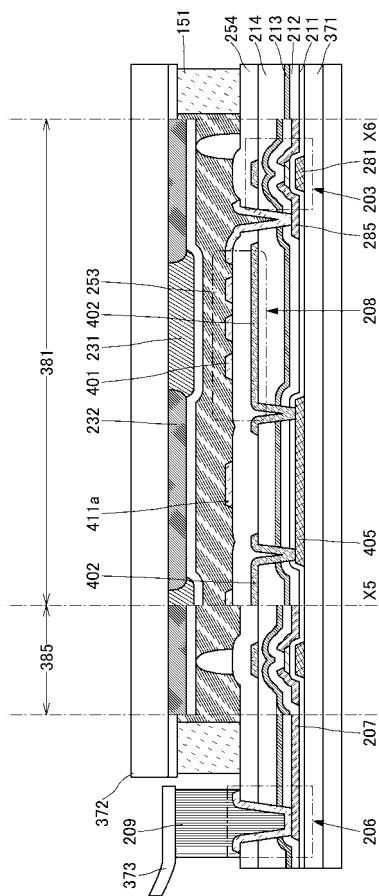

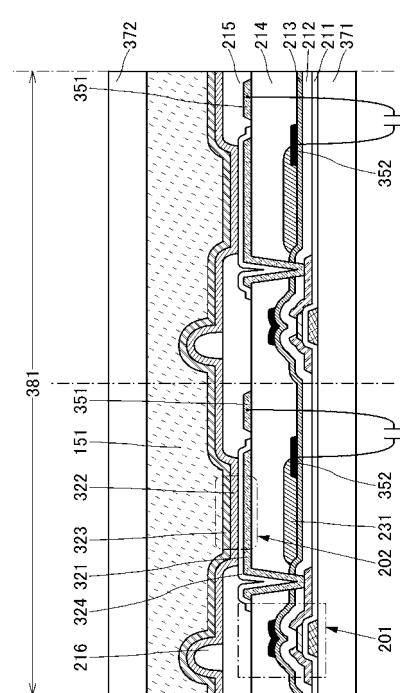

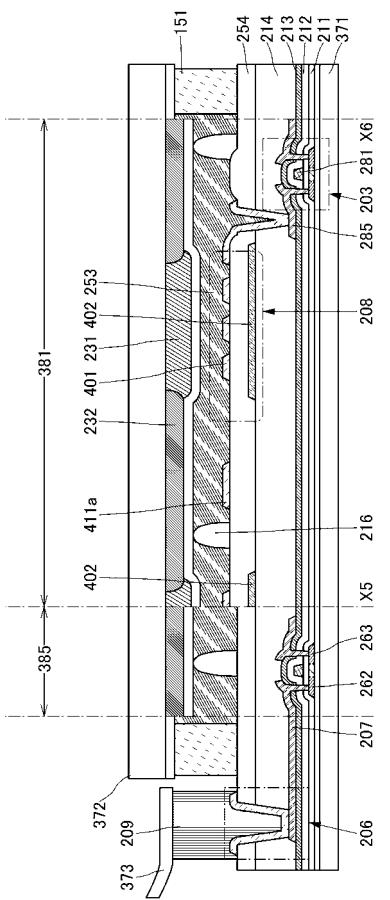

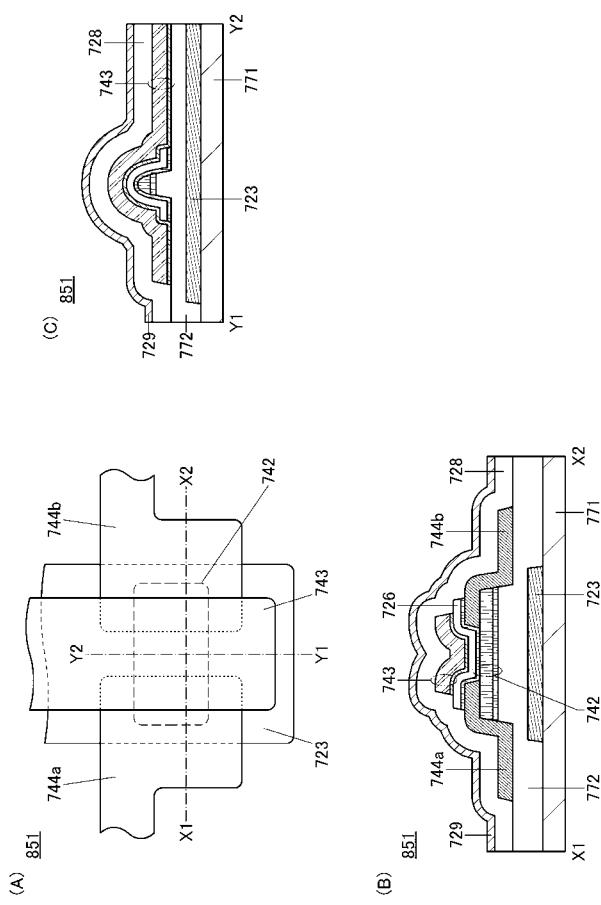

図50は、導電層411a及び導電層411bを導電層401と同一の導電膜を加工して形成し、導電層412a及び導電層412bを導電層402と同一の導電膜を加工して形成した場合の例を示している。したがって、導電層411a、導電層411b、導電層401は、同一面上に配置されていることとなる。同様に、導電層412a、導電層412b、導電層402は、同一面上に配置されていることとなる。また図51に、図50中の切断線X5-X6に対応する部分の断面を含む、タッチパネルの断面概略図を示す。図

50

50 および図51は、図7(E)に対応している。

#### 【0274】

このように、タッチセンサの一対の電極として機能する2つの導電層（例えば、導電層411aと導電層412a、または、導電層411bと導電層412bなど）を、それぞれ異なる層で形成することで、これらを交差させることができる。したがって、構成例1や構成例2と比較して、導電層405を用いたブリッジ部を形成する必要がないため、より構成を簡略化できる。そのため、製造歩留りを向上させることができる。また、導電層411a、導電層412a、導電層411b、または、導電層412bなどの下に、ソース電極及びドレイン電極285やゲート電極281などが配置されていても、問題なくレイアウトすることができる。よって、導電層411a、導電層412a、導電層411b、または、導電層412bは、ゲート電極281や、ソース電極及びドレイン電極285や、ゲート電極281と同一の導電膜を加工して形成された膜や、ソース電極及びドレイン電極285と同一の導電膜を加工して形成された膜と、重ねたり、交差させて配置することができる。つまり、ソース信号線と、導電層411a、導電層412a、導電層411b、または、導電層412bとを、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができます。つまり、開口率を高くすることができます。または、ゲート信号線と、導電層411a、導電層412a、導電層411b、または、導電層412bとを、重ねて配置することができる。そのため、導電層401のレイアウト面積を大きくすることができます。つまり、開口率を高くすることができます。

#### 【0275】

なお、図51では上側の導電層401が画素電極であり、下側の導電層402が共通電極である場合について説明するが、これらの関係を逆転させてもよい。

#### 【0276】

なお、図50において、導電層411a及び導電層411bは、X方向に延在するように配置し、導電層412a及び導電層412bは、Y方向に延在するように配置してもよい。

#### 【0277】

なお、図50、図51において、上側の導電層401が画素電極であり、下側の導電層402が共通電極である場合の例を示した。ただし、本発明の一態様は、これに限定されない。上側の導電層401を共通電極とし、下側の導電層402を画素電極としてもよい。その場合の例を、図52、図53に示す。

#### 【0278】

なお、導電層411a、導電層411b、導電層412a、および、導電層412bの抵抗を下げたい場合には、導電層411a、導電層411b、導電層412a、および、導電層412bの上または下に、抵抗の低い導電層411a\_1、411b\_1、412a\_1、412b\_1を設けてもよい。例えば、アルミニウム、銅、チタン、モリブデン、タンクステン、または、それらの積層を、導電層411a、導電層411b、導電層412a、および、導電層412bの上または下に設けてもよい。または、導電層411a\_1、411b\_1、412a\_1、412b\_1の少なくとも一つは、メッシュ状に加工された金属膜で構成されていてもよい。または、導電層411a\_1、411b\_1、412a\_1、412b\_1の少なくとも一つは、金属ナノワイヤ、またはカーボンナノチューブなどで構成されていてもよい。ただし、導電層401および導電層402は、透光性を有することが望ましい。したがって、開口部においては、導電層401および導電層402の上または下には、抵抗の低い導電層を設けないことが望ましい。その場合の例を、図54と、図55に示す。

#### 【0279】

なお、導電層411a、導電層411b、導電層412a、または、導電層412bの抵抗値を実質的に下げたい場合には、導電層411aa、導電層411bb、導電層412aa、または、導電層412bbを配置してもよい。導電層411a（導電層411b、導電層412a、または、導電層412b）と、導電層411aa（導電層411bb

10

20

30

40

50

、導電層 412aa、または、導電層 412bb)とは、コンタクトホールを介して、接続されている。その場合の例を、図 56 と、図 57 に示す。なお、例えば、導電層 411a と導電層 411aa を接続する場合には、導電層 402 に設けられた穴を介して、接続される。つまり、間に導電層 402 があって、導電層 402 などの上側の導電層と下側の導電層とを接続する場合には、導電層 402 に穴などが設けられている。

#### 【0280】

なお、導電層 411a および導電層 411b と、導電層 412a および導電層 412b とにおいて、交差部において、容量が形成される。しかしながら、この容量の大きさは、小さいことが望ましい場合がある。そこで、この交差容量を減らすようにするために、別の導電層とコンタクトホールを介して、導電層同士が接続されるようにしてもよい。その場合の例を、図 58 と図 59 に示す。図 58 と図 59 では、導電層 412a 同士(導電層 412b 同士)は、コンタクトホールと導電層 405 を介して、接続されている。導電層 405 は、例えば、ゲート電極 281 と同一の導電膜を加工して形成された膜や、ソース電極及びドレイン電極 285 と同一の導電膜を加工して形成された膜を用いて、構成される。これにより、タッチセンサ電極の寄生容量を低減することができる。その結果、タッチセンサの感度を向上させることができる。

10

#### 【0281】

##### [構成例 2 - 4]

上記では、液晶素子を構成する一対の導電層と、タッチセンサを構成する一対の導電層とをそれぞれ設ける構成としたが、液晶素子の一方の導電層が、タッチセンサの一方の導電層を兼ねる構成とすることもできる。

20

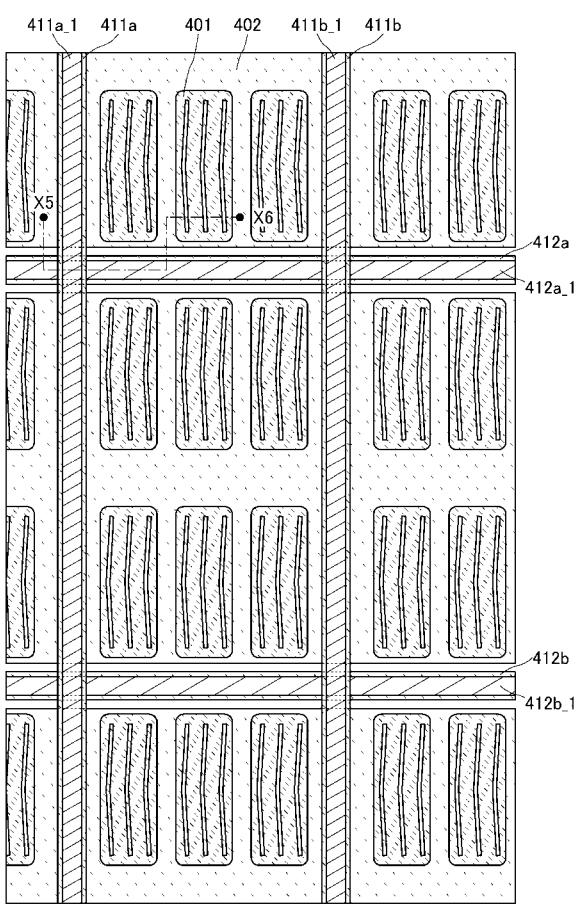

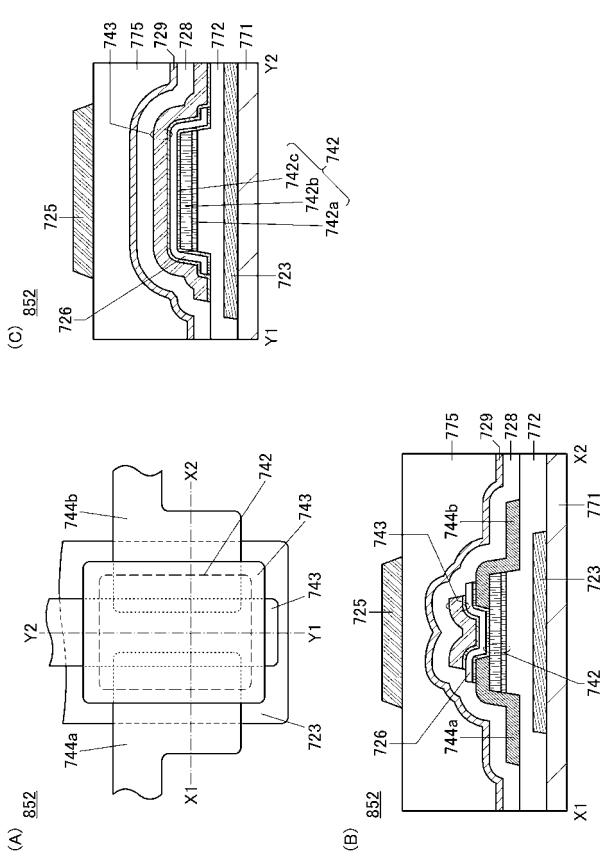

#### 【0282】

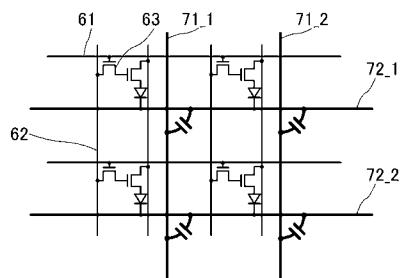

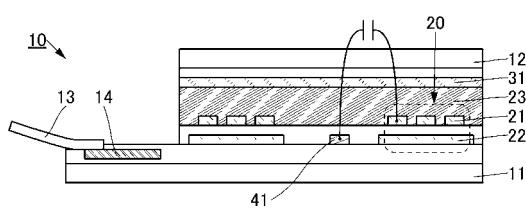

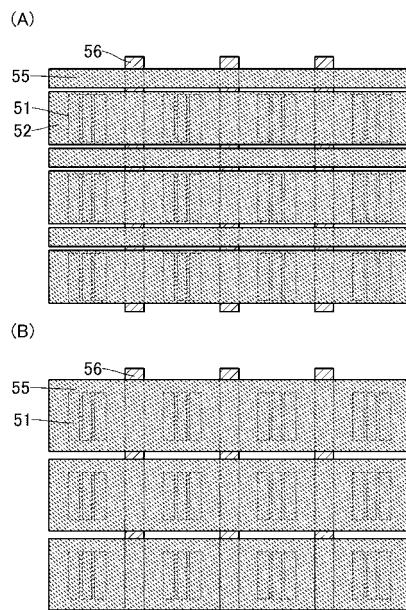

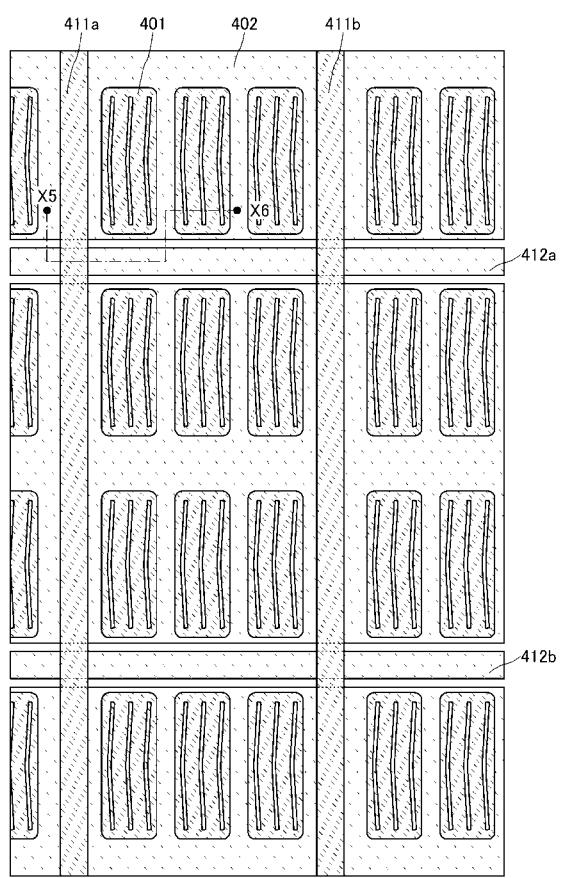

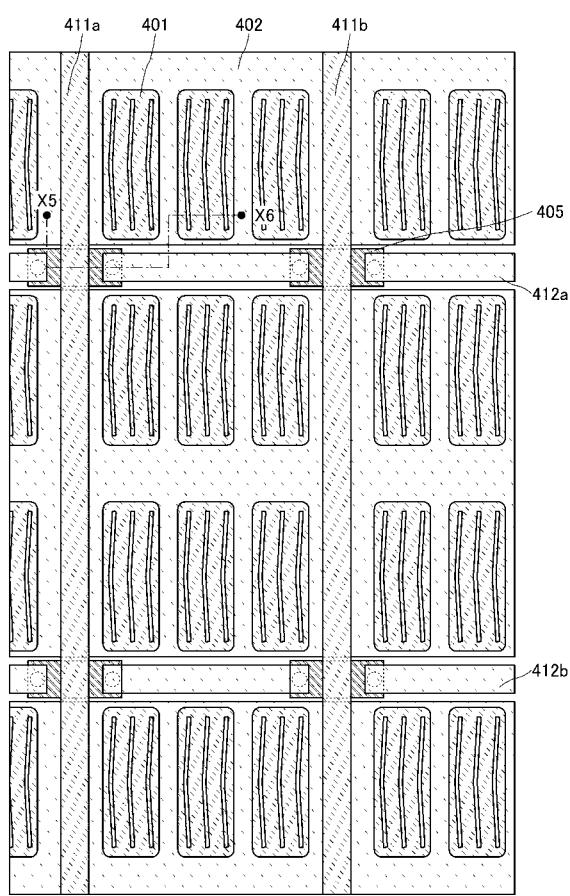

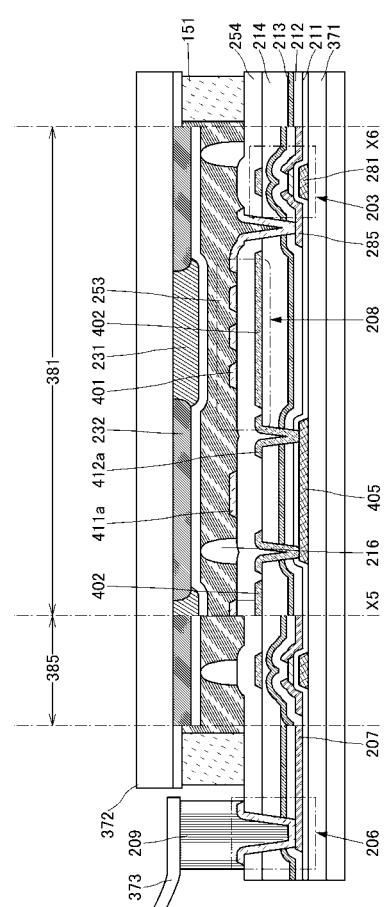

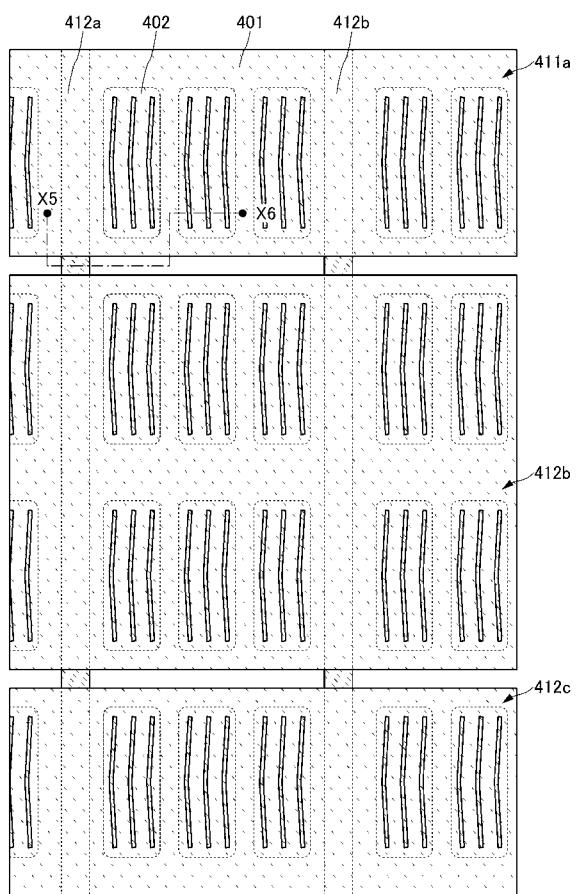

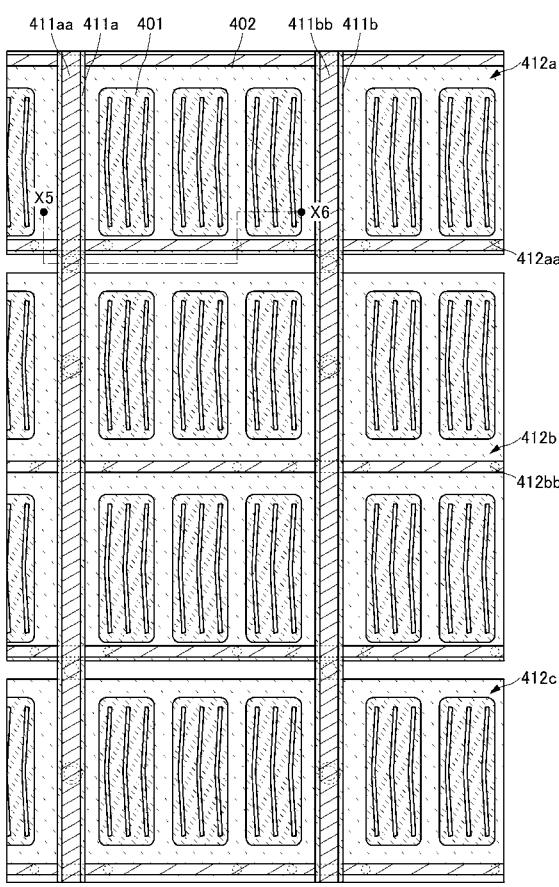

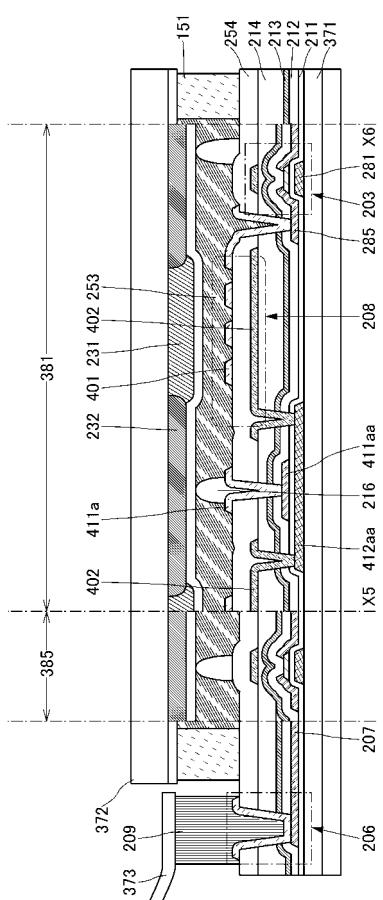

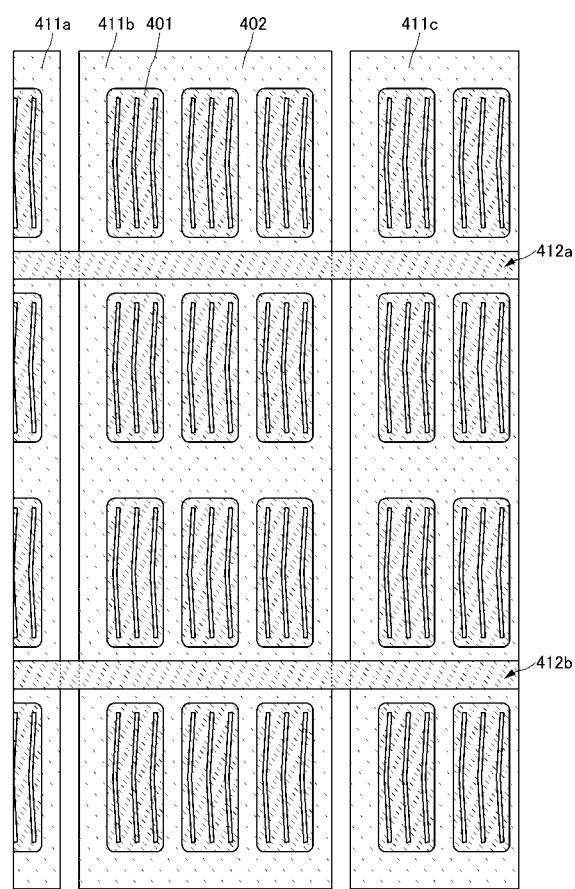

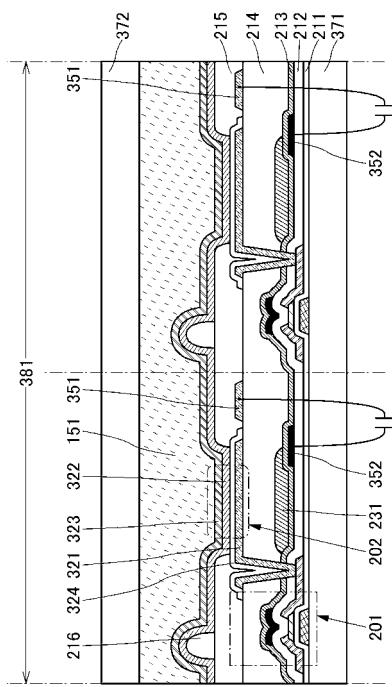

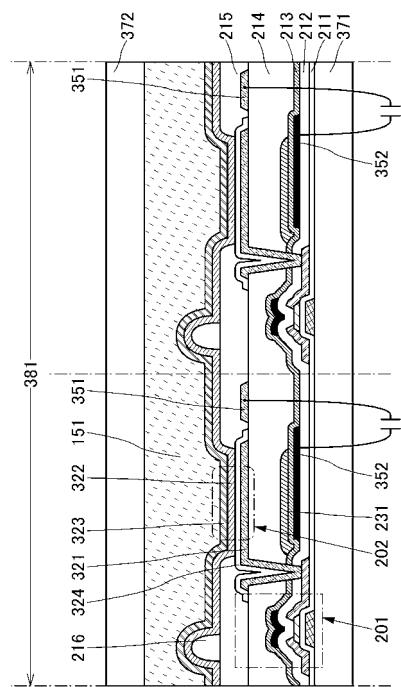

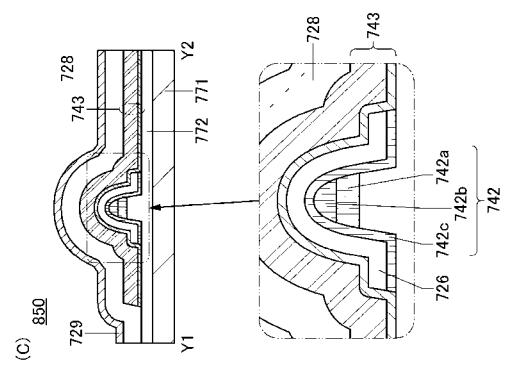

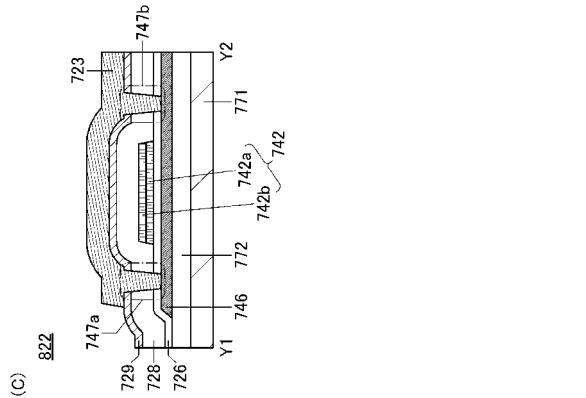

図 60 では、導電層 402 が X 方向に伸びた帯状の形状を有し、Y 方向には分断されている例を示している。このとき、導電層 402 の一つは、タッチセンサの電極として機能する導電層 412a、導電層 412b、または導電層 412c として機能し、液晶素子の一方の導電層、例えば、共通電極としても機能する。また図 61 に、図 60 中の切断線 X5-X6 に対応する部分の断面を含む、タッチパネルの断面概略図を示す。図 60 および図 61 は、図 7(C) に対応している。

#### 【0283】

タッチセンサの一対の電極として機能する導電層(例えば、導電層 412a、導電層 412b など)と、導電層 402 を、それぞれ異なる層で形成することで、これらを交差させることができる。したがって、構成例 1 や構成例 2 と比較して、導電層 405 を用いたプリッジ部を形成する必要がないため、より構成を簡略化できる。そのため、製造歩留りを向上させることができる。また、導電層 411a、導電層 412a、導電層 411b、または、導電層 412b などの下に、ソース電極及びドレイン電極 285 やゲート電極 281 などが配置されていても、問題なくレイアウトすることができる。よって、導電層 411a、導電層 412a、導電層 411b、または、導電層 412b は、ゲート電極 281 や、ソース電極及びドレイン電極 285 や、ゲート電極 281 と同一の導電膜を加工して形成された膜や、ソース電極及びドレイン電極 285 と同一の導電膜を加工して形成された膜と、重ねたり、交差させて配置することができる。つまり、ソース信号線と、導電層 411a、導電層 412a、導電層 411b、または、導電層 412b とを、重ねて配置することができる。そのため、導電層 401 のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。または、ゲート信号線と、導電層 411a、導電層 412a、導電層 411b、または、導電層 412b とを、重ねて配置することができる。そのため、導電層 401 のレイアウト面積を大きくすることができる。つまり、開口率を高くすることができる。

30

40

#### 【0284】

なお、図 60、図 61 において、上側の導電層 401 が画素電極であり、下側の導電層 402 が共通電極である場合の例を示した。ただし、本発明の一態様は、これに限定されない。上側の導電層 401 を共通電極とし、下側の導電層 402 を画素電極としてもよい

50

。その場合の例を、図 6 2、図 6 3 に示す。

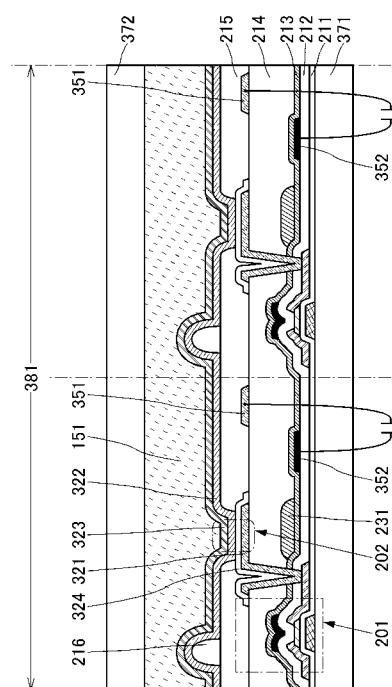

**【0285】**

なお、導電層 411a、導電層 411b、導電層 412a、および、導電層 412b の抵抗を下げたい場合には、導電層 411a、導電層 411b、導電層 412a、および、導電層 412b の上または下に、抵抗の低い導電層 411a\_1、411b\_1、412a\_1、412b\_1 を設けてもよい。例えば、アルミニウム、銅、チタン、モリブデン、タンクステン、または、それらの積層を、導電層 411a、導電層 411b、導電層 412a、および、導電層 412b の上または下に設けてもよい。または、導電層 411a\_1、411b\_1、412a\_1、412b\_1 の少なくとも一つは、メッシュー状に加工された金属膜で構成されていてもよい。または、導電層 411a\_1、411b\_1、412a\_1、412b\_1 の少なくとも一つは、金属ナノワイヤ、またはカーボンナノチューブなどで構成されていてもよい。ただし、導電層 401 および導電層 402 は、透光性を有することが望ましい。したがって、開口部においては、導電層 401 および導電層 402 の上または下には、抵抗の低い導電層を設けないことが望ましい。その場合の例を、図 6 4 と、図 6 5 に示す。

10

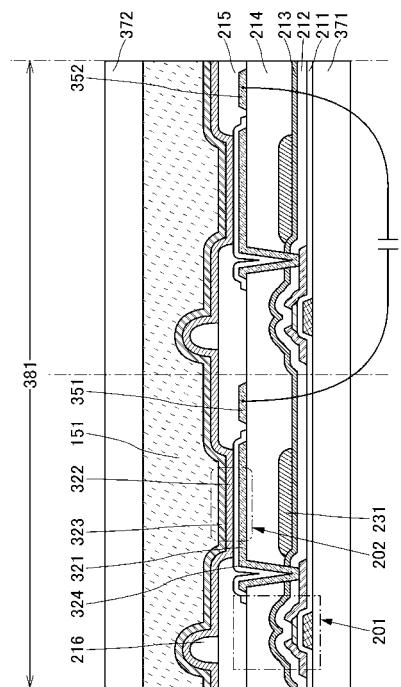

**【0286】**

なお、導電層 411a、導電層 411b、導電層 412a、または、導電層 412b の抵抗値を実質的に下げたい場合には、導電層 411aa、導電層 411bb、導電層 412aa、または、導電層 412bb を配置してもよい。導電層 411a (導電層 411b、導電層 412a、または、導電層 412b) と、導電層 411aa (導電層 411bb、導電層 412aa、または、導電層 412bb) とは、コンタクトホールを介して、接続されている。その場合の例を、図 6 6 と、図 6 7 に示す。なお、例えば、導電層 411a と導電層 411aa とを接続する場合には、導電層 402 に設けられた穴を介して、接続される。つまり、間に導電層 402 があって、導電層 402 などの上側の導電層と下側の導電層とを接続する場合には、導電層 402 に穴などが設けられている。

20

**【0287】**

なお、導電層 411a および導電層 411b と、導電層 412a および導電層 412b とにおいて、交差部において、容量が形成される。しかしながら、この容量の大きさは、小さいことが望ましい場合がある。そこで、この交差容量を減らすようにするため、別の導電層とコンタクトホールを介して、導電層同士が接続されるようにしてよい。その場合の例を、図 6 8 と図 6 9 とに示す。図 6 8 と図 6 9 では、導電層 402 同士は、コンタクトホールと導電層 405 を介して、接続されている。導電層 405 は、例えば、ゲート電極 281 と同一の導電膜を加工して形成された膜や、ソース電極及びドレイン電極 285 と同一の導電膜を加工して形成された膜を用いて、構成される。これにより、タッチセンサ電極の寄生容量を低減することができる。その結果、タッチセンサの感度を向上させることが出来る。

30

**【0288】**

なお、図 6 0において、導電層 411a 及び導電層 411b は、X 方向に延在するように配置し、導電層 412a 及び導電層 412b は、Y 方向に延在するように配置してもよい。

40

**【0289】**

また、図 7 0 では、導電層 402 が Y 方向に伸びた帯状の形状を有し、X 方向には分断されている例を示している。このとき、導電層 402 の一つは、タッチセンサの電極として機能する導電層 411a、導電層 411b、または導電層 411c として機能し、液晶素子の一方の導電層、例えば、共通電極としても機能する。

**【0290】**

このような構成とすることで、より構成を簡略化できるため好ましい。

**【0291】**

なお、ここでは FFS モードが適用された液晶素子を用いる場合の例について説明したが、例えば IPS モードが適用された液晶素子を用いる構成としてもよい。その場合には

50

、導電層 401 と導電層 402 とを同一の導電膜を加工することにより形成すればよい。または、導電層 401 と導電層 402 の両方を、櫛歯状の上面形状にすればよい。また、このとき共通電極として機能する導電層 402 を、X 方向及び Y 方向のいずれか一方に伸びた帯状の形状とし、タッチセンサの一方の電極として機能させることが好ましい。

#### 【0292】

##### [構成例 3]

以下では、上記構成例 1 及び構成例 2 とは一部の構成が異なるタッチパネルの構成例について図面を参照して説明する。

#### 【0293】

以下で説明する本発明の一態様のタッチパネルは、表示素子に有機 EL 素子が適用されたタッチパネルである。

#### 【0294】

##### [構成例 3 - 1]

図 71 には、2 つの副画素を含む領域の断面構成例を示している。図 71 で例示するタッチパネルは、トランジスタ 201 等が形成された基板側に光を射出するボトムエミッション型の発光装置を含む。

#### 【0295】

タッチパネルは、発光素子 202 を有する。発光素子 202 は、導電層 321 と、EL 層 322 と、導電層 323 とが積層された構成を有する。また導電層 321 と導電層 323 の間に、光学調整層 324 が設けられていてもよい。発光素子 202 からの光は基板 371 側に射出される。また導電層 321 及び光学調整層 324 の端部を覆って絶縁層 215 が設けられている。

#### 【0296】

導電層 321 は透光性を有していることが好ましい。また導電層 323 は反射性を有していることが好ましい。

#### 【0297】

また、発光素子 202 よりも基板 371 側に、着色層 231 が設けられている。図 71 に示す構成では、着色層 231 が絶縁層 213 上に設けられている。

#### 【0298】

導電層 351 と導電層 352 は、一方がタッチセンサの一方の電極として機能し、他方がタッチセンサの他方の電極として機能する。導電層 351 は、導電層 321 と同一面上に形成されている。また導電層 352 は、トランジスタ 201 が有する 2 つのゲート電極のうちの一方と同一面上に形成されている。したがって、作製工程を増やすことなくタッチパネルを作製することができる。

#### 【0299】

図 71 に示すように、基板 371 側において、導電層 351 と導電層 352 の間に生じる容量を利用して検出することができる。

#### 【0300】

##### [発光素子について]

発光素子としては、自発光が可能な素子を用いることができ、電流又は電圧によって輝度が制御される素子をその範疇に含んでいる。例えば、発光ダイオード (LED)、有機 EL 素子、無機 EL 素子等を用いることができる。

#### 【0301】

発光素子は、トップエミッション型、ボトムエミッション型、デュアルエミッション型のいずれであってもよい。光を取り出す側の電極には、可視光を透過する導電膜を用いる。また、光を取り出さない側の電極には、可視光を反射する導電膜を用いることが好ましい。

#### 【0302】

EL 層は少なくとも発光層を有する。EL 層は、発光層以外の層として、正孔注入性の高い物質、正孔輸送性の高い物質、正孔ブロック材料、電子輸送性の高い物質、電子注入

10

20

30

40

50

性の高い物質、又はバイポーラ性の物質（電子輸送性及び正孔輸送性が高い物質）等を含む層をさらに有していてもよい。

### 【0303】

E L 層には低分子系化合物及び高分子系化合物のいずれを用いることもでき、無機化合物を含んでいてもよい。E L 層を構成する層は、それぞれ、蒸着法（真空蒸着法を含む）、転写法、印刷法、インクジェット法、塗布法等の方法で形成することができる。

### 【0304】

陰極と陽極の間に、発光素子の閾値電圧より高い電圧を印加すると、E L 層に陽極側から正孔が注入され、陰極側から電子が注入される。注入された電子と正孔はE L 層において再結合し、E L 層に含まれる発光物質が発光する。

10

### 【0305】

発光素子として、白色発光の発光素子を適用する場合には、E L 層に2種類以上の発光物質を含む構成とすることが好ましい。例えば2以上の発光物質の各々の発光が補色の関係となるように、発光物質を選択することにより白色発光を得ることができる。例えば、それぞれR（赤）、G（緑）、B（青）、Y（黄）、O（橙）等の発光を示す発光物質、またはR、G、Bのうち2以上の色のスペクトル成分を含む発光を示す発光物質のうち、2以上を含むことが好ましい。また、発光素子からの発光のスペクトルが、可視光領域の波長（例えば350 nm ~ 750 nm）の範囲内に2以上のピークを有する発光素子を適用することが好ましい。また、黄色の波長領域にピークを有する材料の発光スペクトルは、緑色及び赤色の波長領域にもスペクトル成分を有する材料であることが好ましい。

20

### 【0306】

より好ましくは、E L 層は、一の色を発光する発光材料を含む発光層と、他の色を発光する発光材料を含む発光層とが積層された構成とすることが好ましい。例えば、E L 層における複数の発光層は、互いに接して積層されていてもよいし、分離層を介して積層されていてもよい。例えば、蛍光発光層と燐光発光層との間に分離層を設ける構成としてもよい。

30

### 【0307】

分離層は、例えば燐光発光層中で生成する燐光材料等の励起状態から蛍光発光層中の蛍光材料等へのデクスター機構によるエネルギー移動（特に三重項エネルギー移動）を防ぐために設けることができる。分離層は数nm程度の厚さがあればよい。具体的には、0.1 nm以上20 nm以下、あるいは1 nm以上10 nm以下、あるいは1 nm以上5 nm以下である。分離層は、単一の材料（好ましくはバイポーラ性の物質）、又は複数の材料（好ましくは正孔輸送性材料及び電子輸送性材料）を含む。

30

### 【0308】

分離層は、該分離層と接する発光層に含まれる材料を用いて形成してもよい。これにより、発光素子の作製が容易になり、また、駆動電圧が低減される。例えば、燐光発光層が、ホスト材料、アシスト材料、及び燐光材料（ゲスト材料）からなる場合、分離層を、該ホスト材料及びアシスト材料で形成してもよい。上記構成を別言すると、分離層は、燐光材料を含まない領域を有し、燐光発光層は、燐光材料を含む領域を有する。これにより、分離層と燐光発光層とを燐光材料の有無で蒸着し分けることが可能となる。また、このような構成とすることで、分離層と燐光発光層を同じチャンバーで成膜することが可能となる。これにより、製造コストを削減することができる。

40

### 【0309】

また、発光素子は、E L 層を1つ有するシングル素子であってもよいし、複数のE L 層が電荷発生層を介して積層されたタンデム素子であってもよい。

### 【0310】

#### [構成例3-2]

図72は、図71における導電層352の位置が異なる点で相違している。図72において、導電層352及びトランジスタ201のゲート電極の一方は、絶縁層212と絶縁層213の間に設けられている。

50

## 【0311】

導電層352及びトランジスタ201のゲート電極の一方には、上述した低抵抗化された酸化物半導体を含んで構成されていることが好ましい。

## 【0312】

また、図73のように、導電層352が導電層321、光学調整層324、EL層322、導電層323、着色層231の少なくとも一つと重なるように配置してもよい。また図74に示すように導電層352が導電層321、光学調整層324、EL層322、導電層323、着色層231のいずれとも重ならないように配置してもよい。

## 【0313】

## 〔断面構成例3-2〕

10

図75は、タッチセンサを構成する導電層351と導電層352の両方が、導電層321と同一面上に形成されている場合の例を示している。

## 【0314】

このとき、一方の副画素に配置された導電層351と、他方の副画素に配置された導電層352との間に生じる容量を利用して検出することができる。

## 【0315】

## 〔断面構成例3-3〕

20

図76は、基板372側に光を射出するトップエミッション型の発光装置を含むタッチパネルの断面構成例である。

## 【0316】

ここで、発光素子202において、導電層321は反射性を有し、導電層323は透光性を有する。

## 【0317】

また導電層323は、少なくとも導電層351の一部と重なる部分に開口を有する。また、導電層323は、スリットまたは開口を有していてもよいし、櫛歯状の形状を有していてもよい。

## 【0318】

導電層351及び導電層352は、導電層321と同一面上に形成されている。

## 【0319】

30

図76に示す例では、一方の副画素に配置された導電層351と、他方の副画素に配置された導電層352との間に生じる容量を利用して検出する例を示している。

## 【0320】

また、図77に示すように、導電層323をタッチセンサの電極として用いることもできる。すなわち、導電層351と導電層323の間に生じる容量を利用して検出する構成としてもよい。

## 【0321】

また、図77では、塗り分け方式によりEL層322を形成した例を示している。またこのとき、図77に示すようにEL層322の端部を導電層323で覆うことにより、EL層322への不純物の拡散が抑制され、信頼性を高めることができる。また図77では、着色層231等が設けられていない場合の例を示している。

40

## 【0322】

## 〔他の構成例〕

なお本発明の一態様は上記で例示した構成に限られず、様々な構成をとることができます。

## 【0323】

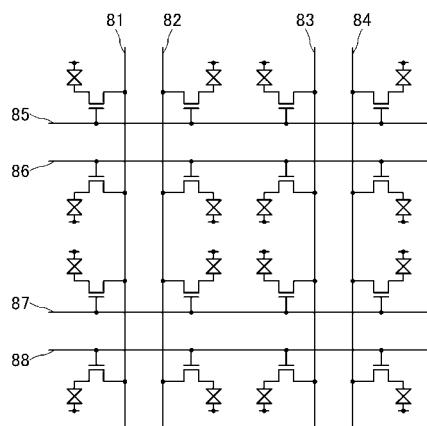

## 〔センサ電極と画素用配線との位置関係〕

例えば、画素が有するソース線（信号線）は、偶数列目と奇数列目とで、ソース線の配置を右か左かに変えることができる。その結果、ソース線が2本隣接する形となる。また、その上に、タッチセンサ用の導電層（電極）を置くことができる。また、画素が有するゲート線も同様に、上下の画素でゲート線を近接しておき、その上に、タッチセンサ用電

50

極を置くことができる。その場合の例を、図78に示す。ソース線81、82、83、84は、2本ずつ隣接されている。また、ゲート線85、86、87、88も、2本ずつ隣接されている。

#### 【0324】

##### 〔周辺回路〕

周辺回路は、一体形成しない構成とすることができます。すなわち、タッチセンサを駆動する回路と、画素を駆動する回路とを、それぞれ別に形成することができます。なお、これらの機能を一つの回路で実現してもよい。

#### 【0325】

また、タッチセンサのX方向の導電層またはY方向の導電層（電極）のうち、一方の導電層の選択を行うドライバ回路をTFTで一体形成することもできる。10

#### 【0326】

またタッチセンサを駆動する回路は、画素を駆動するゲートドライバ側、またはソースドライバ側のいずれに配置してもよい。

#### 【0327】

また、タッチセンサのX方向の導電層またはY方向の導電層（電極）と電気的に接続する2つの回路のうち、検知する機能を有する回路としてはICを用いることが好ましい。このとき、当該導電層はFPCを介して当該ICで制御することが好ましい。

#### 【0328】

##### 〔タッチセンサの導電層（電極）の材質〕

タッチセンサを構成する一対の導電層の少なくとも一つは、液晶素子を構成する共通電極や画素電極などと同じ材料を用いることが好ましい。20

#### 【0329】

または、タッチセンサを構成する一対の導電層の少なくとも一つは、メッシュ状に加工された金属膜（メタルメッシュともいう）で構成してもよい。

#### 【0330】

また、タッチセンサのX方向の導電層またはY方向の導電層（電極）の少なくとも一つは、その直下か直上に金属膜を付けることで、抵抗を下げることができる。このとき、金属酸化物を含む導電膜と、金属を含む導電膜の積層構造とする場合には、ハーフトーンマスクを用いたパターニング技術により形成すると、工程を簡略化できるため好ましい。30

#### 【0331】

##### 〔タッチセンサの導電層（電極）を接続する配線〕

タッチセンサのX方向の導電層とY方向の導電層が交差する部分において、他の導電層を用いてブリッジ構造を実現する場合、例えば、当該導電層をトランジスタのゲート電極と同一面上の導電層とし、X方向の導電層をゲート線と平行に横方向に画素全体で引き回す。または、当該導電層をトランジスタのソース電極及びドレイン電極と同一面上の導電層とし、Y方向の導電層をソース線と平行に、縦方向に画素全体で引き回す。このとき、画素内にコンタクト部を形成することができる。または、当該導電層を共通電極として機能する導電層と同一の導電層、または画素電極として機能する導電層と同一面上の導電層を用いてもよい。40

#### 【0332】

##### 〔タッチセンサの導電層（電極）や液晶素子の導電層（電極）〕

上部に配置されるスリットを有する導電層（電極）を画素電極として用い、下部に配置され、複数の画素にわたって設けられる導電層（電極）を共通電極（コモン電極ともいう）として用いることができる。

#### 【0333】

または、上部に配置され、複数の画素にわたって設けられるスリットを有する導電層（電極）を共通電極として用い、下部に配置され、複数の画素のそれぞれに設けられる導電層（電極）を画素電極として用いることができる。

#### 【0334】

50

タッチセンサのX方向の導電層を、画素電極として機能する導電層、または共通電極として機能する導電層と兼ねる構成とすることができます。または、タッチセンサのY方向の導電層を、画素電極として機能する導電層、または共通電極として機能する導電層と兼ねる構成とすることができます。

#### 【0335】

また、タッチセンサのX方向の導電層をパルス電圧が与えられる導電層または電流の検知を行う導電層のいずれとしてもよい。またこのとき、タッチセンサのY方向の導電層は他方にすればよい。

#### 【0336】

また、タッチセンサのX方向の導電層またはY方向の導電層が交差する部分において、いずれか一方の導電層の形状を、他の部分とは異なる形状とすることができます。例えば、画素電極として機能する導電層と同一面上の導電層のみでタッチセンサの一対の導電層を形成する場合、下部に配置される共通電極として機能する導電層をタッチセンサの導電層の下部には配置しないようにすることができます。ただし、タッチセンサの導電層の下部に位置する共通電極として機能する導電層を全て設けない構成とすると、当該共通電極として機能する導電層が島状となってしまうため、隣接する2つの共通電極として機能する導電層の一部がつながるように、スリットを有するような形状とすることが好ましい。

10

#### 【0337】

また、共通電極として機能する導電層は、複数の画素にわたって設けられる構成としてもよいし、例えばトランジスタのゲート電極と同一面上の導電層により形成された共通配線と電気的に接続されていてもよい。このとき、1つの共通電極として機能する導電層は島状の形状を有していてもよい。

20

#### 【0338】

##### 〔対向基板〕

トランジスタ等が設けられる基板と対向して設けられる基板（対向基板ともいう）にタッチセンサのX方向の導電層またはY方向の導電層を設ける場合、当該導電層よりも視認側に遮光層を配置することが好ましい。

#### 【0339】

また、対向基板に液晶素子の一方の電極を形成する場合（TNモード、MVAモード等の場合）、対向基板に設けられるタッチセンサの導電層と重なる部分には、当該電極にスリットを設けることが好ましい。

30

#### 【0340】

また、FFSモードやIPSモード等のように、一対の電極をトランジスタ等が設けられる基板上に形成する場合であっても、対向基板に液晶の配向を制御する導電層を設けてもよい。このときも同様に、当該導電層には、タッチセンサの導電層と重なる部分にスリットを設けることが好ましい。

#### 【0341】

##### 〔駆動方法〕

タッチセンサの駆動方法としては、例えば画素の駆動における1水平期間（1ゲート選択期間）の隙間で、対応する行のセンシング（走査）をする方法を用いることができる。または、1フレーム期間を2つに分け、前半で全画素の書き込みを行い、後半でセンシングしてもよい。

40

#### 【0342】

##### 〔トランジスタ〕

例えば、本明細書等において、トランジスタとして、様々な構造のトランジスタを用いることが出来る。よって、用いるトランジスタの種類に限定はない。トランジスタの一例としては、単結晶シリコンを有するトランジスタ、または、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、ナノクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有するトランジスタなどを用いることが出来る。または、それらの半導体を薄膜化した薄膜トランジスタ（TFT）などを用いることが

50

出来る。TFTを用いる場合、様々なメリットがある。例えば、単結晶シリコンの場合よりも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることができる。製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多くの個数の表示装置を製造できるため、低コストで製造できる。または、製造温度が低いため、耐熱性の弱い基板を用いることができる。そのため、透光性を有する基板上にトランジスタを製造できる。または、透光性を有する基板上のトランジスタを用いて表示素子での光の透過を制御することが出来る。または、トランジスタの膜厚が薄いため、トランジスタを形成する膜の一部は、光を透過させることが出来る。そのため、開口率が向上させることができる。

## 【0343】

10

なお、多結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。その結果、ゲートドライバ回路（走査線駆動回路）、ソースドライバ回路（信号線駆動回路）、及び信号処理回路（信号生成回路、ガンマ補正回路、D/A変換回路など）を基板上に一体形成することが出来る。

## 【0344】

20

なお、微結晶シリコンを製造するときに、触媒（ニッケルなど）を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することが可能となる。このとき、レーザー照射を行うことなく、熱処理を加えるだけで、結晶性を向上させることも可能である。その結果、ソースドライバ回路の一部（アナログスイッチなど）及びゲートドライバ回路（走査線駆動回路）を基板上に一体形成することが出来る。なお、結晶化のためにレーザー照射を行わない場合は、シリコンの結晶性のムラを抑えることができる。そのため、画質の向上した画像を表示することが出来る。ただし、触媒（ニッケルなど）を用いずに、多結晶シリコン又は微結晶シリコンを製造することは可能である。

## 【0345】

30

なお、シリコンの結晶性を、多結晶又は微結晶などへと向上させることは、パネル全体で行なうことが望ましいが、それに限定されない。パネルの一部の領域のみにおいて、シリコンの結晶性を向上させてもよい。選択的に結晶性を向上させることは、レーザー光を選択的に照射することなどにより可能である。例えば、画素以外の領域である周辺回路領域にのみ、ゲートドライバ回路及びソースドライバ回路などの領域にのみ、又はソースドライバ回路の一部（例えば、アナログスイッチ）の領域にのみ、にレーザー光を照射してもよい。その結果、回路を高速に動作させる必要がある領域にのみ、シリコンの結晶化を向上させることができる。画素領域は、高速に動作させる必要性が低いため、結晶性が向上されなくても、問題なく画素回路を動作させることが出来る。こうすることによって、結晶性を向上させる領域が少なくて済むため、製造工程も短くすることが出来る。そのため、スループットが向上し、製造コストを低減させることが出来る。または、必要とされる製造装置の数も少ない数で製造できるため、製造コストを低減させることが出来る。

## 【0346】

40

なお、トランジスタの一例としては、化合物半導体（例えば、SiGe、GaAsなど）、又は酸化物半導体（例えば、Zn-O、In-Ga-Zn-O、In-Zn-O、In-Sn-O（ITO）、Sn-O、Ti-O、Al-Zn-Sn-O（AZTO）、In-Sn-Zn-Oなど）などを有するトランジスタを用いることが出来る。または、これらの化合物半導体、又は、これらの酸化物半導体を薄膜化した薄膜トランジスタなどを用いることが出来る。これらにより、製造温度を低くできるので、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えばプラスチック基板又はフィルム基板などに直接トランジスタを形成することが出来る。なお、これらの化合物半導体又は酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体又は酸化物半導体を配線、抵抗素子、画素電極、又は透光性を有する電極などとして用いることができる。それらをトランジスタと同時に成膜又は形成することが可能なため、コストを低減できる。

50

## 【0347】

なお、トランジスタの一例としては、インクジェット法又は印刷法を用いて形成したトランジスタなどを用いることが出来る。これらにより、室温で製造、低真密度で製造、又は大型基板上に製造することができる。よって、マスク（レチカル）を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。または、レジストを用いらずに製造することが可能なので、材料費が安くなり、工程数を削減できる。または、必要な部分にのみ膜を付けることが可能なので、全面に成膜した後でエッティングする、という製法よりも、材料が無駄にならず、低コストにできる。

## 【0348】

なお、トランジスタの一例としては、有機半導体やカーボンナノチューブを有するトランジスタ等を用いることができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。有機半導体やカーボンナノチューブを有するトランジスタを用いた装置は、衝撃に強くすることができる。

10

## 【0349】

なお、トランジスタとしては、他にも様々な構造のトランジスタを用いることができる。例えば、トランジスタとして、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを用いることが出来る。トランジスタとしてMOS型トランジスタを用いることにより、トランジスタのサイズを小さくすることが出来る。よって、多数のトランジスタを搭載することができる。トランジスタとしてバイポーラトランジスタを用いることにより、大きな電流を流すことが出来る。よって、高速に回路を動作させることができる。なお、MOS型トランジスタとバイポーラトランジスタとを1つの基板に混在させて形成してもよい。これにより、低消費電力、小型化、高速動作などを実現することが出来る。

20

## 【0350】

例えば、本明細書等において、トランジスタの一例としては、ゲート電極が2個以上のマルチゲート構造のトランジスタを用いることができる。マルチゲート構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に接続された構造となる。よって、マルチゲート構造により、オフ電流の低減、トランジスタの耐圧向上（信頼性の向上）を図ることが出来る。または、マルチゲート構造により、飽和領域で動作する時に、ドレインとソースとの間の電圧が変化しても、ドレインとソースとの間の電流があまり変化せず、傾きがフラットである電圧・電流特性を得ることができる。傾きがフラットである電圧・電流特性を利用すると、理想的な電流源回路、又は非常に高い抵抗値をもつ能動負荷を実現することが出来る。その結果、特性のよい差動回路又はカレントミラー回路などを実現することが出来る。

30

## 【0351】

なお、トランジスタの一例としては、チャネルの上下にゲート電極が配置されている構造のトランジスタを適用することができる。チャネルの上下にゲート電極が配置される構造にすることにより、複数のトランジスタが並列に接続されたような回路構成となる。よって、チャネル領域が増えるため、電流値の増加を図ることが出来る。または、チャネルの上下にゲート電極が配置されている構造にすることにより、空乏層ができやすくなるため、S値の改善を図ることが出来る。

40

## 【0352】

なお、トランジスタの一例としては、チャネル領域の上にゲート電極が配置されている構造、チャネル領域の下にゲート電極が配置されている構造、正スタガ構造、逆スタガ構造、チャネル領域を複数の領域に分けた構造、チャネル領域を並列に接続した構造、又はチャネル領域が直列に接続する構造などのトランジスタを用いることができる。または、トランジスタとして、プレーナ型、FIN型（フィン型）、TRI-GATE型（トライゲート型）、トップゲート型、ボトムゲート型、ダブルゲート型（チャネルの上下にゲートが配置されている）、など、様々な構成をとることが出来る。

## 【0353】

50

なお、トランジスタの一例としては、チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なっている構造のトランジスタを用いることができる。チャネル領域（もしくはその一部）にソース電極やドレイン電極が重なる構造にすることによって、チャネル領域の一部に電荷が溜まることにより動作が不安定になることを防ぐことができる。

#### 【0354】

なお、トランジスタの一例としては、LDD領域を設けた構造を適用できる。LDD領域を設けることにより、オフ電流の低減、又はトランジスタの耐圧向上（信頼性の向上）を図ることができる。または、LDD領域を設けることにより、飽和領域で動作する時に、ドレインとソースとの間の電圧が変化しても、ドレイン電流があまり変化せず、傾きがフラットな電圧・電流特性を得ることができる。

10

#### 【0355】

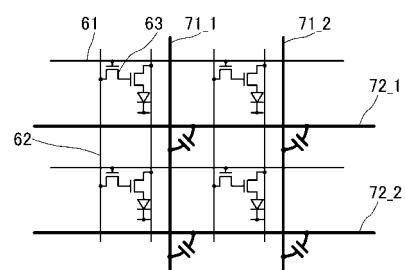

例えば、図61において、トップゲート型のトランジスタを用いた場合を図79に示す。

#### 【0356】

##### [接続とは]

例えば、本明細書等において、XとYとが接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。

20

#### 【0357】

ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

#### 【0358】

XとYとが直接的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に接続されていない場合であり、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）を介さずに、XとYとが、接続されている場合である。

30

#### 【0359】

XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。なお、XとYとが電気的に接続されている場合は、XとYとが直接的に接続されている場合を含むものとする。

40

#### 【0360】

XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（D/A変換回路、A/D変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフト回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きく出来る回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能である。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信

50

号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。なお、XとYとが機能的に接続されている場合は、XとYとが直接的に接続されている場合と、XとYとが電気的に接続されている場合とを含むものとする。

#### 【0361】

なお、XとYとが電気的に接続されている、と明示的に記載されている場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子又は別の回路を挟まずに接続されている場合）とが、本明細書等に開示されているものとする。つまり、電気的に接続されている、と明示的に記載されている場合は、単に、接続されている、とのみ明示的に記載されている場合と同様な内容が、本明細書等に開示されているものとする。

10

#### 【0362】

なお、例えば、トランジスタのソース（又は第1の端子など）が、Z1を介して（又は介さず）、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2を介して（又は介さず）、Yと電気的に接続されている場合や、トランジスタのソース（又は第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（又は第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することが出来る。

20

#### 【0363】

例えば、「XとYとトランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（又は第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（又は第2の端子など）はYと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（又は第1の端子など）とドレイン（又は第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（又は第1の端子など）、トランジスタのドレイン（又は第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（又は第1の端子など）と、ドレイン（又は第2の端子など）とを、区別して、技術的範囲を決定することができる。

30

#### 【0364】