(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6336508号

(P6336508)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月11日(2018.5.11)

(51) Int.Cl.

H04L 25/02 (2006.01)

H03K 19/0175 (2006.01)

F 1

H04L 25/02

H03K 19/0175 220

H03K 19/0175 290

請求項の数 11 (全 18 頁)

(21) 出願番号 特願2016-83699 (P2016-83699)

(22) 出願日 平成28年4月19日 (2016.4.19)

(65) 公開番号 特開2017-50839 (P2017-50839A)

(43) 公開日 平成29年3月9日 (2017.3.9)

審査請求日 平成29年8月2日 (2017.8.2)

(31) 優先権主張番号 特願2015-171942 (P2015-171942)

(32) 優先日 平成27年9月1日 (2015.9.1)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000004695

株式会社 S O K E N

愛知県日進市米野木町南山500番地20

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110000567

特許業務法人 サトー国際特許事務所

(72) 発明者 森 寛之

愛知県西尾市下羽角町岩谷14番地 株式会社日本自動車部品総合研究所内

(72) 発明者 本田 卓矢

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

最終頁に続く

(54) 【発明の名称】 リンギング抑制回路

## (57) 【特許請求の範囲】

## 【請求項 1】

一対の高電位側信号線 (3P), 低電位側信号線 (3N) によりハイ, ローの2値レベルに変化する差動信号を伝送する伝送線路 (3) に接続され、前記信号の伝送に伴い発生するリンギングを抑制するリンギング抑制回路において、

前記一対の信号線間に接続される電圧駆動型で单一の線間スイッチング素子 (15) と、

前記差動信号のレベルが変化したことを検出すると、前記線間スイッチング素子をオンさせて前記信号線間のインピーダンスを低下させる制御部 (6) と、

入力される設定信号により示される抑制期間の長さを検出する期間検出部 (10, 33, 43) と、

前記検出された抑制期間の長さを記憶する抑制期間記憶部 (11, 54) とを備え、

前記制御部は、抑制期間記憶部に記憶された長さの抑制期間だけ、前記線間スイッチング素子をオンさせ、

前記設定信号は、前記抑制期間の長さを電圧レベルで示すリンギング抑制回路。

## 【請求項 2】

前記電圧レベルは、電源電圧を、複数の抵抗素子 (63, 64, 65, 66) からなる分圧回路により分圧することで示される請求項1記載のリンギング抑制回路。

## 【請求項 3】

前記複数の抵抗素子の1つ以上が、可変抵抗素子 (65, 66) である請求項2記載の

リングング抑制回路。

【請求項 4】

前記分圧回路にセレクタ(67)を備え、

前記セレクタにより抵抗素子の通電経路を切替えて、前記電圧レベルを変更する請求項2又は3記載のリングング抑制回路。

【請求項 5】

前記セレクタは、電圧駆動型の半導体スイッチング素子(68)で構成される請求項4記載のリングング抑制回路。

【請求項 6】

一対の高電位側信号線(3P),低電位側信号線(3N)によりハイ,ローの2値レベルに変化する差動信号を伝送する伝送線路(3)に接続され、前記信号の伝送に伴い発生するリングングを抑制するリングング抑制回路において、

前記一対の信号線間に接続される電圧駆動型で单一の線間スイッチング素子(15)と、

前記差動信号のレベルが変化したことを検出すると、前記線間スイッチング素子をオンさせて前記信号線間のインピーダンスを低下させる制御部(6)と、

入力される設定信号により示される抑制期間の長さを検出する期間検出部(10,33,43)と、

前記検出された抑制期間の長さを記憶する抑制期間記憶部(11,54)とを備え、

前記制御部は、抑制期間記憶部に記憶された長さの抑制期間だけ、前記線間スイッチング素子をオンさせ、

前記設定信号は、前記抑制期間の長さをパルス幅で示し、

前記期間検出部は、電源の供給が開始されたことを検出する電源供給検出部と、

前記設定信号のパルスの立下りエッジを検出するエッジ検出部と、

前記電源の供給開始が検出されたことをトリガとして設定イネーブル信号をアクティブにし、前記立下りエッジが検出されたことをトリガとして設定イネーブル信号をインアクティブにするイネーブル信号出力部と、

前記設定イネーブル信号がアクティブである期間の長さに応じた電圧レベルを生成する電圧信号変換部とを備えるリングング抑制回路。

【請求項 7】

一対の高電位側信号線(3P),低電位側信号線(3N)によりハイ,ローの2値レベルに変化する差動信号を伝送する伝送線路(3)に接続され、前記信号の伝送に伴い発生するリングングを抑制するリングング抑制回路において、

前記一対の信号線間に接続される電圧駆動型で单一の線間スイッチング素子(15)と、

前記差動信号のレベルが変化したことを検出すると、前記線間スイッチング素子をオンさせて前記信号線間のインピーダンスを低下させる制御部(6)と、

入力される設定信号により示される抑制期間の長さを検出する期間検出部(10,33,43)と、

前記検出された抑制期間の長さを記憶する抑制期間記憶部(11,54)と、

前記設定信号を前記期間検出部に送信する設定信号送信部(9)とを備え、

前記制御部は、抑制期間記憶部に記憶された長さの抑制期間だけ、前記線間スイッチング素子をオンさせ、

前記設定信号送信部は、前記抑制期間の長さに応じて、前記設定信号が示すハイ又はローレベルの何れかを継続する時間の長さを変化させて送信し、

前記期間検出部は、前記時間の長さに応じてコンデンサ(26)を充電する充電部(24,25)と、

前記コンデンサの端子電圧を、それぞれ異なる閾値と比較する複数のコンパレータ(27)とを備え、

これら複数のコンパレータの出力信号が変化する数に応じて、前記時間の長さを検出する

10

20

30

40

50

るリングング抑制回路。

【請求項 8】

前記抑制期間記憶部(11)は、前記複数のコンパレータの出力信号の変化状態を記憶するラッチ回路を備える請求項7記載のリングング抑制回路。

【請求項 9】

一対の高電位側信号線(3P)、低電位側信号線(3N)によりハイ、ローの2値レベルに変化する差動信号を伝送する伝送線路(3)に接続され、前記信号の伝送に伴い発生するリングングを抑制するリングング抑制回路において、

前記一対の信号線間に接続される電圧駆動型で单一の線間スイッチング素子(15)と

10

前記差動信号のレベルが変化したことを検出すると、前記線間スイッチング素子をオンさせて前記信号線間のインピーダンスを低下させる制御部(6)と、

入力される設定信号により示される抑制期間の長さを検出する期間検出部(10, 33, 43)と、

前記検出された抑制期間の長さを記憶する抑制期間記憶部(11, 54)とを備え、前記制御部は、抑制期間記憶部に記憶された長さの抑制期間だけ、前記線間スイッチング素子をオンさせ、

前記設定信号送信部(32)は、前記抑制期間の長さに応じて、前記設定信号が2値レベル間で遷移するエッジの出力回数を変化させて送信し、

前記期間検出部(33)は、前記出力回数を検出するリングング抑制回路。

20

【請求項 10】

前記期間検出部は、前記設定信号が変化する回数をカウントするカウンタ(36)を備える請求項9記載のリングング抑制回路。

【請求項 11】

前記抑制期間記憶部(11)は、前記コンパレータの出力信号が変化しない状態が所定期間継続すると、前記カウンタのカウンタ値をラッチするラッチ回路で構成される請求項10記載のリングング抑制回路。

【発明の詳細な説明】

【技術分野】

【0001】

30

本発明は、一対の高電位側信号線、低電位側信号線により差動信号を伝送する伝送線路に接続され、前記信号の伝送に伴い発生するリングングを抑制する回路に関する。

【背景技術】

【0002】

伝送線路を介してデジタル信号を伝送する場合、受信側においては、信号レベルが変化するタイミングで信号エネルギーの一部が反射することで、オーバーシュートやアンダーシュートのような波形の歪み、すなわちリングングが生じる問題がある。そして、従来、波形歪みを抑制する技術については様々な提案がされている。例えば特許文献1では、伝送路の電圧レベルがロー、ハイ間で遷移する際に、通信に影響しない一定期間のみインピーダンスを整合させてリングングを抑制する技術が開示されている。

40

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第5498527号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1では、インピーダンスを整合させる期間が固定されている。そのため、実際の通信速度が想定していたものよりも低速であった場合は、十分なリングング抑制効果が得られない。また、実際の通信速度が想定していたものよりも高速であつ

50

た場合は、通信信号を正常に受信できなくなってしまう。このような事態を回避するには、個別の通信速度に対応して製品を設計する必要があり、品番の増加やコストアップの要因となっていた。

【0005】

本発明は上記事情に鑑みてなされたものであり、その目的は、異なる通信速度に対応して最適にリングングを抑制できるリングング抑制回路を提供することにある。

【課題を解決するための手段】

【0006】

請求項1記載のリングング抑制回路によれば、期間検出部は、設定信号により電圧レベルで示される抑制期間の長さを検出し、抑制期間記憶部は検出された抑制期間の長さを記憶する。そして、制御部は、差動信号のレベルが変化したことを検出すると、抑制期間記憶部に記憶された長さの抑制期間だけ線間スイッチング素子をオンさせる。

【0007】

このように構成すれば、差動信号の通信速度に応じて抑制期間の長さを決定して、その長さに応じた設定信号を付与し、抑制期間の長さを抑制期間記憶部に記憶することで、制御部が線間スイッチング素子をオンさせる期間を可変設定できる。したがって、通信速度に応じて最適にリングングを抑制することが可能になる。

【図面の簡単な説明】

【0008】

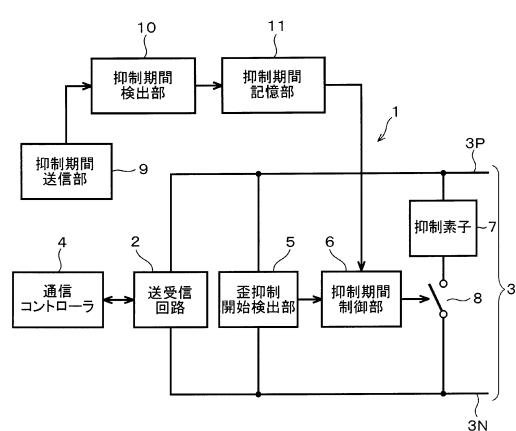

【図1】第1実施形態であり、リングング抑制回路の構成を示す機能ブロック図

20

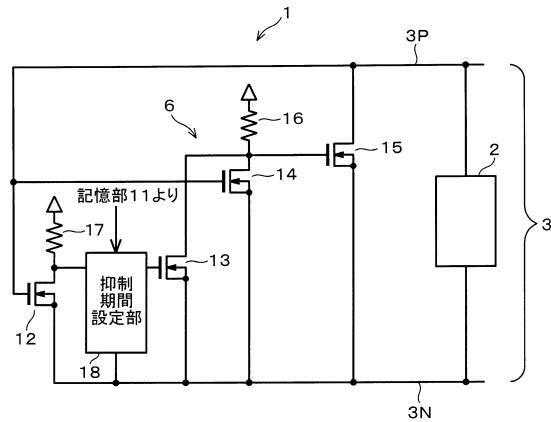

【図2】リングング抑制回路の一部を、具体的な回路で示す図

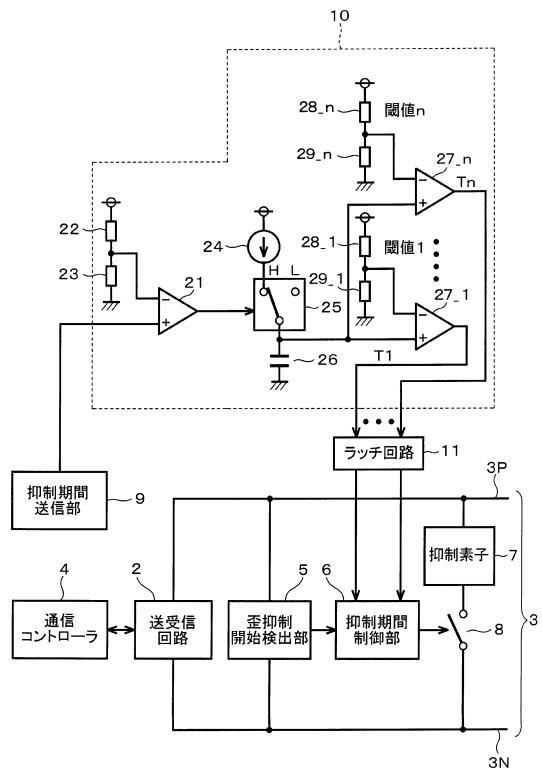

【図3】抑制期間検出部及び抑制期間記憶部の構成をより具体的に示す図

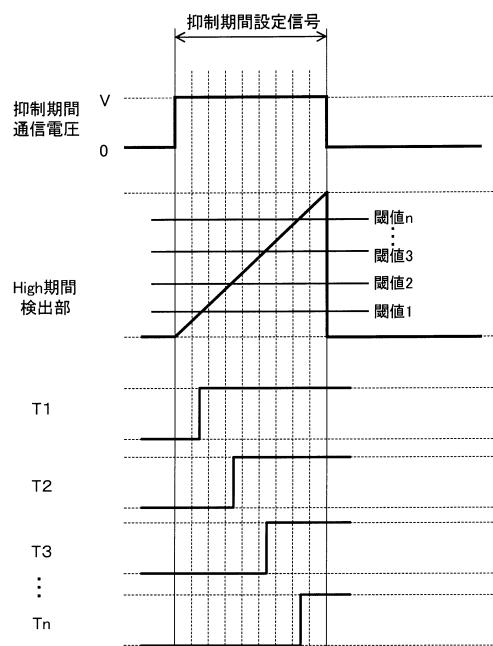

【図4】動作タイミングチャート

【図5】抑制期間設定部の具体的な構成例を示す図（その1）

【図6】信号T1～Tnと各スイッチのオンオフ状態を示す図

【図7】抑制期間設定部の具体的な構成例を示す図（その2）

【図8】信号T1～Tn+1と各スイッチのオンオフ状態を示す図

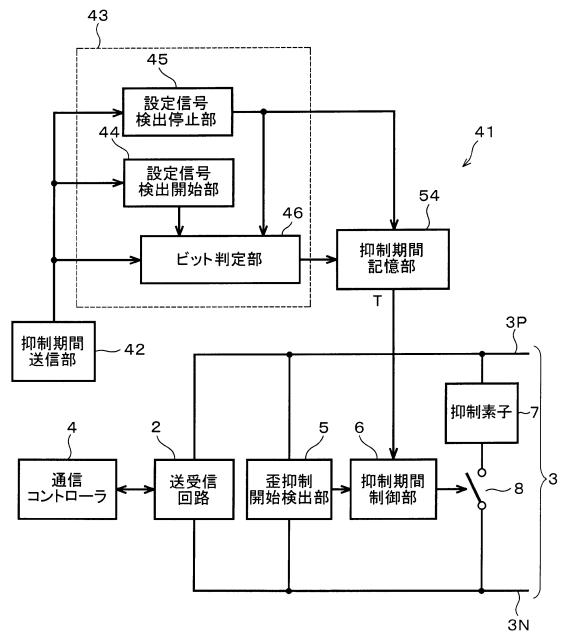

【図9】第2実施形態であり、リングング抑制回路の構成を示す機能ブロック図

【図10】抑制期間検出部及び抑制期間記憶部の構成をより具体的に示す図

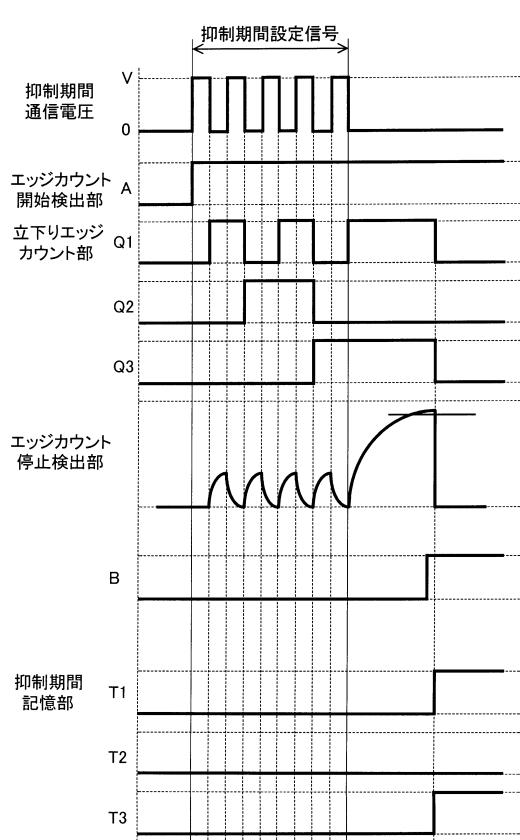

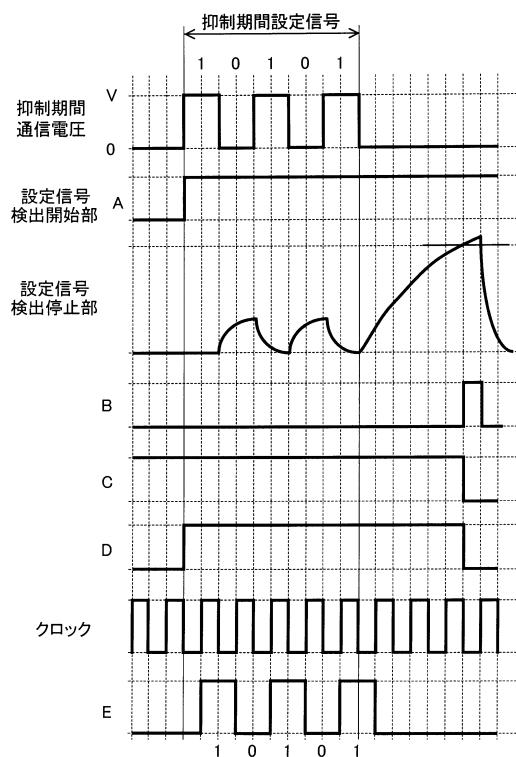

【図11】動作タイミングチャート

30

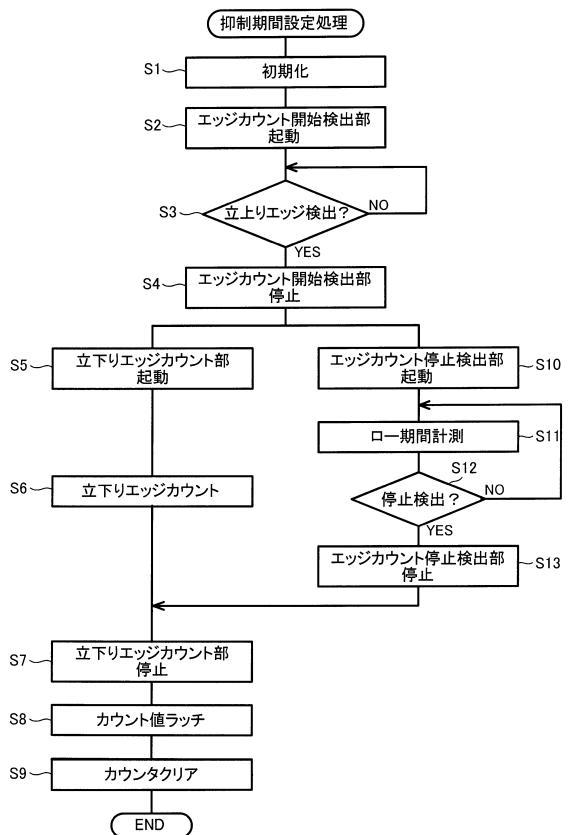

【図12】回路動作を示すフローチャート

【図13】第3実施形態であり、リングング抑制回路の構成を示す機能ブロック図

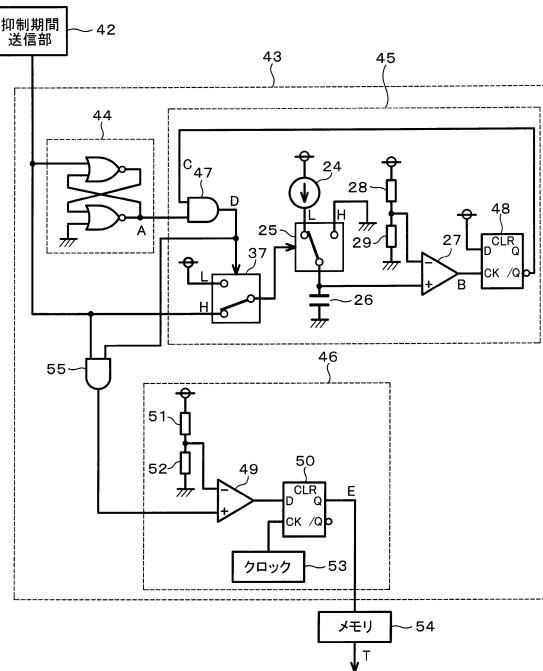

【図14】抑制期間検出部及び抑制期間記憶部の構成をより具体的に示す図

【図15】動作タイミングチャート

【図16】第4実施形態を示す動作タイミングチャート

【図17】第5実施形態であり、リングング抑制回路の構成を示す機能ブロック図

【図18】設定信号を付与する構成の変形例を示す図（その1）

【図19】設定信号を付与する構成の変形例を示す図（その2）

【図20】設定信号を付与する構成の変形例を示す図（その3）

【図21】第6実施形態であり、リングング抑制回路の構成を示す機能ブロック図

40

【図22】動作タイミングチャート

【発明を実施するための形態】

【0009】

（第1実施形態）

以下、第1実施形態について説明する。図1に示すように、リングング抑制回路1は、送受信回路2と共に、高電位側信号線3P、低電位側信号線3Nよりなる伝送線路3の間に並列に接続されている。尚、送受信回路2に替えて、送信回路又は受信回路でも良い。送受信回路2は、通信コントローラ4により制御され、伝送線路3を駆動して差動信号を送信し、また、伝送線路3を介して他の送信ノードより送信された差動信号を受信すると、受信データを通信コントローラ4に入力する。

50

## 【0010】

歪開始回路検出部5は、差動信号が伝送される際に伝送線路3の電圧が変化したことを検出し、抑制期間制御部6に歪、リングングの抑制動作を開始させるトリガ信号を与える。信号線3P, 3Nの間には、抑制素子7及びスイッチ回路8の直列回路が接続されている。抑制期間制御部6は、上記のトリガ信号が入力されると、設定された抑制期間だけスイッチ回路8をオンして伝送路3のインピーダンスを低下させる。

## 【0011】

本実施形態において、前記抑制期間の長さの設定を変更可能にする。そのため、抑制期間送信部9は、抑制期間の長さを抑制期間制御部6に設定する設定信号を送信する。設定信号は抑制期間検出部10により受信されて検出されると、抑制期間記憶部11に記憶される。そして、抑制期間制御部6は、抑制期間記憶部11に記憶された長さの抑制期間だけスイッチ回路8をオンする。

10

## 【0012】

より具体的な構成を示す図2において、4つのNチャネルMOSFET12～15の電位基準側導通端子であるソースは、何れも低電位側信号線3Nに接続されており、NチャネルMOSFET12及び14の制御端子であるゲートは、高電位側信号線3Pに接続されている。

## 【0013】

線間スイッチング素子であるFET15の非基準側導通端子であるドレインは高電位側信号線3Pに接続されており、FET13及び14のドレインはFET15のゲートに接続されていると共に抵抗素子16を介してハイレベル、すなわち電源レベル(Vcc)にプルアップされている。FET12のドレインは、抵抗素子17を介してハイレベルにプルアップされていると共に、抑制期間設定部18を介してFET13のゲートに接続されている。以上において、FET15は図1に示す抑制素子7及びスイッチ回路8の直列回路に相当する。つまり、FET15のオン抵抗が抑制素子7に相当している。また、FET12は歪開始回路検出部5に相当し、その他は抑制期間制御部6に相当する。

20

## 【0014】

図3に示すように、抑制期間検出部10はコンパレータ21を備えている。コンパレータ21の非反転入力端子には、抑制期間送信部9からの送信信号が与えられる。電源とグランドとの間には抵抗素子22及び23の直列回路が接続されており、それらの共通接続点はコンパレータ21の反転入力端子に接続されている。

30

## 【0015】

また、電源とグランドとの間には、電流源24、セレクタ25及びコンデンサ26の直列回路が接続されている。電流源24及びセレクタ25は充電部に相当する。電流源24の下端は、セレクタ25のH側入力端子に接続されており、セレクタ25の出力端子がコンデンサ26の上端に接続されている。セレクタ25のL側入力端子はオープンである。セレクタ25の入力選択はコンパレータ21の出力信号で制御される。すなわち、前記出力信号の二値レベル変化に応じて、H/L側入力端子が選択される。

## 【0016】

更に、抑制期間検出部10は、例えばn個のコンパレータ27\_1～27\_nを備えており、これらの非反転入力端子は共通に、セレクタ25の出力端子に接続されている。各コンパレータ27\_1～27\_nに対応して、コンパレータ21と同様に抵抗素子28\_1～n及び29\_1～nの直列回路が設けられており、それぞれの共通接続点がコンパレータ27\_1～27\_nの反転入力端子に接続されている。各共通接続点の電位によりそれぞれ閾値1～nが付与される。閾値1が最低レベル、閾値nが最高レベルであり、それらの間は順次レベルが上昇するように設定されている。各コンパレータ27\_1～27\_nの出力信号T1～Tnは、ラッチ回路で構成される抑制期間記憶部11を介して抑制期間制御部6に入力されている。

40

## 【0017】

図2に示す抑制期間設定部18は、図5又は図7に示すように、時定数を変更可能な積

50

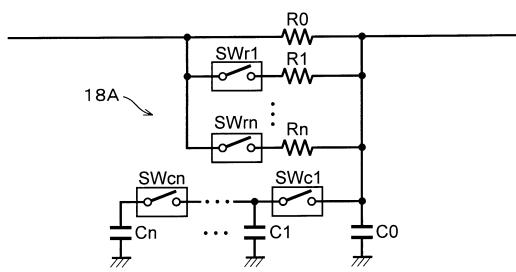

分回路、すなわち遅延回路で構成されている。図5に示す抑制期間設定部18Aは、抵抗素子R0～Rn、コンデンサC0～Cn、スイッチSWr1～SWrn及びSWc1～SWcnを有している。抵抗素子R0に対して、スイッチSWr1及び抵抗素子R1～SWrn及びRnからなる各直列回路が並列に接続されている。

#### 【0018】

各抵抗素子R0～Rnの共通接続点は、コンデンサC0を介してグランドに接続されている。その他のコンデンサC1～Cnの下端は何れもグランドに接続され、コンデンサC0、C1の上端はスイッチSWc1を介して接続され、…コンデンサCn-1、Cnの上端はスイッチSWcnを介して接続されている。スイッチSWr1及びSWc1～SWrn及びSWcnのオンオフは、それぞれ抑制期間記憶部11より入力される信号T1～Tnにより制御される。 10

#### 【0019】

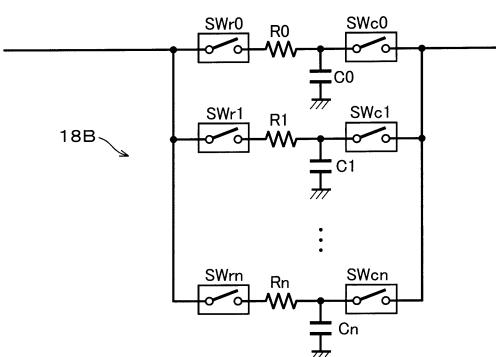

また、図7に示す抑制期間設定部18Bは、抑制期間設定部18Aに加えてスイッチSWr0及びSWc0を備えている。抵抗素子R0及びコンデンサC0、…、抵抗素子Rn及びコンデンサCnがそれぞれ積分回路を構成しており、共通の入力端子と抵抗素子R0、R1、…、Rnとの間にはそれぞれスイッチSWr0、…、SWrnが配置されており、コンデンサC0、…、Cnと共に出力端子との間にはそれぞれスイッチSWc0、…、SWcnが配置されている。スイッチSWr0及びSWc0～SWrn及びSWcnのオンオフは、抑制期間設定部18Aと同様に抑制期間記憶部11より入力される信号により制御されるが、この場合は信号Tn+1まで必要となる。 20

#### 【0020】

次に、本実施形態の作用について説明する。図4に示すように、抑制期間送信部9は、抑制期間の長さをハイレベル期間で示す抑制期間設定信号を送信する。すると、抑制期間検出部10のコンパレータ21は、抑制期間設定信号がハイレベルを示す間に出力信号をハイレベルにする。コンパレータ21の出力信号がハイレベルを示す間、コンデンサ26は電流源24により充電されるので、その端子電圧は線形に上昇する。 20

#### 【0021】

コンデンサ26の端子電圧が上昇する期間の長さに応じて、コンパレータ27は、設定されている閾値が低い方から順次出力信号をハイレベルに変化させる。抑制期間記憶部11は例えばラッチ回路で構成され、各信号の立上りエッジをトリガとして出力信号T1、…をハイレベルにする。 30

#### 【0022】

図5に示す抑制期間設定部18Aの構成では、全てのスイッチがオフの場合は抵抗素子R0及びコンデンサC0のみで積分回路が構成され、時定数が最小になっている。その状態から出力信号T1、…、Tnが順次ハイレベルに変化すると、スイッチSWr1及びSWc1、…、SWrn及びSWcnが順次オンになり、時定数が漸増する(図6参照)。

#### 【0023】

また、図7に示す抑制期間設定部18Bの構成では、出力信号T1、…、Tn+1により、スイッチSWr1及びSWc1、…、SWrn及びSWcnの何れか一組のだけが排他的にオンされる。これにより、積分回路R0及びC0～Rn及びCnの何れか1つが接続される(図8参照)。この場合、積分回路R0及びC0～Rn及びCnの時定数が、次第に大きくなるように設定されている。 40

#### 【0024】

そして、伝送線路3に接続されている通信ノードによって伝送線路3がドライブされて差動信号が送信された際に、差動信号レベルがハイの場合にFET12及び14はオンしているので、FET13はオフしている。したがって、FET15はオフ状態となっている。この状態から、差動信号レベルがハイからローに変化するとFET4及び6がターンオフする。すると、抑制期間設定部18において、抑制期間記憶部11に記憶された設定期間の長さに応じた遅延時間が経過した後にFET15がターンオンする。すると、高電位側信号線3P、低電位側信号線3N間はFET15のオン抵抗を介して接続されること 50

になり、インピーダンスが低下する。これにより、差動信号レベルがハイからローに変化する立下り期間に発生する波形歪みのエネルギーが上記オン抵抗により消費され、リングングが抑制される。

【0025】

以上のように本実施形態によれば、抑制期間送信部9が抑制期間の長さを示す設定信号を送信すると、抑制期間検出部10が設定信号により示される抑制期間の長さを検出し、抑制期間記憶部11は検出された抑制期間の長さを記憶する。そして、抑制期間制御部6は、歪み抑制開始検出部5が差動信号のレベルが変化したことを検出すると、抑制期間記憶部11に記憶された長さの抑制期間だけFET15をオンさせる。

【0026】

このように構成すれば、差動信号の通信速度に応じて抑制期間の長さを決定し、抑制期間送信部9が設定信号を送信することで、抑制期間制御部6がFET15をオンさせる期間を可変設定できる。したがって、リングング抑制回路1は、適用される通信速度に応じてリングングを最適に抑制することが可能になる。

【0027】

この場合、抑制期間送信部9は、抑制期間の長さに応じて設定信号が示すハイレベルの継続時間を変化させて送信し、抑制期間検出部10は前記継続時間の長さを検出するので、簡単な信号形式により抑制期間の長さを示すことができる。

【0028】

また、抑制期間検出部10は、前記継続時間の長さに応じてコンデンサ26を充電し、コンデンサ26の端子電圧を、コンパレータ27\_1～27\_nによりそれぞれ異なる閾値と比較し、コンパレータ27\_1～27\_nの出力信号が変化する数に応じて継続時間の長さを検出するので、簡単なハードウェアにより継続時間の長さを検出できる。そして、抑制期間記憶部11は、コンパレータ27\_1～27\_nの出力信号の変化状態を記憶するラッチ回路を備えるので、継続時間の長さで示された抑制期間の長さをラッチ回路で記憶することができる。

【0029】

加えて、抑制期間設定部18は、時定数を変更可能に構成される積分回路を備え、抑制期間記憶部11に記憶された抑制期間の長さに応じて時定数を変化させ、抑制期間制御部6は、前記時定数に応じてFET15をオンさせる。したがって、抑制期間の長さを簡単な構成によって調整できる。

【0030】

(第2実施形態)

以下、第1実施形態と同一部分には同一符号を付して説明を省略し、異なる部分について説明する。第2実施形態では、抑制期間の長さを示す設定信号の形式が第1実施形態とは異なっている。すなわち、図11に示すように、設定信号のレベルがハイ／ローに変化する回数により抑制期間の長さが示される。

【0031】

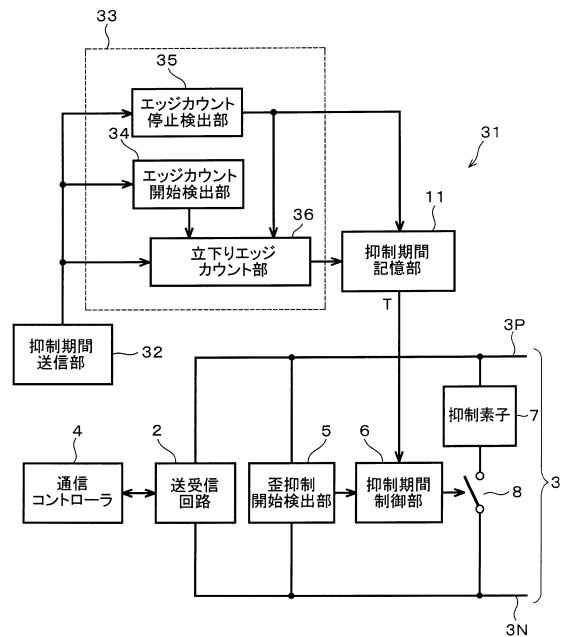

図9に示すように、第2実施形態のリングング抑制回路31は、抑制期間送信部9及び抑制期間検出部10に替わる抑制期間送信部32及び抑制期間検出部33を備えている。抑制期間検出部33は、エッジカウント開始検出部34、エッジカウント停止検出部35及び立下りエッジカウント部36を有している。

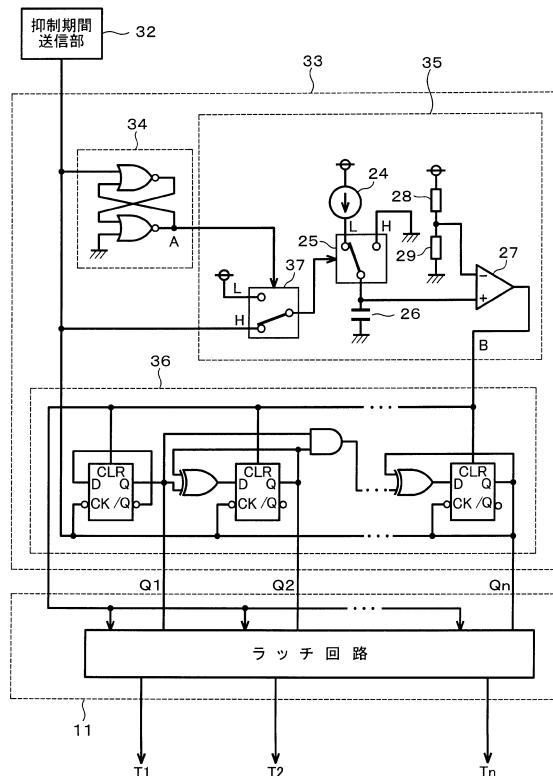

【0032】

図10に示すように、エッジカウント開始検出部34はラッチ回路で構成されている。エッジカウント停止検出部35は、第1実施形態の充電部及びコンデンサ26と、1つのコンパレータ27とを備えている。但し、電流源24はセレクタ25のL側入力端子に接続されており、H側入力端子はグランドに接続されている。

【0033】

これらに加えて、エッジカウント停止検出部35は、もう1つのセレクタ37を備えている。セレクタ37のH側入力端子は抑制期間送信部32の出力端子に接続され、L側入

10

20

30

40

50

力端子は電源にプルアップされている。セレクタ37の入力選択はエッジカウント開始検出部34の出力信号によって行われ、セレクタ25の入力選択はセレクタ37の出力信号によって行われる。

【0034】

立下りエッジカウント部36はnビットカウンタで構成され、そのカウント値は、抑制期間記憶部11のラッチ回路によりラッチされる。前記カウンタは、コンパレータ27の出力信号がハイレベルになるとクリアされ、前記ラッチ回路は前記出力信号の立上りエッジで入力データをラッチする。

【0035】

次に、第2実施形態の作用について説明する。図11に示すように、初期状態では、抑制期間送信部32は出力信号のレベルをローに維持している(図12; S1)。エッジカウント開始検出部34の出力信号Aはローレベルであるから、セレクタ37の出力信号はハイレベルになり、セレクタ25はコンデンサ26を放電させている。したがって、コンパレータ27の出力信号Bはローレベルになっている。この状態から、抑制期間送信部32は出力信号のレベルをハイ/ローの二値レベルで変化させる回数によって設定信号を送信する。

【0036】

最初に抑制期間送信部32の出力信号がハイレベルに変化すると、出力信号Aがハイレベルになり(S2, S3; YES)、以後この状態が固定される(S4)。すると、セレクタ37はH側入力端子を選択するので、コンデンサ26が充電される。ここで、抑制期間送信部32が設定信号としてハイレベルパルスを5回出力したとする。この時、セレクタ25は、設定信号がハイレベルを示す毎にコンデンサ26を放電させており、設定信号のレベルが一定時間内で変化している間は、信号Bはローレベルのままである(S10~S12)。

【0037】

設定信号の立下りエッジにより、立下りエッジカウント部36のカウンタはカウント動作を行う(S5, S6)。図11では3ビット(Q1~Q3)のみを示す。そして、設定信号の送信が完了してローのレベルが継続する状態になると(S7)、コンデンサ26の充電が継続されて端子電圧が上昇する。端子電圧がコンパレータ27の閾値電圧を超えると信号Bがハイレベルとなり(S12; YES)、抑制期間記憶部11のラッチ回路はカウント値「5」をラッチし(S8)、立下りエッジカウント部36のカウンタはクリアされる(S9)。

【0038】

以上のように第2実施形態によれば、抑制期間送信部32は、抑制期間の長さに応じて設定信号が2値レベル間で遷移するエッジの出力回数を変化させて送信し、抑制期間検出部33は、その出力回数を検出する。したがって、よりノイズ耐性を向上させた態様で設定信号を送信できる。この場合、抑制期間検出部33は、立下りエッジカウント部36により前記出力回数をカウントするので、設定信号で示される抑制期間の長さをカウント値により簡単に検出できる。

【0039】

(第3実施形態)

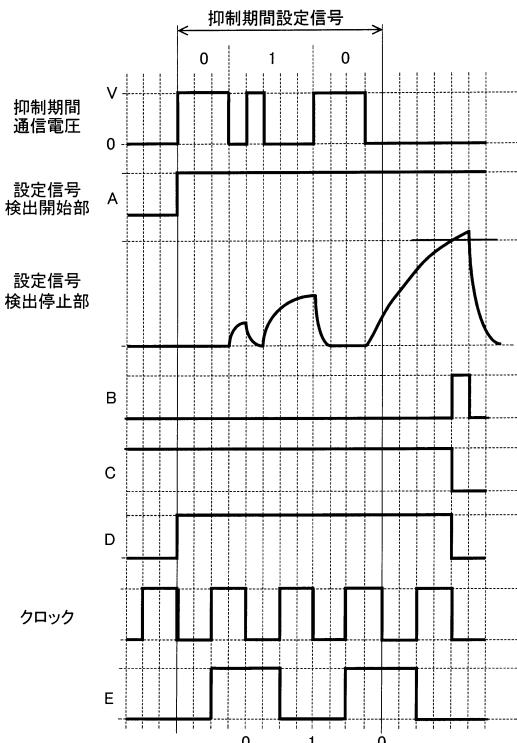

第3実施形態では、抑制期間の長さを示す設定信号の形式が第1及び第2実施形態とは異なっており、図15に示すように、NRZ信号によるデジタルデータで抑制期間の長さが示される。図13に示すように、第3実施形態のリンクギング抑制回路41は、抑制期間送信部9及び抑制期間検出部10に替わる抑制期間送信部42及び抑制期間検出部43を備えている。抑制期間検出部43は、設定信号検出開始部44、設定信号検出停止部45及びビット判定部46を有している。

【0040】

図14に示すように、設定信号検出開始部44は、第2実施形態のエッジカウント開始検出部34と同じくラッチ回路で構成されている。設定信号検出停止部45は、第2実施

10

20

30

40

50

形態のエッジカウント停止検出部 35 に、AND ゲート 47 及び D フリップフロップ 48 を加えて構成されている。上記のラッチ回路の出力信号 A は、AND ゲート 47 を介した信号 D としてセレクタ 37 に入力される。コンパレータ 27 の出力信号 B は、D フリップフロップ 48 のクロック端子 CK に与えられ、D フリップフロップ 48 の出力端子 Q (バー) は、信号 C を AND ゲート 47 の入力端子に与える。D フリップフロップ 48 の入力端子 D は、電源にプルアップされている。

【0041】

ビット判定部 46 は、コンパレータ 49, D フリップフロップ 50 を備えている。コンパレータ 49 の非反転入力端子は、AND ゲート 55 の出力端子に接続されている。AND ゲート 55 の入力端子は、それぞれ抑制期間送信部 42 の出力端子, AND ゲート 47 の出力端子に接続されている。反転入力端子には、電源電圧を抵抗素子 51 及び 52 により分圧した閾値が与えられている。コンパレータ 49 の出力端子は、D フリップフロップ 50 の入力端子 D に接続されており、D フリップフロップ 50 のクロック端子 CK には、クロック発振回路 53 よりクロック信号が与えられている。また、第3実施形態の抑制期間記憶部 54 はメモリ等により構成され、D フリップフロップ 48 の出力端子 Q より出力される信号 (データ) E は、上記のメモリにより記憶される。

【0042】

次に、第3実施形態の作用について説明する。図 16 に示すように、初期状態では、抑制期間送信部 42 は出力信号のレベルをローに維持している。尚、D フリップフロップ 48 の出力信号 C は、初期状態でハイレベルである。第2実施形態と同様、設定信号検出開始部 44 の出力信号 A はローでセレクタ 37 の出力信号はハイレベルになり、セレクタ 25 はコンデンサ 26 を放電させている。したがって、コンパレータ 27 の出力信号 B はローである。また、信号 D がローであるから AND ゲート 55 の出力信号もローとなり、信号 E もローのままである。

【0043】

この状態から、抑制期間送信部 42 が出力信号をハイレベルに変化させると、出力信号 A がハイレベルになり、以後この状態が固定される。すると、セレクタ 37 が H 側入力端子を選択してコンデンサ 26 が充電される。ここで、抑制期間送信部 42 が設定信号として、5 ビットのデータ「10101」を送信したとする。この時、セレクタ 25 は第2実施形態と同様に、設定信号がハイレベルを示す毎にコンデンサ 26 を放電させており、設定信号のレベルが一定時間内で変化している間は、信号 B はローのままである。尚、データ送信周期は、ビット判定部 44 におけるクロック信号周期の 2 分周に設定する。

【0044】

また、信号 A がハイレベルになると信号 D もハイレベルになる。これにより、AND ゲート 55 を介して D フリップフロップ 50 の入力端子 D に設定信号が与えられる。すると、D フリップフロップ 50 はデータ「10101」に応じたレベル変化によりトリガされる。したがって、信号 E もデータ「10101」をシリアルに示す信号となる。

【0045】

そして、設定信号の送信が完了してローでレベルが継続する状態になると、第2実施形態と同様にコンデンサ 26 の充電が継続されて端子電圧が上昇し、コンパレータ 27 の閾値電圧を超えると信号 B がハイレベルとなり D フリップフロップ 48 がトリガされる。すると信号 C がローのままである。それに伴い信号 D もローのままである。

【0046】

ここで、抑制期間記憶部 54 によるデータの記憶は、例えばシフトレジスタ等により入力されるシリアルデータをクロック信号によりシフトすることで行うようにすれば良い。そして、抑制期間記憶部 54 に記憶されたデータを、デコーダを介してデコードすることで、第1実施形態と同様に時定数を調整すれば良い。

【0047】

以上のように第3実施形態によれば、抑制期間送信部 42 は、設定信号において抑制期間の長さを所定の形式である NRZ 信号によりデータ化して送信し、抑制期間検出部 43

10

20

30

40

50

はそのデータ値を検出するようにした。このように構成すれば、抑制期間をより長く設定する場合に応じて、設定信号の送信期間を長くする必要がなくなる。

【0048】

(第4実施形態)

第4実施形態は、第3実施形態のリングング抑制回路41を用いて、設定信号をPWM信号形式で送信する場合を示す。図16に示すように、例えばデューティ比75%をデータ「0」とし、デューティ比25%をデータ「1」とする。そして、PWM周期をクロック発振回路53のクロック信号周期に合わせ、当該クロック信号の立ち上りエッジがPWM周期の中心位相に一致するタイミングで設定信号を送信する。すると、信号Eは、デューティ比100%がデータ「0」、デューティ比0%がデータ「1」を示す信号となる。

以上のように構成される第4実施形態によれば、設定信号をPWM信号形式で送信することができる。

【0049】

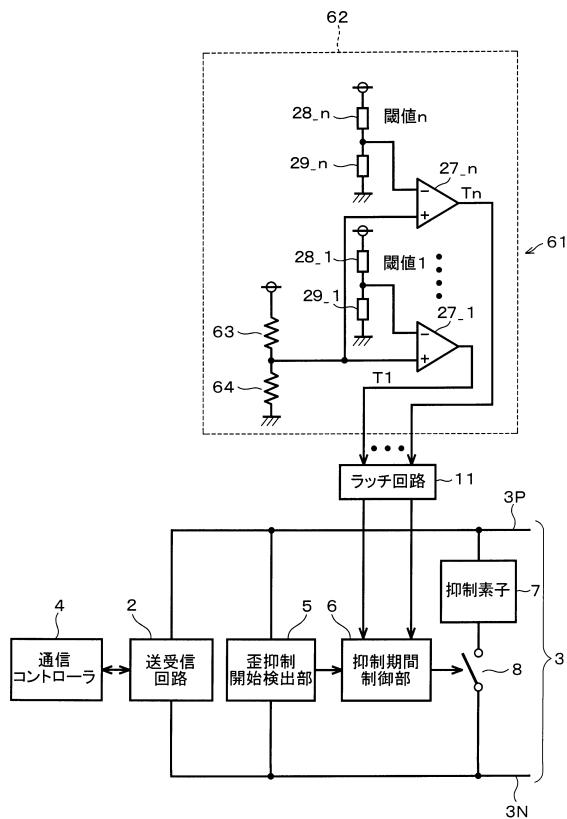

(第5実施形態)

図17に示すように、第5実施形態のリングング抑制回路61は、第1～第4実施形態における抑制期間送信部9等を備えておらず、抑制期間検出部62の入力端子には、電源とグランドとの間に接続される抵抗素子63及び64の共通接続点が接続されている。つまり第5実施形態では設定信号を、電源電圧を分圧した電圧レベルで付与する。そして、抑制期間検出部62は、第1実施形態の抑制期間検出部10よりコンパレータ21～コンデンサ26を削除した構成であり、コンパレータ27\_1～27\_nの非反転入力端子には、抵抗素子63及び64の共通接続点が直接接続されている。すなわち第5実施形態では、設定信号により示される電圧レベルの高低に応じて抑制期間の長短を設定する。

【0050】

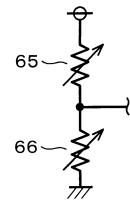

以上のように構成される第5実施形態によれば、第1～第4実施形態のように抑制期間送信部9等を備えずとも、電源電圧を分圧した電圧レベルによって設定信号を付与できる。

【0051】

また、上記のように設定信号を電圧レベルで付与する構成としてはその他、抵抗素子63及び64に替えて、例えば図18に示すように、可変抵抗素子65及び66の直列回路を用いて電圧レベルを変更することもできる。尚、抵抗素子63及び64の何れか一方だけを可変抵抗素子に置き換えるても良い。

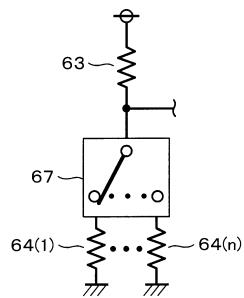

同様に、電圧レベルを変更可能な構成としては、例えば図19に示すように、抵抗素子63の下端にセレクタ67を接続し、それぞれ抵抗値が異なるグランド側の抵抗素子64(1)～64(n)との接続を切替える構成を採用しても良い。

【0052】

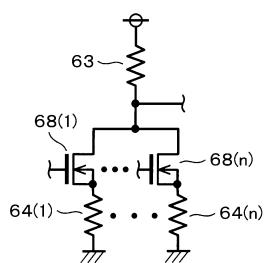

また、例えば図20に示すように、セレクタ67をn個のNチャネルMOSFET68(1)～68(n)に置き換えて、それらの1つ以上を選択的にオンすることで電圧レベルを変更することもできる。この場合、抵抗素子64(1)～64(n)の抵抗値は全て同じであっても良い。また、NチャネルMOSFET68に替えて、NPNトランジスタやアナログスイッチ等を用いても良い。

【0053】

(第6実施形態)

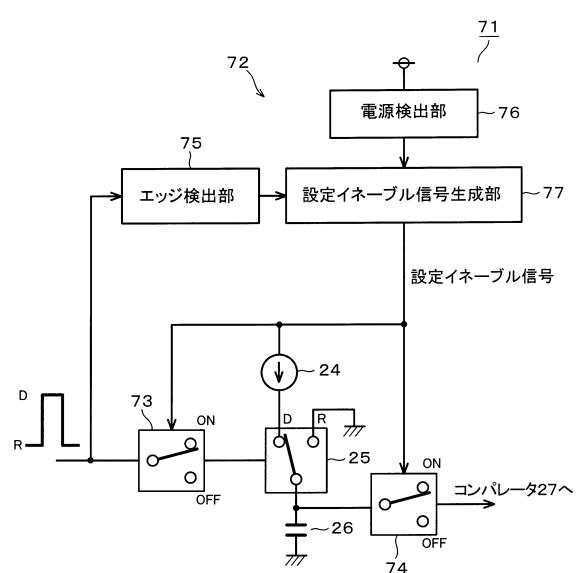

図21に示すように、第6実施形態では、設定信号がパルス信号としてリングング抑制回路71の抑制期間検出部72に入力される。そして、抑制期間の長短は、上記信号のパルス幅で示される。抑制期間検出部72では、第1実施形態の抑制期間検出部10におけるコンパレータ21がセレクタ73に置き換えており、コンデンサ26の上端とコンパレータ27との間にセレクタ74が挿入されている。また、抑制期間検出部72は、エッジ検出部75、電源検出部76及び設定イネーブル信号生成部77を備えている。

【0054】

電源検出部76は、リングング抑制回路71に電源が投入されたことを検出するとON

10

20

30

40

50

トリガ信号を設定イネーブル信号生成部77に出力する。エッジ検出部75は例えばフリップフロップ等で構成され、入力されるパルス信号の立下りエッジを検出するとOFFトリガ信号を設定イネーブル信号生成部77に出力する。設定イネーブル信号生成部77は、ONトリガ信号が入力されると設定イネーブル信号をアクティブルレベルのハイにし、OFFトリガ信号が入力されると設定イネーブル信号をローレベルにする。セレクタ73及び74の切替制御は、設定イネーブル信号によって行われる。

以上において、電源検出部76は電源供給検出部に相当し、設定イネーブル信号生成部77はイネーブル信号出力部に相当する。また、電流源24～コンデンサ26は電圧信号変換部に相当する。

【0055】

10

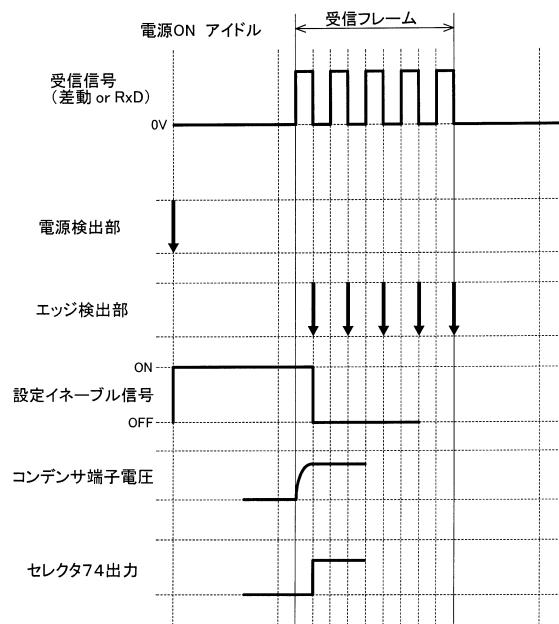

次に、第6実施形態の作用について説明する。初期状態で、セレクタ25はR側に、セレクタ73及び74はOFF側になっている。図22に示すように、リングング抑制回路71に電源が投入されると電源検出部76がONトリガ信号を出力し、設定イネーブル信号生成部77は設定イネーブル信号をハイレベルにする。これにより、セレクタ73及び74は何れもON側に切り替わる。

【0056】

20

この状態で、セレクタ73にパルス信号が入力されると、セレクタ25は、前記信号がハイレベルを示すパルス幅相当の期間だけD側に切り替わり、コンデンサ26は電流源24により充電される。そして、パルス信号のレベルがハイからローに変化すると、その立下りエッジのタイミングでエッジ検出部75がOFFトリガ信号を出力する。これにより、設定イネーブル信号生成部77は、設定イネーブル信号をローレベルにする。すると、コンデンサ26の充電が停止されると共に、セレクタ73及び74が何れもOFF側に切り替わり、その時点のコンデンサ26の端子電圧がコンパレータ27に出力される。

【0057】

30

つまり、抑制期間検出部72では、設定イネーブル信号がアクティブルレベルである期間において、入力されるパルス信号がハイレベルとなる期間、パルス幅に対応する期間でコンデンサ26が充電され、コンデンサ26の端子電圧に応じた長さの抑制期間が設定される。尚、図22では入力される設定信号を複数のパルス列で示しているが、設定信号としては単一のパルス信号で良い。また、設定信号は、例えば第1～第4実施形態のような設定信号送信部が送信しても良い。

【0058】

以上のように第6実施形態によれば、電源検出部76は、リングング抑制回路71に電源が投入されたことを検出するとONトリガ信号を出力し、エッジ検出部75は、抑制期間の長さをパルス幅で示す設定信号の立下りエッジを検出するとOFFトリガ信号を出力する。そして、設定イネーブル信号生成部77は、ONトリガ信号が入力されると設定イネーブル信号をハイレベルにし、OFFトリガ信号が入力されると同信号をローレベルにし、電流源24～コンデンサ26は、設定イネーブル信号がアクティブルである期間に入力される設定信号を、そのパルス幅に応じたレベルの電圧信号に変換する。したがって、抑制期間の設定を短時間で行うことができる。

【0059】

40

本発明は上記した、又は図面に記載した実施形態にのみ限定されるものではなく、以下のような変形又は拡張が可能である。

設定信号送信部により送信される設定信号は、その他、例えば抑制期間の長さを抵抗分圧による電圧レベルで示す形式などでも良い。

何れの構成要素もハードウェアのみならず、ソフトウェアで実現しても良い。

第3及び第4実施形態において、データ「1,0」の定義は逆でも良い。また、第4実施形態におけるデータ値に対応するデューティ比は、適宜変更して定義すれば良い。

抑制期間設定部を、タイマを用いて構成しても良い。

第6実施形態における抑制期間検出部72の構成は一例であり、設定信号のパルス幅に応じたレベルの電圧信号に変換する構成であれば、どのようなロジックであっても良い。

50

## 【 符号の説明 】

【 0 0 6 0 】

1 リンギング抑制回路、3 伝送線路、5 歪開始回路検出部、6 抑制期間制御部、9 抑制期間送信部、10 抑制期間検出部、11 抑制期間記憶部、15 N チャネル M O S F E T。

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

【図7】

【 义 6 】

| T1,T2,···Tn | SWr1 | SWr2 | ··· | SWrn | SWc1 | SWc2 | ··· | SWcn |

|-------------|------|------|-----|------|------|------|-----|------|

| 00···0      | OFF  | OFF  | ··· | OFF  | OFF  | OFF  | ··· | OFF  |

| 10···0      | ON   | OFF  | ··· | OFF  | ON   | OFF  | ··· | OFF  |

| ···         |      |      |     |      |      |      |     |      |

| 11···1      | ON   | ON   | ··· | ON   | ON   | ON   | ··· | ON   |

( 8 )

| T1,T2,···Tn+1 | SWr0 | SWr1 | ··· | SWrn | SWc0 | SWc1 | ··· | SWcn |

|---------------|------|------|-----|------|------|------|-----|------|

| 00···0        | ON   | OFF  | ··· | OFF  | ON   | OFF  | ··· | OFF  |

| 10···0        | OFF  | ON   | ··· | OFF  | OFF  | ON   | ··· | OFF  |

| ···           |      |      |     |      |      |      |     |      |

| 11···1        | OFF  | OFF  | ··· | ON   | OFF  | OFF  | ··· | ON   |

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 4 】

### 【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(72)発明者 岸上 友久

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 磯村 博文

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 阿部 弘

(56)参考文献 特開2012-244220(JP,A)

特開2009-253498(JP,A)

特開2011-244347(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 25/02

H03K 5/08

H03K 19/0175