(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-536287

(P2004-536287A)

(43) 公表日 平成16年12月2日(2004.12.2)

(51) Int.CI.<sup>7</sup>

**GO1R 27/26**

**HO1P 1/203**

**HO1P 1/205**

**HO1P 7/08**

F 1

GO1R 27/26

HO1P 1/203

HO1P 1/205

HO1P 7/08

T

B

テーマコード(参考)

2G028

5J006

審査請求 未請求 予備審査請求 有 (全 65 頁)

|               |                             |

|---------------|-----------------------------|

| (21) 出願番号     | 特願2002-582012(P2002-582012) |

| (86) (22) 出願日 | 平成14年4月2日(2002.4.2)         |

| (85) 翻訳文提出日   | 平成15年10月8日(2003.10.8)       |

| (86) 國際出願番号   | PCT/IB2002/001027           |

| (87) 國際公開番号   | W02002/084310               |

| (87) 國際公開日    | 平成14年10月24日(2002.10.24)     |

| (31) 優先権主張番号  | 60/283,093                  |

| (32) 優先日      | 平成13年4月11日(2001.4.11)       |

| (33) 優先権主張国   | 米国(US)                      |

| (31) 優先権主張番号  | 09/904,631                  |

| (32) 優先日      | 平成13年7月13日(2001.7.13)       |

| (33) 優先権主張国   | 米国(US)                      |

| (31) 優先権主張番号  | 09/912,753                  |

| (32) 優先日      | 平成13年7月24日(2001.7.24)       |

| (33) 優先権主張国   | 米国(US)                      |

|          |                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------|

| (71) 出願人 | 503370192<br>キヨウセラ ワイヤレス コーポレイション<br>アメリカ合衆国 カリフォルニア 921<br>21, サン デイエゴ, キャンパス<br>ポイント ドライブ 10300 |

| (74) 代理人 | 100078282<br>弁理士 山本 秀策                                                                            |

| (74) 代理人 | 100062409<br>弁理士 安村 高明                                                                            |

| (74) 代理人 | 100113413<br>弁理士 森下 夏樹                                                                            |

最終頁に続く

(54) 【発明の名称】低損失チューニング可能強誘電体デバイスおよび特性決定の方法

## (57) 【要約】

チューニング可能強誘電体コンポーネント(610～614)、および強誘電体コンポーネントの損失を測定するための狭帯域共振回路(610～620)が開示される。強誘電体コンポーネントは、共振回路に一体化されたキャパシタであり得る。この試験方法は、損失の他のソースを消去して、強誘電体材料に起因する損失を隔離し、かつこの損失が小さいことを実証する。本発明による方法は、強誘電体コンポーネントを備える回路を製造する工程と、強誘電体コンポーネントに起因する挿入損失および他の損失ソースに起因する他の損失を含む、組み合わされた損失を測定する工程と、他の損失ソースに起因する、挿入損失のコンポーネントを決定する工程と、測定された組み合わされた損失から、他の損失ソースに起因するコンポーネントを除去して、強誘電体コンポーネントと関連した損失を決定する工程とを包含する。

**【特許請求の範囲】****【請求項 1】**

強誘電体回路コンポーネントと関連した損失を決定する方法であって、

該強誘電体コンポーネントを備える回路を製造する工程と、

該強誘電体コンポーネントに起因する挿入損失および他の損失ソースに起因する他の損失

を含む、組み合わされた損失を測定する工程と、

他の損失ソースに起因する、該挿入損失のコンポーネントを決定する工程と、

該測定された組み合わされた損失から、他の損失ソースに起因する該コンポーネントを除

去して、該強誘電体コンポーネントと関連した該損失を決定する工程と

を包含する、方法。

10

**【請求項 2】**

前記強誘電体コンポーネントは、ギャップキャパシタである、請求項 1 に記載の方法。

**【請求項 3】**

前記回路は、前記ギャップキャパシタと一体化された共振器を含む一体化型の構造を備え

る、請求項 2 に記載の方法。

**【請求項 4】**

前記一体型構造は、ギャップによって分離された低損失基板上に配置される導電ストリッ

プと、該ギャップの下に強誘電体材料の薄膜とを備える、請求項 3 に記載の方法。

**【請求項 5】**

前記強誘電体コンポーネントは、インターデジタルキャパシタ、ギャップキャパシタおよ

びオーバーレイキャパシタを含む群より選択される、請求項 1 に記載の方法。

20

**【請求項 6】**

前記回路は、狭帯域共振回路である、請求項 1 に記載の方法。

**【請求項 7】**

前記組み合わされた損失は、ネットワークアナライザを用いて測定される、請求項 1 に記

載の方法。

**【請求項 8】**

他の損失ソースに起因する前記挿入損失の前記コンポーネントは、回路シミュレーション

ツールを用いて決定される、請求項 1 に記載の方法。

30

**【請求項 9】**

他の損失ソースに起因する前記挿入損失の前記コンポーネントは、電磁場シミュレーション

ツールを用いて決定される、請求項 1 に記載の方法。

**【請求項 10】**

前記強誘電体コンポーネントは、100よりも大きいQである、請求項 1 に記載の方法。

**【請求項 11】**

前記強誘電体コンポーネントは、200よりも大きいQである、請求項 1 に記載の方法。

**【請求項 12】**

前記強誘電体コンポーネントを一体化する狭帯域共振回路を製造する工程と、

ネットワークアナライザを用いて該回路の中心周波数および挿入損失を測定する工程と、

回路シミュレーションツールで該回路を解析して、該共振回路の導電性金属コンポーネン

トに起因し、かつ該強誘電体コンポーネントのジオメトリに起因する該挿入損失を決定す

る工程と、

40

該共振回路の導電性金属コンポーネントに起因し、かつ該強誘電体コンポーネントのジオ

メトリに起因する該挿入損失の該コンポーネントを、該測定された挿入損失から除去して

、該強誘電体コンポーネントに起因する該損失を決定する工程と

を包含する、請求項 1 に記載の方法。

**【請求項 13】**

前記狭帯域共振回路は、前記キャパシタを規定するためのギャップを有するマイクロスト

リップ共振器を備える、請求項 12 に記載の方法。

**【請求項 14】**

50

強誘電体膜に起因する損失を隔離する方法を用いて製造される、チューニング可能薄膜強誘電体デバイス。

【請求項 1 5】

前記デバイスは、強誘電体キャパシタおよび共振器を備える、請求項 1 4 に記載のチューニング可能デバイス。

【請求項 1 6】

前記デバイスは、一まとまりの素子、インターデジタルキャパシタに結合された平面の 2 次コムライン帯域通過フィルタを備える、請求項 1 4 に記載のチューニング可能デバイス。

【請求項 1 7】

前記デバイスは、一体型ギャップキャパシタを有するマイクロストリップ共振器を備える、請求項 1 4 に記載のチューニング可能デバイス。

【請求項 1 8】

チューニング可能強誘電体キャパシタは、

第 1 の導電表面と、

第 2 の導電表面とを備え、該第 1 および該第 2 の導電表面はキャパシタを備え、

該第 1 および該第 2 の導電表面に近接する強誘電体材料と、

該強誘電体材料の誘電率の変化に応答し、可変の電圧線に印加された電圧に応答して、該キャパシタのキャパシタンスを変化させるための該強誘電体材料に結合された可変電圧線とを備え、

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、0 . 25 GHz ~ 7 . 0 GHz の周波数範囲で、約 80 よりも大きい、チューニング可能強誘電体キャパシタ。

【請求項 1 9】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 8 GHz ~ 7 . 0 GHz の周波数範囲で、約 80 よりも大きい、請求項 1 8 に記載のチューニング可能強誘電体キャパシタ。

【請求項 2 0】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 25 GHz ~ 2 . 5 GHz の周波数範囲で、約 80 よりも大きい、請求項 1 8 に記載のチューニング可能強誘電体キャパシタ。

【請求項 2 1】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 8 GHz ~ 2 . 5 GHz の周波数範囲で、約 80 よりも大きい、請求項 1 8 に記載のチューニング可能強誘電体キャパシタ。

【請求項 2 2】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、0 . 25 GHz ~ 7 . 0 GHz の周波数範囲で、約 180 よりも大きい、請求項 1 8 に記載のチューニング可能強誘電体キャパシタ。

【請求項 2 3】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 8 GHz ~ 2 . 5 GHz の周波数範囲で、約 180 よりも大きい、請求項 1 8 に記載のチューニング可能強誘電体キャパシタ。

【請求項 2 4】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 3 pF ~ 3 . 0 pF の範囲のキャパシタンスに対して、約 80 よりも大きい、請求項 1 8 に記載のチューニング可能強誘電体キャパシタ。

【請求項 2 5】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 5 pF ~ 1 . 0 pF の範囲のキャパシタンスに対して、約 80 よりも大きい、請求項 1 8 に記載

10

20

30

40

50

のチューニング可能強誘電体キャパシタ。

【請求項 26】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、約 0 . 3 pF ~ 3 . 0 pF の範囲のキャパシタンスに対して、約 180 よりも大きい、請求項 18 に記載のチューニング可能強誘電体キャパシタ。

【請求項 27】

約 - 50 ~ 100 の範囲の温度で動作した場合、該キャパシタの Q は、0 . 5 pF ~ 1 . 0 pF の範囲のキャパシタンスに対して、約 180 よりも大きい、請求項 18 に記載のチューニング可能強誘電体キャパシタ。

【請求項 28】

前記キャパシタは、前記強誘電体材料に 0 電圧が印加された場合、約 0 . 8 ~ 1 . 5 pF のキャパシタンスを有する、請求項 18 に記載のキャパシタ。

【請求項 29】

前記強誘電体材料は、バリウムストロンチウムチタネートを含む、請求項 18 に記載のキャパシタ。

【請求項 30】

前記強誘電体材料は、約 1 ミクロンの厚さを有する膜を含む、請求項 18 に記載のキャパシタ。

【請求項 31】

前記キャパシタは、マイクロストリップギャップキャパシタである、請求項 18 に記載のキャパシタ。

【請求項 32】

前記第 1 の導電表面および前記第 2 の導電表面は、約 2 . 5 ミクロン幅のギャップによって分離される、請求項 31 に記載のキャパシタ。

【請求項 33】

前記コンダクタは、2 ~ 3 ミクロンの範囲の厚さを有する金属ストリップである、請求項 18 に記載のキャパシタ。

【請求項 34】

前記キャパシタは、オーバーレイキャパシタである、請求項 18 に記載のキャパシタ。

【請求項 35】

前記第 2 の導電表面は、金または銀を含む、請求項 18 に記載のキャパシタ。

【請求項 36】

第 1 の強誘電体キャパシタボンディングパッドから前記強誘電体キャパシタへの第 1 のテー<sup>40</sup>パーは、約 1 . 0 ミルの距離にわたって約 4 . 0 ミル幅から約 0 . 1 ミル幅への前記第 1 の導電表面の縮小を含み、

該強誘電体キャパシタから DC バイアスパッド領域への第 2 のテー<sup>40</sup>パーは、約 1 . 0 ミルの距離にわたって約 0 . 1 ミル幅から約 4 . 0 ミル幅への拡大を含む、請求項 18 に記載のキャパシタ。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願)

本出願は、米国特許仮出願第 60 / 283 , 093 号 (2001 年 4 月 11 日) の利益を主張し、この出願は、参考のため、本明細書中に援用される。さらに、本出願は、米国特許出願「 Tunable Ferro-electric Filter 」 (2001 年 7 月 13 日出願)、および米国特許出願「 Tunable Ferro-electric Multiplexer 」 (2001 年 7 月 24 日出願) に関し、これらの出願は、参考のため、本明細書中に援用される。

【0002】

(発明の分野)

10

30

40

50

本発明の分野は、強誘電体チューニング可能電子デバイスおよびコンポーネントである。

【背景技術】

【0003】

(発明の背景)

キャパシタンスの変更によって異なった電子応答が取得され得るので、可変キャパシタが有利である。しかしながら、可変またはチューニング可能キャパシタを搭載するために現在用いられている構造は、性能および実用上の重大な制限を有する。可動の平行プレートは、無線チューニングするために可変のキャパシタンスを提供する間、かさ高く、損失が大きく、雑音があり、通常、制限された範囲にわたってのみ動作するか、または、いくつもの制限を有する。「損失が大きい」コンポーネントまたはデバイスは、高い挿入損失(ILL)を有し、これは、負荷に送達された電力に対する、コンポーネントにおいて散逸された電力の比率である。電子バラクタは、印加された電圧に応答してキャパシタンスをチューニングする半導体デバイスである。バラクタは、通常、損失が大きく、かつ雑音があり、従って、通常、特に、200MHzより大きい、高周波数の用途に対しては有効でない。従って、バラクタは、特に符号分割多重接続(CDMA)が用いられている場合、無線アプリケーションでのフィルタおよびマルチブレクサ等の挿入損失臨界デバイスをチューニングするためには適切でない。可変キャパシタンスを提供する別のインプリメントは、微小電気機械システム(MENS)である。これは、付与された信号に応答して、異なるキャパシタを物理的に選択する小型のスイッチングデバイスである。しかしながら、MENSは、通常、コストがかかり、信頼できず、実質的な制御電圧を必要とし、事前に選択されたキャパシタンス値の個別のセットのみをイネーブルにする。10

20

【0004】

強誘電体材料は誘電率が可変であるので、チューニング可能キャパシタまたは他のチューニング可能コンポーネントを製造するための望ましい候補である。現在用いられている測定および特性決定技術の中で、チューニング可能強誘電体コンポーネントは、処理、ドーピング、または、その損失特性を改善するために用いられる他の技術に関係なく、一貫していて、実質的に損失が大きいという評価を得ている。従って、これらのコンポーネントは、一般に使用されていない。RFまたはマイクロ波領域において動作する強誘電体チューニング可能コンポーネントは、特に損失が大きいと考えられている。この所見は、例えば、最大チューニングが所望される場合に、高いRFまたはマイクロ波損失がバルク(厚さが約1.0mmよりも大きい)f-e材料のための従来の原則であるレーダー(RADAR)アプリケーションでの経験によって裏付けられる。一般に、損失を改善(低減)するための工程が採用されないならば、ほとんどのf-e材料は、損失が大きい。このような工程は、(1)事前または事後堆積アニーリング、あるいは、これらの両方でO<sub>2</sub>空孔を補償する工程、(2)バッファ層を用いて、表面応力を低減する工程、(3)他の材料を用いて合金にするか、またはバッファする工程、および(4)選択的ドーピング工程を含むが、これらに限定されない。30

【0005】

低電力コンポーネントを制限された範囲でチューニングすることへの需要が最近数年間に高まっているので、強誘電体材料への関心がバルク材料よりも薄膜を用いる方に向いている。しかしながら、高い強誘電体損失は、薄膜技術にも適用されることが仮定される。従来の広帯域測定技術は、バルクか薄膜かに関わらず、チューニング可能強誘電体コンポーネントが実質的損失を有するという仮定を強化してきた。40

【0006】

強誘電体キャパシタのキャパシタンス値の広帯域測定は、通常、LCメータ、インピーダンスアナライザまたはネットワークアナライザ等のデバイスを用いて取得される。電力測定から、キャパシタの損失(lossiness)が計算され得る。損失の逆数は、Q係数('Q')と呼ばれる。従って、損失が大きいデバイスは、低Qであり、より効率的なデバイスは高Qを有する。従来の測定技術を用いて取得された、1.8GHz~2.0GHzの周波数範囲で動作する、約0.5pF~1.0pFの範囲のキャパシタンスを有50

する強誘電体キャパシタのQ測定値は、通常、10～50の範囲であると言われている。これは、許容し得ないほど非効率的であり、従って、強誘電体チューニング可能コンポーネントは、一般的な使用には好ましくない。無線通信において、例えば、80よりも大きい、好適には180よりも大きい、およびより好適には350よりも大きいQが約2GHzの周波数が必要とされる。

#### 【0007】

後述されるように、従来の強誘電体コンポーネントは、不適切に製造、測定および特性決定されてきた。その結果、強誘電体チューニング可能コンポーネントは、L帯域における10～50の範囲のQに関して非常に損失が大きいことが一般的に推定される。他の周波数帯域で動作する強誘電体チューニング可能デバイスは、さらに、ほとんどのアプリケーションにとって許容し得ないQを有すると言わされてきた。10

#### 【発明の開示】

##### 【課題を解決するための手段】

#### 【0008】

##### (発明の要旨)

従来技術でのf-e膜の損失、またはその逆数のQを試験する方法には欠陥がある。従来技術の方法は、通常、広帯域試験法、および非一体型(non-integrated)コンポーネントを用いる。試験方法の損失メカニズムのすべて、およびデバイスアンダーテストは、通常、説明されない。これは、研究者が、f-e材料は損失が大きいと考えることにつながっている。20

#### 【0009】

本発明は、狭帯域試験法、およびコンポーネントの一体化を提供する。すべての損失メカニズムは、説明され、そして消去または最小化される。これにより、いくつかのf-e材料が事前に考えられたよりも損失の大きさがはるかに小さいことを示す、より正確な試験結果がもたらされる。

#### 【0010】

この試験法を用いて、f-e材料が首尾良く検査され得、損失とチューニング可能性と他のパラメータとの間の理想的なトレードオフが見出される。低損失チューニング可能f-eデバイスが製造され得る。低損失f-eチューニング可能キャパシタが製作され得る。このようなキャパシタは、チューニング可能性が所望される複数の用途において、構成単位として用いられ得るが、低損失要件が任意の他のチューニング可能デバイスの使用を妨げてきた。例示的用途は、無線通信デバイスにおける用途である。30

#### 【0011】

本発明の詳細は、その構造および動作の両方について、添付の図面を検討することによって部分的に細かく調べられ得る。図面において、同様の参照符号は同様の部分を示す。

##### 【発明を実施するための最良の形態】

#### 【0012】

本発明は、用いられる周波数範囲、および用いられるトポロジーのチューニング可能強誘電体コンポーネントの効率を正確に測定、特性を決定する狭帯域共振回路を利用する試験法を提供する。これらの試験法および回路は、チューニング可能強誘電体コンポーネントが、事前に考えられていたほど一様に損失が大きくではなく、かつチューニング可能強誘電体コンポーネントは、有利にも、無線ハンドセット等の低損失アプリケーションおよびデバイスにおいて用いられ得ることを証明する。損失の正確な決定により、チューニング可能強誘電体コンポーネントは、適切に最適化および設計され得る。特定の損失メカニズムは、同定および消去されるか、またはそうでない場合、低減および限度内にとどめられ得る。40

#### 【0013】

チューニング可能強誘電体コンポーネント、特に、薄膜を用いるチューニング可能強誘電体コンポーネントは、多様な周波数に機敏な(gigle)回路において用いられ得る。チューニング可能コンポーネントは、より小さいコンポーネントサイズおよび高さ、低い50

挿入損失、またはこの挿入損失に対する良好な拒絶、低コスト、ならびに1つ以上の周波数帯域にわたってチューニングする能力を提供し得るため望ましい。複数の帯域を覆い得るチューニング可能コンポーネントの能力は、複数の固定周波数コンポーネントが用いられた場合、必要な個別の帯域間で選択するために必要なスイッチ等の、必要なコンポーネントの数を潜在的に低減する。これらの有利な点は、特に、無線ハンドセットの設計において重要である。ここでは、向上した機能性と、より低いコストおよびサイズの必要性が矛盾した要件であると思われる。C D M A ハンドセットにおいて、例えば、個々のコンポーネントの性能に重点が置かれる。誘電体材料は、さらに、無線デバイスのアンテナインターフェースユニット( A I U )等の、これまで縮小を拒んでいた R F コンポーネントの一体化もまた可能にし得る。

10

## 【 0 0 1 4 】

例えば、A I U は、1つ以上のチューニング可能デュープレクサ(米国のデュアルバンド無線通信デバイスにおけるP C S およびセルラー)、ダイプレクサ、P A およびL N A を組み込み得る。これらのコンポーネントのいくつか、またはすべては、有利にも組み込まれ得、これらの全サイズまたはボリュームまたはこれらの両方が低減され、かつ電子性能が改善される。チューニング可能強誘電体コンポーネントのさらなる用途が、本明細書の後半部分において述べられる。

## 【 0 0 1 5 】

任意の誘電体材料の場合のように、強誘電体材料は、2つの主な損失メカニズム、導電率損失、および誘電体における格子振動による減衰を有する。2つの効果の組み合わせは、材料の損失正接(  $\tan(\theta)$  )と呼ばれる。R F またはマイクロ波回路において考えられる強誘電体材料については、格子振動による減衰が支配的であり、自由な電荷キャリアがない。しかしながら、 $\tan(\theta)$  を測定する任意の方法は、存在する場合、有限導電性の効果を含む。これは、2つのメカニズムの損失効果は、r f /マイクロ波特性に関する限り、区別がつかないためである。

20

## 【 0 0 1 6 】

R F 回路における主なコンポーネントは、キャパシタである。ここで、f - e キャパシタのf - e チューニング可能性について述べられる。キャパシタの全損失は、チューニング可能か否かに関わらず、散逸エネルギーに対する蓄積エネルギーの比率として表されるQ係数( Q )によって与えられ、ここで、エネルギーは電界において蓄積され、抵抗において散逸される。一まとめの素子キャパシタについては、無負荷Q( Q u )は

$$Q_u = X / R_s = 1 / (\omega * R_s * C) \quad (1)$$

30

によって与えられ、ここで、 $\omega$  = ラジアン周波数、R s = キャパシタの直列抵抗、およびC = キャパシタの電気容量である。R s は、測定され、かつ、C および  $\omega$  が周知であると仮定して、Q が計算され得る。直列抵抗は、コンダクタ、および誘電体における散逸損失の両方から生じる(すなわち  $\tan(\theta)$  )。

40

## 【 0 0 1 7 】

チューニング可能キャパシタが共振回路に組み込まれた場合、システムの全Q( Q t )は、ここで、

$$1 / Q_t = 1 / Q_c + 1 / Q_d + 1 / Q_r \quad (2)$$

40

によって与えられ、ここで、Q c はコンダクタQであり、Q d は誘電体Qであり、Q r は放射Qである。良好に設計された非放射システムについては、放射損失がない。従って、コンダクタ損失および誘電体損失が全損失を決定する。誘電体損失は、損失正接  $\tan(\theta)$  の効果であり、導電性損失が存在する場合、誘電体に起因する導電性損失を含む。従って、無負荷Qおよび全Qの両方について、 $\tan(\theta)$  の正確な測定は、チューニング可能デバイスが許容可能な損失特性で製造され得るか否かを判定する際に極めて重要である。

## 【 0 0 1 8 】

空胴共振器法は、材料の誘電率および損失正接を測定するために従来用いられてきた。これらの方針は、特に、セルラー電話が動作する低いマイクロ波周波数( ~ 2 G H z )の場

50

合、空腔のサイズが非常に大きいために困難である。薄い強誘電体膜に対する空腔共振器法の使用は、より大きい問題を引き起こす。なぜなら、1ミクロンの範囲の厚さを有する構造から空腔に導入された振動を測定することは非常に困難だからである。エラーが生じる可能性が高い。

#### 【0019】

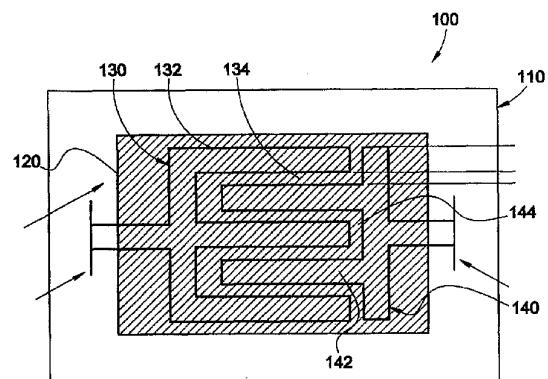

共振器法に問題があるために、インターデジタルキャパシタ（IDC）は、通常、強誘電体膜の質を測定するために用いられる。従来のマイクロストリップ構成における強誘電体インターデジタルキャパシタ（IDC）100が図1に示される。インターデジタルキャパシタ100は、ベース基板110、薄膜強誘電体層120、および第1のコンダクタ130および第2のコンダクタ140を備える。インターデジタルキャパシタは、通常、モノリシックマイクロ波集積回路（MMIC）等の用途、および0.1～6pFの小型のフットプリントおよびキャパシタが必要とされる用途において用いられる。インターデジタルキャパシタにおいて、キャパシタンスは、構造における導電性平行線またはフィンガー間に生成される。10

#### 【0020】

ベース基板110は、通常、例えば、マグネシウム酸化物（MgO）、サファイアまたは高純度のアルミニウム等の低損失材料を含む。基板は、その固有の低損失正接、および、さらなるバッファ層なしで、広範囲のf-e膜の直接的堆積を許容する能力に基づいて選択される。薄い強誘電体膜120は、ベース基板110に堆積される。強誘電体膜120は、通常、0.15～1.5ミクロンの範囲の厚さを有する。コンダクタ層は、その後、強誘電体膜120上に堆積される。接着層が必要とされることもある。導電層は、好適には、銅、金または銀等の金属材料である。これらの材料は、室温で比較的低損失であるために有利である。本明細書のために、室温は、ほとんどの市販のコンポーネントの通常の動作温度範囲を覆う-30～+85の範囲であると規定される。導電層は、通常、0.5～6.0ミクロンの範囲の厚さを有し、0.5～1.5ミクロンの範囲の厚さが最も一般的である。厚さの要件は、周波数に基づいて変化する表皮深さに基づいて変化する。20

#### 【0021】

薄膜（約1.5mm未満の $t_{f-e}$ ）f-e材料について記載されたが、薄膜f-e材料もまた用いられ得る。ここで、「厚膜」は、約1.5μmよりも大きく、約1.0mm未満の $t_{f-e}$ であると規定される。バルクは、約1.0mmよりも大きい。厚膜f-e材料の製造および用途は、薄膜f-e材料のものとかなり異なる。これは、上述の追加的厚さを生成するために、貼り付けまたはsol-gel技術、および、f-e材料を含む。追加の厚さ、および、特に、低減されたコストは、f-e性能がいくらか劣化されること、とりわけ、チューニング可能性が低減されるという代償を払って得られる。30

#### 【0022】

インターデジタルキャパシタ100は、その後、第1のコンダクタ130および第2のコンダクタ140を形成するためにエッチバックまたはリフトバック（lift-back）技術を用いて製造される。第1のコンダクタ130は、フィンガー132および空間134を有し、これらは、第2のコンダクタ140のフィンガー142および空間144に隣接する。コンダクタは、第1のコンダクタ130のフィンガー132が第2のコンダクタ140の空間144に位置し、かつ、第2のコンダクタ140のフィンガー142が第1のコンダクタ130の空間134に位置するように構成される。これまで、f-e膜を製造し、特徴を決定するほとんどの研究者および他の個人経営者は、通常、フィンガーの幅が1～5ミクロン、およびフィンガー間のギャップまたは空間が通常1～5ミクロン幅のIDCを設計してきた。40

#### 【0023】

キャパシタンスは、主に、フィンガー132と142との間に生成される。高レベルのキャパシタンスを生成するために、小さいギャップサイズ(<5ミクロン)および長いフィンガーが必要とされる。強誘電体チューニングキャパシタとして用いられる場合、小さいギャップサイズでも、フィンガー間に大きいチューニングフィールドを生成することを支50

援する。これは、重大な意味がある。なぜなら、多くのチューニングフィールドがキャパシタ100の上の空気領域において失われるからである。

#### 【0024】

この構成における最大損失コンポーネントは、フィンガー領域において生成された奇数モードである。平行線間の結合は、偶数モードおよび奇数モードによって表され得る。偶数モードは、2つの線が同相（通常ゼロとされる）で励起される場合に生じ、奇数モードは、線が、位相から180度ずれて励起される場合に生じる。マイクロストリップ回路において、偶数および奇数モードが伝播する速度は異なる。さらに、薄い導電層（1.5ミクロン未満）、狭いフィンガー幅およびギャップ間隔（どちらか、または両方が5ミクロン未満）、および鋭いコーナーが用いられた場合、損失はさらに大きくなる。

10

#### 【0025】

薄い強誘電体膜損失をインターデジタルキャパシタを介して測定するための標準的手順が後述される。上述のように、約0.5ミクロンの強誘電体膜がマグネシウム酸化物等の低損失基板に堆積される。その後、可能な限り小さいサイズのインターデジタルキャパシタの製造を可能にするために、1ミクロン以下の厚さを有する導電層が堆積される。フィンガー幅およびギャップ間隔の両方は、通常、1~5μmの範囲である。鋭いコーナーを有する幅が狭く長いフィンガーを形成するために、エッチバックまたはリフトバック技術が用いられる。生じたインターデジタルキャパシタは、LRCメータ、またはインピーダンス、またはキャパシタと接触するプロープチップを有するネットワークアナライザ等の広帯域測定ツールを用いて特性決定される。

20

#### 【0026】

この手順を用いて、通常、0.2~1.5pFの範囲のキャパシタが取得され、約500MHz~約2GHzのいずれかの動作周波数で、10~100の範囲のQが測定される。この損失は、通常、完全に強誘電体膜に起因する。これらのQ値は、非常に低いと考えられ、従って、強誘電体チューニング可能コンポーネントは、一般的に、多くの使用に対し高損失であり、許容され得ないとみなされる。無線通信において、例えば、100よりも大きく、好適には、250よりも大きいQは、1.0pF近辺のf-eキャパシタンスの場合に2GHzの範囲の周波数であることが必要である。しかしながら、後述されるように、従来の製造および損失測定技術は、強誘電体膜に起因する実損失について信頼できる表示をもたらさない。

30

#### 【0027】

式(1)に示されるように、キャパシタ損失（チューニング可能か否かに関わらず）は、無線周波数( $f > \text{約} 500 \text{ MHz}$ )の場合の直列損失 $R_s$ に比例し、ここで、キャパシタンスをシャントする大きい並列抵抗の効果が無視され得る。キャパシタは、直列損失のソースが何であるかには拘らず、ソースがあることのみに拘る。例えば、2GHzの場合に許容可能な低さの損失( $Q_u = 250$ )を有する1pFの強誘電体チューニング可能キャパシタについては、直列損失は、わずか0.32オームでなければならない。直列損失は、キャパシタの使用から生じるすべてのソースからの全損失を含む。直列損失のソースを最小化または消去するために、存在する各損失メカニズムを最初に説明しなければならない。これは、特に、強誘電体膜に起因する損失のより正確な決定を可能にする。

40

#### 【0028】

$f-e$ デバイスについて、全損失は、各ソース寄与率の総和によって以下のように決定される。

#### 【0029】

$L_t = L_{geom} + L_{attatch} + L_{metall} + L_{sub} + L_{rad} + L_{meas} + L_{f-e}$ であり、ここで、

$L_{geom}$ は、キャパシタのトポロジーから導き出され、

$L_{attatch}$ は、デバイスの取り付けに起因する損失であり、

$L_{metall}$ は、全金属損失であり、

$L_{sub}$ は、ベース基板損失（存在する場合）、

50

$L_{rad}$  は、放射損失（所望されるものおよび所望されないものの両方）であり、

$L_{meas}$  は、測定誤差から生じる全損失であり、

$L_{f-e}$  は、 $f-e$  損失正接である。

### 【0030】

この損失配分は、 $f-e$  キャパシタが用いられる様で、所望の動作周波数の  $L_{f-e}$ （または  $f-e \tan \theta$ ）の正確な値を取得するために最初に用いられ得る。 $L_{f-e}$  を正確に導き出すために、上述の他の損失寄与ソースのすべてを消去または制限しなければならない。例えば、 $L_{gap\_m}$  は、トポロジーによって異なり、オーバーレイキャパシタの場合は最良であり、ギャップキャパシタの場合は不良であり、IDCキャパシタの場合は極めて不良である。この損失は、低減および制御され得るが、これは、デバイスに固有である。従って、所与の  $f-e$  キャパシタのトポロジーの選択は、 $f-e$  キャパシタによって達成可能な考えられ得る最良の  $Q_c$  に影響を及ぼす。電磁（EM）ソフトウェアは、 $f-e$  膜が損失を有さないと仮定して、所望のジオメトリのベース線損失を確立し得る。このベース線損失は、所与のジオメトリの最良（最低）の損失を表す。

10

### 【0031】

一般に、ギャップキャパシタは、最も容易に製造され得る。IDCは、次に容易であり、オーバーレイキャパシタは、これらの3つの中で最も困難である。IDCと比較して、ギャップキャパシタは、より良好な  $Q$  を有するが、単位断面あたりのキャパシタンスが低い（図1aにおける  $W$ ）。IDCのキャパシタンスは、単位断面あたりに用いられるフィンガーハイの数が多いため、より大きい。しかしながら、複数の通信フィルタアプリケーションの場合、大きいキャパシタンス（ $C = 4.0 \text{ pF}$ ）は必要とされない。従って、ギャップキャパシタは、多くの場合、適切なキャパシタンスを提供し得る。ほとんどの  $f-e$  膜に関して、この固有に高い  $K$  の値は、従来のギャップキャパシタと比較して、単位断面  $W$  あたり比較的高いキャパシタンスを提供することを支援する。

20

### 【0032】

$L_{attach}$  は、例えば、はんだ、銀ペイント、またはワイヤボンディングを含む、個別のデバイス取り付け技術から生じる。これらの取り付け損失は、大きく、かつ予測不可能であり得る。最低損失は、 $f-e$  キャパシタを共振器または他のRF回路に直接的に製造することによって達成され、従って、この損失コンポーネントが除去されない場合は、最小化される。

30

### 【0033】

スタンダードアロン  $f-e$  キャパシタの固有損失は、あまり重要でない。はるかに重要なのは、 $f-e$  キャパシタを回路に取り付けることから生じる任意の追加的損失である。 $f-e$  キャパシタが損失を有しない場合であっても、大きい損失接続が用いられた場合、全体の効果は、損失が大きい  $f-e$  デバイスの効果である。例えば、250GHzでの  $Q = 250$  が  $1.0 \text{ pF}$  のキャパシタンスに対して所望された場合、直列抵抗  $R_s$  全体は、 $0.32 \Omega$  でなければならない。従って、任意の追加的損失は、このキャパシタの  $Q$  をさらに低減する。この追加的損失が実際のキャパシタの外部であることは関係がない。マウントに起因するもの等、やむを得ない損失メカニズムであっても、例えば、システムへの効果という点からキャパシタの有効  $Q$  を低減する。

40

### 【0034】

最小の追加的損失について、 $f-e$  キャパシタと共振器との間の接続は、最低の追加的抵抗を提供する。従って、 $f-e$  キャパシタと関連する電流および電荷は、最小の追加的損失を見出す。はんだ、ワイヤボンディングまたは銀ペイントまたは貼り付け（しかしながら、これらに限定されない）従来のボンディングまたはマウント技術は、このような低損失の制御可能なボンディング（bond）を提供しない。

### 【0035】

このようなボンディング法の使用から生じる追加的な、予測不可能な損失は、 $f-e$  キャパシタが共振器をチューニングする目的で用いられるか、 $f-e$  膜の特性決定の目的で用いられるかに関わらず、実現された  $Q$  を劣化する。従って、最良の性能（最低の損失）の

50

ために、 $f - e$  キャパシタ構造は、チューニングすることが意図された共振器上、または他の重要なRF回路上に直接的に製造されるべきである。直接的に製造することによってのみ、電磁(EM)ソース(電流)の $f - e$  チューニング素子から共振器への最小損失接合部がもたらされ得る。 $f - e$  キャパシタの、共振器上への、または共振器との直接的な製造の所望の効果は、鋭いコーナーまたは接合部の不在によって強化され得る。

#### 【0036】

$L_{meta1}$  の係数は、金属の表面粗さ(SR)、表皮厚さ  $s$  と比較した金属厚さ、および導電率を含む。 $L$  および  $S$  帯域(1 ~ 4 GHz)の動作周波数において、SRが約10マイクロインチ平方二乗平均(rms)よりも小さい場合、SRは、係数として有効に消去され得る。厚さが 1.5  $s$  以上である場合、金属厚さは、係数として低減され得るか、または、厚さが > 5  $s$  である場合、有効に消去される。電極接点については、金属厚さ( $t_m$ )は、約 1.5  $s$  であり得る。進行波または定在波が支援されなければならず、すなわち、波長が検出可能なフラクション(約 10% 以上)において当該の金属が伸長する電磁共振器の場合については、約 5  $s$  以上の金属厚さにより近くなる。

10

#### 【0037】

導電率は、金、銅および銀(Au、Cu および Ag それぞれ)の場合に最良である。従って、 $L_{meta1}$  は、低減および制御され得るが、係数として消去され得ない。しかしながら、その効果は、当業者に周知の式によって、または、Eagleware または Touchstone といった一般的に用いられる回路シミュレータにおいて利用可能な線計算ツールを用いることによって計算され得る。さらに、正確な製造の制御が  $L_{meta1}$  のジオメトリの変更を限度内にとどめ得る。

20

#### 【0038】

$L_{sub}$  によって表される損失寄与率が、対象となる動作周波数で 0.001 未満、好適には、0.005 未満の損失正接を有する低損失基板を選択することによって最小化され得る。適切な材料は、> 99% の純アルミナを含み、損失 / コスト利益の関して、現在の最良の選択である。サファイアまたは MgO は、低損失正接を有するという点でアルミナよりも良好であるが、より高価である。すべてのこれらの材料は、バッファ層を用いることなく  $f - e$  薄膜を許容し得、かつ、さらなる研磨を少しだけ用いるか、または用いずに許容可能である表面粗さを有する。半導体基板は、導電率が比較的高いため、好ましい選択ではない。損失正接の係数、表面粗さおよび価格に加えて、適切な基板は脆性であるべきでなく、より大口径のウェハとして製造され得、かつ広範囲の事前処理を行うことなく容易にメタライゼーションされ得る。

30

#### 【0039】

合成基板( $f - e$  膜と基板)の全損失から  $L_{sub}$  を分離することは、EM場または回路シミュレーションソフトウェアを用いることによって達成され得る。例えば、Sonnet、Momentum または IESD が用いられ得る。従って、 $L_{sub}$  は、著しく低減され、かつ正確に計算され得る。

40

#### 【0040】

$L_{rad}$  は、適切な遮蔽および設計によって消去され得、従って、通常、係数ではない。多様なフィルタ、特に、コムラインまたはヘアピン等の平面フィルタは、放射カップリングに依存して所望の性能を達成することが留意されたい。これらの場合、不用な浮遊カップリングが除去されないとても低減される。

#### 【0041】

$L_{meas}$  は、回路損失誤差を著しく増加させ得る。なぜなら、わずかな追加的損失が、デバイスアンダーテスト(DUT)の測定されたQを低減するか、または、システムが、DUTの固有のQを不明瞭にするからである。材料における誘電率および損失正接を測定する従来の方法は、当業者に周知の空洞共振器摂動技術である。しかしながら、 $L$  帯域では、キャビティのサイズがかなり大きくなる。 $f - e$  膜等の薄膜が(バルクに対して) 1.5  $\mu m$  未満の膜厚の特徴を示す場合、測定誤差が大きくなり得ると、問題は非常に難しくなる。さらに、 $f - e$  キャパシタ(またはフィルタ)は、それが用いられる態様と最も

50

類似の態様で特性決定される。従って、 $f - e$  化合物または膜の特性決定する好適な方法は、マイクロストリップ共振器技術による方法である。

#### 【0042】

共振回路を測定するために、ネットワークアナライザが好適な選択肢である。測定損失を最小化し、最も正確な測定を達成するために、DUTの損失が較正され、ネットワークアナライザの全2ポート較正(full two port calibration)を実行し、較正および測定の平均化が用いられる。

#### 【0043】

デバイス取り付け、基板、放射、および測定誤差損失コンポーネントの最小化または消去によって、全損失は、

$$L_{\text{tot}} = L_{\text{geom}} + L_{\text{metal}} + L_{f-e} + L_{\text{miss}} \quad (4)$$

になる。

#### 【0044】

$L_{\text{tot}}$  は、所与の強誘電体キャパシタジオメトリーの全損失であり、 $L_{\text{geom}}$  および  $L_{\text{metal}}$  は、そのジオメトリの不可欠な部分 (integral parts) である。これらの存在は、特定のデバイスの実損失を決定するために適切であるが、これらは、単に強誘電体材料に起因する損失を決定するために量子化および除去され得る。 $L_{\text{geom}}$  は、強誘電体材料が損失を有さないと仮定して、回路の正確な電磁的シミュレーションから決定され得、 $L_{\text{metal}}$  は、導電表面粗度（適切である場合）および表皮深さを仮定する、金属損失の式を用いて決定され得る。 $L_{\text{miss}}$  は、他の損失メカニズムの不完全な除去と  $L_{\text{geom}} + L_{\text{metal}}$  の有限境界との組み合わせを表す。

#### 【0045】

(a) すべての損失メカニズムを説明する工程、および (b) これらの損失を消去および限度内にとどめる工程の2工程プロセスは、強誘電体損失の正確な決定を可能にするだけでなく、低損失チューニング可能コンポーネントの正確な設計ガイドラインを確立することを支援する。 $L_{f-e}$  を正確に知ることにより、検討中の膜が提示される用途に用いられ得るか否かを最初に決定することが可能である。 $L_{f-e}$  を正確に知ることにより、さらに、強誘電体膜を用いる任意のタイプの最適設計のために必要なベース線が提供される。この知識は、損失正接がチューニング可能性と有効にトレードオフされる場合に必要である。簡単に言えば、正確な製造および測定技術は、一貫した強誘電体膜の損失特性をもたらす。

#### 【0046】

この損失解析に基づいて、低損失チューニング可能強誘電体コンポーネント、特に、チューニング可能強誘電体キャパシタが、多様なアプリケーションで設計、試験および実現され得る。(1) ギャップキャパシタ、(2) オーバーレイキャパシタ、および(3) インターデジタルキャパシタという3つの一般的なタイプのキャパシタに関する損失解析に基づいた設計手順およびインプリメンテーションが後述される。

#### 【0047】

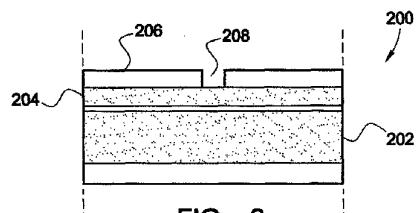

強誘電体チューニング可能ギャップキャパシタ200は、図2に示される。ギャップキャパシタ200は、基板層202、強誘電体層204、およびキャパシタンス誘導ギャップ208を規定する金属層206を備える。以下の設計のインプリメンテーションは、他のソースからの損失を最小化し、強誘電体幕204に起因する損失の正確な決定を可能にする。これは無線ハンドセットのL帯域(1~2GHz)における動作周波数を仮定するが、同じ方法が他の帯域で適用され得る。

#### 【0048】

1インプリメンテーションにおいて、基板202は、20~40ミルの範囲の厚さを有する、99.5%の純度のアルミナの層である。表面粗度は、約5μインチ rms 以下である。強誘電体層204は、0.15~2.0ミクロンの範囲の厚さを有するバリウムストロンチウムチタネート、 $Ba_x Sr_{1-x} TiO_3$  (BSTO) の膜である。1.0μmより大きい膜厚さの使用は、キャパシタンスおよびチューニング範囲を最大化する。

10

20

30

40

50

## 【 0 0 4 9 】

Ba/Sr フラクションの調整、ドーピングまたはアニーリングは、好適には、最低  $t_{an}$  を提供する一方で、必要とされるチューニング範囲を提供するように選択される。1 実施形態において、室温の動作の場合、 $x = 0.5$  ( $Ba_x Sr_{1-x} TiO_3$ ) である。これに代わる強誘電体材料もまた用いられ得る。金属層 206 は、約  $2.5 \mu m$  の厚さであり、これは、この金属層を電極アプリケーションのために適切にする。ギャップ 208 は、30 ~ 80 ミルの幅であり、エッジは、損失を最大限に低減するために丸くされる。ギャップ 208 によって示されるキャパシタンスは、0 電圧 DC バイアスで  $0.6 pF$  ~  $1.5 pF$  の範囲である。

## 【 0 0 5 0 】

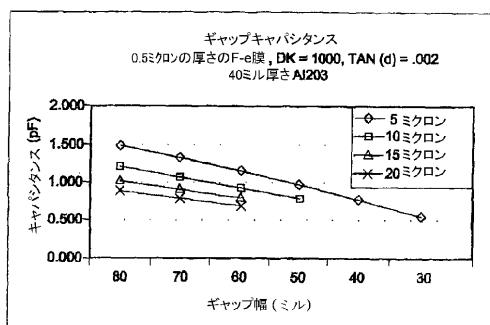

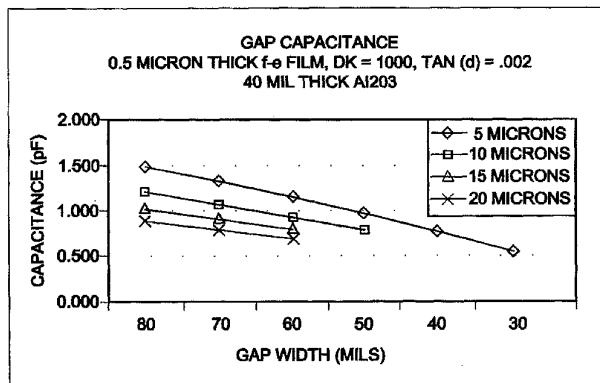

EM シミュレーションは、2 GHz で約  $1 pF$  のキャパシタンスの場合、ギャップキャパシタは、損失正接を  $0.002$  と仮定すると、700 より大きい Q を有し、損失正接を  $0.05$  と仮定すると、300 より大きい Q を有することを示す。図 3 は、ギャップ幅と強誘電体層厚さとキャパシタンスとの間の関係を示すテーブルである。このデータは、ギャップキャパシタ試験回路のターゲット設計のために非常に有用である。図 3 における結果は、0 V DC バイアスで 1000 の誘電率を有する  $0.5 \mu m$  の厚さの強誘電体膜、99.5 % の純度のアルミナの 40 ミル厚さの基板層、および f - e 膜の  $0.002$  の損失正接を想定する。

## 【 0 0 5 1 】

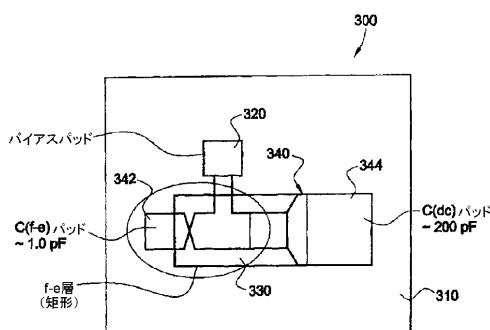

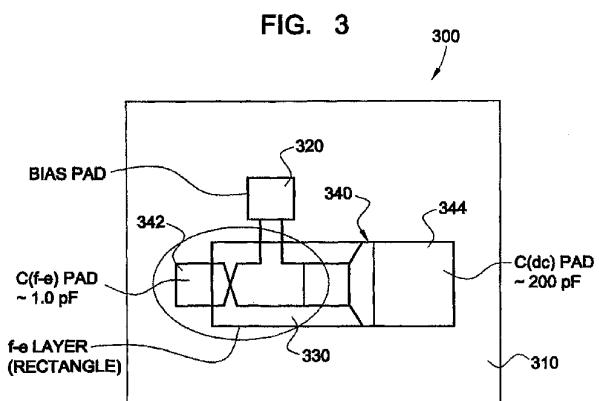

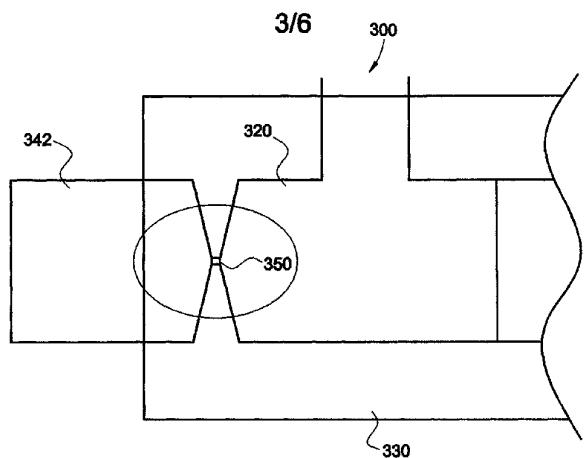

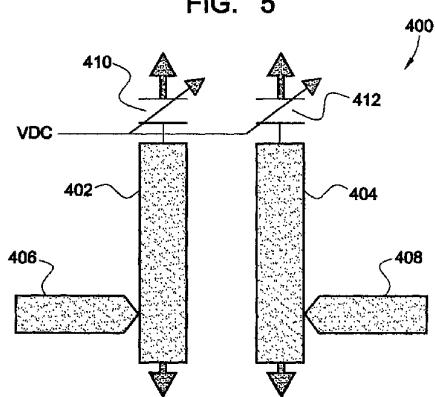

本発明による強誘電体オーバーレイキャパシタ 300 は、図 4 に示される。キャパシタ 300 は、基板 310、バイアスパッド層 320、強誘電体層 330 およびキャパシタパッド層 340 を備える。バイアスパッド層 320 は、DC バイアスパッドを規定し、キャパシタパッド 340 は、キャパシタパッド 342 および DC ブロックキャパシタパッド 344 を規定する。

## 【 0 0 5 2 】

1 インプリメンテーションにおいて、ベース基板 310 は、20 ~ 40 ミルの範囲の厚さを有するアルミナである。バイアスパッド層 320 は、約  $100 nm$  の厚さを有するプラチナの層によって被覆された約  $2.0 \mu m$  の厚さを有する銀のベース電極層を備える。プラチナ層は、強誘電体層が成長する間、銀の層が酸化することを防ぐ。層 320 には、DC バイアスを提供するために  $0.5 \sim 1.0 M$  の範囲の抵抗を接続するためのパッドが埋め込まれている。必要に応じて、より良好な接着を提供するために、薄い ( $10 nm$ ) クロム層がアルミナと銀との間に挿入され得る。強誘電体層 330 は、約  $1 \mu m$  の厚さを有する BSTO の薄膜である。キャパシタパッド 342 は、 $8.0 \times 4.0 \mu m^2$  の最小面積を有し、かつ約  $4.0 \times 4.0 \mu m^2$  の面積を有する金または銀の電極が上に載せられる。DC ブロックキャパシタは、少なくとも  $150 \sim 200 pF$  のキャパシタンス、および約  $100 \times 100 \mu m^2$  の面積を有する。接触パッド 344 の総面積は、最小で  $7.0 \times 8.0 \mu m^2$  である。

## 【 0 0 5 3 】

オーバーレイキャパシタは、 $0.8 \sim 1.5 pF$  の範囲の最小キャパシタンスを有する。キャパシタ 300 の一部分の拡大である図 5 に見出され得るように、キャパシタ 300 の重なった領域は非常に小さい。1 インプリメンテーションにおいて、重なった領域 350 は、 $0.3 \mu m \times 0.3 \mu m$  のサイズを有する。これは、0 ボルト DC で約 1000 の BSTO 誘電率、および約  $1.0 \mu m$  の膜厚さに基づく。パッド 342 および 320 は、キャパシタオーバーレイ領域 350 に向かって、およびこの領域からテーパーになる。テーパーは、 $1.0 \mu m$  の距離で  $4.0 \mu m$  から約  $0.25 \mu m$  になっている。

## 【 0 0 5 4 】

キャパシタ 300 の損失ターゲットは、 $1.0 pF$  の場合に 2.0 GHz で少なくとも 350 の Q である。必要に応じて、強誘電体膜 330 は、ドーピング、アニーリング、またはバッファ層（単数または複数）の使用を介してさらに最適化され得る。最後に、キャパシタンスの変化は、 $0 \sim 2.5$  ボルトのバイアス電圧の変化に対して、好適には 2 : 1 (

10

20

30

40

50

50%以上である。

#### 【0055】

本発明の1局面は、上述のキャパシタ構造が1例である、チューニング可能強誘電体コンポーネントの最適構造および設計基準である。本発明の別の局面は、チューニング可能強誘電体コンポーネントにおける損失を正確に特性決定するための測定方法および装置である。これら的方法は、共振器および狭帯域共振回路の使用を含む。狭帯域測定は適切である。なぜなら、測定されているデバイスは、狭帯域の周波数で動作するように設計されるからである。狭帯域(共振)測定は、さらに、好適である。なぜなら、狭帯域測定は、小さい損失の測定を容易にする効果を当然強化し、かつ測定をより正確にするからである。前の方は、狭帯域デバイスにとって不適切および不正確である広帯域測定を含んでいた。これらの試験共振回路の本発明の2つのインプリメンテーション、すなわち、2次狭帯域通過フィルタ、およびマイクロストリップ共振器回路(半波長または1/4波長)が記載される。10

#### 【0056】

図6は、2つの強誘電体キャパシタ410および412を試験するように構成された共振狭帯域試験回路400を示す。これは2次平面コムラインフィルタである。キャパシタ410および412は、図1および図2に関して記載されたように構成され、損失コンポーネントを最小化するように実現される。試験回路400は、平面2次コムライン帯域通過フィルタを備え、強誘電体キャパシタ410および412とそれぞれ直列に結合された2つの共振器402および404を含む。DCバイアス電圧は、キャパシタ410および412に印加される。キャパシタ410および412は、一まとまりの素子としてか、または基板上に直接プリントすることによって試験するために製造および搭載され得る。DCブロックキャパシタ(約180pFと等しいキャパシタンス)は、図示されない。集中構成において、キャパシタは、はんだ付けされるか、銀ペイントまたはペーストを用いて取り付けられる。これは、多様なデバイスの使用を可能にするが、この搭載方法に起因する大きく、かつ予測不可能な損失がある。プリントは、はんだ付けまたはボンディングが必要とされず、かつ直接的に製造するために低損失であるという点で有利である。しかしながら、用いられ得る基板のタイプは、強誘電体膜が存在するために制限され得る。DCブロックキャパシタは図示されない。20

#### 【0057】

応答は、ネットワークアナライザに接続された入力および出力線406および408を通じて測定される。共振器の中心周波数 $f_0$ の測定は、実キャパシタ値(上記の式(1)を参照)の決定を可能にし、 $f_0$ での挿入損失は、キャパシタQを決定する。これらの測定値が取得された後、回路シミュレーションは、キャパシタンスおよびQ値を取得するために用いられ得、結果が比較され得る。30

#### 【0058】

本発明の試験法を用いて取得された試験結果と従来の試験法との劇的な差異を示すために、図7が参照される。図7におけるテーブルは、Kyocera Wireless Corporation(KWC)(本発明の譲受人)との契約の下でNaval Research Laboratory(NRL)、Washington DCにおいて製造された強誘電体インターデジタルキャパシタサンプルから取得された測定データを提供する。NRLにおいて従来の試験法(この場合、HP4291BインピーダンスアナライザおよびCascade Techマイクロ波プローブ)を用いて、インターデジタルキャパシタサンプルから得られたキャパシタンスおよびQ測定値は、KWCにおいて上述の新しい試験法を用いて、同じサンプルから得られた測定値と比較される。40

#### 【0059】

この実験の目的で、インターデジタルキャパシタは、0.5~1.2pFの範囲のキャパシタンス、約5.0ミクロンのギャップ間隔、少なくとも150ミクロンのフィンガー幅、約0.5ミクロンの強誘電体膜厚さ、1.5~2.5ミクロンの範囲の金属厚さ、および100ミクロン以下のフィンガー長さを有するように製造された。50

## 【0060】

KWC試験回路は、回路400と同様の態様で構成される。これは、約1800MHzで共振するように構成された2次平面チェビシェフ型帯域通過フィルタ(planar Chebychev bandpass filter)である。インターデジタルキャパシタサンプル、一まとまりの素子キャパシタは、銀ペイントを用いて搭載および取り付けられた「フリップチップ」であった。バイアスは、通常C1 C2であるという事実を補正するように印加され、ここで、C1およびC2は、フィルタの動作を補正するために必要とされる2つのコムライン帯域通過フィルタ負荷キャパシタである。C1がC2と等しいことが意図されるが、実際、C1 = C2は、めったに達成されない。より一般的なC1 C2の状態は、補正されない場合、帯域通過挿入損失を著しく増加させる(Q決定に関する限り)。

## 【0061】

0.6~0.8pFの範囲の高いQATCおよびAVXチップキャパシタは、ベース線帯域通過挿入損失を確立するために用いられた。これらのチップキャパシタのQは、試験周波数では600~800の範囲であった。実キャパシタンス、およびインターデジタルキャパシタのQを決定して、測定データと同じ共振周波数および帯域通過挿入損失を与えるためにEagleware回路シミュレータが用いられた。

## 【0062】

図7におけるデータは、実質的に最悪の場合のQデータである。なぜなら、すべての可能な損失コンポーネントを除去(較正)するための試みがなされなかつたためである。このような1つの損失コンポーネントは、線およびインターデジタルキャパシタごとに異なるボンディング(取り付け)損失を含む。別のものは、生じた共振器長さの不整合、キャパシタの位置の下のマイクロストリップギャップオーブンエンド効果、および基本的インターデジタルキャパシタジオメトリから生じる損失である。これは、従来の方法と本発明を用いて取得されたQ値の差異がなおさら著しい場合である。例えば、アルミナまたはMgO基板を用いるギャップキャパシタの直接的製造等のエラーソースのさらなる低減または消去のみがQデータを改善する。

## 【0063】

2次帯域通過フィルタの狭帯域共振試験回路としての使用は、いくつかの有利な点を有する。キャパシタデータは、動作周波数で抽出され得る。トポロジーは、単純、再現可能、および容易に製造される。測定値は、単純であり、測定値を得ることによって追加的エラーがほとんど存在しない。結果は、シミュレートされた結果と容易に比較され得る。留意されるべきいくつかの不利な点もある。上述のキャパシタンス値の差異の可能性は、増加した損失として測定データに表れ得る。しかしながら、バイアス電圧の1つをわずかに調整すると、この相違が補償され得る。さらに、浮遊キャパシタンスおよび結合は、取得されたF<sub>0</sub>およびQ値に影響を及ぼし得る。これらの効果は、さらに、EM場シミュレータを介して説明され得る。f-eキャパシタの不当な搭載は、2つの共振器の電気的長さのわずかな差異をもたらし、これはI.Lに直接的に追加される。f-eキャップの位置合わせ不良は、さらに、それ自体が低Qとして表れる追加的損失をもたらす。

## 【0064】

2次狭帯域共振試験回路450の別の実施形態は、図8に示される。試験回路450は、同軸共振チューニング可能フィルタの形態をとるが、モノブロック、ストリップ線またはマイクロストリップ等の他の共振器が用いられ得る。再び、強誘電体キャパシタ452および454は、一まとまりにされるかプリント化され得る。試験回路450は、さらに、同軸4分の1波長共振器462および464を備える。非強誘電体キャパシタ470(C2)は、共振器462と464との間に結合され、非強誘電体キャパシタ472と474(C1)との間は共振器の外側で結合される。この基本構造は、従来の固定的チューニング第2次上部容量性結合(fix-tuned 2nd order top capacitive coupled)BPFである。

## 【0065】

10

20

30

40

50

回路 450 を用いる測定技術は、以下の通りである。BPF 性能は、最初、所定の位置で  $f_e$  キャパシタなしで測定され、その後、 $f_e$  キャパシタを用いて測定される。第 1 の実施例において、共振器中心周波数  $f_{01}$ 、およびフィルタの挿入損失  $IL_1$  が、最初、強誘電体キャパシタなしで測定される。第 2 の実施例において、共振器中心周波数  $f_{02}$ 、およびフィルタの挿入損失  $IL_2$  が、強誘電体キャパシタ 452 および 454 を用いて測定される。明らかに、共振器 442 および 444 が同じ長さである限り、 $f_{01}$  は常に  $f_{02}$  よりも大きく、 $IL_2$  は、常に  $IL_1$  よりも大きい。キャパシタンス  $C_{fe}$  は、 $f_{01} \sim f_{02}$  から決定され得、 $Q(C_{fe})$  は、シミュレーションと高い精度で比較することによって  $IL_1 \sim IL_2$  から決定され得る。 $f_e$  キャパシタは、もとの回路に追加される必要がない。むしろ、基本の上部容量性結合 (basic top capacitivity coupled) BPF は、 $f_e$  キャパシタを用いて製造され得ず、第 2 の BPF は、直接的に  $f_e$  キャパシタを用いて製造される。これは、最小の追加的損失チューニング可能試験回路をもたらす。なぜなら、これは  $f_e$  キャパシタの回路との直接的な製造を可能にするからである。

10

#### 【0066】

代替的試験回路は、 $f_e$  キャパシタと共に用いられる場合、物理的により短い共振器 442 および 444 の使用を含む。これは、BPF を非  $f_e$  BPF と同じ共振周波数で、またはこれに近い共振周波数で共振させる。同じ  $f_e$  キャパシタ Q 抽出法が用いられる。

20

#### 【0067】

2 次試験回路 450 は、2 次試験回路 400 と比べていくつもの有利な点を有する。回路 400 および回路 450 の両方は、固有の狭帯域構造であるが、同軸共振器 462 および 464 は、非常に高い Q を有し得、その結果、非常に低い挿入損失をもたらす。固有の遮蔽に起因する、ほんの少しの浮遊結合が含まれる。さらに、回路 400 に関するように、試験回路 450 は、試験回路であるだけでなく、実際の用途において帯域通過フィルタとして用いられ得る。しかしながら、回路 450 は、製造および試験が少し困難である。取り付けが決定的に影響し、かつ強誘電体キャパシタを追加することにより搭載に起因するさらなる損失がもたらされる。これは、C1 および C2 を実現するために用いられ、かつ強誘電体キャパシタなしのさらなる回路を有する同じ回路上に強誘電体キャパシタを直接製造することによって克服され得る。

30

#### 【0068】

試験回路および方法は、2 つの共振器ではなく、むしろ単一の共振器を用いることによってさらに単純化され得る。これはキャパシタ不整合の問題を解消する。生じた回路は、よりロバストであり、モデル化がより容易であり、かつより一層エラーを起こし難い。図 7 に示される結果はインターデジタルキャパシタに関する試験の結果であるが、ギャップまたはオーバーレイキャパシタは、有利に用いられ得、これは、ギャップおよびオーバーレイキャパシタの両方がインターデジタルキャパシタよりも高い Q を有し得るからであることに留意されたい。

#### 【0069】

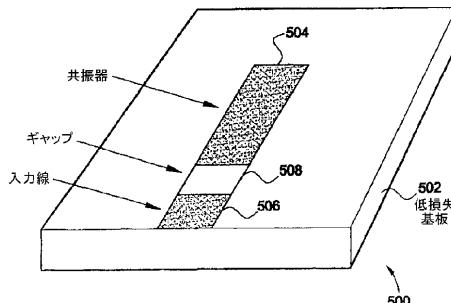

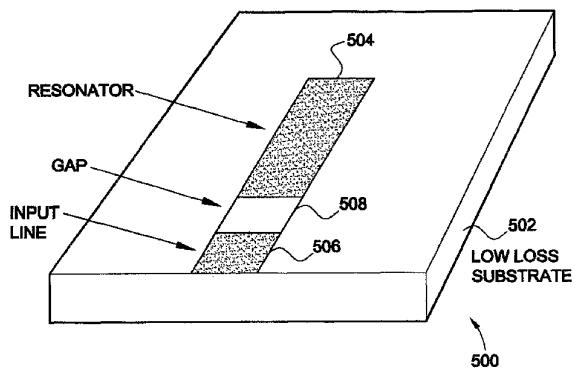

最も単純な形態のギャップ結合マイクロストリップ共振器を備える試験回路 500 は、図 9 に示される。回路 500 は、低損失基板 502、およびギャップ 508 によって入力線 506 から分離されたマイクロストリップ共振器 504 を備える。共振器薄膜は、ギャップ 508 において堆積されて、強誘電体ギャップキャパシタを生成する。従って、共振器 604 およびギャップキャパシタは、単一の一体型の構造として製造される。あるいは、強誘電体材料は、共振器 504 の下に堆積され得、チューニング可能共振器を生成する。

40

#### 【0070】

基板 502 は、マグネシウム酸化物、99% より高い純度を有するアルミナおよびサファイア等の高品質低損失基板である。基板 502 は、さらに、低 S.R (5.0  $\mu$  インチ) を有する。共振器 504 は、半波長 (開回路) または 1/4 波長 (短絡回路) 共振器のどちらかであり得る。半波長共振器は、より長いが製造が容易である一方で、1/4 波長共

50

振器は、より短いガビアを必要とする。近い臨界結合のためにギャップ 508 の幅が選択される。

#### 【0071】

ネットワークアナライザは、好適には、キャパシタンスおよび Q 測定値のために用いられる。ギャップキャパシタンスのモデルおよび金属損失の式は、ここで、ベース基板の Q と強誘電体薄膜の Q とからの複合である誘電体の Q を抽出するために用いられる。従って、ベース基板の損失を越える追加的損失は、強誘電体膜の損失を表す。最後に、S. Toncich および R. E. Collin による「Data Reduction Method for Q Measurements of Strip-Line Resonators」IEEE Transactions in MTT、No. 9 (1992 年 9 月) 1833 ~ 1836 ページ(参考のため、本明細書中に援用される)に概説されたデータ等の測定データの適切な解析がキャパシタアンダーテストの Q または損失を正確に抽出することが必要とされる。10

#### 【0072】

ここで、図 6 ~ 図 8 に記載された 2 次狭帯域共振試験法および回路を、図 9 に記載されたギャップが結合された單一共振器試験法および回路と比較することが有用である。ギャップ結合單一共振器は、小型、単純、および製造が非常に容易であるという点で有利である。これは、入力および出力キャパシタ C1 の可能な不整合をチューニングすることを必要としない。しかしながら、強誘電体損失正接を基板全体および結合キャパシタ損失から抽出することはより困難である。他方、2 次共振回路は、試験回路であることに加えて実際のデバイスであり得る。さらに、測定データと、シミュレーションデータ、または高 Q を有する非強誘電体キャパシタを用いて取得されたデータのどちらかとの比較が非常に容易である。2 次回路の不利な点は、これらがより大きく、より複雑な回路であること、および、最小挿入損失を取得するために必要とされ得る強誘電体キャパシタのチューニングがより多く必要とされ得ることである。20

#### 【0073】

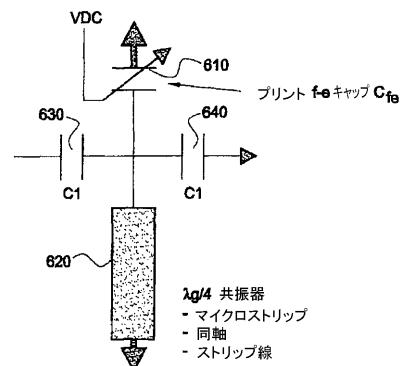

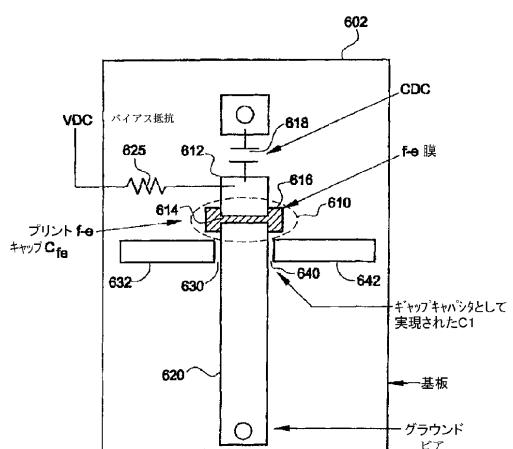

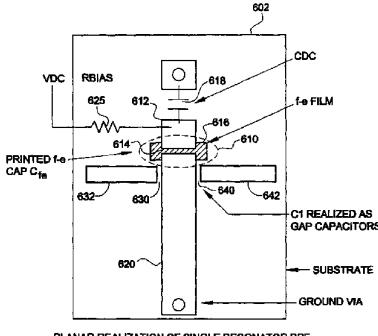

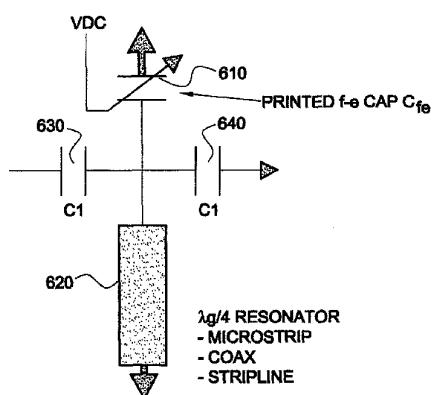

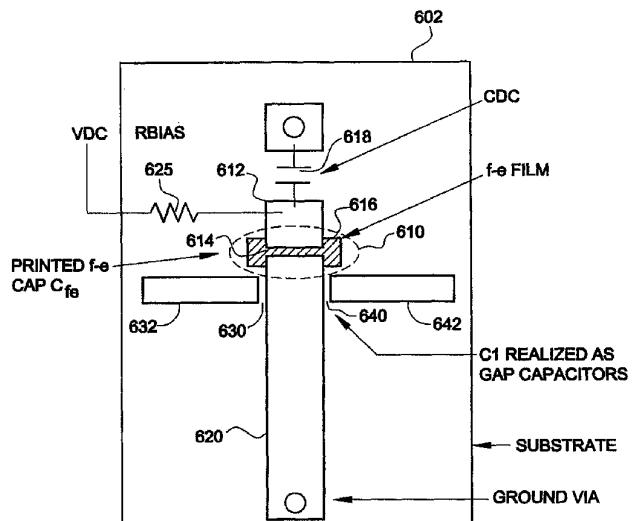

図 10a および図 10b は、好適な共振試験回路 600 を示す。回路 600 は、單一共振器帯域通過フィルタの形態をとる。回路 600 の模式図である図 10a を参照して、回路 600 は、共振器 620 に結合された強誘電体キャパシタ 610 を備える。キャパシタ 630 および 640 (C1) は、共振器を測定機器に接続する入力および出力キャパシタである。30

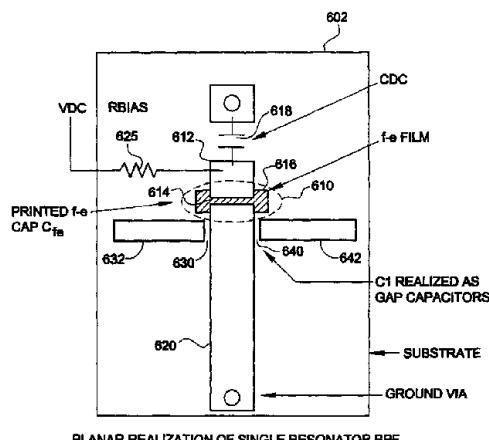

#### 【0074】

図 10b は、平面化した回路 600 である。見出され得るように、キャパシタ 610 および共振器 620 は、一体型のコンポーネントとして製造される。強誘電体膜 616 は、低損失基板 602 上に堆積される。共振器 620 および導電パッド 612 は、ギャップ 614 によって強誘電体膜 616 を介して分離され、強誘電体キャップキャパシタ 610 を規定する。DC バイアス電圧は、パッド 612 に印加され、かつバイアス抵抗器 625 を含み得る。DC ブロックキャパシタ 618 は、パッド 612 とグラウンドとの間に接続される。キャパシタ 630 および 640 は、キャパシタキャップを形成するために共振器 620 から分離された基板 602 上に堆積された導電ストリップ 632 および 642 によって実現される。40

#### 【0075】

1 インプリメンテーションにおいて、基板 602 は、99.5 % の純度のアルミナから形成され、約 40 ミルの厚さおよび約 5.0  $\mu$ インチの SR を有する。強誘電体膜 616 は、約 1.0  $\mu$ m の厚さを有し、かつギャップキャパシタ 610 の領域においてのみ堆積される。マイクロストリップ 612 および 620 は、4 ~ 6  $\mu$ m の厚さを有し、かつ約 1.0  $\mu$ m の間隔が空けられ、ギャップ 614 を規定する。共振器 620 の長さは、構造全体(キャパシタ 610 および共振器 620)が所望の周波数帯域で共振するように選択される。1 インプリメンテーションにおいて、共振器 620 は、1 / 4 波長共振器である。特定の共振周波数が所望または必要とされる場合、共振周波数を微調整するためにさらなる製50

造サイクルが用いられ得る。

【0076】

共振器620は、マイクロストリップ、同軸またはストリップ線共振器として構成され得る。平面マイクロストリップ構成は、回路600からのキャパシタンスおよびQ値の抽出をより容易にすることで好適である。一体型のコンポーネント構造（すなわち、共振器620／キャパシタ610等の一体型のギャップキャパシタを有する共振器）は、別々の共振器および一まとまりの素子キャパシタを使用するよりも有利である。なぜなら、予測不可能であり、かつ一まとまりの素子キャパシタによって導入された損失およびエラーを測定することが困難なキャパシタが取り除かれるからである。

【0077】

回路600等の单一共振器通過帯域試験回路を用いる試験方法は、以下のように進行する。第1に、一体型のギャップキャパシタを有する单一共振器通過帯域フィルタ試験回路が上述のように製造される。正確な薄膜の製造および処理技術は、所望のジオメトリおよび特性が獲得されることを確実にするために用いられる。好適には、±0.5ミクロンの範囲の許容誤差の技術が用いられる。一旦回路が製造されると、中心周波数 $f_0$ 挿入損失 $I_L$ が測定される。好適には、これらの測定値は、フル2ポート較正によって、および平均化を用いて較正されるネットワークアナライザを用いて取得される。

【0078】

次に、同一の回路が、Sonnet、IE3DまたはMomentum等の電磁場シミュレーションツールで設計および分析される。最初に、シミュレーションは、強誘電体膜に起因する損失（すなわち、0の損失正接）を想定する。強誘電体誘電率が、その後、試験回路において測定されたものと同じ中心周波数 $f_0$ を与えるようにギャップ領域において調整される。 $I_L$ は、その後、強誘電体ギャップキャパシタのみに関して計算される。この値は、その後、金属と関連した損失コンポーネント $L_{metal}$ を説明するシミュレーションで用いられる。

【0079】

次に、別の回路シミュレーションが動作するが、今回は、非ゼロ損失正接を用いる。インプリメンテーションにおいて、0.003の損失正接が用いられ、 $I_L$ が再計算される。この双方向プロセスは、試験回路から測定された挿入損失 $I_L$ が取得されるまで継続され、これにより、回路の損失正接の非常に正確な近似値が算出され、かつ特定の構造に基づく損失コンポーネント $L_{geom}$ が試験される（この場合、ギャップキャパシタ）。

【0080】

SR-BPFのベースライン性能は、 $f-e$ 膜を有しない回路を製造することによって確立され得る。生じた共振周波数は、当然、負荷キャパシタ610が小さくなると、より高くなる。これにより、SR-BPFの形状および周波数応答全体に関する正確な情報が提供される。

【0081】

回路600は、強誘電体ギャップによって導入された損失を測定するための精密なメカニズムであるばかりでなく、無線ハンドセット等の幅広い用途において実装され得る低損失チューニング可能フィルタ用の基本構成単位でもある。本明細書中に教示されたように構成された狭帯域共振回路は、典型的なRFトランシーバの複数のコンピーネントの効率を強化し、かつこれにチューニング可能性を追加するために用いられ得る。本発明が実装されるRFコンポーネントの実施例は、デュープレクサ、アイソレータ、整合回路、電力増幅器、マルチプレクサ、帯域通過フィルタおよび低雑音増幅器を含み得るが、これらに限定されない。チューニング可能な各素子を用いて、複数の回路ブロックを用いて、マルチバンドモードを収容することが2つ用になる。必要に応じて、共振回路は、所望のフィルタおよびシステムを生成するために適切な態様でカスケード接続され得、コストおよびサイズを低減する一方で、システム性能を大幅に改善する。典型的な無線ハンドセットのコンポーネントの多くはチューニング可能性によって利益を得る。

10

20

30

40

50

## 【0082】

本明細書中に含まれる記載および図面は、本発明の特定の実施形態であり、本発明によって広く考えられる主題を表す。しかしながら、本発明は、当業者に明らかである他の実施形態を含む。したがって、本発明の範囲は、添付の請求項によってのみ制限される。

## 【図面の簡単な説明】

## 【0083】

【図1】図1は、薄い強誘電体膜で製造されたインター・デジタルキャパシタの平面図である。

【図2】図2は、本発明のチューニング可能強誘電体ギャップキャパシタの断面図である。

10

【図3】図3は、ギャップ幅と強誘電体層厚さとキャパシタとの間の関係を示すテーブルである。

【図4】図4は、本発明による強誘電体オーバーレイキャパシタの平面図である。

【図5】図5は、図4のオーバーレイキャパシタの一部分の分解図である。

【図6】図6は、本発明による2次狭帯域共振試験回路である。

【図7】図7は、図6の試験回路を用いて取得されたデータを従来の試験法を用いて取得されたデータと比較するテーブルである。

【図8】図8は、本発明による2次狭帯域共振試験回路の別の実施形態である。

【図9】図9は、本発明による单一共振器狭帯域試験回路である。

【図10a】図10aは、本発明による单一共振器狭帯域試験回路の別の模式図である。

20

【図10b】図10bは、図10aの回路模式図の平面化である。

## 【図3】

FIG. 3

## 【図4】

FIG. 4

## 【図7】

| KWC | NRL<br>サンプル<br># | NRL<br>(pF)<br>キャパシタ | NRL<br>(0<br>VDC)<br>Q | KWC<br>キャップ<br>(pF) | KWC<br>(0<br>VDC)<br>Q | KWC<br>(40<br>VDC)<br>Q | f <sub>a</sub><br>(MHz) | チュー<br>ニング<br>(MHz/V) | コメント  |

|-----|------------------|----------------------|------------------------|---------------------|------------------------|-------------------------|-------------------------|-----------------------|-------|

| 01  | NRL #<br>1-A     | 1.012                | 10.1                   | 0.99                | 190                    |                         | 1622                    | ~1.0                  |       |

| 02  | NRL #<br>1-A     | 1.012                | 10.1                   | 0.96                | 183                    |                         | 1605                    | ~1.0                  |       |

| 01  | NRL #<br>3-A     | 1.004                | 10.1                   | 0.80                | 101                    | 123                     | 1610                    | ~1.0                  |       |

| 02  | NRL #<br>2-A     | 0.76                 | 10.2                   | 0.75                | 200                    |                         | 1900                    | ~0.5                  |       |

| 06  | NRL #<br>2-A     | 0.76                 | 10.2                   | 0.72                | 205                    |                         |                         | ~0.5                  | 損傷高電圧 |

| 05  | NRL #<br>2-A     | 0.76                 | 10.2                   | 0.71                | 198                    | 200                     | 1912                    | ~0.5                  |       |

FIG. 7

## 【図9】

FIG. 9

【図 10 a】

FIG. 10a

【図 10 b】

FIG. 10b

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

24 October 2002 (24.10.2002)

PCT

(10) International Publication Number

**WO 02/084310 A1**(51) International Patent Classification<sup>5</sup>: G01R 27/26, H01G 7/06

(21) International Application Number: PCT/IB02/01027

(22) International Filing Date: 2 April 2002 (02.04.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

|            |                             |    |

|------------|-----------------------------|----|

| 60/283,093 | 11 April 2001 (11.04.2001)  | US |

| 09/904,631 | 15 July 2001 (13.07.2001)   | US |

| 09/912,753 | 24 July 2001 (24.07.2001)   | US |

| 09/927,732 | 8 August 2001 (08.08.2001)  | US |

| 09/927,156 | 10 August 2001 (10.08.2001) | US |

(81) Designated States (national): AE, AG, AI, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CI, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GI, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GL, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW);

Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TU, TM);

European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR,

GB, GR, IE, IT, LU, MC, NL, PT, SE, TR); OAPI patent

(BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR,

NE, SN, TD, TG).

(71) Applicant: KYOCERA WIRELESS CORPORATION

[US/US]; 10300 Campus Point Drive, San Diego, CA

92121 (US).Published:

— with international search report(72) Inventor: TONCICH, Stanley, Slavko; 11155 Spooner

Court, San Diego, CA 92131 (US).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: LOW-LOSS TUNABLE FERRO-ELECTRIC DEVICE AND METHOD OF CHARACTERIZATION

**WO 02/084310 A1**

(57) Abstract: A tunable ferroelectric component (610-614) and a narrowband resonant circuit (610-620) for measuring the loss of the ferroelectric component. The ferroelectric component may be a capacitor integrated in the resonant circuit. The testing method eliminates other sources of loss to isolate the loss due to the ferroelectric material and to demonstrate that this loss is low.

WO 02/084310

PCT/IB02/01027

LOW-LOSS TUNABLE FERRO-ELECTRIC DEVICE AND METHOD OF

CHARACTERIZATION

5                   Related Applications

[01] This application claims the benefit U.S. Provisional Application 60/283,093, filed April 11, 2001, which is hereby incorporated by reference. Additionally, this application relates to U.S. application "Tunable Ferro-electric Filter," filed on July 13, 2001, and U.S. application "Tunable Ferro-electric Multiplexer," filed on July 24, 2001, which are hereby incorporated by reference.

10                  Field of the Invention

[02] The field of the present invention is ferro-electric tunable electronic devices and components.

15                  Background of the Invention

[03] Variable capacitors are advantageous as different electronic responses can be obtained by variation of the capacitance. The structures presently used to implement variable or tunable capacitors, however, have significant performance and practical limitations. Movable parallel plates, while providing variable capacitance for radio tuning, are bulky, lossy, noisy, generally operate over only a limited range of frequencies, or have any number of these limitations. 20

[04] A "lossy" component or device has a high insertion loss (IL), which is the ratio of power dissipated in the component to power delivered to a load. An electronic varactor is a semiconductor device that adjusts capacitance responsive to an applied voltage. Varactors are typically lossy and noisy, and 25 are therefore generally ineffective for high-frequency applications, particularly those above 200 MHz. Hence, they are not suited for tuning insertion loss-critical devices such 30

WO 02/084310

PCT/IB02/01027

as filters and multiplexers in wireless applications, particularly where Code Division Multiple Access (CDMA) is used. Another implementation providing variable capacitance is a micro-electro-mechanical system (MEMS). This is a miniature switching device that physically selects a different capacitor responsive to an applied signal. MEMS, however, is typically costly, unreliable, requires a substantial control voltage, and enables only a discrete set of pre-selected capacitance values.

[04] Because of their variable dielectric constant, ferroelectric materials are good candidates for making tunable capacitors or other tunable components. Under presently used measurement and characterization techniques, however, tunable ferroelectric components have gained the reputation of being consistently and substantially lossy, regardless of the processing, doping or other fabrication techniques used to improve their loss properties. They have therefore not been widely used. Ferroelectric tunable components operating in RF or microwave regions are perceived as being particularly lossy. This observation is supported by experience in RADAR applications where, for example, high RF or microwave loss is the conventional rule for bulk (thickness greater than about 1.0 mm) f-e materials especially when maximum tuning is desired. In general, most f-e materials are lossy unless steps are taken to improve (reduce) their loss. Such steps include, but are not limited to: (1) pre and post deposition annealing or both to compensate for O<sub>2</sub> vacancies, (2) use of buffer layers to reduce surfaces stresses, (3) alloying or buffering with other materials and (4) selective doping.

[05] As demand for limited range tuning of lower power components has increased in recent years, the interest in ferroelectric materials has turned to the use of thin film rather than bulk materials. The assumption of high ferroelectric loss, however, has carried over into thin film work as well. Conventional broadband measurement techniques

WO 02/084310

PCT/IB02/01027

have bolstered the assumption that tunable ferroelectric components, whether bulk or thin film, have substantial loss. [06] A broadband measurement of the capacitance value of a ferroelectric capacitor is typically obtained using a device such as an LRC meter, impedance analyzer or a network analyzer. From power measurements, one can calculate the lossiness of the capacitor. The inverse of lossiness is referred to as the Quality Factor ("Q"). Thus, a lossy device will have a low Q and a more efficient device will have a high Q. Q measurements for ferroelectric capacitors with capacitances in the range of about 0.5 pF to 1.0 pF operating in a frequency range of 1.8 GHz to 2.0 GHz, obtained using conventional measurement techniques, are typically claimed to be in the range of 10-50. This is unacceptably inefficient, and ferroelectric tunable components are therefore considered undesirable for widespread use. In wireless communications, for example, a Q of greater than 80, and preferably greater than 180, and more preferably greater than 350, is necessary at frequencies of about 2 GHz.

[07] As will be shown below, conventional ferroelectric components have been wrongly fabricated, measured and characterized. As a result, it is commonly assumed that ferroelectric tunable components are very lossy with Qs in the range of 10-50 in the L-band. Ferroelectric tunable devices operating in other frequency bands have also been labeled as having Qs unacceptable for most applications.

Summary of the Invention

[08] The methods of testing the loss, or its inverse, Q, of f-e films are flawed in the prior art. The prior art methods typically use broadband testing methods and non-integrated components. All of the loss mechanisms of the testing methods and devices under test are typically not accounted for. This has led investigators to believe that f-e materials are lossy.

WO 02/084310

PCT/IB02/01027

[09] The invention provides for narrowband testing methods and integration of components. All loss mechanisms are accounted for and eliminated or minimized. This results in more accurate test results, showing that some f-e materials are much less lossy than previously thought.

[10] With this testing method, f-e materials can be successfully investigated to find ideal tradeoffs between loss, tunability and other parameters. Low loss tunable f-e devices can be built. A low loss, f-e tunable capacitor can be built. Such a capacitor can be used as a building block in many applications where tunability is desired, but low loss requirements had been preventing the use of any other tunable devices. An example application is in wireless communication devices.

15        Brief Description of the Drawings

[11] The details of the present invention, both as to its structure and operation, may be gleaned in part by study of the accompanying drawings, in which like reference numerals refer to like parts, and in which:

20 [12] **Figure 1** is a top view of an interdigital capacitor fabricated with a thin ferroelectric film;

[13] **Figure 2** is a sectional view of a tunable ferroelectric gap capacitor according to the present invention;

[14] **Figure 3** is a table showing the relationship between gap width, ferroelectric layer thickness and capacitance;

[15] **Figure 4** is a top view of a ferroelectric overlay capacitor according to the present invention.

[16] **Figure 5** is an exploded view of a portion of the overlay capacitor of **Figure 4**.

30 [17] **Figure 6** is a second order narrowband resonant testing circuit according to the present invention;

[18] **Figure 7** is a table comparing data obtained with the testing circuit of **Figure 6** with data obtained using conventional test methods;

WO 02/084310

PCT/IB02/01027

- [19] **Figure 8** is another embodiment of a second order narrowband resonant testing circuit according to the present invention;

- [20] **Figure 9** is a single resonator narrowband testing circuit

5 according to the present invention;

- [21] **Figure 10a** is a schematic of another embodiment of a single resonator narrowband testing circuit according to the present invention; and

- [22] **Figure 10b** is a planar realization of the circuit

10 schematic of **Figure 10a**.

Detailed Description of the Invention

[23] The present invention provides test methods utilizing narrowband resonant circuits that accurately measure and characterize the efficiency of tunable ferroelectric components in the frequency range in which they will be used, and with topologies that will be used. These test methods and circuits establish that tunable ferroelectric components are not as uniformly lossy as previously thought and that they may advantageously be used in low-loss applications and devices, such as wireless handsets. With an accurate determination of loss, tunable ferroelectric components can be properly optimized and designed. Specific loss mechanisms can be identified and eliminated, or otherwise reduced and bounded.

[24] Tunable ferroelectric components, especially those using thin films, can be employed in a wide variety of frequency agile circuits. Tunable components are desirable because they can provide smaller component size and height, lower insertion loss or better rejection for the same insertion loss, lower cost and the ability to tune over more than one frequency band. The ability of a tunable component that can cover multiple bands potentially reduces the number of necessary components, such as switches that would be necessary to select between discrete bands were multiple fixed frequency components used. These advantages are particularly important

WO 02/084310

PCT/IB02/01027

in wireless handset design, where the need for increased functionality and lower cost and size are seemingly contradictory requirements. In CDMA handsets, for example, performance of individual components is highly stressed.

5 Ferroelectric materials may also permit integration of RF components that to-date have resisted shrinkage, such as an antenna interface unit (AIU) for a wireless device.

[25] For example, an AIU could integrate one or more tunable duplexers (US PCS and cellular in a dual band wireless communication device), diplexers, PA's and LNA's. Some or all of these components could be advantageously integrated, their total size or volume or both being reduced and their electronic performance improved. Further applications for tunable ferroelectric components are set forth in the latter

15 portion of this specification.

[26] As with any dielectric, ferroelectric material has two primary loss mechanisms, conductivity loss and damping from lattice vibrations in the dielectric. The combination of the two effects is referred to as the material's loss tangent (tan(δ)). For ferroelectric materials considered in tunable RF or microwave circuits, damping from lattice vibrations dominate, as there are no free charge carriers. However, any method which measures tan(δ) will include effects of finite conductivity if present. This is because the loss effects of

25 the two mechanisms are indistinguishable as far as rf/microwave properties are concerned.

[27] A primary component in RF circuits is the capacitor. F-E tunability will now be discussed in terms of f-e capacitors. The total loss of a capacitor, whether tunable or not, is given by its quality factor (Q) which is expressed as a ratio of its stored to dissipated energy, where the energy is stored in the electric field and dissipated in resistance. For a lumped element capacitor, the unloaded Q ( $Q_0$ ) is given by:

[28]  $Q_0 = X/R_s = 1 / (\omega * R_s * C)$  (1)

WO 02/084310

PCT/IB02/01027

[29] where  $\omega$  = radian frequency;  $R_s$  = the series resistance of the capacitor; and  $C$  = the capacitance of the capacitor.  $R_s$  is measured and given that  $C$  and  $\omega$  are known,  $Q_u$  can be calculated. The series resistance arises from both the conductor and dissipative loss in the dielectric, i.e.  $\tan(\delta)$ .

[30] If a tunable capacitor is integrated into a resonant circuit, the total  $Q$  ( $Q_t$ ) of the system is now given by:

[31]  $1/Q_t = 1/Q_c + 1/Q_d + 1/Q_r \quad (2)$

[32] where  $Q_c$  is the conductor  $Q$ ;  $Q_d$  is the dielectric  $Q$  and  $Q_r$  is the radiation  $Q$ . For a well designed non-radiating system, there is no radiation loss. Hence, the conductor loss and the dielectric loss determine the total loss. The dielectric loss is the effect of the loss tangent,  $\tan(\delta)$ , including conductivity loss attributable to the dielectric, if the latter loss is present. Hence, for both the unloaded  $Q$  and the total  $Q$ , a correct measurement of  $\tan(\delta)$  is crucial in determining whether a tunable device can be fabricated with acceptable loss characteristics.

[33] Cavity resonator methods are conventionally used to measure a material's dielectric constant and loss tangent. These methods are difficult, especially at lower microwave frequencies (~ 2 GHz) where cellular phones operate, as the size of the cavity is quite large. Use of cavity resonator methods on thin ferroelectric films poses a greater problem, as it is very difficult to measure the perturbation introduced to a cavity from a structure having a thickness in the range of one micron. The potential for error is significant.

[34] Because of this difficulty with resonator methods, interdigital capacitors (IDC's) are usually used to measure ferroelectric film quality. A ferroelectric interdigital capacitor (IDC) 100 in a conventional microstrip configuration is depicted in Figure 1. Interdigital capacitor 100 comprises base substrate 110; thin film ferroelectric layer 120; and first and second conductors 130 and 140. Interdigital

WO 02/084310

PCT/IB02/01027

capacitors are typically used in applications such as monolithic microwave integrated circuits (MMICs) and in applications where small footprints and capacitances in the range of 0.1-6 pF are needed. In an interdigital capacitor, 5 the capacitance is created between conductive parallel lines or fingers in the structure.

[35] Base substrate 110 typically comprises a low loss material such as magnesium oxide (MgO), sapphire or high purity aluminum, for example. The substrate is chosen based on 10 its inherent low loss tangent and its ability to accept the direct deposition of a wide range of f-e films without additional buffer layers. A thin ferroelectric film 120 is deposited on base substrate 110. Ferroelectric film 120 typically has a thickness in the range of 0.15-1.5 microns. A 15 conductive layer is then deposited onto ferroelectric film 120. Sometimes an adhesion layer is needed. The conductive layer is preferably a metallic material such as copper, gold or silver. These metals are advantageous due to their relatively low loss at room temperature. For purposes of this 20 specification, room temperature is defined as being in the range from -30°C to +85°C which covers the typical operating temperature range for most commercial components. The conductive layer typically has a thickness in the range of 0.5 to 6.0 microns, with a thickness in the range of 0.5 to 1.5 25 microns being most common. Thickness requirements vary based on skin depth which varies based on frequency.

[36] While thin film ( $t_{f-e}$  less than about 1.5  $\mu\text{m}$ ) f-e materials have been discussed, thick film f-e material can be used as well. Here, "thick film" is defined to be  $t_{f-e}$  greater 30 than about 1.5  $\mu\text{m}$  and less than about 1.0 mm. Bulk is greater than about 1.0 mm. The fabrication and application of thick film f-e material is quite different than that of thin film f-e material. It usually involves a paste or a sol-gel technique, and the f-e materials to produce the significantly

WO 02/084310

PCT/IB02/01027

added thickness. The added thickness and especially reduced cost comes at the price of somewhat degraded f-e performance, notably, reduced tunability.

[37] Interdigital capacitor 100 is then fabricated using either etch-back or lift-off techniques to form first conductor 130 and second conductor 140. First conductor 130 has fingers 132 and spaces 134 that are proximate fingers 142 and spaces 144 of second conductor 140. The conductors are arranged so that fingers 132 of first conductor 130 are in spaces 144 of second conductor 140, and so that fingers 142 of second conductor 140 are in spaces 134 of first conductor 130. To date, most researchers and other practitioners in f-e film fabrication and characterization have designed IDC's with fingers typically 1-5 microns wide, and the gap or space between the fingers typically 1-5 microns wide.

[38] The capacitance is created primarily between fingers 132 and 142. To generate a high level of capacitance, small gap size (< 5 microns) and long fingers are required. When used as a ferroelectric tuning capacitor, small gap size also assists in creating a large tuning field between the fingers. This is critical because much of the tuning field is lost in the air region above capacitor 100.

[39] The greatest loss component in this configuration is in the odd mode generated in the finger region. The coupling between the parallel lines can be expressed in terms of an even mode and an odd mode. The even mode occurs when both lines are excited in phase (usually taken to be zero), and the odd mode occurs when the lines are excited 180 degrees out of phase. In microstrip circuits, the velocities at which the even and odd modes propagate are different. The loss further increases when a thin conductive layer (less than 1.5 microns), narrow finger width and gap spacing (either or both less than 5 microns) and sharp corners are used.

[40] The standard procedure for measuring thin ferroelectric film loss via an interdigital capacitor is as follows. As

WO 02/084310

PCT/IB02/01027

described above, approximately 0.5 microns of ferroelectric film is deposited on a low loss substrate such as magnesium oxide. Then, a conductive layer having a thickness of 1 micron or less is deposited to permit fabrication of an interdigital capacitor of the smallest possible size. Finger width and gap spacing are both typically in the 1 to 5  $\mu\text{m}$  range. Etch-back or lift-back techniques are used to form narrow, long fingers with sharp corners. The resulting interdigital capacitor is characterized using a broadband measurement tool such as an LRC meter or an impedance or network analyzer with probe tips that contact the capacitor.

[41] Using this procedure, capacitors in the range of 0.2 to 1.5 pF are obtained, with Q's in the range of 10-100 at an operating frequency of anywhere from approximately 500 MHz to approximately 2 GHz is typically measured. This loss is typically attributed entirely to the ferroelectric film. These Q values are considered quite low and, consequently, ferroelectric tunable components are commonly assumed to be high loss and unacceptable for many uses. In wireless communications, for example, a Q of greater than 100 and preferably greater than 250 is necessary at frequencies in the range of 2 GHz for f-e capacitors in the vicinity of 1.0 pF. As will be described below, however, conventional fabrication and loss measurement techniques do not yield a reliable indication of the actual loss attributable to the ferroelectric film.

[42] As indicated in Equation (1), capacitor loss (whether tunable or not) is proportional to the series loss  $R_s$  at radio frequency ( $f >$  about 500 MHz) where the effect of the large parallel resistance that shunts the capacitance is negligible. The capacitor does not care what the source of the series loss is, only that there is a source. For example, for a 1 pF ferroelectric tunable capacitor to have an acceptably low loss ( $Q_u=250$ ) at 2 GHz, the series loss must be only  $0.32\Omega$ . The

WO 02/084310

PCT/IB02/01027

series loss includes the total loss from all sources arising from the capacitor's use. In order to minimize or eliminate the sources of series loss, one must first account for each loss mechanism that is present. This will permit a more 5 accurate determination of the loss attributable specifically to the ferroelectric film.

[43] For f-e devices, the total loss is governed by summing each source contribution as follows:

[44]  $L_t = L_{geom} + L_{attach} + L_{metal} + L_{sub} + L_{rad} + L_{mess} + L_{f-e}$ ;

10 where  $L_{geom}$  is derived from the topology of the capacitor,

$L_{attach}$  is loss due to device attachment,

$L_{metal}$  is the total metal loss,

$L_{sub}$  is the base substrate loss (if present),

$L_{rad}$  is the radiation loss, both desired and undesired,

15  $L_{mess}$  is the total loss arising from measurement errors,

and

$L_{f-e}$  is the f-e loss tangent.

[45] This loss allocation can first be used to obtain an accurate value of  $L_{f-e}$  (or f-e tan  $\delta$ ) at the desired operating 20 frequency in the manner in which the f-e capacitor will be used. To correctly derive  $L_{f-e}$ , one must eliminate or constrain all of the other loss contribution sources just described. For example,  $L_{geom}$  will vary according to topology, being best 25 for an overlay capacitor, worse for a gap capacitor, and much worse for an IDC capacitor. Although this loss can be reduced and controlled, it is inherent to a device. Consequently, the choice of topology for a given f-e capacitor will affect the best possible  $Q_c$  attainable from the f-e capacitor. Electromagnetic (EM) software can establish a baseline loss 30 for a desired geometry, assuming a lossless f-e film. This

WO 02/084310

PCT/IB02/01027

baseline loss represents the best (lowest) loss for a given geometry.

[46] In general, a gap capacitor is easiest to fabricate. An IDC is next easiest, and an overlay capacitor is hardest of 5 these three. Compared to an IDC, the gap capacitor will have a better Q but lower capacitance per unit cross section ( $W$  in Fig. 1a). The IDC's capacitance is greater due to the use of a number of fingers per unit cross section. For many communication filter applications, however, large capacitance 10 ( $C \geq 4.0 \text{ pF}$ ) is not needed. Thus, a gap capacitor often can provide adequate capacitance. The inherently high value of  $\kappa$  for most f-e films helps provide relatively high capacitance per unit cross section,  $W$ , compared to a conventional gap capacitor.

15 [47]  $I_{\text{attach}}$  arises from discrete device attachment techniques, including, for example, solder, silver paint, or wire bonding. These attachment losses may be large and unpredictable. The lowest losses are achieved by direct fabrication of the f-e capacitor to the resonator or other RF circuitry, thus 20 minimizing if not eliminating this loss component.

[48] The inherent loss of a stand-alone f-e capacitor is of little consequence. What is of much greater consequence is any added loss arising from the attachment of the f-e capacitor to a circuit. Even if the f-e capacitor were 25 lossless, should a large loss connection be used, the overall effect is that of a lossy f-e device. For example, if a  $Q \geq 250$  at 2.0 GHz is desired for a capacitance of 1.0 pF, then the total series resistance  $R_s$  must be  $\leq 0.32 \text{ ohm}$ . Any additional loss will thus further reduce the Q of this 30 capacitor. That this additional loss is external to the actual capacitor is irrelevant. Even unavoidable loss mechanisms, such as those due to mounting, for example, lower the effective Q of the capacitor from the perspective of its effect on the system.

WO 02/084310

PCT/IB02/01027

[49] For minimum added loss, the connection between the f-e capacitor and the resonator should provide the lowest added resistance. Thus, the electric currents and charges associated with the f-e capacitor should see a minimum added loss. Conventional bonding or mounting techniques, such as (but not limited to) soldering, wire bonding or silver paint or paste do not provide for such a low loss, controllable bond.

[50] The added, unpredictable loss arising from the use of such bonding methods degrades the realized Q regardless of whether or not the f-e capacitor is being used for resonator tuning purposes or characterization of an f-e film. Thus, for best performance (lowest loss) the f-e capacitor structure should be directly fabricated onto or with the resonator it is meant to tune or onto other essential RF circuitry. Only by direct fabrication can there be a minimum loss transition for electromagnetic (EM) sources (currents) from the f-e tuning elements to the resonator. The desirable effects of direct f-e capacitor fabrication onto or with a resonator can be enhanced by the lack of sharp corners or transitions.

[51] Factors for  $I_{\text{metal}}$  include the surface roughness (SR) of the metal, metal thickness as compared to skin depth,  $\delta_s$ , and conductivity. SR may be effectively eliminated as a factor if SR is less than approximately 10 micro inches root mean square (rms) for operating frequencies in the L and S band (1-4 GHz). The metal thickness may be reduced as a factor if the thickness is  $1.5\delta_s$  or greater, or effectively eliminated if the thickness is  $\geq 5\delta_s$ . For electrode contacts, metal thickness ( $t_m$ ) can be approximately  $1.5\delta_s$ . For the case of electromagnetic resonators, where a travelling or standing wave must be supported, i.e., where the metal in question extends for an appreciable fraction of a wavelength (about 10% or greater), the metal thickness should be closer to about  $5\delta_s$  or greater.

WO 02/084310

PCT/IB02/01027

- [52] Conductivity is best for Au, Cu, or Ag. Thus,  $L_{\text{metal}}$  can be reduced and controlled, but not eliminated as a factor. Its effect, however, can be calculated by expressions well known to those skilled in the art, or by using line calculator tools available in commonly used circuit simulators, such as Eagleware or Touchstone. Further, precise fabrication control can bound geometric variations in  $L_{\text{metal}}$ .

- [53] The loss contribution represented by  $L_{\text{sub}}$  may be minimized by choosing a low loss substrate with a loss tangent less than 0.001 and preferably less than 0.0005 at the operating frequency of interest. Suitable materials include >99% pure alumina, a best current choice for loss/cost benefits. Sapphire or MgO are better than alumina in that they have lower loss tangents, but they are more expensive. All these materials will accept many f-e thin films without buffer layers and have a surface roughness that is acceptable with little or no further polishing. Semiconductor substrates are poor choices because of their relatively high conductivity. In addition to the factors of loss tangent, surface roughness and price, suitable substrates should not be brittle, can be fabricated as larger area wafers, and can be easily metallized without extensive pre-processing.

- [54] Separating out  $L_{\text{sub}}$  from the total loss of a composite substrate (f-e film plus substrate) can be achieved by using EM field or circuit simulation software. For example, Sonnet, Momentum, or IB3D may be used. Thus,  $L_{\text{sub}}$  can be reduced significantly and calculated precisely.

- [55]  $L_{\text{rad}}$  can be eliminated by proper shielding and design, and so is typically not a factor. It should be noted that a wide variety of filters, especially planar filters such as combline or hairpin, depend upon radiative coupling to achieve their desired performance. In these cases, one should ensure that the unwanted, stray coupling is reduced, if not eliminated.

- [56]  $L_{\text{meas}}$  can add significantly to the circuit loss error because small, added loss significantly reduces the measured Q

WO 02/084310

PCT/IB02/01027

of the device-under-test (DUT) or system thus obscuring the intrinsic Q of the DUT. The conventional method for measuring dielectric constant and loss tangent in a material is the cavity perturbation technique, which is well known to anyone skilled in the art. At L-band, however, the size of the cavity becomes quite large. When characterizing thin films (as opposed to bulk) with film thickness  $\leq 1.5 \mu\text{m}$ , such as f-e films, the problem becomes very difficult as measurement errors can be severe. Furthermore, one should characterize an f-e capacitor (or filter) in a manner most similar to how it will be used. Thus, the preferred way to characterize f-e compounds or films is by microstrip resonator techniques.

[57] For measurements on resonant circuits, a network analyzer is the preferred choice. To minimize measurement loss and attain the most accurate measurement using a network analyzer, loss to DUT should be calibrated out, a full two port calibration of the analyzer should be performed and averaging should be used for calibration and measurement.

[58] Through minimization or elimination of the device attachment, substrate, radiation and measurement error loss components, the total loss becomes:

$$[59] L_{\text{tot}} = L_{\text{geom}} + L_{\text{f-e}} + \Delta L_{\text{misc}} \quad (4)$$

[60]  $L_{\text{tot}}$  is the total loss for a given ferroelectric capacitor geometry, and  $L_{\text{geom}}$  and  $L_{\text{metal}}$  are integral parts of that geometry. Their presence is appropriate for determining the actual loss of a specific device, but they can be quantified and removed in order to determine the loss due solely to the ferroelectric material.  $L_{\text{geom}}$  can be determined from an accurate electromagnetic simulation of the circuit assuming a lossless ferroelectric material; and  $L_{\text{metal}}$  can be determined using the expressions for metal loss assuming conductivity, surface roughness (if applicable) and skin depth.  $\Delta L_{\text{misc}}$  represents a combination of incomplete removal of the other loss mechanisms with the finite bounds on  $L_{\text{geom}}$  and  $L_{\text{metal}}$ .

WO 02/084310

PCT/IB02/01027

[61] This two-step process of (a) accounting for all loss mechanisms; and (b) eliminating or bounding these losses not only permits an accurate determination of the ferroelectric loss, it also helps establish correct design guidelines for 5 low loss tunable components. Correct knowledge of  $L_{f-e}$  allows one to first determine whether or not the film under consideration can be used for a proposed application. Knowledge of  $L_{f-e}$  further provides a necessary baseline for any type of optimum design using ferroelectric films. This 10 knowledge is necessary if one is to effectively trade-off loss tangent for tunability. In short, accurate fabrication and measurement techniques result in consistent ferroelectric film loss characterization.

[62] Based on this loss analysis, low loss tunable 15 ferroelectric components, and in particular tunable ferroelectric capacitors, can be designed, tested and implemented in a wide variety of applications. Design procedure and implementation based on this loss analysis for three common types of capacitors- (1) gap capacitors, (2) 20 overlay capacitors and (3) interdigital capacitors - will now be discussed.

[63] A ferroelectric tunable gap capacitor 200 is illustrated 25 in Figure 2. Gap capacitor 200 comprises substrate layer 202, ferroelectric layer 204 and metal layer 206 defining capacitance-inducing gap 208. The following design implementation minimizes losses from other sources and permits an accurate determination of the loss due to the ferroelectric film 204. It assumes an operating frequency in the L-band (1- 30 2 GHz) for wireless handsets, though the same methods could be applied in other bands.

[64] In one implementation, substrate 202 is a layer of 99.5% 35 pure alumina having a thickness in the range of 20-40 mils. Surface roughness should be less than or equal to about 5  $\mu$ inch rms. Ferroelectric layer 204 is a film of barium strontium titanate,  $Ba_xSr_{1-x}TiO_3$ , (BSTO) having a thickness in

WO 02/084310

PCT/IB02/01027

the range of 0.15 to 2.0 microns. Using a film thickness >1.0  $\mu\text{m}$  maximizes capacitance and tuning range.

[65] Adjusting the Ba/Sr fraction, doping or annealing are preferably chosen to provide the minimum  $\tan \delta$  while providing the required tuning range. In one embodiment,  $x = 0.5$  (in  $\text{Ba}_x\text{Sr}_{1-x}\text{TiO}_3$ ) for room temperature operation. Alternative ferroelectric materials could also be used. Metal layer 206 has a thickness of approximately 2.5  $\mu\text{m}$ , which makes it suitable for electrode application. Gap 208 is 30-80 mils wide, and the edges should be rounded to maximize loss reduction. The capacitance demonstrated by gap 208 is in the range of 0.6 pF to 1.5 pF at 0 volts DC bias.

[66] EM simulations indicate that for a capacitance of approximately one pF at two GHz, a gap capacitor has  $Q>700$ , assuming a loss tangent of 0.002, or  $Q>300$ , assuming a loss tangent of 0.005. **Figure 3** is a table showing the relationship between gap width, ferroelectric layer thickness and capacitance. This data is very useful for target design of gap capacitor test circuits. The results in **Figure 3** assume a 0.5 micron thick ferroelectric film with a dielectric constant of 1000 at 0V DC bias, a 40 mil thick substrate layer of 99.5% pure alumina, and a loss tangent of 0.002 for the f-e film.

[67] A ferroelectric overlay capacitor 300 according to the present invention is illustrated in **Figure 4**. Capacitor 300 comprises substrate 310; bias pad layer 320; ferroelectric layer 330; and capacitor pad layer 340. Bias pad layer 320 defines a DC bias pad and capacitor pad 340 defines capacitor pad 342 and DC blocking capacitor pad 344.

[68] In one implementation, base substrate 310 is alumina having a thickness in the range of 20-40 mils. Bias pad layer 320 comprises a base electrode layer of silver having a thickness of approximately 2.0 microns covered by a layer of platinum having a thickness of approximately 100 nm. The

WO 02/084310

PCT/IB02/01027

platinum layer prevents the silver layer from oxidizing during growth of the ferroelectric layer. Layer 320 has a pad built-in for connecting a resistance in the range of 0.5 to 1.0 MΩ to provide DC bias. If needed, a thin (10 nm) chromium layer 5 may be interposed between the alumina and silver to provide better adhesion. Ferroelectric layer 330 is a thin film of BSTO having a thickness of approximately one micron. Capacitor pad 342 has a minimum area of 8.0 by 4.0 mils and is topped by electrodes of gold or silver that have an area of 10 approximately 4.0 by 4.0 mils. The DC blocking capacitor has a capacitance of at least 150-200 pF and an area of approximately 100 by 100 microns. The total area of contact pad 344 is a minimum of 7.0 by 8.0 mils.

[69] An overlay capacitor has a minimum capacitance in the 15 range of 0.8-1.5 pF. As can be seen in Figure 5, which is an enlargement of a portion of capacitor 300, the overlap area 350 of capacitor 300 is very small. In one implementation, overlap area 350 has a size of 0.3 mil by 0.3 mil. This is based on a BSTO dielectric constant of about 1000 at 0 volts 20 DC and a film thickness of about 1.0 microns. The pads 342 and 320 taper to and from capacitor overlay area 350. The taper is from 4.0 mils to about 0.25 mils in 1.0 mil distance.

[70] The loss target for capacitor 300 is a Q of at least 350 at 2.0 GHz for 1.0 pF. If needed, the ferroelectric film 330 25 can be further optimized via doping, annealing or use of a buffer layer or layers. Finally, the change in capacitance should preferably be 2:1 (50%) or greater for a change in bias voltage of 0-2.5 volts.

[71] One aspect of the present invention is optimal structures 30 and design criteria for tunable ferroelectric components, of which the capacitor structures described above are one example. Another aspect of the present invention is measurement methods and apparatus for accurately characterizing the losses in tunable ferroelectric components.

35 These methods involve the use of resonators and narrowband

WO 02/084310

PCT/IB02/01027

resonant circuits. Narrowband measurements are appropriate since the devices being measured are designed to operate at a narrowband of frequencies. Narrowband (resonant) measurements are also preferred as the naturally enhance the effect of small losses making them easier to measure, and they make the measurement more accurate. Prior methods have involved broadband measurements that are inappropriate and inaccurate for narrowband devices. Two inventive implementations of these testing resonant circuits will be described: second order narrowband bandpass filters, and microstrip resonator circuits (halfwave or quarterwave).

[72] Figure 6 shows a resonant narrowband testing circuit 400 configured to test two ferroelectric capacitors 410 and 412. It is a 2<sup>nd</sup> order planar combline filter. Capacitors 410 and 412 are configured as described with respect to Figure 1 and Figure 2 and are implemented to minimize loss components. Testing circuit 400 comprises a planar, second order combline bandpass filter and includes two resonators 402 and 404 coupled in series with, respectively, ferroelectric capacitors 410 and 412. A DC bias voltage is applied to capacitors 410 and 412. Capacitors 410 and 412 may be fabricated and mounted for testing either as lumped elements or by printing directly on the substrate. DC blocking capacitors (capacitance equal to about 180 pF) are not shown. In a lumped configuration, the capacitors are soldered or attached with silver paint or paste. This permits use of a wide variety of devices, however, there is an increased and unpredictable loss due to this mounting method. In a printed configuration, the capacitors are printed directly on the substrate. Printing is advantageous in that no soldering or bonding is required and there is a lower loss due to the direct fabrication. The type of substrates that may be used is limited, however, due to the presence of the ferroelectric film. DC blocking capacitors are not shown.

WO 02/084310

PCT/IB02/01027

[73] The response is measured through input and output lines 406 and 408 connected to a network analyzer. A measurement of the resonator center frequency  $f_0$  permits determination of the actual capacitor value (see equation (1), above), and the 5 insertion loss at  $f_0$  determines the capacitor Q. After these measurements are obtained, a circuit simulation can be used to obtain capacitance and Q values and the results compared.

[74] In order to demonstrate the dramatic difference in test 10 results obtained using the test method of the present invention relative to conventional test methods, reference is made to Figure 7. The table in Figure 7 presents measurement data obtained from ferroelectric interdigital capacitor samples fabricated at the Naval Research Laboratory (NRL), Washington DC, under contract to Kyocera Wireless Corporation 15 (KWC), the assignee of the present invention. Capacitance and Q measurements taken from the interdigital capacitor samples at NRL using conventional test methods (in this case, an HP 4291B Impedance Analyzer and a Cascade Tech microwave probe) are compared to measurements taken from the same samples at 20 KWC using the novel test methods described above.