(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7099560号

(P7099560)

(45)発行日 令和4年7月12日(2022.7.12)

(24)登録日 令和4年7月4日(2022.7.4)

|            |                 |

|------------|-----------------|

| (51)国際特許分類 | F I             |

| H 04 N     | 5/376(2011.01)  |

| H 04 N     | 5/374(2011.01)  |

| H 04 N     | 5/3745(2011.01) |

|            | H 04 N 5/376    |

|            | H 04 N 5/374    |

|            | H 04 N 5/3745   |

請求項の数 11 (全44頁)

|           |                              |          |                          |

|-----------|------------------------------|----------|--------------------------|

| (21)出願番号  | 特願2021-6115(P2021-6115)      | (73)特許権者 | 000004112                |

| (22)出願日   | 令和3年1月19日(2021.1.19)         |          | 株式会社ニコン                  |

| (62)分割の表示 | 特願2016-94185(P2016-94185)の分割 |          | 東京都港区港南二丁目15番3号          |

| 原出願日      | 平成28年5月9日(2016.5.9)          | (74)代理人  | 100096770                |

| (65)公開番号  | 特開2021-61641(P2021-61641A)   | (72)発明者  | 弁理士 四宮 通                 |

| (43)公開日   | 令和3年4月15日(2021.4.15)         |          | 猿渡 修                     |

| 審査請求日     | 令和3年1月19日(2021.1.19)         | (72)発明者  | 東京都港区港南二丁目15番3号 株式会社ニコン内 |

|           |                              |          | 船水 航                     |

|           |                              | (72)発明者  | 東京都港区港南二丁目15番3号 株式会社ニコン内 |

|           |                              |          | 審査官 大室 秀明                |

最終頁に続く

(54)【発明の名称】 撮像素子及び撮像装置

## (57)【特許請求の範囲】

## 【請求項1】

第1方向及び第2方向に設けられ、光を電荷に光電変換する複数の光電変換部と、前記光電変換部で光電変換された電荷による信号が出力される信号線と、前記光電変換部と前記信号線との間に接続され、前記信号を出力するための第1出力部と、第1領域及び前記第1領域と異なる第2領域において前記第1方向及び前記第2方向に複数設けられ、前記第1出力部と前記信号線との間に接続され、前記第1出力部から出力された前記信号を前記信号線に出力するための第2出力部と、前記第1方向に設けられた複数の前記第1出力部に共通して設けられ、前記第1出力部を制御するための第1制御線と、前記第1方向及び前記第2方向に設けられた複数の前記第2出力部に共通して設けられ、前記第2出力部を制御するための第2制御線と、前記第1領域に設けられた前記第2出力部及び前記第2領域に設けられた前記第2出力部の少なくとも1方から前記信号を出力させるための設定を行う設定部と、を有する撮像素子。

## 【請求項2】

第1方向及び第2方向に設けられ、光を電荷に光電変換する複数の光電変換部と、前記光電変換部で光電変換された電荷による信号が出力される信号線と、前記光電変換部と前記信号線との間に設けられ、前記光電変換部で光電変換された電荷による信号を出力する第1出力部と、

前記第1出力部と前記信号線との間に設けられ、前記第1出力部から出力された前記信号を前記信号線に出力するための第2出力部と、

前記第1方向に設けられた複数の前記第1出力部に共通して設けられ、前記第1出力部の電源電圧を供給するための給電線と、

前記第1方向及び前記第2方向に設けられた複数の前記第2出力部に共通して設けられ、前記第2出力部を制御するための制御線と、

を有する撮像素子。

【請求項3】

第1方向及び第2方向に設けられ、光を電荷に光電変換する複数の光電変換部と、

前記光電変換部で光電変換された電荷による信号が出力される信号線と、

前記光電変換部と前記信号線との間に接続され、前記光電変換部で光電変換された電荷による信号を出力する第1出力部と、

第1領域及び前記第1領域と異なる第2領域において、前記第1方向及び前記第2方向に複数設けられ、前記第1出力部と前記信号線との間に接続され、前記第1出力部から出力された前記信号を前記信号線に出力するための第2出力部と、

前記第1方向及び前記第2方向に設けられた複数の前記第1出力部に共通して設けられ、前記第1出力部の電源電圧を供給するための給電線と、

前記第1方向に設けられた複数の前記第2出力部に共通して設けられ、前記第2出力部を制御するための制御線と、

前記第1領域に設けられた前記第2出力部及び前記第2領域に設けられた前記第2出力部の少なくとも1方から前記信号を出力させるための設定を行う設定部と、

を有する撮像素子。

【請求項4】

請求項1から請求項3のいずれか一項に記載の撮像素子において、

前記第2出力部に信号を出力させるための制御信号を保持する保持部を有する撮像素子。

【請求項5】

請求項4に記載の撮像素子において、

前記保持部は、前記第2出力部毎に設けられる撮像素子。

【請求項6】

第1方向及び第2方向に設けられ、光を電荷に光電変換する複数の光電変換部と、

前記光電変換部で光電変換された電荷による信号が出力される信号線と、

前記光電変換部と前記信号線との間に接続され、前記信号を出力するための第1出力部と、

第1領域及び前記第1領域と異なる第2領域において前記第1方向及び前記第2方向に複数設けられ、前記第1出力部と前記信号線との間に接続され、前記第1出力部から出力された前記信号を前記信号線に出力するための第2出力部と、

前記第1方向に設けられた複数の前記第1出力部に接続され、前記第1出力部を制御するための第1制御線と、

前記第1方向及び前記第2方向に設けられた複数の前記第2出力部に接続され、前記第2出力部を制御するための第2制御線と、

前記第1領域に設けられた前記第2出力部及び前記第2領域に設けられた前記第2出力部の少なくとも1方から前記信号を出力させるための設定を行う設定部と、

前記第2出力部毎に設けられ、前記第2出力部に信号を出力させるための制御信号を保持する保持部と、

を有する撮像素子。

【請求項7】

第1方向及び第2方向に設けられ、光を電荷に光電変換する複数の光電変換部と、

前記光電変換部で光電変換された電荷による信号が出力される信号線と、

前記光電変換部と前記信号線との間に設けられ、前記光電変換部で光電変換された電荷による信号を出力する第1出力部と、

前記第1出力部と前記信号線との間に設けられ、前記第1出力部から出力された前記信号

10

20

30

40

50

を前記信号線に出力するための第2出力部と、

前記第1方向に設けられた複数の前記第1出力部に接続され、前記第1出力部の電源電圧

を供給するための給電線と、

前記第1方向及び前記第2方向に設けられた複数の前記第2出力部に接続され、前記第2

出力部を制御するための制御線と、

前記第2出力部毎に設けられ、前記第2出力部に信号を出力させるための制御信号を保持

する保持部と、

を有する撮像素子。

**【請求項8】**

第1方向及び第2方向に設けられ、光を電荷に光電変換する複数の光電変換部と、

前記光電変換部で光電変換された電荷による信号が出力される信号線と、

前記光電変換部と前記信号線との間に接続され、前記光電変換部で光電変換された電荷に

による信号を出力する第1出力部と、

第1領域及び前記第1領域と異なる第2領域において、前記第1方向及び前記第2方向に

複数設けられ、前記第1出力部と前記信号線との間に接続され、前記第1出力部から出力

された前記信号を前記信号線に出力するための第2出力部と、

前記第1方向及び前記第2方向に設けられた複数の前記第1出力部に接続され、前記第1

出力部の電源電圧を供給するための給電線と、

前記第1方向に設けられた複数の前記第2出力部に接続され、前記第2出力部を制御する

ための制御線と、

前記第1領域に設けられた前記第2出力部及び前記第2領域に設けられた前記第2出力部

の少なくとも1方から前記信号を出力させるための設定を行う設定部と、

前記第2出力部毎に設けられ、前記第2出力部に信号を出力させるための制御信号を保持

する保持部と、

を有する撮像素子。

**【請求項9】**

請求項6から請求項8のいずれか一項に記載の撮像素子において、

前記第1出力部は、2つ以上の光電変換部に共通して設けられる撮像素子。

**【請求項10】**

請求項1、3、6、8のうちのいずれか一項に記載の撮像素子と、

前記第1領域及び前記第2領域の少なくとも1つを指定可能な指定部と、

を備え、

前記設定部は、前記指定部で指定された前記第1領域及び前記第2領域の少なくとも1方

から前記信号を出力させるための設定を行う撮像装置。

**【請求項11】**

請求項1、3、6、8のうちのいずれか一項に記載の撮像素子と、

前記撮像素子からの前記信号に基づいて、被写体を検出する検出部と、

を備え、

前記設定部は、前記検出部により検出された被写体の位置に基づいて、前記第1領域及び

前記第2領域の少なくとも1方から前記信号を出力させるための設定を行う撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、固体撮像素子及びこれを用いた撮像装置に関するものである。

**【背景技術】**

**【0002】**

撮像装置において任意の領域を選択する領域選択技術が知られている。領域選択技術では、撮像領域のうちの複数の領域を読み出すことはできなかった。

**【先行技術文献】**

**【特許文献】**

10

20

30

40

50

**【 0 0 0 3 】**

【文献】特開平9-46600号公報

**【発明の概要】****【課題を解決するための手段】****【 0 0 0 4 】**

第1の態様による固体撮像素子は、複数の光電変換部と、前記光電変換部で光電変換された電荷による信号が出力される信号線と、前記光電変換部と前記信号線の間に設けられ、選択された前記光電変換部の前記信号を出力する第1選択部と、前記第1選択部と前記信号線の間に設けられ、前記第1選択部から出力された前記光電変換部の前記信号を前記信号線に出力する第2選択部と、を有するものである。

10

**【 0 0 0 5 】**

第2の態様による固体撮像素子は、前記第1の態様において、前記複数の光電変換部が配置されている撮像領域のうちの部分領域の前記第1選択部又は前記第2選択部を選択する領域設定部を備えるものである。

**【 0 0 0 6 】**

第3の態様による固体撮像素子は、前記第2の態様において、前記撮像領域は予め定められた複数の領域に分けられ、前記領域設定部は、前記予め定められた複数の領域の各々毎に、当該領域の前記第1選択部又は前記第2選択部を一括して選択又は非選択するための選択制御信号を供給し、前記部分領域は、前記予め定められた複数の領域の1つ以上からなるものである。

20

**【 0 0 0 7 】**

第4の態様による固体撮像素子は、前記第2の態様において、前記領域設定部は、前記第1選択部又は前記第2選択部を選択又は非選択するための選択制御信号を保持する保持部と、書き込み制御信号に応じて前記選択制御信号を前記保持部に書き込む書き込み部と、前記書き込み部に前記書き込み制御信号を供給する書き込み制御部とを有するものである。

**【 0 0 0 8 】**

第5の態様による固体撮像素子は、前記第2乃至第4のいずれかの態様において、前記部分領域が複数あり、前記複数の部分領域の各行の前記第2選択部又は前記第1選択部を選択しつつ、前記第2選択部又は前記第1選択部が選択された行に対して読み出し制御を行う制御部を備えるものである。

30

**【 0 0 0 9 】**

第6の態様による固体撮像素子は、複数の光電変換部と、前記光電変換部で光電変換された電荷による信号が出力される信号線と、前記光電変換部と前記信号線の間に設けられ、選択された前記光電変換部の前記信号を出力する選択部と、前記光電変換部と前記信号線の間に前記選択部と直列に設けられ、前記光電変換部の前記信号を出力する増幅部と、前記増幅部の電源電圧として、前記増幅部の動作に有効である有効電圧レベル又は前記動作に有効ではない非有効電圧レベルを選択的に供給する給電制御手段と、を有するものである。

**【 0 0 1 0 】**

第7の態様による固体撮像素子は、複数の光電変換部と、前記光電変換部で光電変換された電荷による信号が出力される信号線と、前記複数の光電変換部のうちの2つ以上の光電変換部に共通して設けられ、選択された前記2つ以上の光電変換部の前記信号を出力する第1選択部と、前記第1選択部と前記信号線の間に設けられ、前記第1選択部から出力された前記光電変換部の前記信号を前記信号線に出力する第2選択部と、を有するものである。

40

**【 0 0 1 1 】**

第8の態様による固体撮像素子は、前記第7の態様において、前記複数の光電変換部が配置されている撮像領域のうちの部分領域の前記第1選択部又は前記第2選択部を選択する領域設定部を備えるものである。

**【 0 0 1 2 】**

50

第9の態様による固体撮像素子は、前記第8の態様において、前記撮像領域は予め定められた複数の領域に分けられ、前記領域設定部は、前記予め定められた複数の領域の各々毎に、当該領域の前記第1選択部又は前記第2選択部を一括して選択又は非選択するための選択制御信号を供給し、前記部分領域は、前記予め定められた複数の領域の1つ以上からなるものである。

【0013】

第10の態様による固体撮像素子は、前記第8の態様において、前記領域設定部は、前記第1選択部又は前記第2選択部を選択又は非選択するための選択制御信号を保持する保持部と、書き込み制御信号に応じて前記選択制御信号を前記保持部に書き込む書き込み部と、前記書き込み部に前記書き込み制御信号を供給する書き込み制御部とを有するものである。

10

【0014】

第11の態様による固体撮像素子は、前記第8乃至第10のいずれかの態様において、前記部分領域が複数あり、前記複数の部分領域の各行の前記第2選択部又は前記第1選択部を選択しつつ、前記第2選択部又は前記第1選択部が選択された行に対して読み出し制御を行う制御部を備えるものである。

【0015】

第12の態様による固体撮像素子は、複数の光電変換部と、前記光電変換部で光電変換された電荷による信号が出力される信号線と、前記複数の光電変換部のうちの2つ以上の光電変換部に共通して設けられ、選択された前記2つ以上の光電変換部の前記信号を出力する選択部と、前記2つ以上の光電変換部と前記信号線の間に前記選択部と直列に設けられ、前記2つ以上の光電変換部の前記信号を出力する增幅部と、前記增幅部の電源電圧として、前記增幅部の動作に有効である有効電圧レベル又は前記動作に有効ではない非有効電圧レベルを選択的に供給する給電制御手段と、を有するものである。

20

【0016】

第13の態様による撮像装置は、前記第2乃至第5及び第8乃至第11のいずれかの態様による固体撮像素子と、使用者が前記部分領域を指令するためのユーザインターフェースと、を備え、前記ユーザインターフェースによる指示に応じて前記部分領域が設定されるものである。

【0017】

第14の態様による撮像装置は、前記第2乃至第5及び第8乃至第11のいずれかの態様による固体撮像素子と、前記固体撮像素子からの画像信号に基づいて、前記撮像領域における複数の撮像対象の位置を検出する検出部と、を備え、前記検出部により検出された前記位置に応じて前記部分領域が設定されるものである。

30

【発明の効果】

【0018】

本発明によれば、撮像領域のうちの所望の複数の部分領域を高速に読み出すことができる固体撮像素子及びこれを用いた撮像装置を提供することができる。

【図面の簡単な説明】

【0019】

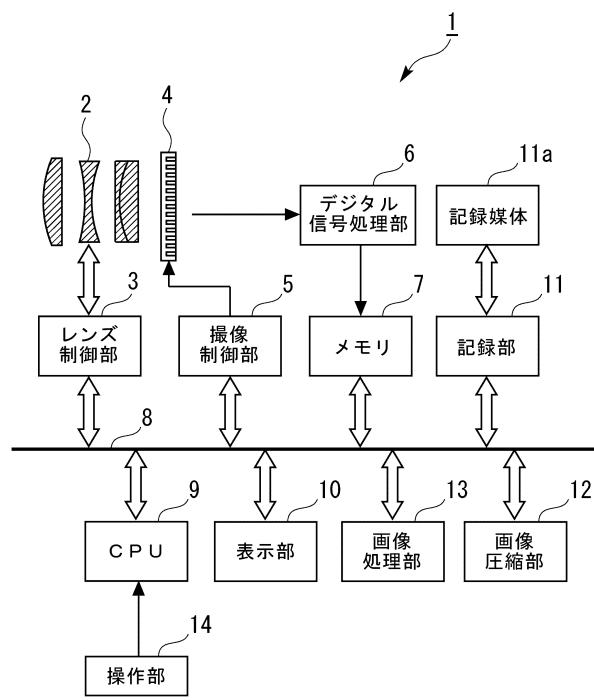

【図1】本発明の第1の実施の形態による電子カメラを示す概略ブロック図である。

40

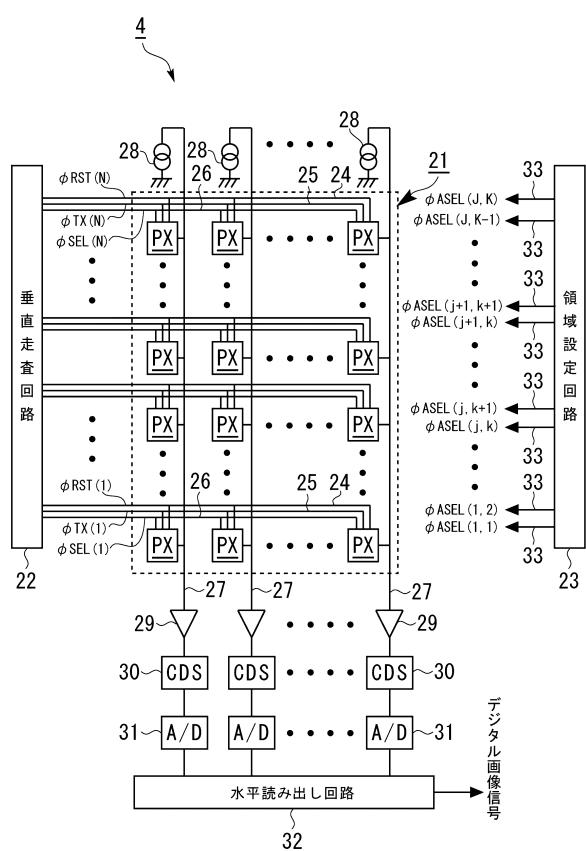

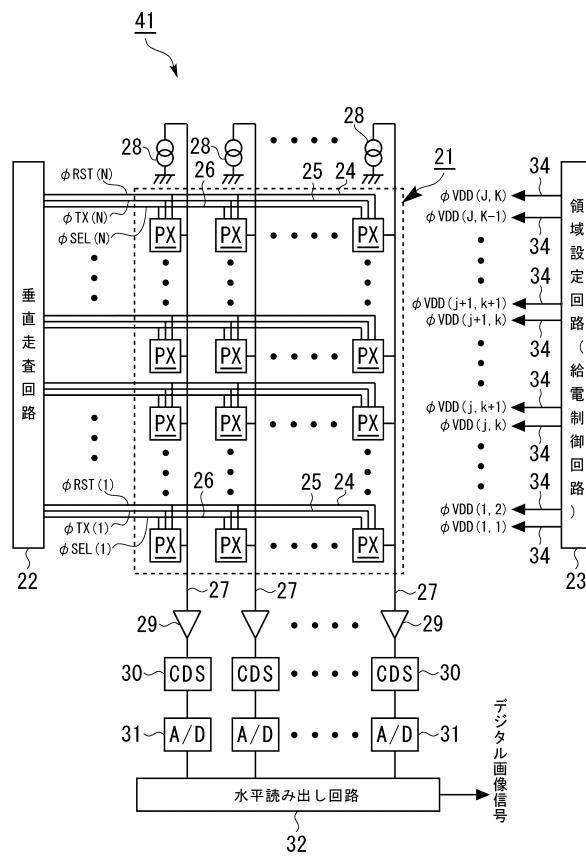

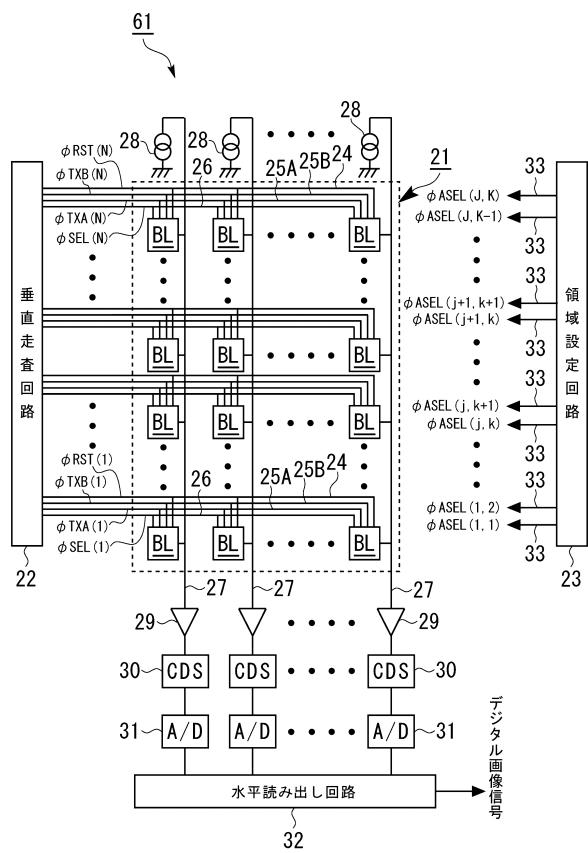

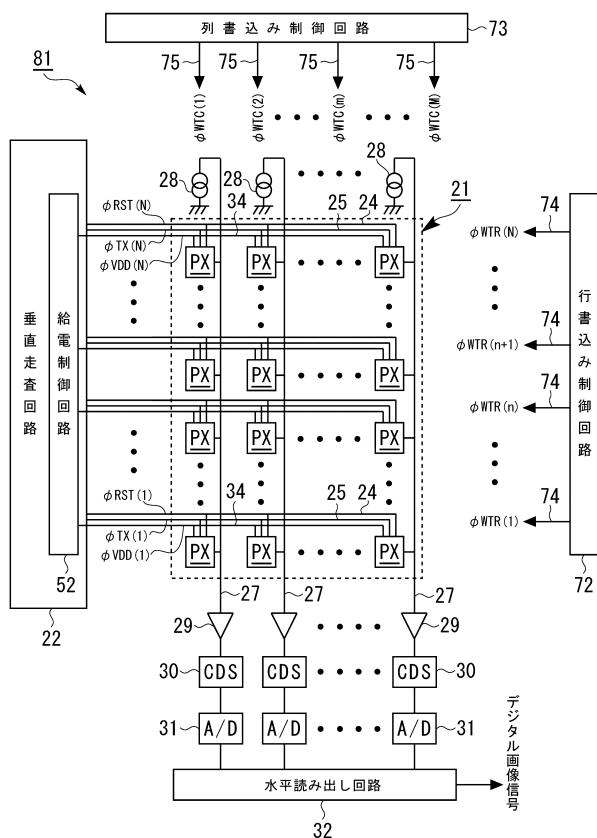

【図2】図1中の固体撮像素子の概略構成を示す回路図である。

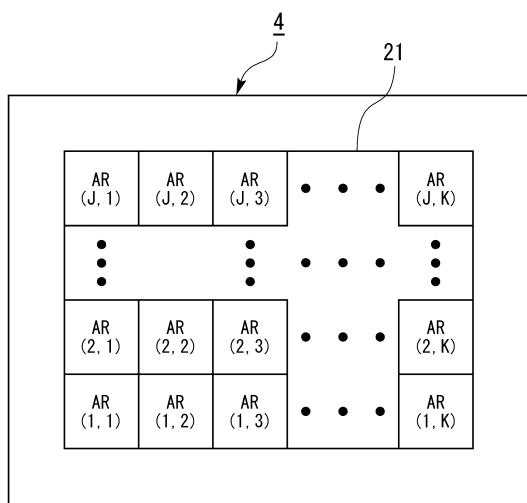

【図3】図1中の固体撮像素子を模式的に示す概略平面図である。

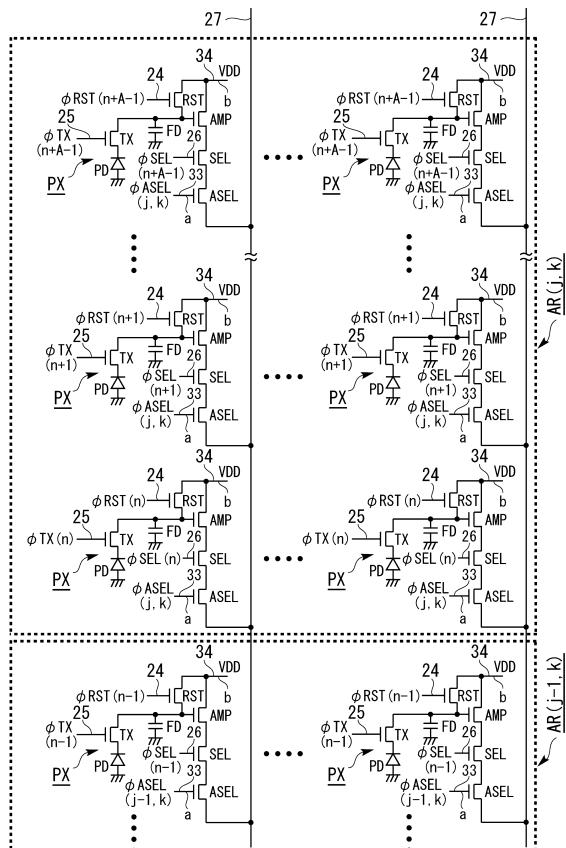

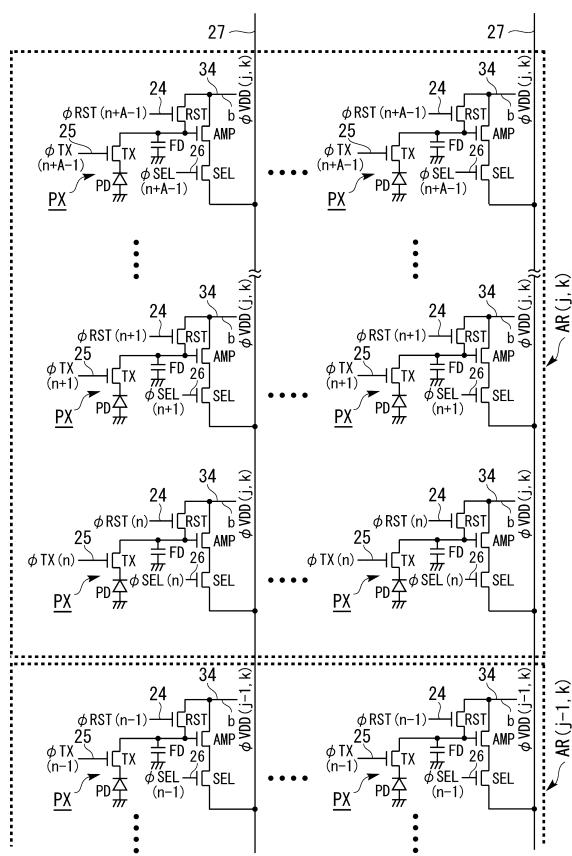

【図4】図1中の固体撮像素子の撮像領域の一部をなす既定部分領域を示す回路図である。

【図5】図4に示す回路を抽象化して示す回路図である。

【図6】図1中の固体撮像素子の撮像領域のうちの読み出す部分領域の設定例を模式的に示す図である。

【図7】図1中の固体撮像素子において図6に示す設定例を実現する選択制御信号を示す図である。

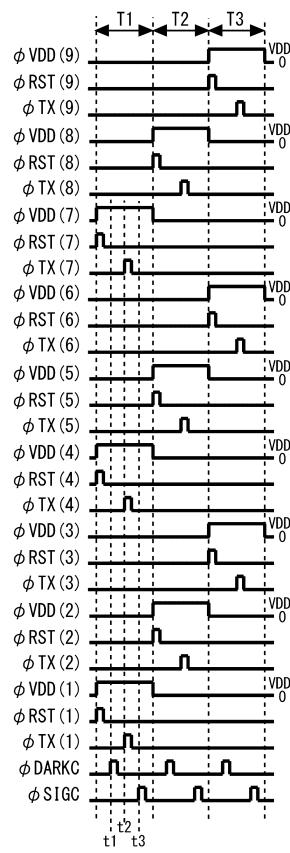

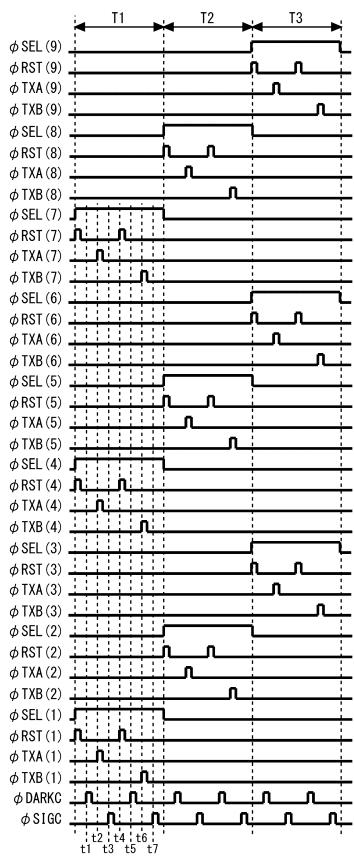

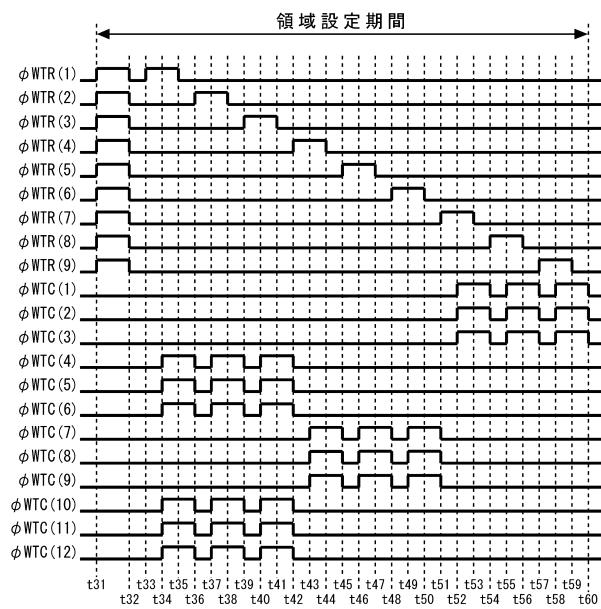

【図8】図1中の固体撮像素子の部分領域撮影モード時の読み出し制御の一例を示すタイミングチャートである。

50

【図 9】図 1 中の固体撮像素子の撮像領域のうちの読み出す部分領域の他の設定例を模式的に示す図である。

【図 10】図 1 中の固体撮像素子において図 9 に示す設定例を実現する選択制御信号を示す図である。

【図 11】図 1 中の固体撮像素子の撮像領域のうちの読み出す部分領域の更に他の設定例を模式的に示す図である。

【図 12】図 11 に示す設定例を実現する選択制御信号を示す図である。

【図 13】図 1 中の固体撮像素子の部分領域撮影モード時の読み出し制御の他の例を示すタイミングチャートである。

【図 14】図 1 中の固体撮像素子の全領域撮影モード時の読み出し制御の一例を示すタイミングチャートである。 10

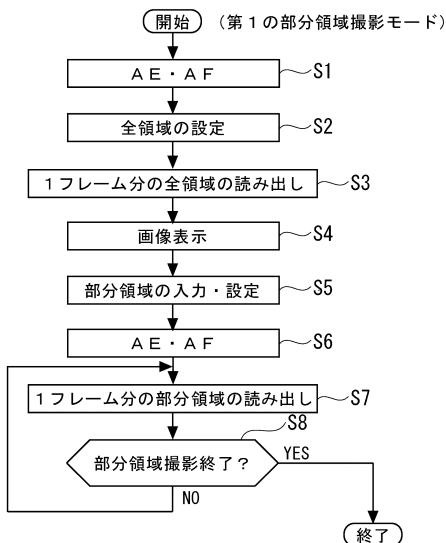

【図 15】図 1 に示す電子カメラの第 1 の部分領域撮影モード時の動作の一例を示す概略フロー チャートである。

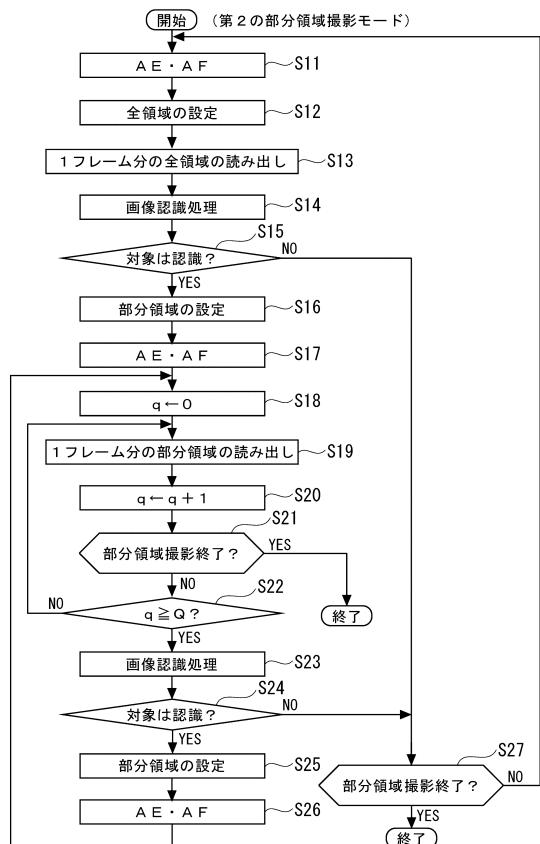

【図 16】図 1 に示す電子カメラの第 2 の部分領域撮影モード時の動作の一例を示す概略フロー チャートである。

【図 17】本発明の第 2 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。

【図 18】図 17 に示す固体撮像素子の撮像領域の一部をなす既定部分領域を示す回路図である。 20

【図 19】図 18 に示す回路を抽象化して示す回路図である。

【図 20】図 17 に示す固体撮像素子において図 6 に示す設定例と同じ設定を実現する電源電圧信号を示す図である。

【図 21】本発明の第 3 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。

【図 22】図 21 に示す固体撮像素子の撮像領域の一部をなす既定部分領域を示す回路図である。

【図 23】図 21 に示す固体撮像素子の部分領域撮影モード時の読み出し制御の一例を示すタイミングチャートである。

【図 24】本発明の第 4 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。 30

【図 25】図 24 に示す固体撮像素子の撮像領域の一部をなす既定部分領域を示す回路図である。

【図 26】図 25 に示す回路を抽象化して示す回路図である。

【図 27】図 24 に示す固体撮像素子の部分領域撮影モード時の読み出し制御の一例を示すタイミングチャートである。

【図 28】本発明の第 5 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。

【図 29】図 28 に示す固体撮像素子の撮像領域の一部を示す回路図である。

【図 30】図 28 に示す固体撮像素子においてコンデンサに H 信号を書き込む場合及び L 信号を書き込む場合の書き込み制御信号を示すタイミングチャートである。 40

【図 31】図 28 に示す固体撮像素子において図 6 に示す設定例と同じ設定を実現する書き込み制御信号を示すタイミングチャートである。

【図 32】本発明の第 6 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。

【図 33】図 32 に示す固体撮像素子の撮像領域の一部を示す回路図である。

【図 34】本発明の第 7 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。

【図 35】図 34 に示す固体撮像素子の撮像領域の一部を示す回路図である。

【図 36】本発明の第 8 の実施の形態による電子カメラで用いられる固体撮像素子の概略構成を示す回路図である。 50

【図37】図36に示す固体撮像素子の1つの画素を示す回路図である。

【図38】図36に示す固体撮像素子において図6に示す設定例と同じ設定を実現する書き込み制御信号を示すタイミングチャートである。

【発明を実施するための形態】

【0020】

以下、本発明による固体撮像素子及び撮像装置について、図面を参照して説明する。

【0021】

【第1の実施の形態】

【0022】

図1は、本発明の第1の実施の形態による撮像装置としての電子カメラ1を示す概略プロ

10

ック図である。

【0023】

本実施の形態による電子カメラ1は、例えば一眼レフのデジタルカメラとして構成されるが、本発明による撮像装置は、これに限らず、コンパクトカメラなどの他の電子カメラや、携帯電話に搭載された電子カメラや、動画を撮像するビデオカメラ等の電子カメラや、監視用の動画を撮像する監視カメラや、顕微鏡に組み込まれ顕微鏡像を撮像する撮像装置や、望遠鏡に組み込まれ望遠鏡像を撮像する撮像装置などの種々の撮像装置に適用することができる。

【0024】

電子カメラ1には、撮影レンズ2が装着される。この撮影レンズ2は、レンズ制御部3によってフォーカスや絞りが駆動される。この撮影レンズ2の像空間には、固体撮像素子4の撮像面が配置される。

20

【0025】

固体撮像素子4は、撮像制御部5の指令によって駆動され、デジタルの画像信号を出力する。静止画撮影時などでは、撮像制御部5は、例えば、全画素を同時にリセットするいわゆるグローバルリセット後に、図示しないメカニカルシャッタで露光した後に、所定の読み出し動作を行うように固体撮像素子4を制御する。また、電子ビューファインダーモード時や動画撮影時（後述する第1及び第2の部分領域撮影モード時や全領域撮影モード時等）などでは、撮像制御部5は、例えばいわゆるローリング電子シャッタを行いつつ所定の読み出し動作を行うように固体撮像素子4を制御する。デジタル信号処理部6は、固体撮像素子4から出力されるデジタルの画像信号に対して、デジタル増幅、色補間処理、ホワイトバランス処理などの画像処理等を行う。デジタル信号処理部6による処理後の画像信号は、メモリ7に一旦蓄積される。メモリ7は、バス8に接続されている。バス8には、レンズ制御部3、撮像制御部5、CPU9、液晶表示パネル等の表示部10、記録部11、画像圧縮部12及び画像処理部13なども接続される。CPU9には、レリーズ釦などの操作部14が接続される。記録部11には記録媒体11aが着脱自在に装着される。

30

【0026】

電子カメラ1内のCPU9は、操作部14の操作により電子ビューファインダーモードや動画撮影や静止画撮影などが指示されると、それに合わせて撮像制御部5を駆動する。このとき、レンズ制御部3によって、フォーカスや絞りが適宜調整される。固体撮像素子4は、撮像制御部5の指令によって駆動され、デジタルの画像信号を出力する。固体撮像素子4からのデジタルの画像信号は、デジタル信号処理部6で処理された後に、メモリ7に蓄積される。CPU9は、電子ビューファインダーモード時にはその画像信号を表示部10に画像表示させ、動画撮影時にはその画像信号を記録媒体11aに記録する。静止画撮影時などの場合は、CPU9は、固体撮像素子4からのデジタルの画像信号がデジタル信号処理部6で処理されてメモリ7に蓄積された後に、操作部14の指令に基づき、必要に応じて画像処理部13や画像圧縮部12にて所望の処理を行い、記録部11に処理後の信号を出力させ記録媒体11aに記録する。

40

【0027】

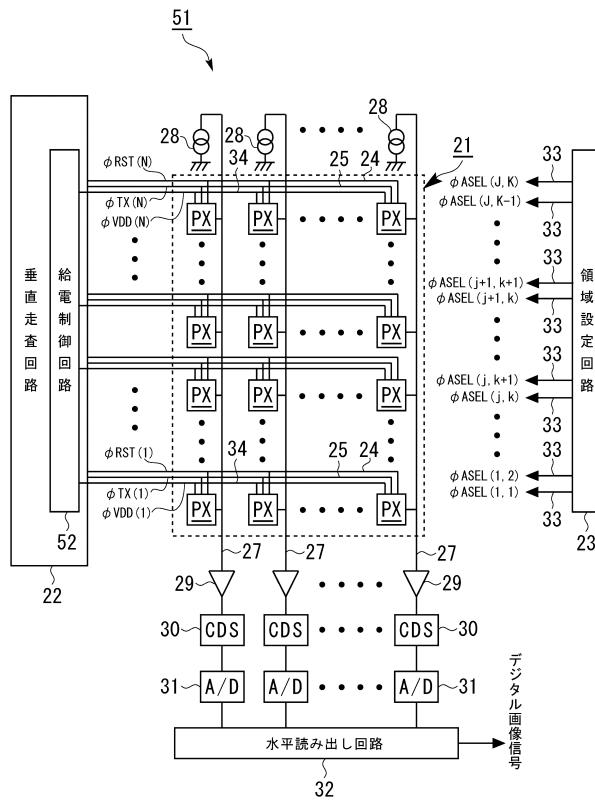

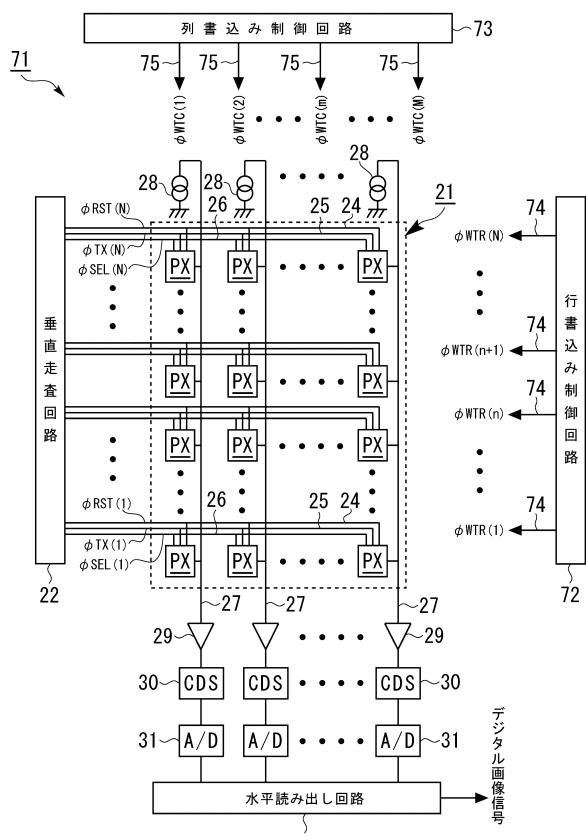

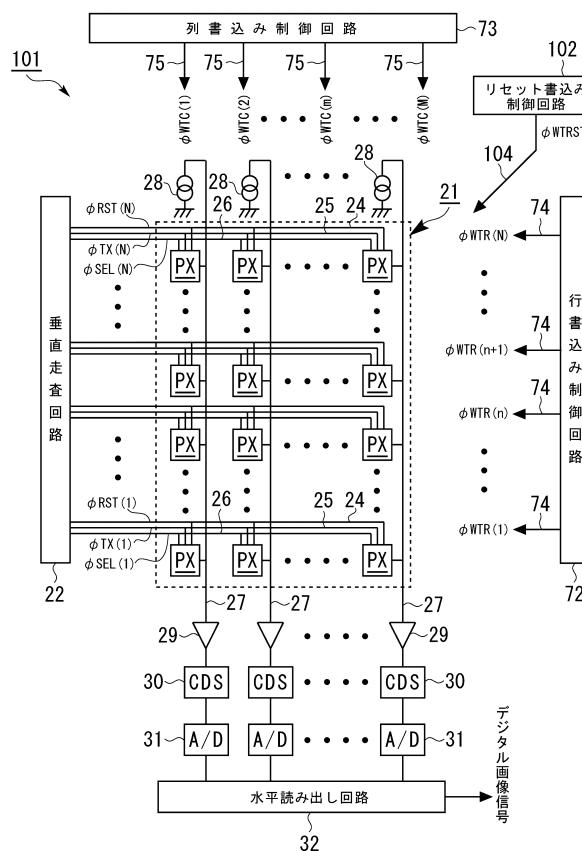

図2は、図1中の固体撮像素子4の概略構成を示す回路図である。本実施の形態では、固

50

体撮像素子 4 は、 C M O S 型の固体撮像素子として構成されているが、例えば、他の X Y アドレス型固体撮像素子として構成してもよい。

【 0 0 2 8 】

固体撮像素子 4 は、撮像領域 2 1 において N 行 M 列に 2 次元マトリクス状に配置された画素 P X と、垂直走査回路 2 2 と、領域設定回路 2 3 と、画素 P X の行毎に設けられた制御線 2 4 ~ 2 6 と、画素 P X の列毎に設けられ対応する列の画素 P X からの信号を受け取る複数の ( M 本の ) 垂直信号線 2 7 と、各垂直信号線 2 7 に設けられた定電流源 2 8 と、各垂直信号線 2 7 に対応して設けられたカラムアンプ 2 9 、 C D S 回路 ( 相関 2 重サンプリング回路 ) 3 0 及び A / D 変換器 3 1 と、水平読み出し回路 3 2 と、撮像領域 2 1 の既定部分領域 A R ( 後述する図 3 参照 ) 每に設けられた制御線 3 3 とを有している。既定部分領域 A R は、撮像領域 2 1 の予め定められた一部の領域 ( 部分領域 ) である。

10

【 0 0 2 9 】

なお、カラムアンプ 2 9 として、アナログ増幅器を用いてもよいし、いわゆるスイッチトキャパシタアンプを用いてもよい。また、カラムアンプ 2 9 は、必ずしも設けなくてもよい。

【 0 0 3 0 】

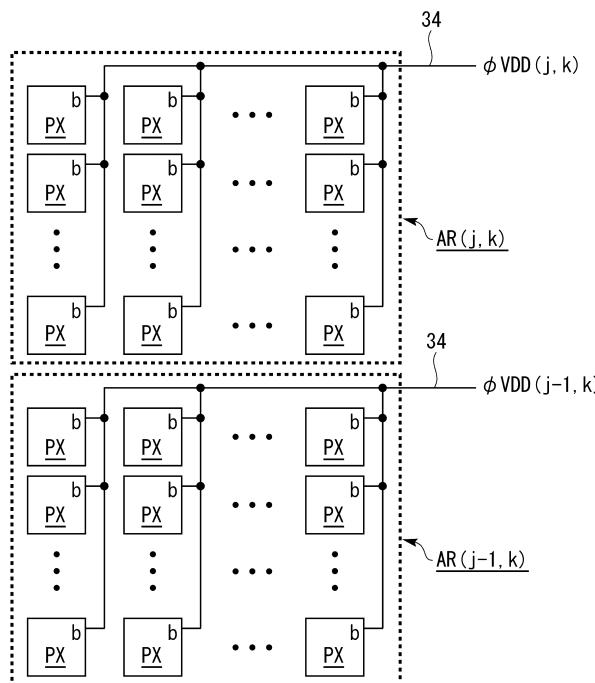

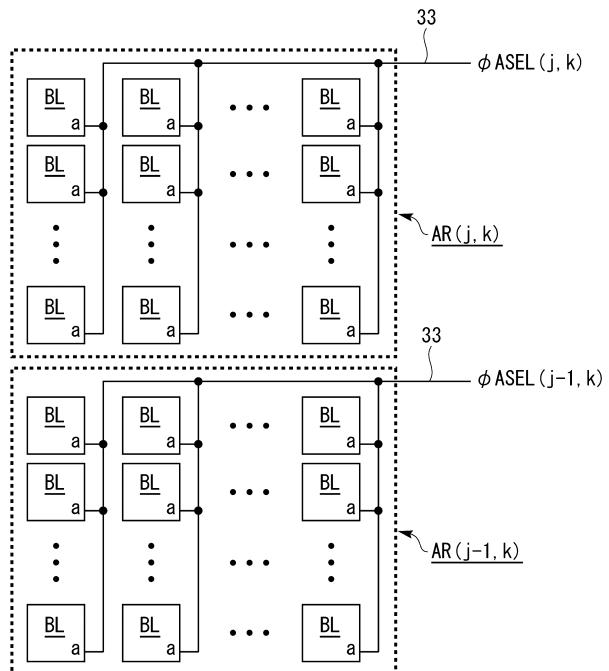

図 3 は、図 1 中の固体撮像素子 4 ( 特にその撮像領域 2 1 ) を模式的に示す概略平面図である。本実施の形態では、図 3 に示すように、固体撮像素子 4 の撮像領域 2 1 は、マトリクス状に配置され予め定められた J 行 K 列の  $J \times K$  個の既定部分領域 A R に分けられている。各既定部分領域 A R を区別する場合、 j 行目かつ k 列目の既定部分領域 A R は符号 A R ( j , k ) で示す。各既定部分領域 A R は、図 4 及び図 5 に示すように、 A 行 B 列の A × B 個 ( A は 2 以上の整数、 B は 1 以上の整数 ) の画素 P X からなる。本実施の形態では、各既定部分領域 A R の大きさ ( 画素 P X の行数 A 及び列数 B ) は互いに同じになっているが、本発明ではこれに限らない。ただし、各既定部分領域 A R の画素 P X の行数 A は互いに同じであることが好ましい。

20

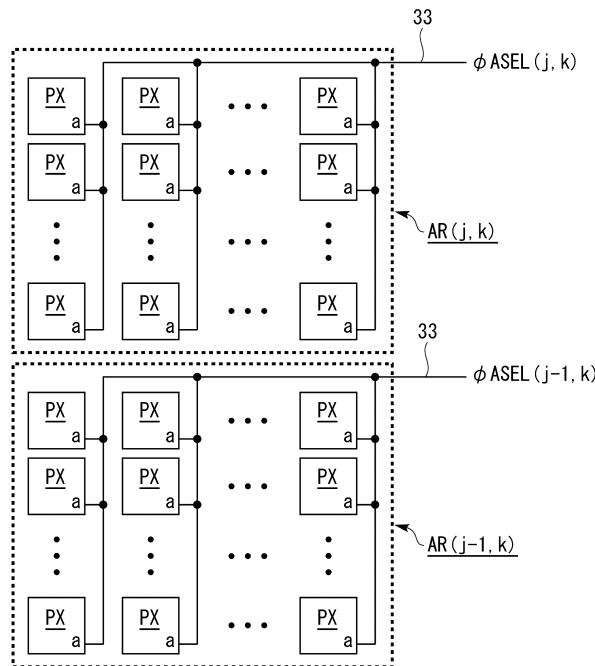

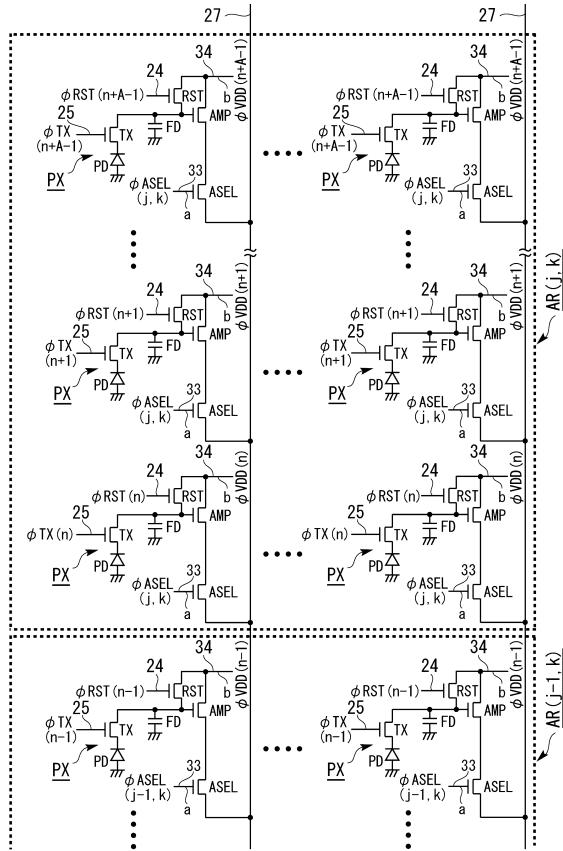

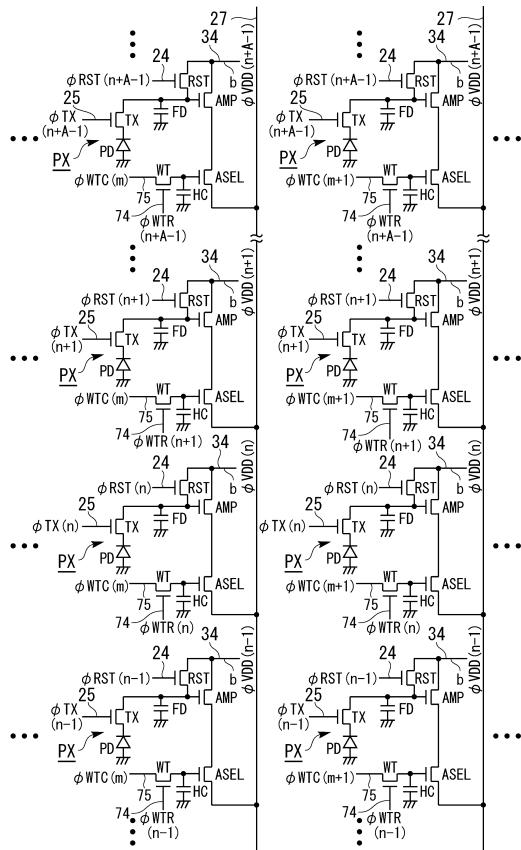

【 0 0 3 1 】

図 4 は、図 1 中の固体撮像素子 4 の撮像領域 2 1 の一部をなす既定部分領域 A R を示す回路図である。図 4 では、 j 行目かつ k 列目の既定部分領域 A R ( j , k ) と、これに隣接する j - 1 行目かつ k 列目の既定部分領域 A R ( j - 1 , k ) の一部を示している。既定部分領域 A R ( j , k ) は、 n 行目から ( n + A - 1 ) 行目までに並んだ A 行かつ B 列の A × B 個の画素 P X からなる。図 4 では、図面表記の便宜上、各制御線 2 4 ~ 2 6 , 3 3 及び後述する給電線 3 4 の接続状態は示していないが、各制御線 2 4 ~ 2 6 は画素 P X の行毎に共通に接続され、制御線 3 3 は既定部分領域 A R 每に共通に接続され、給電線 3 4 は全画素 P X に共通に接続されている。

30

【 0 0 3 2 】

本実施の形態では、いずれの画素 P X も同一の回路構成を有している。本実施の形態では、各画素 P X は、一般的な C M O S イメージセンサと異なり、当該画素 P X を選択するための選択トランジスタを 2 つ ( S E L , A S E L ) 有しているが、各画素 P X のその他の構成は、一般的な C M O S イメージセンサと同様である。

40

【 0 0 3 3 】

すなわち、各画素 P X は、図 4 に示すように、入射光に応じた電荷を生成し蓄積する光電変換部としてのフォトダイオード P D と、前記電荷を受け取って前記電荷を電圧に変換する電荷電圧変換部としてのフローティング容量部 F D と、フローティング容量部 F D の電位に応じた信号を当該画素 P X の出力信号として出力する増幅部としての増幅トランジスタ A M P と、フォトダイオード P D からフローティング容量部 F D に電荷を転送する転送トランジスタ T X と、フローティング容量部 F D の電位をリセットするリセットトランジスタ R S T と、当該画素 P X を選択するための第 1 の選択部としての選択スイッチをなす選択トランジスタ S E L と、当該画素 P X を選択するための第 2 の選択部としての選択スイッチをなす選択トランジスタ A S E L を有し、図 4 に示すように接続されている。本実施の形態では、全画素 P X の増幅トランジスタ A M P のドレイン ( 図 4 中の b 点 ) は、給

50

電線 3 4 により共通に接続され、そこには、増幅トランジスタ A M P の電源電圧として、増幅トランジスタ A M P の動作に有効である有効電圧レベル V D D が固定的に供給される。この有効電圧レベル V D D は、給電線 3 4 により、各画素 P X のリセットトランジスタ R S T のドレインにも供給されている。なお、図 2 において、給電線 3 4 の図示は省略している。

#### 【 0 0 3 4 】

本実施の形態では、各画素 P X の出力信号は、当該画素 P X の前記第 1 及び第 2 の選択部が両方とも選択状態である場合にのみ、当該画素 P X の出力信号及び当該画素 P X に対して列方向に並んだ画素 P X の出力信号を受け取る垂直信号線 2 7 に出力される。これは、具体的には、本実施の形態では、各画素 P X において、増幅トランジスタ A M P のソースと当該画素 P X に対応する垂直信号線 2 7 との間に、選択トランジスタ S E L , A S E L が直列に接続されることによって、実現されている。選択トランジスタ S E L , A S E L が両方ともオンしている（選択状態である）場合にのみ、当該画素 P X の出力信号が垂直信号線 2 7 に出力される。なお、増幅トランジスタ A M P と垂直信号線 2 7 との間ににおける選択トランジスタ S E L 及び選択トランジスタ A S E L の接続順序は、図 4 に示す順序と逆でもよい。

10

#### 【 0 0 3 5 】

図面には示していないが、本実施の形態では、各々の画素 P X のフォトダイオード P D の光入射側には、それぞれが異なる色成分の光を透過させる複数種類のカラーフィルタが、所定の色配列（例えば、ペイヤー配列）で配置されている。画素 P X は、カラーフィルタでの色分解によって各色に対応する電気信号を出力する。

20

#### 【 0 0 3 6 】

なお、本実施の形態では、トランジスタ T X , A M P , R S T , S E L , A S E L は、全て n M O S トランジスタである。

#### 【 0 0 3 7 】

転送トランジスタ T X のゲートは画素 P X の行毎に制御線 2 5 に共通に接続され、そこには、制御信号 T X が垂直走査回路 2 2 から供給される。リセットトランジスタ R S T のゲートは画素 P X の行毎に制御線 2 4 に共通に接続され、そこには、制御信号 R S T が垂直走査回路 2 2 から供給される。選択トランジスタ S E L のゲートは行毎に制御線 2 6 に共通に接続され、そこには、制御信号 S E L が垂直走査回路 2 2 から供給される。各制御信号 T X を行毎に区別する場合、n 行目の画素 P X の転送トランジスタ T X のゲートに供給される制御信号 T X は符号 T X ( n ) で示す。この点は、他の制御信号 R S T , S E L についても同様である。

30

#### 【 0 0 3 8 】

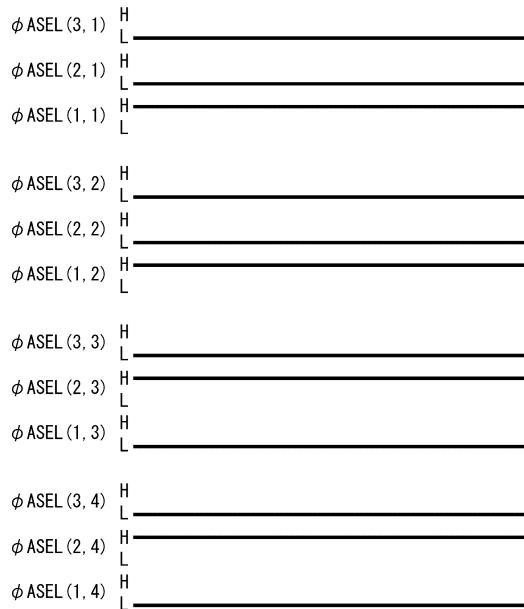

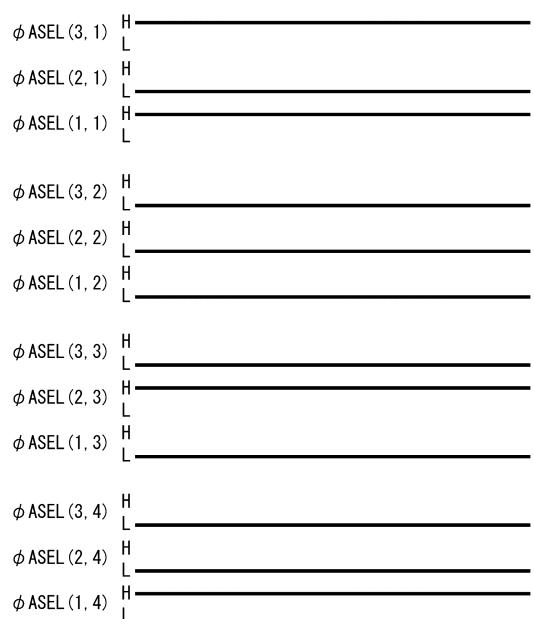

選択トランジスタ A S E L のゲート（図 4 中の a 点）は既定部分領域 A R 每に制御線 3 3 に共通に接続され、そこには、制御信号 A S E L が領域設定回路 2 3 から供給される。図 5 は、図 4 に示す回路を、制御線 3 3 による各既定部分領域 A R の選択トランジスタ A S E L のゲート（a 点）の接続関係に着目して抽象化して示したものである。各制御信号 A S E L を既定部分領域 A R 每に区別する場合、j 行目かつ k 列目の既定部分領域 A R ( j , k ) の画素 P X の選択トランジスタ A S E L のゲートに供給される制御信号 A S E L は符号 A S E L ( j , k ) で示す。なお、領域設定回路 2 3 の配置や制御線 3 3 の実際の配置（引き回す経路等）は、何ら限定されるものではない。

40

#### 【 0 0 3 9 】

領域設定回路 2 3 は、図 1 中の撮像制御部 5 による制御下で、撮像領域 2 1 のうちの既定部分領域 A R の各々毎に、当該既定部分領域 A R の画素 P X の前記第 2 の選択部としての選択トランジスタ A S E L を一括して選択状態又は非選択状態にするための選択制御信号としての制御信号 A S E L を供給する。これにより、領域設定回路 2 3 は、撮像領域 2 1 のうちの画素 P X の出力信号を読み出す領域として、選択トランジスタ A S E L を選択状態にした既定部分領域 A R を、設定する。

#### 【 0 0 4 0 】

50

垂直走査回路 22 は、図 1 中の撮像制御部 5 による制御下で、画素 P X の行毎に、制御信号 TX, RST, SEL をそれぞれ出力し、領域設定回路 23 による領域設定動作と相俟って、静止画読み出し動作や、後述する第 1 及び第 2 の部分領域撮影モード等の動画読み出し動作などを実現する。この制御によって、領域設定回路 23 により設定された領域の画素 P X の信号（アナログ信号）が、それに対応する垂直信号線 27 に供給される。

【 0 0 4 1 】

垂直信号線 27 に読み出された信号は、各列毎に、カラムアンプ 29 で増幅され更に CDS 回路 30 にて光信号（画素 P X で光電変換された光情報を含む信号）と暗信号（光信号から差し引くべきノイズ成分を含む差分用信号）との差分を得る処理が施された後に、A/D 変換器 31 にてデジタル信号に変換され、そのデジタル信号は A/D 変換器 31 に保持される。各 A/D 変換器 31 に保持されたデジタルの画像信号は、水平読み出し回路 32 によって水平走査され、必要に応じて所定の信号形式に変換されて、外部（図 1 中のデジタル信号処理部 6）へ出力される。

10

【 0 0 4 2 】

なお、CDS 回路 30 は、図 1 中の撮像制御部 5 による制御下でタイミング発生回路（図示せず）から暗信号サンプリング信号 DARKC を受け、DARKC がハイレベル（H）からローレベル（L）に切り換わるタイミングでカラムアンプ 29 の出力信号を暗信号としてサンプリングするとともに、図 1 中の撮像制御部 5 による制御下で前記タイミング発生回路から光信号サンプリング信号 SIGC を受け、SIGC がハイレベルからローレベルに切り換わるタイミングでカラムアンプ 29 の出力信号を光信号としてサンプリングする。そして、CDS 回路 30 は、前記タイミング発生回路からのクロックやパルスに基づいて、サンプリングした暗信号と光信号との差分に応じた信号を出力する。このような CDS 回路 30 の構成としては、公知の構成を採用することができる。

20

【 0 0 4 3 】

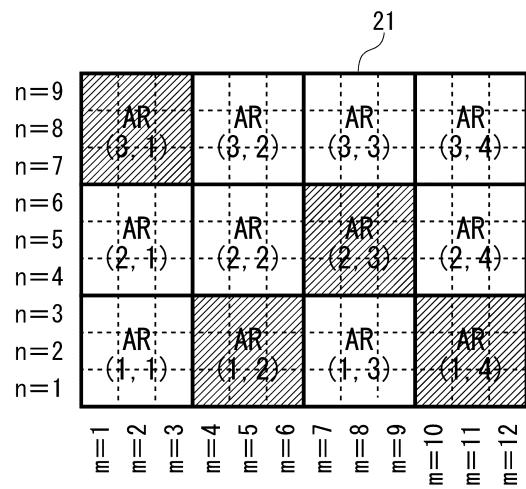

図 6 は、部分領域撮影モードにおいて、固体撮像素子 4 の撮像領域 21 のうちの読み出す部分領域の設定例を模式的に示す図である。部分領域撮影モードは、固体撮像素子 4 の撮像領域 21 のうちの所望の 1 つ又は所望の複数の部分領域の画素 P X の出力信号を選択的に読み出す動作モードである。理解を容易にするため、図 6 では、N = 9、M = 12、A = 3 及び B = 3 であるものとし、撮像領域 21 が 9 行 12 列の 9 × 12 個の画素 P X からなり、各既定部分領域 AR が 3 行 3 列の画素 P X からなるものとしている。N, M, A, B の値が他の値であっても、以下の説明は同様に適合する。

30

【 0 0 4 4 】

図 6 において、読み出す 4 つの部分領域として設定された既定部分領域 AR (3, 1), AR (1, 2), AR (2, 3), AR (1, 4) には、ハッチングを付している。本例では、読み出す各 1 つの部分領域は、1 つの既定部分領域 AR からなる。

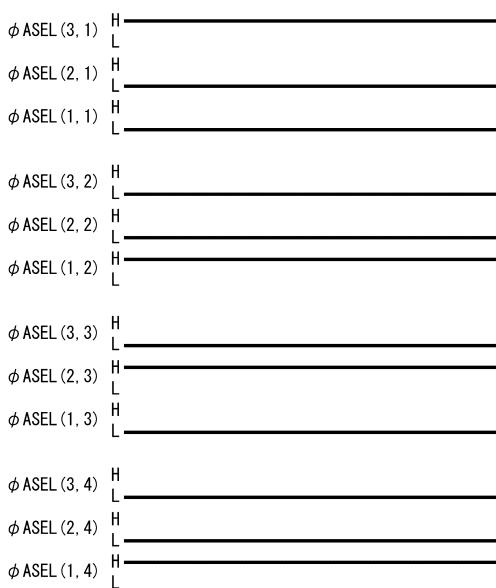

【 0 0 4 5 】

図 7 は、図 1 中の固体撮像素子 4 において図 6 に示す設定例を実現する選択制御信号 ASEL を示している。既定部分領域 AR (3, 1), AR (1, 2), AR (2, 3), AR (1, 4) の選択トランジスタ ASEL のゲートに供給される選択制御信号 ASEL (3, 1), ASEL (1, 2), ASEL (2, 3), ASEL (1, 4) はハイレベル（H）に維持され、他の選択制御信号 ASEL はローレベル（L）に維持される。これにより、既定部分領域 AR (3, 1), AR (1, 2), AR (2, 3), AR (1, 4) の選択トランジスタ ASEL がオンに維持される一方で、他の既定部分領域 AR の選択トランジスタ ASEL はオフに維持される。

40

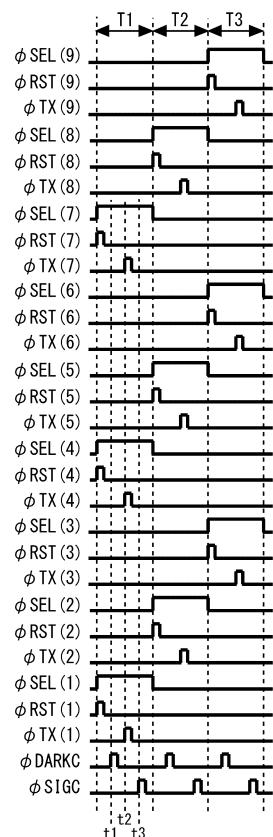

【 0 0 4 6 】

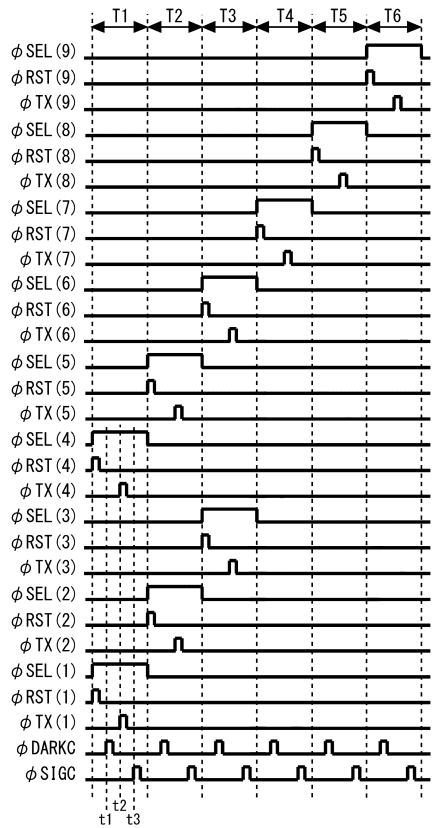

本実施の形態では、部分領域撮影モードにおいて、読み出す部分領域が図 6 に示すように設定される場合には、例えば、図 8 に示すように読み出し制御が行われる。図 8 は、図 1 中の固体撮像素子 4 の部分領域撮影モード時の読み出し制御の一例を示すタイミングチャートである。

【 0 0 4 7 】

50

図 8 に示す例では、垂直走査回路 2 2 によって、期間 T 1 において、各既定部分領域 A R における 1 行目の画素 P X の行に相当する撮像領域 2 1 における 1 行目、4 行目及び 7 行目の画素 P X の行について同時に読み出し制御が行われ、その次の期間 T 2 において、各既定部分領域 A R における 2 行目の画素 P X の行に相当する撮像領域 2 1 における 2 行目、5 行目及び 8 行目の画素 P X の行について同時に読み出し制御が行われ、その次の期間 T 3 において、各既定部分領域 A R における 3 行目の画素 P X の行に相当する撮像領域 2 1 における 3 行目、6 行目及び 9 行目の画素 P X の行について同時に読み出し制御が行われ、これにより 1 フレーム分の読み出しが終了する。期間 T 1 ~ T 3 を順次繰り返すことで、複数のフレームがローリング電子シャッタにより読み出される。例えば、1 行目の画素 P X の露光期間は、1 行目の制御信号 T X ( 1 ) が前回ハイレベルからローレベルになった時点から制御信号 T X ( 1 ) が今回ハイレベルからローレベルになった時点までの期間となる。各期間 T 1 ~ T 3 の読み出し制御について、以下に詳述する。

#### 【 0 0 4 8 】

各期間 T 1 ~ T 3 の開始直前には、全ての行の画素 P X のトランジスタ S E L , R S T , T X はオフしている。

#### 【 0 0 4 9 】

期間 T 1 において、1 行目の S E L ( 1 ) 、4 行目の S E L ( 4 ) 及び 7 行目の S E L ( 7 ) がハイレベルにされ、1 行目、4 行目及び 7 行目の画素 P X の選択トランジスタ S E L ( 1 ) , S E L ( 4 ) , S E L ( 7 ) がオンにされ、1 行目、4 行目及び 7 行目の画素 P X が選択される。ところが、今は図 6 に示す設定例が実現されるように選択制御信号 A S E L が図 7 に示すようになっているので、1 行目の画素 P X のうちのハッチングが付されている列 ( 4 列目乃至 6 列目、10 列目乃至 12 列目 ) の画素 P X の選択トランジスタ A S E L がオンし、1 行目の画素 P X のうちのハッチングが付されていない列 ( 1 列目乃至 3 列目、7 列目乃至 9 列目 ) の画素 P X の選択トランジスタ A S E L がオフしている。また、4 行目の画素 P X のうちのハッチングが付されている列 ( 7 列目乃至 9 列目 ) の画素 P X の選択トランジスタ A S E L がオンし、4 行目の画素 P X のうちのハッチングが付されていない列 ( 1 列目乃至 6 列目、10 列目乃至 12 列目 ) の画素 P X の選択トランジスタ A S E L がオフしている。さらに、7 行目の画素 P X のうちのハッチングが付されている列 ( 1 列目乃至 3 列目 ) の画素 P X の選択トランジスタ A S E L がオンし、7 行目の画素 P X のうちのハッチングが付されていない列 ( 4 列目乃至 12 列目 ) の画素 P X の選択トランジスタ A S E L がオフしている。

#### 【 0 0 5 0 】

したがって、期間 T 1 において、選択トランジスタ S E L , A S E L の両方がオンしている画素 P X ( 1 行目における 4 列目乃至 6 列目及び 10 列目乃至 12 列目の画素 P X 、4 行目における 7 列目乃至 9 列目の画素 P X 、7 行目における 1 列目乃至 3 列目の画素 P X ) のみの出力信号が、対応する垂直信号線 2 7 に出力し得る状態となっている。

#### 【 0 0 5 1 】

期間 T 1 の開始直後から一定時間だけ、1 行目、4 行目及び 7 行目の制御信号 R S T ( 1 ) , R S T ( 4 ) , R S T ( 7 ) がハイレベルにされ、1 行目、4 行目及び 7 行目の画素 P X のリセットトランジスタ R S T が一旦オンにされ、フローティング容量部 F D の電位 ( 増幅トランジスタ A M P のゲートの電位 ) が一旦電圧レベル V D D にリセットされる。

#### 【 0 0 5 2 】

期間 T 1 中のその後の時点 t 1 から一定期間だけ、暗信号サンプリング信号 D A R K C がハイレベルにされることによって、1 行目における 4 列目乃至 6 列目及び 10 列目乃至 12 列目の画素 P X 、4 行目における 7 列目乃至 9 列目の画素 P X 、及び、7 行目における 1 列目乃至 3 列目の画素 P X の増幅トランジスタ A M P のゲートに現れる電位が、当該画素 P X の増幅トランジスタ A M P で増幅された後に当該画素 P X の選択トランジスタ S E L , A S E L を経由して、当該画素 P X に対応する垂直信号線 2 7 に出力され、カラムアンプ 2 9 で増幅された後に、暗信号として C D S 回路 3 0 によりサンプリングされる。

## 【0053】

期間T1中のその後の時点t2から一定期間だけ、1行目、4行目及び7行目の制御信号TX(1), TX(4), TX(7)がハイレベルにされて1行目、4行目及び7行目の画素PXの転送トランジスタTXがオンにされる。これにより、1行目、4行目及び7行目の画素PXのフォトダイオードPDに蓄積されていた信号電荷が、1行目、4行目及び7行目の画素PXのフローティング容量部FDにそれぞれ転送される。1行目、4行目及び7行目の画素PXのフローティング容量部FDの電位（増幅トランジスタAMPのゲートの電位）は、ノイズ成分を除くと、この各信号電荷の量と1行目、4行目及び7行目の画素PXのフローティング容量部FDの各容量値の逆数とに比例した値となる。

## 【0054】

期間T1中のその後の時点t3から一定期間だけ、光信号サンプリング信号SIGCがハイレベルにされることによって、1行目における4列目乃至6列目及び10列目乃至12列目の画素PX、4行目における7列目乃至9列目の画素PX、及び、7行目における1列目乃至3列目の画素PXの増幅トランジスタAMPのゲートに現れる電位が、当該画素PXの増幅トランジスタAMPで増幅された後に当該画素PXの選択トランジスタSEL, ASELを経由して、当該画素PXに対応する垂直信号線27に出力され、カラムアンプ29で増幅された後に、光信号としてCDS回路30によりサンプリングされる。

## 【0055】

その後にSIGCがローレベルになった時点の後に、CDS回路30は、先程サンプリングした暗信号と先程サンプリングした光信号との差分に応じた信号を出力する。A/D変換器31は、この差分に応じた信号をデジタル信号に変換して保持する。各A/D変換器31に保持されたデジタルの画像信号は、水平読み出し回路32によって水平走査され、デジタル信号画像信号として外部（図1中のデジタル信号処理部6）へ出力される。

## 【0056】

期間T1後の期間T2において、2行目のSEL(2)、5行目のSEL(5)及び8行目のSEL(8)がハイレベルにされ、2行目、5行目及び8行目の画素PXの選択トランジスタSEL(2), SEL(5), SEL(8)がオンにされ、2行目、5行目及び8行目の画素PXが選択される。ところが、今は図6に示す設定例が実現されるように選択制御信号ASELが図7に示すようになっているので、2行目の画素PXのうちのハッチングが付されている列（4列目乃至6列目、10列目乃至12列目）の画素PXの選択トランジスタASELがオンし、2行目の画素PXのうちのハッチングが付されていない列（1列目乃至3列目、7列目乃至9列目）の画素PXの選択トランジスタASELがオフしている。また、5行目の画素PXのうちのハッチングが付されている列（7列目乃至9列目）の画素PXの選択トランジスタASELがオンし、5行目の画素PXのうちのハッチングが付されていない列（1列目乃至6列目、10列目乃至12列目）の画素PXの選択トランジスタASELがオフしている。さらに、8行目の画素PXのうちのハッチングが付されている列（1列目乃至3列目）の画素PXの選択トランジスタASELがオンし、8行目の画素PXのうちのハッチングが付されていない列（4列目乃至12列目）の画素PXの選択トランジスタASELがオフしている。

## 【0057】

したがって、期間T2において、選択トランジスタSEL, ASELの両方がオンしている画素PX（2行目における4列目乃至6列目及び10列目乃至12列目の画素PX、5行目における7列目乃至9列目の画素PX、8行目における1列目乃至3列目の画素PX）のみの出力信号が、対応する垂直信号線27に出力し得る状態となっている。

## 【0058】

期間T2の開始直後から一定時間だけ、2行目、5行目及び8行目の制御信号RST(2), RST(5), RST(8)がハイレベルにされ、2行目、5行目及び8行目の画素PXのリセットトランジスタRSTが一旦オンにされ、フローティング容量部FDの電位（増幅トランジスタAMPのゲートの電位）が一旦電圧レベルVDDにリセットされる。

10

20

30

40

50

## 【 0 0 5 9 】

期間 T 2 中のその後の時点から一定期間だけ、暗信号サンプリング信号 D A R K C がハイレベルにされることによって、2行目における4列目乃至6列目及び10列目乃至12列目の画素 P X 、5行目における7列目乃至9列目の画素 P X 、及び、8行目における1列目乃至3列目の画素 P X の増幅トランジスタ A M P のゲートに現れる電位が、当該画素 P X の増幅トランジスタ A M P で増幅された後に当該画素 P X の選択トランジスタ S E L , A S E L を経由して、当該画素 P X に対応する垂直信号線 2 7 に出力され、カラムアンプ 2 9 で増幅された後に、暗信号として C D S 回路 3 0 によりサンプリングされる。

## 【 0 0 6 0 】

期間 T 2 中のその後の時点から一定期間だけ、2行目、5行目及び8行目の制御信号 T X ( 2 ) , T X ( 5 ) , T X ( 8 ) がハイレベルにされて2行目、5行目及び8行目の画素 P X の転送トランジスタ T X がオンにされる。これにより、2行目、5行目及び8行目の画素 P X のフォトダイオード P D に蓄積されていた信号電荷が、2行目、5行目及び8行目の画素 P X のフローティング容量部 F D にそれぞれ転送される。2行目、5行目及び8行目の画素 P X のフローティング容量部 F D の電位（増幅トランジスタ A M P のゲートの電位）は、ノイズ成分を除くと、この各信号電荷の量と2行目、5行目及び8行目の画素 P X のフローティング容量部 F D の各容量値の逆数とに比例した値となる。

10

## 【 0 0 6 1 】

期間 T 2 中のその後の時点から一定期間だけ、光信号サンプリング信号 S I G C がハイレベルにされることによって、2行目における4列目乃至6列目及び10列目乃至12列目の画素 P X 、5行目における7列目乃至9列目の画素 P X 、及び、8行目における1列目乃至3列目の画素 P X の増幅トランジスタ A M P のゲートに現れる電位が、当該画素 P X の増幅トランジスタ A M P で増幅された後に当該画素 P X の選択トランジスタ S E L , A S E L を経由して、当該画素 P X に対応する垂直信号線 2 7 に出力され、カラムアンプ 2 9 で増幅された後に、光信号として C D S 回路 3 0 によりサンプリングされる。

20

## 【 0 0 6 2 】

その後に S I G C がローレベルになった時点の後に、C D S 回路 3 0 は、先程サンプリングした暗信号と先程サンプリングした光信号との差分に応じた信号を出力する。A / D 変換器 3 1 は、この差分に応じた信号をデジタル信号に変換して保持する。各 A / D 変換器 3 1 に保持されたデジタルの画像信号は、水平読み出し回路 3 2 によって水平走査され、デジタル信号画像信号として外部（図 1 中のデジタル信号処理部 6 ）へ出力される。

30

## 【 0 0 6 3 】

期間 T 2 後の期間 T 3 において、3行目の S E L ( 3 ) 、6行目の S E L ( 6 ) 及び9行目の S E L ( 9 ) がハイレベルにされ、3行目、6行目及び9行目の画素 P X の選択トランジスタ S E L ( 3 ) , S E L ( 6 ) , S E L ( 9 ) がオンにされ、3行目、6行目及び9行目の画素 P X が選択される。ところが、今は図 6 に示す設定例が実現されるように選択制御信号 A S E L が図 7 に示すようになっているので、3行目の画素 P X のうちのハッチングが付されている列（4列目乃至6列目、10列目乃至12列目）の画素 P X の選択トランジスタ A S E L がオンし、3行目の画素 P X のうちのハッチングが付されていない列（1列目乃至3列目、7列目乃至9列目）の画素 P X の選択トランジスタ A S E L がオフしている。また、6行目の画素 P X のうちのハッチングが付されている列（7列目乃至9列目）の画素 P X の選択トランジスタ A S E L がオンし、6行目の画素 P X のうちのハッチングが付されていない列（1列目乃至6列目、10列目乃至12列目）の画素 P X の選択トランジスタ A S E L がオフしている。さらに、8行目の画素 P X のうちのハッチングが付されている列（1列目乃至3列目）の画素 P X の選択トランジスタ A S E L がオンし、9行目の画素 P X のうちのハッチングが付されていない列（4列目乃至12列目）の画素 P X の選択トランジスタ A S E L がオフしている。

40

## 【 0 0 6 4 】

したがって、期間 T 3 において、選択トランジスタ S E L , A S E L の両方がオンしている画素 P X ( 3 行目における4列目乃至6列目及び10列目乃至12列目の画素 P X 、6

50

行目における 7 列目乃至 9 列目の画素 P X 、 9 行目における 1 列目乃至 3 列目の画素 P X ) のみの出力信号が、対応する垂直信号線 27 に出力し得る状態となっている。

#### 【 0065 】

期間 T3 の開始直後から一定時間だけ、3 行目、6 行目及び 9 行目の制御信号 R S T (3) , R S T (6) , R S T (9) がハイレベルにされ、3 行目、6 行目及び 9 行目の画素 P X のリセットトランジスタ R S T が一旦オンにされ、フローティング容量部 F D の電位 ( 増幅トランジスタ A M P のゲートの電位 ) が一旦電圧レベル V D D にリセットされる。

#### 【 0066 】

期間 T3 中のその後の時点から一定期間だけ、暗信号サンプリング信号 D A R K C がハイレベルにされることによって、3 行目における 4 列目乃至 6 列目及び 10 列目乃至 12 列目の画素 P X 、 6 行目における 7 列目乃至 9 列目の画素 P X 、及び、9 行目における 1 列目乃至 3 列目の画素 P X の増幅トランジスタ A M P のゲートに現れる電位が、当該画素 P X の増幅トランジスタ A M P で増幅された後に当該画素 P X の選択トランジスタ S E L , A S E L を経由して、当該画素 P X に対応する垂直信号線 27 に出力され、カラムアンプ 29 で増幅された後に、暗信号として C D S 回路 30 によりサンプリングされる。

10

#### 【 0067 】

期間 T3 中のその後の時点から一定期間だけ、3 行目、6 行目及び 9 行目の制御信号 T X (3) , T X (6) , T X (9) がハイレベルにされて 3 行目、6 行目及び 9 行目の画素 P X の転送トランジスタ T X がオンにされる。これにより、3 行目、6 行目及び 9 行目の画素 P X のフォトダイオード P D に蓄積されていた信号電荷が、3 行目、6 行目及び 9 行目の画素 P X のフローティング容量部 F D にそれぞれ転送される。3 行目、6 行目及び 9 行目の画素 P X のフローティング容量部 F D の電位 ( 増幅トランジスタ A M P のゲートの電位 ) は、ノイズ成分を除くと、この各信号電荷の量と 3 行目、6 行目及び 9 行目の画素 P X のフローティング容量部 F D の各容量値の逆数とに比例した値となる。

20

#### 【 0068 】

期間 T3 中のその後の時点から一定期間だけ、光信号サンプリング信号 S I G C がハイレベルにされることによって、3 行目における 4 列目乃至 6 列目及び 10 列目乃至 12 列目の画素 P X 、 6 行目における 7 列目乃至 9 列目の画素 P X 、及び、9 行目における 1 列目乃至 3 列目の画素 P X の増幅トランジスタ A M P のゲートに現れる電位が、当該画素 P X の増幅トランジスタ A M P で増幅された後に当該画素 P X の選択トランジスタ S E L , A S E L を経由して、当該画素 P X に対応する垂直信号線 27 に出力され、カラムアンプ 29 で増幅された後に、光信号として C D S 回路 30 によりサンプリングされる。

30

#### 【 0069 】

その後に S I G C がローレベルになった時点の後に、 C D S 回路 30 は、先程サンプリングした暗信号と先程サンプリングした光信号との差分に応じた信号を出力する。 A / D 変換器 31 は、この差分に応じた信号をデジタル信号に変換して保持する。各 A / D 変換器 31 に保持されたデジタルの画像信号は、水平読み出し回路 32 によって水平走査され、デジタル信号画像信号として外部 ( 図 1 中のデジタル信号処理部 6 ) へ出力される。

40

#### 【 0070 】

このようにして、図 6 に示すように設定された複数の部分領域の画素 P X の出力信号が読み出される。

#### 【 0071 】

図 9 は、部分領域撮影モードにおいて、固体撮像素子 4 の撮像領域 21 のうちの読み出す部分領域の他の設定例を模式的に示す図であり、図 6 に対応している。図 10 は、図 1 中の固体撮像素子 4 において図 9 に示す設定例を実現する選択制御信号 A S E L を示しており、図 7 に対応している。

#### 【 0072 】

図 9 において、読み出す 2 つの部分領域として設定された既定部分領域 A R (1, 1) , A R (1, 2) , A R (2, 3) , A R (2, 4) には、ハッチングを付している。本例

50

では、読み出す1つの部分領域は、2つの既定部分領域AR(1, 1), AR(1, 2)からなり、読み出す他の1つの部分領域は、2つの既定部分領域AR(2, 3), AR(2, 4)からなる。

#### 【0073】

このように、本実施の形態では、読み出す1つ以上の部分領域の各々は、1つの既定部分領域ARからなるものでもよいし、複数の既定部分領域ARからなるものでもよい。また、本実施の形態では、複数の部分領域を読み出す場合、各部分領域は必ずしも同数の既定部分領域ARからなる必要はなく、読み出す1つの部分領域を構成する既定部分領域ARの数は、読み出す他の1つの部分領域を構成する既定部分領域ARの数と異なっていてもよい。

10

#### 【0074】

本実施の形態では、部分領域撮影モードにおいて、読み出す部分領域が図9に示すように設定される場合にも、例えば、読み出す部分領域が図6に示すように設定される場合と同じく図8に示すように読み出し制御が行われる。

#### 【0075】

図11は、部分領域撮影モードにおいて、固体撮像素子4の撮像領域21のうちの読み出す部分領域の更に他の設定例を模式的に示す図であり、図6に対応している。図12は、図1中の固体撮像素子4において図11に示す設定例を実現する選択制御信号ASELを示しており、図7に対応している。

20

#### 【0076】

図11において、読み出す4つの部分領域として設定された既定部分領域AR(3, 1), AR(1, 1), AR(2, 3), AR(1, 4)には、ハッティングを付している。図6に示す設定例及び図9に示す設定例では、既定部分領域ARのいずれの列においても、2つ以上の既定部分領域ARは読み出す領域として設定されていないのに対し、図11に示す設定例では、既定部分領域ARの1列目において、2つの既定部分領域AR(3, 1), AR(1, 1)が、読み出す部分領域として設定されている。

#### 【0077】

したがって、本実施の形態では、部分領域撮影モードにおいて、読み出す部分領域が図11に示すように設定される場合にも、図8に示すように読み出し制御が行われるとすれば、2つ以上の画素PXの出力信号が同時に同じ垂直信号線27に読み出されて両者の信号が干渉してしまい、画素PXの出力信号を適切に読み出すことができない。具体的には、図8中の期間T1において、1行目における1列目乃至3列目の画素PXの出力信号と7行目における1列目乃至3列目の画素PXの出力信号とが同時に同じ垂直信号線27にそれぞれ読み出されて両者の信号が干渉してしまい、図8中の期間T2において、2行目における1列目乃至3列目の画素PXの出力信号と8行目における1列目乃至3列目の画素PXの出力信号とが同時にそれぞれ同じ垂直信号線27に読み出されて両者の信号が干渉してしまい、図8中の期間T3において、3行目における1列目乃至3列目の画素PXの出力信号と9行目における1列目乃至3列目の画素PXの出力信号とが同時にそれぞれ同じ垂直信号線27に読み出されて両者の信号が干渉してしまう。

30

#### 【0078】

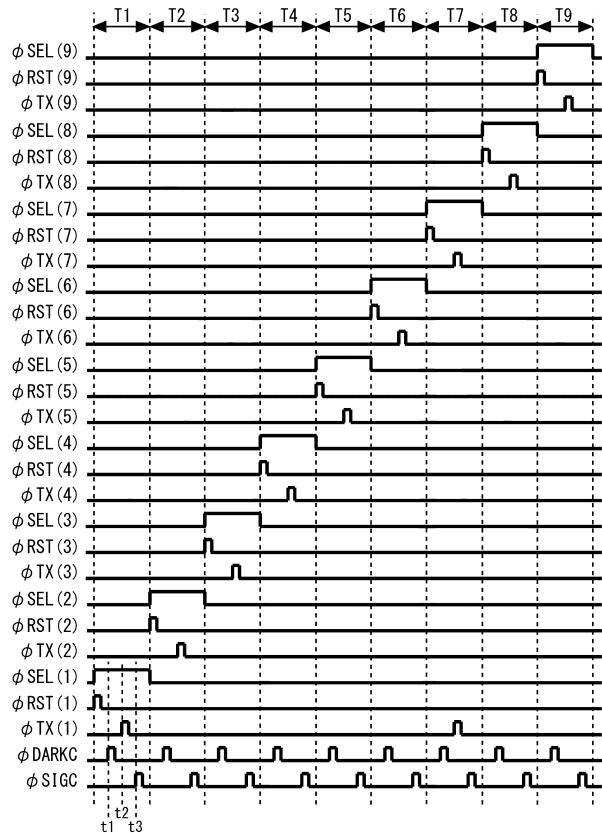

そこで、本実施の形態では、部分領域撮影モードにおいて、読み出す部分領域が図11に示すように設定されることも許容する場合には、垂直走査回路22は、図8に示す読み出し制御に代えて、例えば図13に示す読み出し制御を行えばよい。図13は、図1中の固体撮像素子4の部分領域撮影モード時の読み出し制御の他の例を示すタイミングチャートであり、図8に対応している。

40

#### 【0079】

図13に示す例では、垂直走査回路22は、読み出す図11に示す部分領域の設定に応じて、2つ以上の画素PXの出力信号が同時に同じ垂直信号線27に読み出されることがないこと必要条件として、可能な限り多くの画素行について同時に読み出し制御が行われるように、読み出し制御を行う。

50

## 【0080】

具体的には、図13に示す例では、垂直走査回路22によって、期間T1において、撮像領域21における1行目及び4行目の画素PXの行について同時に読み出し制御が行われ、その次の期間T2において、撮像領域21における2行目及び5行目の画素PXの行について同時に読み出し制御が行われ、その次の期間T3において、撮像領域21における3行目及び6行目の画素PXの行について同時に読み出し制御が行われ、その次の期間T4において、撮像領域21における7行目の画素PXの行について読み出し制御が行われ、その次の期間T5において、撮像領域21における8行目の画素PXの行について読み出し制御が行われ、その次の期間T6において、撮像領域21における9行目の画素PXの行について読み出し制御が行われ、これにより1フレーム分の読み出しが終了する。期間T1～T6を順次繰り返すことで、複数のフレームがローリング電子シャッタにより読み出される。

10

## 【0081】

本実施の形態では、領域設定回路23は、部分領域撮影モードにおいて、読み出す部分領域の設定に際して、既定部分領域ARのいずれの列においても、2つ以上の既定部分領域ARは読み出す領域として同時に設定しないという制約の下で、読み出す領域を任意に設定し得るようにしておき、垂直走査回路22は、部分領域撮影モードにおいて常に図8に示す読み出し制御を行うように構成してもよい。以下の説明では、このような構成を「制約有り部分領域設定の構成」と呼ぶ。この場合には、図6に示すような領域設定や図9に示すような領域設定は許容されるが、図11に示すような領域設定は許容されない。このような垂直走査回路22は、例えば、垂直シフトレジスタやスイッチ等を用いて構成したり、メモリ等を用いたデコーダ回路を用いて構成したりすることができる。

20

## 【0082】

あるいは、本実施の形態では、領域設定回路23は、部分領域撮影モードにおいて、読み出す部分領域の設定に際して、何らの制約もなく読み出す領域を任意に設定し得るようにしておき、垂直走査回路22は、部分領域撮影モードにおいて、部分領域の設定に応じて、2つ以上の画素PXの出力信号が同時に同じ垂直信号線27に読み出されることがないこと必要条件として、可能な限り多くの画素行について同時に読み出し制御が行われるような読み出し制御を行うように構成してもよい。以下の説明では、このような構成を「制約無し部分領域設定の構成」と呼ぶ。この場合には、図6に示すような領域設定や図9に示すような領域設定のみならず、図11に示すような領域設定も許容される。垂直走査回路22は、図6に示すような領域設定や図9に示すような領域設定の場合には、例えば、図8に示す読み出し制御を行い、図11に示すような領域設定の場合には、例えば、図13に示すような読み出し制御を行う。このような垂直走査回路22は、その都度必要な行選択を実現するように、例えば、メモリ等を用いたデコーダ回路を用いて構成することができる。

30

## 【0083】

先の説明からわかるように、本実施の形態では、領域設定回路23は、撮像領域21のうちの所望の複数の部分領域の画素PXの選択トランジスタASELを選択状態する領域設定部を構成している。また、本実施の形態では、垂直走査回路22は、前記複数の部分領域の各行の画素PXの選択トランジスタSELを選択状態にしつつ、選択トランジスタSELが選択状態にされた行の画素PXに対して読み出し制御を行う制御部を構成している。

40

## 【0084】

そして、垂直走査回路22は、図6に示すような領域設定や図9に示すような領域設定の場合において図8に示す読み出し制御を行う場合や、図11に示すような領域設定の場合において図11に示す読み出し制御を行う場合には、前記複数の部分領域（読み出し領域として設定される複数の部分領域）のうちの少なくとも1つの部分領域の1つの行の画素PXの選択トランジスタSEL、及び、前記複数の部分領域のうちの他の少なくとも1つの部分領域の、前記1つの行と異なる1つの行の画素PXの選択トランジスタSELを、同時に選択状態にしつつ、これらの行の画素PXに対して読み出し制御を行うことになる

50

。ここで、前記少なくとも1つの部分領域の画素P Xの出力信号を受け取るいずれの垂直信号線27も、前記他の少なくとも1つ部分領域の画素P Xの出力信号を受け取るいずれの垂直信号線27とも異なる。

【0085】

また、垂直走査回路22は、図6に示すような領域設定や図9に示すような領域設定の場合において図8に示す読み出し制御を行う場合には、前記複数の部分領域（読み出し領域として設定される複数の部分領域）の各部分領域の1つの行の画素P Xの選択トランジスタS E Lを同時に選択状態にしつつこれらの行の画素P Xに対して読み出し制御を行い、この制御を前記複数の部分領域の各部分領域の残りの行の前記画素について順次繰り返すことになる。ここで、前記複数の部分領域の画素P Xの行数が互いに同一である。また、前記複数の部分領域のうちの少なくとも1つの部分領域の画素P Xのいいずれの行も、前記複数の部分領域のうちの他の少なくとも1つの部分領域の画素P Xのいいずれの行とも異なる。さらに、前記複数の部分領域の各部分領域の画素P Xの出力信号を受け取るいずれの垂直信号線27も、前記複数の部分領域のうちの当該部分領域以外の部分領域の画素P Xの出力信号を受け取るいずれの垂直信号線27とも異なる。

10

【0086】

図14は、図1中の固体撮像素子4の全領域撮影モード時の読み出し制御の一例を示すタイミングチャートであり、図8及び図13に対応している。全領域撮影モードは、固体撮像素子4の撮像領域21の全領域の画素P Xの出力信号を読み出す動作モードである。

20

【0087】

全領域撮影モード時には、全ての既定部分領域A Rの選択トランジスタA S E Lのゲートに供給されるいいずれの選択制御信号A S E Lも、ハイレベル（H）に維持される。これにより、撮像領域21の全領域（全ての既定部分領域A R）の選択トランジスタA S E Lがオンに維持される。

【0088】

本実施の形態では、全領域撮影モードでは、例えば、図14に示すように読み出し制御が行われる。図14に示す例では、垂直走査回路22によって、期間T1～T9の各期間において、撮像領域21における1行目の画素P Xの行から9行目の画素P Xの行まで1行ずつについて順次読み出し制御が行われ、これにより1フレーム分の読み出しが終了する。静止画撮影時の全領域撮影モードでは、全画素P Xを同時にリセットするいわゆるグローバルリセット後にメカニカルシャッタ（図示せず）により露光が行われ、その後に期間T1～T9が1回行われる。動画撮影時の全領域撮影モードでは、期間T1～T9が順次繰り返され、複数のフレームがローリング電子シャッタにより読み出される。

30

【0089】

本実施の形態では、固体撮像素子4の各画素P Xが選択トランジスタS E Lの他に選択トランジスタA S E Lも有しているので、部分領域撮影モードにおいて、読み出す領域として例えば図6、図9及び図11に示すように複数の部分領域を設定する場合、図8及び図13に示すように読み出し制御を行うことができ、複数の異なる行の画素P Xを同時に読み出すことができる。したがって、本実施の形態によれば、1フレーム分の画像信号を読み出すのに要する時間を短縮することができ、所望の複数の部分領域を高速に読み出すことができる。具体的には、1フレーム分の画像信号を読み出すためには、全領域撮影モードでは図14に示すように期間T1～T9を要するのに対し、部分領域撮影モードでは、図8に示す場合には期間T1～T3しか要しないとともに、図13に示す場合には期間T1～T6しか要しない。

40

【0090】

なお、前記特許文献1に開示された撮像装置では、複数の異なる行の画素P Xを同時に読み出すことができないので、部分領域撮影モードにおいて、読み出す領域として複数の部分領域を設定する場合、1フレーム分の画像信号を読み出すのに本実施の形態に比べて長時間を要してしまう。例えば、前記特許文献1に開示された撮像装置では、部分領域撮影モードにおいて、読み出す領域として例えば図6及び図11に示すように複数の部分領域

50

を設定する場合、結局、全領域撮影モード時の図14に示す読み出し制御と同様の読み出し制御を行わざるを得ず、1フレーム分の画像信号を読み出すのに長時間を要してしまう。

【0091】

本実施の形態による電子カメラ1は、使用者が操作部14を介して第1の部分領域撮影モードを指令すると、図15に示す動作を行う。図15は、図1に示す電子カメラ1の第1の部分領域撮影モード時の動作の一例を示す概略フローチャートである。

【0092】

CPU9は、操作部14により第1の部分領域撮影モードが指令されると、まず、自動露光制御(AE)及び自動焦点制御(AF)を実現する(ステップS1)。ステップS1におけるAEは、例えば、CPU9が固体撮像素子4とは別に設けられた自動露光用測光センサ(図示せず)からの測光信号に基づいて最適な露光量を演算し、撮影レンズ2の絞りがこの露光量に応じた絞りとなるようにレンズ制御部3を制御することによって、実現される。また、ステップS1におけるAFは、例えば、CPU9が固体撮像素子4とは別に設けられた焦点検出センサ(図示せず)からの信号に基づいて、デフォーカス量を演算し、このデフォーカス量に応じてレンズ制御部3が撮影レンズ2の焦点駆動して撮影レンズ2を合焦させることによって、実現される。なお、固体撮像素子4の画素PXの出力信号を読み出してその信号を自動露光用測光信号として用いてもよい。また、固体撮像素子4を焦点検出用信号も得られるように構成し、その信号を用いてAFを実現してもよい。

10

【0093】

なお、ステップS1や後述するステップS6でAE及びAFを行う代わりに、前記絞りや焦点合わせ等は、予め使用者によりいわゆる手動設定しておくものとしてもよい。

20

【0094】

次に、CPU9は、撮像制御部5を介して領域設定回路23を制御して、領域設定回路23から全ての既定部分領域ARの選択トランジスタASELのゲートに供給される全ての選択制御信号ASELをハイレベルにし、撮像領域21の全領域を読み出し領域として設定する(ステップS2)。

【0095】

この状態で、CPU9は、撮像制御部5を介して垂直走査回路22等を制御して、図14に示す全領域撮影モード時の読み出し制御を実現し、1フレーム分の全領域の画像データを得てメモリ7に一旦格納する(ステップS3)。なお、ここでは、図14中の期間T1に先立って、全画素PXを同時にリセットするいわゆるグローバルリセット後に、図示しないメカニカルシャッタで露光しておく。

30

【0096】

次いで、CPU9は、ステップS3で得られた画像を表示部10に表示させ(ステップS4)、使用者に撮影しようとする所望の部分領域の指定を促す。なお、CPU9は、前記制約有り部分領域設定の構成が採用されている場合には許容される領域指定のみを受け付け、前記制約無し部分領域設定の構成が採用されている場合には、制約無しに領域指定を受け付ける。使用者が表示された画像を見ながら操作部14によって自身が望む部分領域を指定する入力を行い、CPU9がその指定を受け付けると、CPU9は、撮像制御部5を介して領域設定回路23を制御して、その指定による1つ又は複数の部分領域に該当する既定部分領域ARの選択トランジスタASELのゲートに供給される選択制御信号ASELを選択的にハイレベルにし、1つ又は複数の既定部分領域ARを読み出し領域として選択的に設定する(ステップS5)。本実施の形態では、CPU9、表示部10及び操作部14のこれらの機能によって、撮像領域21のうちの所望の1又は複数の部分領域を指令するためのユーザインターフェースが構築されている。

40

【0097】

引き続いて、CPU9は、ステップS1と同様にAE及びAFを行わせる(ステップS6)。ただし、ステップS6では、ステップS1と異なり、ステップS5で設定された部分領域について露光及び焦点合わせが最適化されるよう行われる。

【0098】

50

次に、CPU9は、撮像制御部5を介して垂直走査回路22等を制御して、前述した部分領域撮影モード時の読み出し制御を実現し、1フレーム分の部分領域の画像データを得てメモリ7に一旦格納し、記録部11によりこの画像を部分領域の動画像として記録媒体11aに記録させる(ステップS7)。なお、図15に示す動作によってステップS7が繰り返されることにより、ローリング電子シャッタが実現される。

#### 【0099】

その後、CPU9は、操作部14から部分領域動画撮影終了の指令が得られたか否かを判定し(ステップS8)、その指令がなければステップS7へ戻る一方、その指令があれば第1の部分領域撮影モードの一連の動作を終了する。

#### 【0100】

この第1の部分領域撮影モードでは、このようにして、使用者が任意に設定した所望の1つ又は複数の部分領域の動画像を取得することができる。そして、本実施の形態によれば、前述したように所望の複数の部分領域の1フレーム分の画像信号を読み出すのに要する時間を短縮することができ、所望の複数の部分領域を高速に読み出すことができるので、使用者が任意に設定した所望の複数の部分領域の動画像を高フレームレートで取得することができる。

10

#### 【0101】

したがって、この第1の部分領域撮影モードでは、使用者が任意の複数の着目対象をそれぞれ含む所望の複数の部分領域を指定することで、視野中の複数の着目対象の変化(例えば、形状や大きさや向きや色などの変化)の過程を細かく捕らえた動画像を取得することができ、その動画像によって、視野中の複数の着目対象の変化を見逃さずに観察することができる。例えば、本実施の形態による電子カメラ1が顕微鏡に組み込まれ顕微鏡像を撮像する撮像装置である場合には、細胞を培養しているシャーレを視野とする場合、複数の細胞の変化の過程(例えば、細胞分裂の様子や、心筋細胞の拍動の様子など)を細かく捕らえた動画像を取得することができる。

20

#### 【0102】

本実施の形態による電子カメラ1は、使用者が操作部14を介して第2の部分領域撮影モードを指令すると、図16に示す動作を行う。図16は、図1に示す電子カメラ1の第2の部分領域撮影モード時の動作の一例を示す概略フローチャートである。前記第1の部分領域撮影モードは、部分領域が使用者が指定した領域に固定されるモードであるのに対し、第2の部分領域撮影モードは、撮影される部分領域が着目対象の移動に自動的に追従していくモードである。

30

#### 【0103】

CPU9は、操作部14により第2の部分領域撮影モードが指令されると、図15中のステップS1～S3とそれぞれ同じステップS11～S13を行う。

#### 【0104】

次に、CPU9は、ステップS13でメモリ7に格納された画像に対して公知の画像認識手法による画像認識処理を行い、所望の着目対象(例えば、人の全身、人の顔、移動体、細胞など)を認識し、画像上の位置や大きさ等を検出する(ステップS14)。

40

#### 【0105】

次いで、CPU9は、ステップS14により着目対象が認識されたか否かを判定し(ステップS15)、着目対象が認識されればステップS16へ移行する一方で、着目対象が認識されなければステップS27へ移行する。ステップS27において、CPU9は、操作部14から部分領域動画撮影終了の指令が得られたか否かを判定し、その指令がなければステップS11へ戻る一方、その指令があれば第2の部分領域撮影モードの一連の動作を終了する。

#### 【0106】

ステップS16において、CPU9は、撮像制御部5を介して領域設定回路23を制御して、ステップS14の認識結果に応じて、1つ又は複数の既定部分領域ARを読み出し領域として選択的に設定する。具体的には、CPU9は、撮像制御部5を介して領域設定回

50

路 2 3 を制御して、ステップ S 1 4 で認識された各着目対象及びそのある程度の周囲を含む 1 つ又は複数の部分領域に該当する既定部分領域 A R の選択トランジスタ A S E L のゲートに供給される選択制御信号 A S E L を選択的にハイレベルにする。

【 0 1 0 7 】

引き続いて、C P U 9 は、ステップ S 1 1 と同様に A E 及び A F を行わせる（ステップ S 1 7）。ただし、ステップ S 1 7 では、ステップ S 1 1 と異なり、ステップ S 1 6 で設定された部分領域について露光及び焦点合わせが最適化されるよう行われる。

【 0 1 0 8 】

その後、C P U 9 は、カウント値 q をゼロにリセットする（ステップ S 1 8）。このカウント値 q は、部分領域を最新に設定した後に撮影したフレーム数を示すものである。

10

【 0 1 0 9 】

次に、C P U 9 は、撮像制御部 5 を介して垂直走査回路 2 2 等を制御して、前述した部分領域撮影モード時の読み出し制御を実現し、1 フレーム分の部分領域の画像データを得てメモリ 7 に一旦格納し、記録部 1 1 によりこの画像を現在設定されている部分領域の動画像として記録媒体 1 1 a に記録させる（ステップ S 1 9）。なお、図 1 6 に示す動作によつてステップ S 1 9 が繰り返されることにより、ローリング電子シャッタが実現される。

【 0 1 1 0 】

次いで、C P U 9 は、カウント値 q を 1 だけインクリメントした（ステップ S 2 0）後、操作部 1 4 から部分領域動画撮影終了の指令が得られたか否かを判定し（ステップ S 2 1）、その指令がなければステップ S 2 2 へ移行一方、その指令があれば第 2 の部分領域撮影モードの一連の動作を終了する。

20

【 0 1 1 1 】

ステップ S 2 2 において、C P U 9 は、現在のカウント値 q が値 Q 以上であるか否かを判定し、q < Q でなければステップ S 1 9 へ戻る一方、q > Q であればステップ S 2 3 へ移行する。この値 Q は、第 2 の部分領域撮影モードの開始前に、予め使用者により操作部 1 4 を介して任意に設定された 1 以上の値である。値 Q は、部分領域の再設定のタイミングを決める値である。以下の説明からわかるように、一旦設定した部分領域で撮影したフレーム数が値 Q に達したときに、部分領域が再設定されることになる。着目対象の移動速度が高い場合には、着目対象に対する追従性を高めるべく値 Q は比較的小さい値に設定され、着目対象の移動速度が低い場合には、ステップ S 2 3, S 2 6 などの時間を低減して総合的なフレームレートを高めるべく値 Q は比較的大きい値に設定される。

30

【 0 1 1 2 】

ステップ S 2 3 において、ステップ S 1 9 でメモリ 7 に最新に格納されたフレームの各部分領域の画像に対して公知の画像認識手法による画像認識処理を行い、所望の着目対象を認識し、画像上の位置や大きさ等を検出する。

【 0 1 1 3 】

引き続いて、C P U 9 は、ステップ S 2 3 により着目対象が認識されたか否かを判定し（ステップ S 2 4）、着目対象が認識されればステップ S 2 5 へ移行する一方で、着目対象が認識されなければステップ S 2 7 へ移行する。

40

【 0 1 1 4 】

ステップ S 2 5 において、C P U 9 は、撮像制御部 5 を介して領域設定回路 2 3 を制御して、ステップ S 2 3 の認識結果に応じて、1 つ又は複数の既定部分領域 A R を読み出し領域として選択的に設定する。

【 0 1 1 5 】

その後、C P U 9 は、ステップ S 1 7 と同様に A E 及び A F を行わせた（ステップ S 2 6）後に、ステップ S 1 8 へ戻る。ただし、ステップ S 2 6 では、ステップ S 1 7 と異なり、ステップ S 2 5 で最新に設定された部分領域について露光及び焦点合わせが最適化されるよう行われる。

【 0 1 1 6 】

この第 2 の部分領域撮影モードでは、このようにして、着目対象の移動に自動的に追従し

50

て設定された複数の部分領域の動画像を取得することができる。そして、本実施の形態によれば、前述したように所望の複数の部分領域の1フレーム分の画像信号を読み出すのに要する時間を短縮することができ、所望の複数の部分領域を高速に読み出すことができるるので、着目対象の移動に自動的に追従して設定された部分領域の動画像を高フレームレートで取得することができるとともに、着目対象の移動速度が高くてもA F等に要する時間を確保することができることから合焦状態の動画像を得ることができて追従性が高まる。

#### 【0117】

したがって、この第2の部分領域撮影モードは、例えば、着目対象を人の全身や顔とした監視カメラとして利用する場合などに有効である。複数人の全身又は顔の変化の過程を細かく撮影することができると、複数人の姿勢変化や表情の変化や唇の動きの変化の過程を細かく知ることができ、監視対象から高度な情報を得ることができる。例えば、複数人の格闘の様子を子細に知ることができたり、読唇術を利用して複数人の会話の内容を知ることができたりする。

#### 【0118】

また、前記第2の部分領域撮影モードは、例えば、本実施の形態による電子カメラ1が顕微鏡に組み込まれ顕微鏡像を撮像する撮像装置である場合においても、有効である。着目対象として細胞や微生物等を観察する場合において、その移動速度が極低速であったとしても、当該着目対象が移動し得る場合には、前記第1の部分領域撮影モードでは、長時間経過した後には、使用者が設定した部分領域から着目対象が外れてしまう可能性がある。これに対し、前記第2の部分領域撮影モードは、着目対象の移動に自動的に追従して設定された複数の部分領域の動画像を取得することができるので、このような着目対象であっても、長時間に渡って高フレームレートで撮像することができる。

#### 【0119】

なお、本実施の形態による電子カメラ1は、使用者が操作部14を介して静止画撮影モードを指令すると、通常の電子カメラと同様の静止画撮影動作が行われ、使用者が操作部14を介して動画撮影時の全領域撮影モードを指令するとその動作が行われるが、ここではその説明は省略する。

#### 【0120】

#### [第2の実施の形態]

#### 【0121】

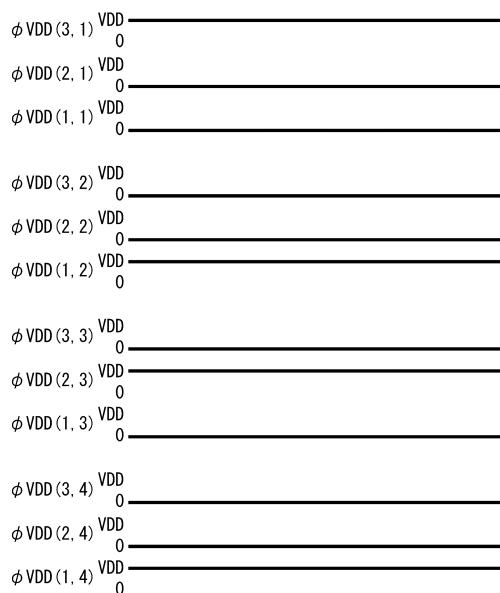

図17は、本発明の第2の実施の形態による電子カメラで用いられる固体撮像素子41の概略構成を示す回路図であり、図2に対応している。図18は、図17に示す固体撮像素子41の撮像領域21の一部をなす既定部分領域ARを示す回路図であり、図4に対応している。図19は、図18に示す回路を抽象化して示す回路図であり、図5に対応している。図20は、図17に示す固体撮像素子41において図6に示す設定例と同じ設定を実現する電源電圧信号VDDを示す図であり、図7に対応している。

#### 【0122】

図17乃至図19において、図2、図4及び図5中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。本実施の形態が前記第1の実施の形態と異なる所は、以下に説明する点である。

#### 【0123】

本実施の形態では、前記第1の実施の形態による電子カメラ1において、固体撮像素子4に代えて固体撮像素子41が用いられている。

#### 【0124】

前記第1の実施の形態では、撮像領域21の各画素PXにおいて選択トランジスタASEL設けられているのに対し、本実施の形態では、撮像領域21の各画素PXにおいて、選択トランジスタASEL及び制御線33が取り除かれ、選択トランジスタSELのソースが、当該画素PXに対応する垂直信号線27に接続されている。

#### 【0125】

前記第1の実施の形態では、全画素PXの增幅トランジスタAMPのドレイン(図4中の

10

20

30

40

50

b点)は、給電線34により共通に接続され、そこには、増幅トランジスタAMPの電源電圧として、増幅トランジスタAMPの動作に有効である有効電圧レベルVDDが固定的に供給される。これに対し、本実施の形態では、給電線34は各既定部分領域AR毎に電気的に分離され、各画素PXの増幅トランジスタAMPのドレイン(図18中のb点)は、既定部分領域AR毎に給電線34により共通に接続され、そこには、増幅トランジスタAMPの電源電圧として電源電圧信号VDDが領域設定回路23から供給される。なお、各画素PXのリセットトランジスタRSTのドレインは、給電線34により、当該画素PXの増幅トランジスタAMPのドレイン(図18中のb点)に接続されている。

#### 【0126】

図19は、図18に示す回路を、給電線34による各既定部分領域ARの増幅トランジスタAMPのドレイン(b点)の接続関係に着目して抽象化して示したものである。各電源電圧信号VDDを既定部分領域AR毎に区別する場合、j行目かつk列目の既定部分領域AR(j,k)の画素PXの増幅トランジスタAMPのドレインに供給される電源電圧信号VDDは符号VDD(j,k)で示す。なお、給電線34の実際の配置(引き回す経路等)は、何ら限定されるものではない。

10

#### 【0127】

本実施の形態では、領域設定回路23は、撮像制御部5による制御下で、各制御信号ASELに代えて、各電源電圧信号VDDを出力する給電制御回路として構成されている。各電源電圧信号VDDは、増幅トランジスタAMPの動作に有効である有効電圧レベルVDD、又は、増幅トランジスタAMPの動作に有効ではない非有効電圧レベル(ここでは、0Vとするが、必ずしも0Vに限らない。)となり、領域設定回路23は、各画素PXの増幅トランジスタAMPの電源電圧としてVDD又は0Vを選択的に供給する。

20

#### 【0128】

本実施の形態において、各画素PXにおいて電源電圧信号VDDがVDDとなって増幅トランジスタAMPが有効に動作する状態及び電源電圧信号VDDが0Vとなって増幅トランジスタAMPが有効に動作しない状態は、各画素PXの出力信号の垂直信号線27への出力の可否に関して、前記第1の実施の形態において、各画素PXにおいて制御信号ASELがハイレベルになって選択トランジスタASELがオンした状態及び制御信号ASELがローレベルになって選択トランジスタASELがオフした状態と、それぞれ実質的に同じになる。

30

#### 【0129】

したがって、本実施の形態では、各画素PXの出力信号は、当該画素PXの選択トランジスタSELが選択状態(オン状態)であるとともに当該画素PXの増幅トランジスタAMPの電源電圧として供給される電源電圧信号VDDが有効電圧レベルVDDである場合にのみ、当該画素PXの出力信号及び当該画素PXに対して列方向に並んだ画素PXの出力信号を受け取る垂直信号線27に出力される。

#### 【0130】

本実施の形態では、領域設定回路23が、前記第1の実施の形態において各ASELとしてハイレベル信号を供給する代わりに各電源電圧信号VDDとして有効電圧レベルVDDを供給し、前記第1の実施の形態において各ASELとしてローレベル信号を供給する代わりに各電源電圧信号VDDとして0Vを供給することによって、前記第1の実施の形態と同様の動作が実現される。例えば、本実施の形態において、図6に示す領域設定例と同じ設定を実現する場合には、領域設定回路23は図20に示す各電源電圧信号VDDを出力すればよい。

40

#### 【0131】

本実施の形態によっても、前記第1の実施の形態と同様の利点が得られる。また、本実施の形態では、各画素PXにおいて選択トランジスタASELが設けられていないので、各画素PXの構成が簡単となる。

#### 【0132】

[第3の実施の形態]

50

## 【0133】

図21は、本発明の第3の実施の形態による電子カメラで用いられる固体撮像素子51の概略構成を示す回路図であり、図2に対応している。図22は、図21に示す固体撮像素子51の撮像領域21の一部をなす既定部分領域ARを示す回路図であり、図4に対応している。図23は、図21に示す固体撮像素子51の部分領域撮影モード時の読み出し制御の一例を示すタイミングチャートであり、図8に対応している。

## 【0134】

図21乃至図23において、図2、図4及び図8中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。本実施の形態が前記第1の実施の形態と異なる所は、以下に説明する点である。

10

## 【0135】

本実施の形態では、前記第1の実施の形態による電子カメラ1において、固体撮像素子4に代えて固体撮像素子51が用いられている。

## 【0136】

前記第1の実施の形態では、撮像領域21の各画素PXにおいて選択トランジスタSEL設けられているのに対し、本実施の形態では、撮像領域21の各画素PXにおいて、選択トランジスタSEL及び接続線26が取り除かれ、選択トランジスタASELのドレインが、当該画素PXの増幅トランジスタAMPのソースに接続されている。

## 【0137】

前記第1の実施の形態では、全画素PXの増幅トランジスタAMPのドレイン（図4中のb点）は、給電線34により共通に接続され、そこには、増幅トランジスタAMPの電源電圧として、増幅トランジスタAMPの動作に有効である有効電圧レベルVDDが固定的に供給される。これに対し、本実施の形態では、給電線34は画素PXの行毎に電気的に分離され、各画素PXの増幅トランジスタAMPのドレイン（図22中のb点）は、画素PXの行毎に給電線34により共通に接続され、そこには、増幅トランジスタAMPの電源電圧として電源電圧信号VDDが、給電制御回路52から供給される。各電源電圧信号VDDを画素PXの行毎に区別する場合、n行目の画素PXの増幅トランジスタAMPのドレインに供給される電源電圧信号VDDは符号VDD(n)で示す。なお、各画素PXのリセットトランジスタRSTのドレインは、給電線34により、当該画素PXの増幅トランジスタAMPのドレイン（図22中のb点）に接続されている。

20

## 【0138】

本実施の形態では、給電制御回路52は、垂直走査回路22の一部として設けられ、撮像制御部5による制御下で、各制御信号SELに代えて各電源電圧信号VDDを出力する。各電源電圧信号VDDは、増幅トランジスタAMPの動作に有効である有効電圧レベルVDD、又は、増幅トランジスタAMPの動作に有効ではない非有効電圧レベル（ここでは、0Vとするが、必ずしも0Vに限らない。）となり、給電制御回路52は、各画素PXの増幅トランジスタAMPの電源電圧としてVDD又は0Vを選択的に供給する。

30

## 【0139】

本実施の形態において、各画素PXにおいて電源電圧信号VDDがVDDとなって増幅トランジスタAMPが有効に動作する状態及び電源電圧信号VDDが0Vとなって増幅トランジスタAMPが有効に動作しない状態は、各画素PXの出力信号の垂直信号線27への出力の可否に関して、前記第1の実施の形態において、各画素PXにおいて制御信号SELがハイレベルになって選択トランジスタSELがオンした状態及び制御信号SELがローレベルになって選択トランジスタSELがオフした状態と、それぞれ実質的に同じになる。

40

## 【0140】

したがって、本実施の形態では、各画素PXの出力信号は、当該画素PXの選択トランジスタASELが選択状態（オン状態）であるとともに当該画素PXの増幅トランジスタAMPの電源電圧として供給される電源電圧信号VDDが有効電圧レベルVDDである場合にのみ、当該画素PXの出力信号及び当該画素PXに対して列方向に並んだ画素PXの

50

出力信号を受け取る垂直信号線 27 に出力される。

【0141】

本実施の形態では、給電制御回路 52 が、前記第 1 の実施の形態において各 SEL としてハイレベル信号を供給する代わりに各電源電圧信号 VDD として有効電圧レベル VD D を供給し、前記第 1 の実施の形態において各 SEL としてローレベル信号を供給する代わりに各電源電圧信号 VDD として 0V を供給することによって、前記第 1 の実施の形態と同様の動作が実現される。例えば、本実施の形態において、部分領域撮影モードにおいて、読み出す部分領域が図 6 に示すように設定される場合には、垂直走査回路 22 は、図 23 に示すように読み出し制御を行えばよい。

【0142】

本実施の形態によっても、前記第 1 の実施の形態と同様の利点が得られる。また、本実施の形態では、各画素 PX において選択トランジスタ SEL が設けられていないので、各画素 PX の構成が簡単となる。

【0143】

【第 4 の実施の形態】

【0144】

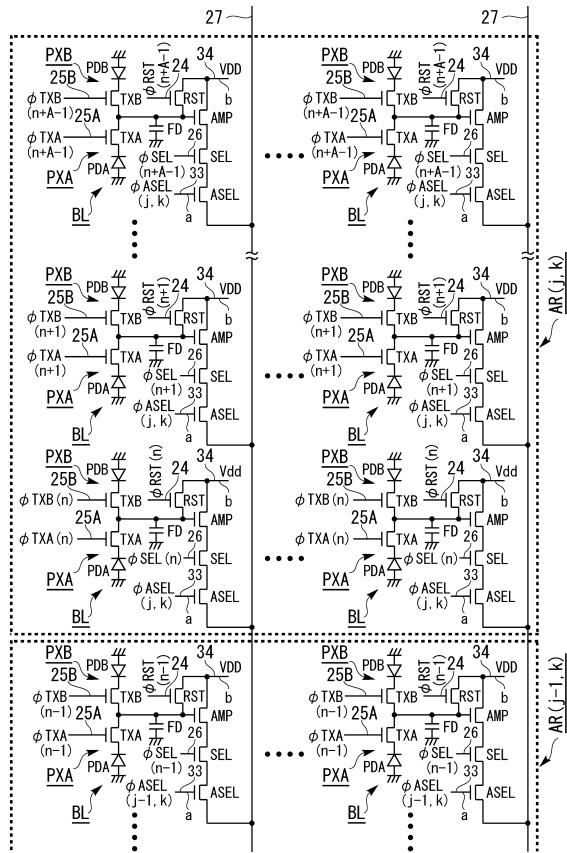

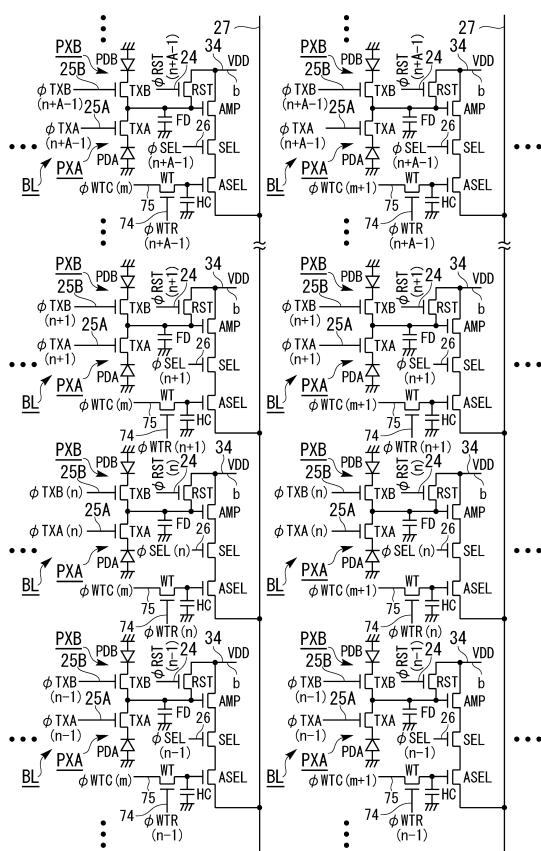

図 24 は、本発明の第 4 の実施の形態による電子カメラで用いられる固体撮像素子 61 の概略構成を示す回路図であり、図 2 に対応している。図 25 は、図 24 に示す固体撮像素子 61 の撮像領域 21 の一部をなす既定部分領域 AR を示す回路図であり、図 4 に対応している。図 26 は、図 25 に示す回路を抽象化して示す回路図であり、図 5 に対応している。図 27 は、図 24 に示す固体撮像素子 61 の部分領域撮影モード時の読み出し制御の一例を示すタイミングチャートであり、図 8 に対応している。図 24 乃至図 27 において、図 2、図 4、図 5 及び図 8 中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。

【0145】

本実施の形態では、前記第 1 の実施の形態による電子カメラ 1 において、固体撮像素子 4 に代えて固体撮像素子 61 が用いられている。

【0146】

本実施の形態が前記第 1 の実施の形態と異なる所は、列方向に隣り合う 2 つの画素 PX 每に、当該 2 つの画素 PX が 1 組のフローティング容量部 FD、増幅トランジスタ AMP、リセットトランジスタ RST 及び選択トランジスタ SEL、ASEL を共有している点と、垂直走査回路 22 が、図 8 に示すような制御信号 SEL, RST, TX に代えて、図 27 に示すような制御信号 SEL, RST, TXA, TXB を出力するよう構成されている点である。

【0147】

図 24 乃至図 26 では、1 組のフローティング容量部 FD、増幅トランジスタ AMP、リセットトランジスタ RST 及び選択トランジスタ SEL、ASEL を共有する 2 つの画素 PX を、画素ブロック BL として示している。また、図 24 及び図 25 では、画素ブロック BL 内の下側の画素 PX のフォトダイオード PD 及び転送トランジスタ TX をそれぞれ符号 PDA, TXA で示し、画素ブロック BL 内の上側の画素 PX のフォトダイオード PD 及び転送トランジスタ TX をそれぞれ符号 PDB, TXB で示し、両者を区別している。また、転送トランジスタ TXA のゲートに供給される制御信号を TXA とし、転送トランジスタ TXB のゲート電極に供給される制御信号を TXB とし、両者を区別している。

【0148】

図 2 及び図 4 では N, n 等は画素行を示しているが、図 24 及び図 25 では N, n 等は画素ブロック BL の行を示している。画素ブロック BL の 1 行は、画素 PX の 2 行に相当している。図 4 及び図 5 では、各既定部分領域 AR は A 行 B 列の A × B 個の画素 PX からなるが、図 25 及び図 26 では、各既定部分領域 AR は A 行 B 列の A × B 個の画素ブロック BL (2 × A × B 個の画素 PX) からなる。なお、各既定部分領域 AR を構成するフォト

10

20

30

40

50

ダイオードPDの行数は2以上でかつフォトダイオードPDの列数は1以上であればよく、本実施の形態では、1つの画素ブロックBLが2つのフォトダイオードPDを有しているので、各既定部分領域ARを構成する画素ブロックBLの行数は1以上でかつ画素ブロックBLの列数は1以上であればよい。

【0149】

本実施の形態では、部分領域撮影モードにおいて、読み出す部分領域が図6や図9に示すように設定される場合には、例えば、図8に示す読み出し制御に代えて、図27に示す読み出し制御が行われる。なお、ここでは、図6及び図9中のnは画素ブロックBLの行を示し、図6及び図9中のmは画素ブロックBLの列を示すものとする。

【0150】

図27に示す例では、垂直走査回路22によって、期間T1において、各既定部分領域ARにおける1行目の画素ブロックBLの行に相当する撮像領域21における1行目、4行目及び7行目の画素ブロックBLの行について同時に読み出し制御が行われ、その次の期間T2において、各既定部分領域ARにおける2行目の画素ブロックBLの行に相当する撮像領域21における2行目、5行目及び8行目の画素ブロックBLの行について同時に読み出し制御が行われ、その次の期間T3において、各既定部分領域ARにおける3行目の画素ブロックBLの行に相当する撮像領域21における3行目、6行目及び9行目の画素ブロックBLの行について同時に読み出し制御が行われ、これにより1フレーム分の読み出しが終了する。期間T1～T3を順次繰り返すことで、複数のフレームがローリング電子シャッタにより読み出される。

10

【0151】

本実施の形態では、部分領域撮影モードにおいて、読み出す部分領域が図11に示すように設定されることも許容する場合には、垂直走査回路22は、図27に示す読み出し制御に代えて、例えば、図8に示す読み出し制御を図27に示す読み出し制御に変形したのと同様に図13に示す読み出し制御を変形した読み出し制御を行えばよい。なお、ここでは、図11中のnは画素ブロックBLの行を示し、図11中のmは画素ブロックBLの列を示すものとする。

20

【0152】

この例では、垂直走査回路22は、読み出す図11に示す部分領域の設定に応じて、2つ以上の画素PXの出力信号が同時に同じ垂直信号線27に読み出されることがないこと必要条件として、可能な限り多くの画素ブロックBLの行について同時に読み出し制御が行われるように、読み出し制御を行う。

30

【0153】

本実施の形態では、領域設定回路23は、部分領域撮影モードにおいて、読み出す部分領域の設定に際して、既定部分領域ARのいずれの列においても、2つ以上の既定部分領域ARは読み出す領域として同時に設定しないという制約の下で、読み出す領域を任意に設定し得るようにしておき、垂直走査回路22は、部分領域撮影モードにおいて常に図27に示す読み出し制御を行うように構成してもよい。以下の説明では、このような構成を「制約有り部分領域設定の構成」と呼ぶ。この場合には、図6に示すような領域設定や図9に示すような領域設定は許容されるが、図11に示すような領域設定は許容されない。

40

【0154】

あるいは、本実施の形態では、領域設定回路23は、部分領域撮影モードにおいて、読み出す部分領域の設定に際して、何らの制約もなく読み出す領域を任意に設定し得るようにしておき、垂直走査回路22は、部分領域撮影モードにおいて、部分領域の設定に応じて、2つ以上の画素PXの出力信号が同時に同じ垂直信号線27に読み出されることがないこと必要条件として、可能な限り多くの画素ブロックBLの行について同時に読み出し制御が行われるような読み出し制御を行うように構成してもよい。以下の説明では、このような構成を「制約無し部分領域設定の構成」と呼ぶ。この場合には、図6に示すような領域設定や図9に示すような領域設定のみならず、図11に示すような領域設定も許容される。垂直走査回路22は、図6に示すような領域設定や図9に示すような領域設定の場合

50

には、例えば、図27に示す読み出し制御を行い、図11に示すような領域設定の場合には、例えば、図8に示す読み出し制御を図27に示す読み出し制御に変形したのと同様に図13に示す読み出し制御を変形した読み出し制御を行う。

【0155】

本実施の形態では、全領域撮影モードでは、例えば、図8に示す読み出し制御を図27に示す読み出し制御に変形したのと同様に図14に示す読み出し制御を変形した読み出し制御が行われる。この例では、垂直走査回路22によって、撮像領域21における1行目の画素ブロックBLの行から9行目の画素ブロックBLの行まで1行ずつについて順次読み出し制御が行われ、これにより1フレーム分の読み出しが終了する。静止画撮影時の全領域撮影モードでは、全画素PXを同時にリセットするいわゆるグローバルリセット後にメカニカルシャッタ(図示せず)により露光が行われ、その後に1行目から9行目までの各行の画素ブロックBLの読み出しが行われる。動画撮影時の全領域撮影モードでは、1行目から9行目までの各行の画素ブロックBLの読み出しが順次繰り返され、複数のフレームがローリング電子シャッタにより読み出される。

10

【0156】

本実施の形態によっても、前記第1の実施の形態と同様の利点が得られる。なお、本実施の形態では、列方向に隣り合う2つの画素PX毎に、当該2つの画素PXが1組のフローティング容量部FD、増幅トランジスタAMP、リセットトランジスタRST及び選択トランジスタSEL, ASELを共有しているが、本発明では、例えば、列方向に隣り合う3つ以上の所定数の画素PX毎に、当該所定数の画素PXが1組のフローティング容量部FD、増幅トランジスタAMP、リセットトランジスタRST及び選択トランジスタSEL, ASELを共有するようにしてもよい。また、本発明では、前記第1の実施の形態を本実施の形態に変形したのと同様の変形を、前記第2及び第3の実施の形態に適用してもよい。

20

【0157】

【第5の実施の形態】

【0158】

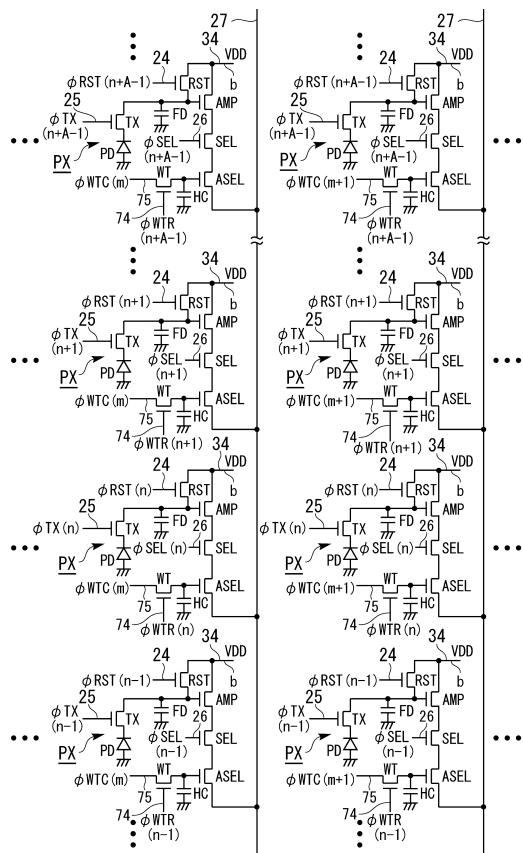

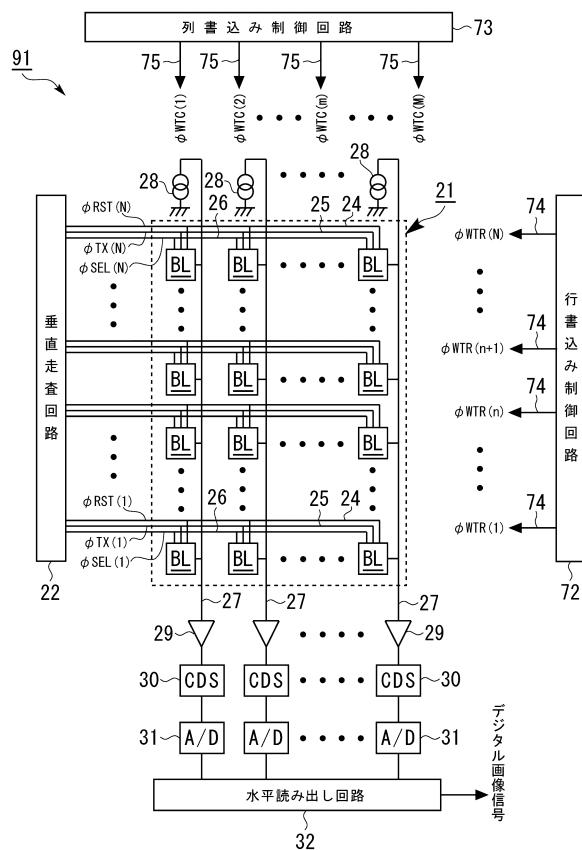

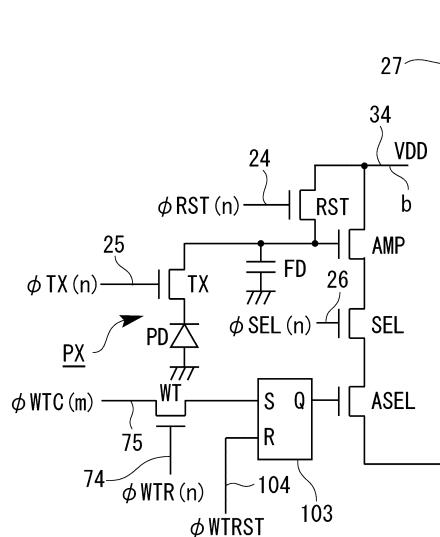

図28は、本発明の第5の実施の形態による電子カメラで用いられる固体撮像素子71の概略構成を示す回路図であり、図2に対応している。図29は、図28に示す固体撮像素子71の撮像領域21の一部を示す回路図であり、図4に対応している。

30

【0159】

図28及び図29において、図2及び図4中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。本実施の形態が前記第1の実施の形態と異なる所は、以下に説明する点である。

【0160】

本実施の形態では、前記第1の実施の形態による電子カメラ1において、固体撮像素子4に代えて固体撮像素子71が用いられている。

【0161】

本実施の形態では、撮像領域21は各既定部分領域ARには分けられていない。また、本実施の形態では、領域設定回路23に代えて、行書き込み制御回路72及び列書き込み制御回路73が設けられている。

40

【0162】

さらに、本実施の形態では、各画素PXにおいて、コンデンサHC及び書き込みトランジスタWTが追加されている。各画素PXのコンデンサHCは、接地と当該画素PXの選択トランジスタASELのゲートとの間に接続され、当該画素PXの選択トランジスタASELを選択状態又は非選択状態にするための選択制御信号を保持する保持部を構成している。各画素PXの書き込みトランジスタWTは、書き込み制御信号WTR, WTCに応じて前記選択制御信号を当該画素PXの前記保持部としてのコンデンサHCに書き込む書き込み部を構成している。

【0163】

50

本実施の形態では、書き込みトランジスタWTはnMOSトランジスタである。各画素PXの書き込みトランジスタWTのソースは、当該画素PXの選択トランジスタASELのゲートに接続されている。各画素PXの書き込みトランジスタWTのゲートは、画素PXの行毎に制御線74により共通に接続され、そこには、行書き込み制御回路72から第1の書き込み制御信号WTRが供給される。各画素PXの書き込みトランジスタWTのドレインは、画素PXの列毎に共通に接続され、そこには、列書き込み制御回路73から第2の書き込み制御信号WTCが供給される。各画素PXの書き込みトランジスタWTは、そのゲートに供給される第1の書き込み制御信号WTRと、そのドレインに供給される第2の書き込み制御信号WTCとのアンドをとってそのアンド出力をそのソースに出力するアンド回路を構成している。前記書き込み部として、書き込みトランジスタWTに代えて、例えば他のアンド回路を用いてもよい。

10

#### 【0164】

各第1の書き込み制御信号WTRを画素PXの行毎に区別する場合、n行目の画素PXの書き込みトランジスタWTのゲートに供給される第1の書き込み制御信号WTRは符号WTR(n)で示す。各第2の書き込み制御信号WTCを画素PXの列毎に区別する場合、m列目の画素PXの書き込みトランジスタWTのドレインに供給される第2の書き込み制御信号WTCは符号WTC(m)で示す。

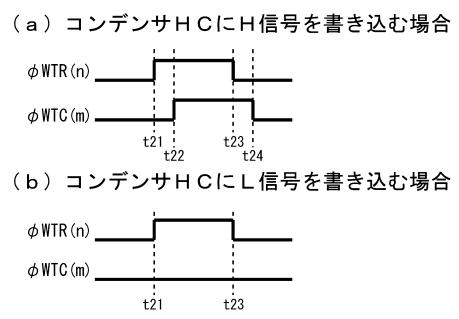

#### 【0165】

図30(a)は、図28に示す固体撮像素子71において、n行目かつm列目の画素PXのコンデンサHCにハイレベル信号(H信号)を書き込む場合の書き込み制御信号WTR(n), WTC(m)を示す図である。時点t21でn行目の書き込み制御信号WTR(n)をハイレベルに立ち上げ、その後の時点t22でm列目の書き込み制御信号WTC(m)をハイレベルに立ち上げ、その後の時点t23で書き込み制御信号WTR(n)をローレベルに立ち下げ、その後の時点t24で書き込み制御信号WTCを立ち下げる。これにより、n行目かつm列目の画素PXのコンデンサHCにハイレベル信号が書き込まれて保持される。その結果、n行目かつm列目の画素PXの選択トランジスタASELがオン状態(選択状態)に保持される。

20

#### 【0166】

図30(b)は、図28に示す固体撮像素子71において、n行目かつm列目の画素PXのコンデンサHCにローレベル信号(L信号)を書き込む場合の書き込み制御信号WTR(n), WTC(m)を示す図である。m列目の書き込み制御信号WTC(m)をローレベルに維持したまま、時点t21でn行目の書き込み制御信号WTR(n)をハイレベルに立ち上げ、その後の時点t23で書き込み制御信号WTR(n)をローレベルに立ち下げる。これにより、n行目かつm列目の画素PXのコンデンサHCにローレベル信号が書き込まれて保持される。その結果、n行目かつm列目の画素PXの選択トランジスタASELがオフ状態(非選択状態)に保持される。

30

#### 【0167】

行書き込み制御回路72は、図1中の撮像制御部5による制御下で、画素PXの行毎に第1の書き込み制御信号WTRを供給する。列書き込み制御回路73は、図1中の撮像制御部5による制御下で、画素PXの列毎に第2の書き込み制御信号WTCを供給する。行書き込み制御回路72及び列書き込み制御回路73は、全体として、各画素PXの書き込み部としての書き込みトランジスタWTに書き込み制御信号WTR, WTCを供給する書き込み制御部を構成している。

40

#### 【0168】

本実施の形態では、行書き込み制御回路72、列書き込み制御回路73、並びに、各画素PXの書き込みトランジスタWT及びコンデンサHCは、全体として、撮像領域21のうちの読み出す所望の1つ又は複数の部分領域の画素PXの選択トランジスタASELを選択状態(オン状態)にする領域設定部を構成している。

#### 【0169】

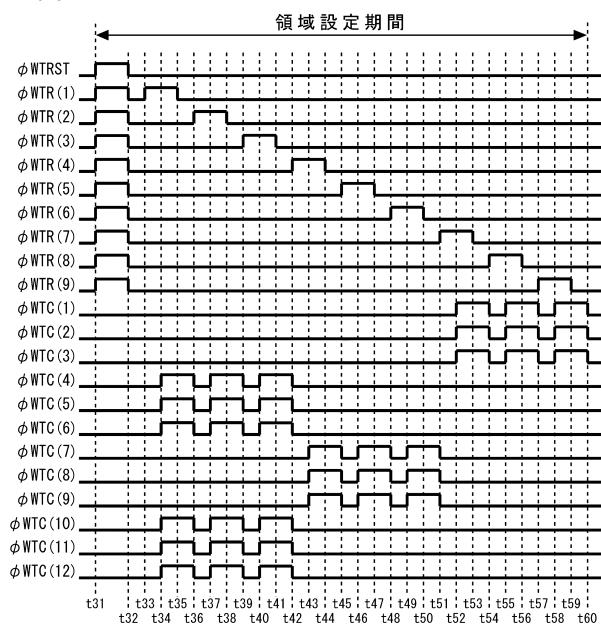

図31は、図28に示す固体撮像素子71において図6に示す領域設定例と同じ設定を実

50

現する書き込み制御信号 WTR, WTC を示すタイミングチャートである。ここでは、図 6 において、各既定部分領域 AR には分けられていないものとするが、ハッチングを付した 4 つの部分領域を、読み出す 4 つの部分領域とする。

【0170】

図 31 に示す例では、まず、全画素 PX のコンデンサ HC にローレベル信号を書き込んだ後に、1 行ずつの画素 PX を順次選びつつ、当該行のうちの必要な画素 PX のコンデンサ HC にハイレベル信号を書き込むことによって、図 6 においてハッチングを付した 4 つの部分領域を、読み出す領域として設定する。

【0171】

具体的には、領域設定期間（読み出す領域を設定する期間）が開始すると、まず、期間  $t_{31} - t_{32}$  において、WTR(1) ~ WTR(9) がハイレベルにされ、WTC(1) ~ WTC(12) がローレベルにされる一方で、WTC(4) ~ WTC(6), WTC(10) ~ WTC(12) がハイレベルにされる。これにより、図 30 (b) から理解できるように、全画素 PX のコンデンサ HC にローレベル信号が書き込まれる。

10

【0172】

次に、期間  $t_{33} - t_{35}$  において WTR(1) がハイレベルにされ、期間  $t_{34} - t_{36}$  において WTC(4) ~ WTC(6), WTC(10) ~ WTC(12) がハイレベルにされる。これにより、図 30 (a) から理解できるように、1 行目の画素 PX のうちの 4 ~ 6 列目及び 10 ~ 12 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

【0173】

次いで、期間  $t_{36} - t_{38}$  において WTR(2) がハイレベルにされ、期間  $t_{37} - t_{39}$  において WTC(4) ~ WTC(6), WTC(10) ~ WTC(12) がハイレベルにされる。これにより、2 行目の画素 PX のうちの 4 ~ 6 列目及び 10 ~ 12 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

20

【0174】

引き続いて、期間  $t_{39} - t_{41}$  において WTR(3) がハイレベルにされ、期間  $t_{40} - t_{42}$  において WTC(4) ~ WTC(6), WTC(10) ~ WTC(12) がハイレベルにされる。これにより、3 行目の画素 PX のうちの 4 ~ 6 列目及び 10 ~ 12 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

【0175】

その後、期間  $t_{42} - t_{44}$  において WTR(4) がハイレベルにされ、期間  $t_{43} - t_{45}$  において WTC(7) ~ WTC(9) がハイレベルにされる。これにより、4 行目の画素 PX のうちの 7 ~ 9 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

30

【0176】

次に、期間  $t_{45} - t_{47}$  において WTR(5) がハイレベルにされ、期間  $t_{46} - t_{48}$  において WTC(7) ~ WTC(9) がハイレベルにされる。これにより、5 行目の画素 PX のうちの 7 ~ 9 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

【0177】

次いで、期間  $t_{48} - t_{50}$  において WTR(6) がハイレベルにされ、期間  $t_{49} - t_{51}$  において WTC(7) ~ WTC(9) がハイレベルにされる。これにより、6 行目の画素 PX のうちの 7 ~ 9 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

40

【0178】

引き続いて、期間  $t_{51} - t_{53}$  において WTR(7) がハイレベルにされ、期間  $t_{52} - t_{54}$  において WTC(1) ~ WTC(3) がハイレベルにされる。これにより、7 行目の画素 PX のうちの 1 ~ 3 列目の画素 PX のコンデンサ HC にハイレベル信号が書き込まれる。

【0179】

50

その後、期間  $t_{54} - t_{56}$  において  $WTR(8)$  がハイレベルにされ、期間  $t_{55} - t_{57}$  において  $WTC(1) \sim WTC(3)$  がハイレベルにされる。これにより、8行目の画素  $PX$  のうちの1～3列目の画素  $PX$  のコンデンサ  $H_C$  にハイレベル信号が書き込まれる。

【0180】

最後に、期間  $t_{57} - t_{59}$  において  $WTR(9)$  がハイレベルにされ、期間  $t_{58} - t_{60}$  において  $WTC(1) \sim WTC(3)$  がハイレベルにされる。これにより、9行目の画素  $PX$  のうちの1～3列目の画素  $PX$  のコンデンサ  $H_C$  にハイレベル信号が書き込まれる。

【0181】

このようにして、図6中のハッチングが付された画素  $PX$  のコンデンサ  $H_C$  にハイレベル信号が書き込まれて、当該画素  $PX$  の選択トランジスタ  $ASEL$  がオン状態に維持され、図6中のハッチングが付されていない画素  $PX$  のコンデンサ  $H_C$  にローレベル信号が書き込まれて、当該画素  $PX$  の選択トランジスタ  $ASEL$  がオフ状態に維持され、図6に示す領域設定が実現される。

10

【0182】

本実施の形態では、例えば、図31と同様に、まず、全画素  $PX$  のコンデンサ  $H_C$  にローレベル信号を書き込んだ後に、1行ずつの画素  $PX$  を順次選びつつ、当該行のうちの所望の画素  $PX$  のコンデンサ  $H_C$  にハイレベル信号を書き込むことによって、撮像領域21のうちの所望の任意の1つ又は複数の部分領域、あるいは、撮像領域21の全領域を、読み出す領域として設定することができる。

20

【0183】

なお、一旦領域設定期間を行った後に、その領域設定を変更することなく長時間に渡って次回の領域設定期間を行わない場合には、コンデンサ  $H_C$  に書き込まれたハイレベル信号が低下してしまって適切に保持されないおそれがある。そこで、領域設定を変更しない場合であっても、一旦領域設定期間を行った後に一定時間内に領域設定期間を行い、コンデンサ  $H_C$  に書き込まれた信号をリフレッシュすることが好ましい。

【0184】

読み出し制御については、本実施の形態においても前記第1の実施の形態と同様である。また、本実施の形態においても、前記第1の実施の形態における制約有り部分領域設定の構成と同様の構成を採用してもよいし、前記第1の実施の形態における制約無し部分領域設定の構成と同様の構成を採用してもよい。

30

【0185】

本実施の形態によっても、前記第1の実施の形態と同様の利点が得られる。また、前記第1の実施の形態では、読み出す領域に各既定部分領域  $AR$  を含めるか否かによって、撮像領域21のうちの読み出す領域の設定を行うのに対し、本実施の形態では、読み出す領域に各画素  $PX$  を含めるか否かによって、撮像領域21のうちの読み出す領域の設定を行う。したがって、本実施の形態によれば、各画素  $PX$  において書き込みトランジスタ  $WT$  及びコンデンサ  $H_C$  を要するものの、前記第1の実施の形態に比べて、撮像領域21のうちの読み出す領域の設定の自由度が高まる。

40

【0186】

[第6の実施の形態]

【0187】

図32は、本発明の第6の実施の形態による電子カメラで用いられる固体撮像素子81の概略構成を示す回路図であり、図28に対応している。図33は、図32に示す固体撮像素子81の撮像領域21の一部を示す回路図であり、図29に対応している。

【0188】

図32及び図33において、図28及び図29中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。本実施の形態が前記第5の実施の形態と異なる所は、以下に説明する点である。

50

## 【0189】

本実施の形態では、前記第5の実施の形態による電子カメラにおいて、固体撮像素子71に代えて固体撮像素子81が用いられている。

## 【0190】

前記第5の実施の形態では、撮像領域21の各画素PXにおいて選択トランジスタSEL設けられているのに対し、本実施の形態では、撮像領域21の各画素PXにおいて、選択トランジスタSEL及び接続線26が取り除かれ、選択トランジスタASELのドレインが、当該画素PXの増幅トランジスタAMPのソースに接続されている。

## 【0191】

前記第5の実施の形態では、全画素PXの増幅トランジスタAMPのドレイン(図29中のb点)は、給電線34により共通に接続され、そこには、増幅トランジスタAMPの電源電圧として、増幅トランジスタAMPの動作に有効である有効電圧レベルVDDが固定的に供給される。これに対し、本実施の形態では、給電線34は画素PXの行毎に電気的に分離され、各画素PXの増幅トランジスタAMPのドレイン(図33中のb点)は、画素PXの行毎に給電線34により共通に接続され、そこには、増幅トランジスタAMPの電源電圧として電源電圧信号VDDが、給電制御回路52から供給される。各電源電圧信号VDDを画素PXの行毎に区別する場合、n行目の画素PXの増幅トランジスタAMPのドレインに供給される電源電圧信号VDDは符号VDD(n)で示す。なお、各画素PXのリセットトランジスタRSTのドレインは、給電線34により、当該画素PXの増幅トランジスタAMPのドレイン(図33中のb点)に接続されている。

10

## 【0192】

本実施の形態では、給電制御回路52は、垂直走査回路22の一部として設けられ、撮像制御部5による制御下で、各制御信号SELに代えて各電源電圧信号VDDを出力する。各電源電圧信号VDDは、増幅トランジスタAMPの動作に有効である有効電圧レベルVDD、又は、増幅トランジスタAMPの動作に有効ではない非有効電圧レベル(ここでは、0Vとするが、必ずしも0Vに限らない。)となり、給電制御回路52は、各画素PXの増幅トランジスタAMPの電源電圧としてVDD又は0Vを選択的に供給する。

20

## 【0193】

本実施の形態において、各画素PXにおいて電源電圧信号VDDがVDDとなって増幅トランジスタAMPが有効に動作する状態及び電源電圧信号VDDが0Vとなって増幅トランジスタAMPが有効に動作しない状態は、各画素PXの出力信号の垂直信号線27への出力の可否に関して、前記第5の実施の形態において、各画素PXにおいて制御信号SELがハイレベルになって選択トランジスタSELがオンした状態及び制御信号SELがローレベルになって選択トランジスタSELがオフした状態と、それぞれ実質的に同じになる。

30

## 【0194】

したがって、本実施の形態では、各画素PXの出力信号は、当該画素PXの選択トランジスタASELが選択状態(オン状態)であるとともに当該画素PXの増幅トランジスタAMPの電源電圧として供給される電源電圧信号VDDが有効電圧レベルVDDである場合にのみ、当該画素PXの出力信号及び当該画素PXに対して列方向に並んだ画素PXの出力信号を受け取る垂直信号線27に出力される。

40

## 【0195】

本実施の形態では、給電制御回路52が、前記第5の実施の形態において各SELとしてハイレベル信号を供給する代わりに各電源電圧信号VDDとして有効電圧レベルVDDを供給し、前記第5の実施の形態において各SELとしてローレベル信号を供給する代わりに各電源電圧信号VDDとして0Vを供給することによって、前記第5の実施の形態と同様の動作が実現される。

## 【0196】

本実施の形態によっても、前記第5の実施の形態と同様の利点が得られる。また、本実施の形態では、各画素PXにおいて選択トランジスタASELが設けられていないので、各

50

画素 P X の構成が簡単となる。

【 0 1 9 7 】

[ 第 7 の実施の形態 ]

【 0 1 9 8 】

図 3 4 は、本発明の第 7 の実施の形態による電子カメラで用いられる固体撮像素子 9 1 の概略構成を示す回路図であり、図 2 8 に対応している。図 3 5 は、図 3 4 に示す固体撮像素子 9 1 の撮像領域 2 1 の一部を示す回路図であり、図 2 9 に対応している。図 3 4 及び図 3 5 において、図 2 8 及び図 2 9 中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。

【 0 1 9 9 】

本実施の形態では、前記第 5 の実施の形態による電子カメラにおいて、固体撮像素子 7 1 に代えて固体撮像素子 9 1 が用いられている。

【 0 2 0 0 】

本実施の形態が前記第 5 の実施の形態と異なる所は、列方向に隣り合う 2 つの画素 P X 每に、当該 2 つの画素 P X が 1 組のフローティング容量部 F D 、増幅トランジスタ A M P 、リセットトランジスタ R S T 、選択トランジスタ S E L , A S E L 、書き込みトランジスタ W T 及びコンデンサ H C を共有している点と、垂直走査回路 2 2 が、図 8 に示すような制御信号 S E L , R S T , T X に代えて、図 2 7 に示すような制御信号 S E L , R S T , T X A , T X B を出力するように構成されている点である。

【 0 2 0 1 】

図 3 4 及び図 3 5 では、1 組のフローティング容量部 F D 、増幅トランジスタ A M P 、リセットトランジスタ R S T 、選択トランジスタ S E L , A S E L 、書き込みトランジスタ W T 及びコンデンサ H C を共有する 2 つの画素 P X を、画素ブロック B L として示している。また、図 3 4 及び図 3 5 では、画素ブロック B L 内の下側の画素 P X のフォトダイオード P D 及び転送トランジスタ T X をそれぞれ符号 P D A , T X A で示し、画素ブロック B L 内の上側の画素 P X のフォトダイオード P D 及び転送トランジスタ T X をそれぞれ符号 P D B , T X B で示し、両者を区別している。また、転送トランジスタ T X A のゲートに供給される制御信号を T X A とし、転送トランジスタ T X B のゲート電極に供給される制御信号を T X B とし、両者を区別している。

【 0 2 0 2 】

図 2 8 及び図 2 9 では N , n 等は画素行を示しているが、図 3 4 及び図 3 5 では N , n 等は画素ブロック B L の行を示している。画素ブロック B L の 1 行は、画素 P X の 2 行に相当している。

【 0 2 0 3 】

読み出し制御については、本実施の形態においても前記第 4 の実施の形態と同様である。また、本実施の形態においても、前記第 4 の実施の形態における制約有り部分領域設定の構成と同様の構成を採用してもよいし、前記第 4 の実施の形態における制約無し部分領域設定の構成と同様の構成を採用してもよい。

【 0 2 0 4 】

本実施の形態によつても、前記第 5 の実施の形態と同様の利点が得られる。なお、本実施の形態では、列方向に隣り合う 2 つの画素 P X 每に、当該 2 つの画素 P X が 1 組のフローティング容量部 F D 、増幅トランジスタ A M P 、リセットトランジスタ R S T 、選択トランジスタ S E L , A S E L 、書き込みトランジスタ W T 及びコンデンサ H C を共有しているが、本発明では、例えば、列方向に隣り合う 3 つ以上の所定数の画素 P X 每に、当該所定数の画素 P X が 1 組のフローティング容量部 F D 、増幅トランジスタ A M P 、リセットトランジスタ R S T 、選択トランジスタ S E L , A S E L 、書き込みトランジスタ W T 及びコンデンサ H C を共有するようにしてもよい。また、本発明では、前記第 5 の実施の形態を本実施の形態に変形したのと同様の変形を、前記第 6 の実施の形態に適用してもよい。

【 0 2 0 5 】

[ 第 8 の実施の形態 ]

10

20

30

40

50

## 【0206】

図36は、本発明の第8の実施の形態による電子カメラで用いられる固体撮像素子101の概略構成を示す回路図であり、図28に対応している。図37は、図36に示す固体撮像素子101の1つの画素PX(n行目かつm列目の画素PX)を示す回路図であり、図29中の一部に対応している。図38は、図36に示す固体撮像素子101において図6に示す設定例と同じ設定を実現する書き込み制御信号を示すタイミングチャートであり、図31に対応している。

## 【0207】

図36乃至図38において、図28、図29及び図31中の要素と同一又は対応する要素には同一符号を付し、その重複する説明は省略する。本実施の形態が前記第5の実施の形態と異なる所は、以下に説明する点である。

10

## 【0208】

本実施の形態では、前記第5の実施の形態による電子カメラにおいて、固体撮像素子71に代えて固体撮像素子101が用いられている。

## 【0209】

本実施の形態では、各画素PXにおいて、当該画素PXの選択トランジスタASELを選択状態又は非選択状態にするための選択制御信号を保持する保持部として、コンデンサHCに代えて、SRラッチ回路103が設けられている。また、本実施の形態では、固体撮像素子101において、SRラッチ回路103のリセット入力部Rに書き込み制御信号の一部をなすリセット信号WTRSTを供給するリセット書き込み制御回路102が追加されている。SRラッチ回路103は、例えば、1組のたすきがけになったNORゲートで構成することができるが、これに限らない。

20

## 【0210】

全画素PXのSRラッチ回路103のリセット入力部Rは制御線104により共通に接続され、そこには、リセット書き込み制御回路102からのリセット信号WTRSTが供給される。各画素PXのSRラッチ回路103のセット入力部Sは、当該画素PXの書き込みトランジスタWTのソースに接続されている。各画素PXのSRラッチ回路103の出力部Qは、当該画素PXの選択トランジスタASELのゲートに接続されている。

## 【0211】

図38と図31との比較からわかるように、本実施の形態では、期間t31-t32において、全画素PXの選択トランジスタASELのゲートに保持される信号としてローレベル信号を書き込むために、WTR(1)~WTR(9)がハイレベルにされる一方でWTC(1)~WTC(12)がローレベルにされて全画素PXのSRラッチ回路103のセット入力部Sにハイレベルを供給するだけでなく、全画素PXのSRラッチ回路103のリセット入力部Rに供給されるリセット信号WTRSTがハイレベルにされる。他の期間においては、リセット信号WTRSTは、ローレベルに維持される。

30

## 【0212】

本実施の形態では、行書き込み制御回路72、列書き込み制御回路73及びリセット書き込み制御回路102は、全体として、各画素PXの書き込み部としての書き込みトランジスタWTに書き込み制御信号WTR、WTC、WTRSTを供給する書き込み制御部を構成している。

40

## 【0213】

本実施の形態では、行書き込み制御回路72、列書き込み制御回路73、リセット書き込み制御回路102、並びに、各画素PXの書き込みトランジスタWT及びラッチ回路103が、撮像領域21のうちの読み出す所望の1つ又は複数の部分領域の画素PXの選択トランジスタASELを選択状態(オン状態)にする領域設定部を構成している。

## 【0214】

本実施の形態によっても、前記第5の実施の形態と同様の利点が得られる。なお、本実施の形態では、前記第5の実施の形態において説明したリフレッシュの動作は不要である。

## 【0215】

50

なお、本発明では、前記第5の実施の形態を本実施の形態に変形したのと同様の変形を、前記第6及び第7の実施の形態に適用してもよい。また、前記保持部として、コンデンサH CやS R ラッチ回路103に代えて、他のラッチ回路やその他のメモリを用いてもよい。さらに、前記保持部として不揮発性メモリを用いてもよい。この場合、電源遮断時に、全画素P Xの当該不揮発性メモリに当該画素を読み出し領域とする情報に記憶させるようにしておくことで、電源投入直後から初期的に、撮像領域21の全領域を読み出し領域とする状態にすることができる。そうすることで、例えば、電源投入直後に静止画撮影を行うような場合に、その静止画撮影を迅速に開始することができ、シャッターチャンスを逃さずにすむ。

## 【0216】

10

以上、本発明の各実施の形態及びそれらの変形例について説明したが、本発明はこれらに限定されるものではない。

## 【0217】

例えば、前記各実施の形態において、列方向に隣り合う各2つの画素P X又は列方向に隣り合う各2つの画素ブロックB Lの増幅トランジスタA M Pのゲート間をオンオフ（電気的に接続及び遮断）する各連結スイッチを設けてもよい。

## 【0218】

また、前記各実施の形態では、同じ列に並んだ画素P Xの出力信号は同じ垂直信号線27に出力されるように構成されているが、同じ列に並んだ画素P Xを複数のグループに分け、そのグループ毎に異なる垂直信号線27に画素出力信号が出力されるように構成してもよい。

20

## 【0219】

さらに、本発明では、固体撮像素子は、単一のチップで構成されたものに限らず、複数のチップを接合した構造を有していてもよい。

## 【0220】

なお、本発明では、前記各実施の形態及びそれらの変形例の各事項は適宜組み合わせてもよい。

## 【符号の説明】

## 【0221】

30

1 電子カメラ

4 固体撮像素子

21 撮像領域

22 垂直走査回路

23 領域設定回路

72 行書き込み制御回路

73 列書き込み制御回路

P X 画素

P D フォトダイオード

T X 転送トランジスタ

A M P 増幅トランジスタ

R S T リセットトランジスタ

F D フローティング容量部

S E L , A S E L 選択トランジスタ

A R 既定部分領域

B L 画素ブロック

W T 書き込みトランジスタ

H C コンデンサ

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図 9】

|       |        |        |        |

|-------|--------|--------|--------|

|       |        |        | 21     |

| $n=9$ | AR     | AR     | AR     |

| $n=8$ | (3, 1) | (3, 2) | (3, 3) |

| $n=7$ |        |        |        |

| $n=6$ | AR     | AR     | AR     |

| $n=5$ | (2, 1) | (2, 2) | (2, 3) |

| $n=4$ |        |        | (2, 4) |

| $n=3$ | AR     | AR     | AR     |

| $n=2$ | (1, 1) | (1, 2) | (1, 3) |

| $n=1$ |        |        | (1, 4) |

| $m=1$ | $m=2$  | $m=3$  | $m=4$  |

| $m=5$ | $m=6$  | $m=7$  | $m=8$  |

| $m=9$ | $m=10$ | $m=11$ | $m=12$ |

【図 10】

20

【図 11】

|       |        |        |        |

|-------|--------|--------|--------|

|       |        |        | 21     |

| $n=9$ | AR     | AR     | AR     |

| $n=8$ | (3, 1) | (3, 2) | (3, 3) |

| $n=7$ |        |        |        |

| $n=6$ | AR     | AR     | AR     |

| $n=5$ | (2, 1) | (2, 2) | (2, 3) |

| $n=4$ |        |        | (2, 4) |

| $n=3$ | AR     | AR     | AR     |

| $n=2$ | (1, 1) | (1, 2) | (1, 3) |

| $n=1$ |        |        | (1, 4) |

| $m=1$ | $m=2$  | $m=3$  | $m=4$  |

| $m=5$ | $m=6$  | $m=7$  | $m=8$  |

| $m=9$ | $m=10$ | $m=11$ | $m=12$ |

【図 12】

40

50

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

10

20

30

40

50

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

10

20

30

40

50

## 【図25】

【 図 2 6 】

【図27】

【図28】

【図 2 9】

【図 3 0】

10

20

30

40

【図 3 1】

【図 3 2】

50

【図 3 3】

【図 3 4】

【図 3 5】

【図 3 6】

10

20

30

40

50

【図 3 7】

【図 3 8】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 国際公開第2013/145765 (WO, A1)

特開2012-054876 (JP, A)

特開2015-173389 (JP, A)

特開2010-098621 (JP, A)

国際公開第2015/022900 (WO, A1)

(58)調査した分野 (Int.Cl., DB名)

H04N 5/30 - 5/378