(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-271969

(P2007-271969A)

(43) 公開日 平成19年10月18日(2007.10.18)

| (51) Int.C1.      | F 1                 | テーマコード (参考)    |

|-------------------|---------------------|----------------|

| <b>G09G 3/30</b>  | (2006.01) G09G 3/30 | H 3K107        |

| <b>G09G 3/20</b>  | (2006.01) G09G 3/20 | 623F 5C080     |

| <b>H01L 51/50</b> | (2006.01) G09G 3/20 | 623R           |

|                   |                     | G09G 3/20 612R |

|                   |                     | G09G 3/20 680G |

審査請求 未請求 請求項の数 6 O L (全 15 頁) 最終頁に続く

|           |                            |          |                                            |

|-----------|----------------------------|----------|--------------------------------------------|

| (21) 出願番号 | 特願2006-97998 (P2006-97998) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成18年3月31日 (2006.3.31)     | (74) 代理人 | 100090538<br>弁理士 西山 恵三                     |

|           |                            | (74) 代理人 | 100096965<br>弁理士 内尾 裕一                     |

|           |                            | (72) 発明者 | 川崎 素明<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

|           |                            | (72) 発明者 | 井関 正己<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

最終頁に続く

(54) 【発明の名称】 カラー表示装置及びアクティブマトリクス装置

## (57) 【要約】

【課題】 DACの特性ばらつきによる表示不均一性を低減する。

【解決手段】 色画素がマトリクス状に配置されたカラー表示部9と、複数のデータ線14と、データ信号を複数のデータ線に行毎に出力する複数の列駆動回路1と、を有するカラー表示装置において、デジタル映像信号を色毎に各々DA変換して得られた色毎のアナログ映像信号の出力先となる列駆動回路を選択するための第1の選択回路13と、列駆動回路からデータ信号の出力先となるデータ線14を選択するための第2の選択回路34と、色毎のアナログ映像信号の出力先となる駆動回路とデータ信号の出力先となる前記データ線とを走査期間毎に順次変更するように、第1及び第2の選択回路を制御する制御回路32、35と、を有する。

【選択図】 図11

**【特許請求の範囲】****【請求項 1】**

複数の電気光学素子を有する画素がマトリクス状に配置されたカラー表示部と、前記カラー表示部に列毎に共通に接続された複数のデータ線と、前記カラー表示部の列に対応して設けられ、前記画素に供給されるデータ信号を前記複数のデータ線に行毎に出力する複数の列駆動回路と、

を有するカラー表示装置において、

デジタル映像信号を色毎に各々 D A 変換して得られた色毎のアナログ映像信号の出力先となる前記列駆動回路を選択するための第 1 の選択回路と、

前記列駆動回路からの前記データ信号の出力先となる前記データ線を選択するための第 2 の選択回路と、

前記色毎のアナログ映像信号の出力先となる前記駆動回路と前記データ信号の出力先となる前記データ線とを走査期間毎に順次変更するように、前記第 1 及び第 2 の選択回路を制御する制御回路と、

を有することを特徴とするカラー表示装置。

**【請求項 2】**

前記第 1 の選択回路は単結晶半導体を用いた集積回路であり、前記第 2 の選択回路は非単結晶半導体を用いた集積回路である請求項 1 に記載のカラー表示装置。

**【請求項 3】**

前記第 1 の選択回路と前記第 2 の選択回路とは非単結晶半導体を用いた集積回路である請求項 1 に記載のカラー表示装置。

**【請求項 4】**

前記第 2 の選択回路と前記列駆動回路とは非単結晶半導体を用いた集積回路である請求項 1 に記載のカラー表示装置。

**【請求項 5】**

前記第 1 の選択回路のスイッチの数は、前記列の数より少ない請求項 1 乃至 4 のいずれか 1 項に記載のカラー表示装置。

**【請求項 6】**

複数の画素回路がマトリクス状に配置されたマトリクス部と、前記マトリクス部に列毎に共通に接続された複数のデータ線と、前記マトリクス部の列に対応して設けられ、前記画素回路に供給されるデータ信号を前記複数のデータ線に行毎に出力する複数の列駆動回路と、

を有するアクティブマトリクス装置において、

デジタル映像信号を色毎に各々 D A 変換して得られた色毎のアナログ映像信号の出力先となる前記列駆動回路を選択するための第 1 の選択回路と、

前記列駆動回路からの前記データ信号の出力先となる前記データ線を選択するための第 2 の選択回路と、

前記色毎のアナログ映像信号の出力先となる前記駆動回路と前記データ信号の出力先となる前記データ線とを走査期間毎に順次変更するように、前記第 1 及び第 2 の選択回路を制御する制御回路と、

を有することを特徴とするアクティブマトリクス装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電気光学素子を有する画素又は画素回路をマトリクス状に配置した表示装置及びアクティブマトリクス装置に関する。

**【背景技術】****【0002】**

近年、次世代ディスプレイとして電気光学素子を用いたディスプレイ等が注目されている。ここでは、素子に流れる電流によって発光輝度が制御される電流制御型の発光素子で

10

20

30

40

50

ある有機エレクトロルミネッセンス(EL)素子を例に挙げて説明する。

【0003】

周辺回路を含んだ有機EL表示装置では、表示領域に限らず、周辺回路においても薄膜トランジスタ(TFT)が用いられている。このような自発光素子であるEL素子を画像表示素子に利用し、その表示領域および周辺回路にTFTを用いた画像表示パネルが特許文献1及び特許文献2により知られている。

【特許文献1】特開2004-145296号公報

【特許文献2】特開2004-295081号公報

【発明の開示】

【発明が解決しようとする課題】

10

【0004】

上記画像表示パネルに入力される映像信号は、赤(R)、緑(G)、青(B)の3色毎のデジタルカラー映像信号をデジタル・アナログ変換器(DAC)により変換されたアナログ映像信号である。或いは、デジタル輝度信号とデジタル色差信号をRGBの3色のデジタルカラー映像信号に変換した後、デジタル・アナログ変換器(DAC)により変換されたアナログ映像信号である。

【0005】

この場合、DACは3つ必要になるが、DACが単結晶シリコンを用いた集積回路で構成されているとはいえ、3つのDACは特性ばらつきを有している。

【0006】

本発明者は、このDACの特性ばらつきが、表示パネルにおいて固定パターンの表示不均一性となって顕在化してしまう恐れがあることを見出した。

20

【0007】

本発明の目的は、DACの特性ばらつきによる表示不均一性を低減することができるカラー表示装置及びアクティブマトリクス装置を提供することにある。

【課題を解決するための手段】

【0008】

本発明の第1の骨子は、

複数の電気光学素子を有する画素がマトリクス状に配置されたカラー表示部と、

前記カラー表示部に列毎に共通に接続された複数のデータ線と、

前記カラー表示部の列に対応して設けられ、前記画素に供給されるデータ信号を前記複数のデータ線に行毎に出力する複数の列駆動回路と、

を有するカラー表示装置において、

30

デジタル映像信号を色毎に各々DA変換して得られた色毎のアナログ映像信号の出力先となる前記列駆動回路を選択するための第1の選択回路と、

前記列駆動回路からの前記データ信号の出力先となる前記データ線を選択するための第2の選択回路と、

前記色毎のアナログ映像信号の出力先となる前記駆動回路と前記データ信号の出力先となる前記データ線とを走査期間毎に順次変更するように、前記第1及び第2の選択回路を制御する制御回路と、

40

を有することを特徴とする。

【0009】

本発明の第2の骨子は、

複数の画素回路がマトリクス状に配置されたマトリクス部と、

前記マトリクス部に列毎に共通に接続された複数のデータ線と、

前記マトリクス部の列に対応して設けられ、前記画素回路に供給されるデータ信号を前記複数のデータ線に行毎に出力する複数の列駆動回路と、

を有するアクティブマトリクス装置において、

デジタル映像信号を色毎に各々DA変換して得られた色毎のアナログ映像信号の出力先となる前記列駆動回路を選択するための第1の選択回路と、

50

前記列駆動回路からの前記データ信号の出力先となる前記データ線を選択するための第2の選択回路と、

前記色毎のアナログ映像信号の出力先となる前記駆動回路と前記データ信号の出力先となる前記データ線とを走査期間毎に順次変更するように、前記第1及び第2の選択回路を制御する制御線と、

を有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、列駆動回路の出力先のデータ線を順次変更しながら、その出力を画素或いは画素回路に供給するように構成する。こうして、画素或いは画素回路に供給される電流の値のばらつきを時間的に平均化、換言すれば空間的に分散させることができる。よって、画面に現れる縦筋のような、表示画像の不均一性を視覚的に低減できる。しかも、D A Cからの出力先を変更する選択回路により、D A Cの特性ばらつきによる所定行毎の固定パターンの表示画像の不均一性を視覚的に低減できる。

【発明を実施するための最良の形態】

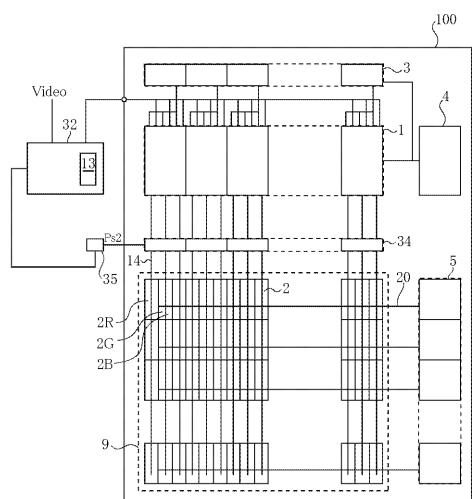

【0011】

図1は、第1の実施形態による表示装置の構成を示す模式図である。図1に示す表示装置は、表示パネル100を有する。表示パネル100の共通基板上には、R G B原色数のE L素子と、このE L素子に入力される電流を制御するためのT F Tから構成される画素回路2とが、積層されている。色毎の画素又は画素回路(2 R、2 G、2 B)は3 N列×M行の2次元状に配列されたカラー表示部(マトリクス部)9を構成しており、周辺回路とともに共通基板上に集積化されている。

【0012】

14は各列毎に共通に画素回路2に接続されて設けられた複数(3 N本)のデータ線、20は各行毎に設けられた複数(M本)の行選択線である。周辺回路には、列駆動回路1、列シフトレジスタ3、行シフトレジスタ5、ゲート回路4と、選択回路34とを備えている。デジタル映像データV i d e oは、信号処理回路32で処理され、信号処理回路内のD A Cに供給される。D A Cからの色毎のアナログ映像信号は、同信号処理回路内の第1の選択回路13を経て列駆動回路1に入力される。

【0013】

表示パネル100の各回路のトランジスタは、多結晶シリコンなどの非単結晶半導体の活性層を有するT F Tで構成される。また、信号処理回路32及び制御回路35のトランジスタは単結晶シリコンなどの単結晶半導体を活性層とするトランジスタで構成されている。

制御回路35は信号処理回路32内に集積化されていてもよい。

【0014】

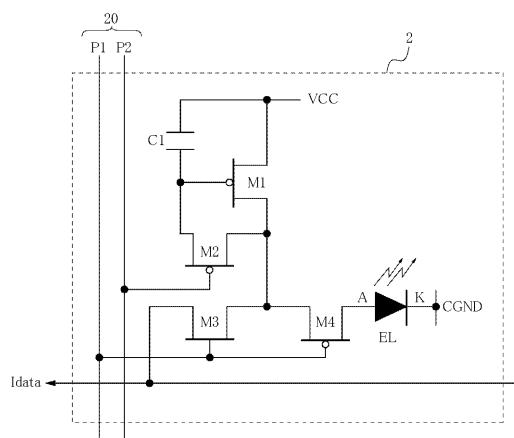

(画素回路)

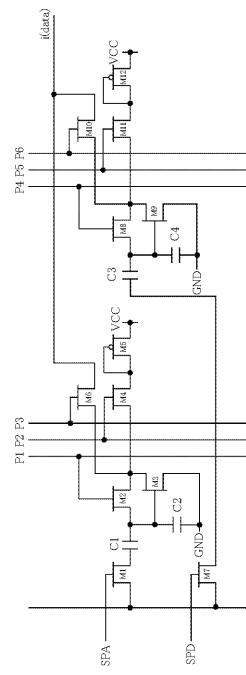

図2は、本発明に用いられる電気光学素子としてのE L素子を含む画素回路2の構成例を示す。図1に示された行選択線20の1本は実はそれぞれ2本の走査線からなる。本発明に用いられる電気光学素子としては、有機E L素子、無機E L素子、電子放出素子と蛍光体とを組み合わせた表示素子、発光ダイオードなどが挙げられる。

【0015】

図2において、P1及びP2が走査信号であり、データ信号として電流データI d a t aが入力される。E L素子の陽極(アノード)はT F T(M4)のドレイン端子に接続されており、陰極(カソード)は接地電位C G N Dに接続されている。M1、M2、M4がP型T F Tであり、M3がN型T F Tである。

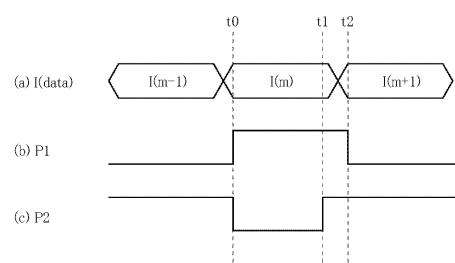

【0016】

図3は、画素回路2の駆動方法を説明するタイミングチャートである。図4において、I(m-1)、I(m)、I(m+1)は、m-1行(1行前)、m行(対象行)、m+1行(1行後)の対象列の画素回路2に入力される電流データI d a t aを示す。

10

20

30

40

50

## 【0017】

まず、時刻  $t_0$  前の時点では、対象行の画素回路 2 には、走査信号  $P_1$  には  $Low$  レベルの信号が、 $P_2$  には  $High$  レベルの信号が入力され、トランジスタ  $M_2$  が  $OFF$ 、 $M_3$  が  $OFF$ 、 $M_4$  が  $ON$  の状態である。この状態では、対象行である  $m$  行の画素回路 2 には、1 行前の電流データ  $I_{data}$  に対応する  $I(m-1)$  は入力されない。

## 【0018】

次いで、時刻  $t_0$  では、 $P_1$  には  $High$  レベルの信号が、 $P_2$  には  $Low$  レベルの信号が入力され、トランジスタ  $M_2$ 、 $M_3$  が  $ON$ 、 $M_4$  は  $OFF$  となる。この状態で、 $m$  行の画素回路 2 に該当行の電流データ  $I_{data}$  に対応する  $I(m)$  が入力される。このとき、 $M_4$  は導通状態でないため、 $EL$  素子には電流が流れない。入力された  $I_{data}$  により  $M_1$  の電流駆動能力に応じた電圧が、 $M_1$  のゲート端子と電源電位  $V_{CC}$  の間に配置された容量  $C_1$  に生じる。つまり、画素回路で一旦電流電圧変換を行う。

## 【0019】

以上の説明では、アクティブマトリクス表示装置を例に挙げて説明したが、本発明に用いられる表示部（マトリクス部）としては、電気光学素子を複数のデータ線と複数の行選択線との交点に配したパッシブマトリクスであってもよい。

## 【0020】

## (列駆動回路)

本発明に用いられる列駆動回路を図 4 に示す。

この回路は、特許文献 1 に記載されている列駆動回路と同じである。詳しい説明は上記特許文献 1 を参照されたい。

## 【0021】

この駆動回路は一対の電圧電流変換回路からなり、それらの主要な動作を説明する。スイッチングトランジスタ  $M_6$  がオフ、スイッチングトランジスタ  $M_{10}$  がオンされて、電圧電流変換トランジスタ  $M_9$  のドレイン電流が output 線  $i_{data}$  に出力される。この時、サンプリング信号  $S_{PA}$  により、スイッチングトランジスタ  $M_1$  がオンして、アナログ映像信号電圧  $V_{IDEO}$  はもう一つの電圧電流変換トランジスタ  $M_3$  のゲート電圧として蓄えられる。これにより、トランジスタ  $M_3$  は所定のドレイン電流を流せる状態となる。

## 【0022】

次に、トランジスタ  $M_6$  がオン、トランジスタ  $M_{10}$  がオフとなり、トランジスタ  $M_3$  のドレイン電流が output 線  $i_{data}$  に出力される。この時、再び、サンプリング信号  $S_{PB}$  によりスイッチングトランジスタ  $M_7$  がオンして、取り込まれたアナログ映像信号電圧  $V_{IDEO}$  はトランジスタ  $M_9$  のゲート電圧として蓄えられる。これによりトランジスタ  $M_9$  はドレイン電流を流せる状態となる。

## 【0023】

以上の 2 つの動作は行走査期間毎に繰り返され、output 線  $i_{data}$  には順次、アナログ信号電流が出力される。アナログ映像信号電圧  $V_{IDEO}$  の実効振幅によるトランジスタ  $M_3$  のゲート及びトランジスタ  $M_9$  のゲートの書き込み電圧  $V$  と、トランジスタ  $M_3$  及び  $M_9$  の駆動係数  $A$  及び  $B$  を各々  $A$  及び  $B$  とする。

## 【0024】

トランジスタ  $M_3$  のドレイン電流  $i(M_3)$  及びトランジスタ  $M_9$  のドレイン電流  $i(M_9)$  は、以下の関係を満たす。

$$i(M_3) = A \times V^2, \\ i(M_9) = B \times V^2.$$

## 【0025】

各電圧電流変換回路の駆動係数は、容量  $C_1$ （または  $C_3$ ）と  $C_2$ （または  $C_4$ ）の容量分割比により決定される。また同時に電圧電流変換トランジスタ  $M_3$ （または  $M_9$ ）のゲート長に対するゲート幅（ $W/L$ ）によっても決定される。

## 【0026】

各トランジスタに用いられる非単結晶半導体を活性層に用いた TFT は特性パラツキが

大きいが、図4の回路構成では各列のトランジスタM3及びトランジスタM6の閾値電圧Vthの変動に基本的に影響されない。各列のトランジスタM3及びM6の駆動係数の変動に対して影響は残るが、トランジスタM3及びM9のサイズを大きくすることで影響を低減できる。しかし、駆動係数の変動に対して残った影響は、各列のデータ信号電流のバラツキとなり、該データ信号の電流量で表示輝度が決まるEL素子では表示画像に「縦筋」のような表示不均一性が視認されてしまう。

## 【0027】

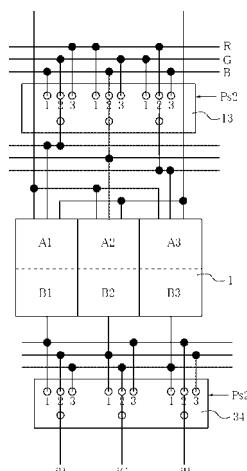

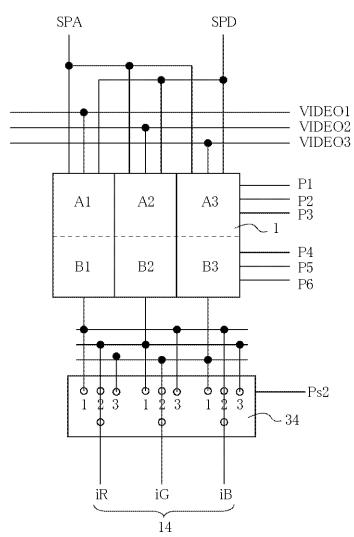

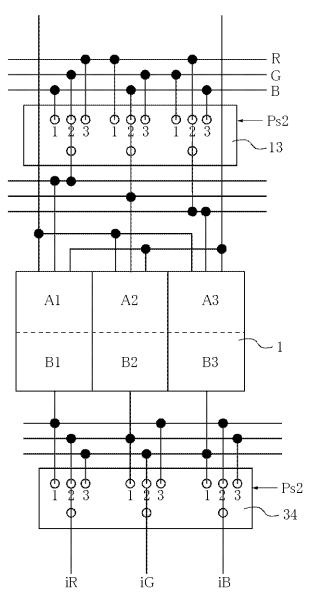

図5は表示画像に現れる「縦筋」を軽減する為の機能を含んだ列駆動回路3及び第2の選択回路の構成を示すものである。

## 【0028】

図5はカラー表示装置に対応しており、RGB3に対応した3列の構成を示している。サンプリング信号SPA及びSPBは列電流発生回路1に入力される。

## 【0029】

入力されるアナログ映像信号電圧VIDE01は駆動係数A1及びB1をもつ電圧電流変換回路（上記図4と同じ一対の電圧電流変換回路）に入力される。入力されるアナログ映像信号電圧VIDE02は駆動係数A2及びB2をもつ電圧電流変換回路（上記図4と同じ一対の電圧電流変換回路）に入力される。入力されるアナログ映像信号電圧VIDE03は駆動係数A3及びB3をもつ電圧電流変換回路（上記図4と同じ一対の電圧電流変換回路）に入力される。

## 【0030】

3つの列駆動回路1の3つ出力線は3つの3入力1出力スイッチを含む分散スイッチ部（第2の選択回路）34に入力され、各々対応するR列、G列、B列にデータ信号電流iR、iG、iBとして出力される。

## 【0031】

分散スイッチ部34は、列駆動回路からデータ信号の出力先となるデータ線14を変更可能に選択する。制御線Ps2に制御回路35から供給される制御信号により、分散スイッチ部34の接続状態を変更可能に決定することができる。

## 【0032】

そして、分散スイッチ部34の3つのスイッチは連動するように制御線Ps2に供給される制御信号により制御される。

## 【0033】

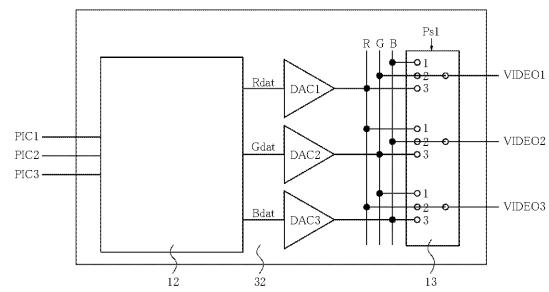

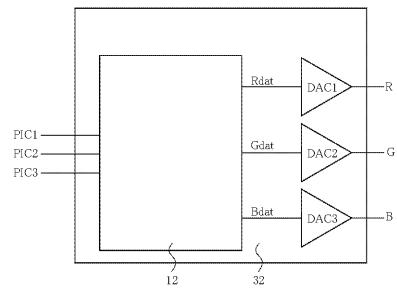

図6は本発明に用いられる信号処理回路32を示す。図6の12は、入力されるデジタル映像データPIC1、PIC2、PIC3を表示パネル100で表示を行うためのデジタル映像信号に変換するデジタル信号処理するDSPである。DSP12から出力された表示パネルの画素構成に対応するデジタル映像信号は、赤色のデジタル映像信号Rdat、緑色のデジタル映像信号Gdat、青色のデジタル映像信号Bdatからなる。

## 【0034】

これらの色毎のデジタル映像信号は夫々デジタル・アナログ変換器DAC1、DAC2、DAC3で色毎のアナログ映像信号に変換され、マトリクス配線部を介して第1の選択回路である分散スイッチ部13に入力される。

## 【0035】

分散スイッチ部13は、制御線Ps1に入力される制御信号により、各DACの出力先であるアナログ映像信号ラインVIDE01、VIDE02、VIDE03が適宜選択される。

## 【0036】

制御線Ps1に供給される制御信号は信号処理回路13内部に集積化されている不図示の制御回路で生成される。制御線Ps1の制御信号によって、分散スイッチ部13の接続状態、つまりDACの出力先をどのアナログ映像信号ラインVIDE01、VIDE02、VIDE03とするかを決定することができる。そして、この接続状態は変更可能である。

10

20

30

40

50

## 【0037】

そして、第1の選択回路34と第2の選択回路13とは、協働して後述する適切な接続状態を選択するように、信号処理回路32内の制御回路13や制御回路35により制御される。

## 【0038】

## (比較例)

ここで、本発明の実施形態による作用効果を容易に理解しやすくするために、比較例について先に説明する。

## 【0039】

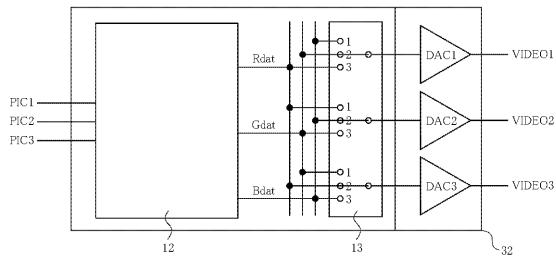

列駆動回路及び選択回路として図5に示した構成を採用し、信号処理回路として、図7に示した構成を採用した場合について説明する。図7は信号処理回路の一例を示す。この回路は単結晶シリコンを用いたトランジスタの集積回路からなるLSIで構成される。

## 【0040】

入力されたデジタル映像データP1C1、P1C2、P1C3はDSP12に入力される。デジタル映像データP1C1、P1C2、P1C3はRGBデータ又はYUVデータでありうる。映像信号処理を行うDSP12ではデジタル映像データP1C1、P1C2、P1C3から表示装置に対応した色毎のデジタル映像信号Rdat、Gdat、Bdatを出力する。

## 【0041】

そのために、DSP12では、必要に応じて色空間変換（入力されるデジタル映像信号がRGBデータのときは不要）を行う。他にもDSP12では、解像度変換、輪郭強調、ノイズリダクション、ガンマ補正、ホワイトバランス、黒設定、輝度設定等から選択される少なくとも1種の処理がデジタル信号処理で行なわれる。

## 【0042】

色毎のデジタル映像信号Rdat、Gdat、Bdatは、分散スイッチ部13を介して、それぞれゲインkのDAC1、DAC2、DAC3のいずれかに入力される。そして、DAC1、DAC2、DAC3からアナログ映像信号VIDEO1、VIDEO2、VIDEO3に変換されて出力される。

## 【0043】

図5の列駆動回路と図7の表示装置制御回路から行なわれるRGB各表示に対応するための信号電流の発生動作を説明する。

## 【0044】

図7の分散スイッチ部13によって各DACに入力される各色データを下表1に示す。状態（1）から（3）は分散スイッチ部13の3つの接続状態に対応している。

## 【0045】

## 【表1】

表1)

| 状態  | DAC1入力 | DAC2入力 | DAC3入力 |

|-----|--------|--------|--------|

| (1) | Bdat   | Rdat   | Gdat   |

| (2) | Gdat   | Bdat   | Rdat   |

| (3) | Rdat   | Gdat   | Bdat   |

## 【0046】

一方、図5の分散スイッチ部34によって選択された列駆動回路の駆動係数を示す。ここで、図4に示した列駆動回路では、先の水平走査期間でアナログ映像信号をサンプリングし、次の水平走査期間で先にサンプリングしたアナログ映像信号を電圧電流変換したデータ信号電流を供給する。よって、下表2に分散スイッチ部13の状態を対応させるとすると、上から（3）（1）（2）（3）（1）（2）の順になる。

## 【0047】

10

20

30

40

## 【表2】

表2)

| 状態  | R列電流 | G列電流 | B列電流 |

|-----|------|------|------|

| (1) | A1   | A2   | A3   |

| (2) | B2   | B3   | B1   |

| (3) | A3   | A1   | A2   |

| (1) | B1   | B2   | B3   |

| (2) | A2   | A3   | A1   |

| (3) | B3   | B1   | B2   |

## 【0048】

上述したとおり、図4の列駆動回路回路から出力される電流は1水平走査期間前に入力されたアナログ映像信号で決定されるので、表1及び表2からわかるように分散スイッチ部34、13の全ての選択状態においてRGB列のデータ線に所望色の信号電流が供給される。

## 【0049】

図8は列駆動回路の1式及び2式で示す電圧電流変換特性に従った各画素に対応する電圧電流変換係数を示した表である。

## 【0050】

図8の左端にある数字は分散スイッチ部34、13の接続状態であり、各行で「(1) (2) (3)」を繰り返す。各列のデータ信号電流とも列駆動回路1内の駆動係数A1、B2、A3、B1、A2、B3の電圧電流変換回路を順次切り換えて出力している。よって、図8に示すように、駆動係数A1、B2、A3、B1、A2、B3間にバラツキが存在しても6行周期で分散されるので、表示画像の「縦筋」が視覚上低減される。

## 【0051】

しかしながら、図7のデジタル・アナログ変換器DAC1、DAC2、DAC3の各ゲインにはバラツキがある。これはLSI製造時に生じるトランジスタや内蔵抵抗器の特性ばらつきに因るものである。デジタル・アナログ変換器DAC1、DAC2、DAC3の各ゲインは、全て同一でなく、各々ゲインk1、k2、k3という互いに相違する値を持っている。

## 【0052】

図9はこの場合の列駆動回路の1式及び2式で示す電圧電流変換特性に従った各画素に対応する電圧電流変換係数を示した表である。

## 【0053】

図9から理解できる様に、DAC1、DAC2、DAC3のゲインバラツキによって、各画素の電流が3行周期で変動してしまう。しかも、ゲインバラツキは2乗特性で強調されてしまう。このため表示画像全域に渡って、3行毎の繰り返し固定パターンの表示不均一性が発生してしまう。このゲインばらつきの2乗効果が、本発明者が見出した表示不均一性の一つの原因である。

## 【0054】

(実施形態1)

そこで、本発明は図1乃至6に示した構成のカラー表示装置により上記技術課題を解決する。図1の構成が、図7に示した構成と基本的に異なる点は、第1の選択回路である分散スイッチ部13とDACの位置が映像信号の流れに対して逆になっている点である。

## 【0055】

図1の分散スイッチ部13によって映像信号出力VIDEO1、VIDEO2、VIDEO3に出力される色信号を分散スイッチ部13の各接続状態で示す。

## 【0056】

10

20

30

40

## 【表3】

表3)

| 状態  | VIDEO01 | VIDEO02 | VIDEO03 |

|-----|---------|---------|---------|

| (1) | B信号     | R信号     | G信号     |

| (2) | G信号     | B信号     | R信号     |

| (3) | R信号     | G信号     | B信号     |

## 【0057】

図7の構成を採用した場合と同様に表3及び表2からわかるように分散スイッチ部34、13の全ての選択状態においてRGB列のデータ線に所望色のデータ信号電流が供給される。図10は列電流発生回路の1式及び2式で示す電圧電流変換特性に従った各画素に對応する電圧電流変換係数を示した表である。

10

## 【0058】

図10の左端にある数字は分散スイッチ部34、13の接続状態であり、各行で「(1)(2)(3)」を繰り返す。各列の電流とも列駆動回路の駆動係数A1、B2、A3、B1、A2、B3の電圧電流変換回路を順次変更しながら発生させる。よって、図10からわかるよう駆動係数A1、B2、A3、B1、A2、B3間にバラツキが存在しても6行周期で分散される。しかも、各色列に供給されるデータ信号電流は同一のデジタル・アナログ変換器DACから来たアナログ映像信号に基づくものである。

20

## 【0059】

ゆえに、DAC1、DAC2、DAC3のゲインバラツキによる、3行毎の固定パターンの表示不均一性は発生しない。

## 【0060】

確かに、DAC1、DAC2、DAC3のゲインバラツキによって、ホワイトバランスはズレるが、ホワイトバランスはDSP12において周知の方法によりデジタル処理で容易に調整可能である。

30

## 【0061】

したがって、図6の信号処理回路を使用すると図4に示した電圧電流変換回路の駆動係数A1、B2、A3、B1、A2、B3バラツキを表示画質に極力現れないように有効に分散できる。

30

## 【0062】

## (実施形態2)

図11と図12は本実施の形態に用いられる第1及び第2の選択回路、列駆動回路、及び信号処理回路を示している。

## 【0063】

図12の信号処理回路には、第1の選択回路を設けずに、表示部と同じ絶縁性表面を有する基板上に、列駆動回路、第2の選択回路とともに第1の選択回路13が集積化されて設けられている。これらの回路のトランジスタは何れも多結晶シリコンなどの非単結晶半導体を活性層に用いたTFTで構成される。

40

## 【0064】

図12に示すように、DSP12からDAC1、DAC2、DAC3を介して各々R信号、G信号、B信号が並列に出力される。分散スイッチ部13は図11で示すように、列駆動回路や第2の選択回路34とともに集積化されている。図12ではDSP12とデジタル・アナログ変換器のみが、単結晶半導体基板に集積化され、1チップLSIとなっている。

## 【0065】

図11に示すように、第1の選択回路である分散スイッチ部13によって色毎のアナログ映像信号RGBは水平走査毎に接続状態が変更され、出力先の列駆動回路が変更される。しかしながら、第2の選択スイッチ34により、列駆動回路からのデータ信号電流の出力先が変更されるため、色毎のデータ信号電流は、対応する色のデータ線(iR, iG,

50

i B ) に供給される。

これら第 1 及び第 2 の選択回路は制御線 P s 1 及び P s 2 により制御される。

【 0 0 6 6 】

実施形態 1 と同様に表 3 及び表 2 からわかるように分散スイッチ部 3 4 、 1 3 の全ての選択状態において R G B 列のデータ線に所望色のデータ信号電流が供給される。

【 0 0 6 7 】

図 1 0 に示すように各画素に対する電圧電流変換係数の分散状態は同じである。分散スイッチ部 1 3 は表示パネル上に表示画面の横サイズ全幅に亘って配置できるので分散スイッチ部 1 3 内の各スイッチの導通抵抗バラツキは極力抑えることができる。そして、各列駆動回路におけるサンプリング時定数に影響されるサンプリング動作のバランスがとれる。

10

【 0 0 6 8 】

また、図 1 1 ではデータ線一列に対して 1 つの分散用のスイッチを設けているが、複数のデータ線群に対して一つのスイッチを設けることも好ましい。このように、第 1 の選択回路のスイッチの数を列の数より少ない数にすることにより、 R G B の各アナログ映像信号線マトリクス配線部の寄生容量を低減できる。また、選択回路 1 3 と列駆動回路 1 との間のマトリクス配線部における寄生容量も低減できる。更には、スイッチ部 1 3 自体のゲートの配線交差によって発生する寄生容量増加を抑えることもできる。こうして、サンプリング時定数が抑えられ、サンプリング動作のバランスが良くなる。

【 0 0 6 9 】

また、実施形態 1 と同様に電圧電流変換回路の駆動係数 A 1 、 B 2 、 A 3 、 B 1 、 A 2 、 B 3 のバラツキが表示画質に極力現れないようにすることもできることは云うまでも無い。

20

【 図面の簡単な説明 】

【 0 0 7 0 】

【 図 1 】 本発明の一実施形態に係る表示装置の構成を示すブロック図である。

【 図 2 】 本発明に用いられる画素回路の回路図である。

【 図 3 】 図 2 に示す画素回路の動作を説明するためのタイミングチャートである。

【 図 4 】 本発明に用いられる列駆動回路の回路図である。

【 図 5 】 本発明の第 1 の実施形態による列駆動回路と第 2 の選択回路を含む周辺回路を説明するための模式図である。

30

【 図 6 】 本発明に第 1 の実施形態による第 1 の選択回路を含む信号処理回路を説明するためのブロック図である。

【 図 7 】 比較例による第 1 の選択回路を含む信号処理回路を説明するためのブロック図である。

【 図 8 】 各画素における電圧電流変換係数を説明するための模式図である。

【 図 9 】 比較例による各画素における電圧電流変換係数を説明するための模式図である。

【 図 1 0 】 本発明の実施の形態による各画素における電圧電流変換係数を説明するための模式図である。

【 図 1 1 】 本発明の第 2 の実施形態による列駆動回路と第 1 及び第 2 の選択回路を含む周辺回路を説明するための模式図である。

40

【 図 1 2 】 信号処理回路を説明するための模式図である。

【 符号の説明 】

【 0 0 7 1 】

1 列駆動回路

2 画素回路 ( 色画素 )

9 カラー表示部 ( マトリクス部 )

1 3 第 1 の選択回路

1 4 データ線

3 2 信号処理回路

50

### 3.4 第2の選択回路

### 3.5 制御回路

## P s 1、P s 2 制御線

【 図 1 】

【 図 2 】

|            |            |            |

|------------|------------|------------|

| 1 列駆動回路    | 5 行シフトレジスタ | 32 信号処理回路  |

| 2 画素回路     | 9 カラー表示部   | 34 第2の選択回路 |

| 3 列シフトレジスタ | 13 第1の選択回路 | 35 制御回路    |

| 4 ゲート回路    |            |            |

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

|     | R列              | G列              | B列              |

|-----|-----------------|-----------------|-----------------|

| (1) | $A1 \times k^2$ | $A2 \times k^2$ | $A3 \times k^2$ |

| (2) | $B2 \times k^2$ | $B3 \times k^2$ | $B1 \times k^2$ |

| (3) | $A3 \times k^2$ | $A1 \times k^2$ | $A2 \times k^2$ |

| (1) | $B1 \times k^2$ | $B2 \times k^2$ | $B3 \times k^2$ |

| (2) | $A2 \times k^2$ | $A3 \times k^2$ | $A1 \times k^2$ |

| (3) | $B3 \times k^2$ | $B1 \times k^2$ | $B2 \times k^2$ |

【図9】

|     | R列               | G列               | B列               |

|-----|------------------|------------------|------------------|

| (1) | $A1 \times k1^2$ | $A2 \times k2^2$ | $A3 \times k3^2$ |

| (2) | $B2 \times k2^2$ | $B3 \times k3^2$ | $B1 \times k1^2$ |

| (3) | $A3 \times k3^2$ | $A1 \times k1^2$ | $A2 \times k2^2$ |

| (1) | $B1 \times k1^2$ | $B2 \times k2^2$ | $B3 \times k3^2$ |

| (2) | $A2 \times k2^2$ | $A3 \times k3^2$ | $A1 \times k1^2$ |

| (3) | $B3 \times k3^2$ | $B1 \times k1^2$ | $B2 \times k2^2$ |

【図10】

|     | R列               | G列               | B列               |

|-----|------------------|------------------|------------------|

| (1) | $A1 \times k1^2$ | $A2 \times k2^2$ | $A3 \times k3^2$ |

| (2) | $B2 \times k1^2$ | $B3 \times k2^2$ | $B1 \times k3^2$ |

| (3) | $A3 \times k1^2$ | $A1 \times k2^2$ | $A2 \times k3^2$ |

| (1) | $B1 \times k1^2$ | $B2 \times k2^2$ | $B3 \times k3^2$ |

| (2) | $A2 \times k1^2$ | $A3 \times k2^2$ | $A1 \times k3^2$ |

| (3) | $B3 \times k1^2$ | $B1 \times k2^2$ | $B2 \times k3^2$ |

【図11】

【図12】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 1 M |

| G 0 9 G | 3/20  | 6 4 2 J |

| G 0 9 G | 3/20  | 6 4 2 L |

| G 0 9 G | 3/20  | 6 1 1 H |

| H 0 5 B | 33/14 | A       |

(72)発明者 川野 藤雄

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 HH04 HH05

5C080 AA06 BB05 CC03 DD05 EE29 EE30 FF10 JJ02 JJ03 JJ04