(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6450169号

(P6450169)

(45) 発行日 平成31年1月9日(2019.1.9)

(24) 登録日 平成30年12月14日(2018.12.14)

|                        |                    |

|------------------------|--------------------|

| (51) Int.Cl.           | F 1                |

| B 41 J 2/14 (2006.01)  | B 41 J 2/14 6 1 1  |

| B 41 J 2/05 (2006.01)  | B 41 J 2/05        |

| B 41 J 2/175 (2006.01) | B 41 J 2/175 1 1 9 |

請求項の数 17 (全 14 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2014-245172 (P2014-245172)  |

| (22) 出願日     | 平成26年12月3日(2014.12.3)         |

| (65) 公開番号    | 特開2015-199332 (P2015-199332A) |

| (43) 公開日     | 平成27年11月12日(2015.11.12)       |

| 審査請求日        | 平成29年11月8日(2017.11.8)         |

| (31) 優先権主張番号 | 特願2014-76461 (P2014-76461)    |

| (32) 優先日     | 平成26年4月2日(2014.4.2)           |

| (33) 優先権主張国  | 日本国(JP)                       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】半導体装置、液体吐出ヘッド、液体吐出カードリッジ及び液体吐出装置

## (57) 【特許請求の範囲】

## 【請求項 1】

液体吐出ヘッド用の半導体装置であって、

第1電圧を供給するための第1電極と、

前記第1電圧とは異なる第2電圧を供給するための第2電極と、

液体にエネルギーを付与するための複数の吐出素子であって、各吐出素子は第1端子及び第2端子を有する、複数の吐出素子と、

前記複数の吐出素子の第1端子と前記第1電極とを電気的に接続するための複数の第1スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第1スイッチ素子を含む、複数の第1スイッチ素子と、

前記複数の吐出素子の第2端子と前記第2電極とを電気的に接続するための複数の第2スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第2スイッチ素子を含む、複数の第2スイッチ素子と、

前記複数の第1スイッチ素子及び前記複数の第2スイッチ素子を制御する制御部を備え、

前記複数の吐出素子のうちの同一の第2スイッチ素子に接続された2つ以上の吐出素子は、前記複数の第1スイッチ素子のうちの互いに異なる第1スイッチ素子に接続されており、

前記複数の第1スイッチ素子の個数は、前記複数の第2スイッチ素子の個数よりも少なく、

10

20

前記複数の吐出素子は、ある方向に並んで配置されており、

前記複数の第1スイッチ素子は、前記方向に並んで配置されており、

前記複数の第2スイッチ素子は、前記方向に並んで配置されており、

前記制御部は、前記複数の第1スイッチ素子を制御する第1制御部と、前記複数の第2スイッチ素子を制御する第2制御部とを含み、

前記第2制御部は、前記複数の第2スイッチ素子に沿って配置されていることを特徴とする半導体装置。

**【請求項2】**

同一の第2スイッチ素子に接続された2つ以上の吐出素子は、隣接して配置されることを特徴とする請求項1に記載の半導体装置。 10

**【請求項3】**

液体吐出ヘッド用の半導体装置であって、

第1電圧を供給するための第1電極と、

前記第1電圧とは異なる第2電圧を供給するための第2電極と、

液体にエネルギーを付与するための複数の吐出素子であって、各吐出素子は第1端子及び第2端子を有する、複数の吐出素子と、

前記複数の吐出素子の第1端子と前記第1電極とを電気的に接続するための複数の第1スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第1スイッチ素子を含む、複数の第1スイッチ素子と、

前記複数の吐出素子の第2端子と前記第2電極とを電気的に接続するための複数の第2スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第2スイッチ素子を含む、複数の第2スイッチ素子と、

前記複数の第1スイッチ素子及び前記複数の第2スイッチ素子を制御する制御部を備え

、

前記複数の吐出素子のうちの同一の第2スイッチ素子に接続された2つ以上の吐出素子は、前記複数の第1スイッチ素子のうちの互いに異なる第1スイッチ素子に接続されており、

前記複数の第1スイッチ素子の個数は、前記複数の第2スイッチ素子の個数よりも少なく、

前記同一の第2スイッチ素子に接続された2つ以上の吐出素子は、隣接して配置され、

前記複数の吐出素子は、ある方向に並んで配置されており、

前記複数の第2スイッチ素子は、前記方向に並んで配置されており、

前記制御部は、前記複数の第1スイッチ素子を制御する第1制御部と、前記複数の第2スイッチ素子を制御する第2制御部とを含み、

前記第2制御部は、前記複数の第2スイッチ素子に沿って配置されていることを特徴とする半導体装置。

**【請求項4】**

前記制御部は、前記複数の吐出素子のうちの1つの吐出素子に接続された第1スイッチ素子及び第2スイッチ素子をオンにすることによって、当該1つの吐出素子を駆動することを特徴とする請求項1乃至3の何れか1項に記載の半導体装置。 40

**【請求項5】**

前記制御部は、前記複数の吐出素子のうちの1つの吐出素子に接続された第1スイッチ素子がオンである状態で、当該1つの吐出素子に接続された第2スイッチ素子のオン・オフを切り替えることを特徴とする請求項4に記載の半導体装置。

**【請求項6】**

前記制御部は、互いに異なる第2スイッチ素子に接続された2つ以上の吐出素子に接続された2つ以上の第1スイッチ素子を同期して制御することを特徴とする請求項4又は5に記載の半導体装置。

**【請求項7】**

前記半導体装置は長方形形状を有し、 50

前記複数の第1スイッチ素子が配置されている方向は前記半導体装置の長手方向であり、

前記第1制御部は、前記複数の第1スイッチ素子と前記半導体装置の短辺との間に配置されていることを特徴とする請求項1乃至6の何れか1項に記載の半導体装置。

**【請求項8】**

液体吐出ヘッド用の半導体装置であって、

第1電圧を供給するための第1電極と、

前記第1電圧とは異なる第2電圧を供給するための第2電極と、

液体にエネルギーを付与するための複数の吐出素子であって、各吐出素子は第1端子及び第2端子を有する、複数の吐出素子と、

10

前記複数の吐出素子の第1端子と前記第1電極とを電気的に接続するための複数の第1スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第1スイッチ素子を含む、複数の第1スイッチ素子と、

前記複数の吐出素子の第2端子と前記第2電極とを電気的に接続するための複数の第2スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第2スイッチ素子を含む、複数の第2スイッチ素子と、

前記複数の第1スイッチ素子及び前記複数の第2スイッチ素子を制御する制御部と、を備え、

前記複数の吐出素子のうちの同一の第2スイッチ素子に接続された2つ以上の吐出素子は、前記複数の第1スイッチ素子のうちの互いに異なる第1スイッチ素子に接続されており、

20

前記複数の第1スイッチ素子の個数は、前記複数の第2スイッチ素子の個数よりも少なく、

前記制御部は、前記複数の吐出素子のうちの1つの吐出素子に接続された第1スイッチ素子がオンである状態で、当該1つの吐出素子に接続された第2スイッチ素子のオン・オフを切り替え、

前記複数の吐出素子は、ある方向に並んで配置されており、

前記複数の第2スイッチ素子は、前記方向に並んで配置されている

前記制御部は、前記複数の第1スイッチ素子を制御する第1制御部と、前記複数の第2スイッチ素子を制御する第2制御部とを含み、

30

前記第2制御部は、前記複数の第2スイッチ素子に沿って配置されていることを特徴とする半導体装置。

**【請求項9】**

前記複数の第1スイッチ素子の個数と前記複数の第2スイッチ素子の個数との和は、前記複数の吐出素子の個数以下であることを特徴とする請求項1乃至8の何れか1項に記載の半導体装置。

**【請求項10】**

前記複数の第1スイッチ素子の個数と前記複数の第2スイッチ素子の個数との積は、前記複数の吐出素子の個数に等しいことを特徴とする請求項1乃至9の何れか1項に記載の半導体装置。

40

**【請求項11】**

前記第2電圧は前記第1電圧よりも低いことを特徴とする請求項1乃至10の何れか1項に記載の半導体装置。

**【請求項12】**

前記第1電圧は電源電圧であり、前記第2電圧は接地電圧であることを特徴とする請求項1乃至11の何れか1項に記載の半導体装置。

**【請求項13】**

前記複数の吐出素子及び前記複数の第2スイッチ素子はブロック内にあり、

前記半導体装置は前記ブロックを複数備えることを特徴とする請求項1乃至12の何れか1項に記載の半導体装置。

50

**【請求項 1 4】**

前記ブロックは前記複数の第1スイッチ素子を含むことを特徴とする請求項1\_3に記載の半導体装置。

**【請求項 1 5】**

請求項1乃至1\_4のいずれか1項に記載の半導体装置と、前記半導体装置によって液体の吐出が制御される吐出口とを備えることを特徴とする液体吐出ヘッド。

**【請求項 1 6】**

請求項1\_5に記載の液体吐出ヘッドとインクを収容する液体容器とを備えることを特徴とする液体吐出カートリッジ。

**【請求項 1 7】**

請求項1\_5に記載の液体吐出ヘッドと、前記液体吐出ヘッドに液体を吐出させるための駆動信号を供給する供給手段とを有することを特徴とする液体吐出装置。 10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、半導体装置、液体吐出ヘッド、液体吐出カートリッジ及び液体吐出装置に関する。

**【背景技術】****【0 0 0 2】**

熱エネルギーを利用する液体吐出ヘッドは、発熱素子によって発生した熱エネルギーを液体に付与することにより、液体中で選択的に発泡現象を生じさせ、その発泡のエネルギーにより吐出口からインクを吐出する。特許文献1に記載された液体吐出ヘッド用の半導体装置では、発熱素子の両端にそれぞれスイッチ素子を接続し、これらの2つのスイッチ素子をオンにすることによって発熱素子に電流を流す。発熱素子に電流を流す必要がない場合に、発熱素子の両端に接続されたスイッチ素子を両方ともオフにすることによって、発熱素子に不要な電圧が印加されることを抑制する。 20

**【先行技術文献】****【特許文献】****【0 0 0 3】**

【特許文献1】米国特許出願公開第2011/0175959号明細書

30

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 4】**

特許文献1の半導体装置では、電源電圧側において複数の発熱素子で1つのスイッチ素子が共有され、接地側において発熱素子のそれぞれに別個にスイッチ素子が接続されている。そのため、この半導体装置で用いられるスイッチ素子の個数は、発熱素子の個数よりも多くなる。スイッチ素子の個数が多くなると、それに伴い、半導体装置のチップ面積も大きくなる。この課題は、発熱素子だけでなく圧電素子などの他の吐出素子を有する半導体装置一般に当てはまる。そこで、本発明は、吐出素子の両側にスイッチ素子が配置された半導体装置を小型化するために有利な技術を提供することを1つの目的とする。 40

**【課題を解決するための手段】****【0 0 0 5】**

上記課題に鑑みて、本発明の一部の実施形態により、液体吐出ヘッド用の半導体装置であって、第1電圧を供給するための第1電極と、前記第1電圧とは異なる第2電圧を供給するための第2電極と、液体にエネルギーを付与するための複数の吐出素子であって、各吐出素子は第1端子及び第2端子を有する、複数の吐出素子と、前記複数の吐出素子の第1端子と前記第1電極とを電気的に接続するための複数の第1スイッチ素子であって、前記複数の吐出素子のうちの2つ以上の吐出素子に接続されている第1スイッチ素子を含む、複数の第1スイッチ素子と、前記複数の吐出素子の第2端子と前記第2電極とを電気的に接続するための複数の第2スイッチ素子であって、前記複数の吐出素子のうちの2つ以 50

上の吐出素子に接続されている第2スイッチ素子を含む、複数の第2スイッチ素子と、前記複数の第1スイッチ素子及び前記複数の第2スイッチ素子を制御する制御部を備え、前記複数の吐出素子のうちの同一の第2スイッチ素子に接続された2つ以上の吐出素子は、前記複数の第1スイッチ素子のうちの互いに異なる第1スイッチ素子に接続されており、前記複数の第1スイッチ素子の個数は、前記複数の第2スイッチ素子の個数よりも少なく、前記複数の吐出素子は、ある方向に並んで配置されており、前記複数の第1スイッチ素子は、前記方向に並んで配置されており、前記複数の第2スイッチ素子は、前記方向に並んで配置されており、前記制御部は、前記複数の第1スイッチ素子を制御する第1制御部と、前記複数の第2スイッチ素子を制御する第2制御部とを含み、前記第2制御部は、前記複数の第2スイッチ素子に沿って配置されていることを特徴とする半導体装置が提供される。

10

## 【発明の効果】

## 【0006】

上記手段により、吐出素子の両側にスイッチ素子が配置された半導体装置を小型化するために有利な技術が提供される。

## 【図面の簡単な説明】

## 【0007】

【図1】一部の実施形態の半導体装置の等価回路図。

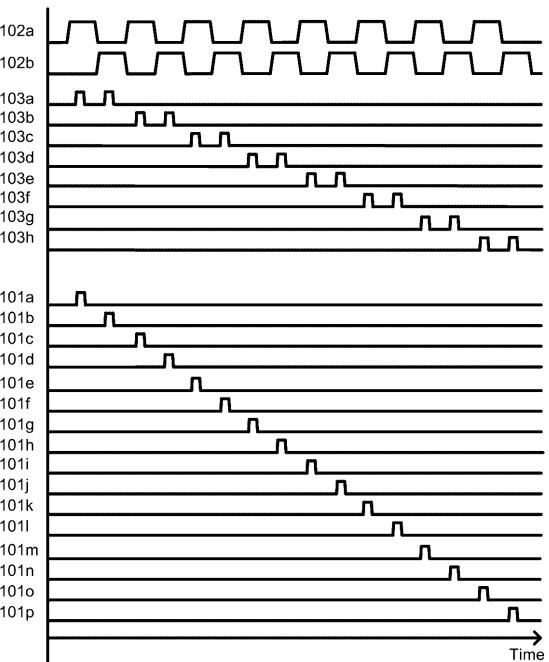

【図2】図1の半導体装置の動作を説明するタイミング図。

20

【図3】一部の実施形態の半導体装置の等価回路図。

【図4】図3の半導体装置の動作を説明するタイミング図。

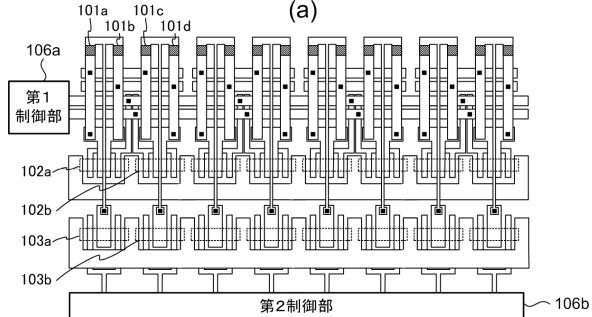

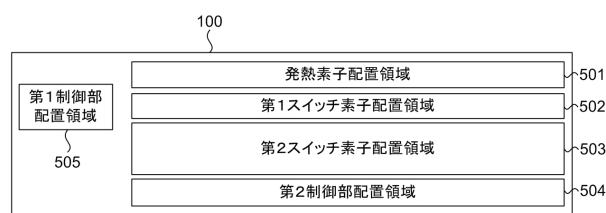

【図5】一部の実施形態の半導体装置の構成要素の配置図。

【図6】他の実施形態を説明する図。

## 【発明を実施するための形態】

## 【0008】

添付の図面を参照しつつ本発明の実施形態について以下に説明する。様々な実施形態を通じて同様の要素には同一の参照符号を付し、重複する説明を省略する。また、各実施形態は適宜変更、組み合わせが可能である。本発明の一部の実施形態は、例えばインクなどの液体を吐出する液体吐出ヘッド用の半導体装置に関する。

30

## 【0009】

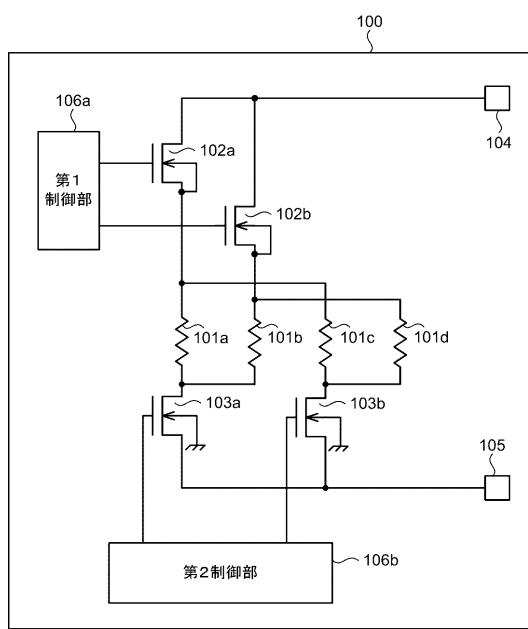

図1の等価回路図を参照して、一部の実施形態に係る半導体装置100の構成例について説明する。半導体装置100は、複数の発熱素子101a～101d、複数の第1スイッチ素子102a～102b、複数の第2スイッチ素子103a～103b、電源電極104、接地電極105、第1制御部106及び第2制御部107を備える。これらの構成要素は例えば半導体基板に形成される。以下の説明において、複数の発熱素子101a～101dを発熱素子101と総称する。発熱素子101についての説明は、複数の発熱素子101a～101dの何れについても当てはまる。同様に、複数の第1スイッチ素子102a～102bを第1スイッチ素子102と総称し、複数の第2スイッチ素子103a～103bを第2スイッチ素子103と総称する。

40

## 【0010】

発熱素子101(ヒータ)は、発熱素子101を流れる電流に応じて発熱し、この熱エネルギーが液体に付与されて吐出口から液体が吐出される。発熱素子101は例えば発熱抵抗体で形成される。発熱素子101に代えて、駆動された場合に液体にエネルギーを付与することが可能な他の吐出素子が用いられてもよい。他の吐出素子の一例として圧電素子がある。以下の説明において、発熱素子101の一方の端(図1の上端)を第1端子と呼び、他方の端(図1の下端)を第2端子と呼ぶ。第1端子と第2端子との間を電流が流れることによって、発熱素子101が発熱する。

## 【0011】

発熱素子101の第1端子は第1スイッチ素子102によって電源電極104に電気的に接続される。具体的に、第1スイッチ素子102がオンの場合に発熱素子101の第1

50

端子と電源電極 104 とが電気的に接続され、第 1 スイッチ素子 102 がオフの場合に発熱素子 101 の第 1 端子と電源電極 104 とが開放される。電源電極 104 には半導体装置 100 の外部から電源電圧が供給される。

#### 【0012】

第 1 スイッチ素子 102 は、例えば NMOS ドラッグで形成される。この場合に、第 1 スイッチ素子 102 である NMOS ドラッグのソースは発熱素子 101 の第 1 端子に接続され、ドレインは電源電極 104 に接続され、バックゲートはソースに接続される。NMOS ドラッグのゲート（制御端子）には第 1 制御部 106a から制御信号が供給される。第 1 スイッチ素子 102 は、NMOS ドラッグの代わりに、PMOS ドラッグや、スイッチ素子として機能する他の回路素子で形成されてもよい。

10

#### 【0013】

発熱素子 101 の第 2 端子は第 2 スイッチ素子 103 によって接地電極 105 に電気的に接続される。具体的に、第 2 スイッチ素子 103 がオンの場合に発熱素子 101 の第 2 端子と接地電極 105 とが電気的に接続され、第 2 スイッチ素子 103 がオフの場合に発熱素子 101 の第 2 端子と接地電極 105 とが開放される。接地電極 105 には半導体装置 100 の外部から接地電圧が供給される。

#### 【0014】

第 2 スイッチ素子 103 は、例えば NMOS ドラッグで形成される。この場合に、第 2 スイッチ素子 103 である NMOS ドラッグのソースは接地電極 105 に接続され、ドレインは発熱素子 101 の第 2 端子に接続され、バックゲートは接地される。NMOS ドラッグのゲート（制御端子）には第 2 制御部 106b から制御信号が供給される。第 2 スイッチ素子 103 は、NMOS ドラッグの代わりに、PMOS ドラッグや、スイッチ素子として機能する他の回路素子で形成されてもよい。

20

#### 【0015】

電源電極 104 に供給される電源電圧が例えば 30V である場合に、第 1 スイッチ素子 102 をオンにするためにゲートに供給する電圧は例えば 28V となり、第 2 スイッチ素子 103 をオンにするためにゲートに供給する電圧は例えば 5V となる。第 1 制御部 106a は高電圧の制御信号を供給する必要があるので、第 1 制御部 106a は、第 1 スイッチ素子 102a、102b のそれぞれに供給する制御信号を生成するための論理回路と、この論理回路の出力信号を高電圧に変換するレベル変換回路とを含む。一方、第 2 制御部 106b はロジック電源レベルの制御信号を供給すればよいので、第 2 制御部 106b は第 2 スイッチ素子 103a、103b のそれぞれに供給する制御信号を生成するための論理回路を含み、レベル変換回路を含まなくてもよい。

30

#### 【0016】

ここで、発熱素子 101、第 1 スイッチ素子 102 及び第 2 スイッチ素子 103 の接続構成について詳細に説明する。発熱素子 101a は、第 1 スイッチ素子 102a と第 2 スイッチ素子 103a とに接続される。発熱素子 101b は、第 1 スイッチ素子 102b と第 2 スイッチ素子 103a とに接続される。発熱素子 101c は、第 1 スイッチ素子 102a と第 2 スイッチ素子 103b とに接続される。発熱素子 101d は、第 1 スイッチ素子 102b と第 2 スイッチ素子 103b とに接続される。このように、同一の第 2 スイッチ素子 103 に接続された複数の発熱素子 101 は、互いに異なる第 1 スイッチ素子 102 に接続されている。半導体装置 100 はこのような接続構成を有するので、第 1 スイッチ素子 102 と第 2 スイッチ素子 103 との組を選択してオンにすることによって、1 つの発熱素子 101 のみに電流を流し、他の発熱素子 101 に電流を流さないことができる。例えば、第 1 スイッチ素子 102a 及び第 2 スイッチ素子 103a をオンにし、他のスイッチ素子をオフにした場合に、発熱素子 101a にのみ電流が流れ、他の発熱素子には電流が流れない。

40

#### 【0017】

また、第 1 スイッチ素子 102a は、2 つの発熱素子 101a、101c に接続される。第 1 スイッチ素子 102b は、2 つの発熱素子 101b、101d に接続される。第 2

50

スイッチ素子 103a は、2つの発熱素子 101a、101b に接続される。第2スイッチ素子 103b は、2つの発熱素子 101c、101d に接続される。このように、各第1スイッチ素子 102 は2つの発熱素子 101 に接続され、各第2スイッチ素子 103 は2つの発熱素子 101 に接続される。電源電極 104 側において複数の発熱素子 101 で1つの第1スイッチ素子 102 を共有し、接地電極 105 側において複数の発熱素子 101 で1つの第2スイッチ素子 103 を共有することによって、半導体装置 100 に含まれるスイッチ素子の個数を低減できる。半導体装置 100 に含まれるスイッチ素子の個数（第1スイッチ素子 102 の個数と第2スイッチ素子 103 の個数の和）は4個であり、これは発熱素子 101 の個数に等しい。このようにスイッチ素子の個数を低減できるので、半導体装置 100 を小型化できる。

10

#### 【0018】

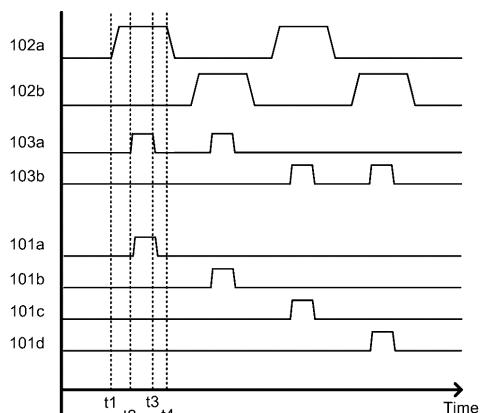

続いて、図2のタイミング図を参照して、半導体装置 100 の動作例、特に制御部 106 の動作例について説明する。この半導体装置 100 の動作例において、電源電極 104 に電源電圧が供給され、接地電極 105 に接地電圧が供給されているとする。図2の横軸は時刻を表す。図2の縦軸は、第1スイッチ素子 102a、102b 及び第2スイッチ素子 103a、103b について、各スイッチ素子のゲートに供給される制御信号の電圧値を表し、発熱素子 101a～101d について、各発熱素子を流れる電流値を表す。半導体装置 100 は、発熱素子 101a～101d に順番に電流を流す。制御部 106 は、半導体装置 100 の外部からの信号に基づいて、図2に示す制御信号を生成してもよい。

#### 【0019】

時刻 t1において、第1制御部 106a は、第1スイッチ素子 102a に供給する制御信号をローレベルからハイレベルに切り替える。これにより、第1スイッチ素子 102a がオンになる。第1スイッチ素子 102a がオンである間に、時刻 t2において、第2制御部 106b は、第2スイッチ素子 103a に供給する制御信号をローレベルからハイレベルに切り替える。これにより、第2スイッチ素子 103a がオンになり、発熱素子 101a に電流が流れる。第1スイッチ素子 102a がオンである間に、時刻 t3において、第2制御部 106b は、第2スイッチ素子 103a に供給する制御信号をハイレベルからローレベルに切り替える。これにより、第2スイッチ素子 103a がオフになり、発熱素子 101a に電流が流れなくなる。時刻 t4において、第1制御部 106a は、第1スイッチ素子 102a に供給する制御信号をハイレベルからローレベルに切り替える。これにより、第1スイッチ素子 102a がオフになる。第1スイッチ素子 102 のオン幅（オンである期間）は例えば数μ秒であり、第2スイッチ素子 103 のオン幅は例えば数十～数百n秒である。

20

#### 【0020】

その後、図2に示すように、制御部 106 は、第1スイッチ素子 102 及び第2スイッチ素子 103 のオン・オフを適宜切り替えることによって、発熱素子 101b～101d に順に電流を流す。

30

#### 【0021】

第1スイッチ素子 102 に供給される制御信号のハイレベルの電圧値（例えば、28V）は、第2スイッチ素子 103 に供給される制御信号のハイレベルの電圧値（例えば、5V）よりも高い。そのため、第1スイッチ素子 102 に供給される制御信号がローレベルからハイレベルに切り替わるまでの時間は、第2スイッチ素子 103 に供給される制御信号がローレベルからハイレベルに切り替わるまでの時間よりも長くなる。そこで、上述のように、制御部 106 は第1スイッチ素子 102 がオンである間に第2スイッチ素子 103 のオン・オフを切り替える。このように動作することにより、発熱素子 101 に流れる電流は、第2スイッチ素子 103 のオン・オフによって制御され、発熱素子 101 を高速に駆動できる。第1スイッチ素子 102 に供給される制御信号の立ち上がり時間・立ち下がり時間は発熱素子 101 に流れる電流の立ち上がり時間・立ち下がり時間に影響しないので、この制御信号を高速に変化させる必要がない。そのため、第1制御部 106a の回路構成を簡略化できるとともに、高電圧の高速に変化させることによるノイズの発生を低

40

50

減できる。

#### 【0022】

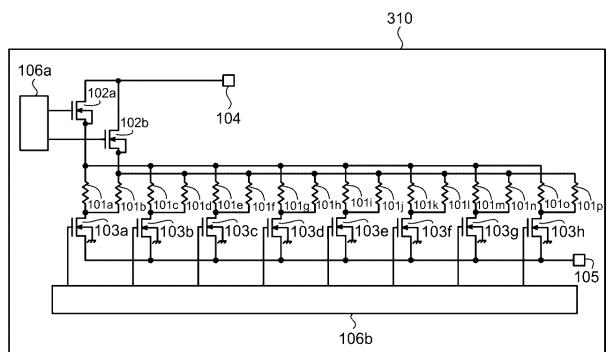

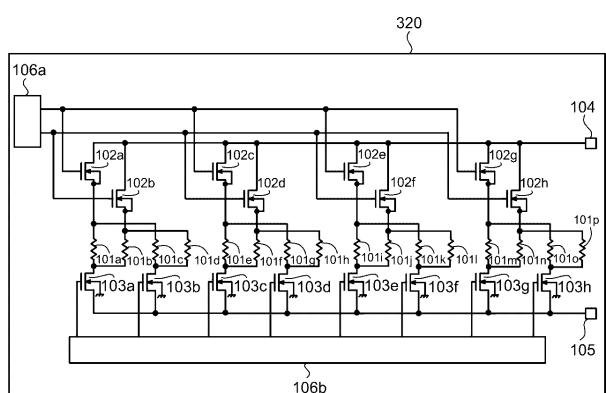

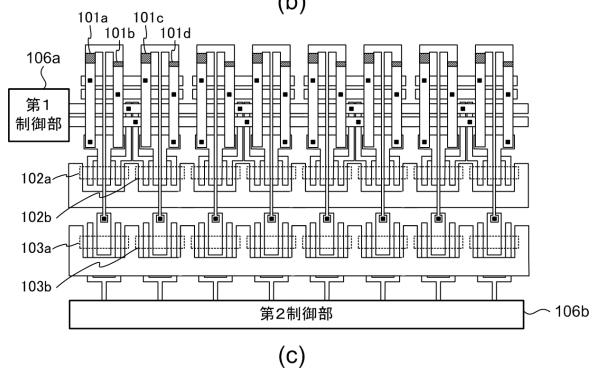

続いて、図3の等価回路図を参照して、他の一部の実施形態の半導体装置の構成例について説明する。図3において、図1の半導体装置100と同様の構成要素は同一の参照符号を付し、重複する説明を省略する。図3(a)に示す半導体装置310は、複数の発熱素子101a～101p、複数の第1スイッチ素子102a～102b、複数の第2スイッチ素子103a～103h、電源電極104、接地電極105、第1制御部106及び第2制御部107を備える。これらの構成要素は例えば半導体基板に形成される。半導体装置100と同様に、複数の発熱素子101a～101pを発熱素子101と総称し、複数の第1スイッチ素子102a～102bを第1スイッチ素子102と総称し、複数の第2スイッチ素子103a～103hを第2スイッチ素子103と総称する。

10

#### 【0023】

半導体装置310においても、同一の第2スイッチ素子103に接続された2以上の発熱素子101は、互いに異なる第1スイッチ素子102に接続されている。従って、半導体装置310においても、第1スイッチ素子102と第2スイッチ素子103との組を選択してオンにすることによって、1つの発熱素子101のみに電流を流し、他の発熱素子101に電流を流さないことができる。

#### 【0024】

また、半導体装置310において、各第1スイッチ素子102は8つの発熱素子101に接続され、各第2スイッチ素子103は2つの発熱素子101に接続される。従って、半導体装置310においても、スイッチ素子の個数を低減できる。半導体装置100に含まれるスイッチ素子の個数(第1スイッチ素子102の個数と第2スイッチ素子103の個数の和)は10個であり、これは発熱素子101の個数(16個)よりも少ない。

20

#### 【0025】

半導体装置310では、第1スイッチ素子102の個数(2個)が第2スイッチ素子103の個数(8個)よりも少ない。この場合に、第2スイッチ素子103は第1スイッチ素子102よりも密に配置される。そこで、1つの第2スイッチ素子103に接続された複数の発熱素子101が互いに隣接するように、複数の発熱素子101と複数の第2スイッチ素子103とを接続してもよい。例えば、第2スイッチ素子103aに接続された2つの発熱素子101a、101bは互いに隣接している。このように配置することによって、発熱素子101と第2スイッチ素子103との接続が容易になり、半導体装置310をさらに小型化できる。

30

#### 【0026】

図3(b)に示す半導体装置320は、複数の発熱素子101a～101p、複数の第1スイッチ素子102a～102h、複数の第2スイッチ素子103a～103h、電源電極104、接地電極105、第1制御部106a及び第2制御部106bを備える。これらの構成要素は例えば半導体基板に形成される。半導体装置100と同様に、複数の発熱素子101a～101pを発熱素子101と総称し、複数の第1スイッチ素子102a～102bを第1スイッチ素子102と総称し、複数の第2スイッチ素子103a～103hを第2スイッチ素子103と総称する。半導体装置320も半導体装置100と同様の構成を有しており、同様の効果を奏する。

40

#### 【0027】

半導体装置320では、第1制御部106aは、複数の第1スイッチ素子102に同一の制御信号(すなわち、同じタイミングでローレベル・ハイレベルが切り替わる制御信号)を供給してこれらの第1スイッチ素子102を同期して制御する。例えば、第1制御部106aは、4つの第1スイッチ素子102a、102c、102e、102gに同一の制御信号を供給し、4つの第1スイッチ素子102b、102d、102f、102hに同一の制御信号を供給する。半導体装置320では、同一の制御信号が供給される複数の第1スイッチ素子が互いに異なる発熱素子101に接続されているので、制御部106は複数の発熱素子101を個別に駆動することができる。

50

**【0028】**

半導体装置320は、4つの発熱素子101とこれらに接続された2つの第1スイッチ素子102及び2つの第2スイッチ素子103からなるブロックを4つ含むものとみなすことができる。この場合に、第1制御部106aは、ブロックごとに共通の制御信号の組を供給する。

**【0029】**

続いて、図4のタイミング図を参照して、半導体装置310、320の動作例、特に制御部106の動作例について説明する。この動作例において、電源電極104に電源電圧が供給され、接地電極105に接地電圧が供給されているとする。図4の横軸は時刻を表す。図2の縦軸は、第1スイッチ素子102a、102b及び第2スイッチ素子103a～103hについて、各スイッチ素子のゲートに供給される制御信号の電圧値を表し、発熱素子101a～101pについて、各発熱素子を流れる電流値を表す。半導体装置320では、第1スイッチ素子102aに供給される制御信号が第1スイッチ素子102c、102e、102gにも供給され、第1スイッチ素子102bに供給される制御信号が第1スイッチ素子102d、102f、102hにも供給される。

10

**【0030】**

半導体装置310、320は、図2で説明した半導体装置100の動作と同様にして、発熱素子101a～101pに順番に電流を流す。制御部106は、半導体装置310、320の外部からの信号に基づいて、図4に示す制御信号を生成してもよい。

20

**【0031】**

第1制御部106aは、トグルスイッチを用いて、ハイレベルの制御信号を供給する第1スイッチ素子102を順次切り替えてよい。これにより、第1制御部106aの出力負荷を一定にしつつ、発熱素子101の駆動周期を短縮できる。また、第1制御部106aが各ブロックに供給する制御信号の組を共通にすることによって、第1制御部106aの回路構成を簡易にでき、半導体装置を更に小型化できる。

**【0032】**

続いて、図5の配置図を参照して、半導体装置100の各構成要素の配置について説明する。半導体装置310、320についても同様に配置しうる。図5(a)に示すように、半導体装置100は横長の長方形形状を有する。発熱素子配置領域501に、複数の発熱素子101a～101dが長手方向に並んで配置される。第1スイッチ素子配置領域502に、複数の第1スイッチ素子102a～102bが長手方向に並んで配置される。第2スイッチ素子配置領域503に、複数の第2スイッチ素子103a～103bが長手方向に並んで配置される。第2制御部配置領域504に、第2制御部106aが複数の第2スイッチ素子103a～103bに沿って配置される。

30

**【0033】**

図5(b)は、図5(a)の発熱素子配置領域、第1スイッチ素子配置領域、および、第2スイッチ素子配置領域の詳細なレイアウトを示す図である。図5(b)は、図1で説明した回路ブロックを4つ並べたものである。ヒータ101(斜線で示す)は第1の方向(図面の横方向)に16個並んでいる。8個の第1スイッチ102と8個の第2スイッチ103とはそれぞれ、ヒータ101と同様に第1の方向に並んでいる。第1スイッチ102および第2スイッチ103はどちらもNMOSトランジスタであり、点線で囲んだ領域に形成されている。

40

**【0034】**

図5(b)の実施例では、トランジスタのゲートを形成するポリ配線と2層のアルミ配線により配線層が構成され、コンタクト(黒塗りの四角で示す)により各配線が接続されている。ヒータ101の一端は第1スイッチ102のソースと接続され、もう一端は第2スイッチ103のドレインと接続される。第1スイッチ102のドレインは電源電極104と接続され、バックゲートはソースと接続される。第2スイッチ103のソースとバックゲートは接地される。第1スイッチ102はそれぞれ、2つのヒータ101と接続される。第2スイッチ103はそれぞれ、異なる第1スイッチ102に接続された2つヒータ

50

のもう一端に接続される。第1スイッチ102のゲートには第1制御部106aから制御信号が入力され、第2スイッチ103のゲートには第2制御部106bから制御信号が入力される。

#### 【0035】

図5(c)に示す実施例は、図5(b)に示す実施例と比較して、ヒータ101の配置・大きさが異なる。図5(c)では、ヒータ101が千鳥に配置されている。偶数奇数でヒータ101のサイズや抵抗値、位置を変えることで、異なる吐出量のインクを出力することができる。

#### 【0036】

第1制御部配置領域505に、第1制御部106aが配置される。上述のように、第1制御部106aはレベル変換回路を有する点で第2制御部106bよりも複雑な回路構成を有する。そこで、第1制御部106aを複数の第1スイッチ素子102a～102bに沿って配置するのではなく、複数の第1スイッチ素子102a～102bと半導体装置100の短辺との間に配置する。これにより、発熱素子101を密に配置できる。また、半導体装置100の短辺の長さを短くできる。この位置に第1制御部106aを配置することによって、第1制御部106aから第1スイッチ素子102までの距離は、第2制御部106bから第2スイッチ素子103までの距離よりも長くなり、第1スイッチ素子102に供給される制御信号の波形が崩れる。しかし、上述のように、発熱素子101を流れる電流は第2スイッチ素子103のオン・オフによって制御されるので、この制御信号の波形の崩れが発熱素子101の駆動に影響を与えない。

10

20

#### 【0037】

半導体装置に含まれる発熱素子101、第1スイッチ素子102及び第2スイッチ素子103の個数は上述の例に限られない。一般に、第1スイッチ素子102の個数をm個とし、第2スイッチ素子103の個数をn個とすると、制御部106は、これらの積(すなわち、 $m \times n$ )の個数以下の発熱素子101を個別に駆動できる。

#### 【0038】

また、上述の例では、複数の第1スイッチ素子102のそれぞれが複数の発熱素子101に接続される。しかし、複数の第1スイッチ素子102が2つ以上の発熱素子101に接続された第1スイッチ素子102を1つ以上含み、他の第1スイッチ素子102がそれぞれ1つの発熱素子101に接続されてもよい。同様に、複数の第2スイッチ素子103が2つ以上の発熱素子101に接続された第2スイッチ素子103を1つ以上含み、他の第2スイッチ素子103がそれぞれ1つの発熱素子101に接続されてもよい。このように、半導体装置が1つの発熱素子101にのみ接続されるスイッチ素子を含んでいたとしても、スイッチ素子全体の個数(すなわち、 $m + n$ )が発熱素子101の個数以下であれば、従来例よりもスイッチ素子の個数を低減できる。

30

#### 【0039】

さらに、上述の実施形態では、電源電極104に電源電圧が供給され、接地電極105に接地電圧が供給されるが、一般に、電源電極104と接地電極105とに互いに異なる電圧が供給されれば上述の半導体装置は動作可能である。

#### 【0040】

40

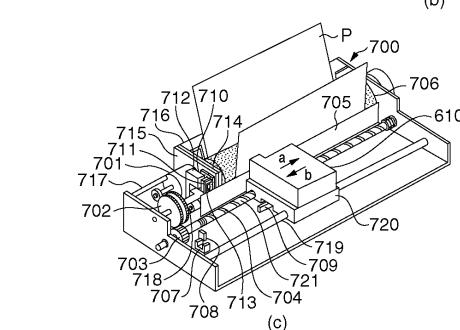

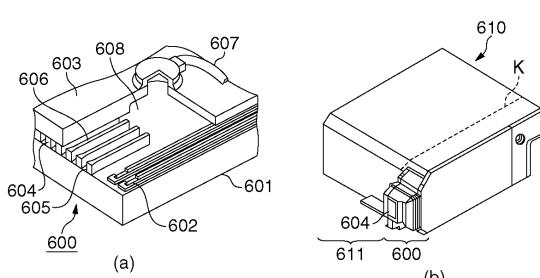

続いて、その他の実施形態として、図6を参照しつつ、上記の実施形態で説明された半導体装置を利用した液体吐出ヘッド、液体吐出カートリッジ及び液体吐出装置を以下に説明する。図6(a)は、いずれかの実施形態で説明された半導体装置を基体601として有する記録ヘッド600の主要部を液体吐出ヘッドの一例として示す。図6(a)では、上述の実施形態の発熱素子101が発熱部602として描かれている。また、説明のために天板603の一部が切り取られている。図6(a)に示されるように、複数の吐出口604に連通した液路605を形成するための流路壁部材606とインク供給口607を有する天板603とを基体601に組み合わせることにより、記録ヘッド600が構成される。この場合に、インク供給口607から注入されるインクが内部の共通液室608へ蓄えられて各液路605へ供給され、その状態で基体601が駆動されることで、吐出口

50

604からインクが吐出される。

**【0041】**

図6(b)は液体吐出カートリッジの一例であるインクジェット用のカートリッジ610の全体構成を説明する図である。カートリッジ610は、上述した複数の吐出口604を有する記録ヘッド600と、この記録ヘッド600に供給するためのインクを収容するインク容器611とを備えている。液体容器であるインク容器611は、境界線Kを境に記録ヘッド600に着脱可能に設けられている。カートリッジ610には、図6(c)に示される記録装置に搭載された場合にキャリッジ側からの駆動信号を受け取るための電気的コンタクト(不図示)が設けられており、この駆動信号によって発熱部602が駆動される。インク容器611の内部には、インクを保持するために纖維質状又は多孔質状のインク吸収体が設けられており、これらのインク吸収体によってインクが保持されている。

10

**【0042】**

図6(c)は液体吐出装置の一例であるインクジェット記録装置700の外観斜視図を示す。インクジェット記録装置700は、カートリッジ610を搭載し、カートリッジ610へ付与される信号を制御することにより、高速記録、高画質記録を実現しうる。インクジェット記録装置700において、カートリッジ610は、駆動モータ701の正逆回転に連動して駆動力伝達ギア702、703を介して回転するリードスクリュー704の螺旋溝721に対して係合するキャリッジ720上に搭載されている。カートリッジ610は駆動モータ701の駆動力によってキャリッジ720と共にガイド719に沿って矢印a又はb方向に往復移動可能である。不図示の記録媒体給送装置によってプラテン706上に搬送される記録用紙P用の紙押え板705は、キャリッジ移動方向に沿って記録用紙Pをプラテン706に対して押圧する。フォトカプラ707、708は、キャリッジ720に設けられたレバー709のフォトカプラ707、708が設けられた領域での存在を確認して駆動モータ701の回転方向の切換等を行うためにホームポジションの検知を行う。支持部材710はカートリッジ610の全面をキャップするキャップ部材711を支持し、吸引部712はキャップ部材711内を吸引し、キャップ内開口を介してカートリッジ610の吸引回復を行う。移動部材715は、クリーニングブレード714を前後方向に移動可能にし、クリーニングブレード714及び移動部材715は、本体支持板716に支持されている。クリーニングブレード714は、図示の形態でなく周知のクリーニングブレードが本実施形態にも適用できる。また、レバー717は、吸引回復の吸引を開始するために設けられ、キャリッジ720と係合するカム718の移動に伴って移動し、駆動モータ701からの駆動力がクラッチ切換等の公知の伝達手法で移動制御される。カートリッジ610に設けられた発熱部602に信号を付与し、駆動モータ701等の各機構の駆動制御を司る記録制御部(不図示)は、装置本体側に設けられている。

20

30

**【0043】**

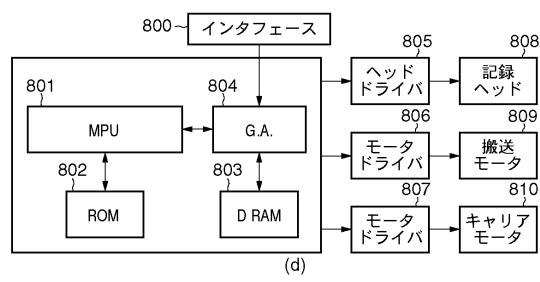

次に、図6(d)に示されるブロック図を用いてインクジェット記録装置700の記録制御を実行するための制御回路の構成について説明する。制御回路は、記録信号が入力するインタフェース800、MPU(マイクロプロセッサ)801、MPU801が実行する制御プログラムを格納するプログラムROM802を備えている。制御回路は更に、各種データ(上記記録信号やヘッドに供給される記録データ等)を保存しておくダイナミック型のRAM(ランダムアクセスメモリ)803と、記録ヘッド808に対する記録データの供給制御を行うゲートアレイ804とを備えている。ゲートアレイ804は、インタフェース800、MPU801、RAM803間のデータ転送制御も行う。さらにこの制御回路は、記録ヘッド808を搬送するためのキャリアモータ810と、記録紙搬送のための搬送モータ809とを備えている。この制御回路はさらに、記録ヘッド808を駆動するヘッドドライバ805、搬送モータ809及びキャリアモータ810をそれぞれ駆動するためのモータドライバ806、807とを備えている。上記制御構成の動作を説明すると、インタフェース800に記録信号が入るとゲートアレイ804とMPU801との間で記録信号がプリント用の記録データに変換される。そして、モータドライバ806、807が駆動されるとともに、ヘッドドライバ805に送られた記録データに従って記録

40

50

ヘッドが駆動され、印字が行われる。

【符号の説明】

【0044】

100 半導体装置； 101a～101p 発熱素子； 102a～102h 第1スイッチ素子； 103a～103h 第2スイッチ素子； 104 電源電極； 105 接地電極； 106a 第1制御部； 106b 第2制御部

【図1】

【図2】

【図3】

(a)

(b)

【図4】

【図5】

(a)

(b)

(c)

【図6】

---

フロントページの続き

(72)発明者 藤井 一成

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 大村 昌伸

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 高松 大治

(56)参考文献 特開2007-283706(JP,A)

特開平11-170512(JP,A)

特開平09-139816(JP,A)

特開平06-069497(JP,A)

特開平06-183107(JP,A)

特開平04-004152(JP,A)

特開平05-104707(JP,A)

特開平09-011504(JP,A)

特開2009-166508(JP,A)

米国特許出願公開第2006/0284909(US,A1)

(58)調査した分野(Int.Cl., DB名)

B41J2/01 - 2 / 215