(12) 发明专利申请

(10) 申请公布号 CN 115963137 A

(43) 申请公布日 2023.04.14

(21) 申请号 202211251800.1

(22) 申请日 2022.10.13

(30) 优先权数据

2021-168233 2021.10.13 JP

(71) 申请人 纽富来科技股份有限公司

地址 日本神奈川县

(72) 发明人 安藤厚司 村田贵比吕

(74) 专利代理机构 永新专利商标代理有限公司

72002

专利代理人 刘杰

(51) Int.Cl.

G01N 23/2251 (2018.01)

权利要求书2页 说明书7页 附图5页

(54) 发明名称

电子束检查装置

(57) 摘要

提供一种电子束检查装置，能够抑制施加了减速电压的基板与支承销之间的空间的电场的集中，进行高精度的检查。本发明的一个方式的电子束检查装置具备：光学系统，向基板上照射1次电子束；射束分离器，将因上述1次电子束照射到上述基板而发射的2次电子束从上述1次电子束分离；检测器，检测分离出的上述2次电子束；工作台，供上述基板载置，且能够移动；支承台，在上述工作台上支承上述基板；以及施加部，对上述基板施加规定的第1电压。上述支承台具有从下方支承上述基板的多个支承销，上述支承销包含柱状的绝缘体以及设置在该绝缘体内的金属膜，对上述金属膜施加规定的第2电压。

1. 一种电子束检查装置，其特征在于，具备：

光学系统，向基板上照射1次电子束；

射束分离器，将因上述1次电子束照射到上述基板而发射的2次电子束从上述1次电子束分离；

检测器，检测分离出的上述2次电子束；

工作台，供上述基板载置，且能够移动；

支承台，在上述工作台上支承上述基板；以及

施加部，对上述基板施加规定的第1电压，

上述支承台具有从下方支承上述基板的多个支承销，

上述支承销包含柱状的绝缘体以及设置在该绝缘体内的金属膜，

对上述金属膜施加规定的第2电压。

2. 根据权利要求1所述的电子束检查装置，其特征在于，

上述第1电压与上述第2电压相同。

3. 根据权利要求1所述的电子束检查装置，其特征在于，

上述金属膜被上述绝缘体覆盖。

4. 根据权利要求3所述的电子束检查装置，其特征在于，

上述金属膜配置在与上述支承销的高度方向正交的方向上，

上述支承销的侧面与上述金属膜的端部的间隔为0.3mm以上2mm以下。

5. 根据权利要求3所述的电子束检查装置，其特征在于，

上述绝缘体具有在上表面形成有凹部的基端体以及在下表面设置有凸部的前端体，上

述凹部与上述凸部嵌合，

在上述凹部的底面与上述凸部的下端面之间设置有上述金属膜。

6. 根据权利要求1所述的电子束检查装置，其特征在于，

上述金属膜配置在与上述支承销的高度方向正交的方向上，

电压施加用的布线从上述金属膜的下表面沿着垂直方向延伸。

7. 根据权利要求6所述的电子束检查装置，其特征在于，

上述支承台具有平板状的台座，

上述支承销从上述台座向上方突出，

上述金属膜从上述台座的正面起的高度为上述支承销的高度的30%以上。

8. 根据权利要求7所述的电子束检查装置，其特征在于，

上述支承销的高度为15mm以上30mm以下。

9. 根据权利要求1所述的电子束检查装置，其特征在于，

上述支承销为上端成为凸曲面的圆柱状。

10. 根据权利要求9所述的电子束检查装置，其特征在于，

上述支承销具有：

前端体，具有平坦的圆形的底面、从该底面的周缘部立起的侧墙面以及与该侧墙面的

上端相连的上述凸曲面；以及

圆柱状的基端体。

11. 根据权利要求10所述的电子束检查装置，其特征在于，

在上述前端体的底面设置有第1金属膜，在上述基端体的上表面设置有第2金属膜，该第1金属膜与该第2金属膜接合。

12. 根据权利要求10所述的电子束检查装置，其特征在于，

上述前端体的底面与上述基端体的上表面通过导电性粘接剂粘接。

## 电子束检查装置

[0001] 本申请以日本专利申请2021-168233号(申请日:2021年10月13日)为基础申请,享受该基础申请的优先权。本申请通过参照该基础申请而包含该基础申请的全部内容。

### 技术领域

[0002] 本发明涉及电子束检查装置。

### 背景技术

[0003] 随着LSI的高集成化,半导体设备所要求的电路线宽逐年微细化。为了向半导体设备形成所希望的电路图案,采用如下方法:使用缩小投影型曝光装置,将在石英上形成的高精度的原画图案缩小转印到晶片上。

[0004] 对于制造成本极高的LSI的制造来说,成品率的提高是不可缺少的。随着形成在半导体晶片上的LSI图案尺寸的微细化,作为图案缺陷而必须检测的尺寸也极小。因此,检查转印到半导体晶片上的超微细图案的缺陷的图案检查装置的重要性增加。

[0005] 作为图案缺陷的检查方法,已知有对拍摄形成在半导体晶片、光刻掩模等基板上的图案而得的测定图像与拍摄设计数据或者基板上的相同图案而得的测定图像进行比较的方法。例如,可举出对拍摄相同基板上的不同部位的相同图案而得的测定图像数据彼此进行比较“die to die(裸片-裸片)检查”、基于图案设计的设计数据生成设计图像数据(参照图像)并将其与成为拍摄图案而得的测定数据的测定图像进行比较“die to database(裸片-数据库)检查”。在所比较的图像不一致的情况下,判定为有图案缺陷。

[0006] 通过电子束在检查对象的基板上进行扫描(scan),检测伴随电子束的照射而从基板发射的2次电子,取得图案像的检查装置的开发正在进行。作为使用了电子束的检查装置,使用了多射束的装置的开发也正在进行。

[0007] 为了提高分辨率,已知有如下方法:提高电子束的加速电压,并对检查对象基板施加负的电压(减速电压),使电子束在基板的正前方减速。检查对象的基板载置在可移动的工作台上,并支承于多根支承销。

[0008] 以往,有时在被施加了减速电压的基板与支承销之间的空间集中电场,诱发放电。如果产生放电,则存在电子束的轨道变化,检查精度劣化的问题。此外,如果产生较大的放电,则有时会产生使装置破损的问题。

### 发明内容

[0009] 本发明提供一种电子束检查装置,能够抑制施加了减速电压的基板与支承销之间的空间的电场的集中,进行高精度的检查。

[0010] 本发明的一个方式的电子束检查装置具备:光学系统,向基板上照射1次电子束;射束分离器,将因上述1次电子束照射到上述基板而发射的2次电子束从上述1次电子束分离;检测器,检测分离出的上述2次电子束;工作台,供上述基板载置,且能够移动;支承台,在上述工作台上支承上述基板;以及施加部,对上述基板施加规定的第1电压,上述支承台

具有从下方支承上述基板的多个支承销，上述支承销包含柱状的绝缘体以及设置在该绝缘体内的金属膜，对上述金属膜施加规定的第2电压。

### 附图说明

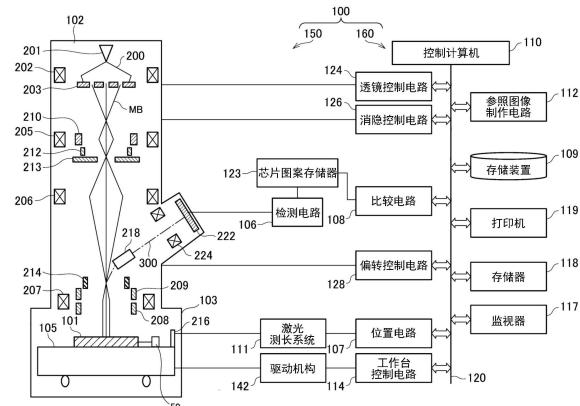

- [0011] 图1是本发明的实施方式的图案检查装置的概要构成图。

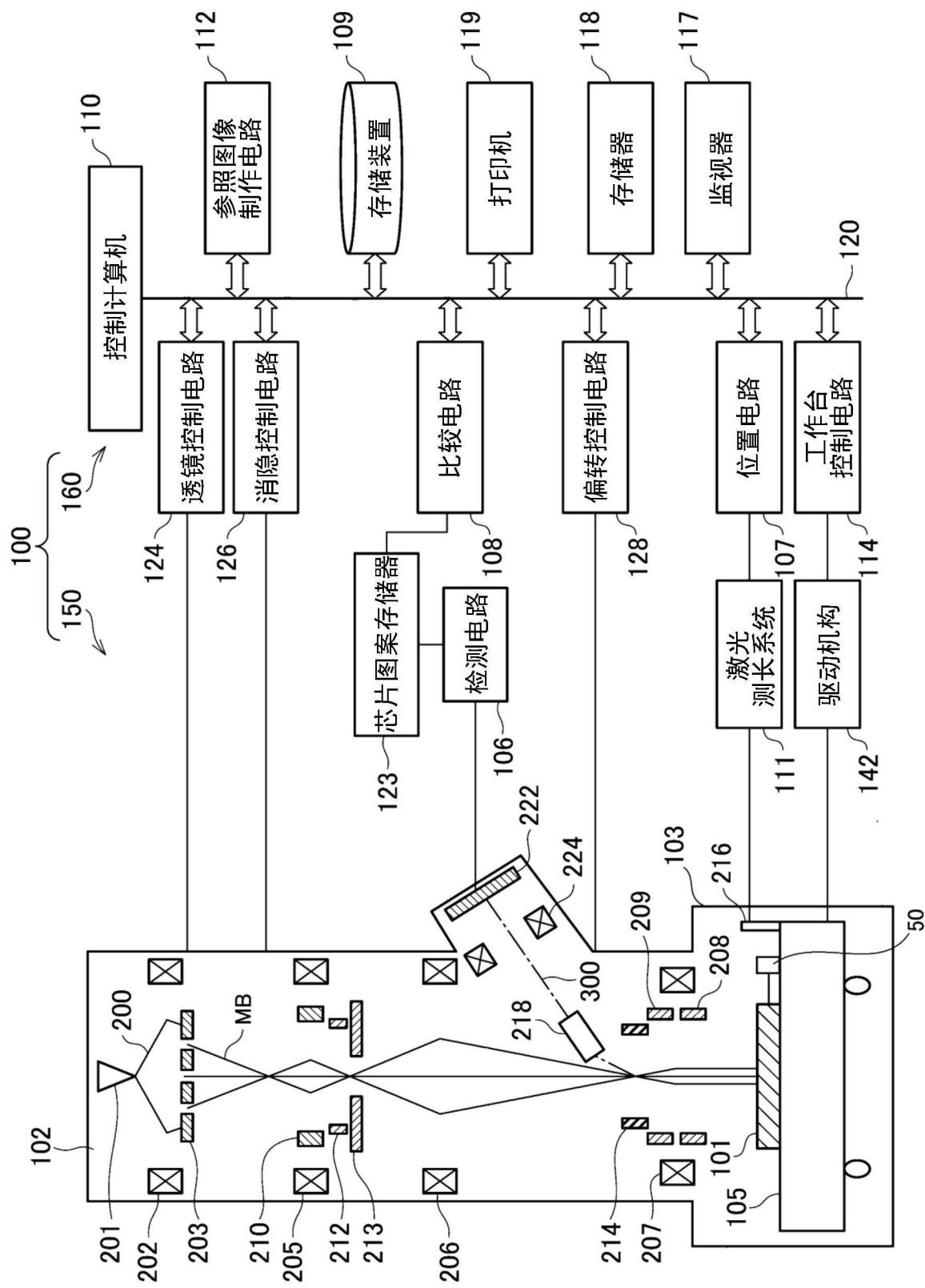

- [0012] 图2是成形孔径阵列基板的俯视图。

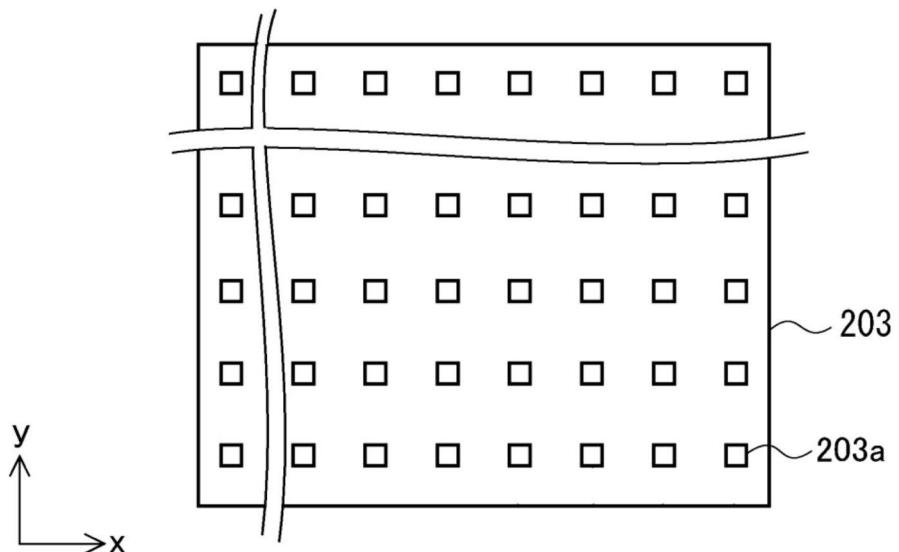

- [0013] 图3是支承台的立体图。

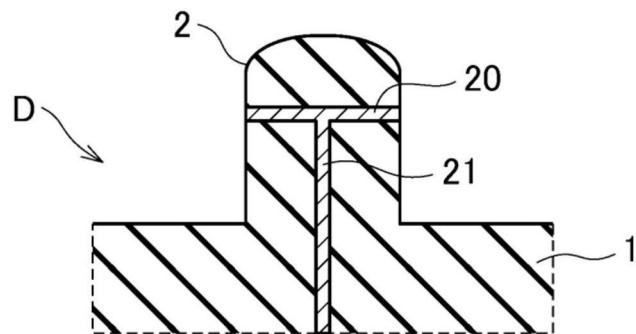

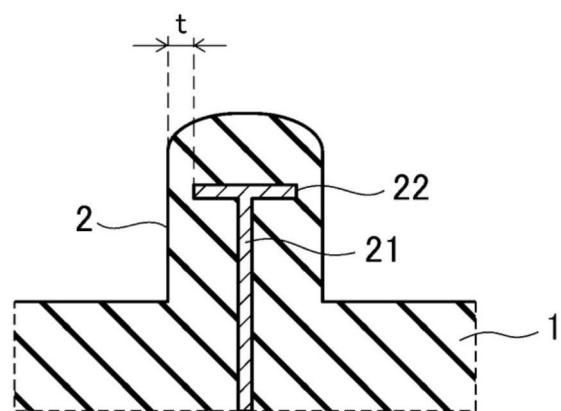

- [0014] 图4是支承销的剖视图。

- [0015] 图5是支承销与基板的示意图。

- [0016] 图6是比较例的支承销和基板的示意图。

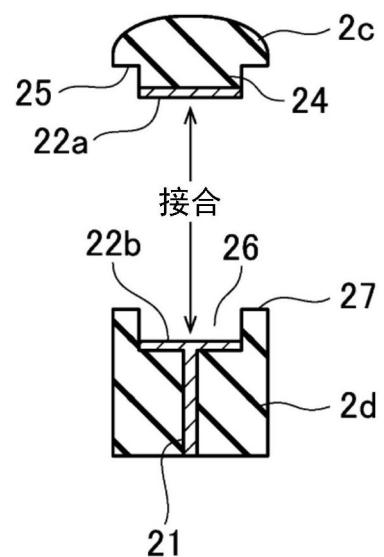

- [0017] 图7是对支承销的制造方法进行说明的图。

- [0018] 图8是支承销的剖视图。

- [0019] 图9是对支承销的制造方法进行说明的图。

- [0020] 符号的说明

- [0021] 1：台座；2：支承销；2a：前端体；2b：基端体；20：金属膜；21：布线；100：图案检查装置；101：基板；105：工作台。

### 具体实施方式

- [0022] 以下，基于附图对本发明的实施方式进行说明。

- [0023] 图1是本实施方式的图案检查装置100的概要构成图。该图案检查装置100将电子束形成的多射束照射到被检查基板来拍摄2次电子像。

- [0024] 如图1所示，图案检查装置100具备图像取得机构150以及控制系统电路160。图像取得机构150具备电子束柱102(电子镜筒)以及检查室103。在电子束柱102内配置有电子枪201、电磁透镜202、成形孔径阵列基板203、电磁透镜205、静电透镜210、一并消隐偏转器212、限制孔径基板213、电磁透镜206、电磁透镜207(物镜)、主偏转器208、副偏转器209、射束分离器214、偏转器218、电磁透镜224以及多重检测器222。

- [0025] 在检查室103内配置有能够沿着XYZ方向移动的工作台105。在工作台105上配置有作为检查对象的基板101(试样)。在基板101中包括曝光用掩模基板以及硅晶片等半导体基板。在基板101为半导体基板的情况下，在半导体基板形成有多个芯片图案(晶片裸片)。在基板101为曝光用掩模基板的情况下，在曝光用掩模基板形成有芯片图案。芯片图案由多个图形图案构成。通过将形成于曝光用掩模基板的芯片图案多次曝光转印到半导体基板上，在半导体基板形成多个芯片图案(晶片裸片)。

- [0026] 基板101将图案形成面朝向上侧地配置于工作台105。在工作台105设置有对基板101的上表面(图案形成面)施加减速电压的电压施加部50。基板101由后述的支承台D(参照图3)从下方侧支承。

- [0027] 在工作台105上配置有反射镜216，该反射镜216反射从配置于检查室103的外部的激光测长系统111照射的激光测长用的激光。

- [0028] 多重检测器222在电子束柱102的外部与检测电路106连接。检测电路106与芯片图案存储器123连接。

[0029] 在控制系统电路160中,对检查装置100整体进行控制的控制计算机110经由总线120与位置电路107、比较电路108、参照图像制作电路112、工作台控制电路114、透镜控制电路124、消隐控制电路126、偏转控制电路128、磁盘装置等存储装置109、监视器117、存储器118以及打印机119连接。

[0030] 偏转控制电路128经由未图示的DAC(数字模拟转换)放大器与主偏转器208、副偏转器209、偏转器218连接。

[0031] 芯片图案存储器123与比较电路108连接。

[0032] 工作台105在工作台控制电路114的控制下由驱动机构142驱动。工作台105能够在水平方向以及旋转方向上移动。此外,工作台105能够在高度方向上移动。

[0033] 激光测长系统111通过接收来自反射镜216的反射光,利用激光干涉法的原理对工作台105的位置进行测长。将由激光测长系统111测定出的工作台105的移动位置通知给位置电路107。

[0034] 电磁透镜202、电磁透镜205、电磁透镜206、电磁透镜207(物镜)、静电透镜210、电磁透镜224以及射束分离器214由透镜控制电路124控制。

[0035] 静电透镜210例如由中央部开口的3层以上的电极基板构成,通过透镜控制电路124经由未图示的DAC放大器对中层电极基板进行控制。对静电透镜210的上层以及下层电极基板施加接地电位。

[0036] 一并消隐偏转器212由2极以上的电极构成,通过消隐控制电路126经由未图示的DAC放大器对每个电极进行控制。

[0037] 副偏转器209由4极以上的电极构成,通过偏转控制电路128经由DAC放大器对每个电极进行控制。主偏转器208由4极以上的电极构成,通过偏转控制电路128经由DAC放大器对每个电极进行控制。偏转器218由4极以上的电极构成,通过偏转控制电路128经由DAC放大器对每个电极进行控制。

[0038] 在电子枪201连接有未图示的高压电源电路,通过从高压电源电路向电子枪201内的未图示的丝极(阴极)与引出电极(阳极)之间的加速电压的施加,并且其他的引出电极(晶片)的电压的施加以及规定的温度的阴极的加热,从阴极发射的电子组被加速,成为电子束200而发射。

[0039] 图2是表示成形孔径阵列基板203的构成的概念图。在成形孔径阵列基板203,在x、y方向上以规定的排列间距呈二维状形成有开口部203a。各开口部203a均为相同的尺寸形状的矩形或者圆形(包括长圆形)。

[0040] 从电子枪201(发射源)发射的电子束200由电磁透镜202折射,对成形孔径阵列基板203整体进行照明。如图2所示,在成形孔径阵列基板203形成有多个开口203a,电子束200对包括多个开口部203a的区域进行照明。照射到多个开口部203a的位置的电子束200的各一部分分别通过多个开口部203a,由此形成多射束MB(多1次电子束)。

[0041] 多射束MB由电磁透镜205以及电磁透镜206折射,一边反复成像以及交叉,一边通过配置在多射束MB的各射束的交叉位置的射束分离器214行进到电磁透镜207(物镜)。然后,电磁透镜207将多射束MB聚焦到基板101上。由电磁透镜207聚焦(对焦)到基板101(试样)面上的多射束MB由主偏转器208以及副偏转器209一并偏转,照射到各射束的基板101上的各个照射位置。由于对基板101施加减速电压(第1电压),所以多射束MB在基板101的正前

方减速。

[0042] 另外,在通过一并消隐偏转器212一并偏转多射束MB整体的情况下,位置从限制孔径基板213的中心的孔偏移,但被限制孔径基板213遮蔽。另一方面,未被一并消隐偏转器212偏转的多射束MB如图1所示那样通过限制孔径基板213的中心的孔。通过一并消隐偏转器212的接通/断开,进行消隐控制,一并控制射束的开启/关闭。

[0043] 当向基板101的所希望的位置照射多射束MB时,从基板101发射与多射束MB(多1次电子束)的各射束对应的、包含反射电子的2次电子的束(多2次电子束300)。

[0044] 从基板101发射的多2次电子束300通过电磁透镜207行进到射束分离器214。

[0045] 射束分离器214在与多射束MB的中心射束行进的方向(轨道中心轴)正交的面上在正交的方向上产生电场和磁场。电场与电子的行进方向无关而在相同的方向上施加力。与此相对,磁场按照弗莱明左手定律施加力。因此,能够根据电子的进入方向使作用于电子的力的朝向变化。

[0046] 在从上侧进入射束分离器214的多射束MB中,由电场产生的力与由磁场产生的力相互抵消,多射束MB朝下方直进。与此相对,在从下侧进入射束分离器214的多2次电子束300中,由电场产生的力与由磁场产生的力都在相同的方向上起作用,多2次电子束300朝斜上方弯曲而从多射束MB分离。

[0047] 朝斜上方弯曲而从多射束MB分离的多2次电子束300由偏转器218偏转,并由电磁透镜224折射,投影到多重检测器222。在图1中,将多2次电子束300的轨道不折射而简化示出。

[0048] 多重检测器222对所投影的多2次电子束300进行检测。多重检测器222例如具有未图示的二极管型的二维传感器。然后,在与多射束MB的各射束对应的二极管型的二维传感器位置处,多2次电子束300的各2次电子与二极管型的二维传感器碰撞,在传感器内部使电子倍增,利用放大后的信号针对每个像素生成2次电子图像数据。

[0049] 由多重检测器222检测到的2次电子的检测数据(测定图像:2次电子图像:被检查图像)按照测定顺序输出到检测电路106。在检测电路106内,通过未图示的A/D转换器将模拟的检测数据转换成数字数据,并保存在芯片图案存储器123中。如此,图像取得机构150取得形成在基板101上的图案的测定图像。

[0050] 参照图像制作电路112基于成为在基板101形成图案的基础的设计数据或者形成于基板101的图案的曝光图形数据中定义的设计图案数据,针对每个掩模裸片制作参照图像。例如,从存储装置109通过控制计算机110读出设计图案数据,将所读出的设计图案数据中定义的各图形图案转换成2值或者多值的图形数据。

[0051] 设计图案数据中定义的图形例如将长方形、三角形作为基本图形,例如保存有通过图形的基准位置处的坐标(x,y)、边的长度、作为区别长方形、三角形等的图形种类的识别符的图形代码这样的信息定义各图案图形的形状、大小、位置等的图形数据。

[0052] 当成为图形数据的设计图案数据输入参照图像制作电路112时,展开至每个图形的数据,解释表示该图形数据的图形形状的图形代码、图形尺寸等。然后,作为配置在以规定的量化尺寸的网格为单位的网眼内的图案,展开为2值或者多值的设计图案的图像数据并输出。

[0053] 换言之,读入设计数据,针对将检查区域假想分割为以规定的尺寸为单位的网眼

而成的每个网眼，对设计图案中的图形所占的占有率进行运算，输出n位的占有率数据。例如，优选将一个网眼设定为1个像素。并且，如果使1个像素具有 $1/2^8 (=1/256)$ 的分辨率，则将 $1/256$ 的小区域分配给配置在像素内的图形的区域的量，对像素内的占有率进行运算。然后，作为8位的占有率数据输出到参照图像制作电路112。网眼(检查像素)只要与测定数据的像素一致即可。

[0054] 接着，参照图像制作电路112对图形的图形数据即设计图案的设计图像数据实施适当的滤波处理。作为测定图像的光学图像数据，处于通过光学系统作用滤波的状态、换言之处于连续变化的模拟状态。因此，通过也对数字值的设计侧的图形数据即设计图案的图像数据实施滤波处理，能够使图像强度(浓淡值)与测定数据一致。制作出的参照图像的图像数据被输出到比较电路108。

[0055] 比较电路108对从基板101测定出的测定图像(被检查图像)与对应的参照图像进行比较。具体而言，针对每个像素对对位后的被检查图像与参照图像进行比较。使用规定的判定阈值按照规定的判定条件对每个像素将两者进行比较，例如判定有无形状缺陷这样的缺陷。例如，如果每个像素的灰度值差大于判定阈值Th，则判定为缺陷候补。然后，输出比较结果。比较结果可以保存于存储装置109、存储器118，可以显示于监视器117，也可以从打印机119打印输出。

[0056] 除了上述的裸片-数据库检查之外，也可以进行裸片-裸片检查。在进行裸片-裸片检查的情况下，对拍摄相同基板101上的不同部位的相同图案而得的测定图像数据彼此进行比较。因此，图像取得机构150使用多射束MB(电子束)，从形成在相同的图形图案彼此(第1图形图案与第2图形图案)不同的位置的基板101取得一方的图形图案(第1图形图案)与另一方的图形图案(第2图形图案)各自的2次电子图像即测定图像。在该情况下，所取得的一方的图形图案的测定图像成为参照图像，另一方的图形图案的测定图像成为被检查图像。所取得的一方的图形图案(第1图形图案)与另一方的图形图案(第2图形图案)的图像可以在相同的芯片图案数据内，也可以分开在不同的芯片图案数据。检查的方法也可以与裸片-数据库检查相同。

[0057] 接着，使用图3～图5对在工作台105上支承基板101的支承台D进行说明。如图3所示，支承台D具有平板状的台座1、以及从台座1朝上方突出的多个支承销2。例如，从台座1突出3根支承销2，对基板101进行3点支承。

[0058] 如图4所示，支承销2为前端(上端)成为凸曲面的圆柱状，在高度方向的中途部分设置有金属膜20。例如，金属膜20配置在与高度方向正交的方向上，换言之与台座1的主面(上表面)平行地配置。布线21从金属膜20的下表面沿着垂直方向延伸，能够对金属膜20施加任意的电压。除了金属膜20以及布线21以外，支承台D由绝缘体构成。

[0059] 支承销2的水平方向的直径为5mm以上15mm以下左右，支承销2的高度(从台座1的主面到支承销2的前端的高度)为15mm以上30mm以下左右。优选金属膜20从台座1的主面起的高度为支承销2的高度的30%以上左右。

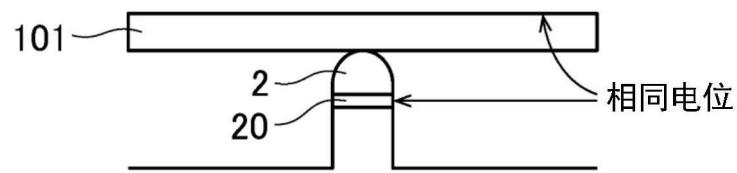

[0060] 在本实施方式中，如图5所示，经由布线21对金属膜20施加电压(第2电压)，以使金属膜20与基板101的表面成为相同的电位。对金属膜20的施加电压例如由工作台控制电路114控制。

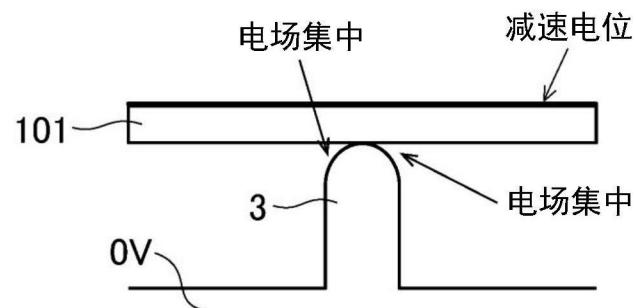

[0061] 作为比较例，如图6所示，在通过不包含金属膜而仅由绝缘体构成的支承销3支承

基板101的情况下,在支承销3的前端部与被施加减速电压的基板101之间的空间集中电场,可能会产生放电。

[0062] 另一方面,在本实施方式中,支承销2的金属膜20与基板101的表面成为相同的电位,因此,能够抑制在支承销2的前端部与基板101之间的空间集中电场,防止放电的产生,进行高精度的检查。

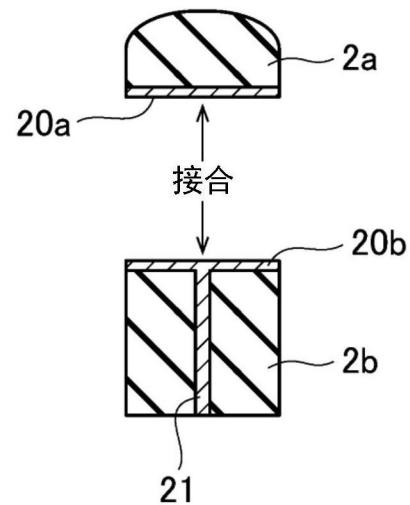

[0063] 如图7所示,通过将前端体2a与基端体2b接合能够制作支承销2。前端体2a具有平坦的圆形的底面、从底面的周缘部立起的侧周面、以及与侧周面的上端相连的凸曲面,在底面设置有金属膜20a。

[0064] 基端体2b为圆柱状,在上表面设置有金属膜20b。此外,在基端体2b的中心轴位置设置有布线21,布线21的上部与金属膜20b连接。布线21的材料能够使用钛、银等。

[0065] 作为前端体2a以及基端体2b中使用的绝缘材料,可举出蓝宝石、堇青石、块滑石、氧化铝、氧化钇、碳化硅、氮化铝、氧化锆等。

[0066] 在前端体2a的底面、基端体2b的上表面,例如能够通过涂布、蒸镀、溅射等形成金属膜20a、20b。金属膜20a、20b例如能够使用银-铜-钛合金进行钎焊。

[0067] 通过将前端体2a的底面的金属膜20a与基端体2b的上表面的金属膜20b接合,前端体2a与基端体2b一体化而制作支承销2。金属膜20a、20b的接合方法没有特别限定,例如可以使用公知的耐热性无机粘接剂,也可以通过固相接合、扩散接合进行接合。

[0068] 也可以使用银膏等的导电性粘接剂,进行金属膜20的形成、以及前端体2a与基端体2b的粘接。

[0069] 图4所示的支承销2的金属膜20的端部向支承销2的侧面露出,因此,在支承销2的表面(沿面方向)产生电场,有可能产生放电。

[0070] 因此,如图8所示,优选以端部不向支承销2的侧面露出的方式设置金属膜22。优选支承销2的侧面与金属膜20的周缘的间隔(深度)t为0.3mm以上2mm以下。

[0071] 通过将金属膜22与基板101的表面设为相同的电位,能够抑制在支承销2的前端部与基板101之间的空间集中电场,并且能够更有效地抑制在支承销2的表面(沿面方向)产生电场。因此,能够防止放电的产生,进行高精度的检查。

[0072] 图8所示的支承销2例如能够通过将图9所示的前端体2c与基端体2d接合来制作。

[0073] 前端体2c在圆形的底面25(下表面)的中央部设置有朝下方突出的凸部24。侧周面从底面25的周缘立起,凸曲面与侧周面的上端相连。在凸部24的前端面(下端面)设置有金属膜22a。

[0074] 基端体2d为圆柱状,在上表面的中央部设置有凹部(凹陷部)26。在凹部26的底面设置有金属膜22b。在基端体2d的中心轴位置设置有布线21,布线21的上部与金属膜22b连接。

[0075] 将前端体2c的凸部24与基端体2d的凹部26嵌合,使前端体2c的底面25与基端体2d的上表面27抵接。通过将前端体2c与基端体2d接合,得到图8所示的构成的支承销2。

[0076] 在上述实施方式中,对使用多射束的检查装置进行了说明,但也可以是使用单射束的检查装置。

[0077] 优选将支承销2的金属膜20、22与基板101的表面设为相同的电位,但即使存在少许的电位差,与图6所示的构成相比,能够抑制支承销2与基板101之间的空间的电场的集

中。

[0078] 另外，本发明并不限于上述实施方式本身，能够在实施阶段在不脱离其主旨的范围内将构成要素变形而具体化。此外，通过上述实施方式中公开的多个构成要素的适当组合，能够形成各种发明。例如，可以从实施方式所示的全部构成要素删除几个构成要素。进而，也可以将不同的实施方式的构成要素适当组合。

图1

图2

图3

图4

图5

图6

图7

图8

图9