(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4880014号 (P4880014)

(45) 発行日 平成24年2月22日(2012.2.22)

(24) 登録日 平成23年12月9日(2011.12.9)

| (51) Int.Cl. |      |           | F I  |      |   |

|--------------|------|-----------|------|------|---|

| HO3L         | 1/02 | (2006.01) | H03L | 1/02 |   |

| HO3L         | 3/00 | (2006.01) | HO3L | 3/00 |   |

| HO3L         | 7/08 | (2006.01) | H03L | 7/08 | G |

請求項の数 5 (全 17 頁)

(21) 出願番号 特願2009-184126 (P2009-184126) (22) 出願日 平成21年8月7日 (2009.8.7) (65) 公開番号 特開2011-40850 (P2011-40850A) (43) 公開日 平成23年2月24日 (2011.2.24) 審査請求日 平成23年3月31日 (2011.3.31) ||(73)特許権者 000232483

日本電波工業株式会社

東京都渋谷区笹塚一丁目50番1号 笹塚 NAビル

(74)代理人 100093104

弁理士 船津 暢宏

|(72)発明者 大西 直樹

北海道千歳市柏台南1丁目3番1号 千歳 アルカディア・プラザ 日本電波工業株式

会社内

審査官 上田 智志

最終頁に続く

(54) 【発明の名称】 周波数シンセサイザ

#### (57)【特許請求の範囲】

#### 【請求項1】

基準信号を発生する基準信号発生回路を備え、前記基準信号発生回路から出力される基準信号と、電圧制御発振器からの出力信号とを比較して、前記電圧制御発振器の出力信号が所望の周波数となるよう制御する周波数シンセサイザであって、

前記基準信号発生回路が、電源投入後短時間で周波数が安定化する特性を備えた第1の発振器と、

電源投入直後は前記第1の発振器よりも周波数が不安定であるが、一定時間経過後以降は前記第1の発振器より周波数の安定度が高い特性を備えた第2の発振器と、

前記第1の発振器からの出力のウェイト調整を行う第1のウェイト変換器と、

前記第2の発振器からの出力のウェイト調整を行う第2のウェイト変換器と、

前記第1及び第2のウェイト変換器からの出力を加算して前記基準信号として出力する 加算器と、

前記第1のウェイト変換器における第1のウェイトと前記第2のウェイト変換器における第2のウェイトについて、電源投入直後は、前記第1のウェイトを前記第2のウェイトより高くして前記第2のウェイトを前記第1のウェイトより低くし、時間経過に応じて徐々に前記第1のウェイトを低く、前記第2のウェイトを高くし、前記一定時間経過後には、前記第1のウェイトを0パーセントとし、前記第2のウェイトを100パーセントとするようウェイトの値を前記第1のウェイト変換器及び前記第2のウェイト変換器に出力する制御部とを有し、

前記第1及び第2の発振器よりも周波数の安定度が高い外部基準信号を入力可能とし、 前記外部基準信号のウェイト調整を行う第3のウェイト変換器を備え、

前記加算器が、前記第1、第2、第3のウェイト変換器からの出力を加算して基準信号 として出力し、

前記制御部が、前記外部基準信号が入力された場合には、前記第1のウェイト変換器における第1のウェイト及び第2のウェイト変換器における第2のウェイトを 0 パーセントとするようウェイトの値を前記第1及び前記第2のウェイト変換器に出力すると共に、前記第3のウェイト変換器における第3のウェイトを100 パーセントとするようウェイトの値を前記第3のウェイト変換器に出力することを特徴とする周波数シンセサイザ。

#### 【請求項2】

制御部が、外部基準信号が入力された場合に、第3のウェイト変換器における第3のウェイトを、予め設定された移行期間内に0パーセントから100パーセントまで徐々に増加させるようウェイトの値を前記第3のウェイト変換器に出力すると共に、第1のウェイト変換器における第1のウェイトの和を、前記移行期間内に100パーセントから0パーセントまで徐々に減少させるようウェイトの値を前記第1及び第2のウェイト変換器に出力することを特徴とする請求項1記載のシンセサイザ。

#### 【請求項3】

電源投入からの時間に対応して、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイトとを記憶する第1のテーブルと、

外部基準信号の入力開始からの時間に対応して、第3のウェイト変換器における第3の ウェイトと、前記第1のウェイトと前記第2のウェイトとの和を記憶する第2のテーブル とを備え、

制御部が、外部基準信号が入力されない場合には、前記第1のテーブルに基づいて、前記第1及び第2のウェイト変換器にウェイトの値を出力し、外部基準信号が入力されると、前記第2のテーブルに基づいて第3のウェイト変換器にウェイトの値を出力すると共に、前記第2のテーブルに記憶された第1及び第2のウェイトの和を、前記第1のテーブルに記憶された前記第1のウェイトと前記第2のウェイトとの比に応じて分配して前記第1及び第2のウェイト変換器にウェイトの値を出力することを特徴とする請求項2記載の周波数シンセサイザ。

#### 【請求項4】

第1の発振器が温度補償水晶発振器であり、第2の発振器が恒温槽制御水晶発振器であることを特徴とする請求項1乃至3のいずれか記載の周波数シンセサイザ。

### 【請求項5】

基準信号を発生する基準信号発生回路を備え、前記基準信号発生回路から出力される基準信号と、電圧制御発振器からの出力信号とを比較して、前記電圧制御発振器の出力信号 が所望の周波数となるよう制御する周波数シンセサイザであって、

前記基準信号発生回路が、電源投入後短時間で周波数が安定化する特性を備えた第 1 の 発振器と、

電源投入直後は前記第1の発振器よりも周波数が不安定であるが、一定時間経過後以降は前記第1の発振器より周波数の安定度が高い特性を備えた第2の発振器と、

前記第1の発振器からの出力のウェイト調整を行う第1のウェイト変換器と、

前記第2の発振器からの出力のウェイト調整を行う第2のウェイト変換器とを備え、

前記第1及び第2の発振器よりも周波数の安定度が高い外部基準信号を入力可能とし、

前記外部基準信号の入力レベルを検出する外部基準信号レベル検出回路と、

前記外部基準信号のウェイト調整を行う第3のウェイト変換器と、

前記第1、第2、第3のウェイト変換器からの出力を加算して基準信号として出力する加算器と、

電源投入時に、前記外部基準信号レベル検出回路で検出された入力レベルが一定レベル 未満であった場合に、前記第1のウェイト変換器における第1のウェイトと前記第2のウ 10

20

30

40

20

30

50

ェイト変換器における第2のウェイトについて、電源投入直後は、前記第1のウェイトを 前記第2のウェイトより高くして前記第2のウェイトを前記第1のウェイトより低くし、 時間経過に応じて徐々に前記第1のウェイトを低く、前記第2のウェイトを高くし、前記 一定時間経過後には、前記第1のウェイトを0パーセントとし、前記第2のウェイトを1 00パーセントとするようウェイトの値を前記第1のウェイト変換器及び前記第2のウェイト変換器に出力する制御部とを備えたことを特徴とする周波数シンセサイザ。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、周波数シンセサイザに係り、特に内部で使用する基準信号を電源投入直後から使用期間全体で安定化させることができる周波数シンセサイザに関する。

#### 【背景技術】

#### [0002]

#### [ 先行技術の説明]

次世代移動体通信、地上デジタル放送等の基地局で用いられる周波数シンセサイザでは、基準信号に対する精度の向上や、起動特性の向上が望まれている。

基準信号源としては、セシウム(Cs)標準発振器、ルビジウム(Rb)標準発振器、GPS信号による周波数同期型の標準発振器、恒温槽制御水晶発振器(OCXO)、及び温度補償水晶発振器(TCXO)等があり、周波数の精度が異なっている。

そのため、それぞれの用途に応じて必要な精度を満たす基準信号源が利用されている。

#### [ 0 0 0 3 ]

OCXOは、温度を一定にする恒温槽を備えた水晶発振器であり、また、TCXOは、温度による変動を補償する温度補償データをメモリに記憶しておき、温度補正を行う水晶発振器である。

#### [0004]

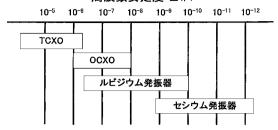

### [発振器の周波数安定度の目安:図6]

基準信号源として用いられる発振器の周波数安定度について図 6 を用いて説明する。図 6 は、基準信号源として用いられる発振器の周波数安定度を示す模式説明図である。

図 6 に示すように、一般的に、TCXOの周波数安定度( f / f ) は、 $10^{-6}$ 程度であり、OCXOは $10^{-8}$ 程度、原子の共鳴現象を利用したルビジウム発振器やセシウム発振器は更に良好な周波数安定度を備えており、それぞれ $10^{-10}$ 、 $10^{-12}$ 程度である。

しかし、ルビジウム発振器やセシウム発振器は高価であり、量産品に搭載することは現 実的ではない。

### [0005]

また、OCXOは、恒温槽内部の温度が一定温度に達するまでの数分間は周波数が大きく変動してしまう。TCXOは、安定するまでの時間が短く、立ち上がり特性は良好であるが、長期的な周波数安定度はOCXOに比べて悪い。

一方、位相雑音特性については、OCXOのほうがTCXOよりも良好であることが知られている。

### [0006]

# 40

#### [関連技術]

尚、周波数シンセサイザに関する技術としては、特開平8-56120号公報「基準発振器回路」(出願人:八重洲無線株式会社、特許文献1)、特開2004-172686 号公報「基準信号発生器」(出願人:日本電気エンジニアリング株式会社、特許文献2)がある。

#### [0007]

特許文献1には、周波数シンセサイザにおいて、TCXOとOCXOの両方を備え、それらを切り替えて基準信号として用いる基準発振器回路が記載されている。

また、特許文献 2 には、電圧制御型デジタル温度補償水晶発振器(VC-DTCXO)と、OCXOとを備え、それらを切り替えて基準信号として用いる基準信号発生器が記載

されている。

しかしながら、特許文献1及び2は、複数の発振器からの出力についてウェイトをかけて合成したり、外部からより安定度の高い基準信号を入力する構成ではない。

【先行技術文献】

【特許文献】

[ 0 0 0 8 ]

【特許文献 1 】特開平 8 - 5 6 1 2 0 号公報

【特許文献2】特開2004-172686号公報

【発明の概要】

【発明が解決しようとする課題】

[0009]

しかしながら、従来の周波数シンセサイザでは、基準信号としてOCXOを用いた場合は立ち上がり時の安定度が悪く、TCXOを用いた場合は立ち上がり時は早く安定するものの長期的な安定度が悪いため、電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られないという問題点があった。

[0010]

本発明は上記実状に鑑みてなされたもので、電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供することを目的とする。

【課題を解決するための手段】

[0011]

上記従来例の問題点を解決するための本発明は、基準信号を発生する基準信号発生回路 を備え、基準信号発生回路から出力される基準信号と、電圧制御発振器からの出力信号と を比較して、電圧制御発振器の出力信号が所望の周波数となるよう制御する周波数シンセ サイザであって、基準信号発生回路が、電源投入後短時間で周波数が安定化する特性を備 えた第1の発振器と、電源投入直後は前記第1の発振器よりも周波数が不安定であるが、 一定時間経過後以降は第1の発振器より周波数の安定度が高い特性を備えた第2の発振器 と、第1の発振器からの出力のウェイト調整を行う第1のウェイト変換器と、第2の発振 器からの出力のウェイト調整を行う第2のウェイト変換器と、第1及び第2のウェイト変 換器からの出力を加算して基準信号として出力する加算器と、第1のウェイト変換器にお ける第1のウェイトと第2のウェイト変換器における第2のウェイトについて、電源投入 直後は、第1のウェイトを第2のウェイトより高くして第2のウェイトを第1のウェイト より低くし、時間経過に応じて徐々に第1のウェイトを低く、第2のウェイトを高くし、 一定時間経過後には、第1のウェイトを0パーセントとし、第2のウェイトを100パー セントとするようウェイトの値を第1のウェイト変換器及び第2のウェイト変換器に出力 する制御部とを有し、第1及び第2の発振器よりも周波数の安定度が高い外部基準信号を 入力可能とし、外部基準信号のウェイト調整を行う第3のウェイト変換器を備え、加算器 が、第1、第2、第3のウェイト変換器からの出力を加算して基準信号として出力し、制 御部が、外部基準信号が入力された場合には、第1のウェイト変換器における第1のウェ イト及び第2のウェイト変換器における第2のウェイトを0パーセントとするようウェイ トの値を第1及び第2のウェイト変換器に出力すると共に、第3のウェイト変換器におけ る第3のウェイトを100パーセントとするようウェイトの値を第3のウェイト変換器に 出力することを特徴としている。

[0013]

また、本発明は、上記周波数シンセサイザにおいて、制御部が、外部基準信号が入力された場合に、第3のウェイト変換器における第3のウェイトを、予め設定された移行期間内に0パーセントから100パーセントまで徐々に増加させるようウェイトの値を第3のウェイト変換器に出力すると共に、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイトの和を、移行期間内に100パーセントから0パーセントまで徐々に減少させるようウェイトの値を第1及び第2のウェイト変換器に出力することを特徴としている。

10

20

30

40

#### [0014]

また、本発明は、上記周波数シンセサイザにおいて、電源投入からの時間に対応して、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイトとを記憶する第1のテーブルと、外部基準信号の入力開始からの時間に対応して、第3のウェイト変換器における第3のウェイトと、第1のウェイトと前記第2のウェイトとの和を記憶する第2のテーブルとを備え、制御部が、外部基準信号が入力されない場合には、第1のテーブルに基づいて、第1及び第2のウェイト変換器にウェイトの値を出力し、外部基準信号が入力されると、第2のテーブルに基づいて第3のウェイト変換器にウェイトの値を出力すると共に、第2のテーブルに記憶された第1及び第2のウェイトの和を、第1のテーブルに記憶された第1のウェイトと第2のウェイトとの比に応じて分配して第1及び第2のウェイト変換器にウェイトの値を出力することを特徴としている。

#### [0015]

また、本発明は、上記周波数シンセサイザにおいて、第1の発振器が温度補償水晶発振器であり、第2の発振器が恒温槽制御水晶発振器であることを特徴としている。

また、本発明は、基準信号を発生する基準信号発生回路を備え、基準信号発生回路から 出力される基準信号と、電圧制御発振器からの出力信号とを比較して、電圧制御発振器の 出力信号が所望の周波数となるよう制御する周波数シンセサイザであって、基準信号発生 回路が、電源投入後短時間で周波数が安定化する特性を備えた第1の発振器と、電源投入 直後は前記第1の発振器よりも周波数が不安定であるが、一定時間経過後以降は前記第1 の発振器より周波数の安定度が高い特性を備えた第2の発振器と、第1の発振器からの出 力のウェイト調整を行う第1のウェイト変換器と、第2の発振器からの出力のウェイト調 整を行う第2のウェイト変換器とを備え、第1及び第2の発振器よりも周波数の安定度が 高い外部基準信号を入力可能とし、外部基準信号の入力レベルを検出する外部基準信号レ ベル検出回路と、外部基準信号のウェイト調整を行う第3のウェイト変換器と、第1、第 2、第3のウェイト変換器からの出力を加算して基準信号として出力する加算器と、電源 投入時に、外部基準信号レベル検出回路で検出された入力レベルが一定レベル未満であっ た場合に、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器におけ る第2のウェイトについて、電源投入直後は、第1のウェイトを第2のウェイトより高く して第2のウェイトを第1のウェイトより低くし、時間経過に応じて徐々に第1のウェイ トを低く、第2のウェイトを高くし、一定時間経過後には、第1のウェイトを0パーセン トとし、第2のウェイトを100パーセントとするようウェイトの値を第1のウェイト変 換器及び第2のウェイト変換器に出力する制御部とを備えたことを特徴としている。

#### 【発明の効果】

### [0016]

本発明によれば、基準信号を発生する基準信号発生回路が、電源投入後短時間で周波数 が安定化する特性を備えた第1の発振器と、電源投入直後は前記第1の発振器よりも周波 数が不安定であるが、一定時間経過後以降は第1の発振器より周波数の安定度が高い特性 を備えた第2の発振器と、第1の発振器からの出力のウェイト調整を行う第1のウェイト 変換器と、第2の発振器からの出力のウェイト調整を行う第2のウェイト変換器と、第1 及び第2のウェイト変換器からの出力を加算して基準信号として出力する加算器と、第1 のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイ トについて、電源投入直後は、第1のウェイトを第2のウェイトより高くして第2のウェ イトを第1のウェイトより低くし、時間経過に応じて徐々に第1のウェイトを低く、第2 のウェイトを高くし、一定時間経過後には、第1のウェイトを0パーセントとし、第2の ウェイトを100パーセントとするようウェイトの値を第1のウェイト変換器及び第2の ウェイト変換器に出力する制御部とを有し、第1及び第2の発振器よりも周波数の安定度 が高い外部基準信号を入力可能とし、外部基準信号のウェイト調整を行う第3のウェイト 変換器を備え、加算器が、第1、第2、第3のウェイト変換器からの出力を加算して基準 信号として出力し、制御部が、外部基準信号が入力された場合には、第1のウェイト変換 器における第1のウェイト及び第2のウェイト変換器における第2のウェイトを0パーセ 10

20

30

40

ントとするようウェイトの値を第1及び第2のウェイト変換器に出力すると共に、第3のウェイト変換器における第3のウェイトを100パーセントとするようウェイトの値を第 <u>3のウェイト変換器に出力</u>する周波数シンセサイザとしているので、電源投入直後は第1の発振器の寄与分を大きくして短時間で周波数を安定化させると共に、第2の発振器の寄与分により第1の発振器を単独で用いるのに比べて立ち上がり時の位相雑音特性を向上させることができ、更に第2の発振器が安定する一定時間経過後は第2の発振器のみを利用することにより、電源投入直後から長期にわたる使用期間全体において安定した基準信号を供給することができ、更に、外部基準信号が入力された場合には、安定度の高い外部基準信号を最優先で出力することにより、高安定の基準信号を供給でき、ループを迅速に収束させることができる効果がある。

#### [0018]

また、本発明によれば、制御部が、外部基準信号が入力された場合に、第3のウェイト 変換器における第3のウェイトを、予め設定された移行期間内に0パーセントから100 パーセントまで徐々に増加させるようウェイトの値を第3のウェイト変換器に出力すると 共に、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイトの和を、移行期間内に100パーセントから0パーセントまで徐々に減少させるようウェイトの値を第1及び第2のウェイト変換器に出力する上記周波数シンセサイザとしているので、ループが安定する前に基準信号の周波数が急激に変動して周波数シンセサイザ出力が不安定になるのを防ぐことができる効果がある。

### [0019]

また、本発明によれば、電源投入からの時間に対応して、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイトと第3のウェイトを換器における第3のウェイトと、第1のウェイトと前記第2のウェイトとの和を記憶する第2のける第3のウェイトと、第1のウェイトと前記第2のウェイトとの和を記憶する第2のテーブルとを備え、制御部が、外部基準信号が入力されない場合には、第1のテーブルに基づいて、第1及び第2のウェイト変換器にウェイトの値を出力し、外部基準信号が入力されない場合には、外部基準信号が入力された第1ので、第1のテーブルに記憶された第1及び第2のウェイトの値を出力するとに応じて分配して第1及び第2のウェイトとのたが第1のウェイトと第1のウェイトと前にでで、第1ので、制御部は、管理な処理で電源投入からの時間に応じた適切なウェイトの値を第1及び第2のウェイトが登録に出力できるとともに、外部基準信号が入力された場合には、周波数が急激に変動しない適切なウェイトの値を第1、第2、第3のウェイト変換器に容易に出力できる効果がある。

### [0020]

また、本発明によれば、第1の発振器が温度補償水晶発振器であり、第2の発振器が恒温槽制御水晶発振器である上記周波数シンセサイザとしているので、電源投入直後から長期にわたって基準信号の安定度が高く、位相雑音特性が良好な周波数シンセサイザを比較的安価に実現できる効果がある。

また、本発明によれば、基準信号を発生する基準信号発生回路を備え、基準信号発生回路から出力される基準信号と、電圧制御発振器からの出力信号とを比較して、電圧制御発振器の出力信号が所望の周波数となるよう制御する周波数シンセサイザであって、基準信号発生回路が、電源投入後短時間で周波数が安定化する特性を備えた第1の発振器と、電源投入直後は前記第1の発振器よりも周波数が不安定であるが、一定時間経過後以降は前記第1の発振器より周波数の安定度が高い特性を備えた第2の発振器と、第1の発振器からの出力のウェイト調整を行う第1のウェイト変換器と、第2の発振器からの出力のウェイト調整を行う第2のウェイト変換器とを備え、第1及び第2の発振器よりも周波数の安定度が高い外部基準信号を入力可能とし、外部基準信号の入力レベルを検出する外部基準信号レベル検出回路と、外部基準信号のウェイト調整を行う第3のウェイト変換器と、第1、第2、第3のウェイト変換器からの出力を加算して基準信号として出力する加算器と

10

20

30

40

、電源投入時に、外部基準信号レベル検出回路で検出された入力レベルが一定レベル未満であった場合に、第1のウェイト変換器における第1のウェイトと第2のウェイト変換器における第2のウェイトについて、電源投入直後は、第1のウェイトを第2のウェイトより高くして第2のウェイトを第1のウェイトより低くし、時間経過に応じて徐々に第1のウェイトを低く、第2のウェイトを高くし、一定時間経過後には、第1のウェイトを0パーセントとし、第2のウェイトを100パーセントとするようウェイトの値を第1のウェイト変換器及び第2のウェイト変換器に出力する制御部とを備えた周波数シンセサイザとしているので、外部基準信号の入力レベルが低い場合に、電源投入直後は第1の発振器の寄与分を大きくして短時間で周波数を安定化させると共に、第2の発振器の寄与分により第1の発振器を単独で用いるのに比べて立ち上がり時の位相雑音特性を向上させることができ、更に第2の発振器が安定する一定時間経過後は第2の発振器のみを利用することにより、電源投入直後から長期にわたる使用期間全体において安定した基準信号を供給することができる効果がある。

【図面の簡単な説明】

[0021]

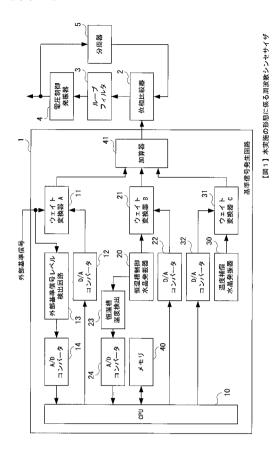

- 【図1】本実施の形態に係る周波数シンセサイザの構成ブロック図である。

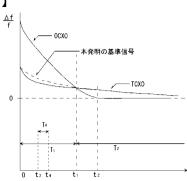

- 【図2】OCXO,TCXOの周波数安定度の特性を示す模式説明図である。

- 【図3】基本ウェイトテーブルの模式説明図である。

- 【図4】外部基準信号ウェイトテーブルの模式説明図である。

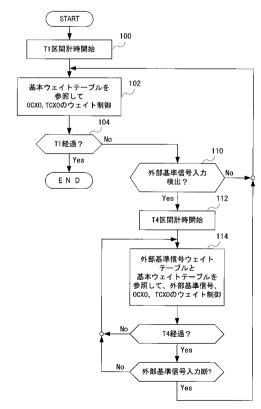

- 【図5】CPU10における電源投入時のウェイト制御の処理を示すフローチャートである。

- 【図6】基準信号源として用いられる発振器の周波数安定度を示す模式説明図である。

【発明を実施するための形態】

[0022]

[実施の形態の概要]

本発明の実施の形態について図面を参照しながら説明する。

本発明の実施の形態に係る周波数シンセサイザは、内部にOCXOとTCXOと、それぞれに対応して出力のウェイトを調整するウェイト変換器と、各ウェイト変換器からの出力を加算して基準信号としてPLL回路に出力する加算器と、各ウェイト変換器を制御する制御部とを備え、制御部が、電源投入時にはTCXOのウェイトを高くし、徐々にOCXOのウェイトを上げ、OCXOの恒温槽が一定温度になってからはOCXOのみとするよう各ウェイト変換器を制御するものであり、電源投入時の基準信号の周波数を迅速に安定させると共に、長期的にも安定させることができるものである。

[0023]

また、本発明の実施の形態に係る周波数シンセサイザは、上記構成に加えて、より安定度の高い発振器からの外部基準信号を入力可能とし、外部基準信号の出力ウェイトを調整するウェイト変換器を備え、外部基準信号が入力された場合には、制御部が、外部基準信号のウェイトを高くして優先的に出力するものであり、立ち上がり時に外部基準信号を入力すれば、精度の高い基準信号を出力でき、PLL回路を迅速にロックさせることができるものである。

[0024]

「実施の形態に係る発振器:図1]

本実施の形態に係る周波数シンセサイザの構成について図1を用いて説明する。図1は、本実施の形態に係る周波数シンセサイザ(本周波数シンセサイザ)の構成ブロック図である

図1に示すように、本周波数シンセサイザは、基本的に、基準信号発生回路1と、位相比較器2と、ループフィルタ3と、電圧制御発振器4と、分周器5とから構成されている

そして、位相比較器 2 が、基準信号発生回路 1 から出力される基準信号と分周器 5 からの分周されたシンセサイザ出力とを比較して位相差を検出して位相差信号を出力し、ルー

10

20

30

40

プフィルタ3が位相差信号を平滑化して制御電圧を電圧制御発振器に出力し、電圧制御発振器から所定の周波数を出力させるものである。

#### [0025]

「基準信号発生回路1:図1]

次に、本周波数シンセサイザの特徴部分である基準信号発生回路1について図1を用いて説明する。

基準信号発生回路1は、内部に恒温槽制御水晶発振器(OCXO)20と、温度補償水晶発振器(TCXO)30とを備え、更に外部から入力される外部基準信号をユーザの操作で入力可能とし、OCXO20、TCXO30、外部基準信号のウェイト比率を調整して加算し、基準信号として出力するものである。OCXO20は請求項に記載した第2の発振器に相当し、TCXO30は第1の発振器に相当している。

[0026]

尚、内部に設けられる第1、第2の発振器は、TCXOやOCXOに限るものではなく、第1の発振器は電源投入後に迅速に周波数偏差( f/f)が安定化する特性を備え、第2の発振器は第1の発振器より安定化に時間がかかるが、電源投入後一定時間経過後は周波数安定度が第1の発振器よりも高い特性を備えている組み合わせであればよい。

[0027]

ここで、外部基準信号は、例えばルビジウム発振器やセシウム発振器からの信号であり、内部に設けられているOCXO20,TCXO30よりも高安定の発振器から出力される信号である。

また、内部のOCXO20,TCXO30よりも高安定であれば、外部基準信号の信号源は水晶発振器であってもよい。

[0028]

基準信号発生回路1の構成について具体的に説明する。

図1に示すように、基準信号発生回路1は、CPU10と、恒温槽制御水晶発振器(OCXO)20と、温度補償水晶発振器(TCXO)30と、ウェイト変換器A(11)と、ウェイト変換器B(21)と、ウェイト変換器C(31)と、D/Aコンバータ12,22,32と、外部基準信号レベル検出回路13と、A/Dコンバータ14,24と、恒温槽温度検出部23と、メモリ40と、加算器41とを備えている。

[0029]

各構成部分について説明する。

ウェイト変換器 A ( 1 1 ) は、外部から入力される外部基準信号のウェイトを C P U 1 0 からのウェイト値に基づいて変換して加算器 4 1 に出力する。

ウェイト変換器 B (21)は、O C X O 20の出力のウェイトを C P U 10 からのウェイト値に基づいて変換して加算器 41に出力する。

ウェイト変換器 C (3 1) は、 T C X O 3 0 の出力のウェイトを C P U 1 0 からのウェイト値に基づいて変換して加算器 4 1 に出力する。

ウェイト変換器 A , B , C は、それぞれ、請求項に記載した第 3 のウェイト変換器、第 2 のウェイト変換器、第 1 のウェイト変換器に相当し、ウェイト変換器 A , B , C におけるウェイト値は、それぞれ、請求項の、第 3 、第 2 、第 1 のウェイトに相当する。

加算器 4 1 は、ウェイト変換器 A , B , C からの出力を加算して基準信号として位相比較器 2 に出力する。

[0030]

CPU10は、請求項に記載した制御部に相当し、ウェイト変換器A,B,Cでのウェイトを制御するウェイト値を出力する。これにより、本周波数シンセサイザでは外部基準信号、OCXO20、TCXO30の出力を適切に重み付けして加算することにより、周波数安定度が高く、位相雑音特性の優れた基準信号を出力するものである。CPU10の処理については後で具体的に説明する。

[0031]

D / A コンバータ 1 2 , 2 2 , 3 2 は、C P U 1 0 からのウェイト値をアナログ信号に

20

10

30

40

変換して、それぞれ、ウェイト変換器A,B,Cに出力する。

外部基準信号レベル検出回路 1 3 は、外部基準信号の入力レベル(アナログ)を検出する。尚、外部基準信号は、システムで要求される周波数安定度により、入力する場合としない場合があり、入力のオン / オフはスイッチ等によりユーザが手動で切り替えるようにしている。

A / D コンバータ 1 4 は、アナログ信号の入力レベルをデジタルの入力レベルに変換する。

そして、CPU10は、A/Dコンバータ14からの外部基準信号レベルが一定レベル 以上となった場合に、外部基準信号が入力されたと判断する。

#### [0032]

恒温槽温度検出部23は、OCXO20の恒温槽の温度を検出し、A/Dコンバータ24にアナログ信号の温度信号を出力する。

A / Dコンバータ 2 4 は、アナログ信号の温度信号をデジタルの温度データに変換する

メモリ40は、CPU10におけるウェイト制御の基準となる基本ウェイトテーブルと外部基準信号ウェイトテーブルの2種類のウェイトテーブルを記憶している。ウェイトテーブルについては後で説明する。

本周波数シンセサイザでは、予めシミュレーション又は実験により求められた電源投入時からの時間とOCXO20及びTCXO30の周波数安定度の関係に基づいて基本ウェイトテーブルを生成して、メモリ40に記憶しておく。

また、恒温槽温度検出部23を利用したウェイト制御の応用例については後述する。

#### [0033]

[OCXO, TCXOの安定度:図2]

次に、本周波数シンセサイザに用いられるOCXO,TCXOの周波数安定度の特性について図2を用いて説明する。図2は、OCXO,TCXOの周波数安定度の特性を示す模式説明図である。

図 2 に示すように、電源投入時の時刻を 0 とすると、 O C X O は、電源投入後、しばらくの間は周波数安定度 ( f / f ) は良好ではなく、時刻 t 2 で恒温槽の温度が十分上昇して一定温度になると周波数安定度は良好となる。尚、本模式図の例では、目標とする周波数安定度 ( f / f ) を 0 として、全てプラス側で表している ( O C X O 、 T C X O によっては実際にはマイナス側から始まる特性を持つものもある )。 T C X O は、電源投入後、短い時間で安定するものの、時刻 t 1 以降は O C X O よりも不安定となってしまう。

#### [0034]

そこで、本周波数シンセサイザでは、電源投入直後にはTCXOのウェイトを100%として、立ち上がり時に迅速に基準信号の周波数を安定させ、徐々にTCXOのウェイトを減らしてOCXOのウェイトを増加させ、OCXOの安定度がTCXOを上回る頃にはOCXOのウェイトを100%とするよう、ウェイト変換器B,Cを制御する。

#### [0035]

つまり、電源投入後、時刻 t 1までの T 1区間においては、 T C X O のウェイトを 1 0 0 % から徐々に減らし、 O C X O のウェイトを 0 パーセントから徐々に増やして 1 0 0 パーセントとし、 T 2区間 (時刻 t 1以降)では、 そのまま O C X O のウェイトを 1 0 0 % とする。 その結果、 本実施の形態の周波数シンセサイザの基準信号は点線で示したようになる

本周波数シンセサイザでは、後述する基本ウェイトテーブルに基づいて、電源投入後から T1が経過するまでは、時間に応じたウェイト制御を行う。

### [0036]

このように、T1区間において、ウェイト調整を行いながらTCXOとOCXOを併用することにより、OCXOが十分安定するまでの間はTCXOの寄与分を大きくして周波数安定度を向上させつつ、OCXOの寄与分によってTCXO単体とした場合に比べて位相雑音特性を向上させることができるものである。

10

20

30

40

#### [0037]

また、本周波数シンセサイザでは、T1区間において周波数安定度があまりよくない場合や、ループを早く収束させたい場合に、ユーザからの指示(手動による外部基準信号源接続)で外部基準信号を入力できるようにしている。

外部基準信号が入力された場合には、外部基準信号のウェイトを100%とし、OCX O,TCXOのウェイトはいずれも0%とする。

#### [0038]

但し、外部基準信号入力による急激な基準周波数の変動を防ぐために、外部基準信号の入力開始から一定の微小時間が経過するまでは移行期間として、外部基準信号のウェイトを徐々に増加させるよう、ウェイト変換器 A , B , C を制御する。ここでは、微小時間をT4としている。T4区間のウェイト制御については後述する外部基準信号ウェイトテーブルに基づいて行われる。

#### [0039]

図2の例では、時刻t3で外部基準信号が入力開始されると、時刻t4までのT4区間で外部基準信号のウェイトを0%から100%となるよう徐々に変化させる。T4区間終了後は、外部基準信号のウェイトを100%とする。

そして、ユーザからの指示(手動による外部基準信号源接続切断)で外部信号の入力が無くなると、CPU10は、基本ウェイトテーブルを参照して、電源投入時からの時間に応じたウェイト制御を行うようになっている。

#### [0040]

「外部基準信号が入力されない場合の動作:図1,21

CPU10は、電源投入後、計時を開始し、それと共に定期的にA/Dコンバータ14からの外部基準信号レベルに基づいて、外部基準信号の入力の有無を判断する。そして、外部基準信号が入力されていなければ、基本ウェイトテーブルを参照しながら、定期的にD/Aコンバータ22にOCXOのウェイト値を出力し、D/Aコンバータ32にTCXOのウェイト値を出力する。

各ウェイト値は、D/A変換されて、ウェイト変換器Bとウェイト変換器Cにそれぞれ入力され、OCXO20及びTCXO30の出力がウェイト変換されて、基本ウェイトテーブルで設定されたウェイト比で加算器41に入力され、加算されて基準信号として出力される。

#### [0041]

[外部基準信号が入力された場合の動作:図1,2]

CPU10が、A/Dコンバータ14からの外部基準信号レベルに基づいて外部基準信号の入力を認識した場合には、外部基準信号のウェイトを徐々に増加させ、移行期間である T4区間終了後に、OCXO及びTCXOのウェイトをいずれも0%とし、外部基準信号のウェイトを100%とするよう、D/Aコンバータ12,22,32にウェイト値を出力する。

外部基準信号は安定度が最も高いので、外部基準信号が入力された場合にはこれを最優先して、迅速に基準周波数及びシンセサイザ出力を安定させるものである。 T4区間のウェイト制御については後述する。

### [ 0 0 4 2 ]

尚、外部基準信号の入力 / 切断は、ユーザの操作によって行われ、外部基準信号入力時にはまだ周波数が不安定であるため、移行期間として T 4 区間で特別なウェイト制御を行うが、外部基準信号の入力でループが収束した後は、外部基準信号を切断して O C X O 2 0 と T C X O 3 0 の組み合わせ(又は O C X O 2 0 のみ)に移行しても、周波数が大きく変動してしまうことはない。

#### [0043]

「基本ウェイトテーブル:図31

次に、メモリ40に記憶されているウェイトテーブルの内、基本ウェイトテーブルについて図3を用いて説明する。図3は、基本ウェイトテーブルの模式説明図である。尚、基

10

20

30

40

本ウェイトテーブルは、請求項に記載した第1のテーブルに相当している。

基本ウェイトテーブルは、ウェイト制御の基準となるものであり、CPU10が、OC XO20のウェイト調整を行うウェイト変換器B(21)と、TCXO30のウェイト調 整を行うウェイト変換器C(31)のウェイト値を記憶している。また、基本ウェイトテ ーブルの各数値は、OCXO20が標準的な温度遷移で温度上昇した場合に合わせて決め られている。OCXOが安定するまでの時間が長い場合には、T1は大きくなる。

#### [0044]

図3に示すように、基本ウェイトテーブルでは、電源投入からの時間と、OCXO20 (ウェイト変換器B)及びTCXO30(ウェイト変換器C)のそれぞれのウェイト値が 記憶されている。

電源投入時には、上述したようにOCXOが0%、TCXOが100%であり、T1ではOCXOが100%、TCXOが0%である。その間は、徐々に変化するように設定されている。

経過時間に応じてうウェイト制御を行うのは、基本的には電源投入後 T 1までであり、 T 1以降は O C X O が安定しているため、 T 1経過時のウェイトのまま O C X O を 1 0 0 % とする。

#### [0045]

「外部基準信号ウェイトテーブル:図41

次に、メモリ40に記憶されている外部基準信号ウェイトテーブルについて図4を用いて説明する。図4は、外部基準信号ウェイトテーブルの模式説明図である。尚、外部基準信号ウェイトテーブルは、請求項に記載した第2のテーブルに相当している。

外部基準信号ウェイトテーブルは、外部基準信号が入力された場合の移行期間であるT4区間におけるウェイト制御の基準となるテーブルである。

尚、移行期間T4は、外部基準信号の周波数安定度と、TCXO及びOCXOの周波数安定度との関係に加えて、シンセサイザとして周波数同期を行う時間(PLLループが収束する時間)により決定される。

図4に示すように、外部基準信号ウェイトテーブルは、外部基準信号の入力検出時から時間 T4が経過するまでの外部基準信号(ウェイト変換器 A)のウェイトと、OCXO及び T C X O の合計のウェイトをそれぞれ記憶しているものである。

### [0046]

図4の例では、外部基準信号の入力検出時(時間0)は外部基準信号のウェイトを0%、OCXO+TCXOのウェイトを100%とし、時間T4まで時刻に比例してウェイトを変化させ、徐々に外部基準信号の割合を上げていって、T4以降では外部基準信号のウェイトを10%としている。

### [0047]

これにより、外部基準信号を入力した場合に、徐々に外部基準信号に切り替えることができ、急激な基準周波数の変動が発生するのを防ぐことができ、また、外部基準信号に移行した後は、ユーザによって切断されるまで外部基準信号を優先して基準信号として出力し続け、迅速にシンセサイザ出力を安定化させることができるものである。

#### [0048]

T4区間のウェイト制御について具体的に説明する。

例えば、外部基準信号の入力検出からT4/2が経過した時点では、外部基準信号とOCXO+TCXOのウェイトは共に50%となっている。つまり、この時点では、外部基準信号のウェイトは50%であり、OCXOとTCXOのウェイトは合計で50%である。OCXOとTCXOのウェイトは、当該時点の電源投入時からの経過時間に基づいて、図3に示した基本ウェイトテーブルで設定されたウェイト比で分配される。

つまり、外部基準信号が入力された後、T4までのOCXOとTCXOのウェイトは、 どちらも、外部基準信号ウェイトテーブルのウェイト値×基本ウェイトテーブルのウェイト値となる。

### [0049]

10

20

30

例えば、外部基準信号の入力開始が早く、外部基準信号の入力検出から T4 / 2 が経過した時点が、電源投入後 T1 / 4 であった場合には、

TCXOのウェイトは、0.5×0.875×100=43.75% となる。

#### [0050]

また、外部基準信号の入力開始がもっと遅く、外部基準信号の入力検出から T4/2 が 経過した時点が、電源投入後 T1/2 であった場合には、

OCXOのウェイトは、0.5×0.25×100=12.5% となり、

TCXOのウェイトは、0.5×0.75×100=37.5% となる。

いずれの場合も、OCXOとTCXOのウェイトの合計は50%である。

### [0051]

そして、外部基準信号の入力が無くなると、CPU10は、再び図3の基本ウェイトテーブルを参照して、その時点(電源投入時からの時間)に応じたウェイト値でOCXOとTCXOのウェイトを制御する。

#### [0052]

「電源投入時のウェイト制御の処理:図5]

次に、СРU 1 0 における電源投入時のウェイト制御の処理について図 5 を用いて説明する。図 5 は、СРU 1 0 における電源投入時のウェイト制御の処理を示すフローチャートである。

図 5 に示すように、CPU10は、電源が投入されるとT1の計時を開始し(100) 、基本ウェイトテーブルを参照して、OCXO20,TCXO30のウェイト制御を行う (102)。

#### [0053]

そして、CPU10は、T1が経過したか否かを判断し、T1が経過した場合には(Yesの場合)、その時点のウェイト(OCXOが100%、TCXOが0%)を保持し、処理を終了する。

#### [0054]

また、処理104でT1が経過していなかった場合には(Noの場合)、CPU10は、A/Dコンバータ14からの外部基準信号レベルに基づいて外部基準信号の入力が検出されたか否かを判断し(110)、外部基準信号の入力が検出されていなければ(Noの場合)、処理102に移行して基本ウェイトテーブルに基づく制御を行う。

### [0055]

また、処理110で外部基準信号の入力が検出された場合には(Yesの場合)、CPU 10はT4区間の計時を開始し(112)、外部基準信号ウェイトテーブルと基本ウェイトテーブルの両方を参照して、外部基準信号とOCXOとTCXOのウェイト制御を行う(114)。

### [0056]

そして、CPU10は、T4が経過したか否かを判断し(116)、経過していない場合には(Noの場合)、処理114に移行して徐々に外部基準信号のウェイトを増加させる制御を行う。

また、処理116でT4が経過した場合には(Yesの場合)、外部基準信号のウェイトは 100%、OCXOとTCXOは0%となっており、CPU10は、外部基準信号の入力 が切断されたか否かを判断し(118)、切断されていない場合(Noの場合)には、処理 114に移行する。つまり、T4区間が終了した後は、外部基準信号の入力が継続してい る限り、外部基準信号のウェイトは100%で保持する。

処理118で、外部基準信号の入力が切断されている場合には(Yesの場合)、CPU 10は、処理102に移行して、基本ウェイトテーブルに基づく制御を行う。

このようにして、CPU10における電源投入時のウェイト制御の処理が行われるものである。

### [0057]

10

20

30

40

#### 「ウェイト制御の応用例 1

次に、ウェイト制御の応用例について説明する。

応用例は、CPU10が、恒温槽温度検出部23からの温度情報に基づいて、基本ウェイトテーブルの値を微調整してウェイト制御するものである。

応用例では、予め実験的に求めた電源投入からの時間と恒温槽温度との標準的な関係(標準的な温度遷移)をメモリ40に記憶しておき、CPU10は、電源投入後、恒温槽温度検出部23からの温度情報を標準的な温度遷移と比較して、OCXO20の恒温槽の温度が標準より早く上昇している場合や、標準より遅い場合に、基本ウェイトテーブルのウェイト値を調整して出力するようにしている。

#### [0058]

例えば、図3の基本ウェイトテーブルでは、電源投入からT2/2が経過した時点のウェイトは、OCXOのウェイトが25%、TCXOのウェイトが75%となっており、CPU10は、恒温槽温度検出部23で検出された温度と、標準的な温度遷移における当該時点の温度(標準温度)との差が一定範囲であれば基本ウェイトテーブルの値をそのまま出力する。

#### [0059]

また、運用時の温度上昇が標準の温度遷移に比べて早く、恒温槽温度検出部23で検出された温度が標準温度より高かった場合には、例えば、OCXOのウェイトを30%とし、TCXOのウェイトを70%とする。

逆に、検出された温度が標準温度より低かった場合には、例えば、OCXOのウェイトを20%とし、TCXOのウェイトを80%とすることが考えられる。

#### [0060]

ウェイト値の調整は、例えば、CPU10において恒温槽の温度と標準温度との差に応じた係数を算出し、当該係数を基本ウェイトテーブルのウェイト値に乗算してOCXOのウェイトを求めればよい。

このようにすれば、恒温槽の温度状態に応じてOCXOのウェイトを微調整することができ、OCXOが早く安定した場合には早めにOCXOに移行させることができ、また、OCXOの恒温槽の温度上昇が遅くなってしまった場合には、OCXOへの移行を遅らせて、安定した基準信号を出力できるものである。

### [0061]

#### [実施の形態の効果]

本発明の実施の形態に係る周波数シンセサイザによれば、基準信号発生回路1に、OC X O 2 0 と、TC X O 3 0 と、それぞれの出力に対してウェイト調整を行うウェイト変換器 2 1 ,3 1 と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器 4 1 を備え、CPU10が、電源投入時にはTC X O 3 0 のウェイトを100%、OC X O 2 0 のウェイトを 0 %とし、徐々にOC X O 2 0 のウェイトを上げて、予め設定された一定時間後にTC X O 3 0 のウェイトを 0 %、OC X O 2 0 のウェイトを 1 0 0 %とするようにウェイト変換器 B ,Cを制御する周波数シンセサイザとしているので、OC X O 2 0 の恒温槽が十分加熱されるまでの間はTC X O 3 0 とOC X O 2 0 を併用して基準信号を生成でき、電源投入時に早く周波数を安定させることができ、また、恒温槽加熱後はOC X O 2 0 のみとして長期にわたって良好な周波数安定度を保つことができる効果がある

#### [0062]

また、本周波数シンセサイザによれば、上記構成に加えてより安定度の高い外部基準信号を入力可能とし、外部基準信号のウェイトを調整するウェイト変換器 A (11)と、外部基準信号の入力レベルを検出する外部基準信号レベル検出回路 13とを備え、CPU10が、外部基準信号が入力された場合には、外部基準信号のウェイトを100%とし、OCXO20とTCXO30のウェイトを0%とするようウェイト変換器 A,B,Cを制御する周波数シンセサイザとしているので、高精度の外部基準信号が入力された場合には、外部基準信号を優先して基準信号として出力でき、立ち上がり時に迅速に基準信号を安定

10

20

30

40

化させて、PLLのループを迅速に収束させることができる効果がある。

#### [0063]

また、本周波数シンセサイザによれば、CPU10が、外部基準信号の入力があった場合に、直ちに外部基準信号に切り替えるのではなく、移行期間T4の間に徐々に外部基準信号のウェイトを上げていき、T4の終わりには外部基準信号のウェイトが100%になるよう制御しているので、周波数の急激な変動を防ぐことができる効果がある。

#### [0064]

更に、CPU10が、TCXO30のウェイトが0%になった場合には、TCXO30 及びウェイト変換器C(31)への電源供給を停止するよう電源回路を制御するようにしてもよく、これにより消費電力を大幅に低減できるものである。

#### [0065]

また、本周波数シンセサイザによれば、CPU10が、恒温槽温度検出部23からの温度情報を、記憶されている標準の温度と比較して、差が一定範囲より大きい場合には、標準より温度が高ければOCXOのウェイト値を上げ、低ければOCXOのウェイトを下げるよう、基本ウェイトテーブルの値を調整して出力するようにしているので、恒温槽の温度状態に応じてOCXOのウェイトを微調整することができ、一層安定した基準信号を出力できるものである。

### 【産業上の利用可能性】

### [0066]

本発明は、基準信号を、電源投入直後から使用期間全体で安定させることができる周波数シンセサイザに適している。

#### 【符号の説明】

#### [0067]

1 ... 基準信号発生回路、 2 ... 位相比較器、 3 ... ループフィルタ、 4 ... 電圧制御発振器、 5 ... 分周器、 1 0 ... C P U、 2 0 ... 恒温槽制御水晶発振器(O C X O )、 3 0 ... 温度補償水晶発振器(T C X O )、 1 1 , 2 1 , 3 1 ... ウェイト変換器 A , B , C 、 1 2 , 2 2 , 3 2 ... D / A コンバータ、 1 3 ... 外部基準信号レベル検出回路、 2 3 ... 恒温槽温度検出部、 1 4 , 2 4 ... A / D コンバータ、 4 0 ... メモリ、 4 1 ... 加算器

10

### 【図1】

### 【図2】

【図2】0CX0、TCX0の安定度

# 【図3】

| 時間         | ocxo  | тсхо    |

|------------|-------|---------|

| 0          | 0 (%) | 100 (%) |

| •          | :     | :       |

| <u>T</u> 1 | 12.5  | 87.5    |

| :          | :     | :       |

| <u>T1</u>  | 25    | 75      |

| :          | :     | :       |

| Tı ~       | 100   | 0       |

【図3】基本ウェイトテーブル

### 【図4】

| 時間                      | 外部    | 0XCO+TCXO |  |

|-------------------------|-------|-----------|--|

| 0                       | 0 (%) | 100 (%)   |  |

|                         |       | ·         |  |

|                         |       |           |  |

|                         |       |           |  |

| <u>T<sub>4</sub></u> 50 |       | 50        |  |

|                         |       |           |  |

|                         |       |           |  |

|                         |       | •         |  |

| T4 ~                    | 100   | 0         |  |

【図4】外部基準信号ウェイトテーブル

### 【図5】

【図5】ウェイト制御のフロー

# 【図6】

### 周波数安定度 Δf/f

【図 6 】各種発振器の周波数安定度の目安

### フロントページの続き

```

(56)参考文献 特開平08-056120(JP,A)

特開2005-043289(JP,A)

特開平08-317564(JP,A)

特開昭63-036675(JP,A)

特開2002-135235(JP,A)

実開昭50-107040(JP,U)

特開昭59-194519 (JP,A)

特開平06-260932(JP,A)

特開平02-214222(JP,A)

特開昭53-146560(JP,A)

(58)調査した分野(Int.CI., DB名)

H03L 1/02,3/00,7/00-7/23,

H03B 5/00-5/28,

H04B 1/74,

H04L 1/22,

H04N 5/265,

G06F 1/04,303

```