# **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

6 April 1995 (06.04.95)

### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 6: (11) International Publication Number: H01R 43/00, H01L 23/14 **A1** (43) International Publication Date:

WO 95/09459

(21) International Application Number: PCT/US94/10415

(81) Designated States: DE, GB, JP, KR, European patent (AT, BE,

(22) International Filing Date: 14 September 1994 (14.09.94) CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT,

(30) Priority Data:

129,753

30 September 1993 (30.09.93) US **Published**

With international search report.

(71) Applicant: ATMEL CORPORATION [US/US]; 2125 O'Nel Drive, San Jose, CA 95131 (US).

(72) Inventor: LAM, Ken; 720 San Gabriel Place, Colorado Springs, CO 80906 (US).

(74) Agent: SCHNECK, Thomas; Schneck & McHugh, P.O. Box 2-E, San Jose, CA 95109-0005 (US).

(54) Title: TAB TESTING OF AREA ARRAY INTERCONNECTED CHIPS

### (57) Abstract

A plurality of electrically conductive leads (45) are formed on an electrically insulative substrate (35) by tape automated bonding methods. The leads (35) extend from peripherally disposed test terminals (60) to centrally disposed interconnect pads (55) and are aligned therebetween with bond pads (30) that are disposed near a perimeter (32) of a face (17) of a chip (15). The leads (35) are connected to the bond pads (30) and are encapsulated with a cement, and the substrate is adhered to the chip face. The leads (35) are then severed closely peripheral to the bond pads (30), disconnecting the test terminals (60) from the chip (15). The chips that pass the testing are connected via the interconnect pads (55), which may be arranged in a pad grid array, to matching terminals (90) in a package (95).

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| ΑT | Austria                  | GB | United Kingdom               | MR  | Mauritania               |

|----|--------------------------|----|------------------------------|-----|--------------------------|

| ΑÜ | Australia                | GE | Georgia                      | MW  | Malawi                   |

| BB | Barbados                 | GN | Guinea                       | NE  | Niger                    |

| BE | Belgium                  | GR | Greece                       | NL  | Netherlands              |

| BF | Burkina Faso             | HU | Hungary                      | NO  | Norway                   |

| BG | Bulgaria                 | Œ  | Ireland                      | NZ  | New Zealand              |

| BJ | Benin                    | rt | Italy                        | PL  | Poland                   |

| BR | Brazil                   | JP | Japan                        | PT  | Portugal                 |

| BY | Belarus                  | KE | Kenya                        | RO  | Romania                  |

| CA | Canada                   | KG | Kyrgystan                    | RU  | Russian Federation       |

| CF | Central African Republic | KP | Democratic People's Republic | SD  | Sudan                    |

| CG | Congo                    |    | of Korea                     | SE  | Sweden                   |

| CH | Switzerland              | KR | Republic of Korea            | SI  | Slovenia                 |

| CI | Côte d'Ivoire            | KZ | Kazakhstan                   | SK  | Slovakia                 |

| CM | Cameroon                 | LI | Liechtenstein                | SN  | Senegal                  |

| CN | China                    | LK | Sri Lanka                    | TD  | Chad                     |

| CS | Czechoslovakia           | LU | Luxembourg                   | TG  | Togo                     |

| CZ | Czech Republic           | LV | Latvia                       | TJ  | Tajikistan               |

| DE | Germany                  | MC | Monaco                       | TT  | Trinidad and Tobago      |

| DK | Denmark                  | MD | Republic of Moldova          | UA  | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | US  | United States of America |

| FI | Finland                  | ML | Mali                         | UZ  | Uzbekistan               |

| FR | France                   | MN | Mongolia                     | VN  | Viet Nam                 |

| GA | Gabon                    |    | · ·                          | *** | , 100 1 10011            |

### Description

# TAB Testing of Area Array Interconnected Chips

5

10

30

35

### Technical Field

The present invention relates generally to packaging integrated circuit chips. More particularly, it relates to a method and apparatus for connecting and testing integrated circuit chips with external circuitry.

### Background Art

The need for lightweight, thin, low cost packaging materials for integrated circuit (IC) applications such as consumer products has led to development and use 15 of a method of connecting IC chips termed tape automated bonding (TAB). TAB involves forming electrical leads for IC chips on thin, flexible tape which is similar in appearance to 35 mm film. The tape is electrically insu-20 lative, and the leads are typically formed from a thin layer of metal which has been deposited on the tape and photolithographically etched. The precisely formed leads are aligned with and bonded to signal terminals from the integrated circuit located near a perimeter of a surface 25 of the chip. The signal terminals of the chip are often termed "bond pads." The leads extend outwardly from the chip for connection with an external element, often called a "package" or "assembly."

A problem with TAB is that the leads may be only a few thousandths of an inch in cross-section and are cantilevered from the tape at the point where the leads are to be bonded to the terminals of the chip. These tiny, cantilevered electrical leads are thus the only mechanical support between the chip and the package at the edge of the chip, an area prone to deformational stress from any change in position of the chip relative to the package. As a result, the leads may break at this point, causing the chip and package to fail.

PCT/US94/10415

-2-

Another problem with TAB is that the leads fan outwardly from the chip for bonding to the package, and thus require a larger package area than that dictated by the size of the chip. It is often desirable, and appears 5 to be a long term trend in electronics, to condense information capabilities in smaller packages, and the larger area or "footprint" required by traditional TAB packaging stands in the way of this trend.

Another type of electrical and mechanical connection of an IC chip to a package is called "flip-chip" 10 or "controlled collapse chip connection" (C4), and is described in U.S. Pat. Nos. 3,401,126 to Lewis F. Miller et al. and 3,429,040 to Lewis F. Miller. C4 involves forming solder balls on the surface of the chip that connect signal terminals of the chip with corresponding 15 connections on the package, the solder balls providing both electrical contacts and mechanical support between the chip and the package.

One difficulty with the flip chip type intercon-20 nection is that the thermal coefficient of expansion is usually significantly different for the chip, often formed of silicon, and the package, typically made of ceramic and materials conventionally used in forming printed circuit boards. As a result, changes in temperature of the chip or substrate, or both, lead to stresses 25 between the solder balls and the chip or substrate. may cause the solder ball connections to break, or may cause stresses within the chip that create chip failures.

Another difficulty with the flip-chip interconnections is that they do not allow testing prior to committing the chip to the package, other than wafer probe testing which does not allow testing with all the signal terminals connected or "burn-in" testing such as can be performed with TAB. This difficulty is underscored by the realization that it is often more appropriate to speak of committing the package to the chip rather than the chip to the package, since discarding even a multichip package may be more economical than trying to

30

determine which chip of the module failed and to then replace that chip.

Yet another difficulty with this technology is that many IC chips are designed and built with bond pads formed in a row near the perimeter of the chip surface. Since a chip may have well over 500 such bond pads, the organizing of these terminals into a row requires that the terminals and the separation between the terminals be too small to reliably form effective solder bumps for connection to a package.

10

15

20

25

30

35

One approach to overcoming these difficulties is described in U.S. Pat. No. 4,472,876 to Nelson, which teaches a flexible area bonding tape containing electrical paths connecting a chip to a package. The tape and conductive paths absorb stresses caused by thermal expansion and also conduct heat from the chip to the package, thereby reducing expansion stress. The approach of Nelson, however, requires an interconnection package having a larger footprint than that of the chip. Another approach is described in U.S. Pat. Nos. 5,148,265 and 5,148,266, both issued to Khandros et al., which also describe an insulative tape having conductive leads connecting terminals on a chip with those on a substrate. The interconnection with the substrate does not fan out, instead being located in an array having an area equal to or less than that of the chip surface, but the chip is tested with wafer probes. This wafer probe testing does not allow testing of all the functions of a chip, is more expensive than TAB testing, and has additional disadvantages caused by a reduction of thermal conductivity created to accommodate the wafer probe testing.

It is an object of the present invention to provide improved testing of a chip prior to interconnection to a package, while that interconnection occupies a surface no larger than that of the chip.

Summary of the Invention

10

15

20

25

35

The present invention provides a means for connecting an integrated circuit chip with external elements that offers many of the advantages of both tape automated bonding and area array interconnections.

An array of electrically conductive leads is formed on an electrically insulative substrate, the leads extending inwardly to a chip from test terminals peripheral to the chip so as to align with bond pads disposed in a row near a perimeter of a face of the chip, like a traditional TAB lead frame. The leads continue inwardly from the bond pads, however, to conclude in an array of interconnect pads disposed on an area of the substrate above the face of the chip.

The leads are bonded to the bond pads with which they are aligned, and then tested with the test terminals of the TAB lead frame. This testing prior to interconnection with external elements allows a greatly increased yield of functional chips to be connected to a package, which in turn saves costs and increases the quality of the product. Those chips which pass the test then have the portion of the leads connecting the bond pads to the test terminals excised close to the bond pads. The interconnect pads are then connected to a matching array of package terminals which, like the interconnect pads, are arranged in an array having an area less than that defined by the row of bond pads near the perimeter of the face of the chip.

The present invention is particularly advantageous for the packaging of multi-chip modules, since the probability that a package contains a defective chip increases with the number of chips contained in the package. The testing of chips prior to chip packaging afforded by the present invention thus reduces the risk that a multi-chip package will be discarded because one or more of the chips in the module is defective. Moreover, the small interconnect footprint allows many chips to be packed closely together.

5

10

20

35

Brief Description of the Drawings

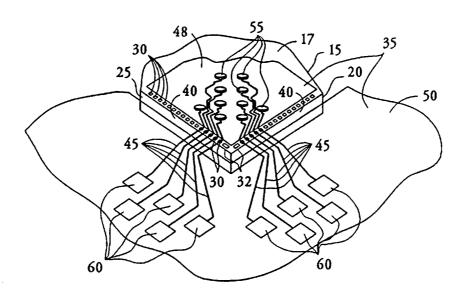

Fig. 1 is a perspective view of a portion of the present invention connected to a portion of an integrated circuit chip.

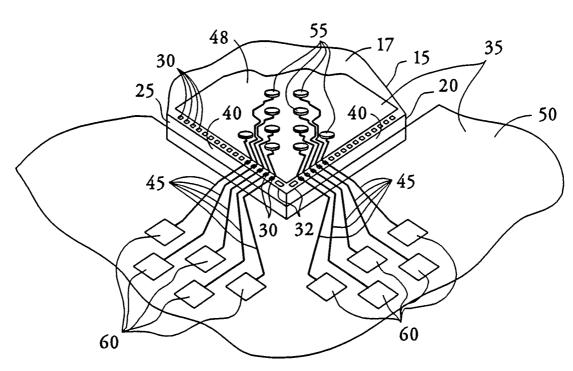

Fig. 2 is a top view of a portion of a tape with several devices of the present invention connected to several integrated circuit chips.

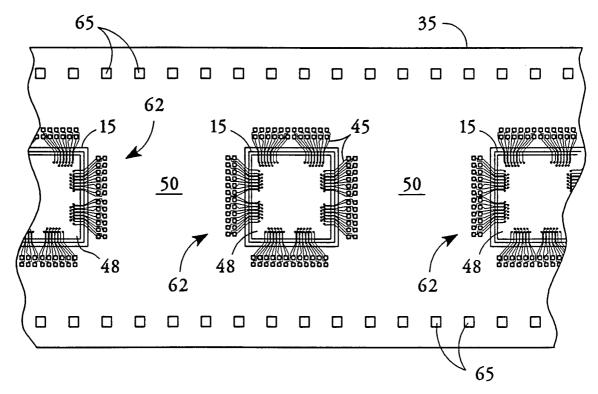

Fig. 3 is a cross-sectional view of a lead of the present invention connected to an integrated circuit chip for testing.

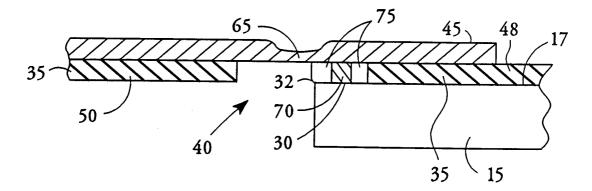

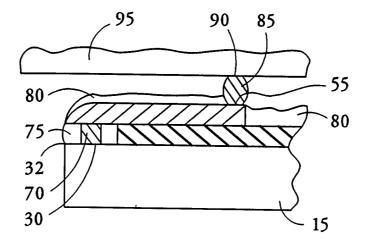

Fig. 4 is a cross-sectional view of the lead and chip of Fig. 3 connected to a package after the test lead has been severed.

Best Mode for Carrying Out the Invention 15

Referring to Fig. 1, a portion of a semiconductor integrated circuit chip 15 having a top surface or face 17 and edges 20 and 25 is shown. The chip 15 has a row of bond pads 30 located near a perimeter 32 of its face 17 that is defined, in part, by edges 20 and 25. The bond pads 30 offer electrical communication with the internal circuitry of the chip 15.

Disposed on top of the face 17 is a thin, flexible, electrically insulative, thermally conductive 25 substrate or tape 35. The tape 35 has a gap 40 above the perimeter of the face 17 where the tape 35 has been re-On top of the tape 35 are a plurality of thin, electrically conductive leads 45 that extend over the gap 40 to connect an inner area 48 of the tape 35 with an 30 outer area 50 of the tape 35. Each conductive lead 45 concludes at one end with an interconnect pad 55 located on the inner area 48 and at another end with a test terminal 60 located on the outer area 50 of the tape 35. The interconnect pads 55 are arranged on the inner area 48 in a pad grid array.

Each conductive lead 45 is aligned with and connected to a bond pad 30. The leads 45 are bent in several places between their connections with the bond 5

10

15

20

25

30

35

pads 30 and the interconnect pads 55, allowing the distance between the bond pads 30 and the interconnect pads 55 to vary in length in order to alleviate stress caused by differential thermal expansion.

Fig. 2 shows several devices 62 comprised of a portion of the tape 35 having leads 45, interconnect pads 55 and test terminals 60, each corresponding to a different chip 15 are shown. For clarity of illustration, the devices 62 are shown in FIGS. 1 and 2 with only a few leads 45, interconnect pads 55 and test terminals 60. In practice, such devices 62 may each have several hundred such leads 45, each lead 45 connecting an interconnect pad 55 with a test terminal 60. The test terminals 60 are typically formed in area arrays peripheral to the chip 15 in order to facilitate connection of the device 62 to external circuitry, not shown, for testing the chip 15.

Each test terminal 60 may have generally square sides approximately 0.75 mm in length, and may be separated from adjacent test terminals 60 by a similar distance. The interconnect pads 55 are arranged in an area array over the face 17 of the chip 15, each interconnect pad 55 being generally circular with a typical diameter of about 0.3 mm and spaced from adjacent such pads by about 0.3 mm. The bond pads 30 of the chip 15 may be generally rectangular, with a width in a direction parallel to the adjacent perimeter 32 of about 0.5 mm. The leads 45 may be approximately 0.025 mm in width, and separated from each other by at least that distance. The dimensions given above are for a chip with 368 bond pads and can be varied to suit chips having more or less bond pads.

The tape 35 may be composed of polyimide or any other flexible, electrically insulative substrate known in the art of TAB, and may be approximately 0.1 mm in thickness. The tape 35 has sprocket holes 65 for advancement and alignment, and is similar in appearance to film for 35 mm cameras.

The device 62 is formed by adhering a thin sheet of copper, not shown, which may be about 0.3 mm in thickness to the tape 35 with epoxy and etching the sheet to form the leads 45, interconnect pads 55 and test terminals 60. Alternate methods of lead frame formation known for TAB may instead be employed. The gap 40 is then formed, preferably by etching, from the tape 35 in a strip corresponding to the perimeter 32. The tape 35 is then positioned over the chip 15 so that contact areas 10 of the leads 45 are precisely aligned with bond pads 30. The inner area 48 is adhered to the face 17 of the chip 15, preferably with a thermally conductive substance such as silicon adhesive, and the leads 45 are connected to the bond pads 30. The leads 45 may be connected with the 15 bond pads 30 by thermocompressive bonding or any other technique known in the art. Preferably gold or eutectic alloy solder bumps, not shown, have been deposited on the bond pads 30 as an aid to such bonding. Such bumps help to avoid breakage of the leads 45 during bonding. 20 bon of epoxy, not shown, is then flowed around and between the connections between the leads 45 and the bond pads 30 to encapsulate and rigidify those connections.

As is most easily seen in the cross-sectional view of a lead 45 shown in Fig. 3, the leads 45 have been etched near the perimeter 32 of the chip 15 more than elsewhere, so that a weakened or thinned section 65 exists on each lead 45 approximately above the perimeter 32 of the face 17. Although Fig. 3 shows a cross-section of a lead 45 that is vertically thinner or notched, the thinned section 65 can also or alternatively be of a reduced thickness in a horizontal dimension. Also near the perimeter 32, but positioned slightly closer to an interior of the face 17, is the gap 40 in the tape 35 between the inner tape area 48 and the outer tape area 50. A bump 70 formed from gold or other metals such as eutectic alloys used for TAB bonding bumps has been deposited on a bond pad 30, and the bump 70 has been bonded to the lead 45. Such bumps 70 preferably have a top that is slightly

25

30

higher than the thickness of the tape 35, so that they can be connected to the leads 45 without the leads being vertically deformed. An epoxy encapsulant 75 has been flowed onto, under and, although not shown in this cross-sectional view, between the connections between the leads 45 and the gold bumps 70 in an area of the gap 40 within the perimeter 32.

5

25

30

35

After the encapsulant 75 has hardened, the chip 15 is tested by applying electrical signals to the test terminals 60. Each test terminal 60 is, as described 10 above, electrically connected to a bond pad 30, allowing the chip 15 to have full-scale testing performed of all of its circuits. It is possible to perform tests in this manner that would not be possible using wafer probes. For example, burn in and temperature testing of the chip 15 15 may be performed. Only chips 15 that pass this testing are connected to a package such as a circuit board, thereby greatly increasing the likelihood that the chip or chips in a package are fully functional. It should also be noted that the epoxy encapsulant 75 and the at-20 tachment of the leads 45 to the inner area 48 of the tape 35 offer stronger connections than typical cantilevered lead end to bond pad connections known in TAB.

After testing of the chip 15 via the test terminals 60 has been completed, the leads 45 may be severed above the perimeter 32, as shown in Fig. 4. This severing may be accomplished by applying a stress to the leads 45 that is sufficient to cause the leads 45 to break at their thinned sections 65 near the encapsulant 75. Alternatively, the leads 45 may be severed with a knife or other known methods, not shown, in which case the leads 45 may not need the thinned sections 65 described above. A solder resist 80 is deposited on the leads 45 and the inner area 48 of the tape 35 but not on the array of interconnect pads 55, in order to isolate the leads from "lands" offered by the interconnect pads 55 for solder to be deposited onto. Solder bumps 85 are then formed on the interconnect pads 55 for connection with a predeter-

PCT/US94/10415 WO 95/09459

-9-

mined array of terminals 90 of a package 95, and the chip is connected to the package by known flip-chip techniques.

Alternatively, connection of the interconnect pads 55 to the package 95 may be by means of a z-axis adhesive, not shown. A z-axis adhesive, which may be an epoxy paste, is formed to be electrically conductive in only one direction. When such an adhesive is used in the present invention to connect a device 62 to a package 95, it is formed to conduct electricity in the general 10 direction connecting the device 62 and the package 95, without conducting electricity generally transversely to that direction. Thus, the z-axis adhesive forms electrically conductive pathways connecting the array of interconnect pads 55 with their respective terminals 90, without allowing crossover connections or short circuits.

Thus the interconnection of the chip 15 with a package 95 requires only the area of the array of interconnect pads 55, which is less than the area of the chip face 17, yet the chip 15 can be fully tested prior to interconnection.

25

15

20

PCT/US94/10415

## Claims

-10-

A method of making a device for connecting an integrated circuit chip to external circuitry comprising: providing an integrated circuit chip having

5

10

15

20

25

30

bond pads disposed near a perimeter of a chip face; positioning a flexible tape having an electrically insulative substrate and a plurality of electrically conductive leads having inner portions and outer portions, said inner portions extending from said bond pads to interconnect pads disposed within a central region of said chip face, said outer portions extending from between said bond pads to peripherally disposed test terminals such that said tape is adjacent to said chip face and said leads are aligned with said bond pads;

bonding said bond pads to said leads at areas of said leads between said interconnect pads and said test terminals, thereby positioning said interconnect pads within said perimeter;

testing said integrated circuit chip, including channeling electrical signals via said test terminals; and

severing said leads proximate to said perimeter of said chip, thereby disconnecting both said outer portions and said test terminals from said chip.

- The method of claim 1 further comprising bonding said interconnect pads to external circuitry, after severing said outer portions of said leads proximate to said perimeter of said chip.

- The method of claim 1 further comprising bonding said substrate to said chip face before severing said outer 35 portions of said leads proximate to said perimeter of said chip.

-11-

4. The method of claim 3 wherein severing said outer portions of said leads proximate to said perimeter of said chip includes:

providing said leads with a weakened portion proximate to said perimeter; and

applying a stress to said leads sufficient to cause said leads to break at said weakened portion, but insufficient to cause said leads to break elsewhere.

10

5

5. The method of claim 1 further comprising forming said leads, including:

depositing an electrically conductive layer on said substrate; and

selectively etching said conductive layer.

- The method of claim 1 further comprising removing a strip of said substrate corresponding to said bond pads,

prior to bonding said bond pads to said leads at areas of said leads between said interconnect pads and said test terminals.

- 7. The method of claim 1 further comprising forming said interconnect pads in an area array on a surface of said tape distal to said chip face.

- 30 8. The method of claim 7 further comprising:

forming said leads on said surface; and

depositing an electrically insulative coating

on said leads but not on said interconnect pads.

35

9. The method of claim 8 further comprising depositing solder bumps on said interconnect pads.

-12-

10. The method of claim 3 wherein severing said leads proximate to said bond pads includes encapsulating said leads with a rigid substrate around said bond between said leads and said bond pads.

5

10

15

20

11. A device for providing electronic and support connections for an integrated circuit comprising:

an integrated circuit chip having bond pads adjacent to a perimeter of a face of said chip;

a flexible, electrically insulative tape having opposed first and second major surfaces and a gap near said perimeter of said chip face, said first major surface connected to said chip face; and

a plurality of electrically and thermally conductive leads supported on said second major surface, said leads having test terminals disposed beyond said perimeter of said chip face and having interconnect pads disposed in an area array adjacent to said face, said leads connected to said bond pads of said chip and having a reduced thickness closely peripheral to said connections to said bond pad, whereby said leads are severable at regions closely peripheral to said bond pads after testing said chip via test terminals.

25

12. The device of claim 11 further comprising an electrically insulative layer covering said leads disposed adjacent to said face but not said interconnect pads.

30

13. The device of claim 11 wherein said leads are encapsulated with a rigid material at said connections to bond pads.

14. The device of claim 11 wherein said leads disposed adjacent to said face include bends and are variable in length.

5

10

15

20

25

15. The device of claim 13 further comprising electrically conductive bumps having a height similar to a distance between said first and second major surfaces of said tape, said bumps connecting said bond pads to said leads.

16. A device for connecting an integrated circuit chip with external circuitry comprising:

an integrated circuit chip having a face with perimetrically disposed bond pads;

a flexible, electrically insulative, thermally conductive tape having generally oppositely disposed first and second major surfaces and a gap near said perimeter of said face, said first major surface adhered to said face; and

a plurality of alternate state, electrically conductive leads attached to said second major surface of said tape and to bond said pads, said leads having a first connective state in which said leads extend outwardly from said bond pads to peripheral test terminals for testing, and said leads having a second connective state in which said leads are limited to extending inwardly from said bond pads to interconnect pads for connection to a package, said first connective state having said interconnect pads free of mechanical connections, said second connective state having portions of leads extending outwardly from said bond pads severed.

-14-

17. The device of claim 16 further comprising an electrically insulative layer covering portions of said leads extending inwardly from said bond pads except for said interconnect pads, said interconnect pads being capped with electrically conductive bumps, whereby said interconnect pads can be connected to a package after said portions of said leads extending outwardly from said bond pads are severed.

10

15

- 18. The device of claim 16 wherein said leads have a smaller thickness closely peripheral to said bond pads, whereby an said leads can be severed closely peripheral to said bond pads with an amount of stress that is insufficient to sever said leads elsewhere.

- 19. The device of claim 16 wherein said interconnect pads are disposed in an area array.

20

25

20. The device of claim 18 further comprising electrically conductive bumps having a height similar to a distance between said first and second major surfaces, said bumps connecting said bond pads to said leads.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

### INTERNATIONAL SEARCH REPORT

International application No.

PCT/US94/10415

| A. CLASSIFICATION OF SUBJECT MATTER IPC(6) :H01R 43/00; H01L 23/14                                                                                 |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| US CL :29/827; 174/52.4 According to International Patent Classification (IPC) or to both national classification and IPC                          |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| B. FIELDS SEARCHED                                                                                                                                 |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| Minimum documentation searched (classification system followed by classification symbols)                                                          |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| U.S. : 29/827; 830, 832, 846; 174/52.4; 228/180.22, 437/8, 209, 220                                                                                |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                      |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)                       |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                             |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| Category*                                                                                                                                          | Citation of document, with indication, where a                                                                                                                     | ppropriate, of the relevant passages                                                                                                                                             | Relevant to claim No.                                             |  |  |  |  |

| A                                                                                                                                                  | US,A, 4,866,508 (EICHELBERGER<br>12 SEPTEMBER 1989                                                                                                                 | RET AL)                                                                                                                                                                          | 1-20                                                              |  |  |  |  |

| A                                                                                                                                                  | US,A, 4,903,113 (FRANKENY ET<br>20 FEBRUARY 1990                                                                                                                   | 1-20                                                                                                                                                                             |                                                                   |  |  |  |  |

| Α                                                                                                                                                  | US,A, 5,008,614 (SHREEVE ET A                                                                                                                                      | 1-20                                                                                                                                                                             |                                                                   |  |  |  |  |

| A                                                                                                                                                  | US,A, 5,036,380 (CHASE) 30 JU                                                                                                                                      | 1-20                                                                                                                                                                             |                                                                   |  |  |  |  |

| A                                                                                                                                                  | US,A, 5,042,147 (TASHIRO) 27                                                                                                                                       | 1-20                                                                                                                                                                             |                                                                   |  |  |  |  |

| A                                                                                                                                                  | US,A, 5,156,983 (SCHLESINGER                                                                                                                                       | 1-20                                                                                                                                                                             |                                                                   |  |  |  |  |

| A                                                                                                                                                  | US,A, 5,157,476 (YOSHIDA) 20                                                                                                                                       | 1-20                                                                                                                                                                             |                                                                   |  |  |  |  |

|                                                                                                                                                    |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| X Further documents are listed in the continuation of Box C. See patent family annex.                                                              |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| "A" do                                                                                                                                             | ecial categories of cited documents:<br>cument defining the general state of the art which is not considered                                                       | "T" later document published after the inte<br>date and not in conflict with the applica<br>principle or theory underlying the inv                                               | ation but cited to understand the                                 |  |  |  |  |

| *E* earlier document published on or after the international filing date "X" document of particular relevance; considered novel or cannot be consi |                                                                                                                                                                    | "X" document of particular relevance; the considered novel or cannot be considered when the document is taken alone                                                              | e claimed invention cannot be<br>red to involve an inventive step |  |  |  |  |

| cit                                                                                                                                                | cument which may throw doubts on priority claim(s) or which is<br>ed to establish the publication date of another citation or other<br>ecial reason (as specified) | "Y" document of particular relevance; the                                                                                                                                        |                                                                   |  |  |  |  |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                       |                                                                                                                                                                    | considered to involve an inventive step when the document is<br>combined with one or more other such documents, such combination<br>being obvious to a person skilled in the art |                                                                   |  |  |  |  |

|                                                                                                                                                    | cument published prior to the international filing date but later than<br>priority date claimed                                                                    | '&' document member of the same patent                                                                                                                                           | family                                                            |  |  |  |  |

| Date of the actual completion of the international search 20 DECEMBER 1994  Date of mailing of the international search report  1 1 JAN 1995       |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| Name and mailing address of the ISA/US Commissioner of Patents and Trademarks Box PCT Washington, D.C. 20231  Authorized officer CARL J. ARBES     |                                                                                                                                                                    |                                                                                                                                                                                  |                                                                   |  |  |  |  |

| Eimila N                                                                                                                                           | Faccinile No. (702) 205 2220                                                                                                                                       |                                                                                                                                                                                  |                                                                   |  |  |  |  |

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/US94/10415

| C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                    |                       |  |  |  |  |

|-------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Category*                                             | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |  |  |  |  |

| A                                                     | JP,A, 4-167,584 (NAGAO) 15 JUNE 1992                                               | 1-20                  |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

| Š                                                     |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    | ,                     |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |

|                                                       |                                                                                    |                       |  |  |  |  |