# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) Int. CI. <sup>6</sup><br>H01L 27/108 |                                    | (45) 공고일자<br>(11) 등록번호<br>(24) 등록일자 | 2000년03월02일<br>10-0245909<br>1999년12월02일 |

|-------------------------------------------|------------------------------------|-------------------------------------|------------------------------------------|

| (21) 출원번호<br>(22) 출원일자                    | 10-1995-0059696<br>1995년 12월27일    | (65) 공개번호<br>(43) 공개일자              | 특 1996-0026877<br>1996년 07월 22일          |

| (30) 우선권주장                                | 8/365,617 1994년 12월28일             | 미국(US)                              |                                          |

| (73) 특허권자                                 | 인터내셔널 비지네스 머신즈<br>미국 10504 뉴욕주 아몬크 | 코포레이션 포만 제                          | 프리 엘                                     |

| (72) 발명자                                  | 웬델 피. 노블 주니어                       |                                     |                                          |

| (74) 대리인                                  | 미합중국 05468 버몬트주 스<br>김성기, 송병옥      | 왐프 로드 84                            |                                          |

| 심사관 : 신양환                                 |                                    |                                     |                                          |

## <u>(54) 5개의 스퀘어를 갖는 폴드된 비트라인 디램 셀</u>

#### 요약

본 발명은 게이트 도체의 개별적인 세그먼트 및 세그먼트 게이트와 접촉하는 전도성 스페이서 레일 워드라인을 갖는 게이트를 트랜지스터를 포함하는 DRAM 셀에 관한 것이다. 워드라인 커넥터는 게이트 세그먼 트 위의 측벽을 따라 형성된 도체를 방향성 에칭함으로써 형성된다. 측벽은 맨드릴내에 홈을 에칭함으로 써 형성된다. 이러한 구조는 5개의 스퀘어를 갖는 폴드된 비트라인 DRAM 셀의 설계를 허용한다.

## 대표도

## 명세서

[발명의 명칭]

5 스퀘어의 면적을 갖는 폴드된 비트라인 디램(DRAM)셀

[도면의 간단한 설명]

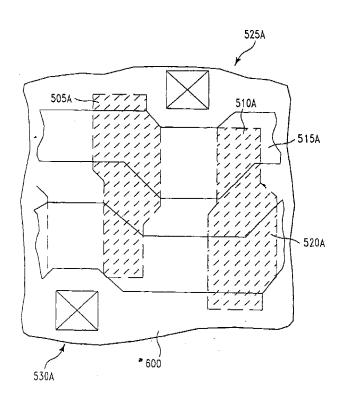

제1도는 종래 기술의 DRAM 셀 쌍의 레이아웃을 도시하는 상면도.

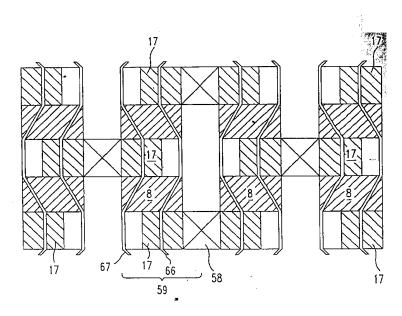

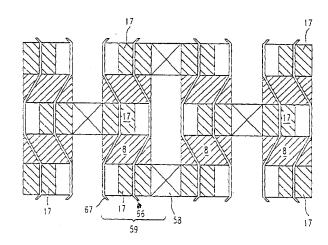

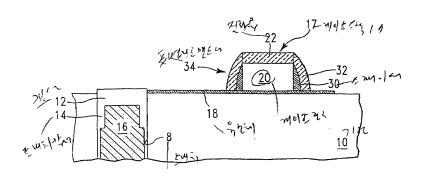

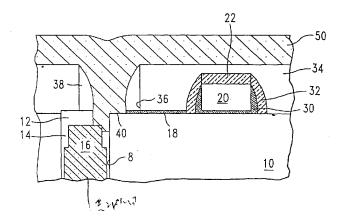

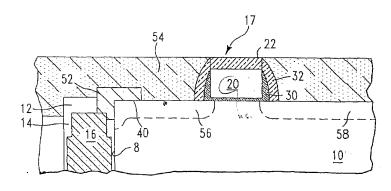

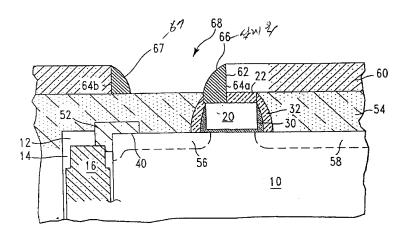

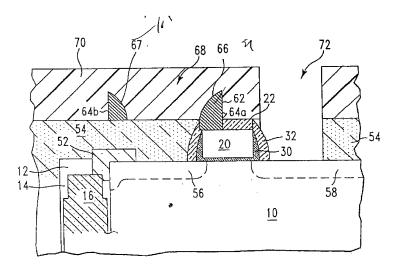

제2도 내지 제6도는 본 발명에 따른 DRAM 셀을 제조하기 위한 프로세스 단계를 도시하는 횡단면도.

제7도는 본 발명에 따른 어레이의 DRAM 셀 및 일부의 레이아웃을 도시하는 상면도.

\* 도면의 주요부분에 대한 부호의 설명

10 : 실리콘 기판 8 : 딥 트렌치 12 : 트렌치 캡 산화물 14 : 트렌치 칼러 17 : 게이트 스택 16 : 트렌치 폴리실리콘

18 : 게이트 유전체 22 : 질화물 캡

20 : 폴리실리콘 게이트 세그먼트 34 : 폴리실리콘 맨드릴

52 : 스트랩 66. 67 : 셀 레일

#### [발명의 상세한 설명]

본 발명은 일반적으로 DRAM 셀 설계 및 반도체 상호 접속 기술에 관한 것이다. 특히, 본 발명은 DRAM 셀용 전도성 측벽 레일 워드라인 (conductive sidewall rail wordline) 및 상당히 축소된 크기의 셀 설계에 관한 것이다.

많은 수의 DRAM 셀의 워드라인들로 상호 접속되어야 하는데, 워드라인과, 워드라인들 간의 공간은 폴드된 비트라인 셀(folded-bitline cell)의 크기를 결정한다. 전형적으로, 워드라인은, 반도체 표면상의 절면 물질상에 피착되며 포토리소그래피 방식으로 라인으로서 정의되는, 알류미늄 또는 폴리실리콘과 같은도체의 박막으로 형성된다. 라인의 폭 및 라인 간의 공간 모두 실질적으로 포토리소그래피 방식으로 정의되는 최소 라인보다 작게 형성될 수 없기 때문에, 워드라인과 워드라인들 간의 공간을 줄이기 위한 시도는 제한적이다. 라인의 폭을 줄이는 것은 가능하지만, 예를 들어, 라인의 폭을 감소시키는 것은 일반적으로 라인간 공간을 증가시키므로, 전체 워드라인 피치 (wordline pitch)는 향상되지 않는다. 포토리소그래피 최소 치수 (photolithographic minimum dimension)를 감소시키는 비용은 비싸고, 이러한 시도가 있을때마다 후속 세대의 반도체 제품(succeeding generation)이 정의되었다. DRAM 셀의 각각의 세대에서, 포토리소그래피 방식으로 정의된 워드라인 및 그 관련 공간은 각각 포토리소그래피 최소 치수로 형성되었다.

폴드된 비트라인 DRAM 셀(folded-bitline DRAM cell)설계에서, 디.엠. 케니(D.M Kenney)에게 허여된 '머지 절연된 반도체 트렌치 캐패시터 노드 트렌치 구성(Semiconductor Trench Capaciter Cell with Merged Isolation and Node Trench Construction)' 이라는 명칭의 미합중국 특허 제4,801,988호(이후, '988 특허)에 기술된 바와 같이, 활성 및 통과 워드라인(an active and a passing wordline)이 각각의 셀을 통과 하는데, 이는 본원의 제1도에 도시되어 있다. 제1도에서 한 쌍의 셀에 대한 트렌치 캐패시터(505A 및 510A) 위로 워드라인(515A 및 520A)이 교차하고 있다. 이러한 DRAM 셀을 위해 필요한 공간은, 각각의 셀내의 2개의 워드라인 각각에 대한 최소 치수 및 각각의 워드라인 간의 공간에 대한 부가적인 최소 치수이다. 따라서, 전형적인 셀의 전체 최소 길이는 4 최소 치수 (4 minimum dimensions)이다. 셀의 폭은 적어도 2 최소 치수인데. 이들 중 하나는 셀의 부품용이고, 다른 하나는 셀들 간의 공간에서의 두터운 절연부 (thick isolation) (트렌치 캐패시터는 이 절연의 일부일 수 있음)용이다. 따라서, 전형적인 셀의 최소 면적은 8 평방 최소 치수(8 square minimum dimension), 또는 8 스퀘어이다.

포토리소그래프적 제한을 피하기 위한 하나의 방법은 전도성 측벽 레일로 형성된 워드라인을 제공하는 것이다. 이러한 레일의 폭은 피착된 도체의 두께에 의해 정해지고, 이 두께는 최소 리소그래피 치수보다 상당히 작을 수 있다. Hsieh에게 허여된 '딥-서브미크론 게이트로 형성된 전계 효과 트랜지스터 (Field Effect Transistor Formed with Deep-Submicron Gate)' 라는 명칭의 미합중국 특허 제5,202,272호 및 로우레이(Lowrey)에게 공동으로 허여된 '유효 포토리소그래피의 해상도 제한을 초월하는 특징 폭을 갖는 DRAM 어레이를 제조하기 위한 프로세스(Process for Fabricating a DRAM Array Having Feature Widths that Transcend the Resolution Limit of Available photolithigraphy)' 라는 명칭의 미합중국 특허 제5,013,680호 (이후, '680 특허)는 워드라인을 형성하기 위해 최소 치수 미만의 전도성측벽 스페이서 레일 (subminimum dimension conductive sidewall spacer rail)을 사용하는 방법을 개시하고 있다.

이러한 최소 치수 미만의 스페이서 레일 워드라인을 사용할 때 발생하는 한가지 문제점은 장치의 길이와 소스 및 드레인의 측방향 확산 정도를 정확히 제어하기가 어렵다는 것이다. 예를 들어, 스페이서 두께 또 는 측방향 확산의 작은 변이는 최소 치수 미만 채널의 길이의 큰 변이를 일으킬 수 있다. 이 결과는 한편 으로는 큰 누출 전류를 발생시키고 다른 한편으로는 성능 저하를 가져온다. 본 발명은 종래 기술의 최소 치수 미만 측벽 스페이서 레일 워드라인의 문제점을 해결한다.

그러므로, 본 발명의 목적은 포트리소그래피 방식으로 형성된 게이트를 갖고 있고, 8 평방 최소 치수 미만의 면적을 갖는 폴드된 비트라인 DRAM 셀을 제공하는 것이다.

본 발명의 특징은 최소 치수 미만의 스페이서 레일 워드라인이 대략 최소 치수를 갖는 개별적인 게이트 세그먼트들(gate segments)을 연결하는 것이다.

본 발명의 다른 목적은 개별적인 세그먼트 게이트 도체 및 최소 치수 미만의 스페이서 레일 게이트 커넥 터를 갖는 트랜지스터를 제공하는 것이다.

본 발명의 이들 및 다른 목적은 게이트 스택(gate stack)의 얇은 유전체와 실질적으로 동일한 공간에 걸쳐 있는(coextensive) 게이트 도체의 개별적인 세그먼트를 포함하는 게이트를 갖는 트랜지스터를 포함하는 반도체 구조에 의해 달성된다. 전도성 스페이서 레일인 커넥터는 세그먼트 게이트와 접촉하고 있다.

본 발명의 다른 특징은 게이트 스택의 얇은 유전체와 실질적으로 동일한 공간에 걸쳐 있는 게이트 도체의 개별적인 세그먼트를 포함하는 게이트를 갖는 트랜지스터를 포함하는 DRAM 셀을 포함한다. 전도성 스페이 서 레일인 워드라인은 세그먼트 게이트와 접촉하고 있다.

본 발명의 출원인은 폴드된 비트라인 구성에서, 최소 치수 미만 스페이서 레일 워드라인을 사용한 것은 셀의 긴 방향을 따라 1½개의 최소 치수를 절약하여 이 길이의 4 최소 치수에서 2½ 최소 치수까지 감소시킴으로써, DRAM 셀의 면적을 8 스퀘어에서 5 스퀘어까지 감소시키고, 셀 면적을 37.5% 감소시킬 수 있다는 것을 인식하였다. 또한, 본 발명에서 워드라인의 게이트 기능과 스트래핑 기능(strapping function)이 분리되었기 때문에, 폴리실리콘 게이트의 장점이 보유될 수 있는 동시에 텅스텐 또는 알루미늄과 같은 고 전도율 물질이 최소 치수 미만 워드라인을 형성하기 위해 사용될 수 있으므로 워드라인에 대한 고

전도성도 보유될 수 있다.

본 발명의 다른 특징은 게이트 도체의 개별적인 세그먼트를 포함하는 트랜지스터의 게이트를 형성하는 단계; 게이트 도체 위에 측벽을 갖는 맨드릴(mandrel)을 형성하는 단계; 측벽에 인접하고 게이트 도체와 접속하는 전도성 물질을 형성하는 단계; 및 스페이서 레일 도체를 형성하기 위해 도체 물질을 방향성 에칭(directionaletch)하는 단계를 포함하는 방법에 의해 달성된다.

본 발명의 이들 및 다른 목적, 특징 및 장점은 본 발명의 도면 및 상세한 설명으로부터 명백해질 것이다.

제2도 내지 제7도에 도시된 바와 같이, 본 발명은 [오버레이(overlay) 허용 공차내에서] 대략 1 최소 치수의 길이 및 폭을 갖는 게이트 도체의 개별적인 세그먼트로부터 형성된 게이트를 갖는 DRAM 셀을 제공한다. 이러한 세그먼트 게이트들을 상호 접속하는 워드라인 및 워드라인들 간의 공간은, 워드라인이 측벽을따라 도체를 방향성 에칭하여 형성됨으로써, 각각 최소 치수 미만의 치수를 갖는다. 이러한 구성은 5-8스퀘어의 면적을 갖는 폴드된 비트라인 구조를 갖는 DRAM 셀의 설계를 가능하게 한다.

폴드된 비트라인 DRAM 어레이는 본 발명이 적용될 수 있는 트랜지스터 어레이의 한 예이다. 본 발명은 폴 드된 비트라인 DRAM 어레이가 2.5 × 2 최소 치수의 크기 또는 5 스퀘어의 면적을 갖게 한다.

본 예에서 사용된 용어 '수평적(horizontal)' 은 칩의 방향성(orientation)에 무관하게 반도체 칩 또는 웨이퍼의 종래의 플레이너(planar) 표면에 평행한 평면(plane)으로서 정의된다. 용어 '수직적(vertical)'은 상기에 정의된 바와 같은 수평에 수직인 방향에 관한 것이다. '온(on), ['측벽(sidewell)' 에서와같은] '측(side)', '하이어(higher)', 로우어(lower)', 위(over) 및 '아래(under)' 와 같은 전치사는 칩의 방향성에 무관하게 칩 또는 웨이퍼의 상부 표면 상의 종래의 플레이너 표면에 대해 정의된다.

제2도 내지 제6도에 도시된 프로세스 단계에 사용되는 단결정 반도체 웨이퍼는 실리콘, 게르마늄 및 갈륨 비소와 같은 물질로 형성된다. 실리콘이 가장 광범하게 사용되고, 그 특성이 가장 널리 알려졌기 때문에, 이하에서는 예시를 위해 실리콘이 사용되었다. 웨이퍼는 후술하는 것과 같은, 프로세스 순차를 개시하기 전에 완료되는 주입, 확산, 산화 및 기타의 프로세스 단계를 가질 수 있다.

제2도 내지 제6도는 본 발명의 DRAM 셀을 제조하는 프로세스의 단계를 도시한다. 본 발명의 제조의 초기 프로세스 단계는 본 명세서에 참조되는 디.엠.케니 (D.M.Kenney)에게 허여된 '확산 매립 플레이트 트렌치 DRAM 셀 어레이(Diffused Buried Plate Trench DRAM Cell Array) '라는 명칭의 미합중국 특허 5,264,716호(이후, '716호 특허)의 제3도 내지 제10도에 도시되어 있다. '716호 특허에서는 전체 워드라인이 마스킹 단계에 의해 정의된다. 그러나, 본 발명에서는 (전체 워드라인 대신) 개별적인 직사각형 또는 사각형 게이트 스택 세그먼트가 마스킹 단계에 의해 정의되는데, 각각의 세그먼트는 단일 트랜지스터용의 단일세그먼트만을 갖는다. 양호하게는, 게이트 세그먼트는 플레이너 표면을 따라 각 방향으로 대략 1 최소 치수의 크기 (또는 오버레이 허용 공차를 수용하기 위해 조금 더 큰 크기)를 갖고, 게이트는 트렌치 캐패시터들 간의 최소 치수 공간을 채우도록 정렬된다.

제2도를 참조하면, 실리콘 기판(10)내의 딥 트렌치(8)는 트렌치 캡 산화물 (12), 트렌치 칼러(14) 및 트렌치 폴리실리콘(16)으로 구성된다. 게이트 스택(17)은 게이트 유전체(18), 폴리실리콘 게이트 세그먼트(20) 및 질화물 캡(22)을 포함한다. 산화물 스페이서(30)가 열적으로 성장하거나 피착되고, 방향성 에칭된다. 이어서, 질화물 측벽 스페이서(32)가 피착되어 방향성 에칭된다. 따라서, 본 발명에서는, 게이트 세그먼트(20)는 모든 4개의 측상에 스페이서(30 및 32)를 갖는다. 스페이서가 게이트 세그먼트의 크기에 부가되므로, 게이트 스택(17) 및 트렌치(8)의 약간의 오정렬은 허용 가능하다. 또한, 딥 트렌치를 형성하기 위한 포토리소그래피 단계에서, 전형적으로 트렌치는 마스크 최소 치수보다 조금 크게 형성되고, 트렌치들간의 공간도 이에 대응하여 최소 치수보다 작게 된다. 따라서, 게이트 스택 자체는 최소 치수의 폭(또는 최소 치수보다 조금 큰 폭)을 갖지만 딥 트렌치들 간의 거리의 전체길이(full extent)는 게이트 스택(17) 및 스페이서(30 및 32)에 의해 커버된다. 이 풀커버리지(full coverage)는 소스/드레인 확산부를 형성하기 위한 나중의 이온 주입 단계에서 소스와 드레인 사이의 단락을 피하기 위해 중요하다.

제3도에 도시된 바와 같이, 다음 단계에서 진성(intrinsic) 폴리실리콘 맨드릴 (34)이 피착되어 평탄화된다. 이어서, 진성 폴리실리콘 맨드릴(34)을 통해 노드 스트랩 (node strap)용 홀(36)을 정의하고 에칭하기 위해 최소 이미지 마스크가 사용된다. 이러한 실리콘 에칭은 게이트 유전체(18) 및 트렌치 캡 산화물(12)상에서 중지된다. 이어서, 제2진성 폴리실리콘층이 피착되어, 맨드릴(34)내의 홀(36)의 측벽을 따라스페이서 칼러(38)를 남겨놓도록 방향성 에칭된다. 따라서, 맨드릴(34)내의 홀(36)의 크기는 스페이서 칼러(38)의 최소 미만 치수 만큼 감소된다. 이어서, 트렌치 캡 산화물(12), 트렌치 칼러(14) 및 게이트 유전체(18)의 노출 부분은 트렌치 폴리실리콘(16)의 표면 및 트랜지스터의 노드 확산부로 될 영역(40)을 노출시키기 위해 에칭된다. 이어서, 도핑된 폴리실리콘(50)이 피착되어, 홀(36)을 충진하고, 트렌치 폴리실리콘(16)과 트랜지스터의 노드 확산부로 될 영역(40)을 전기적으로 접속하기 위한 스트랩(52)(제4도 참조)을 제공한다.

다음으로, 도핑된 폴리실리콘(50)이 리세스 에칭(recess etch)되어, 스트랩 (52)이 질화물 캡(22) 아래의 레벨에 있게 된다. 이제 제4도를 참조하면, 다음으로 진성폴리실리콘 맨드릴(34) 및 진성 폴리실리콘 스페이서 칼러(38)가 선택적 에칭에 의해 제거되고 고농도 도핑된 폴리실리콘(50)을 사실상 원상태 그대로 남겨놓게 된다. 본 명세서에 참고 문헌으로 사용되고, 씨. 더블유. 디. 프라이서(C.W.D.Pricer) 등에게 허여된 미합중국 특허 제5,160,987호에 기술된 것과 같은 KOH 및 알콜, 에틸렌다아민 및 피로카테콜, 또는 갈산 에천트를 포함하는 몇몇 선택적 에칭제가 유용하다. 따라서, 폴리실리콘의 도핑되지 않은 부분은 제거되고, 도핑된 부분은 남겨진다. 이어서, 도핑된 산화물(54)이 게이트(20) 및 게이트 질화물 캡(22)의 높이보다 더 큰 두께로 피착된다. 산화물(54)은 n-채널 어레이용으로 비소 도핑되고, p-채널 어레이용으로 붕소 도핑된다. 이어서, 도핑된 산화물(54)은 게이트 질화물 캡(22)상에서 중지할 때까지 다시폴리쉬된다. DRAM 어레이 외부의 칩 영역에 트랜지스터를 형성하기 위해, 블록 마스크(block mask)가 도핑된 글라스(54)를 제거하기 위해 사용될 수도 있다. 이어서, 종래의 소스/드레인 주입이 이들 논-어레이 영역내에서 수행된다. 확산을 위한 어닐링 및 드라이브 인(drive-in) 단계는 또한 도핑된 산화물(54) 및 폴리실리콘 스트랩(52)으로부터 기판(10)내로 도펀트를 확산시켜 트랜지스터(59)의 노드 확산부(56) 및

비트라인 확산부(58)를 제공한다.

제5도에 도시된 바와 같이, 이어서 두꺼운 진성 폴리실리콘 맨드릴(60)이 피착되고, 평탄화되며, 마스크를 사용하여 패턴화된다. 패턴은 폴리실리콘 맨드릴(60)내에, 게이트 질화물(22) 및 게이트 폴리실리콘(20) 위로 연장하는 측벽(64a)을 갖는 최소 치수의 홈(groove: 62)을 제공한다. 홈(62) 및 측벽(64a 및 64b)은 어레이의 많은 셀의 게이트 위로 연장된다. 이어서, 방향성 에칭이 홈(62)내에 노출된 게이트 폴리실리콘(20)으로부터 질화물(22)의 일부분을 제거하기 위해 수행된다. 다음 단계에서 도체가 피착되고, 측벽(64a)을 따라 게이트 폴리실리콘(20)에 접촉하는 최소치수 미만의 전도성 스페이서 레일(66)을 남겨놓도록 방향성 에칭된다. 이 에칭은 또한 측벽(64b)을 따라서도 최소 치수 미만의 전도성 스페이서 레일(67)을 남겨놓는다. 인접 워드라인 커넥터 (66 및 67)사이의 연관된 공간(68)도 또한 이 에칭에 의해 형성되고, 또한 최소 치수 미만을 갖는다. 레일(66 및 67)은 어레이의 워드라인 상호 접속 게이트 세그먼트를 제공한다. 제5도에 도시된 셀에서, 레일(66)은 활성 워드라인이고 [이 셀에서 레일(66)은 게이트 세그먼트와 접촉함], 레일(67)은 통과 워드라인이다 [이 셀에서 레일(67)은 게이트 세그먼트와 접촉함], 레일(67)은 통과 워드라인이다 [이 셀에서 레일(67)은 게이트 세그먼트와 접촉함].

다음 단계에서, 블록 마스크가 에칭과 함께 사용되어 어레이의 에지에서 접속하는 레일(66 및 67)의 일부분들을 제거함으로써 이들 인접한 레일을 서로로부터 분리한다. 이어서 진성 폴리실리콘 맨드릴(60)이 스트립된다. 제6도에 도시된 바와같이, 레벨간 유전체(70)가 피착되어 라인 프로세싱의 표준 백 엔드(standard backend)가 계속된다. 예를 들어, 레일(66)로 정렬된 마스크를 사용하여 보더레스(borderless)비트 라인 컨택트(72)가 레벨간 유전체(70)내에서 에칭된다. 홈(62)의 에지(64)가 게이트 폴리(20)의일부분 위로 연장하는 한, 워드라인에 대해 상당한 정렬 허용 공차가 허용가능하다. (제5도)

전도성 레일(66)은 금속 또는 금속 실리사이드와 같은 저저항성 금속으로 형성된다. 텅스텐, 몰리브덴, 티타늄 또는 알루미늄과 같은 금속이 적절하다. 저저항성 물질은 화학 증착과 같은 종래 기술에 공지된 방법으로 피착될 수 있다. 또한, 이러한 물질은 고농도로 도핑된 폴리실리콘으로부터 형성될 수도 있다. 이어서, 전도성 레일(66)은 방향성 에칭에 의해 피착된 도체로부터 형성된다. 방향성 에칭은 수직 벽을 따르는 부분을 실질적으로 제거하기 전에 수평 표면상의 물질 부분을 에칭 제거한다.

제7도를 참조하면, 셀 레이아웃은 게이트 스택(17), 게이트 스택(17)과 접촉하는 활성 워드라인(66), 인접 셀내의 게이트 스택과 접촉하는 통과 워드라인(67), 트렌치 캐패시터(8) 및 인접 셀과 공유되는 비트라인 확산부(58)를 갖는 트랜지스터(59)를 포함한다.

본 발명의 몇몇 실시예가 그 변형과 함께 기술되고 첨부된 도면에 도시되었지만, 다른 변형들이 본 발명의 범위를 벗어나지 않고 행해질 수 있다는 것이 명백하다. 예를 들어, 광범위한 물질이 맨드릴(34, 38 및 60) 및 레일(66)을 위해 사용될 수 있다. 본 발명이 상술한 바와 같이 폴드된 비트라인 구성에 가장적절하다고 나타나 있지만, 개방 비트라인 구성과 같은 다른 구성이 사용될 수도 있다. 본 발명은 폴리실리콘 스트랩 및 노드 폴리실리콘의 도핑 변화에 대응하여 n- 또는 p-채널 트랜지스터로 실시될 수 있다. 상술한 명세서는 첨부된 특허청구 범위보다 좁게 본 발명을 제한하려는 것이 아니다. 예는 배타적이라기보다는 예시하기 위한 것이다.

# (57) 청구의 범위

## 청구항 1

DRAM 셀에 있어서, a) 얇은 게이트 유전체 상의 게이트 도체의 개별적인 세그먼트로 이루어지는 게이트 와, 솔기가 없는 단결정 반도체 기판-여기서 단결정 반도체 기판은 어떠한 트렌치 캐패시터 위에도 걸쳐 있지 않음-으로 구성되는 트랜지스터; b) 내부에 캐패시터를 갖는 트렌치; c) 상기 트렌치 위로 지나가며, 상기 세그먼트 게이트 도체의 윗면과 전기적으로 접촉하는 전도성 스페이서 레일인 워드 라인; 및 d) 상기 트렌치 위로 지나가는 전도성 스페이서 레일인 통과 워드라인을 포함하되, 상기 트렌치는 상기 게이트와 게이트 사이에서 게이트 도체의 개별적인 세그먼트에 인접하게 형성되며, 상기 트렌치의 길이 방향의 길이는 상기 게이트와 드레인을 합한 길이 이하이고, 상기 워드 라인 및 통과 워드라인은 각각 일측벽이 수직형이고 타측벽이 라운드형인 맨드릴(mandrel)구조로 되어 있고, 상기 게이트와 접촉하는 하부면이 1 최소 치수(one minimum dimension)의 약1/4의 폭을 가지며, 자신들 사이에 1 최소 치수 이하의 공간을 가져, 상기 DRAM 셀이 약 2½ 최소 치수의 셀 길이 및 약 5평방 최소 치수의 셀 면적을 가지는 DRAM 셀.

# 청구항 2

제1항에 있어서, 상기 게이트 도체는 폴리실리콘으로 구성되고, 상기 워드라인은 저저항성 물질로 구성되는 DRAM 셀.

## 청구항 3

제1항에 있어서. 상기 게이트가 약 1 최소 치수의 길이를 간는 DRAM 셀.

#### 청구항 4

제1항에 있어서, 상기 DRAM 셀이 폴드된 비트라인 구조(folded-bitline architecture)를 간는 어레이의 일부분인 DRAM 셀.

#### 처그하 5

반도체 구조를 제조하는 방법에 있어서, a) 단결정 반도체 기판 내에 내부에 커패시터를 갖는 트렌치를 형성하는 단계; b) 상기 트렌치 캐패시터에 인접하며, 얇은 유전체, 및 이와 실질적으로 동일 공간에 걸 쳐 있는 게이트 도체-여기서 게이트 도체는 대향하는 제1 및 제2엣지 및 대향하는 제3및 제4엣지를 상부 표면을 가지며, 상기 기판은 단결정 반도체를 포함하고, 상기 게이트 아래에 있는 상기 기판은 어떠한 트렌치 캐패시터 위로도 연장되지 않음—의 개별적인 세그먼트를 포함하는 게이트 전극을 반도체 기판상 에 형성하는 단계; c) 상기 제1 및 제2엣지에는 접하되 상기 제3및 제4엣지에는 접하지 않으며, 적어도 1 최소 치수(one minimum dimension)의 측방향 크기를 갖는 두터운 절연부를 상기 기판 상에 형성하는 단계; d) 상기 제3엣지에 자기-정렬(self-align)되는 소오스(source)와 상기 제4엣지에 자기-정렬되는 드레인(drain)을 형성하는 단계; e) 상기 게이트 도체 상부 표면과 전기적으로 접촉하며, 상기 게이트 전국을 지나 연장되는 전도성 스페이서 레일인 커넥터를 형성하는 단계; 및 f) 상기 트렌치 위로 지나가는 전도성 스페이서 레일인 통과 커넥터를 형성하는 단계를 포함하되, 상기 트렌치는 게이트와 게이트 사이에서 게이트 도체의 개별적인 세그먼트에 인접하게 형성되며, 상기 트렌치의 길이 방향의 길이는 상기 게이트와 드레인을 합한 길이 이하이고, 상기 커넥터 및 통과 커넥터는 각각 일측벽이 수직형이고 타측벽이라운드형인 맨드릴(mandrel)구조로 되어 있고, 상기 게이트와 접촉하는 하부면이 1 최소 치수(one minimum dimension)의 약 1/4의 폭을 가지며, 자신들 사이에 1 최소 치수 이하의 공간을 가져, 상기 반도체 구조가 약 2½ 최소 치수의 길이 및 약 5평방 최소 치수의 면적을 가지는 반도체 구조 제조 방법.

#### 청구항 6

제5항에 있어서, 상기 커넥터는 워드라인이고, 상기 통과 커넥터는 통과 워드라인이며, 상기 반도체 구조는 DRAM 셀인 반도체 구조 제조 방법.

#### 청구항 7

제5항에 있어서, 상기 게이트 도체의 상기 개별적인 세그먼트의 길이 및 폭이 각각 약 1 최소 치수인 반도체 구조 제조 방법.

#### 도면

## 도면1

## 도면2

도면3

도면4

도면5

도면6

도면7