(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6478488号 (P6478488)

(45) 発行日 平成31年3月6日(2019.3.6)

(24) 登録日 平成31年2月15日(2019.2.15)

(51) Int. CL. FLнозм 1/56 (2006, 01) нозм 1/56 нозм 1/16 (2006, 01)нозм 1/16 Α 5/378 HO4N (2011.01) H04N 5/378

請求項の数 16 (全 19 頁)

||(73)特許権者 000001007 (21) 出願番号 特願2014-125206 (P2014-125206) (22) 出願日 平成26年6月18日 (2014.6.18) キヤノン株式会社 (65) 公開番号 特開2016-5171 (P2016-5171A) 東京都大田区下丸子3丁目30番2号 (43) 公開日 ||(74)代理人 100094112 平成28年1月12日(2016.1.12) 平成29年6月15日 (2017.6.15) 審查請求日 弁理士 岡部 讓 |(74)代理人 100101498 弁理士 越智 隆夫 (74)代理人 100106183 弁理士 吉澤 弘司 (74)代理人 100128668 弁理士 齋藤 正巳

(72) 発明者 橋本 誠二

東京都大田区下丸子3丁目3〇番2号 キャルン株式会社中

ヤノン株式会社内

最終頁に続く

## (54) 【発明の名称】 A D変換装置及び固体撮像装置

### (57)【特許請求の範囲】

## 【請求項1】

アナログ信号をデジタル信号に変換するAD変換装置であって、

時間の経過に伴い電圧が変化する、第1のランプ信号及び第2のランプ信号を出力する 参照信号発生回路と、

前記参照信号発生回路から共通の前記第1のランプ信号及び共通の前記第2のランプ信号が入力される、複数の回路部と

を備え、

前記複数の回路部の各々は、前記アナログ信号の電圧と前記第1のランプ信号の電圧と の比較を行う比較回路を含み、

前記AD変換装置は、前記比較に基づくデジタルデータを生成して出力する制御回路をさらに備え、

前記複数の回路部の各々は、前記デジタルデータに基づく比較基準電圧をデジタルアナログ変換によって生成するとともに、前記比較基準電圧から、前記第2のランプ信号の電圧の変化によって、時間の経過に伴って電圧が変化する信号を生成し、前記信号を前記比較回路に出力するデジタルアナログ変換器をさらに含み、

前記 A D 変換装置は、経過時間を計測することによりカウント値を生成するカウンタを さらに備え、

前記比較回路は、前記アナログ信号の電圧と前記デジタルアナログ変換器から出力される前記信号の電圧との比較をさらに行い、

前記カウンタは、前記第1のランプ信号の電圧の時間の経過に伴う変化が開始してから、前記比較回路に入力される前記アナログ信号の電圧と前記第1のランプ信号の電圧との大小関係が変化するまでの時間を計測することにより第1のカウント値を取得し、

前記デジタルデータは、前記第1のカウント値に基づく値を有し、

前記第1のランプ信号は前記第2のランプ信号よりも電圧の時間変化率が大きく、

前記AD変換装置が出力する前記デジタル信号は、前記アナログ信号の電圧と前記第1

のランプ信号の電圧との比較に基づく前記デジタルデータを少なくとも含む

ことを特徴とするAD変換装置。

## 【請求項2】

前記カウンタは、前記第2のランプ信号の電圧の時間の経過に伴う変化が開始してから、前記比較回路に入力される前記アナログ信号の電圧と前記第2のランプ信号の電圧との大小関係が変化するまでの時間を計測することにより第2のカウント値を取得することを特徴とする請求項1に記載のAD変換装置。

### 【請求項3】

前記アナログ信号は、前記第1のカウント値に基づくデジタルデータを上位ビットとし、前記第2のカウント値に基づくデジタルデータを下位ビットとして組み合わせることによりデジタル信号に変換されることを特徴とする請求項2に記載のAD変換装置。

## 【請求項4】

前記比較回路は、前記アナログ信号が入力される一方の入力端子と、前記デジタルアナログ変換器の出力信号と前記参照信号発生回路の出力信号とのいずれかが選択的に入力されるよう構成された他方の入力端子とを有し、

前記参照信号発生回路から前記第1のランプ信号が前記比較回路に入力されるように前記参照信号発生回路が選択されたとき、前記比較回路は、前記アナログ信号と前記第1のランプ信号とを比較することを特徴とする請求項1に記載のAD変換装置。

### 【請求項5】

前記比較回路は、前記アナログ信号が入力される一方の入力端子と、前記デジタルアナログ変換器からの出力信号が入力されるよう構成された他方の入力端子とを有し、

前記参照信号発生回路から出力される前記第1のランプ信号が、前記デジタルアナログ変換器を介して前記比較回路に入力されたとき、前記比較回路は、前記アナログ信号と前記第1のランプ信号とを比較することを特徴とする請求項1に記載のAD変換装置。

#### 【請求項6】

前記比較回路は、前記アナログ信号及び前記デジタルアナログ変換器の出力信号が入力される一方の入力端子を有し、

前記比較回路の他方の入力端子と前記比較回路の出力端子との間に接続されたスイッチと、

前記比較回路の他方の入力端子に一端が接続された容量素子とをさらに含み、

前記容量素子の他端に前記第1のランプ信号が入力されたとき、前記比較回路は、前記アナログ信号と前記第1のランプ信号とを比較することを特徴とする請求項1に記載のAD変換装置。

### 【請求項7】

前記スイッチをオンにした状態で、前記アナログ信号を前記比較回路に入力して、前記容量素子に前記比較回路のオフセット電圧を保持し、

その後、前記スイッチをオフにした後に、前記比較回路に前記第1のランプ信号が入力されることを特徴とする請求項6に記載のAD変換装置。

#### 【請求項8】

前記制御回路は、前記第1のカウント値を少なくとも1ビット、シフトした値を上位ビットの値とすることを特徴とする請求項3、4、5及び7のいずれか1項に記載のAD変換装置。

### 【請求項9】

前記比較回路が前記アナログ信号の電圧と前記第1のランプ信号の電圧との比較を行う

10

20

30

40

前に、前記比較回路は、前記アナログ信号を供給する信号源の基準信号と、前記第2のランプ信号を比較して、基準信号をデジタル信号に変換することを特徴とする請求項1に記載のAD変換装置。

#### 【請求項10】

前記基準信号と前記第2のランプ信号の比較において、前記第2のランプ信号にはオフセット電圧が付加されていることを特徴とする請求項9に記載のAD変換装置。

#### 【 請 求 項 1 1 】

前記第2のランプ信号は第1のランプ信号を分圧することによって生成されることを特徴とする請求項1に記載のAD変換装置。

#### 【請求項12】

前記アナログ信号の電圧と前記第1のランプ信号の電圧との比較を行う前に、前記デジタルアナログ変換器は、最上位ビットの値を1にして発生させた電圧を前記比較回路に入力して前記アナログ信号と比較させることにより、前記アナログ信号の最上位ビットの値を決定することを特徴とする請求項5に記載のAD変換装置。

#### 【請求項13】

前記デジタルアナログ変換器は、バイナリウェイトの容量値が設定された複数の容量素子を有する容量型のデジタルアナログ変換器であることを特徴とする請求項 1 に記載の A D 変換装置。

### 【請求項14】

前記デジタルアナログ変換器は、第1の抵抗値を有する抵抗素子と、第1の抵抗値の2 倍の抵抗値を有する抵抗素子がラダー型に接続されたR-2Rラダー型のデジタルアナロ グ変換器であることを特徴とする請求項1に記載のAD変換装置。

#### 【請求項15】

入射された光に応じたアナログ信号を出力する画素部と、

前記アナログ信号をデジタル信号に変換する請求項1乃至<u>14</u>のいずれか1項に記載のAD変換装置と

を備えることを特徴とする固体撮像装置。

#### 【請求項16】

入射された光に応じたアナログ信号を出力する画素部と、

前記アナログ信号をデジタル信号に変換する請求項1乃至<u>14</u>のいずれか1項に記載のAD変換装置と、

前記デジタル信号の処理を行う信号処理部と

を備えることを特徴とする撮像システム。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、AD変換装置及びそれを搭載した固体撮像装置に関する。

## 【背景技術】

### [0002]

AD変換装置の低消費電力化のための技術として、上位ビットを取得後に下位ビットを取得する2ステップAD変換手法がある(特許文献1)。特許文献1のAD変換装置は、画素信号と階段波状の参照信号とを比較し、比較器の出力電圧が反転するまでのカウント値を上位ビットとする。その後、スイッチを非導通にすることによりこの参照信号を遮断し、その時点の参照信号の電圧を第1の容量素子C1に保持する。次に、保持された電圧に、第2の容量素子C2を介して前述の参照信号よりもステップ幅が小さな参照信号を重置させることで得られた電圧を比較器に入力する。この電圧を画素信号と比較して、比較器の出力電圧が反転するまでのカウント値を下位ビットとする。このようにして2ステップAD変換を実現する技術が特許文献1に開示されている。

## 【先行技術文献】

### 【特許文献】

50

20

10

30

30

#### [0003]

【特許文献1】特開2002-23291号公報

## 【発明の概要】

【発明が解決しようとする課題】

### [0004]

特許文献1に記載されたAD変換装置においては、上位ビットを取得するための参照信号を供給する信号線と、下位ビットを取得するための参照信号を供給する信号線とをスイッチによって切り替える構成となっている。このスイッチを切り替える際に、第1の容量素子C1に保持された信号にスイッチの遮断ノイズが混入する場合がある。第1の容量素子C1に保持された信号は上位ビットを取得する際の比較信号として用いられるので、遮断ノイズは変換精度を劣化させる要因となり得る。したがって、特許文献1に記載されたAD変換装置は変換精度が不十分である場合がある。

### [0005]

本発明は、上述した課題に鑑みてなされたものであって、高精度なAD変換を実現するAD変換装置を提供することを目的とする。

【課題を解決するための手段】

### [0006]

本発明の一態様に係るAD変換装置は、アナログ信号をデジタル信号に変換するAD変 換装置であって、時間の経過に伴い電圧が変化する、第1のランプ信号及び第2のランプ 信号を出力する参照信号発生回路と、前記参照信号発生回路から共通の前記第1のランプ 信号及び共通の前記第2のランプ信号が入力される、複数の回路部とを備え、前記複数の 回路部の各々は、前記アナログ信号の電圧と前記第1のランプ信号の電圧との比較を行う 比較回路を含み、前記AD変換装置は、前記比較に基づくデジタルデータを生成して出力 する制御回路をさらに備え、前記複数の回路部の各々は、前記デジタルデータに基づく比 較基準電圧をデジタルアナログ変換によって生成するとともに、前記比較基準電圧から、 前記第2のランプ信号の電圧の変化によって、時間の経過に伴って電圧が変化する信号を 生成し、前記信号を前記比較回路に出力するデジタルアナログ変換器をさらに含み、前記 AD変換装置は、経過時間を計測することによりカウント値を生成するカウンタをさらに 備え、前記比較回路は、前記アナログ信号の電圧と前記デジタルアナログ変換器から出力 される前記信号の電圧との比較をさらに行い、前記カウンタは、前記第1のランプ信号の 電圧の時間の経過に伴う変化が開始してから、前記比較回路に入力される前記アナログ信 号の電圧と前記第1のランプ信号の電圧との大小関係が変化するまでの時間を計測するこ とにより第1のカウント値を取得し、前記デジタルデータは、前記第1のカウント値に基 づく値を有し、前記第1のランプ信号は前記第2のランプ信号よりも電圧の時間変化率が 大きく、前記AD変換装置が出力する前記デジタル信号は、前記アナログ信号の電圧と前 記第1のランプ信号の電圧との比較に基づく前記デジタルデータを少なくとも含むことを 特徴とする。

### 【発明の効果】

## [0007]

本発明によれば、高精度なAD変換を実現するAD変換装置を提供することができる。 【図面の簡単な説明】

[0008]

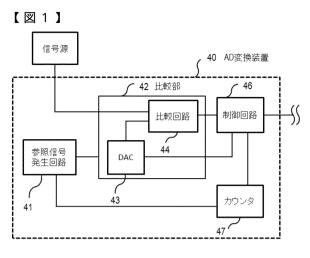

【図1】第1実施形態のAD変換装置の構成を示す図である。

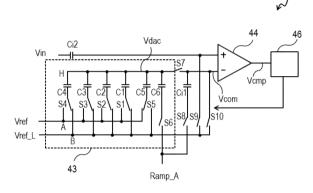

【図2】第2実施形態のAD変換装置の構成を示す図である。

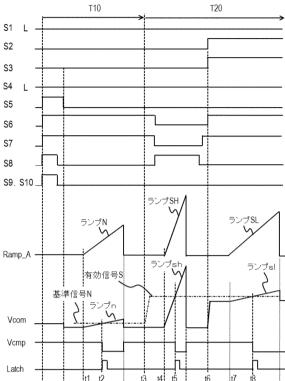

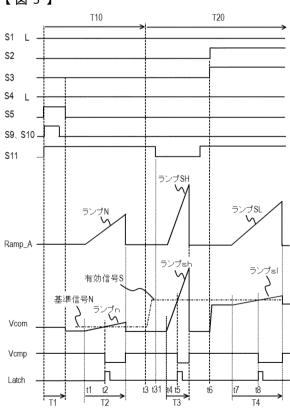

【図3】第2実施形態に係る駆動タイミングを示す図である。

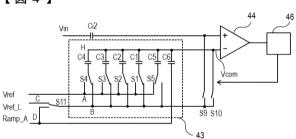

【図4】第3実施形態のAD変換装置の構成を示す図である。

【図5】第3実施形態に係る駆動タイミングを示す図である。

【図6】第4実施形態のAD変換装置の構成を示す図である。

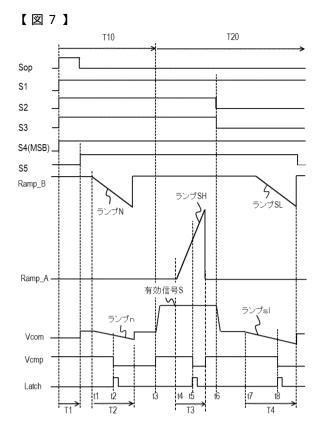

【図7】第4実施形態に係る駆動タイミングを示す図である。

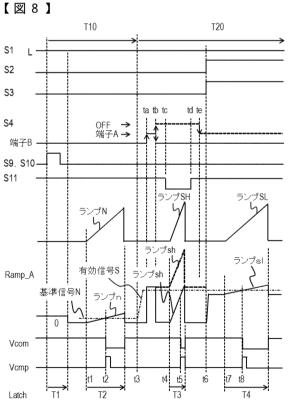

【図8】第5実施形態に係る駆動タイミングを示す図である。

10

20

30

40

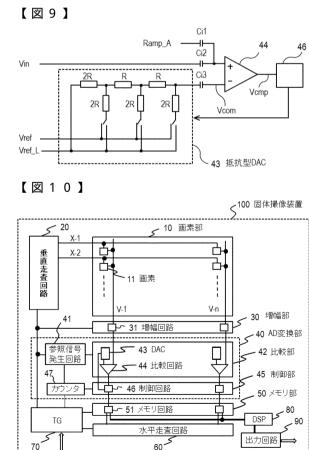

- 【図9】第6実施形態のAD変換装置の構成を示す図である。

- 【図10】第7実施形態の固体撮像装置の構成を示す図である。

- 【図11】第8実施形態の撮像システムの構成を示す図である。

【発明を実施するための形態】

### [0009]

図面を参照しつつ本発明の実施形態を説明する。各実施形態の図面において、同様な機能を有する要素には同一の符号を付し、重複した説明を省略することもある。

## [0010]

#### (第1実施形態)

図1は、本発明の第1実施形態に係るAD変換装置40の構成を示す図である。第1実施形態のAD変換装置40は、光電変換素子などの信号源から入力されるアナログ信号をデジタル信号に変換する回路であり、参照信号発生回路41、比較部42、制御回路46及びカウンタ47を含む。

## [0011]

参照信号発生回路 4 1 は、電圧が時間的に変化する参照信号を発生する。参照信号は入力されるアナログ信号の電圧との比較に用いられる信号であり、例えば時間に対して単調に電圧が増加又は減少するランプ信号などの信号を用いることができる。

#### [0012]

比較部42は、アナログ信号と参照信号を比較して比較結果に基づく信号を出力する回路であり、入力された信号電圧の大小関係を比較して、それに応じた電圧を出力する比較回路44とデジタルアナログ変換器43(以降、DACと呼ぶ)とを含む。比較回路44は、例えば、2つの入力端子と1つの出力端子を有し、一方の入力端子と他方の入力端子の電圧を比較してハイレベル又はローレベルの2値のいずれかの電圧信号を出力する、比較器を用いて構成可能である。

#### [0013]

カウンタ47は、参照信号の電圧変化が開始する時刻からの経過時間をカウントし、制御回路46に出力する。制御回路46は、カウンタ47から取得するカウント値に基づく制御信号を生成して比較部42に送信することにより、比較部42を制御する。

## [0014]

A D 変換装置 4 0 は、低分解能な変換を実行してデジタル信号の上位ビットを取得する 第 1 の A D 変換と、高分解能な変換を実行してデジタル信号の下位ビットを取得する第 2 の A D 変換との 2 段階の A D 変換を行う。すなわち、 A D 変換により得られるデジタルデータは低分解能な上位ビットと高分解能な下位ビットからなるデータである。

#### [0015]

AD変換装置40は、入力されるアナログ信号と参照信号発生回路41からの第1の参照信号との電圧を比較し、これらの大小関係を示す信号を制御回路46に出力する。制御回路46は、カウンタ47からカウント値を取得することにより、2つの信号の電圧の大小関係が反転するまでの時間を第1のカウント値として計測する。このようにして第1のAD変換が行われる。

### [0016]

次に、制御回路46から第1のカウント値に基づく制御信号がDAC43に入力される。DAC43は、少なくとも1つのサブレンジに対応するDAC電圧を、上位ビットの電圧レベルを示す比較基準電圧として比較回路44に出力する。サブレンジは、ここでは、第1のAD変換における1LSB相当の電圧範囲をもつ。仮に第1のAD変換がnビットで行われる場合には、第1のAD変換において変換できるアナログ信号の大きさの範囲の1/2°が、1つのサブレンジの大きさである。この時点において、参照信号発生回路41は、第1の参照信号よりも電圧の時間変化率が小さい第2の参照信号を出力する。比較回路44は、DAC電圧に第2の参照信号を重畳した信号と、アナログ信号とを比較し、その大小関係を示す信号を制御回路46に出力する。制御回路46は、再びカウンタ47からカウント値を取得することにより、2つの信号電圧の大小関係が反転するまでの時間

40

10

20

30

を第2のカウント値として計測する。このようにして第2のAD変換が行われる。

## [0017]

AD変換装置40は、以上のようにしてアナログ信号に対し第1及び第2のAD変換を行うことにより、第1及び第2のカウント値に変換する。第1のカウント値を上位ビットのデータとし、第2のカウント値を下位ビットのデータとして組み合わせることにより、AD変換後のデジタル信号が取得される。

#### [0018]

DAC43は、例えば、複数の容量素子とスイッチを有する容量型、複数の抵抗とスイッチを有する抵抗型などの種々のデジタルアナログ変換の機能を有する回路により構成することができる。

## [0019]

上述したように、本発明の第1実施形態に係るAD変換装置40は、入力されたアナログ信号と第2の参照信号との比較のために、比較基準電圧をDAC43で発生させてAD変換を行う。

#### [0020]

本実施形態では、上位ビットに対応する比較基準電圧をDAC43から供給しているため、スイッチ遮断ノイズは比較基準電圧に重畳しない。したがって、ノイズの影響が抑制され、精度の良いAD変換を実現することができる。

#### [0021]

### (第2実施形態)

図2は、本発明の第2実施形態に係るAD変換装置40の構成を示す図である。本実施形態は、複数の容量素子とスイッチを有する容量型のDAC43を用いたAD変換装置40であり、第1実施形態のDAC43の構成をより具体化したものである。本実施形態の説明においてDAC43に入力される参照信号をランプ信号Ramp\_Aとする。また、AD変換装置40は、入力されるアナログ信号電圧Vinを上位4ビット、下位8ビットのデジタルデータに変換する構成とするが、ビット数はこれに限定されず適宜変更可能である。なお、図2において、参照信号発生回路41及びカウンタ47については記載を省略している。

## [0022]

比較回路44は非反転入力端子、反転入力端子及び出力端子を有する差動入力型の比較器である。非反転入力端子には信号源から容量素子Ci2を介してアナログ信号電圧Vinが入力され、反転入力端子にはDAC電圧Vdacにランプ信号Ramp\_Aが重畳された入力電圧Vcomが入力される。

## [ 0 0 2 3 ]

DAC43は容量素子C1~C6及びスイッチS1~S6を有する容量型のデジタルアナログ変換器である。スイッチS1~S5は、一端が回路上の配線に常時接続され、他端は回路上の2接点のいずれかを選択的に接続できるように構成された単極双投スイッチである。スイッチS6はオン(接続)又はオフ(非接続)が選択可能な単極単投スイッチである。容量素子C1~C6の一端は接続点Hに共通接続され、他端はスイッチS1~S6の常時接続されている側にそれぞれ接続される。スイッチS1~S5の他端は端子Aと端子Bのどちらか一方に選択的に接続されるよう構成されている。スイッチS6の他端にはランプ信号Ramp\_Aが入力される。端子Aには基準電圧Vrefが、端子Bには基準電圧Vrefより小さい電圧である基準電圧Vrefが、それぞれ参照信号発生回路41から供給される。容量素子C1~C6の接続点HがDAC43の出力端子となっており、その出力端子から出力されるDAC電圧Vdacの範囲はVrefからVref\_Lの間の値となる。

#### [0024]

AD変換装置40は容量素子Ci1及び単極単投スイッチS7~S10をさらに有する。スイッチS7はDAC43の出力端子と比較回路44の反転入力端子の間に接続される。スイッチS9は端子Bと比較回路44の非反転入力端子の間に接続され、スイッチS1

10

20

30

40

0は端子Bと比較回路44の反転入力端子の間に接続される。容量素子Ci1の一端は比較回路44の反転入力端子に接続され、他端はスイッチS8に接続される。

### [0025]

容量素子C1~C4の容量値は順に、1C、2C、4C、8Cであり、バイナリウェイトの容量値になっている。すなわち、各スイッチが端子Aに接続されている場合を「1」、端子Bに接続されている場合を「0」とすれば、これらの値を組み合わせて各位の値を表現した2進数により、合成容量値が表現できるように構成されている。容量素子C4が最上位ビット(MSB:Most Significant Bit)に対応し、容量素子C1が最下位ビット(LSB:Least Significant Bit)に対応する。例えば、スイッチS2とS3が「1」でスイッチS1とS4が「0」のとき、各スイッチのオンオフを表現する2進数は0110(10進数では6)となる。これは合成容量値が6Cであることに対応している。

#### [0026]

このようにして、 DAC43は各スイッチの接続端子を端子A又は端子Bのいずれかから選択して4ビット、ずなわち、 $2^4 = 16$ 種類の容量値を選択可能である。よって、 DAC43は入力されたデジタルデータに応じた 16種類の DAC電圧 Vdacを比較回路 44へ入力することができる。

## [0027]

容量素子 C 5 は、アナログ信号電圧 V i n との比較が可能になるように D A C 電圧 V d a c にオフセット電圧を付加するために設けられている。容量素子 C 5 の容量値は、比較回路 4 4 にサブレンジの半分のオフセット電圧を付加するため、 C / 2 とする。

#### [ 0 0 2 8 ]

次に図3のタイミング図を参照して本実施形態のAD変換動作を説明する。図3には、スイッチS1からS10を駆動する制御信号の動作タイミングと、ランプ信号Ramp\_Aと、入力電圧Vcomと、出力電圧Vcmpと、ラッチ信号Latchの変化が示されている。出力電圧Vcmpがハイレベルからローレベルに変化すると、制御回路46はラッチ信号Latchを発生する。これによりその時点のカウント値が制御回路46の後段のメモリにデジタルデータとして取り込まれる。一点鎖線により入力電圧Vcomと重ねて描画されている基準信号N及び有効信号Sは信号源から出力されるアナログ信号電圧Vinの変化を示している。

## [0029]

期間T10は基準信号N(例えば、信号源のオフセット電圧など)の供給期間であり、 期間T20は基準信号Nに重畳された有効信号Sの供給期間である。

## [0030]

期間T10内の期間T1はAD変換装置40の初期化期間であり、期間T2は基準信号NのAD変換期間(N AD変換期間)である。期間T20内の期間T3は有効信号SをAD変換する第1のAD変換期間、時刻t6はDAC電圧Vdacが比較回路44の反転入力端子に入力される時刻、期間T4はDAC電圧Vdacと有効信号Sの電圧差をAD変換する第2のAD変換期間である。

### [0031]

ランプ信号 R a m p \_ A は時間に対し電圧の傾きが正である 3 つの電圧傾斜部(ランプ)を有する波形である。期間 T 2 における電圧変化をランプ N 、期間 T 3 における電圧変化をランプ S L とする。またこのときの出力電圧 V c o m の変化をそれぞれランプ n 、ランプ s h 、ランプ s l とする。

#### [0032]

スイッチ S 8 がオン、スイッチ S 6 、 S 7 がオフのとき、スイッチ S 8 に接続された容量素子 C i 1 にランプ S H が入力される。このとき、比較回路 4 4 の反転入力端子に供給される電圧の変化がランプ s h である。ランプ s h は第 1 の A D 変換時に参照信号として用いられる。ランプ S H の電圧変化期間における最大値と最小値の幅(以下振幅と呼ぶ)は、アナログ信号電圧 V i n の A D 変換のダイナミックレンジに相当する基準電圧 V r e

10

20

30

40

20

30

40

50

fと基準電圧Vref Lの電圧差とほぼ同じ値に設定される。

#### [0033]

スイッチS8がオフ、スイッチS6、S7がオンのとき、容量素子C6にランプN又はランプSLが入力される。このとき、比較回路44の反転入力端子に供給される電圧の変化がランプn又はランプs1である。ランプnとランプs1は、容量素子C6が容量素子C1~C5の合成容量により比率(C6/(C1+C2+C3+C4+C5+C6))で分圧された振幅になる。容量素子C6の容量値を1Cとすると、ランプnとランプs1の振幅は、それぞれランプNとランプSLの約1/16になり、サブレンジの振幅とほぼ同じになる。ランプs1の振幅は理想的にはサブレンジ幅と一致していれば良い。しかしながら、振幅とサブレンジ幅が完全に一致している場合、DAC電圧の設定精度及びサブレンジ間の境界領域で誤差が発生する可能性がある。そのため、本実施形態では第2のAD変換期間を長くして振幅に余裕をもたせることにより、サブレンジ幅をカバーする範囲でAD変換が行われるように設定している。

## [0034]

スイッチS9、S10は比較部42の初期化のためのスイッチである。スイッチS9、S10がオンになると、比較回路の各入力端子とDAC43がいずれも端子Bと接続され、基準電圧Vref\_Lにリセットされる。

#### [0035]

ランプ信号Ramp\_AとAD変換期間のカウント周波数について述べる。N-AD期間T2と第2のAD変換期間T4において、ランプnとランプs1の時間変化率(傾き)は同じであり、またそれぞれのカウンタクロックCLKは同一周波数とする。クロック周波数を同一にすることで、AD変換で得られたデータは同一の分解能として取り扱うことができる。第1のAD変換期間T3のランプshの傾きを第2のAD変換期間T4のランプs1の傾きの4倍とし、第1のAD変換期間T3のカウンタクロックCLK2は第2のAD変換のカウンタクロックCLKの4分の1の周波数としている。なお、ランプshの傾きを大きくし、同程度の比率でカウンタクロックCLK2を高周波化することにより、第1のAD変換期間T3におけるAD変換の速度を高速化することもできる。

#### [0036]

次に各動作タイミングにおける各スイッチの動作を説明する。タイミング図においてスイッチS1~S5は制御信号電圧がローレベルのときに端子Bに接続され、ハイレベルのときに端子Aに接続されるものとする。またスイッチS6~S10は制御信号電圧がハイレベルのときにオン、ローレベルのときにオフになるものとする。

#### [0037]

期間T1の初期において、スイッチS6~S10はオンであり、DAC43のスイッチS1~S4は端子Bに、スイッチS5は端子Aに接続される。このとき、比較回路44の非反転入力端子には基準電圧Vref\_Lが入力される。これにより、比較回路44の入力端子は基準電圧Vref\_Lにクランプされる。また、容量素子C5には電圧(Vref.Vref\_L)が印加され、電荷が蓄積される。

## [0038]

## [0039]

その後、スイッチS8~S10がオフになり、これに続いてスイッチS5が端子Aから端子Bに切り替わる。容量素子C5に蓄積された電荷により、入力電圧Vcomにサブレンジの1/2の大きさに相当する負のオフセット電圧(-31.25mV)が付加され、N AD変換のためのAD変換装置40の初期化が完了する。

### [0040]

期間T2の時刻t1において、ランプnの変化が開始する。時刻t2において、ランプ

nの電圧が基準信号Nの電圧(0V)を超えて比較結果が反転すると、ラッチ信号Latchのパルスにより、t1からt2まで期間にカウントされたカウント値が制御回路46の後段のメモリに保存される。このカウント値が基準信号Nの下位ビット用のデジタルデータとなる。

## [0041]

時刻 t 3 において、信号源から有効信号 S が比較回路 4 4 に入力される。以下、有効信号 S の信号電圧が 4 2 0 m V であるものとする。時刻 t 4 において、有効信号 S とランプ s h を比較処理する第 1 の A D 変換が開始される。ランプ s h が 4 2 0 m V を超えた時刻 t 5 において、比較回路 4 4 の出力電圧 V c m p のレベルが反転し、比較回路 4 4 はラッチ信号 L a t c h のパルスを発生する。

[0042]

上述のように第1のAD変換で取得される上位ビットのデータは4ビットなので、アナログ信号は2進数0000~1111に変換される。これらの2進数にはアナログ電圧値が62.5mV刻みで割り振られる。例えば、2進数0110(10進数では6に相当)は、62.5mV×6=375mVに対応し、2進数0111(10進数では7に相当)は、62.5mV×7=437.5mVに対応する。有効信号Sの信号電圧は420mVなので、出力電圧Vcmpのレベルが反転する時刻t5におけるカウント値(第1のカウント値)は0111(437.5mVに相当)である。

[0043]

その後、第1のカウント値は1LSB分ビットシフトされてから、上位ビットデータとして制御回路46の次段のメモリに保持される。すなわち、上位ビットデータの値は0111を1ビットシフトした0110となる。第1のAD変換期間T3の終了後、スイッチS8がオフになり、続いてスイッチS7がオンになり、その後時刻t6において、スイッチS6もオンになる。これにより、DAC電圧が比較回路44に入力され、第2のAD変換を行う準備が完了する。同時刻において、制御回路46は、上位ビットデータ0110に対応するようにDAC43の各スイッチS4~S1を制御する。上述のように各スイッチS4~S1が上位ビットデータの各位の値にそれぞれ対応しているので、本実施形態の場合、スイッチS1、S4がオフ、スイッチS2、S3がオンになる。この結果、DAC43の出力であるDAC電圧は375mVになる。

[0044]

時刻 t 7 において、ランプ s 1 が D A C 電圧に重畳され、有効信号 S の第 2 の A D 変換が開始される。これにより、上位ビットデータ 0 1 1 0 に対応する 3 7 5 m V と、 0 1 1 1 に対応する 4 3 7 . 5 m V との間の 1 サブレンジでの高精度な A D 変換が行われる。その後時刻 t 8 で比較回路 4 4 の出力電圧 V c m p のレベルが反転すると、時刻 t 8 の時点でのカウント値(第 2 のカウント値)が 8 ビットの下位ビットデータとして同様に保持される。

[0045]

その後、第1のAD変換で得られた上位ビットデータ0110と第2のAD変換で得られた下位8ビットのデータを合成すると12ビットのAD変換データが得られる。この12ビットの有効信号Sのデータと下位ビットである基準信号Nのデータとの差分を取得する処理を行うことで、信号源のノイズ、比較回路のオフセット電圧等の基準信号Nの影響を除去したデジタルデータが取得できる。

[0046]

カウンタ信号を 1 クロックずらしてカウントすることにより、第 1 のカウント値をシフトする処理を省略して、出力電圧 V c m p のレベルが反転した時点のカウント値を直接 D A C 4 3 に入力しても良い。

[0047]

本実施形態のAD変換装置40は固体撮像装置の画素部の列ごとに備えられる信号読み出し回路(列回路)に適用することができる。列回路の列数は固体撮像装置の画素部の水平方向の画素数によって決定され、例えば数千の列数である。このように列数が多い場合

10

20

30

40

20

30

40

50

、カウンタ信号の遅延又は比較回路 4 4 の反転タイミングのバラツキが生じる可能性がある。この問題が生じうる場合、 D A C 4 3 への入力データをサブレンジ 2 つ分シフトして、さらに A D 変換期間を長くすることにより、 2 つのサブレンジ幅による第 2 の A D 変換を行っても良い。あるいは、 D A C のキャリブレーション電圧に負のオフセット電圧を付加することで第 2 の A D 変換の変換レンジをシフトしても良い。

#### [0048]

本実施形態では、第1のAD変換で得られた電圧を容量型のDAC43を用いて第2のAD変換時に重畳させるように構成している。したがって、AD変換の参照信号を切り替える際のスイッチの遮断ノイズが保持容量に保持されるというメカニズムによる精度劣化は抑制されている。よって、本実施形態のAD変換装置40によれば、高精度なAD変換が実現される。また、第2のAD変換範囲を一つのサブレンジ幅より広く設定した場合には、サブレンジ境界がAD変換精度に与える影響を低減する効果も得られる。

#### [0049]

本実施形態では参照信号としてランプ信号Ramp\_Aを例示したが、電圧が階段状に変化する階段波を参照信号として用いてもよい。他の実施形態においても同様である。

#### [0050]

### (第3実施形態)

図4は、本発明の第3実施形態に係るAD変換装置40の構成を示す図であり、図5は第3実施形態に係るAD変換装置40の動作タイミング図である。本実施形態は第2実施形態に対して、第1のAD変換に用いられるスイッチ及び容量素子の構成と動作タイミングを変更したことにより、ランプ信号の生成方法が異なっている。より具体的には、第1のAD変換において、第2実施形態では容量素子Ci1を介してランプ信号を入力しているが、本実施形態ではDAC43の全体の合成容量を介してランプ信号を入力する点が差異点である。他の動作は同じであるので、重複する部分の説明は省略する。

#### [0051]

第3実施形態に係るAD変換装置40は、第2実施形態に対し、スイッチS6、S7、S8及び容量素子Ci1を備えておらず、スイッチS11を追加した構成となっている。スイッチS11は、ランプ信号Ramp\_Aを供給する配線と、基準信号Vref\_Lを供給する配線とのどちらにDAC43の入力端子を接続するかを選択する単極双投スイッチである。スイッチS11は、第1のAD変換期間において、ランプshをDAC43の端子Bに入力することにより、比較回路44に供給するために用いられる。なお、DAC43の入力である端子Bは、スイッチS11の制御信号がハイレベルのときに端子Cに接続され、ローレベルのときに端子Dに接続されるものとする。

## [0052]

### [0053]

時刻 t 3 1 において、S 1 1 の接続が端子 C から端子 D に切り替わる。これにより、各容量素子 C 1 ~ C 5 は全て端子 D に接続され、D A C 4 3 にはランプ信号 R a m p \_\_ A が入力される。時刻 t 4 において、ランプ信号 R a m p \_\_ A の電圧の変化(ランプ S H)が開始されると、ランプ S H が各容量素子 C 1 ~ C 5 を介して、比較回路 4 4 の反転入力端子に入力される。これにより、第 1 の A D 変換が行われる。第 1 の A D 変換が完了した後、スイッチ S 1 1 は端子 C、すなわち基準電圧 V r e f \_\_ L に再び接続される。これ以降の動作は第 2 実施形態と同様である。

## [0054]

本実施形態では、第2実施形態と同様の効果が得られるとともに、第2実施形態のスイッチS7、S8及び容量素子Ci1を省略することができるので、AD変換装置40を小型化することができる。また、DAC43と比較回路44の信号経路にはスイッチS7を有しないので、スイッチのオン、オフを切り替えることに起因するスイッチノイズの影響

20

30

40

50

が抑制される。

## [0055]

## (第4実施形態)

図6は、本発明の第4実施形態に係るAD変換装置40の構成を示す図であり、図7は第4実施形態に係るAD変換装置40の動作タイミングを示す図である。本実施形態のAD変換装置40は容量素子Coff及びスイッチSopを第2実施形態にさらに付加している。一方、第2実施形態の容量素子Ci1及びスイッチS7~S10は本実施形態のAD変換装置40には備えられていない。

#### [0056]

ランプ信号Ramp\_Aは容量素子Coffを介して比較回路44の反転入力端子に入力される。スイッチSopは単極単投スイッチであり、比較回路44の反転入力端子と出力端子の間に接続される。ランプ信号Ramp\_Bは容量素子C6を介して比較回路44の非反転入力端子に入力される。アナログ信号電圧Vinは容量素子Ci2を介してDAC43の接続点Hに入力され、DAC43の出力端子から比較回路44の非反転入力端子に入力される。なお、ランプ信号Ramp\_Bの電圧傾斜部の傾きは符号が異なっている。本実施形態では、ランプ信号Ramp\_Aは時間に対し単調増加するランプSHを有し、ランプ信号Ramp\_Bは時間に対し単調減少するランプN、SLを有するものとする。

## [0057]

前述の第2及び第3実施形態においては、アナログ信号電圧Vinが容量素子Ci2を介して比較回路44の非反転入力端子に入力され、DAC電圧が比較回路44の反転入力端子に入力される。これに対し、本実施形態では比較回路44の非反転入力端子にアナログ信号電圧VinとDAC電圧がともに入力される点が第2及び第3実施形態との差異点である。また、アナログ信号源から出力される基準信号N(以下、この電圧をVnとする。)と比較回路44のオフセット電圧を反転入力端子に接続された容量素子Coffに保持できるように構成されている。本実施形態の説明では、第1のAD変換のためのランプSHは反転入力端子に接続された容量素子Coffの一端から入力しているが、第2及び第3実施形態と同様に比較回路44の入力端子から入力するように変形しても良い。

## [0058]

図7を参照して本実施形態の動作タイミングを説明する。AD変換装置40の初期化期間T1の初期において、比較回路44のスイッチSopはオンである。このとき、比較回路44の反転入力端子と出力端子は短絡され、比較回路44はボルテージフォロワ回路を構成する。このとき、比較回路44の非反転入力端子にはアナログ信号源の基準電圧Nが入力されているため、容量素子Coffには、比較回路44のオフセット電圧に基準電圧Nが重畳された電圧Vdarkが入力される。その後、スイッチSopがオフになり、容量素子Coffに電圧Vdarkが保持される。また、このときDAC回路43の端子Aは基準電圧Vrefに接続されており、比較回路の入力電圧Vcomはアナログ信号の基準電圧Vrefに接続されており、比較回路、スイッチS5が端子Bから端子Aに切り替わる。これにより、入力電圧Vcomの電圧は、容量素子C5(容量値C/2)を介して入力される基準電圧Vrefにより上昇する

## [0059]

時刻 t 2 において、ランプ n が入力電圧 V c o mに重畳され、N - A D 変換が開始される。比較回路の反転入力端子には容量素子 C o f f により電圧 V d a r k が保持されているので、N - A D 変換は必須ではなく省略することも可能である。しかしながら、比較回路 4 4 の遅延及び特性変動による誤差が生じうるため、本実施形態のようにN - A D 変換を行うことが好ましい。

## [0060]

時刻t3において、アナログ信号の有効信号Sが比較回路44に入力される。そのときの入力電圧Vcomは420mVとする。時刻t4において、第1のAD変換の比較信号

20

30

40

50

であるランプSHが変化を開始し、時刻 t 5 において、比較回路 4 4 の出力電圧 V c m p のレベルが反転する。この時点でのカウント値である 2 進数のデータは 0 1 1 1 ( 1 0 進数では 7 ) であり、この 2 進数に対応する電圧値は 6 2 . 5 m V x 7 = 4 3 7 . 5 m V である。時刻 t 6 に、 2 進数 0 1 1 1 を 1 L S B 分ピットシフトした 2 進数 0 1 1 0 が D A C 4 3 に入力される。

#### [0061]

本実施形態では第1の実施形態とは逆に、各スイッチが端子Aに接続されている場合を「0」、端子Bに接続されている場合を「1」とした2進数により、合成容量値が表現されているものとする。DAC43にデータ0110が入力されると、スイッチS2、S3の接続先が端子Aから端子Bに切り替わる。これにより、容量素子C2、C3に入力される電圧はVrefからVref\_Lに変化する。DAC回路43の出力電圧は2進数0110(10進数では6)に対応した電圧値は62.5 mV×6=375 mVであることから、電位は420 mVから375 mVだけ低下する。したがって、比較回路44の入力電圧VcomはVn+45 mVとなる。

## [0062]

時刻 t 7 においてランプ s 1 の電圧変動が開始し、期間 T 4 において第 2 の A D 変換が行われる。時刻 t 8 において比較回路 4 4 の出力電圧 V c m p のレベルは反転し、その時のカウント値が下位の 8 ビットとして比較回路 4 4 の後段のメモリに保持される。

### [0063]

第1のAD変換で得られた上位ビットデータ0110と第2のAD変換で得られた下位8ビットのデータを合成すると12ビットのAD変換データが得られる。この12ビットの有効信号Sのデータと下位ビットである基準信号Nのデータとの差分を取得する処理を行うことで、オフセット電圧を除去したデジタルデータが取得できる。

#### [0064]

本実施形態では、アナログ信号の基準信号電圧Vnと比較回路44のオフセット電圧とを容量素子Coffに保持し、この電圧を基準にAD変換を行っているため、期間T1後、比較回路の入力電圧Vcomに重畳するオフセット電圧が小さくなる。そのため、第2実施形態及び第3実施形態と比較してランプnの期間が短縮される。

## [0065]

## (第5実施形態)

図8は、本発明の第5実施形態に係る動作タイミングを示す図である。本実施形態は第3実施形態と同様の回路構成においてスイッチS4の動作が異なっている。第3実施形態では、スイッチS4が端子A又は端子Bに切り替わることにより、容量素子C4に基準電圧Vref又は基準電圧Vref\_Lのいずれか一方が入力されるように構成されている。これに対し、本実施形態ではスイッチS4が端子A、端子Bへの接続に加えて、OFF状態を選択できるように構成される。

## [0066]

## [0067]

様であるため説明を省略する。なお、図8において、この場合の時刻tb以降のスイッチS4の動作タイミングと入力電圧Vcomの変化は破線で示されている。

### [0068]

入力電圧Vcomと有効信号Sの電圧の比較により、有効信号Sの電圧が500mV未満であった場合、有効信号SのMSBとしてデータ値「0」が取得され、時刻tbにおいてスイッチS4が端子Bに再び接続される。この結果、入力電圧Vcomは基準電圧Vref\_Lに降下する。第1のAD変換期間T3にランプshと有効信号Sとの比較処理が行われる。時刻t6以降の動作は第3実施形態の図5の動作タイミングと同様であるため説明を省略する。なお、図8において、この場合の時刻tb以降のスイッチS4の動作タイミングと入力電圧Vcomの変化は実線で示されている。

[0069]

以上のように、本実施形態では第1の段階として時刻taからtbの間の期間において有効信号Sの電圧が500mV以上であるかどうかを決定し、これに基づいてMSBのデータ値を決定する。その後、第1のAD変換期間T3でMSB以外の3ビットのデータを取得し、これとMSBのデータ値を合成することで上位ビットである4ビットのデジタルデータを取得することができる。

[0070]

本実施形態では、MSBのデータ取得がスイッチ<u>S</u>4の切り替えによって行われる。よって、第1のAD変換期間 T3において変換するビット数が第3の実施形態に対して1ビット少なくなるため、ランプ shの振幅が1/2になり、第1のAD変換期間 T3が1/2に短縮される。よって、AD変換の所要時間を短縮することができる。

[0071]

また、ランプshの振幅が小さいので、参照信号発生回路の消費電力が低減される。

[0072]

(第6実施形態)

図9は、本発明の第6実施形態に係るAD変換装置40の構成を示す図である。本実施形態ではDAC43の回路として、抵抗型DACが用いられている。DAC43は抵抗値R又はその2倍の抵抗値2Rの抵抗素子をラダー型に配列したR-2Rラダー型のデジタルアナログ変換回路を構成している。本実施形態では、DAC43は、抵抗値2Rの抵抗素子を4個、抵抗値Rの抵抗素子を2個有している。これらの抵抗はラダー型に配置されており、基準電圧Vref又は基準電圧Vref\_Lに接続される抵抗素子は抵抗値2R、それ以外の抵抗素子は抵抗値Rとしている。

[0073]

DAC43は3ビットの入力を有しており、3つの抵抗素子2Rの一端が3つのスイッチを介して基準電圧Vref又は基準電圧Vref\_Lに接続される。上述の第2乃至第5の実施形態と同様に、入力される2進数デジタルデータの各位のビット値に対応して各スイッチが切り替わる。スイッチの切り替えにより、ラダー型に配列された抵抗による入力電圧の分圧方法が変化するため、DAC43の入力電圧Vcomが変化する。本実施形態のDAC43の入力は3ビットなので、2³=8種類のDAC電圧を生成することが可能である。DAC43の出力電圧Vdacは容量素子Ci3を介して比較回路44の反転入力端子へ入力される。また、ランプ信号Ramp\_Aは容量素子Ci1を介して比較回路44の非反転入力端子へ入力され、入力電圧Vinは容量素子Ci2を介して同様に比較回路44の非反転入力端子へ入力される。動作タイミング及び入出力信号の電圧変化は上述の実施形態と同様であるため省略する。

[0074]

本実施形態においても第1のAD変換後にDAC電圧Vdacを保持する時に、DAC43と比較回路44の信号経路にスイッチS7を有しない。したがって、第3実施形態と同様にスイッチのオン、オフを切り替えることに起因するスイッチノイズの影響が抑制される。

[0075]

10

20

30

なお、DAC43のラダー型回路の段数を変更することにより、適宜入力可能なビット数を変更することができる。例えば、第2乃至第5の実施形態と同様に4ビットとしてもよい。

## [0076]

上述した第2乃至第6実施形態において、参照信号としてランプ信号Ramp\_Aが例示されているが、電圧が階段状に変化する階段波をランプ信号Ramp\_Aに替えて参照信号として用いてもよい。

## [0077]

### (第7実施形態)

図10は第1乃至第6実施形態のAD変換装置40を搭載した固体撮像装置の構成を示す図である。固体撮像装置100は、画素部10、垂直走査回路20、増幅部30、AD変換部40、メモリ部50、水平走査回路60、TG(タイミング発生回路)70、DSP(デジタルシグナルプロセッサ)80及び出力回路90を含む。本実施形態のAD変換部40として、上述の第1乃至第6実施形態のAD変換装置40を用いることができる。

#### [0078]

画素部10は行列状に配置された複数の画素11を有する。画素11は、入射された光量に応じて生成された電荷を電圧信号に変換して出力する回路である。画素11は、画素回路のリセット時の基準信号N(すなわち入射光による信号を含まないノイズ成分)と、生成された電荷に対応する有効信号Sとを出力する。垂直走査回路20からの駆動信号(X・1、X・2・・・)によって画素信号の読み出しを行う画素行が順次選択される。画素11から出力される画素信号は列ごとに垂直信号線(V・1・・・V・n)を介して、増幅部30に設けられた増幅回路31に伝送される。

#### [0079]

増幅部30に入力された画素信号は撮影感度に応じて増幅され、AD変換部40へ入力される。AD変換部40は参照信号発生回路41、比較部42、制御部45及びカウンタ47を含む。比較部42は画素列ごとに備えられたDAC43、比較回路44を有し、制御部45は画素列ごとに備えられた制御回路46を有する。これにより、AD変換部40は増幅部30から入力された信号のAD変換が並行して行われる。

## [0800]

参照信号発生回路 4 1 から出力されるランプ信号 R a m p \_\_ A とカウンタ 4 7 から出力されるカウンタ信号は各列に共通に供給される。制御回路 4 6 から出力されるデータ(例えば 1 2 ビットの 2 進数デジタルデータ)はメモリ部 5 0 内に列ごとに備えられたメモリ回路 5 1 に一時的に保持され、水平走査回路 6 0 からの制御信号により、 D S P 8 0 に伝送される。

## [0081]

DSP80は有効信号SのデータとN-ADデータとの差分を取得する処理、AD変換部40の校正データに基づくデータの補正などを行う。DSP80から出力されたデータは出力回路90から、固体撮像装置100が搭載される撮像システムの映像信号処理部などへ出力される。TG70はシステム制御部からの制御信号に基づき固体撮像装置100を制御する。

## [0082]

上述した実施形態では、AD変換部40の前段に増幅部30が設けられているが、列ごとに増幅をする必要がない場合、増幅部30を有しない構成であってもよい。また、画素部10と増幅部30の間、又は増幅部30とAD変換部40の間等にサンプリング回路を追加してもよい。

## [0083]

### (第8実施形態)

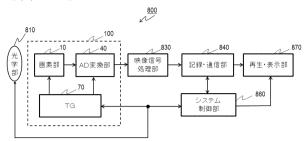

図11は、本発明の第8実施形態に係る撮像システムの構成を示す図である。撮像システム800は、例えば、光学部810、固体撮像装置100、映像信号処理部830、記録・通信部840、システム制御部860、及び再生・表示部870を含む。固体撮像装

10

20

30

40

置100は、画素部10、AD変換部40及びTG70を有する。本実施形態のAD変換部40には、第1乃至第6実施形態のAD変換装置40を用いることができる。また、固体撮像装置100を用いることができる。

### [0084]

レンズ等の光学系である光学部810は、被写体からの光を固体撮像装置100内の、複数の画素11が2次元状に配列された画素部10に結像させ、被写体の像を形成する。TG70は、画素部10、AD変換部40等の固体撮像装置100内の回路の動作タイミングを制御する。固体撮像装置100は、画素部10に結像された光に応じたアナログ信号を、AD変換部40によってデジタル信号に変換して出力する。固体撮像装置100から出力された信号は、映像信号処理部830に入力される。映像信号処理部830は、プログラム等によって定められた方法に従って信号処理を行う。映像信号処理部830での処理によって得られた信号は画像データとして記録・通信部840に送られる。記録・通信部840は、画像を形成するための信号を再生・表示部870に送り、再生・表示部870に動画や静止画像を再生・表示させる。記録・通信部840は、また、映像信号処理部830からの信号を受けて、システム制御部860と通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

#### [0085]

システム制御部860は、撮像システムの動作を統括的に制御するものであり、光学部810、TG70、記録・通信部840、及び再生・表示部870の駆動を制御する。また、システム制御部860は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラム等が記録される。また、システム制御部860は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム800内に供給する。具体的な例としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらし等である。

#### [0086]

本実施形態に係る撮像システム800は本発明の第1乃至第6実施形態のAD変換装置40又は第7実施形態の固体撮像装置100を備えており、AD変換の精度が向上されている。よって、本実施形態に係る撮像システム800によれば高品質な撮像が可能となる

## [0087]

上記の各実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

### 【符号の説明】

## [0088]

- 40 AD変換装置

- 4 1 参照信号発生回路

- 4 2 比較部

- 43 DAC(デジタルアナログ変換器)

- 4.4 比較回路

- 46 制御回路

- 47 カウンタ

10

20

30

【図3】

N-AD変換

第1のAD変換

第2のAD変換

【図2】

【図4】

【図5】

Ramp\_A

Coff

Vin Ci2 H

C1 C5 C6

Ramp\_B

S3 / S2 / S1

43

Vref\_L

Vcom

# 【図11】

## フロントページの続き

(72)発明者 戸塚 洋史

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 鈴木 建

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

## 審査官 白井 亮

(56)参考文献 特開昭53-120248(JP,A)

特開2010-239604(JP,A)

特表2010-503253(JP,A)

特開2002-232291(JP,A)

特開2014-007527(JP,A)

特開昭56-096527(JP,A)

特開2011-250039(JP,A)

特開2013-026734(JP,A)

特開2013-098895(JP,A)

米国特許出願公開第2011/080512(US,A1)

特開2012-029038(JP,A)

特開2014-120868(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 3 M 1 / 5 6

H 0 3 M 1 / 1 6

H04N 5/378