(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2017-514394

(P2017-514394A)

(43) 公表日 平成29年6月1日(2017.6.1)

(51) Int.Cl.

H04L 29/08 (2006.01)

G06F 13/38 (2006.01)

F 1

H04L 13/00

G06F 13/38307A

350

テーマコード(参考)

5B077

5KO34

審査請求 未請求 予備審査請求 未請求 (全 49 頁)

(21) 出願番号 特願2016-563438 (P2016-563438)

(86) (22) 出願日 平成27年4月10日 (2015.4.10)

(85) 翻訳文提出日 平成28年10月19日 (2016.10.19)

(86) 國際出願番号 PCT/US2015/025464

(87) 國際公開番号 WO2015/164102

(87) 國際公開日 平成27年10月29日 (2015.10.29)

(31) 優先権主張番号 61/982,466

(32) 優先日 平成26年4月22日 (2014.4.22)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/682,846

(32) 優先日 平成27年4月9日 (2015.4.9)

(33) 優先権主張国 米国(US)

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 仙石 祥一郎

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

F ターム(参考) 5B077 AA18

最終頁に続く

(54) 【発明の名称】マルチシンボルワードのための同期方法

## (57) 【要約】

カメラ制御インターフェース(CCIe)バスの向上した性能を提供するシステム、方法および装置について記載する。データ通信の方法は、シリアルバス上で第1の同期コードを送信するステップと、第1の同期コードに応答して、シリアルバスに結合された第1のデバイスとの同期を確立するステップと、第1のデバイスとの同期を確立した後、第1のプロトコルに従って、シリアルバスを介して第1のデバイスと通信するステップと、シリアルバス上で第1の非同期コードを送信するステップであつて、非同期コードは、第1のデバイスとの同期の喪失を引き起こすように構成される、ステップと、シリアルバス上で第2の同期コードを送信するステップと、第2の同期コードに応答して、シリアルバスに結合された第2のデバイスとの同期を確立するステップと、第2のデバイスとの同期を確立した後、第2のプロトコルに従って、シリアルバスを介して第2のデバイスと通信するステップとを含む。

## 【特許請求の範囲】

## 【請求項 1】

データ通信の方法であって、

シリアルバス上で第1の同期(SYNC)コードを送信するステップと、

前記第1のSYNCコードに応答して前記第1のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第1の動作モードに従って、前記シリアルバスを介して第1のデバイスと通信するステップと、

前記シリアルバス上で非同期(UNSYNC)コードを送信するステップであって、前記UNSYNCコードは、前記第1のデバイスとの同期の喪失を引き起こすように構成される、ステップと、

10

前記シリアルバス上で第2のSYNCコードを送信するステップと、

前記第2のSYNCコードに応答して前記第2のデバイスとの同期を確立した後、前記第1のプロトコルに関連付けられた第2の動作モードに従って、前記シリアルバスを介して第2のデバイスと通信するステップとを含む方法。

## 【請求項 2】

前記第1のプロトコルはカメラ制御インターフェース(CCIE)プロトコルを含み、前記第1の動作モードは、前記シリアルバス上で送信されるべき12個のシンボル中でデータワードが符号化される動作モードに対応する、請求項1に記載の方法。

20

## 【請求項 3】

前記第1のSYNCコードを送信するステップは、

前記シリアルバス上で、12個のシンボルからなるシーケンスを送信するステップであって、12個のシンボルからなる前記シーケンスは、前記シリアルバスのシリアルクロック(CL)線を、12個のシンボルからなる前記シーケンスの送信中、論理高シグナリング状態に留ませ、さらに、前記シリアルバスのシリアルデータ(SDA)線に、12個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移においてシグナリング状態を変えざるように選択される、ステップを含む、請求項2に記載の方法。

## 【請求項 4】

前記第1のプロトコルはCCIEプロトコルを含み、前記第2の動作モードは、前記シリアルバス上で送信されるべき20個のシンボル中でデータワードが符号化される動作モードに対応する、請求項1に記載の方法。

30

## 【請求項 5】

前記第2のSYNCコードを送信するステップは、

前記シリアルバス上で、20個のシンボルからなるシーケンスを送信するステップであって、20個のシンボルからなる前記シーケンスは、前記シリアルバスのシリアルクロック(CL)線を、20個のシンボルからなる前記シーケンスの送信中、論理高シグナリング状態に留ませ、さらに、前記シリアルバスのシリアルデータ(SDA)線に、20個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移においてシグナリング状態を変えざるように選択される、ステップを含む、請求項4に記載の方法。

## 【請求項 6】

前記第1のプロトコルはCCIEプロトコルを含み、前記第1のデバイスと通信するステップは、

40

シンボルのシーケンス中で、1つまたは複数のデータワードをスレーブCCIEデバイスに送信するステップを含む、請求項1に記載の方法。

## 【請求項 7】

前記第1のSYNCコードは同期ワードおよびハートビートワードを含み、前記ハートビートワードは、1つまたは複数のスレーブCCIEデバイスがクロック信号を生成することを可能にする、請求項1に記載の方法。

## 【請求項 8】

前記UNSYNCコードはエラー条件のインジケータを含み、前記エラー条件の前記インジケータの存在は、前記第1のデバイスを非同期状態に入らせる、請求項1に記載の方法。

50

**【請求項 9】**

前記シリアルバス上で一斉呼出しを送信するステップであって、前記一斉呼出しは、前記シリアルバスをアイドル状態に入らせるために選択される、ステップと、

前記シリアルバスが前記アイドル状態に入った後、第2のプロトコルを使って、前記シリアルバスに結合された第3のデバイスと通信するステップとをさらに含む、請求項1に記載の方法。

**【請求項 10】**

前記第1のプロトコルはCCl eプロトコルを含み、前記第2のプロトコルはインター集積回路(I2C)プロトコルを含む、請求項9に記載の方法。

**【請求項 11】**

前記シリアルバスに接続された少なくとも1つのデバイスは、インター集積回路(I2C)プロトコルを使って通信することに制限される、請求項1に記載の方法。

10

**【請求項 12】**

シリアルバスを介して通信するために構成されたトランシーバと、

少なくとも1つのプロセッサとを備える装置であって、前記少なくとも1つのプロセッサは、

第1の同期(SYNC)コードを、前記シリアルバス上での送信のために前記トランシーバに与え、

前記第1のSYNCコードに応答して、前記第1のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第1の動作モードに従って、前記シリアルバスを介して第1のデバイスと通信し、

20

非同期(UNSYNC)コードを、前記シリアルバス上での送信のために前記トランシーバに与え、前記UNSYNCコードは、前記第1のデバイスとの同期の喪失を引き起こすように構成され、

第2のSYNCコードを、前記シリアルバス上での送信のために前記トランシーバに与え、

前記第2のSYNCコードに応答して、前記第2のデバイスとの同期が確立された後、前記第1のプロトコルに関連付けられた第2の動作モードに従って、前記シリアルバスを介して第2のデバイスと通信するように構成される、装置。

**【請求項 13】**

前記第1のプロトコルはカメラ制御インターフェース(CCl e)プロトコルを含み、前記第1の動作モードは、前記シリアルバス上で送信されるべき12個のシンボル中でデータワードが符号化される動作モードに対応する、請求項12に記載の装置。

30

**【請求項 14】**

前記第1のSYNCコードは、前記シリアルバスのシリアルクロック(SCL)線を、12個のシンボルからなるシーケンスの送信中、論理高シグナリング状態に留まらせるように選択され、シリアルデータ(SDA)線に、12個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移においてシグナリング状態を変えさせるようにさらに選択された、12個のシンボルからなる前記シーケンスを含む、請求項13に記載の装置。

**【請求項 15】**

前記第1のプロトコルはCCl eプロトコルを含み、前記第2の動作モードは、前記シリアルバス上で送信されるべき20個のシンボル中でデータワードが符号化される動作モードに対応する、請求項12に記載の装置。

40

**【請求項 16】**

前記第2のSYNCコードは、前記シリアルバスのシリアルクロック(SCL)線を、20個のシンボルからなるシーケンスの送信中、論理高シグナリング状態に留まらせるように選択され、シリアルデータ(SDA)線に、20個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移においてシグナリング状態を変えさせるようにさらに選択された、20個のシンボルからなる前記シーケンスを含む、請求項15に記載の装置。

**【請求項 17】**

前記第1のプロトコルはCCl eプロトコルを含み、

50

シンボルのシーケンス中に、1つまたは複数のデータワードを符号化するように適応されたエンコーダであって、シンボルの前記シーケンスは、前記トランシーバによって、前記シリアルバスを介してスレーブCCleデバイスに送信される、エンコーダをさらに備える、請求項12に記載の装置。

**【請求項 18】**

前記第1のSYNCコードは同期ワードおよびハートビートワードを含み、前記ハートビートワードは、1つまたは複数のスレーブCCleデバイスがクロック信号を生成することを可能にする、請求項12に記載の装置。

**【請求項 19】**

前記UNSYNCコードはエラー条件のインジケータを含み、前記エラー条件の前記インジケータの存在は、前記第1のデバイスを非同期状態に入らせる、請求項12に記載の装置。 10

**【請求項 20】**

前記少なくとも1つのプロセッサは、

前記シリアルバス上で一斉呼出しを送信させ、前記一斉呼出しは、前記シリアルバスをアイドル状態に入らせるために選択され、

前記シリアルバスが前記アイドル状態に入った後、第2のプロトコルを使って、前記シリアルバスに結合された第3のデバイスと通信するように構成され、

前記第1のプロトコルはCCleプロトコルを含み、前記第2のプロトコルはインター集積回路(I2C)プロトコルを含む、請求項12に記載の装置。 20

**【請求項 21】**

命令を記憶したコンピュータ可読記憶媒体であって、前記命令は、プロセッサによって実行されると、前記プロセッサに、

第1の同期(SYNC)コードを、シリアルバス上での送信のためにトランシーバに与えさせ、

前記第1のSYNCコードに応答して、前記第1のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第1の動作モードに従って、前記シリアルバスを介して第1のデバイスと通信させ、

非同期(UNSYNC)コードを、前記シリアルバス上での送信のために前記トランシーバに与えさせ、前記UNSYNCコードは、前記第1のデバイスとの同期の喪失を引き起こすように構成され、 30

第2のSYNCコードを、前記シリアルバス上での送信のために前記トランシーバに与えさせ、

前記第2のSYNCコードに応答して、前記第2のデバイスとの同期が確立された後、前記第1のプロトコルに関連付けられた第2の動作モードに従って、前記シリアルバスを介して第2のデバイスと通信させる、記憶媒体。 30

**【請求項 22】**

前記第1のプロトコルはカメラ制御インターフェース(CCle)プロトコルを含み、前記第1の動作モードは、前記シリアルバス上で送信されるべき12個のシンボル中に第1のデータワードが符号化される動作モードに対応し、前記第2の動作モードは、前記シリアルバス上で送信されるべき20個のシンボル中に第2のデータワードが符号化される動作モードに対応する、請求項21に記載の記憶媒体。 40

**【請求項 23】**

前記第1のSYNCコードは、前記シリアルバスのシリアルクロック(SCL)線を、12個のシンボルからなるシーケンスの送信中、論理高シグナリング状態に留まらせるように選択され、前記シリアルバスのシリアルデータ(SDA)線に、12個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移においてシグナリング状態を変えさせるようにさらに選択された、12個のシンボルからなるシーケンスを含み、前記第2のSYNCコードは、前記シリアルバスの前記SCL線を、20個のシンボルからなる前記シーケンスの送信中、前記論理高シグナリング状態に留まらせるように選択され、前記SDA線に、20個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移におけるシグナリング状態を変えさ 50

せるようにさらに選択された、20個のシンボルからなる前記シーケンスを含む、請求項21に記載の記憶媒体。

**【請求項 2 4】**

前記UNSYNCコードはエラー条件のインジケータを含み、前記エラー条件の前記インジケータの存在は、前記第1のデバイスを非同期状態に入らせる、請求項21に記載の記憶媒体。

**【請求項 2 5】**

前記命令は、前記プロセッサに、

前記シリアルバス上で送信されるべき一斉呼出しを与える、前記一斉呼出しは、前記シリアルバスをアイドル状態に入らせるために選択され、

10

前記シリアルバスが前記アイドル状態に入った後、第2のプロトコルを使って、前記シリアルバスに結合された第3のデバイスと通信させ、

前記第1のプロトコルはCCl eプロトコルを含み、前記第2のプロトコルはインター集積回路(I2C)プロトコルを含む、請求項21に記載の記憶媒体。

**【請求項 2 6】**

シリアルバスを介して通信するために構成されたトランシーバと、

第1の同期(SYNC)コードを、前記シリアルバス上での送信のために前記トランシーバに与えるための手段と、

前記第1のSYNCコードに応答して、前記第1のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第1の動作モードに従って、前記シリアルバスを介して第1のデバイスと通信するための手段と、

20

非同期(UNSYNC)コードを、前記シリアルバス上での送信のために前記トランシーバに与えるための手段であって、前記UNSYNCコードは、前記第1のデバイスとの同期の喪失を引き起こすように構成される、手段と、

第2のSYNCコードを、前記シリアルバス上での送信のために前記トランシーバに与えるための手段と、

前記第2のSYNCコードに応答して、前記第2のデバイスとの同期が確立された後、前記第1のプロトコルに関連付けられた第2の動作モードに従って、前記シリアルバスを介して第2のデバイスと通信するための手段とを備える、装置。

**【請求項 2 7】**

前記第1のプロトコルはカメラ制御インターフェース(CCl e)プロトコルを含み、前記第1の動作モードは、前記シリアルバス上で送信されるべき12個のシンボル中に第1のデータワードが符号化される動作モードに対応し、前記第2の動作モードは、前記シリアルバス上で送信されるべき20個のシンボル中に第2のデータワードが符号化される動作モードに対応する、請求項26に記載の装置。

**【請求項 2 8】**

前記第1のSYNCコードは、前記シリアルバスのシリアルクロック(SCL)線を、12個のシンボルからなるシーケンスの送信中、論理高シグナリング状態に留まらせるように選択され、前記シリアルバスのシリアルデータ(SDA)線に、12個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移においてシグナリング状態を変えざるようさらに選択された、12個のシンボルからなるシーケンスを含み、前記第2のSYNCコードは、前記シリアルバスの前記SCL線を、20個のシンボルからなる前記シーケンスの送信中、前記論理高シグナリング状態に留まらせるように選択され、前記SDA線に、20個のシンボルからなる前記シーケンスの連続するシンボルの間の各遷移におけるシグナリング状態を変えざるようさらに選択された、20個のシンボルからなる前記シーケンスを含む、請求項26に記載の装置。

**【請求項 2 9】**

前記UNSYNCコードはエラー条件のインジケータを含み、前記エラー条件の前記インジケータの存在は、前記第1のデバイスを非同期状態に入らせる、請求項26に記載の装置。

**【請求項 3 0】**

10

20

30

40

50

前記シリアルバス上で送信されるべき一斉呼出しを送信させるための手段であって、前記一斉呼出しは、前記シリアルバスをアイドル状態に入らせるために選択される、手段と、

前記シリアルバスが前記アイドル状態に入った後、第2のプロトコルを使って、前記シリアルバスに結合された第3のデバイスと通信する手段とをさらに備え、

前記第1のプロトコルはCClバスのプロトコルを含み、前記第2のプロトコルはインター集積回路(I2C)バスのプロトコルを含む、請求項26に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

関連出願の相互参照

本出願は、その内容全体が参考により本明細書に組み込まれる、2014年4月22日に米国特許庁に出願された仮特許出願第61/982,466号および2015年4月9日に米国特許庁に出願された米国非仮出願第14/682,846号の優先権および利益を主張する。

【0002】

本開示は、一般に、ホストプロセッサとカメラなどの周辺デバイスとの間のインターフェースに関し、より詳細には、カメラ制御通信インターフェースバス上のデータレートを向上させることに関する。

【背景技術】

【0003】

20

セルラー電話など、モバイルデバイスの製造業者は、モバイルデバイスの構成要素を、異なる製造業者を含む様々なソースから取得し得る。たとえば、セルラー電話におけるアプリケーションプロセッサは第1の製造業者から取得されることがあり、セルラー電話のディスプレイは第2の製造業者から取得されることがある。アプリケーションプロセッサおよびディスプレイまたは他のデバイスは、規格ベースまたはプロプライエタリな物理インターフェースを使用して相互接続され得る。たとえば、ディスプレイは、モバイル業界プロセッサインターフェース(MIPI)アライアンスによって指定されたカメラシリアルインターフェース規格に準拠するインターフェースを提供することができる。

【0004】

30

一例では、MIPI規格は、マスタおよび1つまたは複数のスレーブを接続するバスとして構成された、2線式、双方向、半二重のシリアルインターフェースを使用するカメラ制御インターフェース(CCI)を定義する。従来のCCIは、インター集積回路(I2C)バスの変形態において使用されるプロトコルと互換性があり、単一のマスタを用いて、バス上で複数のスレーブを扱うことが可能である。CCIバスは、シリアルクロック(SCL)信号およびシリアルデータ(SDA)信号を含む場合がある。I2Cバスを必要とする他の通信もI2Cプロトコルを使っている間、2つ以上のCCIデバイスがCCIプロトコルを使って通信することができるよう、CCIデバイスおよびI2Cデバイスは、同じバス上に展開され得る。CCIの後期バージョンは、より高いシグナリングレートをサポートするための修正プロトコルを使って、より高いスループットを与えることができる。

【0005】

40

一例では、CCI拡張(CCIe)バスは、CClバスの動作と互換性があるデバイスにより高いデータレートを提供するために使用することができる。そのようなデバイスはCClバスデバイスと呼ばれる場合があり、CClバスデバイスは、従来のCCIバスのSCLラインとSDAラインの両方において送信されるシンボルとしてデータを符号化することによって、互いに通信するとき、より高いデータレートに達し得る。第1の時間間隔中に、CClバスデバイスを使ってデータを送信することができ、他のデータは、I2Cシグナリング慣行に従って異なる時間間隔中に送信することができるよう、CClバスデバイスおよびI2Cデバイスは、同じCClバス上に共存してよい。

【発明の概要】

【発明が解決しようとする課題】

50

## 【0006】

モバイルデバイス内でマスタ構成要素とスレーブ構成要素とを接続するバスとして構成されたシリアルインターフェース上で最適化された通信を実現することが現在求められている。

## 【課題を解決するための手段】

## 【0007】

本明細書で開示する実施形態は、CC1eバスを使うカメラ制御インターフェースの性能を向上させることができるシステム、方法および装置を提供する。

## 【0008】

本開示のある態様において、データ通信の方法は、シリアルバス上で第1の同期(SYNC)コードを送信するステップと、第1のSYNCコードに応答して、シリアルバスに結合された第1のデバイスとの同期を確立するステップと、第1のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第1の動作モードに従って、シリアルバスを介して第1のデバイスと通信するステップと、シリアルバス上で第1の非同期(UNSYNC)コードを送信するステップであって、UNSYNCコードは、第1のデバイスとの同期の喪失を引き起こすように構成される、ステップと、シリアルバス上で第2のSYNCコードを送信するステップと、第2のSYNCコードに応答して、シリアルバスに結合された第2のデバイスとの同期を確立するステップと、第2のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第2の動作モードに従って、シリアルバスを介して第2のデバイスと通信するステップとを含む。

10

20

## 【0009】

本開示のある態様において、データ通信用に構成された装置は、シリアルバス上で第1のSYNCコードを送信するための手段と、第1のSYNCコードに応答して、シリアルバスに結合された第1のデバイスとの同期を確立するための手段と、第1のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第1の動作モードに従って、シリアルバスを介して第1のデバイスと通信するための手段と、シリアルバス上でUNSYNCコードを送信するための手段であって、UNSYNCコードは、第1のデバイスとの同期の喪失を引き起こすように構成される、手段と、シリアルバス上で第2のSYNCコードを送信するための手段と、第2のSYNCコードに応答して、シリアルバスに結合された第2のデバイスとの同期を確立するための手段と、第2のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第2の動作モードに従って、シリアルバスを介して第2のデバイスと通信するための手段とを含む。

30

## 【0010】

本開示のある態様において、装置は、シリアルバスを介して通信するために構成されたトランシーバと、少なくとも1つのプロセッサとを含む。少なくとも1つのプロセッサは、第1のSYNCコードを、シリアルバス上の送信のためにトランシーバに与え、第1のSYNCコードに応答して、第1のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第1の動作モードに従って、シリアルバスを介して第1のデバイスと通信し、UNSYNCコードを、シリアルバス上の送信のためにトランシーバに与え、ここでUNSYNCコードは、第1のデバイスとの同期の喪失を引き起こすように構成され、第2のSYNCコードを、シリアルバス上の送信のためにトランシーバに与え、第2のSYNCコードに応答して、第2のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第2の動作モードに従って、シリアルバスを介して第2のデバイスと通信するように構成され得る。

40

## 【0011】

本開示のある態様において、コンピュータ可読記憶媒体は、命令および/またはデータを記憶または維持する。記憶媒体は一時的であっても非一時的であってもよい。命令は、プロセッサによって実行され、かつ/または処理回路の動作を制御することができる。いくつかの例において、命令は、プロセッサによって実行されると、プロセッサまたは処理回路に、第1のSYNCコードを、シリアルバス上の送信のためにトランシーバに与えさせ、第1のSYNCコードに応答して、第1のデバイスとの同期が確立された後、第1のプロトコ

50

ルに関連付けられた第1の動作モードに従って、シリアルバスを介して第1のデバイスと通信させ、UNSYNCコードを、シリアルバス上での送信のためにトランシーバに与えさせ、ここでUNSYNCコードは、第1のデバイスとの同期の喪失を引き起こすように構成され、第2のSYNCコードを、シリアルバス上での送信のためにトランシーバに与えさせ、第2のSYNCコードに応答して、第2のデバイスとの同期が確立された後、第1のプロトコルに関連付けられた第2の動作モードに従って、シリアルバスを介して第2のデバイスと通信させる。

【図面の簡単な説明】

【0 0 1 2】

【図1】複数の利用可能な規格のうちの1つに従って選択的に動作する集積回路(IC)デバイス間のデータリンクを使用する装置を示す図である。

10

【図2】ICデバイス間のデータリンクを利用する装置のためのシステムアーキテクチャを示す図である。

【図3】本明細書で開示されるいくつかの態様による送信機および受信機のいくつかの態様を示す図である。

【図4】本明細書で開示されるいくつかの態様による、データをトランスコードするための符号化方式を示す図である。

【図5】I2Cの1バイトデータ書き込み動作のタイミング図である。

【図6】START条件がレガシーI2Cスレーブノードに対して与える影響を示す図である。

【図7】I2Cデバイス用の状態機械を示す図である。

【図8】I2Cデバイスが共有バス上でのCCl e送信中に誤動作するのを防止する送信方法を示す図である。

20

【図9】SDAラインおよびSCLライン上の入力フィルタによる、パルスのフィルタリングを示す図である。

【図10】I2C受信機の入力フィルタによる、シンボルのフィルタリングを示す図である。

。

【図11】CCl eデバイスにおいて送信されるシンボルの伸長を示す図である。

【図12】シンボル期間が伸長されたときの最良および最悪ケースのスループットを示す図である。

【図13】シンボルをいつ伸長するか判断するための技法を示す図である。

【図14】CCl eデバイスによる送信中に、シンボルスロットが選択的に伸長される別の例を示す図である。

30

【図15】CCl eデバイスによる送信中に、シンボルスロットが選択的に伸長されるさらに別の例を示す図である。

【図16】準安定状態が発生し得る条件を示す図である。

【図17】SDAラインとSCLラインの両方が同時に状態を変えたときの準安定条件の発生を示す図である。

【図18】意図しないSTARTまたはSTOP条件を防止するために回避されなければならない条件を示す図である。

【図19】準安定条件を引き起こし得る、シンボルの間の遷移の排除を示す図である。

【図20】シンボルごとに3つの状態の12個のシンボル、およびシンボルごとに2つの状態の20個のシンボルを使う送信方式を比較する図である。

40

【図21】シンボルごとに2つの状態をもつ20個のシンボルを使うCCl e送信用のいくつかのシナリオを示す図である。

【図22】CCl eインターフェースにおいて送信されるワードの第19のビットに関連したいくつかの態様を示す図である。

【図23】CCl e送信システムにおいて使われるマッピングの一例を示すテーブルである。

【図24】CCl e送信システムにおいて使われるマッピングの一例を示すテーブルである。

【図25】SDAラインおよびSCLラインを介してハートビートクロックがどのように送信され得るかの一例と、ハートビートクロックの送信中に起こり得る同期機会とを示す図である。

50

【図26】12シンボルおよび20シンボルCCle送信モードで利用可能な、いくつかのデータ範囲を示す図である。

【図27】CCleインターフェースにおける、12シンボルおよび20シンボル動作モードへの遷移図の例を示す図である。

【図28】12シンボル送信方式と20シンボル送信方式の両方についての、SDAラインおよびSCLラインのシグナリング状態を示す図である。

【図29】SYNC検出の間に使うことができる回路を示す図である。

【図30】SCLおよび/またはSDA信号のマスキングを許可するように適応されたクロックおよびデータ復元回路を示す図である。

【図31】CCle送信モードを判断するのに、およびSCLマスキング信号を生成するために使うことができる論理回路を示す図である。

【図32】SDAマスキング信号を生成するために使われる論理回路を示す図である。

【図33】20シンボルCCle送信モードを判断するのに使うことができる、論理回路中の信号のタイミングを示す図である。

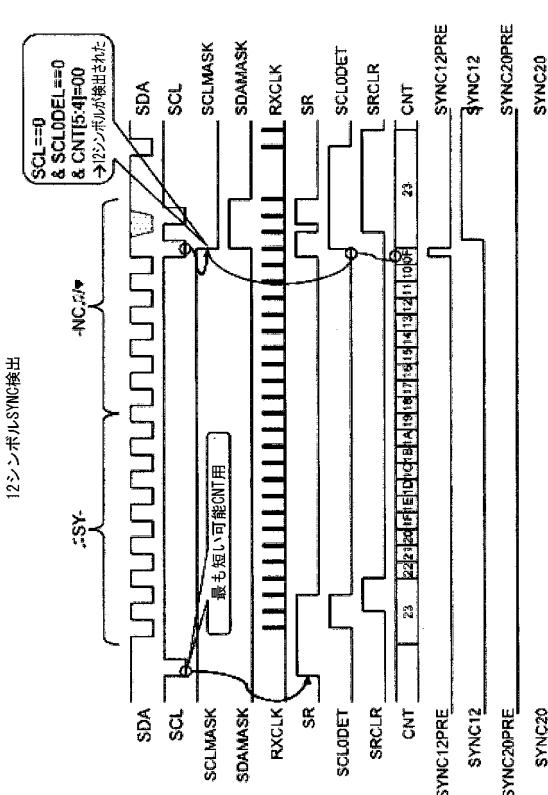

【図34】12シンボルCCle送信モードを判断するのに使うことができる、論理回路中の信号のタイミングを示す図である。

【図35】CCleインターフェースを介して送信される通信がI2Cプロトコルに準拠するときのCCle SYNC検出論理の動作を示す図である。

【図36】CCleとI2Cの混合環境において動作するCCleデバイス向けのフレーム同期プロセスを示す図である。

【図37】CCleデバイスの、非同期状態への遷移を取得するために送信され得るCCleワードを示す図である。

【図38】本明細書で開示するいくつかの態様による、シリアルバスの動作モードの間、および/またはシリアルバス上で使うことができる複数のプロトコルの間を遷移するための一般化方式を示す図である。

【図39】本明細書で開示するいくつかの態様による、I2CプロトコルとCCleプロトコルとの間、およびCCle送信モードの間でのモード切替えを示す図である。

【図40】本明細書で開示するいくつかの態様による、異なるCCle送信モードの間での切替えに関連したモード切替えシーケンスを示す図である。

【図41】本明細書で開示するいくつかの態様に従って適応され得る処理システムを利用する装置の例を示すブロック図である。

【図42】本明細書で開示される1つまたは複数の態様による、CCleバス上で通信するための方法のフローチャートである。

【図43】本明細書で開示される1つまたは複数の態様による、CCleバスを介して通信するための装置のためのハードウェア実装形態の一例を示す図である。

【発明を実施するための形態】

【0013】

図面に関して、ここで様々な態様について記述する。以下の説明では、説明の目的で、1つまたは複数の態様を完全に理解できるように多数の具体的な詳細を記載する。しかし、そのような態様がこれらの具体的な詳細なしに実践されてもよいことは、明らかであろう。

【0014】

本出願で使用されるとき、「構成要素」、「モジュール」、「システム」などの用語は、限定はしないが、ハードウェア、ファームウェア、ハードウェアおよびソフトウェアの組合せ、ソフトウェア、または実行中のソフトウェアのような、コンピュータ関連のエンティティを含むことを意図している。たとえば、構成要素は、限定はしないが、プロセッサ上で稼働するプロセス、プロセッサ、オブジェクト、実行可能ファイル、実行スレッド、プログラム、および/またはコンピュータとすることができます。例として、コンピューティングデバイス上で稼働するアプリケーションと、そのコンピューティングデバイスの両方が、構成要素であり得る。1つまたは複数の構成要素は、プロセスおよび/または実行

10

20

30

40

50

スレッド内に存在することができ、構成要素は、1つのコンピュータ上に局在することができ、および/または2つ以上のコンピュータ間に分散することができる。さらに、これらの構成要素は、種々のデータ構造を記憶している種々のコンピュータ可読媒体から実行することができる。構成要素は、ローカルシステム内、分散システム内、および/または、インターネットなどのネットワークにわたる別の構成要素と対話する1つの構成要素からのデータなどの、1つまたは複数のデータパケットを有する信号などに従うローカルプロセスおよび/またはリモートプロセスにより、信号によって他のシステムと通信することができる。

【0015】

さらに、「または」という用語は、排他的な「または」ではなく、むしろ包括的な「または」を意味することを意図している。すなわち、別段の規定がない限り、または文脈から明白でない限り、「XはAまたはBを利用する」という言い回しは、自然な包括的並べ替えのいずれかを意味することを意図している。すなわち、「XはAまたはBを利用する」という語句は、以下の事例、すなわち、XはAを利用する、XはBを利用する、またはXはAとBの両方を利用する、のいずれかによって成立する。さらに、本出願および添付の特許請求の範囲で使用する冠詞「a」および「an」は、別段の規定がない限り、または単数形を示すことが文脈から明白でない限り、概して「1つもしくは複数」を意味するものと解釈すべきである。

【0016】

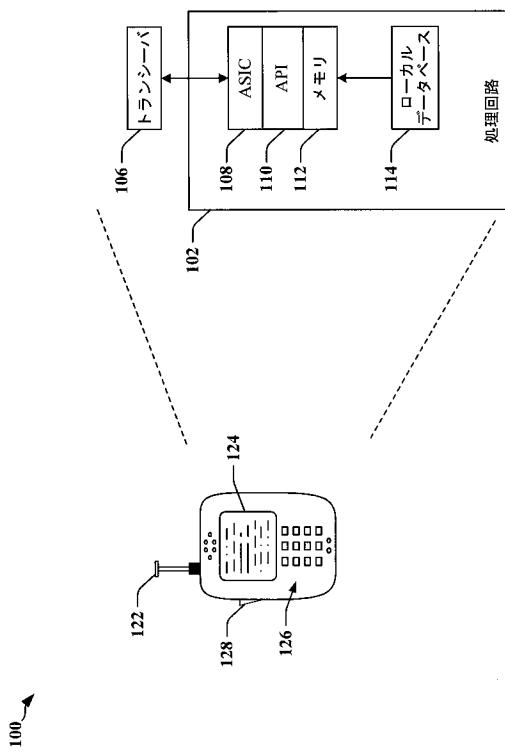

本発明のいくつかの態様は、電話、モバイルコンピューティングデバイス、アプライアンス、自動車用電子機器、アビオニクスシステムなど、装置のサブ構成要素を含み得る電子デバイス間に配備される通信リンクに対して適用可能であり得る。図1は、ICデバイス間で通信リンクを利用することができる装置を描写する。一例では、装置100は、無線アクセスネットワーク(RAN)、コアアクセスネットワーク、インターネット、および/または別のネットワークとRFトランシーバを介して通信するワイヤレス通信デバイスを含み得る。装置100は、処理回路102に動作可能に結合された通信トランシーバ106を含み得る。処理回路102は、特定用途向けIC(ASIC)108などの1つまたは複数のICデバイスを含み得る。ASIC108は、1つまたは複数の処理デバイス、論理回路などを含み得る。処理回路102は、処理回路102によって実行される場合がある命令およびデータを維持することができるメモリデバイス112などのプロセッサ可読ストレージを含み、ならびに/またはそれに結合されてもよい。処理回路102は、オペレーティングシステム、および、ワイヤレスデバイスのメモリデバイス112などの記憶媒体の中に存在するソフトウェアモジュールの実行をサポートし可能にするアプリケーションプログラミングインターフェース(API)110レイヤのうちの1つまたは複数によって制御され得る。メモリデバイス112は、読み取り専用メモリ(ROM)もしくはランダムアクセスメモリ(RAM)、電気的消去可能プログラマブルROM(EEPROM)、フラッシュカード、または処理システムおよびコンピューティングプラットフォームにおいて使用され得る任意のメモリデバイスを含み得る。処理回路102は、装置100を構成し、動作させるために使用される動作パラメータおよび他の情報を維持することができるローカルデータベース114を含むか、またはそれにアクセスし得る。ローカルデータベース114は、データベースモジュール、フラッシュメモリ、磁気媒体、EEPROM、光媒体、テープ、ソフトディスクまたはハードディスクなどのうちの1つまたは複数を使用して実装され得る。処理回路はまた、他の構成要素の中でも、アンテナ122、ディスプレイ124などの外部デバイス、ボタン128、およびキーパッド126などのオペレータ制御に動作可能に結合される場合がある。

【0017】

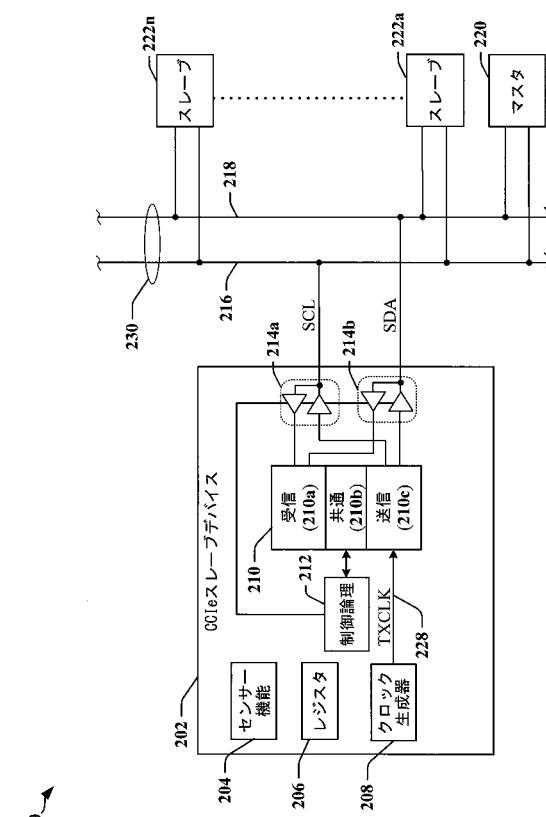

図2は、通信バスに接続された装置200のいくつかの態様を示すブロック概略図であり、ここで、装置は、ワイヤレスモバイルデバイス、モバイル電話、モバイルコンピューティングシステム、ワイヤレス電話、ノートブックコンピュータ、タブレットコンピューティングデバイス、メディアプレーヤ、ゲーミングデバイスなどのうちの1つまたは複数において実施され得る。装置200は、PCIeバス230を使用して通信する複数のデバイス202、220

10

20

30

40

50

、および222a～222nを含み得る。CCIEバス230は、CCIEバス230によってサポートされる強化された機能のために構成されているデバイス用に、従来のCCIEバスの能力を拡張することができる。たとえば、CCIEバス230は、CCIEバスよりも高いビットレートをサポートすることができる。本明細書で開示するいくつかの態様によると、CCIEバスのいくつかのバージョンは、16.7Mbps以上のビットレートをサポートするように構成または適応されてよく、CCIEバスのいくつかのバージョンは、少なくとも23メガビット毎秒のデータレートをサポートするように構成または適応されてよい。

#### 【0018】

図2に示される例では、イメージングデバイス202は、CCIEバス230上でスレーブデバイスとして動作するように構成される。イメージングデバイス202は、たとえば、イメージセンサーを管理するセンサー制御機能204を提供するように適応され得る。加えて、イメージングデバイス202は、構成レジスタ206または他のストレージと、制御論理212と、トランシーバ210と、ラインドライバ/受信機214aおよび214bとを含み得る。制御論理212は、状態機械、シーケンサ、信号プロセッサ、または汎用プロセッサなどの処理回路を含み得る。トランシーバ210は、受信機210aと、送信機210cと、タイミング、論理、およびストレージの回路および/またはデバイスを含む共通回路210bとを含み得る。一例では、送信機210cは、クロック生成回路208によって与えられたタイミングに基づいて、データを符号化および送信する。

#### 【0019】

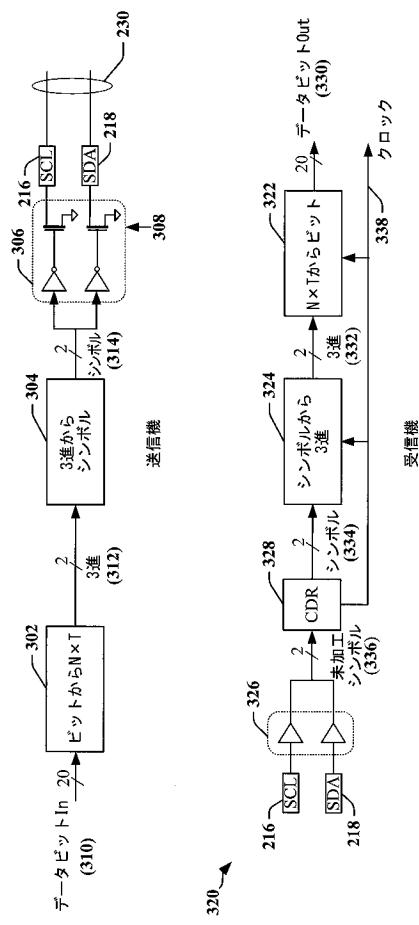

図3は、本明細書で開示されるいくつかの態様に従って構成された送信機300および受信機320の一例を示すブロック図である。CCIEの動作の場合、送信機300は、入力データ310を3進(ベース3)数にトランスクードすることができ、3進数は、SCL信号216およびSDA信号218の信号線上で送信されるシンボルとして符号化される。描寫された例では、入力データ310の各(データワードとも呼ばれる)データ要素は、19ビットまたは20ビットを有する場合がある。トランスクーダ302は、入力データ310を受信し、データ要素ごとに3進数312のシーケンスを生成することができる。3進数312は、2ビットで符号化されてよく、3進数の各シーケンス312内に12個の3進数があり得る。エンコーダ304は、ラインドライバ306を通して送信される2ビットシンボル314のストリームを生成する。図示の例では、ラインドライバ306は、オープンドレイン出力トランジスタ308を含む。しかしながら、他の例では、ラインドライバ306は、プッシュプルドライバを使用してSCL信号216およびSDA信号218の信号線を駆動することができる。エンコーダによって生成された2ビットシンボル314の出力ストリームは、連続するシンボルのペアは2つの同一のシンボルを含まないことを保証することによって、連続するシンボル314間のSCL信号216およびSDA信号218の信号線のうちの少なくとも1つの状態における遷移を有する。少なくとも1つの信号216および/または218における状態の遷移の可用性により、受信回路320がデータシンボル314のストリームから受信クロック338を抽出することが可能になる。

#### 【0020】

CCIEシステムでは、受信機320は、クロックおよびデータ復元(CDR)回路328を含むか、またはそれと協働する場合がある。受信機320は、CDR328に未加工の2ビットシンボル336のストリームを与えるラインインターフェース回路326を含み得る。CDR328は、未加工のシンボル336から受信クロック338を抽出し、2ビットシンボル334のストリームおよび受信クロック338を、受信機320の他の回路324および322に与える。いくつかの例では、CDR328は、複数のクロック338を生成することができる。デコーダ324は、受信クロック338を使用して、シンボル334のストリームを12個の3進数332のシーケンスに復号することができる。3進数332は、2ビットを使って符号化することができる。次いで、トランスクーダ322は、12個の3進数332の各シーケンスを19ビットまたは20ビットの出力データ要素330に変換することができる。

#### 【0021】

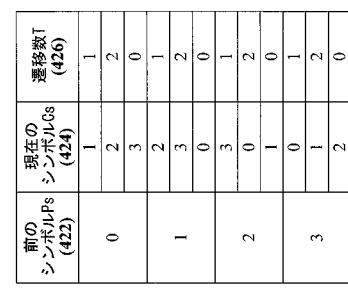

図4は、CCIEバス230上での送信のための埋め込みクロックをもつシンボル314のシーケンスを生成するために、エンコーダ304によって使用され得る符号化方式400を示す図であ

10

20

30

40

50

る。符号化方式400はまた、CCleバス230から受信されたシンボルから3進遷移数を抽出するため、デコーダ324によって使用され得る。CCle符号化方式400では、CCleバス230の2本のワイヤにより、4つの基本シンボルS:{0,1,2,3}の規定が可能になる。シンボルのシーケンス314、334内の任意の2つの連続するシンボルは様々な状態を有し、シンボルシーケンス0,0、1,1、2,2、および3,3は、連続するシンボルの無効な組合せである。したがって、各シンボル境界で3つのみの有効なシンボル遷移が可能であり、ここで、シンボル境界は送信クロックによって決定され、第1のシンボル(前のシンボルPs)422が終了し、第2のシンボル(現在のシンボルCs)424が開始するポイントを表す。

#### 【0022】

本明細書で開示されるいくつかの態様によると、3つの可能な遷移は、各Psシンボル422について値「T」をもつ3進数426を割り当てられる。Tは、3進数によって表すことができる。一例では、遷移数426の値は、符号化方式用のシンボル順序付けサークル402を割り当てるによって決定される。シンボル順序付けサークル402は、4つの可能なシンボル用のシンボル順序付けサークル402上のロケーション404a～404dと、ロケーション404a～404dの間の回転の方向406とを割り振る。描写された例では、回転406の方向は時計回りである。遷移数426は、有効な現在のシンボル424と直前のシンボル422との間の離隔を表すことができる。離隔は、前のシンボル422から現在のシンボルCs424に到達するために必要なシンボル順序付けサークル402上の回転406の方向に沿ったステップの数として定義することができる。ステップの数は、単一の桁のベース3の数として表現することができる。シンボル間の3ステップの差分は、 $0_{base-3}$ として表すことができる。図4のテーブル420は、この手法を使用する符号化方式を要約する。

10

20

20

#### 【0023】

送信機300において、前に生成されたシンボル422、および遷移数426として使用される入力3進数を知らされると、テーブル420は、送信されるべき現在のシンボル424をルックアップするために使用され得る。受信機320において、テーブル420は、前に受信されたシンボル422と現在受信されたシンボル424との間の遷移を表す遷移数426を決定するためのルックアップとして使用され得る。遷移数426は、3進数として出力することができる。

#### 【0024】

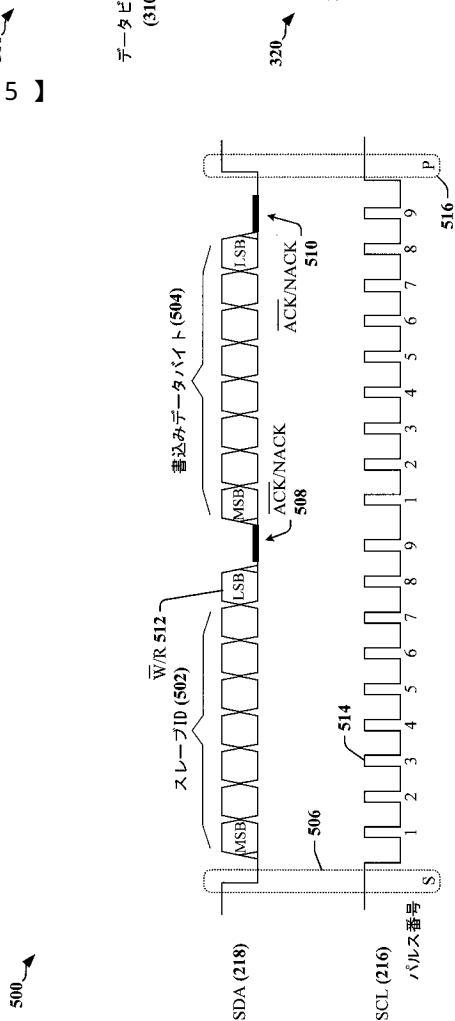

図5は、I2Cの1バイト書き込みデータ動作を示すタイミング図500である。I2Cマスタノードは、I2Cバス上のどのスレーブノードにマスタノードがアクセスすることを望むかを示すために、SDA信号218上で7ビットのスレーブ識別子(スレーブID)502と、続いて、動作が読み取り動作であるか、それとも書き込み動作であるかを示す、読み取り/書き込みビット512を送り、それによって、読み取り/書き込みビット512は、書き込み動作を示すために論理0にあり、読み取り動作を示すために論理1にある。IDが7ビットのスレーブID502と一致するスレーブノードのみが、書き込み(または他の)動作に応答することができる。I2Cスレーブノードがそれ自体のスレーブID502を検出するために、マスタノードは、SCL信号216上の8個のクロックパルスとともに、SDA信号218上で少なくとも8ビットを送信する。レガシーアクセス動作がCCle動作に反応することを防止するために、この挙動が活用されてCCle動作モードでデータを送信し得る。

30

#### 【0025】

図6は、レガシーアクセス動作とCCle動作との競合を示すタイミング図600である。図600では、SDA信号218が高のシグナリング状態にある間にSCL信号216が低のシグナリング状態に遷移する。この例600では、いくつかのSTART状態606または608は、完全な7ビットのスレーブIDが送信される前に検出することができる。結果として生じた不完全なスレーブID602、604は、いかなるスレーブデバイスによっても認識されない。動作中、SCL信号216上に6個のみのパルス612を送った後、START状態608、610を発行するマスタノードの効果には、SDA信号218上でそれぞれのI2CスレーブIDを認識する可能性が起こる前に、すべてのレガシーアクセス動作がCCle動作に反応することを防止するために、この挙動が活用されてCCle動作モードでデータを送信し得る。

40

50

02、604中の情報は、スレーブノードのうちのいずれによっても有効なスレーブIDとして復号されない。その結果、レガシーI2Cスレーブノードは、不完全なスレーブID602、604に応答することを期待されない。

【0026】

図6はまた、CCIEモードにおけるデータ送信用のI2CバスのSCL信号216とSDA信号218の組合せの使用を示す例620を含む。CCIEシンボルは、I2C送信用のSCL信号216上で送信されるクロック信号614の各トグルに対応する時間において送信することができる。したがって、2つのSTART状態608と610との間で送信されるクロックトグルの数は、CCIE送信ごとに送信され得るシンボルの数を規定することができる。したがって、12シンボルの送信622、624は、任意のスレーブノードにI2CスレーブIDとしてシーケンスを検出させずに、不完全なスレーブID602、604の送信に等価な6個のSCLパルスシーケンスの間に利用可能な12個のシグナリング状態において、実現することができる。

10

【0027】

SCL信号216上の遷移と同時にSDA信号218上で発生する遷移は、そのような遷移をSTART状態として解釈することができるレガシーI2Cデバイスには重要でない。しかしながら、レガシーI2Cデバイスは、後で発生する有効なSTART状態628、630を検出し、それらは、I2Cスレーブノードのバス論理検出をリセットする。したがって、I2Cスレーブノードは、CCIE送信622、624の間に発生するいくつかのSDA遷移をSTOP状態として検出することができるが、CCIE送信622、624内でのそのようなSTOP状態の検出は、不完全なSID602、604の早い終了を引き起こすにすぎない。同様に、CCIE送信622、624の間のSTART状態の検出は、スレーブノードのI2C機能のバス論理リセットを実施させるだけである。

20

【0028】

したがって、レガシーI2Cスレーブノードが6個のSCLパルスシーケンス中の12シンボルのCCIE送信622、624を不完全なI2CスレーブID602、604として無視することが明らかである。さらに、START状態606、608、および610の間の14個のSCLトグルの間、12個のシンボルは、SCL信号216および/またはSDA信号218上で送信することができる。

30

【0029】

I2CバスのSCL信号216および/またはSDA信号218は、クロック信号がシンボル遷移内に埋め込まれたとき、CCIEモードにおけるデータ送信に利用することができる。その結果、SDA信号218およびSCL信号216は、レガシーI2Cスレーブノードの機能に影響を与えることなく、かつブリッジデバイスを使用してCCIE互換ノードからレガシーI2Cスレーブノードを隔離せずに、2つの連続するSTART状態626、628、および/または630の間で任意の12個のシンボルを送信するために使用することができる。I2Cモードでは、START状態はI2Cマスターのみによって送られ、CCIEモードでは、START状態は12シンボルのワードを送信する予定があるどのノードによっても送られる。

30

【0030】

いくつかの条件下では、I2Cデバイスは、送信622、624中のいくつかのCCIEシンボルシーケンスを有効なI2Cパルスとして混同または誤解釈する場合があり、そうすることによって、求められていない、予測不可能な変化をI2Cデバイス状態機械に対して引き起こす。たとえば、I2C仕様によって許容される最大期間( $t_{BIT}$ )の半分よりも短いシンボル期間に送られる12個のCCIEシンボルは、セットアップタイミングエラーにより、I2Cデバイス状態機械を未知の状態に進ませる場合がある。 $\min t_{BIT}$ 要件よりも大きい最小SCL期間を満足するようにCCIEシンボルレートを減速させると、CCIEビットレートが14Mbpsから2.4Mbpsまで遅くなる場合がある。したがって、CCIEデバイスは、I2Cデバイスにおいて、衝突も、求められていない状態変化も引き起こすことなく、I2Cバスを介して動作するように構成することができる。

40

【0031】

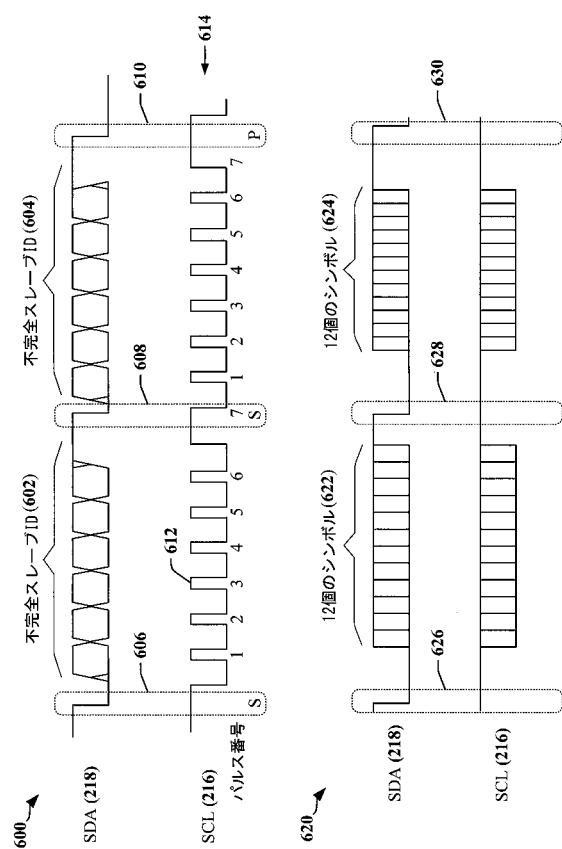

図7は、I2Cデバイス用の状態機械700を示すブロック図を含む。I2Cプロトコルにおいて、状態機械700は、I2Cフレームおよび/またはワードの送信および/または受信を追跡するように維持される。状態機械700は、バスのSCL信号216に基づいてトリガされ、様々な状

50

態702を遷移する。状態機械遷移図714は、状態機械700の一例についての、状態702における可能な遷移を示す。

【0032】

タイミング図710、712という2つの例は、SCL信号216における信号中のエッジの発生頻度が増したときの、状態機械700の挙動の差を示す。したがって、第1のタイミング図710は、より遅いCClEシンボル送信期間に関してよく、第2のタイミング図712は、予測不可能な変化をより高い頻度で経る状態機械700の状態702における遷移を示す。これらの予測不可能な変化の結果、I2Cデバイスが、バスを介して受信または送信するのを、そうすることが想定されるときに開始し、またはI2Cデバイスが無反応になり、制御された動作をやめ、かつ/もしくはさらなる機能をやめる不確定状態に入る場合がある。

10

【0033】

一例では、組合せ論理732が最終的な、安定した結果を生じる前に、状態機械700の状態702を維持するフリップフロップが論理732の出力をサンプリングするとき、問題が発生し得る。特に、順序論理は、1つまたは複数の意図しない状態の間を遷移し得るが、それは、組合せ論理732が、CClE通信モード用の2つのシンボル期間であり得る、SCL信号216における信号のエッジの間の最も短い期間に追いつくことができないからである。言い換えると、SCLライン上でのシンボル送信の期間は、状態機械組合せ論理732、および状態702を維持するフリップフロップの最大許容可能セットアップ時間よりも短い。I2Cデバイスは、持続時間が50ns未満であるシンボル送信期間をフィルタ除去する入力フィルタを含み得る。フィルタリングされた信号は、50ns以下のシンボル送信が状態変化をトリガしないように、I2Cデバイス中の組合せ論理732に与えられてよい。ただし、50nsよりも大きいシンボル送信期間は、組合せ論理732まで入力フィルタを通り、それらのより長いシンボル送信は、順序外れであり得る状態変化をトリガする場合があり、そうすることによって、I2Cデバイスにおいて問題を引き起こす。この例では、より短いクロック信号706bが、不正確にキャプチャされた状態716における不確定分岐を引き起こす無効状態値716をキャプチャし得る。

20

【0034】

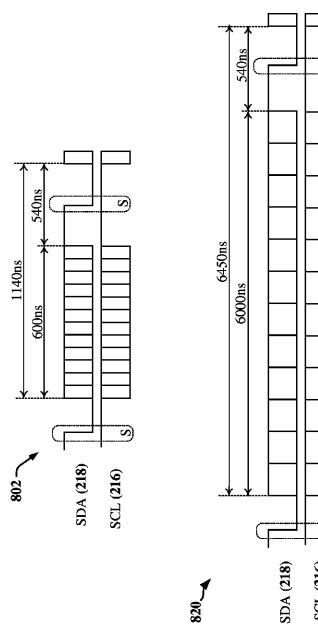

図8は、共有バス上でのCClE送信中にI2Cデバイス状態機械700が変化するのを防止することができる送信方法の例を示す。この手法において、すべてのCClEシンボル送信802(図6も参照)が、50nsから500nsに伸長される。500nsのシンボル周期があるので、最も短い可能SCL期間は、高速モードプラス(Fm+)をサポートするために設計されたI2Cデバイスがセットアップタイミング問題を回避することができるようになるFm+セットアップ( $f_{SCL}$ )最大要件を満たす1000ns(1MHz)である。ただし、シンボル期間を50nsから500nsに伸長すると、スループットを14.04Mbpsから2.45Mbpsに低減させるという望ましくない影響がある。

30

【0035】

図9は、SDAラインおよびSCLライン上の入力フィルタによる、50ns未満のシンボル期間を有するパルスのフィルタリングを示す図面900である。50ns以下のシンボルが、I2C高速モード(Fm)またはFm+デバイスと互換性があるか、または準拠するデバイスによってフィルタリングされることが、I2C仕様の要件である。したがって、いくつかの事例では、50ns以上の効果的な期間を引き起こすシンボル送信のみが伸長されるように、選択的伸長が適用され得る。

40

【0036】

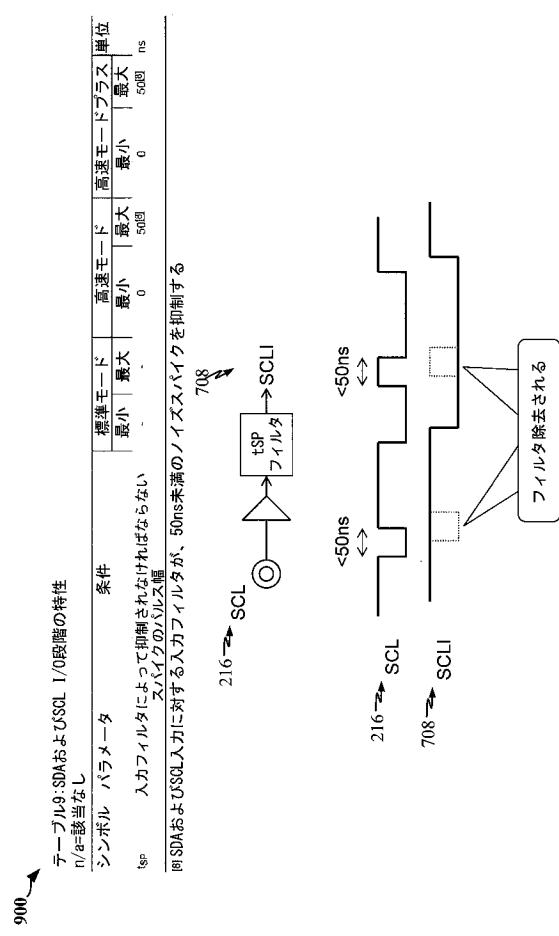

図10は、I2Cデバイス受信機の入力フィルタによっていくつかのシンボルがフィルタリングされ得る例を示す図1000である。第1のグラフ1002において、SDA信号218およびSCL信号216は、50ns以下のシンボル持続時間有する。つまり、この例では、SCL信号216上のシンボルは、毎期間に状態を切り替える(たとえば、低-高または高-低)。SCL信号216上のシンボルは、SCL1ライン708が遷移しない(すなわち、どのクロック信号も組合せ論理732に届かない)ように、I2Cデバイス受信機の入力フィルタによってフィルタ除去される。

50

【0037】

第2のグラフ1004において、SCL信号216上のシンボルのうちのいくつかは、毎期間ごとに状態をえるのではなく、したがっていくつかは、50nsよりも大きい期間を有するパルス1008として現れる。したがって、SCLIライン708上のこれらのパルス1008は、I2Cデバイス受信機の入力フィルタによってフィルタ除去されない。これらのパルス1008は次いで、組合せ論理に届き、求められていない状態変化を引き起こし得る。

#### 【0038】

第3のグラフ1006において、より多くのパルスがSCLIライン708に届き、求められていない状態変化をI2Cデバイスに対して引き起こす。

#### 【0039】

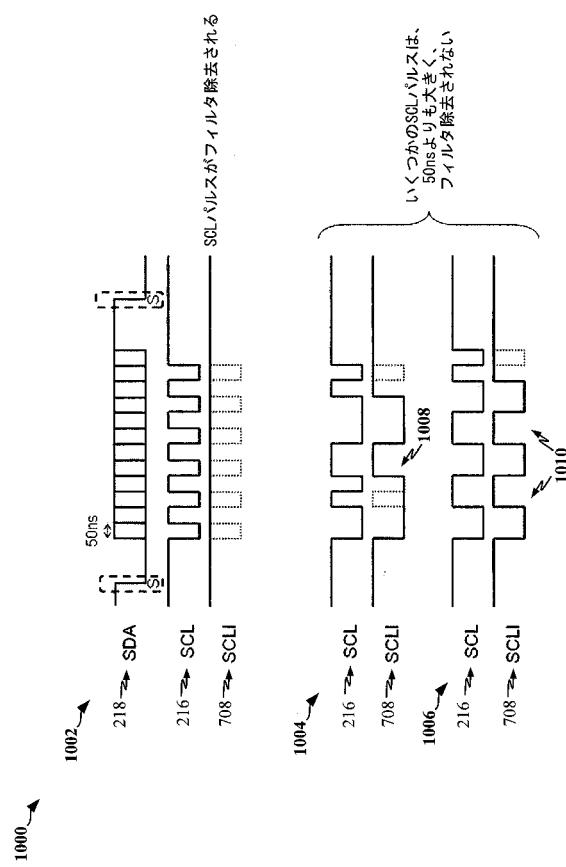

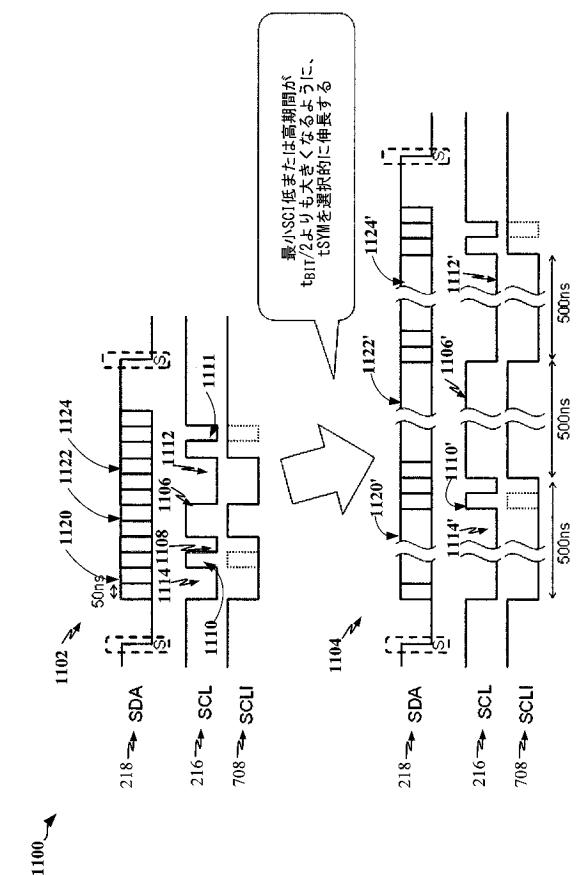

図11は、SCL信号216上の、CClモードで送信されるいくつかのシンボルが、求められていない状態変化がI2Cデバイス上で発生しないように選択的に伸長され得る例を示す。第1のグラフ1102は、いくつかのシンボルスロットが伸長を必要とし得る間にI2Cデバイス受信機の入力フィルタによってフィルタリングされ得るいくつかのパルスを示す。たとえば、各々が単一のシンボルスロット内にある第1のパルス1110および第2のパルス1111が、フィルタリングされ得る(SCLIライン706参照)。第1のシンボルスロット1120(第1のシンボルパルス1114を有する)、第2のシンボルスロット1122(第2のシンボルパルス1106を有する)、および第3のシンボルスロット1124(第3のシンボルパルス1112を有する)が伸長され得る。たとえば、第1のシンボルパルス1114と次のシンボルスロットとの間で低から高への遷移が発生するので、I2Cデバイスにおける求められていない状態変化が引き起こされ得るという条件が発生する。したがって、対応するシンボルスロット1120は伸長を必要とし得る。同様の条件が、第2のシンボルパルス1106および第3のシンボルパルス1112の後に存在する。

10

20

20

#### 【0040】

第2のグラフ1104において、伸長されたシンボルスロット1120'、1122'および1124'は、状態変化の間の期間が少なくとも500nsであるように示され、そうすることによって、I2Cデバイス状態に対する変化を防止する。そのような伸長を実施するために、送信側CClモードデバイスは、状態の変化が発生しているかどうかを確かめるために少なくとも次のシンボルパルスをルックアヘッドすることができるに留意されたい。

30

#### 【0041】

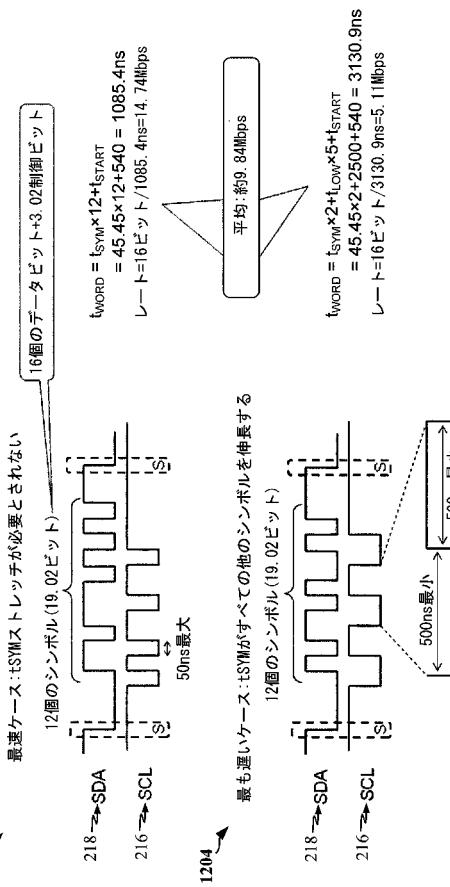

図12は、いくつかのシンボル期間が選択的に伸長される手法のための、最良および最悪ケースのデータスループットの算出を示すタイミングチャート1202、1204の例を含む。平均スループットの例は、通信インターフェースの異なる構成についての達成可能なデータレートの比較を行うために算出されてよい。異なる構成は、最大 $f_{SCL}$ および/または意図しないS/P準安定性に関連した問題に対処するために適用され得る。

30

#### 【0042】

一例が、第1のタイミングチャート1202によって示されている。この例では、12シンボルCCl構成が、同じバス上でどのレガシーアクセスモードも作動されないとき、またはバスに接続されたすべてのデバイスが $t_{SYM}$ における各CClワードの前のSTART条件を検出することができるとき、約23Mbpsのデータレートを達成し得る。この例では、 $t_{START}=2 \times t_{SYM}$ であり、 $t_{SYM}$ は伸長されない。12シンボルCCl構成は、同じバス上で作動されるすべてのレガシーアクセスモードが、適度に速いクロックとの使用のために同期して設計されているとともに、最大 $f_{SCL}$ および意図しないS/P準安定性問題が存在しないとき、約14Mbpsのデータレートを達成し得る。この例では、 $t_{START}$ はI2C ACとして定義され、 $t_{SYM}$ は伸長されない。

40

#### 【0043】

別の例が、第2のタイミングチャート1204によって示されている。この例では、12シンボルCCl構成は、同じバス上で作動されるすべてのレガシーアクセスモードが、同期して設計され、意図しないS/P準安定性問題と無縁であるとき、9.8Mbpsの平均データレートを達成し得るが、1つまたは複数のレガシーアクセスモードが、最大 $f_{SCL}$ 問題によって影響を受ける場合がある。この例では、 $t_{START}$ はI2C ACとして定義され、 $t_{SYM}$ は伸長される。

50

ボルCCl<sub>e</sub>構成は、同じバス上で作動される1つまたは複数のレガシーI2Cデバイスが、最大 $f_{SCL}$ 問題および/または意図しないS/P準安定性問題を受けやすいとき、6.2Mbpsの平均データレートを達成し得る。この例では、 $t_{START}$ はI2C ACとして定義され、 $t_{SYM}$ は伸長される。

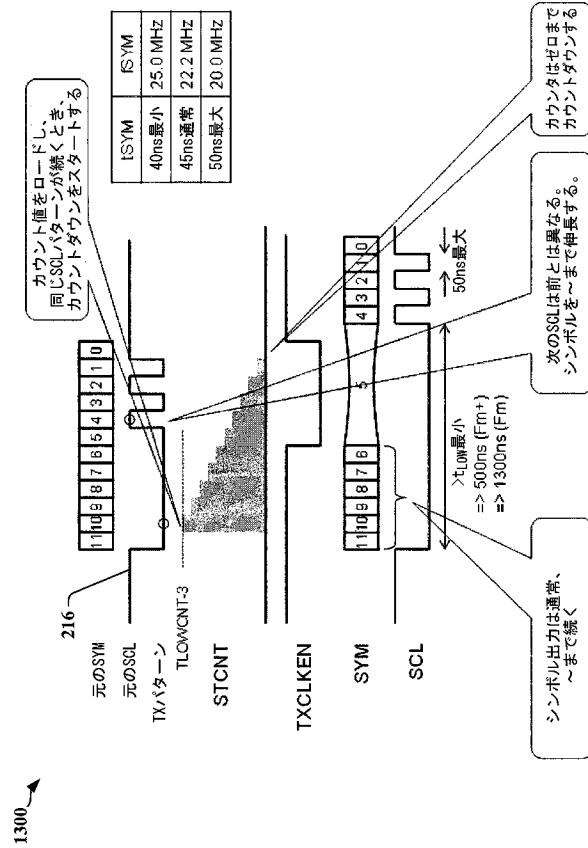

#### 【0044】

図13は、CCl<sub>e</sub>送信機によって、いつシンボルが伸長されるべきか判断するのに使うことができる技法の一例を示す。ここで、SCL信号216は、低シグナリング状態において伸長され得る。2つ以上のシンボルが、一定の高または低論理状態など、同じシグナリングパターンを作成するとき、特定のシンボルが伸長されるべきである時間量を確かめるために、カウントダウン値(STCNT)が始動される。カウントダウン値は、ゼロに達するまで、事前ストレッチシンボル周期ごとに低下されてよい。この例では、カウントダウン値がゼロに低減されたとき、I2C受信機において知覚されるパルスは、少なくとも500nsの長さである。この例では、シンボル11～5は、SCL信号216上で同じシグナリング状態(すなわち、論理低)を生じ、シンボル4は、異なるシグナリング状態(すなわち、論理高)を生じる。したがって、シンボル5は、I2Cデバイスにおける知覚されるパルスが、500nsに等しいかまたはそれよりも大きくなるように伸長されてよい。

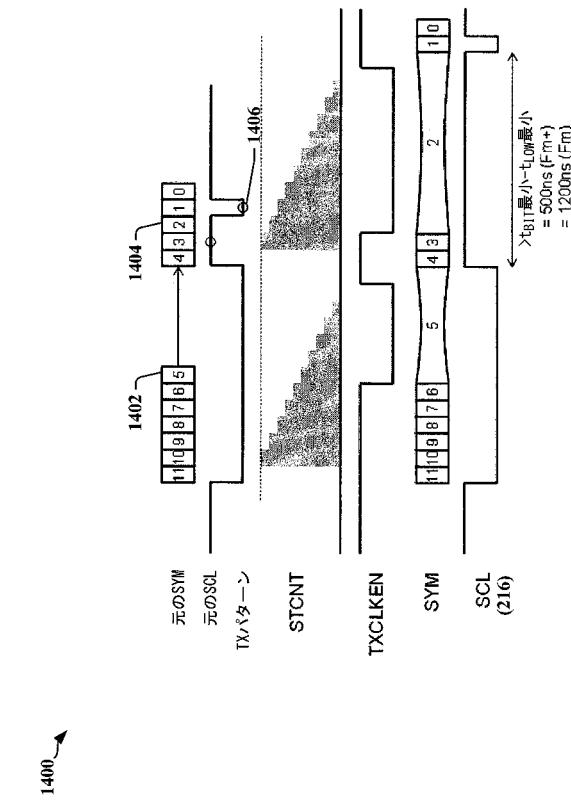

#### 【0045】

図14は、第5のシンボルスロット1402における第1のシンボルパルスと、第2のシンボルスロット1404における第2の、連続するパルスの両方が伸長されるように、送信側CCl<sub>e</sub>デバイスによる送信中にシンボルスロットが選択的に伸長される別の例を示す。この例では、第2のシンボルスロット1404は、少なくとも2つの連続するシンボルパルスが、後続パルス1406の長さを考慮せずに、SCL信号216を同じ状態にさせると、ブラインド伸長されてよい。

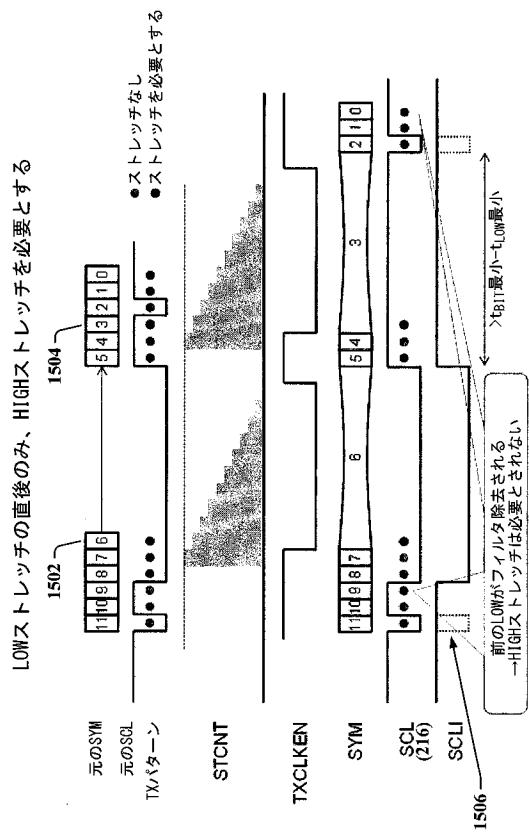

#### 【0046】

図15は、送信側CCl<sub>e</sub>デバイスによる送信中に2つのシンボルスロット1502および1504が伸長される別の例を示す。ここで、HIGHストレッチは、LOWストレッチの後に発生するだけである。したがって、シンボル10～9に対してはHIGHストレッチが発生せず、というのは、シンボル11のSCL=0がI2Cデバイスによってフィルタ除去されるので、それらのシンボルに先行するLOWストレッチがないからである。

#### 【0047】

この例では、第6のシンボルスロット1502は低状態にあり、伸長され、第3のシンボルスロット1504も、高状態にあり、伸長される。この例は、シンボルパルス11からシンボルパルス10へのシンボル遷移がある場合であっても、パルスが1506においてI2Cデバイスの入力フィルタによってフィルタ除去されるので、シンボルスロット11を伸長する必要はないことも示す。ただし、第9のシンボルスロットから第8のシンボルスロットへの、高から低への遷移は、I2C受信機によってパルスとして知覚される。したがって、第6のシンボルパルスから第5のシンボルパルスへの、低から高への遷移があるので、第6のシンボルスロットは、カウントダウン値(STCNT)がゼロに達するまで(たとえば、知覚されるパルス期間が少なくとも500nsになるまで)伸長される。

#### 【0048】

別の例では、ルックアヘッド手法が、送信側CCl<sub>e</sub>デバイスによる送信中に2つのシンボルスロットを伸長させる。送信パターンに対してルックアヘッドが実施され、送信機は、HIGH期間についてのストレッチの持続時間を、後続シンボルスロット中の将来のシンボル送信に基づいて決める。将来、フィルタリングされていないLOW期間がない場合、ワード時間を最小限にするのに必要なだけのシンボルに対して、1つのHIGH期間ストレッチが続いている。

#### 【0049】

いくつかの準安定条件が、CCl<sub>e</sub>送信中に起こり得る。本明細書に記載する12CCl<sub>e</sub>シンボル送信中、信号準安定性が、CCl<sub>e</sub>デバイスと共有されるバスに結合されたレガシーI2Cデバイスの論理デバイス中で発生し得る。そのような準安定性は、たとえば、SDA信号218お

10

20

30

40

50

よりSCL信号216の状態が同時に変化するときに発生し得る。レガシーI2Cデバイスは、いくつかの事例では遷移がSTARTまたはSTOP条件であると判断する場合があり、他の事例ではそうではないと判断する場合がある。そのような検出は準安定になる場合があり、それにより、共有バスに結合されたレガシーI2Cデバイス中の論理デバイスが、間違った/未知の状態に進み得る。

#### 【0050】

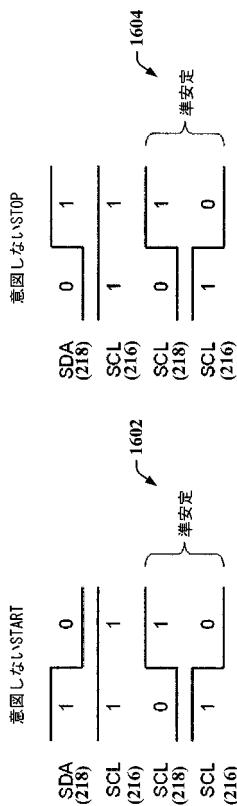

図16は、1つまたは複数のI2Cデバイスにおいて準安定状態が発生し得る条件を示す。準安定状態は、データ信号(SDA信号218)とクロック信号(SCL信号216)の両方が同じ時間1602、1604に変化するときのシグナリング状態を含み得る。

#### 【0051】

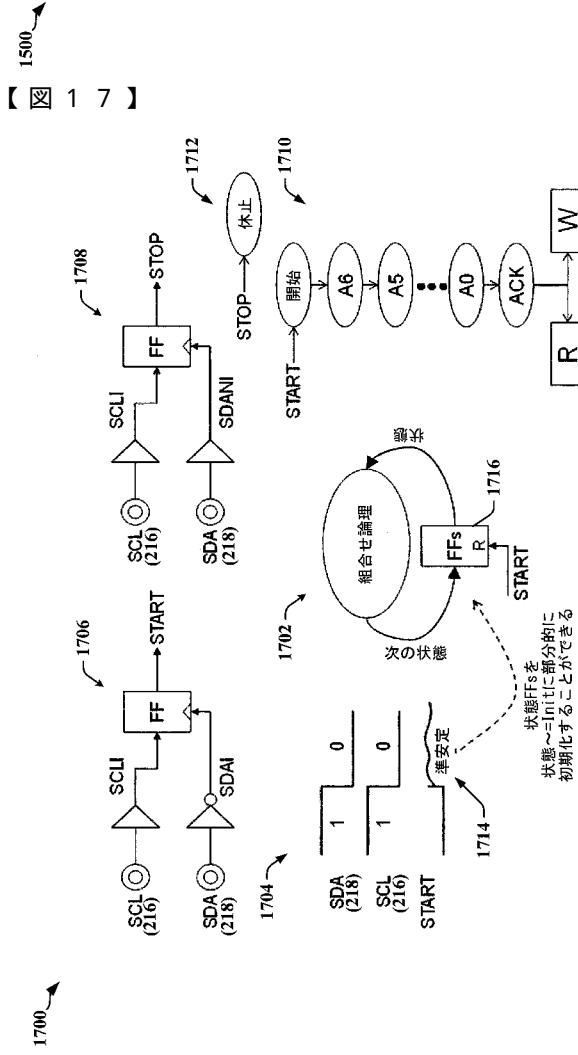

図17は、I2Cデバイス用の状態機械1702に対する、準安定状態の起こり得る影響を示す。I2Cプロトコルにおいて、状態機械1702は、I2Cフレームおよび/またはワードの送信および/または受信を追跡するように維持される。状態機械1702は、バスのSCL信号216およびSDA信号218中の遷移に基づいてトリガされる。状態機械は、スタート条件が検出されたときに初期化されるフリップフロップ1716を含み得る。スタート条件はスタート検出論理1706によって検出することができ、ストップ条件は第2の論理1708によって検出することができる。状態機械遷移は、スタート条件が検出された後、状態図1710に従って構成されてよく、状態機械1702は、ストップ条件が検出されたとき、リセットまたは休止されてよい(状態図1712参照)。SDA信号218とSCL信号216の両方が、スタート検出論理1706を、スタート条件の明らかな発生に応答させるように状態を変えたとき、準安定条件1714が発生し得る。

#### 【0052】

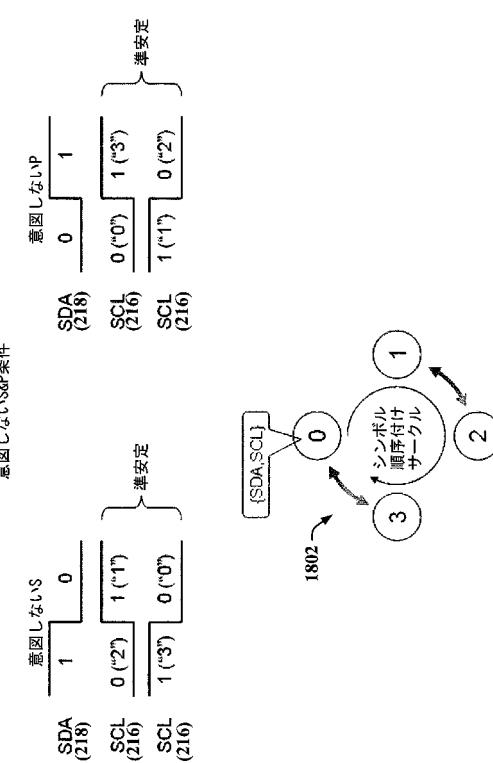

図18は、意図しないSTARTまたはSTOP条件を防止するために回避されてよい条件を示す。「シンボル」1802は、SDA信号218とSCL信号216との間の状態の組合せによって定義することができる。たとえば、シンボル「0」は、SDA信号218とSCL信号216の両方が低(0)であるときである。シンボル「1」は、SDA信号218が低(0)であり、SCL信号216が高(1)であるときである。シンボル「2」は、SDA信号218が高(1)であり、SCL信号216が低(0)であるときである。シンボル「3」は、SDA信号218が高(1)であり、SCLラインが高(1)であるときである。ここで、シンボル「2」からシンボル「1」への、およびシンボル「3」からシンボル「0」へのシンボル遷移が、STARTインジケータに対する準安定条件を引き起こすことが諒解されよう。同様に、シンボル「0」からシンボル「3」への、およびシンボル「2」からシンボル「1」へのシンボル遷移が、STOPインジケータに対する準安定条件を引き起こす。

#### 【0053】

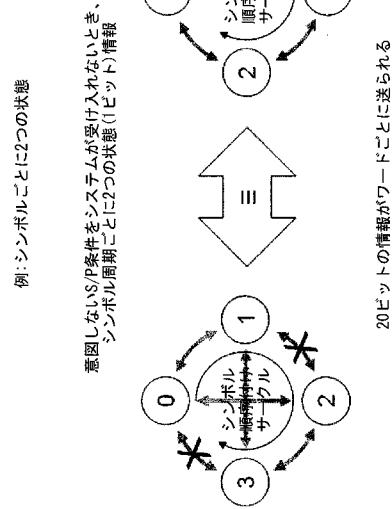

図19は、準安定条件を引き起こし得るシンボルの間のいくつかの遷移をなくすことができる技法を示す。この方式の下で、データスループットは低下することができ、効果的なデータスループットを増大させるため、ならびに元の12シンボルCClueシステムとの互換性を可能な限り保つために、ワードごとの20ビットが送られ得る。

#### 【0054】

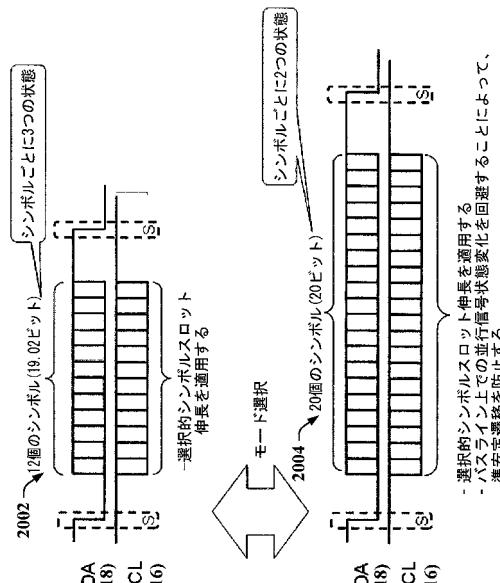

図20は、シンボルごとに3つの状態の12個のシンボルを使う第1の送信方式と、シンボルごとに2つの状態の20個のシンボルを使う第2の送信方式との間の比較を示す。第1の送信方式は、12個のシンボル内で19.02ビットを送信することができ、第2の送信方式は、20個のシンボル内で20ビットを送信することができる。

#### 【0055】

一態様によると、バスに結合されたマスタデバイスは、バスに結合されたレガシーI2Cデバイスがあるかどうか確かめることができる。どのレガシーI2Cデバイスもバスに結合されていない場合、CClueデバイスは、準安定条件を引き起こすことを心配する必要はなく、シンボルごとに3つの状態の12個のシンボルを送信することができる。

#### 【0056】

I2Cデバイスがバスに結合されている場合であっても、CClueデバイスは依然として、バ

10

20

30

40

50

ス上のすべてのレガシーI2Cデバイスが、同期して設計された論理回路を使う場合、シンボルスロット伸長も、準安定条件を回避しようと試みることもなく、および/または(シンボルスロットの選択的伸長の必要性ならびに準安定条件の可能性を回避することができる)適度に速いクロックを用いて、シンボルごとに3つの状態の12個のシンボルを送信することができる。

【0057】

バスに結合されたレガシーI2Cデバイスがあり、バス上のすべてのレガシーI2Cデバイスが、同期して設計され、準安定性の可能性と無縁であるが、いくつかのI2Cデバイスは状態機械変化を免れない場合、シンボルスロット伸長が使われてよい。CCleデバイスは依然として、シンボルごとに3つの状態の12個のシンボルを送信することができるが、伸長されたシンボルスロットにより、図12に示したように、平均9.6Mbpsということになり得る。

10

【0058】

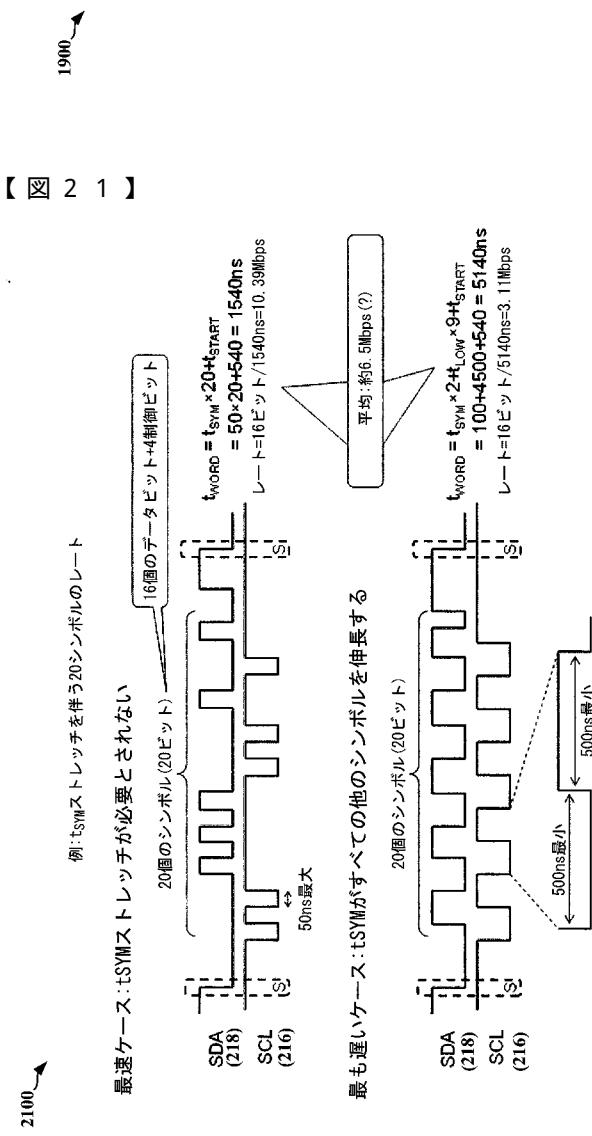

バスに結合されたレガシーI2Cデバイスがあり、レガシーI2Cデバイスのうちの少なくとも1つが、非同期に設計され、準安定性を受けやすい場合、準安定状態遷移を引き起こす、シンボルスロット伸長とシンボルの防止の両方が実装される。CCleデバイスは次いで、シンボルごとに2つの状態の20個のシンボルを送信することができ、これは平均6.5Mbpsになり得る(図21に示される)。

【0059】

図21は、CCle送信のための最速および最も遅いレートのシナリオを示し、ここで、20個のシンボル(シンボルごとに2つの状態がある)が、オーバーヘッドビットを含まずに、2つのSTARTインジケータの間で使われる。

20

【0060】

様々なデータスループットケースが、バスを介して可能であり得る。第1のケースにおいて、12シンボルCCle送信システムは、レガシーI2Cスレーブがバス上に存在しない場合、または同じバス上のすべてのデバイスが、 $t_{SYM}$ において各CCleワードの前のSTARTを適切に検出することができる場合、23Mbpsを達成し得る。第2のケースにおいて、同じバス上のすべてのレガシーI2Cデバイスが、シンボルスロットの選択的伸長の必要性ならびに準安定条件の可能性を回避する適度に速いクロッキングを用いて同期して設計されている場合、14Mbps向けの $t_{SYM}$ ストレッチを利用しない12シンボルCCle送信システムが使われ得る。第3のケースにおいて、同じバス上のすべてのレガシーI2Cデバイスが、同期して設計され、準安定性と無縁である場合、いくつかが上で論じた状態機械変化を免れない場合であっても、12シンボルCCle送信システムは、 $t_{SYM}$ ストレッチを用いて9.6Mbpsという平均を達成し得る。第4のケースにおいて、準安定性と状態機械問題の両方が存在する場合、20シンボルCCle送信システムが $t_{SYM}$ ストレッチとともに使われてよい。

30

【0061】

CCleインターフェースを利用するいくつかのシステムは、スレーブデバイスの同期を可能にするためにバスを介してCCleマスタデバイスによって定期的に送信されるCCle「ハートビート」ワードを定義することができる。マスタデバイスは、電力節約のために十分遅く、しかし、スレーブがクロックサイクルを渴望しない程度に十分速いレートで、この「ハートビート」CCleワードを送信してよい。一例によると、「ハートビート」は、図3に示されるCCle通信インターフェースに概ね従って、2線の制御データバスを通じた送信のためにデータビットを符号化するために使用される20ビットの3進数空間内に符号化され、または組み込まれ得る。

40

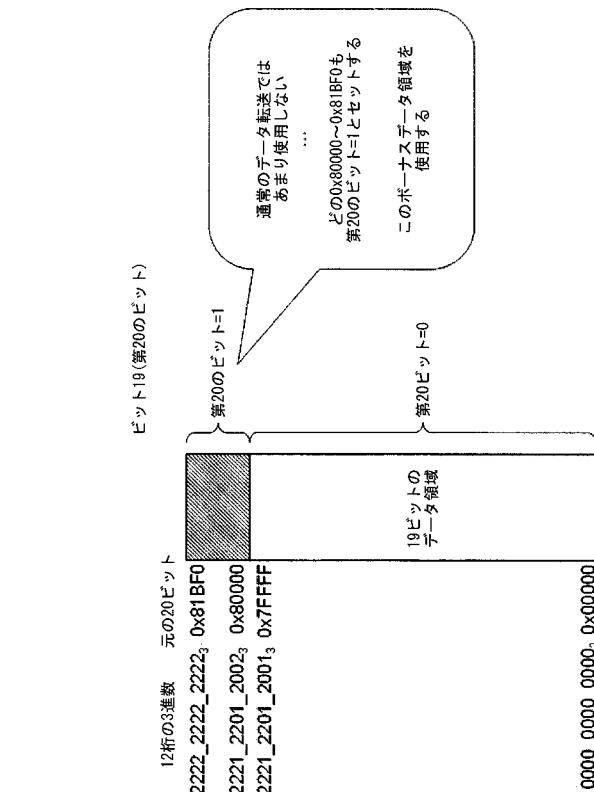

【0062】

図22は、第1のビット(ビット0)においてビットカウントがスタートしたときに送信される第20のビットであるビット19に関連したいくつかの態様を示す図2200である。言い換えれば、コンピュータ科学において一般的であるように、ビットごとのカウントは0において開始し、ビット19は第20のビットである。ここで、ビット0~18は、0000\_0000\_0000<sub>3</sub>~2221\_2201\_2001<sub>3</sub>としての3進数の範囲内で表される。2221\_2201\_2002<sub>3</sub>から2222\_2222\_222

50

2<sub>3</sub>の範囲内の3進数は、データ送信のためには使用されない。したがって、3進数の範囲221\_2201\_2002<sub>3</sub> ~ 2222\_2222\_2222<sub>3</sub>は、ビット19(すなわち、第20のビット)を表すために使用されてよい。言い換えると、2221\_2201\_2002<sub>3</sub>という3進数は、1000\_0000\_0000\_0000\_0000という2進数(0x80000という16進数)であり、2222\_2222\_2222<sub>3</sub>という3進数(0x81BF0)はとり得る最大の12桁の3進数である。一例では、スリープオンリーおよびスリープ除外コマンドが第20ビット(ビット19)を使う。ハートビートが送信され得るのは、この第20のビット(ビット19)の数空間内である。

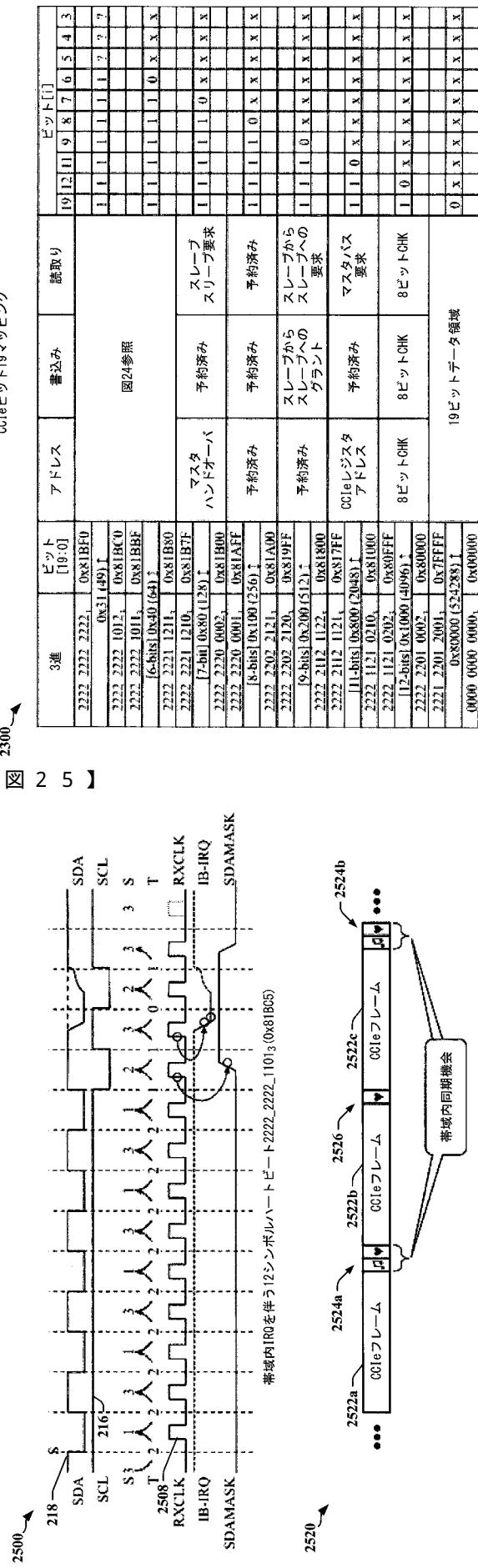

## 【0063】

図23は、CCl送信システムにおいて使われるマッピングの一例を示すテーブル2300である。このマッピングにおいて、ビット19の数空間は、数2221\_2201\_2002<sub>3</sub> ~ 2222\_2222\_2222<sub>3</sub>に及んでよく、この範囲の数は、6つの細区分に下位分割することができる。CClは、マルチマスター制御データバスアーキテクチャであり、制御データバスの制御は、あるマスターデバイスから別のマスターデバイスに移されてよい。したがって、「マスタバス要求」コマンド(サブレンジ2222\_1121\_0210<sub>3</sub> ~ 2222\_2112\_1121<sub>3</sub>内で)、ならびに「マスタハンドオーバ」が(サブレンジ2222\_2220\_0002<sub>3</sub> ~ 2222\_2221\_1210<sub>3</sub>内で)利用可能である。

10

## 【0064】

図24は、12シンボルCCl送信システムにおいてハートビートを定義するのに使われ得るビット19の数空間内の範囲を示すテーブル2400である。

## 【0065】

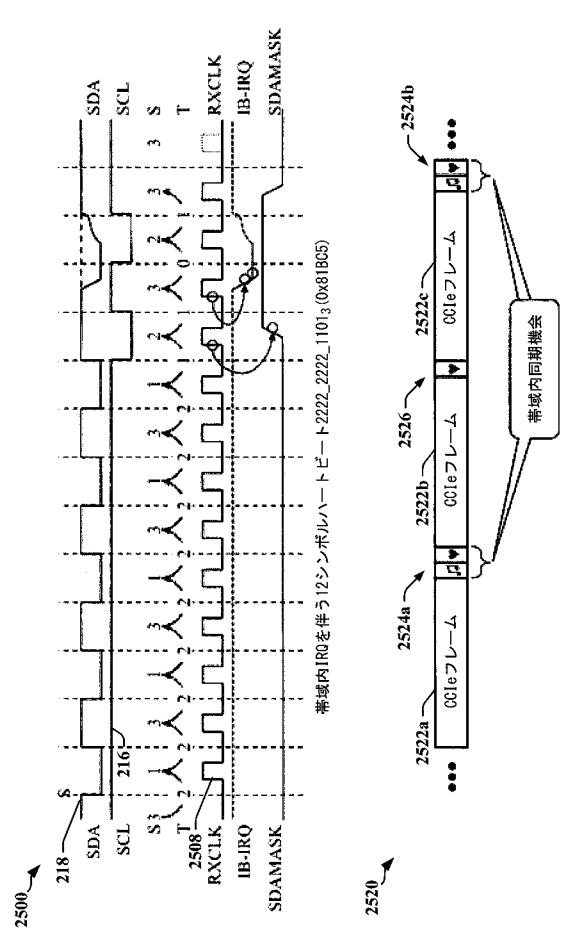

図25において、タイミング図2500は、12シンボルCCl送信システムにおける、SDA信号218およびSCL信号216を介した、ハートビートクロックの送信の一例を示す。受信機クロック(RXCLK信号)2508が、制御データバスを介して、送信シンボルの状態遷移から抽出され得る。この例は、ハートビートクロックが、送信もしくは符号化の前、ならびに/または受信および復号の後にどのように現れ得るかを示す。理解され得るように、ハートビートクロックの第1の部分2502はSDAライン上で送信されるが、ハートビートクロックの第2の部分2504はSCLライン上で送信され得る。このようにして、ハートビートクロックの一部をSCLラインに移動することによって、空間2506がSDAライン上に作られる。

20

## 【0066】

フレーミングタイミング図2520からわかるように、ハートビートクロックの送信は同期機会2524a、2524bを提供し得る。本明細書の他の箇所で記載するように、SYNCパターンの第1のワードは、「SY-」と呼ばれ、

30

## 【0067】

## 【数1】

“♪-”

## 【0068】

シンボル(音符の後にダッシュ)で示され、SYNCパターンの第2のワードは、「-NC」と呼ばれ、

40

## 【0069】

## 【数2】

“▼”

## 【0070】

シンボルで、または

## 【0071】

## 【数3】

“-♪”

## 【0072】

シンボル(音符の前にダッシュ)で示され得るハートビートである。SYNCは、いくつかのフ

50

レーム2522a、2522cの送信の後に送信される。図示される例において、同期機会2524a、2524bはSYNCを含む。いくつかの事例では、SYNCの代わりにハートビートワード2526が送信される。

#### 【0073】

図26は、20シンボルCCle送信モードで利用可能であり得るデータ範囲2604をもつ12シンボルCCle送信モードで利用可能なデータ範囲2602を比較する図面2600である。2つのデータ範囲2602、2604の各々の中のサブレンジ2606、2608は、第19のビットが論理1にセットされているワードを含んでよく、これらのサブレンジ2606、2608は、同期、ハートビートおよび制御情報を送信する能力を提供し得る。一例では、各CCle送信モードは、サブレンジ2606、2608内で送信される制御および/または同期ワードの対応するセットを有し得る。一例では、各CCle送信モードは、SYNCとして動作するワード(

10

#### 【0074】

#### 【数4】

♥/-♪

#### 【0075】

と表される)を与え得る。CCleバス上のスレーブID走査および割込みハンドリングに関連した情報を含む他の情報が、ビット19のサブレンジ2606、2608内で送信されてよい。

#### 【0076】

本明細書で開示するいくつかの態様によると、SYNC送信は、「SY-」ワードと、ハートビートワードに対応する「-NC」ワードとを含み得る。一例では、12シンボルモードで動作するデバイスが、SY-ワードとして0x81BF0を、およびハートビートワードとして0x81BC5を送信し得る。20シンボルモードで動作するとき、デバイスは、SY-ワードとして0xFFFFFを、およびハートビートワードとして0xFFFF8を送信することができる。SYNCは、CCle送信機の動作モードを識別するのに使うことができる。SYNCは、SDA信号218およびSCL信号216のシグナリング状態において、一意のパターンを生じ得る。一例では、SYNCは、12シンボルCCleインターフェース用に0x81BF0+0x81BC5を、および20シンボルCCleインターフェース用に0xFFFFF+0xFFFF8を含み得る。これらのワード組合せは、他のどのCCleデータ転送においても発生しない、かつ通常のI2Cモード送信において発生しない、一意のパターンを生じるように選択すればよい。

20

#### 【0077】

SYNCは、利用可能または可能な送信モードの間を区別するのに使うことができる。たとえば、CCleバスマスタが、20ビットデータを符号化するのにCCle送信が12個のシンボルそれとも20個のシンボルを使うかを示すための適切なSYNCを送信することができる。CCleバスマスタは、動作モードを示すためにSYNCパターンを定期的に送信してよく、送信の間の期間は、CCleバスへの、新たに加わったデバイスの、信頼できる効率的な同期を保証するように選択されてよい。たとえば、新たに加わったデバイスは、ホットプラグデバイス、または起動を完了した、かつ/もしくは電源切断/起動周期から回復中であるデバイスを含み得る。新たに加わったデバイスは、SYNCの検出および識別に基づいて、CCleワード境界に同期するように構成されてよい。

30

#### 【0078】

一例では、マスタデバイスは、SYNCパターンの送信頻度を判断することができ、SYNCパターンを可変頻度で送信することができる。マスタは、たとえば、システム起動の後、SYNCパターンを比較的頻繁に送信する場合がある。CCleバス上で加わり、起き、または起動するスレーブデバイスは、CCle送信を適切に監視し、送信し、または受信するために、SYNCパターンを求めるように適応されてよい。SYNC送信は、たとえば、エラー条件または構成要素故障による同期の喪失の後、同期を再獲得するのにも使うことができる。

40

#### 【0079】

いくつかの事例では、CCleスレーブデバイスは、同期と並行して、CCle送信モードを判断するように構成または適応され得る。一例では、モード検出は、SCL信号216およびSDA

50

信号218における遷移を比較することによって実施することができる。12シンボル送信モードでのハートビートワード(

【0080】

【数5】

◆

【0081】

、NC)の送信中、SDA信号218のシグナリング状態が前のシンボルの後に立ち上ると、SCL信号216のシグナリング状態は最初に、(論理0に)立ち下がる。SDA信号218およびSCL信号216のこの並行トグリングは、20シンボルCCle送信モードに対しては許可されず、というの 10

は、20シンボル送信モードは、ただ1つの信号がトグルしてよいと規定するからである。CCleスレーブデバイスは、SDA信号218およびSCL信号216中のエッジのタイミングに基づいて送信モードを検出することができる。

【0082】

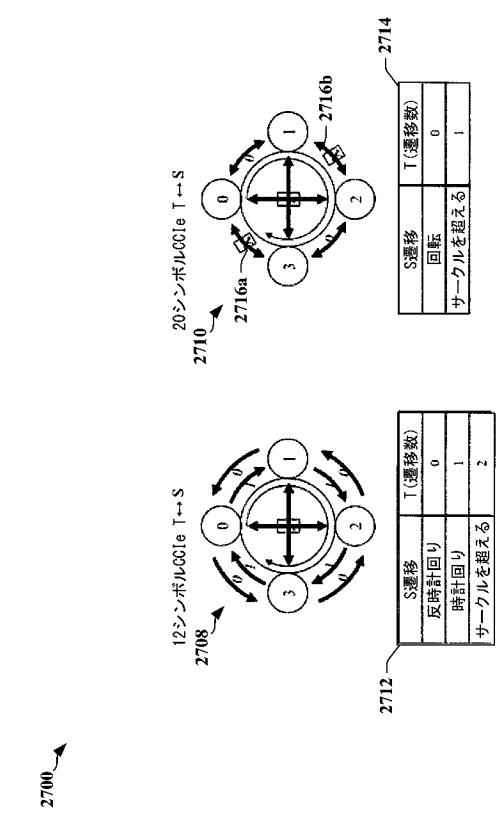

図27は、それぞれ、12シンボルおよび20シンボルモード動作用の遷移図2708、2710と、利用可能遷移の対応するテーブル2712、2714とを挙げる。図19に関して論じたように、20シンボル送信は、12シンボル送信におけるよりも少ない利用可能遷移を各シンボル間隔において有し、というの 20

は、いくつかの遷移2716aまたは2716bが、受信機におけるエラーの事例を削減するために禁止されるからである。バス上のCCleデバイスは、ハートビートワードが後に続くSYNCワードによってCCleワード境界と同期し得る。

【0083】

いくつかの事例では、送信の間のSDA信号218およびSCL信号216上で、符号化された要求をシグナリングすることによって、帯域内割込み要求(「帯域内IRQ」)が、1つまたは複数のCCleデバイスによって発行され得る。一例では、ハートビートワードが送信されると、スレーブCCleデバイスが帯域内IRQをアサートし得る。SYNC-ハートビートという組合せが送信されると、帯域内IRQは、ハートビートワードの送信中にアサートされ得る。

【0084】

いくつかの事例では、SYNCパターンが、省電力モード中に低速稼働クロックとして使われ得る。

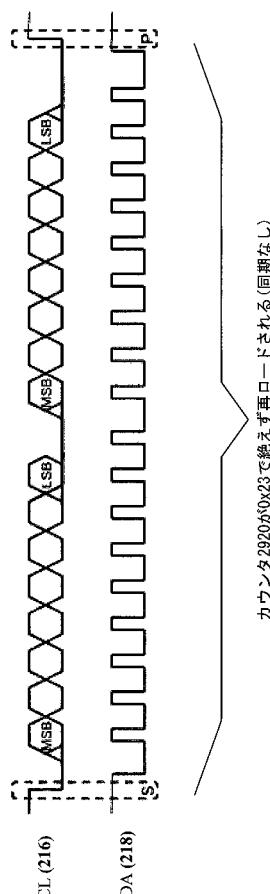

【0085】

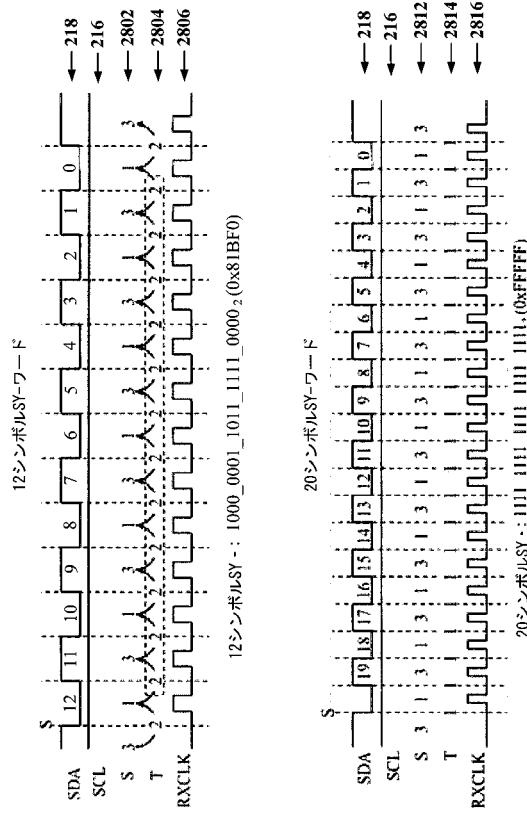

図28は、SDA信号218およびSCL信号216のシグナリング状態、CCleインターフェース上で送信されるシンボル2802、2812、ならびに12シンボルおよび20シンボル送信方式の両方についての対応する遷移数2804、2814を示すタイミング図2800、2810を挙げる。両方のモードにおいて、SDA信号218は、SCL信号216が高に留まる間、12または20個のシンボルからなるシーケンス中の各シンボル間隔においてトグルする。各モード向けに、受信クロック信号(RXCLK信号)2806、2816が、シンボルの間の検出された遷移に基づいて生成され、現在のシンボル2802、2812の値に従って駆動されるSDA信号218およびSCL信号216のシグナリング状態をサンプリングするのに使われる。

【0086】

CCle受信機は、CCleインターフェース上で送信されたSY-ワードを検出するように適応または構成されてよい。起動、すなわちCCleデバイスが動作環境に挿入されるホットプラグイベントの後、および/またはCCleバス上の送信との同期の喪失の検出もしくは通知後のCCleバスへの接続中にSY-検出が使われる。

【0087】

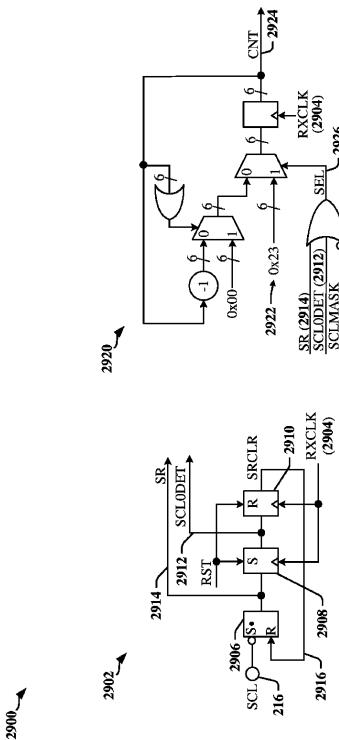

図29は、SYNC送信を検出するように構成することができるいくつかの回路を示すブロック図2900である。第1の回路2902が、SCL信号216を搬送する線上の論理低シグナリング状態(すなわち、SCL=0)を検出するのに使われ得る。SYNC送信中、SCL信号216は、有効なSYNCの持続時間は、高論理状態に留まる。論理低状態の検出は、SYNC検出周期またはカウンタを終了するのに使うことができる。第1の回路2902は、SCL信号216を受信する非同期S-Rラッチ2906を含み、フリップフロップ2908、2910は、SCL信号216が論理高に留まる場合は

10

20

30

40

50

低に留まるSCL低検出(SCL0DET)信号2912を生じるため、およびS-Rラッチ2906の出力(SR信号2914)をクリアするリセット信号2916を与えるための、S-Rラッチ2906の出力(SR信号2914)の2つの順序サンプルをキャプチャする。フリップフロップ2908および2910は、SCL信号216はCDR回路に対してマスクされているので、SDA信号218のみから復元されるRXCLK信号2904を使って計時される。

#### 【0088】

セレクタ信号(SEL信号2926)が低状態にあるとき、第2の回路(ダウンカウンタ2920)が有効にされる。SEL信号2926は、SCLMASK信号2928の状態がアクティブ(高)であるとともに、SR信号2914とSCL0DET信号2912の両方が低であるとき、低状態にあり、SR信号2914およびSCL0DET信号2912は、第1の回路2902によって生成される。SCLMASK信号2928の状態は、SCL信号216がクロック生成に使われないように、CDRからSCL信号216をマスクするようにセットされる。動作中、図示されるダウンカウンタ2920は、出力(CNT信号2924)が0x23という初期化値2922を反映するように初期化される。ダウンカウンタ2920は、制御信号2912および2914によって示されるように、SCL信号216において低レベル(SCL=0)が検出されると、またはSCLMASK信号2928の状態が論理0にセットされたとき、初期化される。SEL信号2926が低であるとき、ダウンカウンタ2920の出力は0に向かって減分される。

10

#### 【0089】

CCleデバイスは、CCleバス上での送信との同期の喪失が検出または通知されると、CDRへのSCL入力をブロックまたはマスクするために、SCLMASK信号2928の状態を論理1にセットすればよい。SYNC検出論理が次いで、有効にされ得る。SYNC検出中、SCLMASK信号2928は、CDRに、SDA信号218におけるシンボル遷移から、およびSCL信号216における遷移を使うことも考慮することもなく、クロック信号を生成させるように動作し得る。同期を達成すると、SCLMASK信号2928の状態はクリアされる。

20

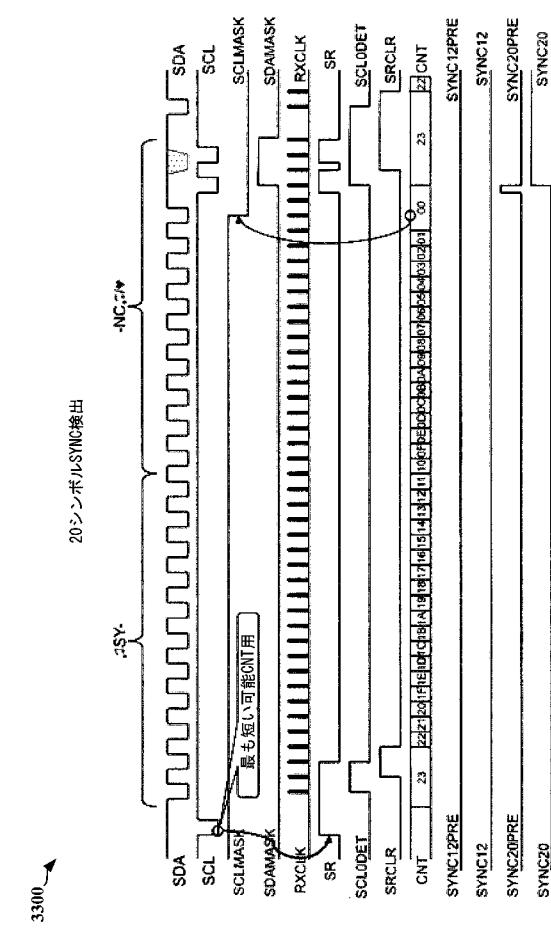

#### 【0090】

ダウンカウンタ2920は、どの利用可能モードに対しても、SYNC送信におけるシンボルの最大数を反映する値からカウントダウンし得る。図33および図34によって示される例において、ダウンカウンタ2920は、0x23(10進の35)という初期値2922に初期化される。ダウンカウンタ2920によって出力されたCNT信号2924は次いで、受信機クロック(RXCLK2904)の動作を通して、SDA信号218における各遷移において減分されてよい。SYNCワードの送信が完了されると、SCL信号216は降下し、有効な数の遷移がカウントされたかどうか判断するために、カウント値が調べられる。完全ワードの持続時間に対する高SCL信号216とトグリングSDA信号218の組合せは、SYNCワードに対してのみ発生し、カウント値は、認識されたCCle送信モード向けの送信におけるシンボルの数と一致する場合に有効である。

30

#### 【0091】

ダウンカウンタ2920は、SCL信号216において「0」値が検出されると、その初期値2922にリセットされ得る。SCL信号216は、CDRによって生じたRXCLK信号2904を使って計時されるS-Rラッチ2906、ならびにフリップフロップ2908および2910の動作を通してサンプリングされる。SCL信号216は、SYNC送信中は高に留まり、SYNC送信が完了されそうになった後、論理「0」値まで低く降下する(すなわち、2つのSCL=0パルスが、ワードを完成するに要求され得る)。いくつかの事例では、同期は、論理0(SCL=0)におけるSCL信号216の第1の検出において、いくつかの他の要求される条件が整っているとき、完了したと見なされる。SCLMASK信号2928の状態は、同期の検出が成功したとき、リセットされる。

40

#### 【0092】

##### マスキングを用いるクロックおよびデータ復元回路の例

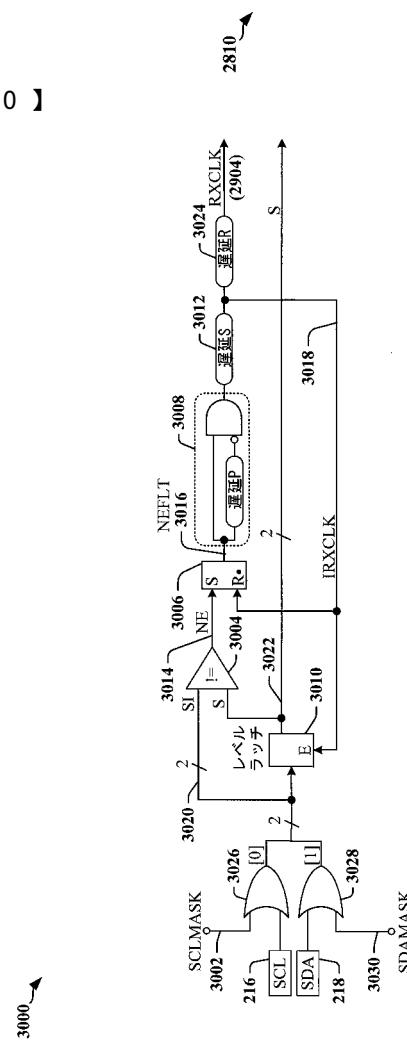

図30は、CCle通信リンクから埋め込みクロック情報を復元するのに利用することができるCDR回路3000の例を示すブロック図である。CDR回路3000は、SCL信号216および/またはSDA信号218のマスキングを許可するように適応される。この例では、第1のゲート3026におけるSCL信号216のブロッキングを可能にするために、SCLMASK信号3002が与えられてよく、第2のゲート3028におけるSDA信号218のブロッキングを可能にするために、SDAMASK信号3030が与えられてよい。いくつかの事例では、図示されるCDR回路3000および/または他の

50

CDR回路の他の変形体が使われてよい。

【0093】

SCL信号216およびSDA信号218中で、シンボルのシーケンスが受信される。対応する信号の状態が未定義、不確定、非常駐または場合によっては不安定であるシンボルの間には遷移時間が存在し得る。比較器3004、セットリセットラッチ3006、「遅延S」遅延要素3012、および(バス接続された)レベルラッチ3010は、入力(SI)信号3020の遅延されたインスタンスを表すレベルラッチされた信号(S信号)3022を生成するように構成されてよい。SI信号3020における変化の検出と、変化したS信号3022の出力との間の遅延は、遅延S遅延要素3012を構成することによって選択することができる。

【0094】

比較器3004は、SI信号3020をS信号3022と比較し、2進比較信号(NE信号)3014を出力する。セットリセットラッチ3006は、NE信号3014を比較器3004から受信し、NE信号3014のフィルタリングされたバージョンである信号(NEFLT信号)3016を出力することができる。セットリセットラッチ3006の動作は、NE信号3014中のいかなる非常駐不安定性(スパイク)も除去するように構成されてよい。NEFLT信号3016はワンショット回路3008に与えられ、回路3008は、NEFLT信号3016における立上りエッジに応答して、事前構成された固定長のパルスを生じる。ワンショット回路3008の出力は、現在のシンボルをキャプチャし、かつ/またはセットリセットラッチ3006をリセットするのに使われる内部受信クロック(IRXCLK)信号3018を与えるように、遅延要素3012を使って遅延させることができる。セットリセットラッチ3006の「リセット」入力は、NE信号3014の状態にかかわらず、IRXCLK信号3018が高であるとき、NEFLT信号3016がリセットされるように、優先され得る。

【0095】

一例では、IRXCLK信号3018は、RXCLK信号2904(図29参照)を与えるために、別の遅延要素3024を使って遅延させることができる。いくつかの事例では、IRXCLK信号3018は、外部回路構成によって、CDR回路3000のデータ出力をサンプリングするのに使うことができる。IRXCLK信号3018、またはIRXCLK信号3018の派生信号(たとえば、RXCLK信号2904)は、デコーダまたは直並列変換器回路に与えられ得る。いくつかの事例では、NEFLT信号3016など、他の信号が、外部回路構成向けのクロック信号を生成するのに使われてよい。レベルラッチ3010は、SI信号3020を受信するとともにS信号3022を出力し、ここで、レベルラッチ3010は、IRXCLK信号3018によってトリガされるか、さもなければ制御される。一例では、S信号3022は、CDR回路3000のシンボル出力として働き得る。他の例では、S信号3022を、CDR回路3000のシンボル出力として使用するために、遅延させ、ラッチし、かつ/または場合によっては条件づけるための追加回路構成が、CDR回路3000中に含まれ得る。

【0096】

動作中、比較器3004は、SI信号3020を、レベルラッチ3010から出力されるS信号3022と比較する。比較器3004は、SI信号3020とS信号3022とが等しいとき、NE信号3014を第1の状態(たとえば、論理低)に駆動し、SI信号3020とS信号3022とが等しくないとき、NE信号3014を第2の状態(たとえば、論理高)に駆動する。SI信号3020およびS信号3022が異なるシンボルを表すとき、NE信号3014は第2の状態にある。したがって、第2の状態は遷移が発生していることを示す。

【0097】

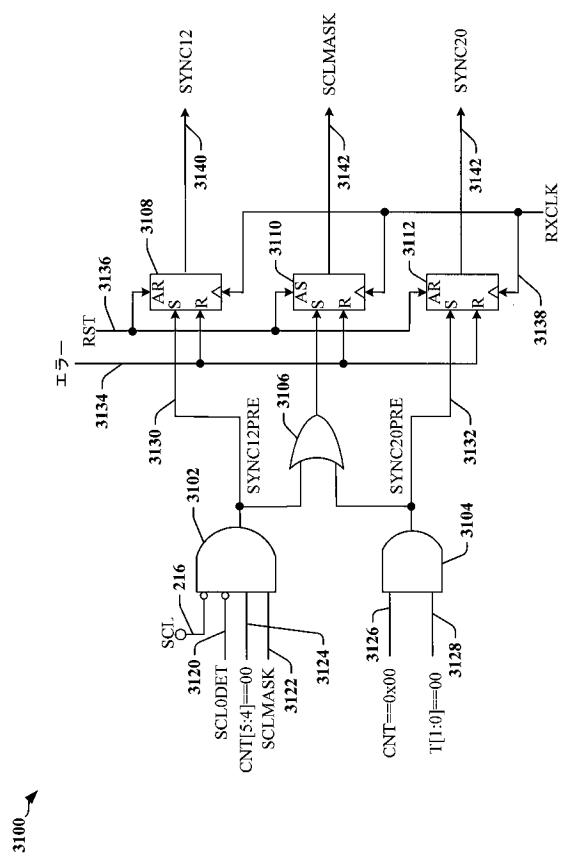

図31は、SCLMASK信号3142を生成するのに、およびCCl e送信モードを判断するのに使うことができる論理回路構成3100の例を示すブロック図である。図29への参照を続けると、論理回路構成3100は、SCL信号216、SCL0DET信号2912、SCLMASK信号2928の値に基づいてSYNC12PRE信号3130を生じるように構成された第1のゲート3102と、「00」とダウンカウンタ2920(図29参照)によって出力されるCNT信号2924の2つの最上位ビットとの間の比較の結果3124を生じるように構成された比較論理の出力とを含む。論理回路構成3100は、0x00と、CNT信号2924のすべてのビットとの間の比較の結果3128を生じるように構成された比較論理の出力に基づいて、SYNC20PRE信号3132も生じる。論理回路構成3100は、12シンボルCCl e送信モードに対して同期が達成されたことを示す信号(SYNC12)3140と、20シンボルCCl e

10

20

30

40

50

送信モードに対して同期が達成されたことを示す別の信号(SYNC20)3142とを生じ得る。CCle送信モードは、CNT信号2924の値の判断に少なくとも部分的に基づいて判断することができる。論理回路構成3100は、SCLMASK信号3142を生成することもでき、信号3142は、SDA MASK信号3030とともにCDR回路3000に与えられ得る。

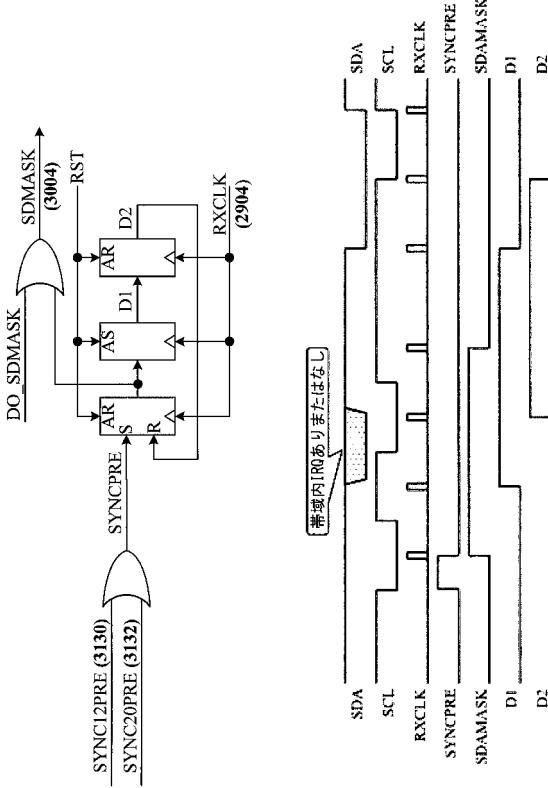

#### 【0098】

図32は、SDAMASK信号3206を生成するのに使われる論理回路構成3200のある例の動作を示すタイミング図3220を含む。SDAMASK信号は、たとえば、帯域内IRQ生成に使うことができる。

#### 【0099】

いくつかの事例では、CCle動作用に構成または適応されたデバイスは、複数のモードで動作することが可能であり得る。さらに、CCleバス上で利用可能な動作モードは、システムリセットまたは起動時ではなく、動作中に判断することができる。一例では、ホットプラグCCleデバイスは、12シンボルまたは20シンボルCCle送信モードに対応するSYNCパターンを待てばよい。CCleデバイスは、I2Cプロトコルを使って通信することも可能であり得るが、CCleデバイスは一般に、I2C通信タイミングに同期することは要求されない。

#### 【0100】

図35は、SCL信号216およびSDA信号218を介して送信される通信がI2Cプロトコルに準拠するときのSYNC検出論理の動作を示すタイミング図である。SCL信号216が論理低レベルにあるとき、SYNC論理は、有効なCCle送信を検出せず、カウンタは、その最大値にリセットされ得る。

#### 【0101】

##### フレーム同期

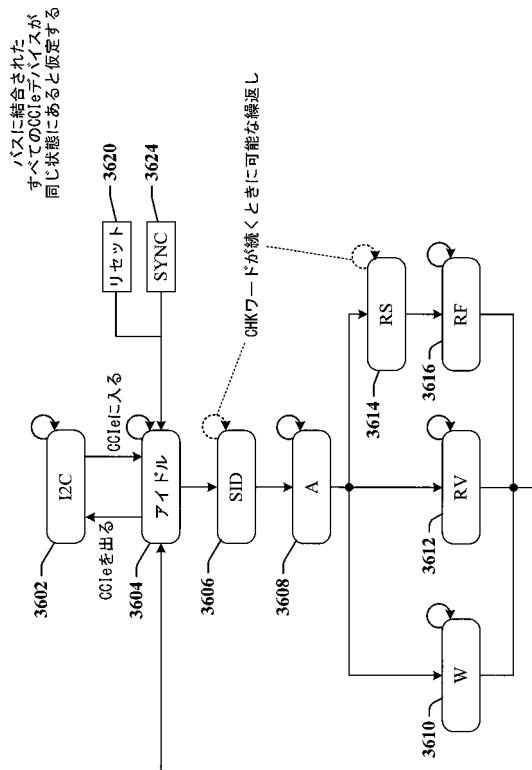

図36は、CCleとI2Cの混合環境において動作するCCleデバイス向けのフレーム同期プロセスを示す状態図3600である。最初に、CCleデバイスは、同一の動作モードにあり、フレームに同期されている。アイドル状態3604において、CCleデバイスは、I2C動作モードをサポートする状態3602に遷移し得る。I2CモードからCCleモードへの遷移は、CCleデバイスをアイドル状態3604に置き、この状態から、CCleデバイスはアクティブ通信状態3602、3606に遷移し得る。初期CCleアクティブ通信状態3606において、CCle通信は、CCleデバイスが、デバイスによって使われるスレーブIDに対応するスレーブIDを検出したときに始まり得る。スレーブは次いで、状態3608に入り、この状態で、アドレス情報を待つ。読み取りまたは書き込みが次いで、書き込み状態3610または1つもしくは複数の読み取り状態3612、3614、3616において完了される。いくつかのアクティブ状態3610、3612、または3616からの退出により、デバイスはアイドル状態3604に戻り得る。

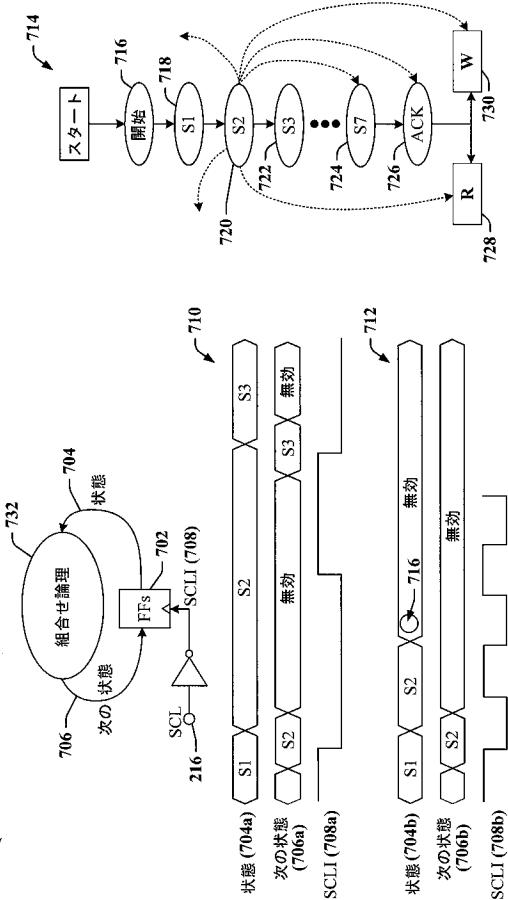

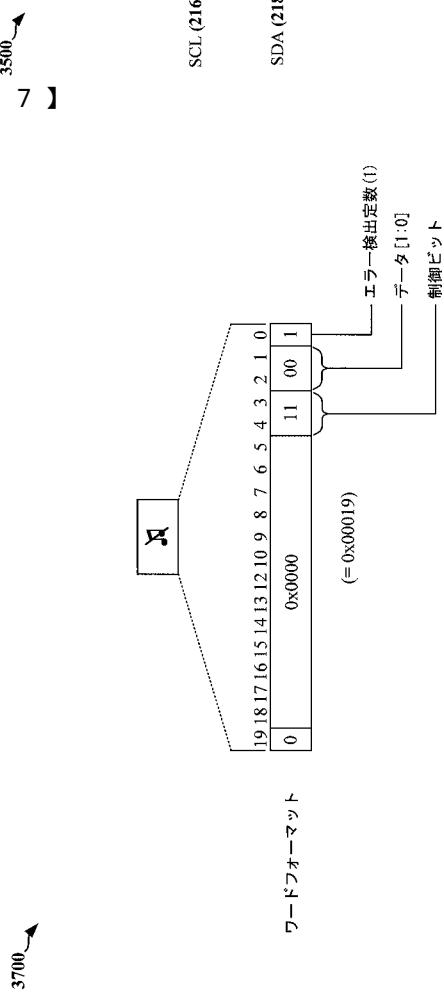

#### 【0102】

いくつかの事例では、CCleデバイスを非同期状態に置くことが望ましい場合がある。一例では、シリアルバスの動作モードの変化を容易にするか、または強制するために、デバイスが非同期状態に置かれ得る。一例では、CCleマスタが、同期を断つために意図的なシンボルエラーを送信し得る。図37は、CCleマスタによって、非同期状態への遷移に影響するように送信され得る、UNSYNCコード3700と呼ばれるCCleワードを示す。フレームは、0x0000にセットされた、およびエラー条件を示すように「1」にセットされたエラー検出ビットをもつSIDを有し得る。この送信は、UNSYNCコード3700と呼ばれる得る。UNSYNCコード3700を受信すると、スレーブデバイスが、非同期状態に降下し、CCleバスのシグナリング状態におけるSYNCパターンを探し始め得る。

#### 【0103】

##### シリアルバスの動作モードの間の遷移

本明細書で開示するいくつかの態様に従って適応されたマスタおよびスレーブデバイスは、複数の動作モードおよび/または複数のプロトコルをサポートするシリアルバスに結合され、そのシリアルバスを介して通信することができる。

#### 【0104】

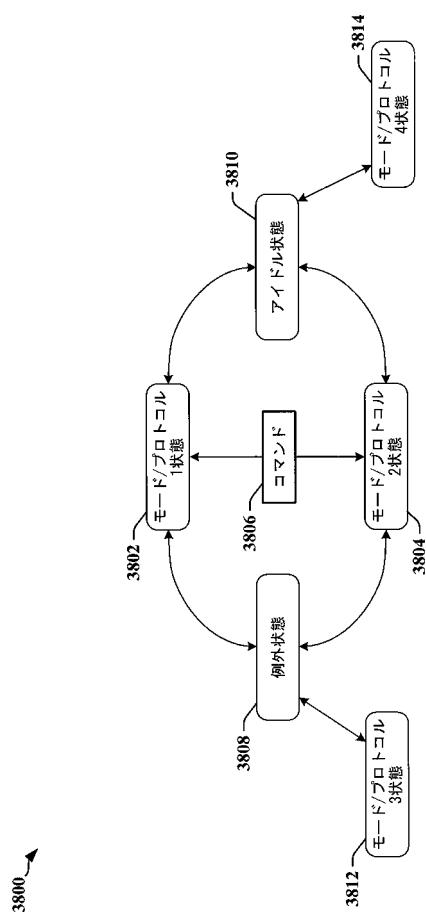

図38は、シリアルバスの動作モードの間、および/またはシリアルバス上で使うことが

10

20

30

40

50

できる複数のプロトコルの間を遷移するための一般化方式を示す流れ図3800である。各動作モードおよび/またはプロトコルは、対応するアクティブ状態3802、3804、3812、3814に関連付けられ得る。バスの動作モードは、シグナリング方式、データスループット、送信フォーマットなどの間を区別し得る。異なる動作モードがプロトコル用に定義されてよい。たとえば、12シンボルおよび20シンボルモードが、CCleプロトコル用に定義されてよい。

#### 【0105】

アクティブ状態3802、3804、3812、3814の間で、異なるタイプの遷移が利用可能であり得る。第1の例において、シリアルバスは、アイドル状態3810に入ることができ、この状態から、次のアクティブ状態3802、3804、3814が開始され得る。アイドル状態3810には、第1のプロトコルに従って通信する2つ以上のデバイスが、通信トランザクションを完了しているとともにバスを解放したとき、入ることができる。マスタデバイスなど、バスを介して通信することを望むデバイスは、調停および/または交渉を通してアイドル状態3810中にバスの制御を獲得することができ、調停プロセスに勝つと、通信を始めることができる。バスの制御を獲得したデバイスは、第1のプロトコルを使って通信を開始することができる。第2の、異なるプロトコルを使って通信するデバイスは、第1のプロトコルを伴う通信を無視するように構成されてよい。たとえば、I2Cデバイスは、共有バス上でのCCle通信を無視してよい。

10

#### 【0106】

第2の例において、アクティブ状態3802、3804、3812の間の遷移は、バスを強制的に「例外」状態3808にすることによって遂行することができる。例外状態3808は、スレーブデバイスがマスタデバイスと同期していないときに存在し得る。例外状態3808は、バスに結合されたデバイスのグループに対してリセットが実施された後で存在し得る。

20

#### 【0107】

第3の例において、アクティブ状態3802、3804の間の遷移は、コマンド3806のセットを使って実施することができる。たとえば、CCleマスタデバイスが12シンボル動作モードと20シンボル動作モードとの間で選択することを許可するコマンド構造が与えられ得る。CCleマスタは、遷移が発生した後、シリアルバスの制御を保持し得る。

#### 【0108】

アクティブ状態3802、3804、3812、および/または3814の間を遷移するための他の手段が企図される。いくつかの構成では、アイドル状態3810とコマンド3806の組合せが利用されてよい。たとえば、シリアルバスに結合されたいくつかのデバイスは、共通プロトコルにおいてデータを送信および/または受信するように構成され得る。後者の例において、構成、再構成、調停および/または交渉は、I2Cプロトコルを使ってアイドル状態3810から開始することができる。

30

#### 【0109】

いくつかの構成では、アクティブ状態3802、3804、3812、および/または3814の間を遷移するための複数の手段が利用され得る。I2C、CCI、および/またはCCleプロトコルの何らかの組合せをサポートするシリアルバス用に、プロトコル、プロトコルの変形体およびシグナリング方式の間の切替えが、UNSYNCコード3700(図37参照)および/または本明細書では一斉呼出しと呼ばれる専用制御ワードを使って遂行され得る。一例では、UNSYNCコード3700は、20シンボルおよび12シンボルCCle送信モードの間の変化を開始するために送信され得る。

40

#### 【0110】

プロトコルの間の(たとえば、I2CとCCleとの間の)、および/または20シンボルCCle送信モードと12シンボルCCle送信モードとの間の変化は、1つまたは複数の一斉呼出しの送信によって開始することができる。一斉呼出しは、あらかじめ定義されたコードワードを使って実装することができ、かつ/または予約済みSIDおよび/もしくはアドレスにアドレス指定することができる。一例では、SID[15:0]==0x0000のとき、CCleフレームが一斉呼出しとして識別され得る。マスタデバイスは、アドレスワードを使って、一斉呼出しのタイ

50

プを指定することができる。一斉呼出しは、スレーブデバイスに書き込み、またはそこから読み取ることができるデータワードとして送信されるペイロードを含み得る。

#### 【0111】

UNSYNCコード3700の使用により、リソース共有を通してCCleスレーブ内のハードウェアを最小化することができ、CCle送信モードの間のより高速な切替えを遂行することができる。対照的に、一斉呼出しは一般に、特別な復号論理および/またはモード切替え論理を必要とし、一斉呼出しは一般に、完了するのに特別なワード周期を必要とする。

#### 【0112】

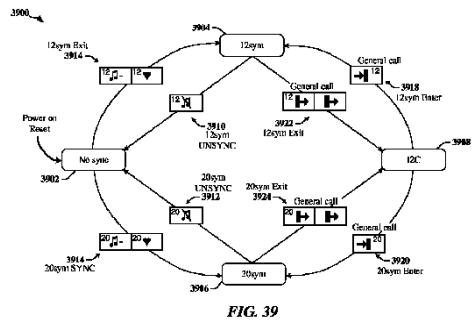

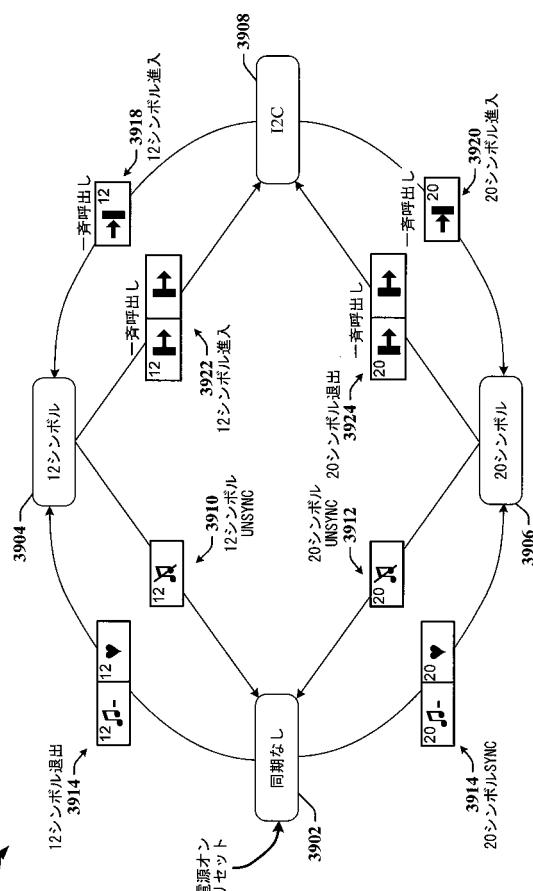

図39は、I2CモードとCCleモードとの間、およびCCle送信モードの間でのモード切替えを示す状態図3900である。一例では、UNSYNCコード3910が、スレーブデバイスを非同期モード3902にフォールバックさせるために、12シンボルCCle送信モード3904中に送信され得る。UNSYNCコード3912が、スレーブデバイスを非同期モード3902にフォールバックさせるために、20シンボルCCle送信モード3906中に送信され得る。UNSYNCコード3910は、エラーが検出されたときに実施され得る復元プロセスと同様の復元プロセスを、スレーブデバイスに効果的に実施させる。非同期モード3902は、電源オン、リセットまたはホットプラグの後で想定または開始されるデバイス状態と等価であり得る。

10

#### 【0113】

I2Cモード3908への遷移は、図示されるCCle送信モード3904、3906のいずれからでも開始され得る。したがって、非同期モード3902からI2Cモード3908への遷移は、CCleモード3904または3906のうちの1つへの遷移を含んでよく、このモードから、「12シンボル退出」一斉呼出し3922、または「20シンボル退出」一斉呼出し3924が発行され得る。I2Cモード3908からCCleモードへの遷移は、「12シンボル進入」I2C一斉呼出し3918、または20シンボルCCleに入るための「20シンボル進入」I2C一斉呼出し3920の使用を通して直接行うことができる。

20

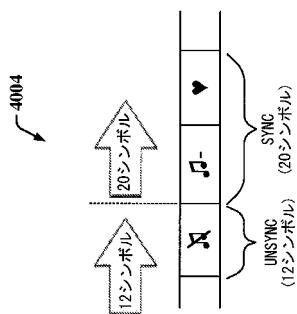

#### 【0114】

CCleモード3904と3906との間の遷移は、非同期モード3902を通じて遷移することによって遂行することができる。図40に示すように、20シンボルCCle送信モード3906から12シンボルCCle送信モード3904への遷移は、UNSYNCと、それに続く12シンボルSYNCパターンを送信するプロセス4002を伴い得る。12シンボルCCle送信モード3904から20シンボルCCle送信モード3906への遷移は、UNSYNCと、それに続く20シンボルSYNCパターンを送信するプロセス4004を伴い得る。

30

#### 【0115】

いくつかの回路システムおよび方法の追加説明

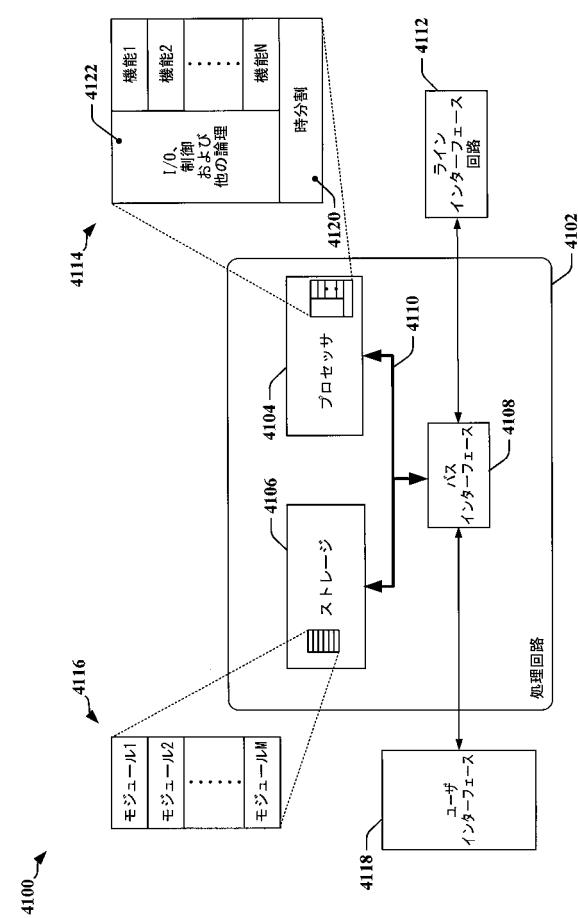

図41は、本明細書において開示される1つまたは複数の機能を実施するように構成することができる処理回路4102を利用する装置のためのハードウェア実施態様の簡略化された例を示す概念図4100である。本開示の様々な態様によると、本明細書で開示するような要素、または要素の任意の部分、または要素の任意の組合せは、処理回路4102を使用して実装されてもよい。処理回路4102は、ハードウェアモジュールとソフトウェアモジュールの何らかの組合せによって制御される1つまたは複数のプロセッサ4104を含んでもよい。プロセッサ4104の例は、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ(DSP)、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブル論理デバイス(PLD)、状態機械、シーケンサ、ゲート論理、個別ハードウェア回路、および本開示全体にわたって記載された様々な機能性を実施するように構成された他の適切なハードウェアを含む。1つまたは複数のプロセッサ4104は、特定の機能を実施し、ソフトウェアモジュール4116のうちの1つによって構成され、増強され、または制御されてもよい専用プロセッサを含んでもよい。1つまたは複数のプロセッサ4104は、初期化中にロードされたソフトウェアモジュール4116の組合せを通じて構成されてもよく、動作中に1つまたは複数のソフトウェアモジュール4116のローディングまたはアンローディングによってさらに構成されてもよい。

40

#### 【0116】

50

図示された例では、処理回路4102は、バス4110によって概略的に表されるバスアーキテクチャを用いて実装することができる。バス4110は、処理回路4102の具体的な適用例および全体的な設計制約に応じて、任意の数の相互接続するバスおよびブリッジを含む場合がある。バス4110は、1つまたは複数のプロセッサ4104およびストレージ4106を含む様々な回路を互いにリンクさせる。ストレージ4106は、メモリデバイスおよび大容量記憶デバイスを含んでもよく、本明細書ではコンピュータ可読媒体および/またはプロセッサ可読媒体と呼ばれる場合がある。バス4110は、タイミングソース、タイマー、周辺機器、電圧調整器、および電力管理回路などの様々な他の回路をリンクさせることもできる。バスインターフェース4108は、バス4110と1つまたは複数のトランシーバ4112との間のインターフェースを提供してもよい。トランシーバ4112は、処理回路によってサポートされるネットワーキング技術ごとに提供されてもよい。場合によっては、複数のネットワーキング技術が、トランシーバ4112の中に見出される回路または処理モジュールの一部または全部を共有してもよい。各トランシーバ4112は、伝送媒体を介して様々な他の装置と通信するための手段を提供する。装置の性質に応じて、ユーザインターフェース4118(たとえば、キーパッド、ディスプレイ、スピーカ、マイクロフォン、ジョイスティック)が設けられてもよく、直接またはバスインターフェース4108を通じてバス4110に通信可能に結合されてもよい。

10

## 【0117】

プロセッサ4104は、バス4110の管理、およびストレージ4106を含む場合があるコンピュータ可読媒体に記憶されたソフトウェアの実行を含む場合がある全体的な処理を担当することができる。この点で、プロセッサ4104を含む処理回路4102は、本明細書で開示する方法、機能および技法のうちのいずれかを実装するために使用され得る。ストレージ4106は、ソフトウェアを実行するとき、プロセッサ4104によって操作されるデータを記憶するために使用される場合があり、ソフトウェアは、本明細書において開示された方法のうちの任意の1つを実装するように構成される場合がある。

20

## 【0118】

処理回路4102内の1つまたは複数のプロセッサ4104はソフトウェアを実行することができる。ソフトウェアは、ソフトウェア、ファームウェア、ミドルウェア、マイクロコード、ハードウェア記述言語と呼ばれるか、または他の名称で呼ばれるかどうかにかかわらず、命令、命令セット、コード、コードセグメント、プログラムコード、プログラム、サブプログラム、ソフトウェアモジュール、アプリケーション、ソフトウェアアプリケーション、ソフトウェアパッケージ、ルーチン、サブルーチン、オブジェクト、実行可能ファイル、実行スレッド、プロシージャ、関数、アルゴリズムなどを意味するように広く解釈されるべきである。ソフトウェアは、コンピュータ可読の形でストレージ4106中または外部コンピュータ可読媒体中に存在することができる。外部コンピュータ可読媒体および/またはストレージ4106は、非一時的コンピュータ可読媒体を含んでもよい。非一時的コンピュータ可読媒体は、例として、磁気記憶デバイス(たとえば、ハードディスク、フロッピーディスク、磁気ストリップ)、光ディスク(たとえば、コンパクトディスク(CD)またはデジタル多用途ディスク(DVD))、スマートカード、フラッシュメモリデバイス(たとえば、「フラッシュドライブ」、カード、スティック、またはキードライブ)、ランダムアクセスメモリ(RAM)、読み取り専用メモリ(ROM)、プログラマブルROM(PROM)、消去可能PROM(EPROM)、電気的消去可能PROM(EEPROM)、レジスタ、リムーバブルディスク、およびコンピュータがアクセスし読み取ってもよいソフトウェアおよび/または命令を記憶するための任意の他の適切な媒体を含む。コンピュータ可読媒体および/またはストレージ4106は、例として、搬送波、伝送路、ならびに、コンピュータがアクセスし読み取ることができるソフトウェアおよび/または命令を送信するための任意の他の適切な媒体も含み得る。コンピュータ可読媒体および/またはストレージ4106は、処理回路4102中に存在するか、プロセッサ4104中に存在するか、処理回路4102の外部に存在するか、または処理回路4102を含む複数のエンティティにわたって分散され得る。コンピュータ可読媒体および/またはストレージ4106は、コンピュータプログラム製品において具現化され得る。例として、コ

30

40

50

ンピュータプログラム製品は、パッケージング材料中のコンピュータ可読媒体を含み得る。当業者は、特定の適用例およびシステム全体に課された全体的な設計制約に応じて、本開示全体にわたって提示する説明した機能性を最善の形で実装する方法を認識されよう。

【0119】

ストレージ4106は、ロード可能なコードセグメント、モジュール、アプリケーション、プログラムなどにおいて維持され、および/または編成されるソフトウェアを維持することができ、これは、本明細書ではソフトウェアモジュール4116と呼ばれる。ソフトウェアモジュール4116の各々は、処理回路4102にインストールまたはロードされ、1つまたは複数のプロセッサ4104によって実行されたとき、1つまたは複数のプロセッサ4104の動作を制御するランタイム画像4114に寄与する命令およびデータを含む場合がある。実行されると、いくつかの命令は、処理回路4102に、本明細書で説明するいくつかの方法、アルゴリズム、およびプロセスに従って機能を実施させることができる。

10

【0120】

ソフトウェアモジュール4116のうちのいくつかは、処理回路4102の初期化中にロードされてもよく、これらのソフトウェアモジュール4116は、本明細書で開示する様々な機能の実施を可能にするように処理回路4102を構成することができる。たとえば、いくつかのソフトウェアモジュール4116は、プロセッサ4104の内部デバイスおよび/または論理回路4122を構成することができ、たとえばトランシーバ4112、バスインターフェース4108、ユーザインターフェース4118、タイマー、数学的コプロセッサなどの外部デバイスへのアクセスを管理することができる。ソフトウェアモジュール4116は、割込みハンドラおよびデバイスドライバと対話し、処理回路4102によって提供される様々なリソースへのアクセスを制御する、制御プログラムおよび/またはオペレーティングシステムを含む場合がある。リソースには、メモリ、処理時間、トランシーバ4112へのアクセス、ユーザインターフェース4118などを含めてよい。

20

【0121】

処理回路4102の1つまたは複数のプロセッサ4104は、多機能とすることができ、それによって、ソフトウェアモジュール4116のいくつかは、ロードされ、異なる機能または同じ機能の異なるインスタンスを実施するように構成される。1つまたは複数のプロセッサ4104は、さらに、たとえば、ユーザインターフェース4118、トランシーバ4112、およびデバイスドライバからの入力に応答して開始されるバックグラウンドタスクを管理するように適応され得る。複数の機能の実施をサポートするために、1つまたは複数のプロセッサ4104は、マルチタスク環境を提供するように構成される場合があり、それにより、複数の機能の各々が、必要または要望に応じて、1つまたは複数のプロセッサ4104によってサービスされる1組のタスクとして実装される。一例では、マルチタスク環境は、異なるタスク間でプロセッサ4104の制御を渡す時分割プログラム4120を使用して実装される場合があり、それにより、各タスクは、任意の未処理動作の完了後、および/または割込みなどの入力に応答して、時分割プログラム4120に1つまたは複数のプロセッサ4104の制御を戻す。タスクが1つまたは複数のプロセッサ4104の制御を有するとき、処理回路は、事実上、制御するタスクに関連付けられた機能によって対処される目的に特化される。時分割プログラム4120は、オペレーティングシステム、ラウンドロビンベースで制御を移すメインループ、機能の優先順位付けに従って1つもしくは複数のプロセッサ4104の制御を割り振る機能、および/または、1つもしくは複数のプロセッサ4104の制御を処理機能に提供することによって外部イベントに応答する割込み駆動のメインループを含み得る。

30

【0122】

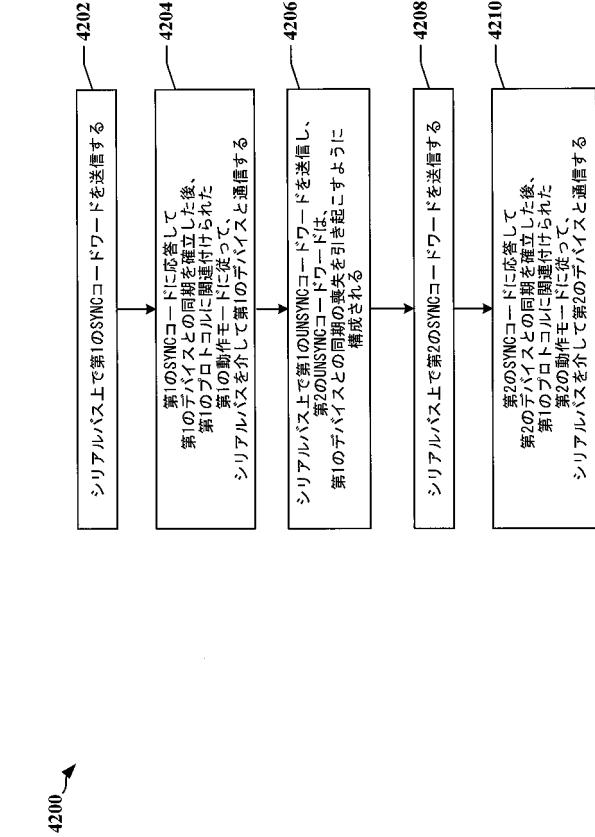

図42は、シリアルバス上でのデータ通信のための方法を示すフローチャート4200である。シリアルバスはPCIeバスであってよく、本方法において具陳される様々な手順および機能は、図2に示されるPCIeマスタデバイス220、図3に示されるデバイス(送信機300もしくは受信機320)、および/または本明細書に記載する他のデバイスの何らかの組合せを含むデバイスによって実施することができる。

40

【0123】

50

ロック4202において、マスタデバイス220が、シリアルバス上で第1のSYNCコードを送信し得る。第1のSYNCコードは、同期ワードおよびハートビートワードを含んでよく、ハートビートワードは、1つまたは複数のスレーブCCleデバイスがクロック信号を生成することを可能にし得る。

【0124】

ロック4204において、マスタデバイス220は、第1のSYNCコードに応答して、シリアルバスに結合された第1のデバイスとの同期を確立することができる。マスタデバイス220は、第1のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第1の動作モードに従って、シリアルバスを介して第1のデバイスと通信することができる。

【0125】

ロック4206において、マスタデバイス220は、シリアルバス上でUNSYNCコードを送信することができ、ここでUNSYNCコードは、第1のデバイスとの同期の喪失を引き起こすように構成される。UNSYNCコードは、エラー条件のインジケータを含み得る。エラー条件のインジケータの存在により、第1のデバイスは非同期状態に入り得る。

【0126】

ロック4208において、マスタデバイス220が、シリアルバス上で第2のSYNCコードを送信し得る。

【0127】

ロック4210において、マスタデバイス220は、第2のSYNCコードに応答して、シリアルバスに結合された第2のデバイスとの同期を確立することができる。マスタデバイス220は、第2のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第2の動作モードに従って、シリアルバスを介して第2のデバイスと通信することができる。

【0128】

一例では、第1のプロトコルはCCleプロトコルである。第1の動作モードは、シリアルバス上で送信されるべき12個のシンボル中でデータワードが符号化される動作モードに対応し得る。第1のSYNCコードは、シリアルバス上で、12個のシンボルからなるシーケンスを送信することによって送信され得る。12個のシンボルからなるシーケンスは、CCleバスのSCL線を、12個のシンボルからなるシーケンスの送信中、論理高シグナリング状態に留まらせるように構成または選択されてよい。SDA線は、12個のシンボルからなるシーケンスの連続するシンボルの間の各遷移において、シグナリング状態を変えることができる。

【0129】

別の例では、第1のプロトコルはCCleプロトコルである。第1の動作モードは、シリアルバス上で送信されるべき20個のシンボル中でデータワードが符号化される動作モードに対応し得る。第1のSYNCコードは、シリアルバス上で、20個のシンボルからなるシーケンスを送信するためのトランシーバを使って送信され得る。20個のシンボルからなるシーケンスは、CCleバスのSCL線を、20個のシンボルからなるシーケンスの送信中、論理高シグナリング状態に留まらせるように構成または選択されてよい。SDA線は、20個のシンボルからなるシーケンスの連続するシンボルの間の各遷移において、シグナリング状態を変えることができる。

【0130】

第1のプロトコルがCCleプロトコルである場合、第1のデバイスと通信することは、シンボルのシーケンス中で、スレーブCCleデバイスに1つまたは複数のデータワードを送信することを含み得る。

【0131】

いくつかの事例では、デバイスは、シリアルバス上で一斉呼出しを送信し得る。一斉呼出しは、シリアルバスをアイドル状態に入らせることができる。デバイスは、シリアルバスがアイドル状態に入った後、第2のプロトコルを使って、シリアルバスに結合された第3のデバイスと通信することができる。第1のプロトコルはCCleプロトコルであってよく、第2のプロトコルはI2Cプロトコルであってよい。シリアルバスに接続された少なくとも1つのデバイスは、I2Cプロトコルを使う通信に制限され得る。

10

20

30

40

50

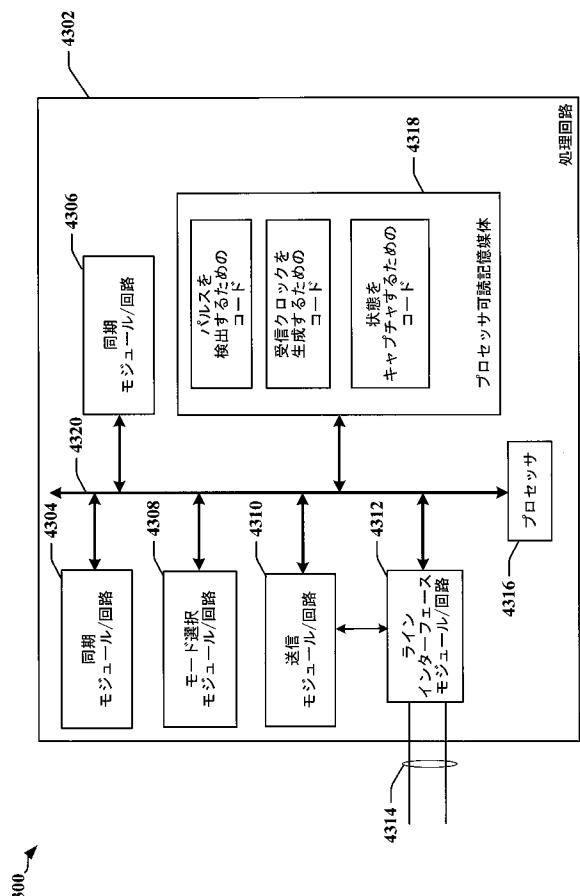

## 【0132】

図43は、処理回路4302を採用する装置4300のためのハードウェア実装の簡略化された例を示す図である。処理回路は、一般に、マイクロプロセッサ、マイクロコントローラ、デジタル信号プロセッサ、シーケンサ、および状態機械のうちの1つまたは複数を含み得るプロセッサ4316を有する。処理回路4302は、バス4320によって概して表されるバスアーキテクチャを用いて実装され得る。バス4320は、処理回路4302の具体的な用途および全体的な設計制約に応じて、任意の数の相互接続バスおよびブリッジを含み得る。バス4320は、プロセッサ4316、モジュールまたは回路4304、4306、4308、および4310、コネクタまたはワイヤ4314を介して通信するように構成可能なラインインターフェース回路4312、ならびにコンピュータ可読記憶媒体4318によって表される、1つもしくは複数のプロセッサおよび/またはハードウェアモジュールを含む様々な回路を互いにリンクする。バス4320は、タイミングソース、周辺機器、電圧調整器、および電力管理回路などの様々な他の回路をリンクさせてもよいが、これらの回路は当技術分野でよく知られており、したがって、これ以上は説明しない。

10

## 【0133】

プロセッサ4316は、コンピュータ可読記憶媒体4218に記憶されたソフトウェアの実行を含む全体的な処理を担当する。ソフトウェアは、プロセッサ4316によって実行されると、処理回路4302に、任意の特定の装置のための上記で説明した様々な機能を実施させる。コンピュータ可読記憶媒体4318は、ソフトウェアを実行するとき、コネクタ4314を介して送信されるシンボルから復号されたデータを含めて、プロセッサ4316によって操作されるデータを記憶するために使用されてもよい。処理回路4302は、モジュール4304、4306、4308、および4310のうちの少なくとも1つをさらに含む。モジュール4304、4306、4308、および4310は、プロセッサ4316の中で動作しコンピュータ可読記憶媒体4318に常駐する/記憶されるソフトウェアモジュール、プロセッサ4316に結合された1つもしくは複数のハードウェアモジュール、またはそれらの何らかの組合せであってもよい。モジュール4304、4306、4308および/または4310は、マイクロコントローラ命令、状態機械構成パラメータ、またはそれらの何らかの組合せを含み得る。

20

## 【0134】

一構成では、ワイヤレス通信のための装置4300は、同期コードを生成するためのモジュールおよび/または回路4304、一斉呼出しを含むコマンドを生成するためのモジュールおよび/または回路4306、プロトコルおよび動作モードを選択するためのモジュールおよび/または回路4308、プロトコルおよび/または動作モードの間を遷移するために、シリアルバス上でSYNC、UNSYNCおよび/または一斉呼出しを送信するためのモジュールおよび/または回路4310を含む。

30

## 【0135】

一例では、処理回路4302は、コンピュータ可読記憶媒体4318中で維持される命令を実行することができ、そのような実行により、装置4300は、第1のSYNCコードに応答して、コネクタ4314に結合された第1のデバイスとの同期を確立し、第1のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第1の動作モードに従って、コネクタ4314を介して第1のデバイスと通信し、コネクタ4314上でUNSYNCコードを送信し、ここでUNSYNCコードは、第1のデバイスとの同期の喪失を引き起こすように構成され、コネクタ4314上で第2のSYNCコードを送信し、第2のSYNCコードに応答して、コネクタ4314に結合された第2のデバイスとの同期を確立し、第2のデバイスとの同期を確立した後、第1のプロトコルに関連付けられた第2の動作モードに従って、コネクタ4314を介して第2のデバイスと通信する。

40

## 【0136】

上述した手段は、たとえば、プロセッサまたは制御論理212、トランシーバ210およびラインドライバ/受信機214a、214bならびに記憶媒体またはレジスタ206および/または210bを含む物理層デバイスの何らかの組合せを使って実装されてよい。

## 【0137】

50

開示したプロセスにおけるステップの特定の順序または階層は、例示的な手法の一例であることを理解されたい。設計上の優先事項に基づいて、プロセスにおけるステップの特定の順序または階層が並べ替えられてもよいことを理解されたい。添付の方法クレームは、様々なステップの要素を例示的な順序で提示したものであり、提示された特定の順序または階層に限定されることを意味するものではない。

#### 【0138】

上記の説明は、本明細書で説明される様々な態様を当業者が実践できるようにするために与えられる。これらの態様に対する様々な変更形態は、当業者に容易に明らかになり、本明細書において規定される一般原理は、他の態様に適用される場合がある。したがって、特許請求の範囲は本明細書に示された態様に限定されるものではなく、文言通りの特許請求の範囲に整合するすべての範囲を与えられるべきであり、単数形の要素への言及は、そのように明記されていない限り、「唯一無二の」を意味することを意図せず、「1つまたは複数の」を意味する。別段に明記されていない限り、「いくつかの」という用語は1つまたは複数を指す。当業者に知られている、または後に知られるようになる、本開示全体にわたって説明する様々な態様の要素の構造的および機能的な均等物のすべては、参照により本明細書に明確に組み込まれ、特許請求の範囲によって包含されるように意図されている。さらに、本明細書で開示するいかなる内容も、そのような開示が特許請求の範囲で明示的に記載されているかどうかにかかわらず、公に供することは意図されていない。いかなるクレーム要素も、要素が「ための手段」という語句を使用して明確に記載されていない限り、ミーンズプラスファンクションとして解釈されるべきではない。

10

20

30

40

50

#### 【符号の説明】

#### 【0139】

- 100 装置

- 102 処理回路

- 106 トランシーバ

- 108 特定用途向けIC(ASIC)

- 110 アプリケーションプログラミングインターフェース(API)

- 112 メモリ、メモリデバイス

- 114 ローカルデータベース

- 122 アンテナ

- 124 ディスプレイ

- 126 キーパッド

- 128 ボタン

- 200 装置

- 202 デバイス、イメージングデバイス

- 204 センサー制御機能

- 206 構成レジスタ、記憶媒体、レジスタ

- 208 クロック生成回路

- 210 トランシーバ

- 210a 受信機

- 210b 共通回路、記憶媒体、レジスタ

- 210c 送信機

- 212 制御論理、プロセッサ

- 214a ラインドライバ/受信機

- 214b ラインドライバ/受信機

- 216 SCL信号、信号

- 218 SDA信号、信号

- 220 デバイス、CCl eマスタデバイス、マスタデバイス

- 222a ~ n デバイス

- 230 CCl eバス

|      |                      |    |

|------|----------------------|----|

| 300  | 送信機                  |    |

| 302  | トランスコーダ              |    |

| 304  | エンコーダ                |    |

| 306  | ラインドライバ              |    |

| 308  | オープンドレイン出力トランジスタ     |    |

| 310  | 入力データ                |    |

| 312  | 3進数                  |    |

| 314  | シンボル                 |    |

| 320  | 受信機、受信回路             | 10 |

| 322  | 回路、トランスコーダ           |    |

| 324  | 回路、デコーダ              |    |

| 326  | ラインインターフェース回路        |    |

| 328  | クロックおよびデータ復元(CDR)回路  |    |

| 330  | 出力データ要素              |    |

| 334  | シンボル                 |    |

| 336  | シンボル                 |    |

| 338  | 受信クロック、クロック          |    |

| 402  | シンボル順序付けサークル         |    |

| 422  | Psシンボル、前のシンボル        |    |

| 424  | 現在のシンボル              | 20 |

| 426  | 3進数、遷移数              |    |

| 502  | スレーブ識別子(スレーブID)      |    |

| 512  | 読み取り/書き込みビット         |    |

| 602  | スレーブID、シーケンス         |    |

| 604  | スレーブID、シーケンス         |    |

| 606  | START状態              |    |

| 608  | START状態              |    |

| 610  | START状態              |    |

| 612  | パルス                  |    |

| 614  | クロック信号               | 30 |

| 622  | 12シンボルの送信、CCl e送信、送信 |    |

| 624  | 12シンボルの送信、CCl e送信、送信 |    |

| 626  | START状態              |    |

| 628  | START状態              |    |

| 630  | START状態              |    |

| 700  | 状態機械                 |    |

| 702  | 状態                   |    |

| 706  | SLCIライン              |    |

| 706b | クロック信号               |    |

| 708  | SLCIライン              | 40 |

| 716  | 状態、無効状態値             |    |

| 732  | 組合せ論理、論理             |    |

| 802  | CCl eシンボル送信          |    |

| 1008 | パルス                  |    |

| 1106 | 第2のシンボルパルス           |    |

| 1110 | 第1のパルス               |    |

| 1111 | 第2のパルス               |    |

| 1112 | 第3のシンボルパルス           |    |

| 1114 | 第1のシンボルパルス           |    |

| 1120 | 第1のシンボルスロット、シンボルスロット | 50 |

|       |                        |    |

|-------|------------------------|----|

| 1120' | 伸長されたシンボルスロット          |    |

| 1122  | 第2のシンボルスロット            |    |

| 1122' | 伸長されたシンボルスロット          |    |

| 1124  | 第3のシンボルスロット            |    |

| 1124' | 伸長されたシンボルスロット          |    |

| 1402  | 第5のシンボルスロット            |    |

| 1404  | 第2のシンボルスロット            |    |

| 1406  | 後続パルス                  |    |

| 1502  | シンボルスロット               | 10 |

| 1504  | シンボルスロット               |    |

| 1702  | 状態機械                   |    |

| 1706  | スタート検出論理               |    |

| 1708  | 第2の論理                  |    |

| 1714  | 準安定条件                  |    |

| 1716  | フリップフロップ               |    |

| 1802  | シンボル                   |    |

| 2508  | 受信機クロック(RXCLK信号)       |    |

| 2522a | フレーム                   |    |

| 2522c | フレーム                   |    |

| 2524a | 同期機会                   | 20 |

| 2524b | 同期機会                   |    |

| 2526  | ハートビートワード              |    |

| 2602  | データ範囲                  |    |

| 2604  | データ範囲                  |    |

| 2606  | サブレンジ                  |    |

| 2608  | サブレンジ                  |    |

| 2716a | 遷移                     |    |

| 2716b | 遷移                     |    |

| 2802  | 現在のシンボル、シンボル           |    |

| 2812  | 現在のシンボル、シンボル           | 30 |

| 2806  | 受信クロック信号(RXCLK信号)      |    |

| 2816  | 受信クロック信号(RXCLK信号)      |    |

| 2902  | 第1の回路                  |    |

| 2904  | RXCLK信号                |    |

| 2906  | 非同期S-Rラッチ、S-Rラッチ       |    |

| 2908  | フリップフロップ               |    |

| 2910  | フリップフロップ               |    |

| 2912  | SCL低検出(SCL0DET)信号、制御信号 |    |

| 2914  | SR信号、制御信号              |    |

| 2916  | リセット信号                 | 40 |

| 2920  | ダウンカウンタ                |    |

| 2922  | 初期化値、初期値               |    |

| 2924  | CNT信号                  |    |

| 2926  | SEL信号                  |    |

| 2928  | SCLMASK信号              |    |

| 3000  | CDR回路                  |    |

| 3002  | SCLMASK信号              |    |

| 3004  | 比較器                    |    |

| 3006  | セットリセットラッチ             |    |

| 3008  | ワンショット回路               | 50 |

|      |                                   |    |

|------|-----------------------------------|----|

| 3010 | レベルラッチ                            |    |

| 3012 | 「遅延S」遅延要素、遅延要素                    |    |

| 3014 | 2進比較信号(NE信号)                      |    |

| 3016 | 信号(NEFLT信号)                       |    |

| 3018 | 内部受信クロック(IRXCLK)信号                |    |

| 3020 | 入力(SI)信号                          |    |

| 3022 | 信号(S信号)                           |    |

| 3024 | 遅延要素                              |    |

| 3026 | 第1のゲート                            | 10 |

| 3028 | 第2のゲート                            |    |

| 3030 | SDAMASK信号                         |    |

| 3100 | 論理回路構成                            |    |

| 3102 | 第1のゲート                            |    |

| 3124 | 比較の結果                             |    |

| 3128 | 比較の結果                             |    |

| 3130 | SYNC12PRE信号                       |    |

| 3132 | SYNC20PRE信号                       |    |

| 3140 | 信号(SYNC12)                        |    |

| 3142 | SCLMASK信号、信号(SYNC20)              |    |

| 3200 | 論理回路構成                            | 20 |

| 3206 | SDAMASK信号                         |    |

| 3602 | 状態、アクティブ通信状態                      |    |

| 3604 | アイドル状態                            |    |

| 3606 | アクティブ通信状態、初期CCleアクティブ通信状態         |    |

| 3608 | 状態                                |    |

| 3610 | 書き込み状態、アクティブ状態                    |    |

| 3612 | 読み取り状態、アクティブ状態                    |    |

| 3614 | 読み取り状態                            |    |

| 3616 | 読み取り状態、アクティブ状態                    |    |

| 3700 | UNSYNCコード                         | 30 |

| 3802 | アクティブ状態                           |    |

| 3804 | アクティブ状態                           |    |

| 3806 | コマンド                              |    |

| 3808 | 「例外」状態                            |    |

| 3810 | アイドル状態                            |    |

| 3812 | アクティブ状態                           |    |

| 3814 | アクティブ状態                           |    |

| 3902 | 非同期モード                            |    |

| 3904 | 12シンボルCCle送信モード、CCle送信モード、CCleモード | 40 |

| 3906 | 20シンボルCCle送信モード、CCle送信モード、CCleモード |    |

| 3908 | I2Cモード                            |    |

| 3910 | UNSYNCコード                         |    |

| 3912 | UNSYNCコード                         |    |

| 3918 | 「12シンボル進入」I2C一斉呼出し                |    |

| 3920 | 「20シンボル進入」I2C一斉呼出し                |    |

| 3922 | 「12シンボル退出」一斉呼出し                   |    |

| 3924 | 「20シンボル退出」一斉呼出し                   |    |

| 4102 | 処理回路                              |    |

| 4104 | プロセッサ                             |    |

| 4106 | ストレージ                             | 50 |

- |      |                |

|------|----------------|

| 4108 | バスインターフェース     |

| 4110 | バス             |

| 4112 | トランシーバ         |

| 4114 | ランタイム画像        |

| 4116 | ソフトウェアモジュール    |

| 4118 | ユーチュイナーフェース    |

| 4120 | プログラム、時分割プログラム |

| 4122 | 論理回路           |

| 4300 | 装置             |

| 4302 | 処理回路           |

| 4304 | モジュールまたは回路     |

| 4306 | モジュールまたは回路     |

| 4308 | モジュールまたは回路     |

| 4310 | モジュールまたは回路     |

| 4312 | ラインインターフェース回路  |

| 4314 | コネクタ、ワイヤ       |

| 4316 | プロセッサ          |

| 4318 | コンピュータ可読記憶媒体   |

| 4320 | バス             |

10

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

FIG. 8

【図 9】

【図 10】

いくつかのSCLパルスは、

50nsよりも大きく、

フィルタ除去されない

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図 22】

【 図 2 3 】

【 図 2 4 】

| 3進   |       | ビットs<br>[9:0]     | アドレス        | 書き込み        | 読み取り   | 9[12:11] | 9[8:7] | 6[5:4] | 3[2:1] | 0[0:0] |

|------|-------|-------------------|-------------|-------------|--------|----------|--------|--------|--------|--------|

| 2222 | 22222 | 22222             | 0x81B0F     | ASY.        | 禁止     | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22222 | 22221             | 0x81BEF     |             |        | 0        | 0      | 0      | 0      | 0      |

|      |       |                   | 0x81A42[1]  |             | 禁止     |          |        |        |        |        |

| 2222 | 22222 | 1102              | 0x81BC6     |             |        |          |        |        |        |        |

| 2222 | 22222 | 1101              | 0x81BC5     | ハートマーク▼.NC# | 禁止     | 1        | 1      | 1      | 1      | 0      |

| 2222 | 22222 | 1100              | 0x81BC4     |             |        | 0        | 0      | 0      | 1      | 0      |

|      |       |                   | 0x82A42[1]  |             | 禁止     |          |        |        |        |        |

| 2222 | 22222 | 1000              | 0x81BBB     |             |        |          |        |        |        |        |

| 2222 | 22222 | 0222              | 0x81BBA     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22222 | 0221              | 0x81BB9     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22222 | 0220              | 0x81BB8     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22222 | 0219              | 0x81BB7     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22222 | 0218              | 0x81BB6     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22222 | 0124              | 0x81BB0     |             |        |          |        |        |        |        |

| 2222 | 22222 | 0120              | 0x81BAF     |             |        |          |        |        |        |        |

|      |       | [4:bits 0x10][16] | 0x81BAF     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 0      |

| 2222 | 22222 | 0000              | 0x81BA0     |             |        |          |        |        |        |        |

| 2222 | 22221 | 22222             | 0x81BF9     |             |        |          |        |        |        |        |

|      |       |                   | 0x10[16].1  |             | 禁止     |          |        |        |        |        |

| 2222 | 22221 | 2102              | 0x81B90     |             |        |          |        |        |        |        |

| 2222 | 22221 | 2101              | 0x81BAF     | 禁止          | SIDE查定 | 禁止       | 1      | 1      | 1      | 0      |

|      |       |                   | 0x81B90[16] |             |        |          | 1      | 1      | 1      | 0      |

| 2222 | 22221 | 2100              | 0x81BAE     |             |        |          |        |        |        |        |

|      |       |                   | 0x81A10[1]  |             | 禁止     |          |        |        |        |        |

| 2222 | 22221 | 2000              | 0x81B84     |             |        |          |        |        |        |        |

| 2222 | 22221 | 1223              | 0x81B83     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22221 | 1221              | 0x81B83     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

| 2222 | 22221 | 1220              | 0x81B83     | 予約済み        | 予約済み   | 1        | 1      | 1      | 1      | 1      |

|      |       |                   | 0x81B83[1]  |             |        |          |        |        |        |        |

【 図 2 5 】

【 四 26 】

【 図 27 】

【 図 2 9 】

【 図 2 8 】

2800

【図 3 1】

【図 3 2】

【図 3 3】

【図 3 4】

【図 3 5】

【図 3 6】

【図 3 7】

【図 3 8】

【図 39】

【図 40】

【図 41】

【図 42】

【図 4 3】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2015/025464 |

|---------------------------------------------------|

|                                                               |

|---------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. G06F13/42<br>ADD. |

|---------------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>G06F |

|---------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) |

|------------------------------------------------------------------------------------------------------------------------------|

|                        |

|------------------------|

| EPO-Internal, WPI Data |

|------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                         | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2013/272177 A1 (WEI DONG [US] ET AL)<br>17 October 2013 (2013-10-17)<br>the whole document<br>-----                     | 1-30                  |

| A         | US 2003/217213 A1 (IMMING KERRY<br>CHRISTOPHER [US] ET AL)<br>20 November 2003 (2003-11-20)<br>the whole document<br>----- | 1-30                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

|                                                           |                                                    |

|-----------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search | Date of mailing of the international search report |

|-----------------------------------------------------------|----------------------------------------------------|

|              |            |

|--------------|------------|

| 17 June 2015 | 09/07/2015 |

|--------------|------------|

|                                      |                    |

|--------------------------------------|--------------------|

| Name and mailing address of the ISA/ | Authorized officer |

|--------------------------------------|--------------------|

|                                                                                                                              |                |

|------------------------------------------------------------------------------------------------------------------------------|----------------|

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Ghidini, Mario |

|------------------------------------------------------------------------------------------------------------------------------|----------------|

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2015/025464

| Patent document cited in search report | Publication date | Patent family member(s)              | Publication date         |

|----------------------------------------|------------------|--------------------------------------|--------------------------|

| US 2013272177 A1                       | 17-10-2013       | US 2013272177 A1<br>WO 2013152742 A1 | 17-10-2013<br>17-10-2013 |

| US 2003217213 A1                       | 20-11-2003       | NONE                                 |                          |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

F ターム(参考) 5K034 AA02 CC06 DD02 LL01 LL02 LL09