(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4690938号

(P4690938)

(45) 発行日 平成23年6月1日(2011.6.1)

(24) 登録日 平成23年2月25日(2011.2.25)

(51) Int.Cl.

F 1

|                   |                  |                   |          |

|-------------------|------------------|-------------------|----------|

| <b>H01L 23/00</b> | <b>(2006.01)</b> | <b>H01L 23/00</b> | <b>C</b> |

| <b>H05K 5/00</b>  | <b>(2006.01)</b> | <b>H05K 5/00</b>  | <b>C</b> |

| <b>H01L 23/29</b> | <b>(2006.01)</b> | <b>H01L 23/30</b> | <b>B</b> |

| <b>H01L 23/31</b> | <b>(2006.01)</b> |                   |          |

請求項の数 4 (全 7 頁)

(21) 出願番号

特願2006-136290 (P2006-136290)

(22) 出願日

平成18年5月16日 (2006.5.16)

(65) 公開番号

特開2007-311396 (P2007-311396A)

(43) 公開日

平成19年11月29日 (2007.11.29)

審査請求日

平成20年2月4日 (2008.2.4)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 110000235

特許業務法人 天城国際特許事務所

(72) 発明者 吉田 大広

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 小向工場内

審査官 長谷部 智寿

(56) 参考文献 特開2005-340656 (JP, A )

特開2003-179181 (JP, A )

最終頁に続く

(54) 【発明の名称】高周波素子モジュール

## (57) 【特許請求の範囲】

## 【請求項1】

表面に電極が設けられ裏面に接地基板が設けられた絶縁基板と、この絶縁基板に設けられ、この素子の端子が前記電極と接続された高周波素子と、この高周波素子に塗布されたポリイミドと、このポリイミドの塗布された前記高周波素子を封止するポッティング材と、このポッティング材の上に設けられ、前記接地基板と接続された金属層と、この金属層を覆うように設けられた絶縁層と、この絶縁層の上に設けられ、前記電極と接続される配線パターンと、この配線パターンの上に設けられた保護層と、を有することを特徴とする高周波素子モジュール。

## 【請求項2】

孔部を有し表面に電極が設けられた絶縁基板と、この絶縁基板の裏面で少なくとも前記孔部を覆う接地基板と、前記孔部内に設けられ、この素子の端子が前記電極に接続された高周波素子と、この高周波素子に塗布されたポリイミドと、このポリイミドの塗布された前記高周波素子を封止するポッティング材と、このポッティング材の上に設けられ、前記接地基板と接続された金属層と、この金属層を覆うように設けられた絶縁層と、この絶縁層の上に設けられ、前記電極と接続される配線パターンと、

10

20

この配線パターンの上に設けられた保護層と、

を有することを特徴とする高周波素子モジュール。

【請求項3】

前記金属層は、アルミニウムの薄膜であることを特徴とする請求項1又は2記載の高周波素子モジュール。

【請求項4】

前記高周波素子は、モノリシックマイクロ波集積回路素子であることを特徴とする請求項1乃至3のいずれか1項記載の高周波素子モジュール。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、マイクロ波素子などの高周波素子を埋め込んだ高周波素子モジュールに係り、特にその構造に関する。

【背景技術】

【0002】

最近の情報化社会の進展に伴い伝送容量の増大の要求はますます強まっており、より伝送容量の大きいシステムや高度な変調方式が求められるようになってきた。これに伴って高い利得を有ししかも低価格のデバイスが求められている。

【0003】

このような要求に対して、セラミックの単板に金属プレートを備え素子を固着した簡易型パッケージにポリイミドを塗布して表面を保護し、その上にワイヤや素子を保護するためのポッティング材を塗布したモジュールが知られている（例えば、特許文献1参照）。

【0004】

しかし、ポッティング材は絶縁性を有するが、高性能の素子や高利得の素子では電磁界が放射され、外部に悪影響を及ぼしたり、逆に周囲の電磁界や自己が発するマイクロ波の出力の回りこみによって、著しく性能を劣化させるので、用途が限定される場合がある。

【特許文献1】特開2001-345419号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

30

本発明は上記のような従来の高周波素子モジュールの問題点にかんがみてなされたもので、電磁波の外部への影響及び外部から影響が少なくしたがって電気的性能がよく、構造が簡単でしかも廉価な高周波素子モジュールを提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の請求項1によれば、表面に電極が設けられ裏面に接地基板が設けられた絶縁基板と、この絶縁基板に設けられ、この素子の端子が前記電極と接続された高周波素子と、この高周波素子に塗布されたポリイミドと、このポリイミドの塗布された前記高周波素子を封止するポッティング材と、このポッティング材の上に設けられ、前記接地基板と接続された金属層と、この金属層を覆うように設けられた絶縁層と、この絶縁層の上に設けられ、前記電極と接続される配線パターンと、この配線パターンの上に設けられた保護層と、を有することを特徴とする高周波素子モジュールを提供する。

40

【発明の効果】

【0007】

本発明によれば、電磁波の外部への影響及び外部から影響が少なくしたがって電気的性能がよく、構造が簡単でしかも廉価な高周波素子モジュールが得られる。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施形態について図面を用いて説明する。

【0009】

50

## &lt;第1の実施形態&gt;

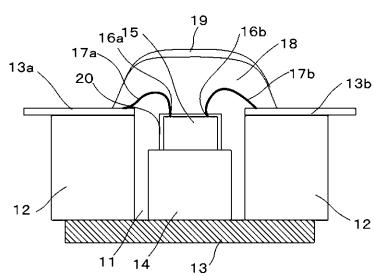

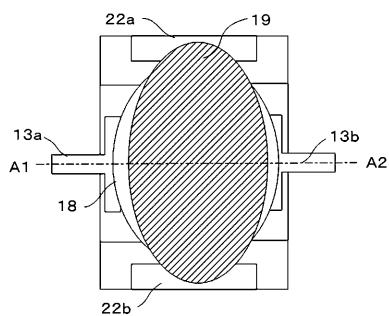

図1は本発明第1の実施形態の高周波素子モジュールの構造を示す断面図であり、図2は、この高周波素子モジュールの上面図である。図1は、図2のA1-A2における断面を表す。

## 【0010】

所定の孔部11を有し、セラミックで構成され、表面に配線が設けられた絶縁基板12と、この絶縁基板12の表面に配線された電極13a, 13bと、孔部11の裏面を含んで設けられた接地基板13と、この接地基板13上の孔部11内に設けられた台部14と、この台部14の上に固定された高周波素子15と、この高周波素子15の素子端子16a, 16bと上記絶縁基板13上の電極13a, 13bとを接続する、例えば金で構成されたワイヤ17a, 17bと、これらのワイヤ17a, 17bや上記高周波素子15の上にかぶせられ封止されるポッティング材18と、このポッティング材18の上に設けられた金属膜19とから成っている。高周波素子15は例えば電界効果トランジスタ(FET)であり、その周囲には、この素子の表面を保護し密着性をよくするために例えばポリイミド20が塗布される。10

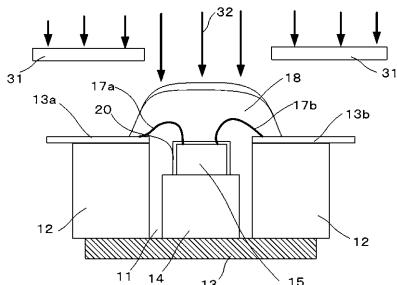

## 【0011】

次にこの実施形態の高周波素子モジュールの製造方法について述べる。ポッティング材18を設けるまでは従来と同じ方法でよい。次に図3に示すように、ポッティング材18の上部の必要な部分のみを空けたマスクパターン31を設けてこのマスクパターンにより金属材料、例えばアルミニウムを蒸着させることにより金属膜19を設ける。金属膜19の厚さは、1~5ミクロン程度とすることが好ましい。20

## 【0012】

また、金属膜19は、図2に示すような大きさ、形状とする。すなわち、図1に示す断面とは直交する方向の絶縁基板12上において、図2に示されるように接地端子22a, 22bが設けられており、ポッティング材18上の金属膜19は、これらの接地端子22a, 22bに接続されるような形状とする。接地端子22a, 22bは上記接地基板13と接続されている。

## 【0013】

一方、絶縁基板12の孔部11に電極13a, 13bも含めてポッティング材18により覆われているが、この上の金属膜19は上記電極13a, 13bに接触しないように設けられる。金属膜19をこのような大きさ、形状とすることにより、金属膜19と接地端子22a, 22bが接続され、電磁遮蔽されることになる。30

## 【0014】

金属膜としてアルミニウムを用いれば遮蔽効果も高く、廉価な高周波素子モジュールが得られる。

## 【0015】

この実施形態によれば、高周波素子15をほぼ完全に電磁シールでき、外部の影響を少なくすることができる。しかもアイソレーションが向上するので高利得の高周波素子を取り扱うことができ、廉価な高周波素子モジュールが得られる。

## 【0016】

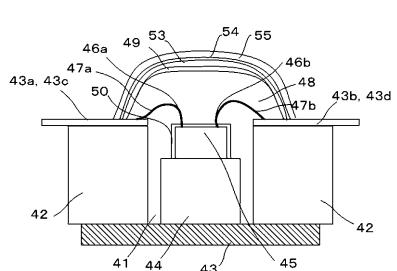

## &lt;第2の実施形態&gt;

ところで、上記の高周波素子として用いられるモノリシックマイクロ波集積回路(MMIC; Monolithic Microwave Integrated circuits)素子などでは、小型化の要求からモジュールの端子位置を変更することが頻繁に行われるようになっている。このような場合、ボンディングワイヤを変更することも考えられるが、MMIC素子など高利得のデバイスでは、上記高周波素子の上をワイヤがまたぐ形になると、デバイスで発生した電磁界の誘導を拾って発振するなどの不具合を生ずる場合がある。次に述べる第2の実施形態は、このような場合に適する高周波素子モジュールである。

## 【0017】

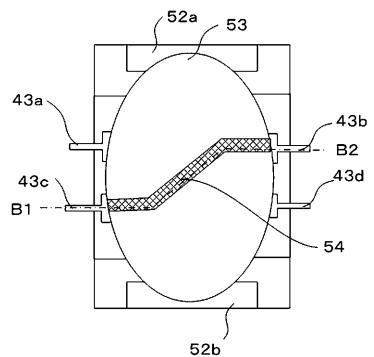

図4は、この第2の実施形態の高周波素子モジュールの構造を示す断面図である。番号40

50

41～50は図1に示す番号11～20に対応する。例えばセラミックで構成された絶縁基板42の孔部41に台部41が設けられこの上に、例えばMMIC素子である高周波素子45がマウントされ、裏面は接地基板43が設けられている。絶縁基板42の表面には、電極43a, 43cや電極43b, 43dが設けられており、金で構成されるワイヤ47a, 47bなどがこれらの電極に接続される。高周波素子45の周囲には、ポリイミド50がコーティングされる。高周波素子45やワイヤはポッティング材48により封止される。このポッティング材48の上には、上記第1の実施形態と同じように、金属膜49、例えば蒸着によりアルミニウムが1～5ミクロンの厚さで設けられる。

## 【0018】

この実施形態では、この金属膜49の上に絶縁層として有機系のポリイミド53が塗布され、更にその上に、図5に示すように、例えば上記電極43bと電極43cを接続するための配線パターン54が設けられる。図4は一点鎖線B1, B2間の断面図である。

10

## 【0019】

図4に示すように、その上にはこの配線パターン54を保護するための保護層として、例えば有機系のポリイミド55が塗布される。

## 【0020】

本発明のこの実施形態によれば、素子の端子となる電極間を接続しても発振などを生ぜず、安定し、しかも廉価な高周波素子モジュールが得られる利点がある。

20

## 【0021】

上記実施形態では、高周波素子として、FET及びMMIC素子を用いる場合について述べたが、本発明はこれらに限らず、一般的にはマイクロ波など高周波に用いられる素子を有するモジュールに適用可能である。

## 【0022】

また、上記実施形態では、絶縁基板に設けた孔部に高周波素子を設けてポッティング材で封止した構造の高周波素子モジュールについて説明した。しかし本発明はこのようなモジュールに限らず、絶縁基板の上に高周波素子を設けてポッティング材で覆う構造の高周波素子モジュールにも適用可能である。

## 【0023】

上記実施形態の説明では、ポッティング材の上に金属膜が設けられた場合について述べたが、本発明は金属膜だけでなく、一般的には金属層が設けられればよい。

30

## 【0024】

また上記実施形態では、絶縁基板の裏面に接地基板が設けられ、この接地基板に接続された接地端子が絶縁基板の表面に設けられている場合について説明した。しかし本発明はこのような構造のモジュールに限らず、上記ポッティング材の上に形成される金属層は接地端子に接続されていればよい。

## 【0025】

本発明は上記実施形態に限定されるものではなく、本発明の技術思想の範囲内で種々変形して実施可能である。

## 【図面の簡単な説明】

## 【0026】

40

【図1】本発明の第1の実施形態の構造を示す断面図。

【図2】本発明の第1の実施形態の上面図。

【図3】本発明の第1の実施形態の製造方法を説明するための図。

【図4】本発明の第2の実施形態の構造を示す断面図。

【図5】本発明の第2の実施形態において配線パターンを説明するための図。

## 【符号の説明】

## 【0027】

11, 41・・・孔部、

12, 42・・・絶縁基板、

13, 43・・・接地基板、

50

1 3 a , 1 3 b , 4 3 a , 4 3 b , 4 3 c , 4 3 d . . . 電極、

1 4 , 4 4 . . . 台部、

1 5 , 4 5 . . . 高周波素子、

1 6 a , 1 6 b , 4 a , 4 6 b . . . 素子端子、

1 7 a , 1 7 b , 4 7 a , 4 7 b . . . ワイヤ、

1 8 , 4 8 . . . ポッティング材、

1 9 , 4 9 . . . 金属膜、

2 0 , 5 0 , 5 3 , 5 5 . . . ポリイミド、

2 2 a , 2 2 b , 5 2 a , 5 2 b . . . 接地端子、

3 1 . . . マスクパターン。

10

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 0 1 L      2 3 / 0 0    2 3 / 1 2    2 3 / 2 8 - 2 3 / 3 1

2 3 / 3 4 - 2 3 / 4 7 3

H 0 5 K      5 / 0 0