(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5081902号

(P5081902)

(45) 発行日 平成24年11月28日(2012.11.28)

(24) 登録日 平成24年9月7日(2012.9.7)

(51) Int.Cl.

G 11 C 11/407 (2006.01)

F 1

G 11 C 11/34 354 D

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2009-511128 (P2009-511128)

(86) (22) 出願日 平成19年3月22日 (2007.3.22)

(65) 公表番号 特表2009-537933 (P2009-537933A)

(43) 公表日 平成21年10月29日 (2009.10.29)

(86) 國際出願番号 PCT/US2007/064583

(87) 國際公開番号 WO2007/133849

(87) 國際公開日 平成19年11月22日 (2007.11.22)

審査請求日 平成22年3月17日 (2010.3.17)

(31) 優先権主張番号 11/433,998

(32) 優先日 平成18年5月15日 (2006.5.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 リストン、トーマス ダブリュ.

アメリカ合衆国 78727 テキサス州

オースティン メイズ ベンド ドライ

ブ 1629

最終頁に続く

(54) 【発明の名称】 レベルシフト・ワード線ドライバを伴うメモリ、およびその動作方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリの動作方法であって、前記メモリはアドレス・デコード回路(116)、ワード線ドライバ回路(118)、およびビットセルアレイ(120)を備え、

前記アドレス・デコード回路(116)は第1電圧において動作可能であり、

前記ワード線ドライバ回路(118)と前記ビットセルアレイ(120)は、それぞれ前記第1電圧よりも高い第2電圧において動作可能であり、

前記動作方法は、

アクティブ・モードにおいて、前記第1電圧を前記アドレス・デコード回路(116)に与え、且つ前記第2電圧を前記ワード線ドライバ回路(118)と前記ビットセルアレイ(120)に与えることと；

低電力モードにおいて、前記第1電圧未満の第3電圧を前記アドレス・デコード回路(116)に与え、前記第2電圧以下の第4電圧を前記ビットセルアレイ(120)に与えることと

を含み、

前記アドレス・デコード回路(116)は、前記第3電圧において実質的に動作不可能であり、

前記ビットセルアレイ(120)は、記憶したデータを前記第4電圧において保持するように動作可能であることを特徴とする、動作方法。

## 【請求項 2】

10

20

前記第3電圧はゼロである、請求項1記載の動作方法。

【請求項3】

前記第4電圧は前記第2電圧に等しい、請求項1記載の動作方法。

【請求項4】

前記第2電圧を前記ワード線ドライバ回路(118)に与えることは、

前記第2電圧を、複数の出力を有する前記ワード線ドライバ回路(118)に与えることであり、それぞれ前記出力は、前記ビットセルアレイ(120)の対応するワード線に接続され、

前記動作方法は更に、

前記出力を、前記第1電圧から前記第2電圧に電圧レベルシフトすることと

を含む、請求項1記載の動作方法。

10

【請求項5】

前記アドレス・デコード回路(116)は、複数の第1厚さトランジスタを備え、

前記第1厚さトランジスタは、第1ゲート酸化物厚さを有し、

前記ワード線ドライバ回路(118)と前記ビットセルアレイ(120)は、複数の第2厚さトランジスタを備え、

前記第2厚さトランジスタは、前記第1ゲート酸化物厚さよりも大きな第2ゲート酸化物厚さを有する、請求項1記載の動作方法。

【請求項6】

前記第2電圧を、前記ワード線ドライバ回路(118)と前記ビットセルアレイ(120)に与えることは、前記第2電圧を、前記ワード線ドライバ回路(118)の電圧レベルシフタに与えることを含み、

20

前記電圧レベルシフタは、第1トランジスタ(302)、第2トランジスタ(304)、第3トランジスタ(306)、および第4トランジスタ(308)を有し、

前記第1トランジスタ(302)は、第1プレデコード値の対応するビット値を受信するように接続されるゲート電極と；第2プレデコード値の対応するビット値を受信するように接続される第1電流電極と；前記電圧レベルシフタの第1ノード(310)に接続される第2電流電極とを有し、

前記第2トランジスタ(304)は、接地電圧基準を受信するゲート電極と；前記第1ノード(310)に接続される第1電流電極と；前記第2電圧を受け取る第2ノード(312)に接続される第2電流電極とを有し、

30

前記第3トランジスタ(306)は、前記第1ノード(310)に接続されるゲート電極と；前記第2ノード(312)に接続される第1電流電極と；前記電圧レベルシフタの第3ノード(314)に接続される第2電流電極とを有し、

前記第4トランジスタ(308)は、前記第1ノード(310)に接続されるゲート電極と；前記第3ノード(314)に接続される第1電流電極と；接地電圧基準を受信する第2電流電極とを有し、前記第3ノード(314)は、前記ビットセルアレイ(120)の対応するワード線に接続され、

前記第1トランジスタ(302)、前記第2トランジスタ(304)、前記第3トランジスタ(306)、および前記第4トランジスタ(308)は、それぞれ前記第2ゲート酸化物厚さを有する、請求項5記載の動作方法。

40

【発明の詳細な説明】

【技術分野】

【0001】

本開示は一般的にメモリに関し、より詳細にはメモリへの電力供給に関する。

【背景技術】

【0002】

メモリは通常、ワード線ドライバを介してアクセスされるビットセルアレイとして実現される。ワード線ドライバは、メモリアクセスに付随する行アドレスのデコーディングに基づき起動される。データ信頼性と性能の理由から、多くの場合、ビットセルアレイとワード線ドライバは、同一のメモリチップ上に実装される。

50

ード線ドライバを動作させる電圧は、メモリの周辺回路の場合よりも高い方が優位である。このデュアル電圧ドメイン技術は、次の点でも優位である。すなわちメモリの周辺回路を低電力モードに設定することによって、ビットセルアレイに対する電圧供給を乱すことなく漏れ電流を減らすことができ、そのため、ビットセルアレイが記憶データを保持できる。

### 【0003】

デュアル電圧ドメインを用いる場合に通常は、周辺回路と、ワード線ドライバおよびビットセルアレイとの間で電圧レベルシフタを用いることが必要となる。

### 【発明の開示】

#### 【発明が解決しようとする課題】

10

### 【0004】

従来のレベルシフトを実現する際には通常、比較的大きな基板領域が必要となる。このためシフトを、メモリ・セル・ピッチが比較的小さいメモリ・トポロジにおいて用いることは、特に階層ワード線コーディングを用いるメモリセル・トポロジにおいて用いることは難しかった。またこれらの従来のレベルシフトを実現することによって通常は、比較的遅い回路が実現される。しかし遅い回路は、周辺回路とワード線の間の臨界経路となり、メモリアクセスの性能を妨げてしまう。従って、複数の電圧ドメインメモリにおいて、電圧レベルシフトを行なうための改善された技術が存在すれば優位である。

### 【課題を解決するための手段】

### 【0005】

20

同じ参照符号を異なる図面内で用いた場合、同様または同一の物品を示す。

本開示の一態様によれば、ワード線ドライバは、第1プレデコード値を受信する第1入力と、第2プレデコード値を受信する第2入力と、メモリのワード線に接続される出力とを有する。ワード線ドライバは、第1トランジスタと第2トランジスタを有する。第1トランジスタは、第1入力に接続されるゲート電極と、第2入力に接続される第1電流電極と、第1ノードに接続される第2電流電極とを有する。第2トランジスタは、第1電圧基準に接続されるゲート電極と、第2電圧基準に接続される第1電流電極と、第1ノードに接続される第2電流電極とを有する。ワード線ドライバは更に、第3トランジスタと第4トランジスタを有する。第3トランジスタは、第1ノードに接続されるゲート電極と、第3電圧基準に接続される第1電流電極と、第2ノードに接続される第2電流電極とを有する。第2ノードはメモリのワード線に接続される。第4トランジスタは、第1ノードに接続されるゲート電極と、第2ノードに接続される第1電流電極と、第1電圧基準に接続される第2電流電極とを有する。

30

### 【0006】

本開示の別の態様によれば、メモリは、複数のグローバル・ワード線と、グローバル・ワード線ドライバ回路とを有する。グローバル・ワード線ドライバ回路は、複数の出力を有する。各々の出力は、複数のグローバル・ワード線のうちの対応するグローバル・ワード線に接続される。メモリは更に、アドレス・デコード回路とローカル・ビットセルアレイを備える。アドレス・デコード回路は、プレデコード値を与える出力を有する。ローカル・ビットセルアレイは、複数のローカル・ワード線を含む。メモリは更に、ローカル・ワード線ドライバ回路を含む。ローカル・ワード線ドライバ回路は、アドレス・デコード回路の出力に接続される第1入力と、複数のグローバル・ワード線のうちの対応するグローバル・ワード線に接続される第2入力と、複数の出力とを有する。各々の出力は、複数のローカル・ワード線のうちの対応するローカル・ワード線に接続される。ローカル・ワード線ドライバ回路は、複数の電圧レベルシフタを含む。各々の電圧レベルシフタは、ローカル・ビットセルアレイの対応するローカル・ワード線に付随する。グローバル・ワード線ドライバ回路とアドレス・デコード回路は、第1電圧ドメインにおいて動作可能である。ローカル・ビットセルアレイとローカル・ワード線ドライバ回路は、第1電圧ドメインとは異なる第2電圧ドメインにおいて動作可能である。

40

### 【0007】

50

本開示の別の態様によれば、メモリの動作方法が提供される。メモリはアドレス・デコード回路、ワード線ドライバ回路、およびビットセルアレイを備える。アドレス・デコード回路は、第1電圧において動作可能である。ワード線ドライバ回路とビットセルアレイは、第2電圧において動作可能である。メモリの動作方法は、第1電圧をアドレス・デコード回路に与えることと、第2電圧をワード線ドライバ回路とビットセルアレイに与えることを、アクティブ・モードにおいて行なうことを含む。また動作方法は、第3電圧をアドレス・デコード回路に与えることと、第4電圧をビットセルアレイに与えることを、低電力モードにおいて行なうことを含む。アドレス・デコード回路は、第3電圧において実質的に動作不可能である。ビットセルアレイは、記憶したデータを第4電圧において保持するように動作可能である。

10

#### 【0008】

添付図面を参照することによって、本開示はより良好に理解され、またその多くの特徴と優位性が当業者に明らかになり得る。

#### 【発明を実施するための最良の形態】

#### 【0009】

図1～図5は、電圧レベルシフト（以下、「レベルシフト」）を、複数の電圧レベルを有するメモリデバイスにおいて用いるための典型的な技術を例示する。少なくとも本実施形態によれば、メモリは、周辺回路、ビットセルアレイ、およびワード線ドライバを含む。ビットセルアレイとワード線ドライバは、第2電圧ドメインにおいて動作する。周辺回路は、たとえば第1電圧ドメインにおいて動作するアドレス・デコード回路である。周辺回路を低電力状態で停止させること、または低電力状態に設定することは、第1電圧ドメインに対する電圧を低減または遮断する一方、第2電圧ドメインにおける電圧をデータ保持目的で維持することによって可能である。第2電圧ドメインは、第1電圧ドメインに供給される電圧よりも大きな電圧で動作できる。そのため、ワード線ドライバによって、電圧レベルシフタ（以下、「レベルシフタ」）を実現し、第1電圧ドメインと第2電圧ドメインの間のインターフェーシングを容易にすことができる。本実施形態では、周辺回路のトランジスタである第1厚さトランジスタは、第1ゲート酸化物厚さを用いて実現される。ワード線ドライバ（レベルシフタを含む）のトランジスタや、ビットセルアレイのトランジスタである第2厚さトランジスタは、第1ゲート酸化物厚さよりも大きな第2ゲート酸化物厚さを用いて実現される。よって、周辺回路の第1厚さトランジスタは、ワード線ドライバやビットセルアレイの第2厚さトランジスタよりも、速くまた低い電圧において動作できる。またビットセルアレイの第2厚さトランジスタは、一層厚いゲート酸化物を用いる。その結果、第2電圧ドメインに高電圧が供給されても、第2厚さトランジスタ内の漏れ電流が減る。

20

#### 【0010】

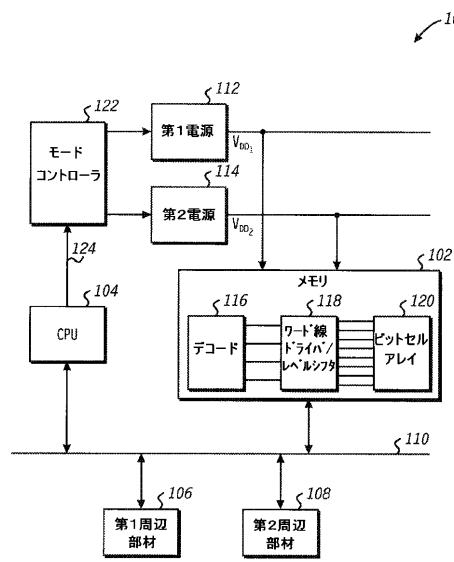

図1に示すように、本開示の少なくとも本実施形態による典型的な処理システム100を例示する。処理システム100は、たとえばマイクロプロセッサまたはマイクロコントローラを含めることができる。また処理システム100は、単一の集積回路デバイス（たとえばシステム・オン・チップ（SOC）または特定用途向け集積回路（ASIC）など）として実現しても良い。代替的に、処理システム100は、複数の別個の集積回路デバイスとして実現することもできる。

30

#### 【0011】

図示した例では、処理システム100はメモリ102、CPU（中央演算処理装置）104、1つまたは複数の周辺コンポーネント、第1電源112、および第2電源114を含む。メモリ102はたとえばランダム・アクセス・メモリ（RAM）であり、2つの電圧ドメインを有する。周辺コンポーネントは、たとえば第1周辺部材106と第2周辺部材108である。第1周辺部材106と第2周辺部材108は、1または複数のバス110を介して接続される。第1電源112は、処理システム100の第1電圧ドメイン用の第1電圧 $V_{DD1}$ を供給する。第1電圧 $V_{DD1}$ は、たとえばほぼ0.9ボルトである。第2電源114は、処理システム100の第2電圧ドメイン用の第2電圧 $V_{DD2}$ を、処

40

50

理システム100がアクティブ・モードの場合に供給する。第2電圧 $V_{DD2}$ は、たとえばほぼ1.2ボルトである。本実施形態では、第1電源112と第2電源114は単一電源である。

#### 【0012】

メモリ102は、周辺回路たとえばアドレス・デコード回路116を含む。アドレス・デコード回路116は、第1電圧ドメインにおいて動作する。またメモリ102は、ワード線ドライバ回路118とビットセルアレイ120を含む。ワード線ドライバ回路118とビットセルアレイ120は、第2電圧ドメインにおいて動作する。本明細書において更に詳しく説明するように、第1電圧ドメインの動作電圧は、第2電圧ドメインの動作電圧とは異なる。たとえば第2電圧ドメインの動作電圧は、第1電圧ドメインの動作電圧よりも高い。従って、ワード線ドライバ回路118がレベルシフト回路を実現すると、第1電圧ドメインと第2電圧ドメインという2つの互いに異なる電圧間のインターフェーシングが容易になる。

#### 【0013】

メモリ102が2つ以上の電圧ドメインに渡って動作できるように、第1電圧ドメインのコンポーネントにおいて実現されるトランジスタ（たとえばアドレス・デコード回路116のトランジスタ）は、第1ゲート酸化物厚さを用いる第1厚さトランジスタである。第2電圧ドメインのコンポーネントにおいて実現されるトランジスタ（たとえばワード線ドライバ回路118とビットセルアレイ120のトランジスタ）は、第2ゲート酸化物厚さを用いる第2厚さトランジスタである。少なくとも本実施形態では、第2ゲート酸化物厚さは、第1ゲート酸化物厚さよりも大きい。たとえば第1ゲート酸化物厚さは、1.4オングストローム未満とすることができる。第2ゲート酸化物厚さは、1.9オングストローム未満とすることができる。ゲート酸化物材料の例は、二酸化ケイ素や、窒化ケイ素などを含めることができる。

#### 【0014】

当然のことながら、ゲート酸化物が厚い第2厚さトランジスタの最小動作電圧は、通常、ゲート酸化物が薄い第1厚さトランジスタの場合よりも大きい。逆に、ゲート酸化物が厚い第2厚さトランジスタの漏れ電流は、通常、ゲート酸化物が薄い第1厚さトランジスタの場合よりも小さい。従って本実施形態では、メモリ102がアクティブ・モードの間は、第2電圧ドメインに供給される動作電圧は、第1電圧ドメインの場合よりも高くなる（すなわち $V_{DD2} > V_{DD1}$ ）。その結果、周辺回路、ワード線ドライバ回路118、およびビットセルアレイ120それぞれのトランジスタは、すべて動作状態となる。低電圧モード（たとえばスリープ・モード）では、第2電圧ドメインに供給される電圧は、ビットセルアレイ120におけるデータ保持目的にとって十分なものである。また周辺回路（たとえばアドレス・デコード回路116）のトランジスタを不動作状態に設定することは、第1電圧ドメインに供給する電圧を、周辺コンポーネントのトランジスタの閾値電圧よりも低くすることによってなされる（たとえばゼロ・ボルトを供給することによって）。その結果、電力の節約は、非アクティブ時間の間にメモリ102の周辺回路を効果的に停止させることによって可能である。一方、データは、ビットセルアレイ120内に維持される。代替的な実施形態では、第2電圧ドメインに供給される動作電圧は、第1電圧ドメインの場合よりも低い（すなわち $V_{DD2} < V_{DD1}$ ）。

#### 【0015】

幾つかの互いに異なる動作モードを実現するために、処理システム100は、モード・コントローラ122を含む。モード・コントローラ122は、CPU104から送られるモード選択信号124に応答して第1電源112と第2電源114を制御する。モード選択信号124を用いて、メモリ102はアクティブ・モードに入っていくのか低電圧モードに入っていくのか示すことができる。モード選択信号124がアクティブ・モードを示す場合、それに応答してモード・コントローラ122は、第1電源112に $V_{DD1}$ 電圧を供給するように命令し、第2電源114に $V_{DD2}$ 電圧を供給するように命令する。その結果、第1電圧ドメインの周辺回路と、第2電圧ドメインのワード線ドライバ回路11

10

20

30

40

50

8およびビットセルアレイ120とは、動作状態に維持される。モード選択信号124が低電圧モードを示す場合、それに応答してモード・コントローラ122は、第1電源112に、 $V_{DD1}$ よりも低くまた周辺回路のトランジスタの閾値電圧よりも低い電圧を供給する（たとえばゼロ・ボルトを供給する）ように命令し、第2電源114は引き続き $V_{DD2}$ 電圧を供給するように命令する。その結果、メモリ102の周辺回路は、効果的に無効にされる。一方、ビットセルアレイ120は、引き続き記憶データを保持する。

#### 【0016】

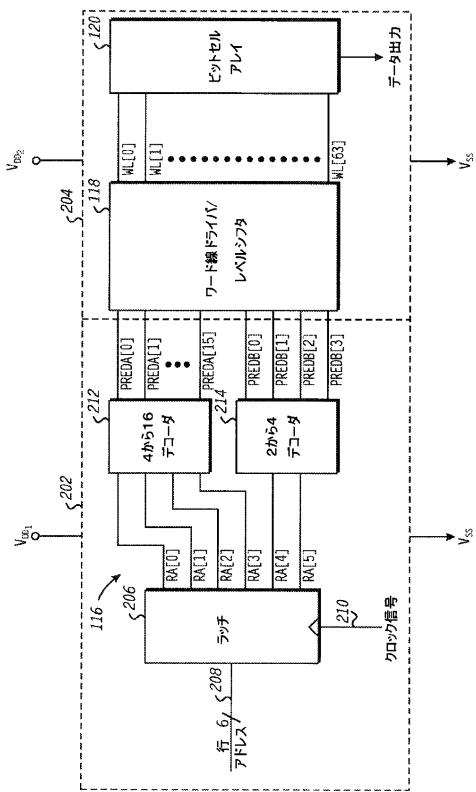

図2は、本開示の少なくとも本実施形態による図1のメモリ102の典型的な具体化を例示する。メモリ102は、アドレス・デコード回路116を含む。アドレス・デコード回路116は、第1電圧ドメイン202において動作する。第1電圧ドメイン202は、アクティブ・モードの間に第1電圧（第1動作電圧） $V_{DD1}$ を受取る。メモリ102に更に、ワード線ドライバ回路118（レベルシフト回路を含む）とビットセルアレイ120を含む。ワード線ドライバ回路118とビットセルアレイ120は、第2電圧ドメイン204において動作する。第2電圧ドメイン204は、アクティブ・モードの間に第2電圧 $V_{DD2}$ を受取る。

#### 【0017】

図示した具体化において、アドレス・デコード回路116は、ラッチ206を含む。ラッチ206は、行アドレス値208を受信する第1入力と、クロック信号210を受信する第2入力と、複数の出力とを有する。各々の出力は、行アドレス値208の対応するビット値のラッチした表現を、クロック信号210に応答して与える。説明を目的として、次のことを想定する。すなわち行アドレス値208は、6つのビット値（ビットRA[0]～RA[5]）である。従ってラッチ206は、ラッチした出力ビットRA[0]～RA[5]を与える。

#### 【0018】

アドレス・デコード回路116は更に、第1デコーダ212と第2デコーダ214を含む。第1デコーダ212は、ラッチした行アドレス値208のビット値の第1サブセットを受信する入力を有する。第2デコーダ214は、ラッチした行アドレス値208のビット値の第2サブセットを受信する入力を有する。第1サブセットと第2サブセットは、相互に排他的とすることもできるし、重なっていても良い。第1デコーダ212は、複数の出力を有する。各々の出力は、ビット値の第1サブセットに基づき、第1デコーダ212によって決定される第1プレデコード値（PredA）の対応するビットを与える。第2デコーダ214は、複数の出力を有する。各々の出力は、ビット値の第2サブセットに基づき、第2デコーダ214によって決定される第2プレデコード値（PredB）の対応するビットを与える。例示した例では、第1デコーダ212は、4対16デコーダ（4から16デコーダ）を含む。4対16デコーダは、ラッチした行アドレス値208のビットRA[0]～RA[3]を受信する4つの入力と、PredAに対する16ビット（すなわちPredA[0]～PredA[15]）を与える16の出力とを有する。更にこの例では、第2デコーダ214は、2対4デコーダ（2から4デコーダ）を含む。2対4デコーダは、ビットRA[4]とRA[5]を受信する2つの入力と、PredBに対する4ビット（すなわちPredB[0]～PredB[3]）を与える4つの出力とを有する。

#### 【0019】

図示した例では、ワード線ドライバ回路118は、第1組の入力と、第2組の入力を含む。第1組の入力は、第1デコーダ212の出力に接続されていて、PredA[0]～PredA[15]に対する対応するビット値を受信する。第2組の入力は、第2デコーダ214に接続されていて、PredB[0]～PredB[3]に対する対応するビット値を受信する。ワード線ドライバ回路118は更に、複数の出力（ビットセルアレイ120のワード線に接続される）を含む。特定のワード線は、ワード線ドライバ回路118によって、任意の特定のアクセス・サイクルの間にアサートされ、ワード線ドライバ回路118において受信されたビットPredA[0]～PredA[15]およびPred

10

20

30

40

50

B [ 0 ] ~ P r e d B [ 3 ] の最終デコードに基づき決定される。例示した例において、ワード線ドライバ回路 118 は、ビットセルアレイ 120 の 64 本のワード線 (WL 0 ~ WL 63) に接続される。

#### 【0020】

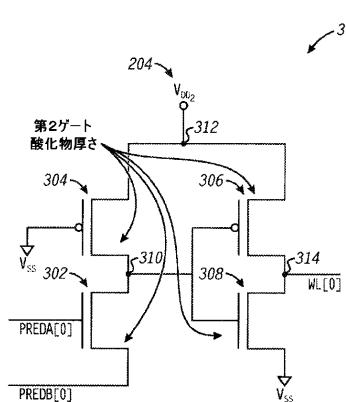

前述したように、アドレス・デコード回路 116 のトランジスタは、より薄いゲート酸化物を用いて実現されている。アドレス・デコード回路 116 は、V<sub>DD1</sub> に対して、より低い電圧において動作できる。ワード線ドライバ回路 118 とビットセルアレイ 120 のトランジスタは、より厚いゲート酸化物を用いて実現されている。ワード線ドライバ回路 118 とビットセルアレイ 120 は、より高い電圧において動作でき、漏れ電流に対してそれほど敏感ではない。しかし、ワード線ドライバ回路 118 とビットセルアレイ 120 に与える第 2 電圧 V<sub>DD2</sub> を、アドレス・デコード回路 116 に与える第 1 電圧 V<sub>DD1</sub> よりも高くすることによって、異なるトランジスタ電圧と漏れ特性の利益を利用できる。よって、第 1 デコーダ 212 と第 2 デコーダ 214 それぞれの出力と、ワード線 WL 0 ~ WL 63 の動作電圧との間に、電位差が存在する。従って、ワード線ドライバ回路 118 は、ワード線 WL 0 ~ WL 63 のそれぞれに対するレベルシフタを実現する。図 3 と図 4 に示すように、ワード線ドライバ回路 118 の、対応するワード線に対するワード線ドライバの典型的な具体化について、詳しく例示する。

#### 【0021】

図 3 は、本開示の少なくとも本実施形態による、ビットセルアレイ 120 (図 2) の対応するワード線 (たとえば WL 0) を駆動するために用いられるワード線ドライバ 300 の典型的な具体化を例示する。図示した例では、ワード線ドライバ 300 は、第 1 トランジスタ 302、第 2 トランジスタ 304、第 3 トランジスタ 306、および第 4 トランジスタ 308 を含む。第 1 トランジスタ 302 と第 4 トランジスタ 308 は、それぞれ n - チャンネル・トランジスタであり、たとえば n - チャンネル電界効果トランジスタすなわち N F E T である。第 2 トランジスタ 304 と第 3 トランジスタ 306 は、それぞれ p - チャンネル・トランジスタであり、たとえば p - チャンネル電界効果トランジスタすなわち P F E T である。前述したように、第 1 トランジスタ 302 ~ 第 4 トランジスタ 308 は、それぞれメモリ 102 (図 2) の周辺回路のトランジスタたとえばアドレス・デコード回路 116 のゲート酸化物厚さと比較して、より大きなゲート酸化物厚さを用いて実現される。そのため、第 1 トランジスタ 302 ~ 第 4 トランジスタ 308 それぞれの動作電圧は、高くなる必要があるが、結果として漏れ電流は小さくなる。

#### 【0022】

第 1 トランジスタ 302 は、P r e d A の対応するビット値 (たとえば P r e d A [ 0 ]) を受信するゲート電極と、P r e d B の対応するビット値 (たとえば P r e d B [ 0 ]) を受信する第 1 電流電極と、第 1 ノード 310 に接続される第 2 電流電極とを含む。第 2 トランジスタ 304 は、電圧基準 V<sub>SS</sub> (または接地) に接続されるゲート電極と、第 1 ノード 310 に接続される第 1 電流電極と、第 2 ノード 312 に接続される第 2 電流電極とを含む。第 2 ノード 312 は、第 2 電圧ドメイン 204 から電圧 (たとえばアクティブ・モードにおいて第 2 電圧 V<sub>DD2</sub>) を受取るように接続される。第 3 トランジスタ 306 は、第 1 ノード 310 に接続されるゲート電極と、第 2 ノード 312 に接続される第 1 電流電極と、第 3 ノード 314 に接続される第 2 電流電極とを含む。第 3 ノード 314 は、ビットセルアレイ 120 (図 2) の対応するワード線 (たとえば WL 0) に接続される。第 4 トランジスタ 308 は、第 1 ノード 310 に接続されるゲート電極と、第 3 ノード 314 に接続される第 1 電流電極と、電圧基準 V<sub>SS</sub> (たとえば接地) に接続される第 2 電流電極とを含む。

#### 【0023】

動作時、第 3 ノード 314 の出力電圧、従ってワード線 WL 0 は、P r e d A [ 0 ] と P r e d B [ 0 ] のビット値によって決まる。第 1 トランジスタ 302 は、P r e d A と P r e d B の最終デコードとしての機能を果たす。すなわちワード線ドライバ 300 に割当てられた P r e d A と P r e d B のそれぞれの対応するビットがアサートされると (例

示した例では  $P_{redA}[0]$  と  $P_{redB}[0]$  )、第 1 ノード 310 をより低い電位にする。そして第 3 ノード 314 を第 2 ノード 312 と実質的に同じ電位にすることによって、ワード線 WL0 のアサーションが行なわれる。そうではなくて、対応するビットのどちらかが非アサートされる場合、第 1 ノード 310 を第 2 電圧  $V_{DD2}$  に実質的に等しい電位にすることによって、第 3 ノード 314 を電圧基準  $V_{SS}$  に実質的に等しい電位にし、その結果、ワード線 WL0 が非アサートされる。

#### 【0024】

例示したように、ワード線ドライバ 300 によって、レベルシフトが実現される。すなわち入力信号たとえば  $P_{redA}[0]$  と  $P_{redB}[0]$  は、第 1 電圧ドメイン 202 (図 2) の低い方の第 1 電圧  $V_{DD1}$  に基づく。しかし、ワード線ドライバ 300 の出力が対応するワード線を駆動することは、第 2 電圧ドメイン 204 (図 2) の高い方の第 2 電圧  $V_{DD2}$  に基づき行なわれる。比較的少ない数のトランジスタを用いて、 $P_{redA}$  と  $P_{redB}$  値の両方の最終デコーディングを実現し、また対応するワード線を駆動しているため、ワード線ドライバ 300 を、ピッチが比較的小さいメモリにおいても用いることができる。

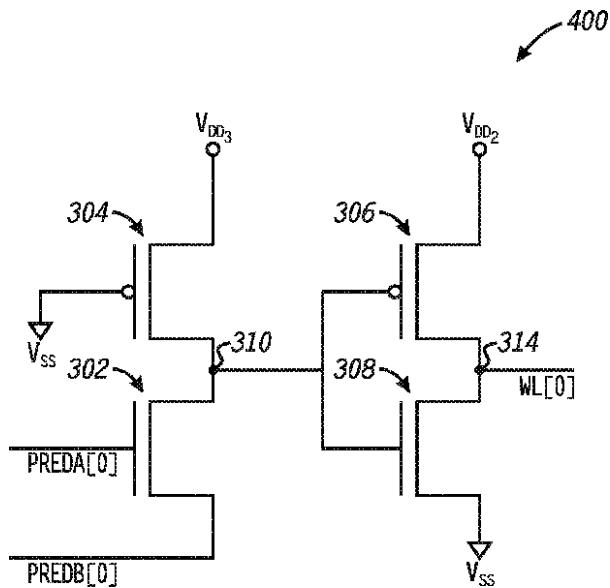

#### 【0025】

図 4 は、本開示の少なくとも本実施形態によるワード線ドライバ 400 の代替的な具体化を例示する。ワード線ドライバ 400 は、第 1 トランジスタ 302 ~ 第 4 トランジスタ 308 を含み、これらは以下の点を除いて、図 3 のワード線ドライバ 300 について前述したように接続される。すなわち第 2 トランジスタ 304 の第 2 電流電極は、第 3 電圧ドメイン (第 1 電圧  $V_{DD3}$  を有する) に接続されている。ワード線ドライバ 400 は、2 つを超える電圧ドメイン間でシフトできる。そのため、低電力モードの間、第 2 電圧  $V_{DD2}$  を下げて、電圧基準  $V_{SS}$  と実質的に同等な電位にすることができる。結果として、低電力モードの間、ワード線ドライバ 400 における電流漏れが減る。

#### 【0026】

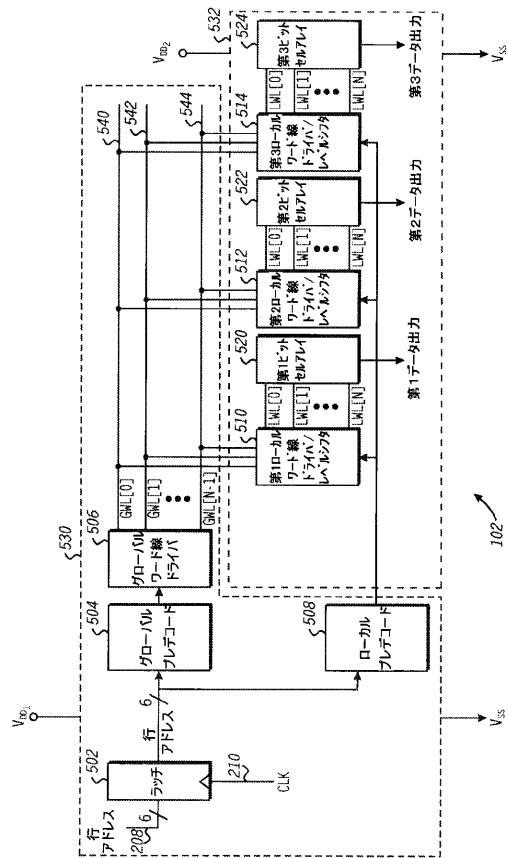

図 5 は、本開示の少なくとも本実施形態による、図 1 のメモリ 102 の別の典型的な具体化を例示する。図示した例では、メモリ 102 はラッチ 502、グローバル・プレデコード回路 504、グローバル・ワード線ドライバ回路 506、ローカル・プレデコード回路 508、複数のローカル・ワード線ドライバ回路、および複数のローカル・ビットセルアレイを含む。

#### 【0027】

ローカル・ワード線ドライバ回路はレベルシフト回路を含み、たとえば第 1 ローカル・ワード線ドライバ回路 510、第 2 ローカル・ワード線ドライバ回路 512、および第 3 ローカル・ワード線ドライバ回路 514 である。ローカル・ビットセルアレイは、たとえば第 1 ローカル・ビットセルアレイ 520、第 2 ローカル・ビットセルアレイ 522、および第 3 ローカル・ビットセルアレイ 524 である。ラッチ 502、グローバル・プレデコード回路 504、グローバル・ワード線ドライバ回路 506、およびローカル・プレデコード回路 508 は、第 1 電圧ドメイン 530 において動作する (第 1 動作電圧  $V_{DD1}$ )。グローバル・ワード線ドライバ回路 506 は、グローバル書込線ドライバ回路である。

#### 【0028】

第 1 ローカル・ワード線ドライバ回路 510 ~ 第 3 ローカル・ワード線ドライバ回路 514 と、第 1 ローカル・ビットセルアレイ 520 ~ 第 3 ローカル・ビットセルアレイ 524 は、それぞれ第 2 電圧ドメイン 532 において動作する (第 2 動作電圧  $V_{DD2}$ )。

#### 【0029】

図示した具体化において、ラッチ 502 は、行アドレス値 208 を受信する第 1 入力と、クロック信号 210 を受信する第 2 入力と、複数の出力とを含む。各々の出力は、行アドレス値 208 の対応するビット値のラッチした表現を、クロック信号 210 に応答して与える。説明を目的として、次のことを想定する。すなわち行アドレス値 208 は、6 つのビット値である。従ってラッチ 502 は、6 つのラッチした出力ビットを与える。

10

20

30

40

50

## 【0030】

グローバル・プレデコード回路504は、ラッチした行アドレス・ビットを受信する入力と、第1組のプレデコード・ビット値（たとえばPredA）を、ラッチした行アドレス・ビットに基づき与える出力とを含む。同様に、ローカル・プレデコード回路508は、ラッチした行アドレス・ビットを受信する入力と、第2組のプレデコード・ビット値（たとえばPredB）を、ラッチした行アドレス・ビットに基づき与える出力とを含む。

## 【0031】

グローバル・ワード線ドライバ回路506は、グローバル・プレデコード回路504の出力に接続されていて第1組のプレデコード・ビット値を受信する入力を含む。グローバル・ワード線ドライバ回路506は更に、複数の出力を含む。各々の出力は、対応するグローバル・ワード線（たとえば第1グローバル・ワード線540、第2グローバル・ワード線542、および第3グローバル・ワード線544）に接続される。特定のグローバル・ワード線が、グローバル・ワード線ドライバ回路506によって任意の特定のアクセス・サイクルの間にアサートされることは、グローバル・ワード線ドライバ回路506において受信された第1組のプレデコード・ビットの値に基づき行なわれる。例示した例において、グローバル・ワード線ドライバ回路506は、N個のグローバル・ワード線（GWL[0]～GWL[N-1]）に接続される。

## 【0032】

各々のローカル・ワード線ドライバ回路（510～514）は、対応するグローバル・ワード線に接続される第1入力と、ローカル・プレデコード回路508に接続されて第2組のプレデコード・ビットを受信する第2入力とを含む。各々のローカル・ワード線ドライバ回路（510～514）は更に、複数の出力を含む。各々の出力は、対応するローカル・ビットセルアレイ（520～524）の対応するローカル・ワード線に接続される。特定のローカル・ワード線は、ローカル・ワード線ドライバ回路（510～514）によって任意の特定のアクセス・サイクルの間にアサートされ、第2組のプレデコード・ビットの値に基づき、更にどのグローバル・ワード線がグローバル・ワード線ドライバ回路506によってアサートされるかに基づく。例示を目的として、第1ローカル・ワード線ドライバ回路510は、GWL[0]に接続される入力と、第1ローカル・ビットセルアレイ520のN個のローカル・ワード線（LWL[0]～LWL[N-1]）に接続される複数の出力とを含む。第2ローカル・ワード線ドライバ回路512は、GWL[1]に接続される入力と、第2ローカル・ビットセルアレイ522のN個のローカル・ワード線（LWL[0]～LWL[N-1]）に接続される複数の出力とを含む。第3ローカル・ワード線ドライバ回路514は、GWL[N-1]に接続される入力と、第3ローカル・ビットセルアレイ524のN個のローカル・ワード線（LWL[0]～LWL[N-1]）に接続される複数の出力とを含む。

## 【0033】

前述したように、ラッチ502、グローバル・プレデコード回路504、グローバル・ワード線ドライバ回路（グローバル書込線ドライバ回路）506、およびローカル・プレデコード回路508は、ローカル・ワード線ドライバ回路（510～514）やローカル・ビットセルアレイ（520～524）の場合とは異なる電圧ドメインにおいて動作する。従って、第1電圧ドメイン530において動作する回路のトランジスタは、より薄いゲート酸化物を用いて実現されている。第1電圧ドメイン530の回路は、V<sub>DD1</sub>に対してより低い電圧において動作できるようになっている。これに対して、第2電圧ドメイン532において動作する回路のトランジスタは、より厚いゲート酸化物を用いて実現されている。第2電圧ドメイン532の回路は、より高い電圧において動作でき、漏れ電流に対してそれほど敏感ではない。しかしローカル・ワード線ドライバ回路（510～514）とローカル・ビットセルアレイ（520～524）に与えられる第2電圧V<sub>DD2</sub>を、周辺回路に与える第1電圧V<sub>DD1</sub>よりも大きくすることによって、異なるトランジスタ電圧と漏れ特性の利益が利用できる。よって、電位差は、ローカル・プレデコード回路508とグローバル・ワード線の出力の電圧レベルと、ローカル・ワード線ドライバ回路（

10

20

30

40

50

510～514) がローカル・ワード線上に駆動する電圧レベルとの間に存在する。従つて、ローカル・ワード線ドライバ回路(510～514)は、ローカル・ワード線LWL[0]～LWL[N-1]のそれぞれに対するレベルシフタを実現する。

【0034】

図3と図4に示すように、ワード線ドライバ回路の、対応するワード線に対するワード線ドライバの典型的な具体化について、詳しく例示する。これらの具体化において、対応するグローバル・ワード線からの入力値は、第1トランジスタ302のゲート電極または第1電流電極(図3と図4)のどちらかに対する入力として機能できる。一方、ローカル・プレデコード回路508からの対応するプレデコード・ビット値は、第1トランジスタ302のゲート電極または第1電流電極の他方に対する入力として機能する。

10

【0035】

当然のことながら、ローカル・ワード線ドライバを用いることによって、ビットセルのアレイがブロックに分割される。よって、グローバル・ワード線に沿って配置されるセルの何分の1かのみが選択される。より少ない数のセルを選択できることによって、メモリ消費電力が小さくなる。更に、グローバル・ワード線ドライバをV<sub>DD1</sub>のドメインにおいて実現することは、ゲート酸化物が薄いトランジスタ厚さを用いて可能である。よって、トランジスタの速度が増加し、動作電圧を下げることができる。その結果、メモリの速度と消費電力が改善される。

【0036】

本開示の他の実施形態、使用方法、および優位性は、明細書を検討することと本明細書で開示された開示を実施することによって、当業者には明らかとなる。例示を目的として、典型的な電圧とゲート酸化物厚さについて本明細書では説明してきたが、これらの値は単に典型である。代替的な実施形態では、任意の数の電圧ドメイン、任意の数の異なる電圧レベル、および任意の数の異なるゲート厚さを用いても良い。明細書と図面は単に典型であると考えるべきであり、従つて本開示の範囲は、添付の請求項とその均等物のみによって限定されることが意図される。

20

【図面の簡単な説明】

【0037】

【図1】本開示の少なくとも本実施形態による複数電圧ドメインメモリを用いた典型的な、処理システムのブロック図。

30

【図2】図1の複数の電圧ドメインメモリのブロック図。

【図3】図2の電圧レベルシフトを実現する、ワード線ドライバの回路図。

【図4】図3とは別の、ワード線ドライバの回路図。

【図5】図1とは別の、複数の電圧ドメインメモリのブロック図。

【図1】

【図2】

【図3】

【図4】

FIG. 4

【 図 5 】

---

フロントページの続き

(72)発明者 チョウダリー - ネーグル、シャーナズ ピー .

アメリカ合衆国 78750 テキサス州 オースティン リリオブ コーブ 10013

(72)発明者 ベレー ザ サード、ペリー エイチ .

アメリカ合衆国 78726 テキサス州 オースティン インディゴ ブラッシュ ドライブ

9606

審査官 堀江 義隆

(56)参考文献 特開2002-150770 (JP, A)

特開平09-073783 (JP, A)

特開2001-110184 (JP, A)

特開2000-036193 (JP, A)

特開平04-089694 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/401 - 11/4197