PCT

WELTORGANISATION FÜR GEISTIGES EIGENTUM

Internationales Büro

## ATION FÜR GEIST Internationales Büro

**INTERNATIONALE ANMELDUNG VERÖFFENTLICH NACH DEM VERTRAG ÜBER DIE

INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT)**

|                                                                                                                                              |                                 |    |                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| (51) Internationale Patentklassifikation <sup>6</sup> :<br><br><b>H01L</b>                                                                   |                                 | A2 | (11) Internationale Veröffentlichungsnummer: <b>WO 97/21241</b>                                                                                  |

|                                                                                                                                              |                                 |    | (43) Internationales<br>Veröffentlichungsdatum: 12. Juni 1997 (12.06.97)                                                                         |

| (21) Internationales Aktenzeichen:                                                                                                           | PCT/DE96/02236                  |    | (81) Bestimmungsstaaten: CN, JP, KR, RU, UA, US, europäisches<br>Patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT,<br>LU, MC, NL, PT, SE). |

| (22) Internationales Anmeldedatum:                                                                                                           | 21. November 1996<br>(21.11.96) |    |                                                                                                                                                  |

| (30) Prioritätsdaten:<br>195 45 558.4                                                                                                        | 6. December 1995 (06.12.95)     | DE | <b>Veröffentlicht</b><br><i>Ohne internationalen Recherchenbericht und erneut zu<br/>veröffentlichen nach Erhalt des Berichts.</i>               |

| (71) Anmelder (für alle Bestimmungsstaaten ausser US): SIEMENS<br>AKTIENGESELLSCHAFT [DE/DE]; Wittelsbacherplatz 2,<br>D-80333 München (DE). |                                 |    |                                                                                                                                                  |

| (72) Erfinder; und                                                                                                                           |                                 |    |                                                                                                                                                  |

| (75) Erfinder/Anmelder (nur für US): SEDLAK, Holger [DE/DE];<br>Balanstrasse 63, D-81541 München (DE).                                       |                                 |    |                                                                                                                                                  |

(54) Title: METHOD OF DRIVING A FIELD EFFECT TRANSISTOR

**(54) Bezeichnung:** VERFAHREN ZUR ANSTEUERUNG EINES FELDEFFEKTTRANSISTORS

### (57) Abstract

A method is disclosed of driving a field effect transistor with a source section (2), a drain section (3) and a gate section (5): a gate voltage ( $U_G$ ) is applied to the gate section and ensures the formation and/or maintenance of an electrically conducting channel between the source and drain sections. The claimed method is characterised in that, once the channel has been formed, the gate section is cut off from a gate voltage source which provides it with the gate voltage.

### (57) Zusammenfassung

Es wird ein Verfahren zur Ansteuerung eines Feldeffekttransistors mit einem Sourceabschnitt (2), einem Drainabschnitt (3) und einem Gateabschnitt (5) beschrieben, wobei an den Gateabschnitt eine Gatespannung ( $U_G$ ) angelegt wird, die die Ausbildung und/oder Aufrechterhaltung eines elektrisch leitenden Kanals zwischen dem Sourceabschnitt und dem Drainabschnitt bewirkt. Das beschriebene Verfahren zeichnet sich dadurch aus, daß nach der Kanalausbildung der Gateabschnitt von einer diesen mit der Gatespannung beaufschlagenden Gatespannungs-Versorgungsquelle getrennt wird.

#### **LEDIGLICH ZUR INFORMATION**

Codes zur Identifizierung von PCT-Vertragsstaaten auf den Kopfbögen der Schriften, die internationale Anmeldungen gemäss dem PCT veröffentlichen.

|    |                                |    |                                   |    |                                |

|----|--------------------------------|----|-----------------------------------|----|--------------------------------|

| AM | Armenien                       | GB | Vereinigtes Königreich            | MX | Mexiko                         |

| AT | Österreich                     | GE | Georgien                          | NE | Niger                          |

| AU | Australien                     | GN | Guinea                            | NL | Niederlande                    |

| BB | Barbados                       | GR | Griechenland                      | NO | Norwegen                       |

| BE | Belgien                        | HU | Ungarn                            | NZ | Neuseeland                     |

| BF | Burkina Faso                   | IE | Irland                            | PL | Polen                          |

| BG | Bulgarien                      | IT | Italien                           | PT | Portugal                       |

| BJ | Benin                          | JP | Japan                             | RO | Rumänien                       |

| BR | Brasilien                      | KE | Kenya                             | RU | Russische Föderation           |

| BY | Belarus                        | KG | Kirgisistan                       | SD | Sudan                          |

| CA | Kanada                         | KP | Demokratische Volksrepublik Korea | SE | Schweden                       |

| CF | Zentrale Afrikanische Republik | KR | Republik Korea                    | SG | Singapur                       |

| CG | Kongo                          | KZ | Kasachstan                        | SI | Slowenien                      |

| CH | Schweiz                        | LI | Liechtenstein                     | SK | Slowakei                       |

| CI | Côte d'Ivoire                  | LK | Sri Lanka                         | SN | Senegal                        |

| CM | Kamerun                        | LR | Liberia                           | SZ | Swasiland                      |

| CN | China                          | LK | Litauen                           | TD | Tschad                         |

| CS | Tschechoslowakei               | LU | Luxemburg                         | TG | Togo                           |

| CZ | Tschechische Republik          | LV | Lettland                          | TJ | Tadschikistan                  |

| DE | Deutschland                    | MC | Monaco                            | TT | Trinidad und Tobago            |

| DK | Dänemark                       | MD | Republik Moldau                   | UA | Ukraine                        |

| EE | Estland                        | MG | Madagaskar                        | UG | Uganda                         |

| ES | Spanien                        | ML | Mali                              | US | Vereinigte Staaten von Amerika |

| FI | Finnland                       | MN | Mongolei                          | UZ | Usbekistan                     |

| FR | Frankreich                     | MR | Mauretanien                       | VN | Vietnam                        |

| GA | Gabon                          | MW | Malawi                            |    |                                |

## Beschreibung

## Verfahren zur Ansteuerung eines Feldeffekttransistors

5 Die vorliegende Erfindung betrifft ein Verfahren zur Ansteuerung eines Feldeffekttransistors gemäß dem Oberbegriff des Patentanspruchs 1, d.h. ein Verfahren zur Ansteuerung eines Feldeffekttransistors mit einem Sourceabschnitt, einem Drainabschnitt und einem Gateabschnitt, wobei an den Gateabschnitt 10 eine Gatespannung angelegt wird, die die Ausbildung und/oder Aufrechterhaltung eines elektrisch leitenden Kanals zwischen dem Sourceabschnitt und dem Drainabschnitt bewirkt.

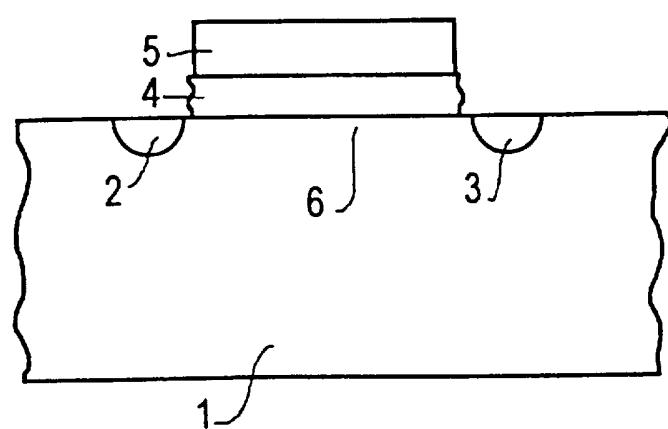

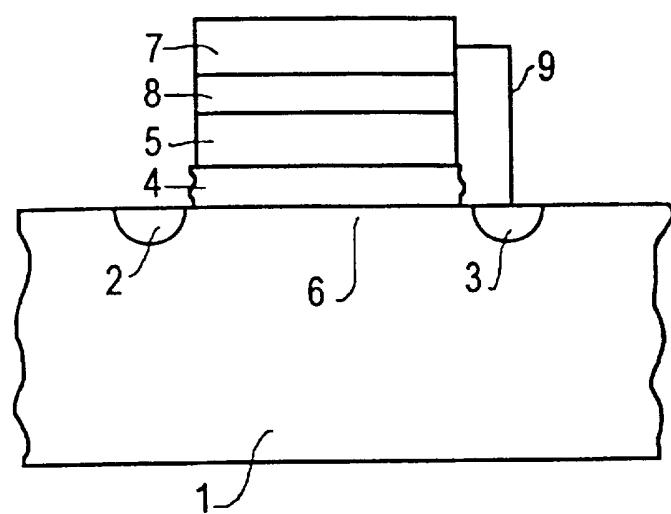

15 Derartige Feldeffekttransistoren (FETs) und Verfahren zu deren Ansteuerung sind seit langem bekannt. Ein praktisches Ausführungsbeispiel eines derartigen Transistors ist in Figur 4 gezeigt.

20 In Figur 4 ist schematisch ein herkömmlicher Anreicherungstyp-NMOS-FET dargestellt. Der gezeigte Transistor besteht aus einem aus p-dotiertem Halbleitermaterial gebildeten Substrat 1, einem an der Substratoberfläche vorgesehenen, aus n-dotiertem Halbleitermaterial gebildeten Sourceabschnitt 2, einem an der Substratoberfläche vorgesehenen, aus n-dotiertem 25 Halbleitermaterial gebildeten Drainabschnitt 3, einer auf dem Substrat aufgebrachten Isolationsschicht 4, und einem über der Isolationsschicht vorgesehenen Gateabschnitt 5.

Legt man an den Gateabschnitt 5 eine positive Spannung, beispielsweise +5 V an, so werden zu dem dem Gateabschnitt gegenüberliegenden Bereich des Substrats (Kanalausbildungsbereich 6) aus den weiter vom Gateabschnitt entfernten Substratbereichen Elektronen angezogen. Der zunächst wegen der p-Dotierung einen Elektronenmangel aufweisende und folglich elektrisch nicht leitende Kanalausbildungsbereich 6 wird dadurch allmählich zu einem einen Elektronenüberschuss aufweisenden Bereich, der schließlich einen elektrisch leitenden

Kanal zwischen dem Sourceabschnitt 2 und dem Drainabschnitt 3 bildet. Die Ausbildung eines derartigen Kanals bewirkt ein Durchschalten des Transistors, d.h. eine niederohmige elektrische Verbindung von Sourceabschnitt und Drainabschnitt.

5

Die Ausbildung bzw. Aufrechterhaltung des beschriebenen Kanals findet jedoch nur statt, wenn und solange die Gatespannung ( $U_G$ ) einen gewissen Mindestwert aufweist, der unter anderem von der am Sourceabschnitt anliegenden Sourcespannung 10 ( $U_S$ ) und der am Drainabschnitt anliegenden Drainspannung ( $U_D$ ) abhängt. Im stationären Betrieb des Transistors gilt dabei im wesentlichen die Bedingung, daß

$$U_G \geq \min (U_S, U_D) + U_T$$

15

erfüllt sein muß, wenn der Durchschaltzustand des Transistors erreicht bzw. aufrechterhalten werden soll, wobei  $U_T$  eine materialabhängige Schwellen- bzw. Thresholdspannung für die Kanalbildung darstellt, die bei Feldeffekttransistoren vom NMOS-20 Anreicherungstyp einen Wert von  $U_T > 0$  V aufweist.

25

Es ist folglich bei herkömmlichen Feldeffekttransistoren im stationären Betrieb nicht möglich, eine an den Source- oder den Drainabschnitt angelegte Spannung durch eine gleich hohe oder niedrigere Gatespannung durchzuschalten. Die Gatespannung muß zu diesem Zweck vielmehr auf einen Pegel gebracht werden, der um mindestens  $U_T$  über der durchzuschaltenden Spannung liegt.

30

Dies ist insbesondere in der Digitaltechnik, wo Feldeffekttransistoren vom Anreicherungstyp vorherrschen, mit nicht unerheblichen Schwierigkeiten verbunden, wenn Spannungspegel geschaltet werden sollen, die über der Versorgungsspannung liegen. Das Erzeugen eines zusätzlichen Spannungspegels zur 35 Verwendung als Gatespannung erfolgt bisher mittels sogenannter Pumpen, welche eine Spannung mit niedrigem Pegel (bei Bedarf stufenweise) auf eine Spannung mit einem höheren Pegel

anheben. Die schaltungstechnische Realisierung derartiger Pumpen erfordert eine Vielzahl von zusätzlichen elektronischen Bauelementen (insbesondere Transistoren und Kondensatoren), was vor allem bei integrierten Schaltungen nachteilig 5 ist (fächensintensiv; Hoch- und Niedervoltflächen sind schwer zu trennen).

Der vorliegenden Erfindung liegt daher die Aufgabe zugrunde, das Verfahren zur Ansteuerung von Feldeffekttransistoren 10 gemäß dem Oberbegriff des Patentanspruchs 1 derart weiterzubilden, daß auf einfache Weise ein Durchschalten hoher Spannungen unter Verwendung gleich hoher oder niedrigerer Gatespannungen ermöglicht wird.

15 Diese Aufgabe wird erfindungsgemäß durch die im kennzeichnenden Teil des Patentanspruchs 1 beanspruchten Merkmale gelöst.

Demnach ist vorgesehen, daß nach der Kanalausbildung der Gateabschnitt von einer diesen mit der Gatespannung beaufschlagenden Gatespannungs-Versorgungsquelle getrennt wird.

20 Das Vorsehen dieser Maßnahme ermöglicht es, das (jetzt flottende bzw. nicht mehr aktiv getriebene) Gatepotential mittels einer nach dem Abtrennen des Gateabschnittes von der Gatespannungs-Versorgungsquelle angelegten (durchzuschaltenden) Spannung auf ein das Potential der durchzuschaltenden Spannung übersteigendes Potential anzuheben, so daß ohne aufwendiges Generieren einer separaten Gatespannung auch Spannungen 25 geschaltet werden können, die bei herkömmlicher Feldeffekt-transistor-Ansteuerung mangels Erfüllbarkeit der Bedingung 30

$$U_G \geq \min (U_S, U_D) + U_T$$

nicht durchschaltbar sind.

35 Es wurde mithin ein Verfahren zur Ansteuerung von Feldeffekt-transistoren geschaffen, das auf einfache Weise ein Durch-

schalten hoher Spannungen unter Verwendung gleich hoher oder niedrigerer Gatespannungen ermöglicht.

5 Vorteilhafte Weiterbildungen der Erfindung sind Gegenstand der Unteransprüche.

Das erfindungsgemäße Ansteuerverfahren ist darüber hinaus aufgrund des daraus resultierenden Verhaltens des angesteuerten Feldeffekttransistors auch noch in einer nicht übersehbaren Vielzahl weiterer Anwendungsfälle nutzbringend einsetzbar.

15 Die Erfindung wird nachfolgend anhand eines Ausführungsbeispiels unter Bezugnahme auf die Zeichnungen detailliert beschrieben. Es zeigen

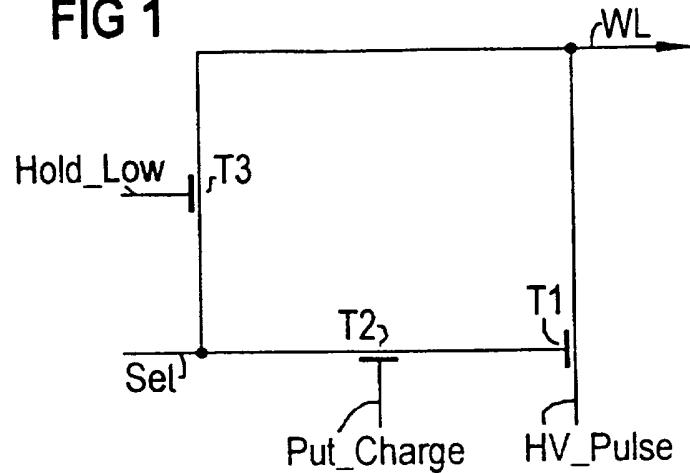

Figur 1 eine Schaltung zur Erläuterung des erfindungsgemäßen Ansteuerverfahrens,

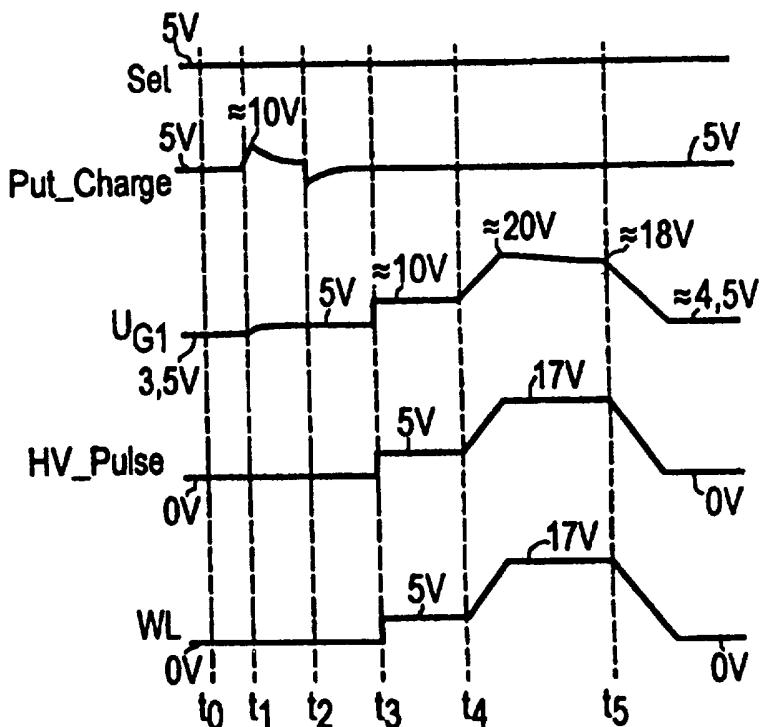

20 Figur 2 eine Darstellung, die die zeitlichen Signalverläufe an ausgewählten Punkten in der Schaltung gemäß Figur 1 veranschaulicht,

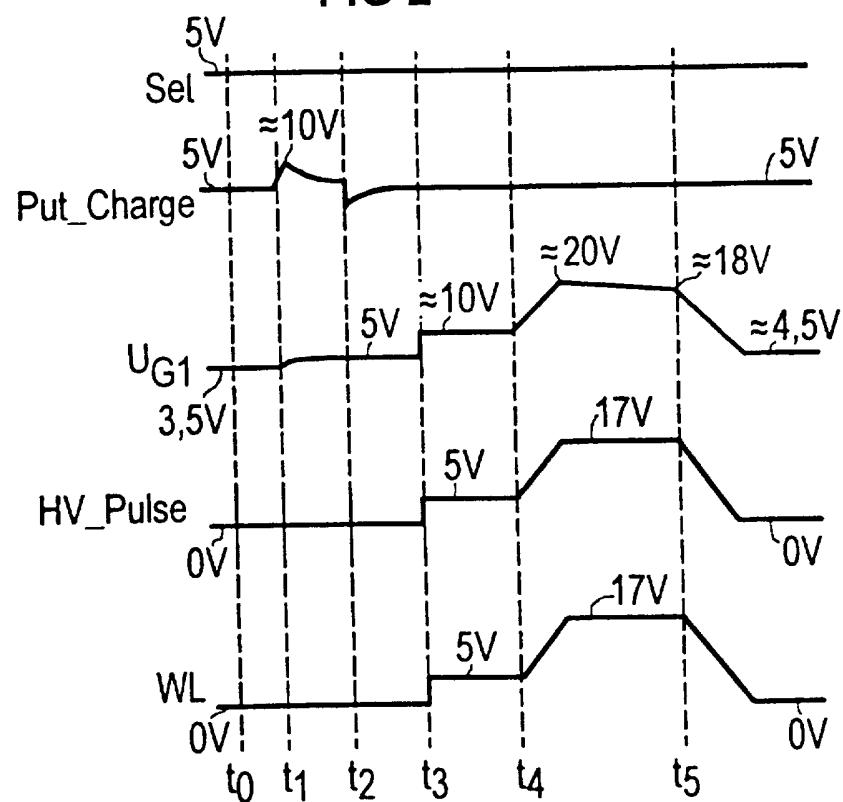

25 Figur 3 eine schematische Querschnittsansicht eines bei dem erfindungsgemäßen Ansteuerverfahren vorteilhaft einsetzbaren Feldeffekttransistors, und

Figur 4 eine schematische Querschnittsansicht eines herkömmlichen Feldeffekttransistors.

30

Die in der Figur 1 gezeigte Schaltung weist Anreicherungstyp-NMOS-Feldeffekttransistoren T1, T2 und T3 auf.

35 Vom Transistor T1 sind der Sourceabschnitt mit einer ein Signal HV\_Pulse führenden Signalleitung, der Drainabschnitt mit

einer ein Signal WL führenden Signalleitung und der Gateabschnitt mit dem Drainabschnitt des Transistors T2 verbunden.

5 Vom Transistor T2 sind der Sourceabschnitt mit einer ein Signal Sel führenden Signalleitung, der Drainabschnitt mit dem Gateabschnitt des Transistors T1 und der Gateabschnitt mit einer ein Signal Put\_Charge führenden Signalleitung verbunden.

10 Vom Transistor T3 sind der Sourceabschnitt mit der das Signal Sel führenden Signalleitung, der Drainabschnitt mit der das Signal WL führenden Signalleitung und der Gateabschnitt mit einer ein Signal Hold\_Low führenden Signalleitung verbunden.

15 Mittels des Signals HV\_Pulse ist an den Sourceabschnitt des Transistors T1 eine Spannung anlegbar, die im beschriebenen Ausführungsbeispiel Werte zwischen 0 V und +17 V annehmen kann.

20 Mittels des Signals Sel ist an die Sourceabschnitte der Transistoren T2 und T3 eine Spannung anlegbar, die im beschriebenen Ausführungsbeispiel Werte von 0 V oder +5 V annehmen kann.

25 Mittels des Signals Hold\_Low ist an den Gateabschnitt des Transistors T3 eine Spannung anlegbar, die im beschriebenen Ausführungsbeispiel Werte von 0 V oder +5 V annehmen kann.

30 Über die Signalleitung Put\_Charge ist an den Gateabschnitt des Transistors T2 eine Spannung anlegbar, die im beschriebenen Ausführungsbeispiel Werte von 0 V oder +5 V annehmen kann.

35 Ziel ist es, durch den Transistor T1 dessen maximale Source- spannung (17 V) zur Signalleitung WL durchzuschalten.

Bei Verwendung eines herkömmlichen Verfahrens zur Transistorsteuerung müßte hierfür an den Gateabschnitt des Transistors 1 eine Gatespannung  $U_{G1} \geq 17 \text{ V} + U_T$  angelegt werden.

5 Das erfindungsgemäße Verfahren beschreitet demgegenüber, wie nachfolgend unter Bezugnahme auf Figur 2 detailliert erläutert wird, einen anderen Weg.

10 In Figur 2 sind die zeitlichen Verläufe der Signale Sel, Put\_Charge, HV\_Pulse, WL sowie der zeitliche Verlauf des Potentials  $U_{G1}$  des Gateabschnittes des Transistors T1 gezeigt.

Es sei angenommen, daß die Signale Sel und Put\_Charge zu einem Ausgangszeitpunkt  $t_0$  jeweils auf 5 V liegen.

15 Da Put\_Charge so groß wie Sel und mithin nicht gleich oder größer als Sel +  $U_T$  ist, kann sich im Transistor T2 kein leitender Kanal zwischen dessen Sourceabschnitt und dessen Drainabschnitt ausbilden, so daß das Potential dessen Drainabschnittes und damit auch das Potential  $U_{G1}$  des Gateabschnittes des Transistors T1 floatend (nicht aktiv getrieben) ist und zum betrachteten Zeitpunkt Put\_Charge -  $U_T$  ( $\approx 3,5 \text{ V}$ ) beträgt.

25 Die Tatsache, daß  $U_{G1} = 3,5 \text{ V}$  beträgt, hat zur Folge, daß sich der Transistor T1 im schwach leitenden Zustand befindet.

Wenn nun zum Zeitpunkt  $t_1$  Put\_Charge wie in Figur 2 gezeigt auf beispielsweise 10 V ansteigt, so bildet sich im Transistor T2 ein leitender Kanal aus und dessen Sourcespannung (5 V) wird (gegebenenfalls mit einer gewissen zeitlichen Verzögerung) zu dessen Drainabschnitt bzw. zum Gateabschnitt des Transistors T1 durchgeschaltet.

35 Da das Signal HV\_Pulse (Sourcespannung des Transistors T1) zum Zeitpunkt  $t_1$  0 V beträgt, bewirkt das Ansteigen der Gatespannung  $U_{G1}$  des Transistors T1 auf +5 V, daß sich in diesem

Transistor ein gut leitender Kanal ausbildet. Die Drainspannung bzw. das Signal WL bleiben bzw. werden dadurch auf 0 V gelegt.

- 5 Wenn nun mit dem Abschluß der Kanalausbildung in Transistor T1 oder beliebige Zeit danach Put\_Charge wieder auf ca. 5 V oder eine niedrigere Spannung zurückfällt bzw. zurückgenommen wird (Zeitpunkt t2), führt dies zur Auflösung des leitenden Kanals im Transistor T2. Der Transistor T2 geht damit in den 10 Sperrzustand über, so daß die über den Drainabschnitt des Transistors T2 verlaufende Verbindung zwischen dem Gateabschnitt des Transistors T1 und einer derselben mit einer Spannung beaufschlagenden Versorgungsquelle aufgetrennt ist.

- 15 Der Drainabschnitt des Transistors T2 und damit auch der Gateabschnitt des Transistors T1 ist in diesem Zustand daher floatend (nicht aktiv getrieben); diese Abschnitte behalten daher ihr vorheriges Potential von 5 V unverändert bei, so daß der im Transistor T1 gebildete Kanal unverändert aufrecht 20 erhalten wird.

Nach Erlangung dieses Zustandes wird zum Zeitpunkt t3 HV\_Pulse von 0 V auf 5 V gesetzt, die infolge der zuvor erfolgten Floatend-Schaltung des Gateabschnittes des Transistors T1 (und anders als bei herkömmlichen Ansteuerverfahren) vom Sourceabschnitt zum Drainabschnitt durchgeschaltet werden.

Noch bevor sich nämlich der Kanal auflösen kann (weil die Bedingung  $U_{G1} \geq \min(U_{S1}, U_{D1}) + U_T$  nicht mehr erfüllt ist), steigt das Potential des Gateabschnittes des Transistors T1 um ca. 5 V auf ca. 10 V an, so daß die am Sourceabschnitt anliegenden 5 V durchgeschaltet werden können, ohne daß der Kanal zusammenbricht.

35

Die erwähnte selbständige Erhöhung des Gatepotentials am Transistor T1 läßt sich folgendermaßen erklären: Der Gateab-

schnitt und der diesem gegenüberliegende Substratabschnitt, in welchem auch der Kanal ausgebildet ist (sofern vorhanden) wirken wie Platten eines Kondensators. Die Platten befanden sich zum Zeitpunkt t<sub>2</sub>, als die eine der Platten (der Gateabschnitt) von der Versorgungsquelle getrennt wurde, im Gleichgewicht. Zu diesem Zeitpunkt, da die Sourcespannung (HV\_Pulse) noch 0 V betrug, konnte über den Kanal kein Strom fließen. Dies änderte sich jedoch zum Zeitpunkt t<sub>3</sub>, als die Sourcespannung auf 5 V erhöht und über den weiterhin existierenden Kanal durchgeschaltet wurde. Das Durchschalten der 5 V bewirkte aufgrund der veränderten Ladungsträgermenge auf einer der Platten (im Kanal) eine Störung des Gleichgewichts im Kondensator. Um das Gleichgewicht wiederherzustellen, wurden auf die Platte mit den weniger Ladungsträgern (Gateabschnitt) 15 zusätzliche Ladungsträger angezogen, was wiederum ausschlaggebend für die sich einstellende Potentialerhöhung ist.

Durch die gezielte Ausnutzung dieses bislang noch nicht erkannten Effekts kann ein Durchschalten des Transistors selbst 20 dann bewerkstelligt werden, wenn die Bedingung

$$U_G \geq \min (U_S, U_D) + U_T$$

nicht erfüllbar zu sein scheint.

25 Im Ergebnis liegen ab dem Zeitpunkt t<sub>3</sub> am Drainabschnitt des Transistors T<sub>1</sub> (=Signalleitung WL) die vom Sourceabschnitt desselben durchgeschalteten 5 V an.

30 Die auf ca. 10 V angehobene Gatespannung U<sub>G1</sub> bleibt zumindest vorübergehend im wesentlichen unverändert erhalten.

Wenn zu einem (beliebigen) Zeitpunkt t<sub>4</sub> die Sourcespannung des Transistors T<sub>1</sub> (HV\_Pulse) kontinuierlich ansteigend auf 35 den Maximalwert von 17 V erhöht wird, erhöht sich dadurch infolge der vorstehend erläuterten Gründe die Gatespannung des Transistors T<sub>1</sub> auf ca. 20 V, so daß auch die 17 V problemlos

zum Drainabschnitt des Transistors T1 bzw. zur Signalleitung WL durchgeschaltet werden können.

Die Erhöhung der Sourcespannung des Transistors T1 auf den 5 durchzuschaltenden Wert (hier von 0V auf 17 V) kann in beliebig vielen Etappen erfolgen, und zwar vorzugsweise stufenweise oder kontinuierlich ansteigend, gegebenenfalls jedoch auch sprungartig.

10 Das Durchschalten der 17 V wird entweder durch ein Abschalten der Sourcespannung (HV\_Pulse) oder automatisch durch Zeitablauf beendet.

15 Die in der Figur 2 veranschaulichte Beendigung des Durchschaltens durch Zeitablauf tritt auf, weil vom Gateabschnitt infolge parasitärer Leckpfade (unerwünschte Kapazitäten zwischen Gateabschnitt und benachbarten elektrischen, elektromechanischen oder mechanischen Komponenten; im Ersatzschaltbild ein Kondensator vom Gateabschnitt gegen Masse) 20 allmählich Ladungen abfließen und damit das Gatepotential schrumpft. So lange die Bedingung

$$U_{G1} \geq \min (U_{S1}, U_{D1}) + U_T$$

25 erfüllt ist, kann die Signalleitung WL mittels HV\_Pulse wieder nach 0 V entladen werden (Zeitpunkt t5).

Bei entsprechender Ansteuerung des Transistors T3 kann die 30 Signalleitung WL im Sperrzustand des Transistors T1 aktiv auf beliebige Spannungswerte getrieben werden.

Die Dauer, während der die Hochspannung (17 V) durch den Transistor T1 durchgeschaltet werden kann, hängt wesentlich davon ab, wie hoch das Gatepotential zum Zeitpunkt t3 ist, 35 wie gut das Gatepotential einer Ladungsträgermengenerhöhung im Kanal folgen kann und wie schnell sich der auf Hochspannung angehobene Gateabschnitt entlädt.

Sind die zuletzt genannten Punkte bei einem herkömmlichen Transistor für eine beabsichtigte Anwendung nicht zufriedenstellend, so kann in Betracht gezogen werden, einen im Hin-

5 blick darauf optimierten Transistor zu verwenden.

Ein derartiger Transistor ist in der Figur 3 schematisch dar-

gestellt.

10 Der in der Figur 3 gezeigte Feldeffekttransistor (Anreiche-

rungstyp-NMOS-FET) weist ein Substrat 1, einen Sourceab-

schnitt 2, einen Drainabschnitt 3, einen Isolationsschicht 4,

einen Gateabschnitt 5 und einen Kanalausbildungsbereich 6

auf.

15 Diese Elemente entsprechen den jeweiligen Elementen des vor-

stehend bereits beschriebenen herkömmlichen Feldeffekttran-

sistors gemäß Figur 4 und werden daher nicht nochmals erläu-

tert.

20 Im Unterschied zu dem in Figur 4 gezeigten Feldeffekttran-

sistor weist der Feldeffekttransistor gemäß Figur 3 zusätz-

lich eine Gateabdeckung 7 auf.

25 Die Gateabdeckung 7 ist gemäß der Figur 3 an der vom Substrat

1 abgewandten Seite des Gateabschnitts 5 vorgesehen. Sie be-

steht aus elektrisch leitendem Material und ist über eine

Verbindungsleitung 9 elektrisch mit dem Drainabschnitt 3 ver-

bunden.

30 Zwischen dem Gateabschnitt 3 und der Gateabdeckung 7 ist eine

dünne Isolationsschicht 8 (die Dicke bewegt sich vorzugsweise

im nm- oder  $\mu$ m-Bereich) vorgesehen, um die Elemente elek-

trisch voneinander zu isolieren.

35 Die Gateabdeckung 7 bewirkt, daß das vorstehend detailliert

erläuterte Ansteuerverfahren auch noch in solchen Fällen ein-

setzbar ist, bei denen sich der gewünschte Effekt andererfalls nicht im benötigten Umfang und/oder der geforderten Zuverlässigkeit einstellen würde.

- 5 Diese Funktion der Gateabdeckung beruht im wesentlichen darauf, daß sie um den Gateabschnitt eine Abschirmung bildet, die im Gegensatz zu herkömmlichen Abschirmungen auf demselben Potential wie das Drainpotential liegt und mithin einerseits den selben positiven Effekt wie der Kanal bewirkt, und andererseits den Abfluß von Ladungen vom Gateabschnitt über parasitäre Kapazitäten (unerwünschte Kapazitäten zwischen Gateabschnitt und benachbarten elektrischen, elektromechanischen oder mechanischen Komponenten; im Ersatzschaltbild ein Kondensator vom Gateabschnitt auf Masse) zumindest einschränkt

- 10 und zudem das Verhältnis von Nutzkapazität (Kapazitäten zwischen dem Gateabschnitt und dem Substrat sowie zwischen dem Gateabschnitt und der Gateabdeckung) zu parasitären Kapazitäten erhöht.

- 15

- 20 Die Gateabdeckung 7 ist gemäß Figur 3 nur oberhalb des Gateabschnittes 5 vorgesehen und deckt denselben daher nur auf der vom Substrat abgewandten Seite des Gateabschnittes ganz oder teilweise ab. Hierauf besteht jedoch keine Einschränkung. Die Gateabdeckung kann statt dessen oder zusätzlich

- 25 auch die gemäß Figur 1 seitlichen Flächen des Gateabschnittes bedecken. Die beste Wirkung der Gateabdeckung stellt sich ein, wenn sämtliche dem Substrat nicht zugewandten Bereiche des Gateabschnittes (jeweils unter Zwischenschaltung der Isolationsschicht 8) von der Gateabdeckung umgeben sind.

- 30

- 35 Die Gateabdeckung ist gemäß Figur 3 elektrisch mit dem Drainabschnitt verbunden. Auch hierauf besteht keine Einschränkung. Eine im wesentlichen gleichartige Wirkung der Gateabdeckung kann auch erzielt werden, wenn die Gateabdeckung statt dessen mit dem Sourceabschnitt elektrisch verbunden ist.

Mit oder ohne Gateabdeckung fällt das auf die beschriebene Weise erhöhte Gatepotential des Transistors T1 allmählich wieder ab, was schließlich zu einem Zusammenbruch des Kanals (Sperren des Feldeffekttransistors) führt. Zwischen dem Trennen des Gateabschnittes von der Versorgungsquelle und dem Zusammenbruch des Kanals liegen je nach Gestaltung des Transistors Bruchteile von Sekunden bis zu mehreren Minuten oder gar Stunden. Während dieser Zeit ist der Transistor stationär betreibbar.

10

Der selbständige Zusammenbruch des Kanals ist eine der eingangs bereits erwähnten zusätzlichen nutzbringend einsetzbaren Wirkungen des erfindungsgemäßen Ansteuerverfahrens. Sie verleiht dem derart angesteuerten Transistor zusätzlich die Funktion eines Monoflops und eröffnet mithin völlig neue Einsatzgebiete für Transistoren.

Besondere Effekte können demnach also auch dadurch erzielt werden, daß die vorstehend bereits angesprochenen Gateabschnitts-Nutzkapazitäten (Kapazitäten zwischen dem Gateabschnitt und dem Substrat sowie gegebenenfalls zwischen dem Gateabschnitt und der Gateabdeckung) gezielt verändert bzw. auf bestimmte Werte eingestellt werden (beispielsweise durch Veränderung der Zusammensetzung und/oder der Dicke der jeweiligen Isolationsschichten (Isolationsschichten 4 und 8)), um so das zeitliche Verhalten des Feldeffekttransistors an die beabsichtigte Anwendung anpassen zu können.

Das erfindungsgemäße Ansteuerverfahren wurde vorstehend anhand eines Anreicherungstyp-NMOS-Feldeffekttransistors beschrieben. Es versteht sich jedoch von selbst, daß eine derartige Ansteuerung - gegebenenfalls nach entsprechender Anpassung an die jeweiligen Gegebenheiten - auch bei beliebigen anderen Arten von Feldeffekttransistoren realisierbar und nutzbringend einsetzbar ist.

## Patentansprüche

1. Verfahren zur Ansteuerung eines Feldeffekttransistors mit einem Sourceabschnitt (2), einem Drainabschnitt (3) und einem Gateabschnitt (5), wobei an den Gateabschnitt eine Gatespannung ( $U_G$ ) angelegt wird, die die Ausbildung und/oder Aufrechterhaltung eines elektrisch leitenden Kanals zwischen dem Sourceabschnitt und dem Drainabschnitt bewirkt, dadurch gekennzeichnet, daß nach der Kanalausbildung der Gateabschnitt von einer diesen mit der Gatespannung beaufschlagenden Gatespannungs-Versorgungsquelle getrennt wird.

2. Verfahren nach Anspruch 1, dadurch gekennzeichnet, daß das Abtrennen des Gateabschnittes (5) von der Gatespannungs-Versorgungsquelle unmittelbar nach der Kanalausbildung oder innerhalb einer relativ kurzen Zeit danach erfolgt.

3. Verfahren nach Anspruch 1 oder 2, dadurch gekennzeichnet, daß das Abtrennen des Gateabschnittes (5) von der Gatespannungs-Versorgungsquelle derart durchgeführt wird, daß das Gatepotential ( $U_G$ ) hierbei im wesentlichen unverändert erhalten bleibt.

4. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, daß das Abtrennen des Gateabschnittes (5) von der Gatespannungs-Versorgungsquelle derart durchgeführt wird, daß sich der Gateabschnitt nach dem Abtrennen in einem im wesentlichen floatenden Zustand befindet.

5. Verfahren nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, daß zum Abtrennen des Gateabschnittes (5) von der Gatespannungs-Versorgungsquelle eine die elektrische Verbindung zwi-

schen dem Gateabschnitt und der Gatespannungs-Versorgungsquelle unterbrechende Schaltvorrichtung verwendet wird.

6. Verfahren nach einem der vorhergehenden Ansprüche,

5 dadurch gekennzeichnet,

daß die Sourcespannung und die Drainspannung bis zum Abtrennen des Gateabschnittes (5) von der Gatespannungs-Versorgungsquelle zur Annahme von Werten veranlaßt sind, die im Zusammenwirken mit der Gatespannung ( $U_G$ ) die Ausbildung

10 und/oder Aufrechterhaltung des elektrisch leitenden Kanals bewirken.

7. Verfahren nach einem der vorhergehenden Ansprüche,

dadurch gekennzeichnet,

15 daß die Sourcespannung nach dem Abtrennen des Gateabschnittes (5) von der Gatespannungs-Versorgungsquelle zur Annahme von Werten veranlaßt wird, deren Durchschalten zum Drainabschnitt (3) gewünscht ist, wobei die Sourcespannung dabei auch Werte annehmen kann, deren Vorsehen vor dem Abtrennen des Gateabschnittes von der Gatespannungs-Versorgungsquelle den Kanalaufbau verhindert oder dessen Zusammenbruch bewirkt hätten.

8. Verfahren nach Anspruch 7,

dadurch gekennzeichnet,

25 daß mit den vorzunehmenden Veränderungen der Sourcespannung unmittelbar nach dem Abtrennen des Gateabschnittes von der Gatespannungs-Versorgungsquelle oder innerhalb einer relativ kurzen Zeit danach begonnen wird.

30 9. Verfahren nach Anspruch 7 oder 8,

dadurch gekennzeichnet,

daß die vorzunehmenden Veränderungen der Sourcespannung nur allmählich vorgenommen werden.

35 10. Verfahren nach Anspruch 9,

dadurch gekennzeichnet,

daß die Sourcespannung stufenweise erhöht wird.

11. Verfahren nach Anspruch 9,

dadurch gekennzeichnet,

daß die Sourcespannung kontinuierlich erhöht wird.

1 / 2

FIG 1

FIG 2

2 / 2

FIG 3

FIG 4