RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 529 412**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 82 11212**

(54) Convertisseur numérique — analogique de haute résolution à auto-étalonnage.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 03 K 13/02.

(22) Date de dépôt..... 25 juin 1982.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 52 du 30-12-1983.

(71) Déposant : Société dite : THOMSON-CSF. — FR.

(72) Invention de : André Bourdoux et François de Massol.

(73) Titulaire :

(74) Mandataire : Thomson-Guilguet P.,

SCPI, 173, bd Haussmann, 75379 Paris Cedex 08.

CONVERTISSEUR NUMERIQUE-ANALOGIQUE DE HAUTE RESOLUTION

A AUTO-ETALONNAGE

La présente invention concerne les convertisseurs numérique-analogique, capables de recevoir un code numérique d'entrée sous forme de N chiffres binaires de poids décroissants, et de fournir à la sortie un courant proportionnel au nombre 5 représenté par ce code.

Un tel convertisseur comprend essentiellement N sources de courant en parallèle, dont les amplitudes sont dans des rapports correspondants aux différents poids binaires ; chaque source peut être mise en service ou interrompue individuellement sous la 10 commande d'un chiffre respectif du code d'entrée.

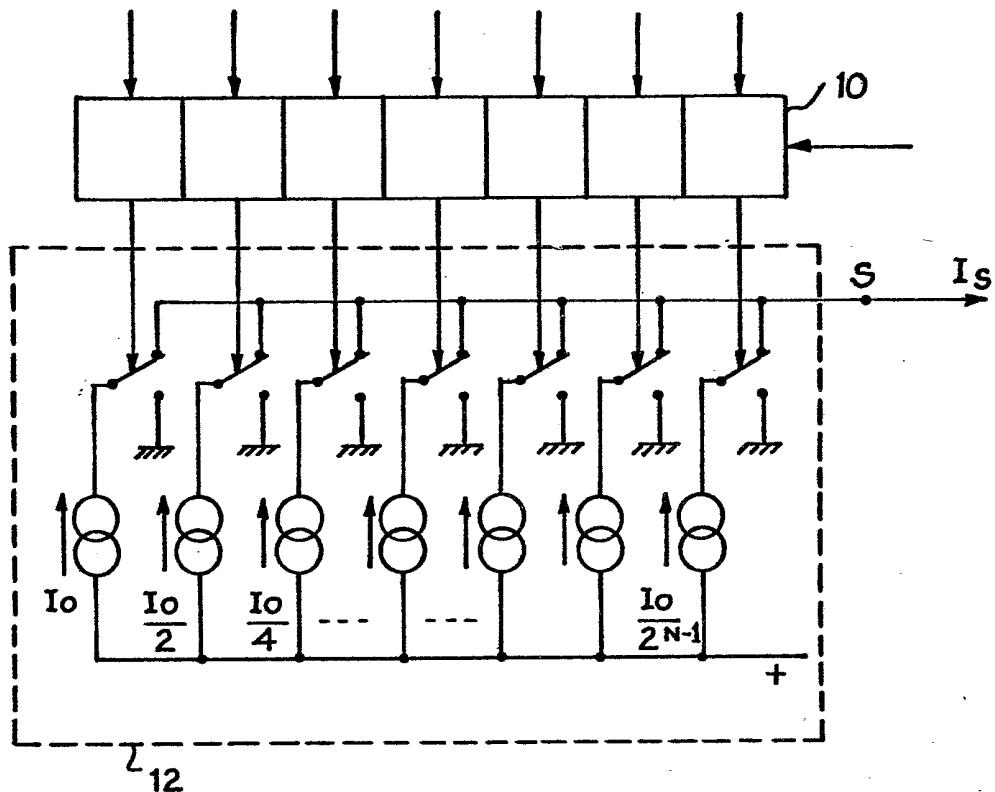

La figure 1 représente le schéma de principe d'un tel convertisseur. Les sources de courant ont des amplitudes  $I_0$ ,  $I_0/2$ ,  $I_0/4 \dots I_0/2^{N-1}$  dans l'ordre des poids décroissants. On sait faire actuellement des convertisseurs dont la résolution est de douze 15 bits ; la précision d'un tel convertisseur doit alors être d'au moins douze bits, c'est à dire que l'erreur maximale sur le courant engendré par le convertisseur ne doit pas excéder la valeur  $I_0/2^{12}$ , c'est à dire la moitié de l'amplitude de la source de courant de poids le plus faible. Cette précision de douze bits 20 peut être obtenue actuellement par des techniques d'ajustage au laser des résistances de ponts diviseurs servant à définir l'amplitude des sources de courant.

Si on veut réaliser des convertisseurs ayant une résolution de seize bits, il faudrait obtenir une précision de 25 seize bits sur la réalisation des sources de courant, c'est à dire que l'erreur sur le courant global engendré ne doit pas excéder  $I_0/2^{16}$ . La technologie ne le permet pas.

Cependant, on peut contourner cette difficulté en réalisant un convertisseur à seize bits dans lequel les onze bits 30 de poids le plus faible ont la précision maximale possible, soit douze bits, c'est à dire que l'erreur sur le courant engendré n'excède pas le quart de l'amplitude de la source de courant de

poids le plus faible. Les cinq sources de courant de poids fort, sont aussi réalisées avec une précision de douze bits, ce que l'on sait faire, mais cette précision est tout à fait insuffisante puisqu'elle conduit à une erreur de conversion pouvant atteindre 5  $I_0/2^{12}$  soit huit fois la valeur de l'amplitude de la plus petite source de courant ( $I_0/2^{15}$ ) du convertisseur. Après fabrication, on étalonne et on corrige le convertisseur pour aboutir à une précision effective de seize bits. L'étalonnage et la correction portent sur les cinq sources de poids fort, et ils sont faits avec 10 une précision d'un quart de l'amplitude de la plus petite source de courant ; comme les onze sources de poids faible ont déjà cette précision au moment de la fabrication, la précision sera au total de la moitié de l'amplitude de la plus petite source de courant, ce qui donne bien une précision globale de seize bits.

15 On a proposé de stocker en mémoire morte des valeurs numériques de correction, la mémoire étant programmée au moment de l'étalonnage et fournissant ensuite, pour chaque combinaison possible des cinq bits de poids fort, la valeur numérique pré-enregistrée de la correction à apporter pour cette combinaison.

20 Mais ce procédé de correction ne tient pas compte des dérives possibles dans le temps des paramètres électriques du circuit constituant le convertisseur. L'étalonnage est fait une fois pour toutes et ne peut être changé.

On a proposé aussi de faire un réétalonnage périodique 25 du convertisseur en effectuant l'enregistrement des corrections dans une mémoire vive. Le circuit comporte alors ses propres moyens d'étalonnage. Par exemple, le circuit engendre une rampe ultralinéaire (précision 18 bits), en même temps qu'on fait démarrer un compteur à 18 bits comptant à fréquence constante, les 30 cinq premiers bits servant à commander les cinq sources de courant de poids fort. On effectue une comparaison entre le courant de la rampe et le courant de sortie fourni par les combinaisons successives des cinq sources ; le contenu du compteur est relevé et enregistré au moment de l'égalité (pour chaque combinaison). 35 Moyennant un appariement extrêmement précis et délicat de la fréquence de comptage et de la pente de la rampe, on peut faire

en sorte que le contenu du compteur représente l'erreur de conversion pour chaque combinaison possible des cinq bits de poids fort. Cette méthode requiert une précision extrêmement difficile à obtenir sur la linéarité et la pente de la rampe. De plus elle nécessite une interruption du fonctionnement du convertisseur pendant les quelques centaines de millisecondes que dure la phase d'étalonnage.

La présente invention vise à réaliser un convertisseur numérique-analogique de grande résolution ne nécessitant pas l'établissement d'une rampe ultralinéaire de pente extrêmement précise, mais permettant quand même un auto-étalonnage périodique du convertisseur avec une mémoire vive de stockage des valeurs numériques de correction à apporter, la phase d'étalonnage pouvant être effectuée sans interrompre le travail de conversion du convertisseur.

Cette dernière caractéristique peut être très intéressante par exemple pour une application de restitution de son numérisé : l'auto-étalonnage peut se poursuivre périodiquement au cours de la reproduction de paroles ou musique sans entraîner d'interruptions de quelques centaines de millisecondes qui ne seraient pas tolérables pour l'auditeur.

Le convertisseur selon l'invention comprend à cet effet une source de courant supplémentaire, de substitution, qui est mise en service ou déconnectée en fonction de la valeur du code numérique à l'entrée du convertisseur : pour certaines valeurs de ce code, ou plus précisément lorsque ce code est compris dans une gamme de valeurs prédéterminées, la source supplémentaire peut être substituée aux n sources de poids les plus forts du convertisseur (par exemple  $n = 5$ ) pour fournir le courant de sortie du convertisseur ; pendant ce temps on procède à l'étalonnage de ces n sources ; à la fin de cet étalonnage, on peut étalonner la source de substitution elle-même en remettant momentanément en service les n sources de poids forts. Lorsque le code d'entrée sort de la gamme de valeurs prédéterminées, les n sources de poids fort sont maintenues en service pour établir le courant de sortie en fonction du code d'entrée.

En choisissant bien la gamme de valeurs pour lesquelles on fait la substitution, on peut s'arranger pour que l'étalonnage complet puisse être fait très souvent sans empêcher le travail du convertisseur. Par exemple, le son numérisé avec une résolution de seize bits correspond à une dynamique possible de 90 décibels environ, mais il est relativement exceptionnel que l'enregistrement aille au delà d'une dynamique de 60 décibels.

Il sera donc très fréquent que l'entrée du convertisseur reste avec une ou deux configurations fixes des premiers bits de poids fort. Par exemple, avec une configuration 100000 dans l'ordre des poids décroissants, on couvre une gamme de 60 décibels ; avec une configuration 011111, on couvre 60 décibels aussi ; avec les deux configurations on obtient donc une dynamique de 60 décibels en courant positif (100000) ou en courant négatif (011111) ; les termes positif et négatif sont pris arbitrairement pour désigner les courants au dessus ou au dessous d'une valeur moyenne  $I_0$  correspondant à la source de poids le plus fort. Pratiquement, on peut utiliser une ou deux sources de substitution à la place des cinq sources de courant de poids fort, tant qu'on reste dans cette dynamique de 60 décibels, et étalonner pendant ce temps ces sources de poids fort.

En pratique on verra que pour remplacer les deux combinaisons les plus fréquentes 10000 et 01111 on pourra utiliser une source de courant de substitution d'amplitude intermédiaire entre les courants théoriquement donnés par ces deux combinaisons de cinq sources.

La source de substitution aurait alors une valeur correspondant à la combinaison 01111 des six bits de poids les plus forts. Plus généralement, si on veut étalonner  $n$  sources de poids fort, la source de substitution aura une valeur correspondant à la combinaison 011...1 des  $n + 1$  sources de poids les plus forts.

L'étalonnage se fait alors suivant un cycle consistant à établir successivement toutes les combinaisons possibles des  $n$  sources de poids forts, à charger une capacité avec le courant correspondant à une combinaison donnée pendant un temps fixe

correspondant à un cycle complet de comptage à fréquence fixe d'un compteur, à décharger alors linéairement la capacité avec un courant de référence fixe connu, sous-multiple du courant nominal correspondant à la combinaison, et d'examiner le contenu du compteur, pour l'enregistrer en temps que valeur de correction, à la fin de la décharge linéaire. De préférence, le courant de référence a la valeur correspondant au bit numéro  $n$  dans l'ordre des poids décroissants et le compteur a une capacité de  $2^{N-n+2}$  pour donner une indication de correction en unités correspondant à 10 un quart de l'amplitude de la plus petite source de courant (un quart de  $I_0/2^{N-1}$ ).

La combinaison 00000 des cinq ( $n$ ) premiers bits ne correspond pas à un étalonnage véritablement nécessaire car on peut estimer que les sources interrompues fournissent effectivement un courant nul. On met à profit le moment où cette combinaison se présente à la fin du cycle d'étalonnage des diverses combinaisons possibles, pour étalonner la source de substitution elle-même, en remettant en service les sources de poids forts directement commandées par les chiffres binaires qui leur 20 correspondent dans le code numérique d'entrée.

D'autres caractéristiques et avantages de l'invention apparaîtront à la lecture de la description détaillée qui suit et qui est faite en référence aux dessins annexés dans lesquels :

- la figure 1 représente un schéma extrêmement simplifié expliquant le fonctionnement d'un convertisseur numérique-analogique ;

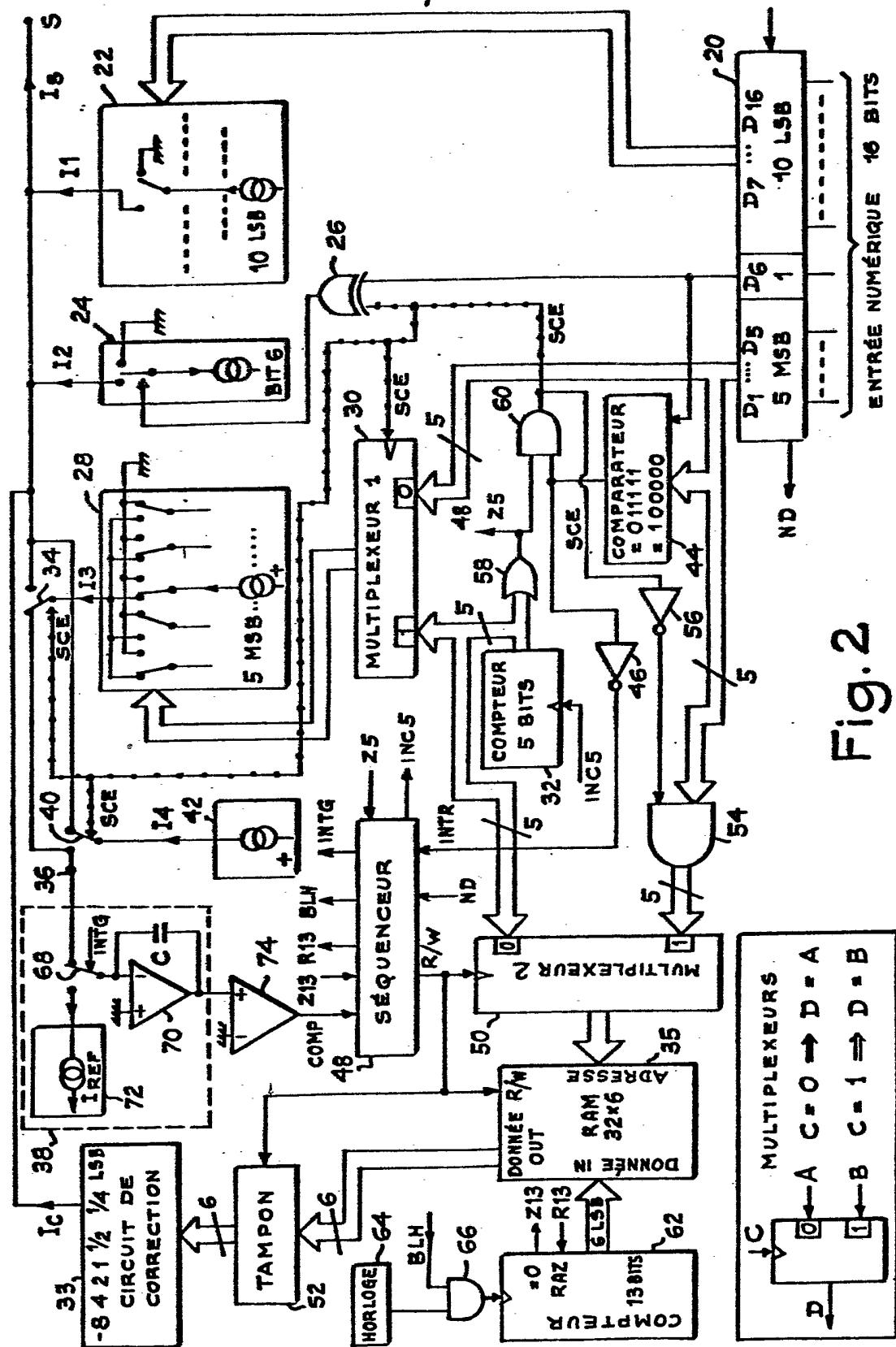

- la figure 2 représente un schéma détaillé du convertisseur selon l'invention.

La figure 1 montre un registre tampon 10 susceptible de recevoir un code numérique binaire d'entrée, représentant un nombre binaire à  $N$  chiffres, dont les chiffres ont des poids décroissants de la gauche vers la droite. Ce registre peut être chargé périodiquement.

Chaque chiffre du registre commande le basculement d'un 35 commutateur respectif susceptible de relier une source de courant respective soit à la sortie S du convertisseur soit à une masse

électrique. Par exemple, un chiffre 0 connecte la source correspondante à la masse et un chiffre 1 la connecte à la sortie S. Les sources sont par ailleurs reliées à une alimentation électrique fournissant l'énergie nécessaire.

- 5       Les sources ont des poids binaires décroissants de la gauche vers la droite, la première ayant une amplitude nominale  $I_0$ , la seconde  $I_0/2$ , etc., la dernière  $I_0/2^{N-1}$ . Le courant de sortie global  $I_S$  du convertisseur a une amplitude qui est la somme des courants des sources effectivement connectées à la sortie S.

- 10      Ce courant est donc proportionnel au nombre binaire à N chiffres présent dans le registre 10.

L'ensemble de conversion proprement dit (N sources de courant de poids binaires décroissants et les commutateurs correspondants) est représenté dans un cadre pointillé désigné par 15 la référence 12. Des ensembles de conversion similaires seront repris dans le circuit de l'invention.

Avec un schéma du type de la figure 1, le courant de sortie varie de 0 (pour un code nul 000...0 à l'entrée) à pratiquement  $2I_0$  (pour un code 111...1), en passant par une valeur 20 médiane  $I_0$  (pour un code médian 100...0 à l'entrée).

La figure 2 montre le schéma synoptique du circuit selon l'invention, pour un convertisseur à seize bits de résolution.

Un registre tampon d'entrée 20 reçoit périodiquement un 25 nombre binaire à N chiffres (ici N = 16). Ce registre est chargé parallèlement et délivre une impulsion ND chaque fois qu'il reçoit une nouvelle donnée à son entrée. Le contenu du registre à un instant donné est constitué par N chiffres binaires D1 à D16 dans l'ordre des poids binaires décroissants. Ces chiffres vont être traités de diverses manières en fonction de leur poids pour 30 effectuer la conversion numérique-analogique.

Les 10 chiffres de plus faible poids, D7 à D16, servent directement à commander un ensemble de conversion 22 à 10 interrupteurs et 10 sources de courant de poids décroissants, de  $I_0/2^6$  à  $I_0/2^{15}$ , analogue à celui de la figure 1.

35      L'ensemble de conversion 22 fournit un courant Il proportionnel au nombre représenté par les chiffres binaires D7 à

D16. Ce courant constitue une partie du courant  $I_s$  de sortie du convertisseur et il est appliqué à la sortie S de celui-ci.

Le chiffre binaire D6 sert quant à lui à la commande d'un ensemble de conversion 24 comportant un interrupteur unique 5 et une source de courant d'amplitude  $I_o/2^5$  susceptible d'être reliée à la sortie S. Le courant de sortie  $I_2$  de l'ensemble de conversion 24 ( $I_2 = 0$  ou  $I_2 = I_o/2^5$ ) constitue une partie du courant  $I_s$  de sortie du convertisseur et il est appliqué à la sortie S de celui-ci.

10 Toutefois le chiffre D6 issu du registre 20 n'est pas appliqué directement comme signal de commande à l'ensemble de conversion 24 : il passe à travers une porte OU exclusif 26 commandée par un signal SCE (Signal de Commande d'Etalonnage), de manière à passer tel quel si SCE est à 0 et à être inversé (on verra 15 pourquoi) si SCE est à 1.

La précision de fabrication des deux ensembles de conversion 22 et 24 est élevée et telle que l'erreur de conversion numérique-analogique n'excède pas un quart de l'amplitude de la plus petite source de courant, soit  $I_o/4 \times 2^{15}$ .

20 Les chiffres binaires D1 à D5, constituant les n bits de poids le plus fort, avec  $n = 5$ , servent à commander un troisième ensemble de conversion 28 à n interrupteurs et n sources de courant d'amplitudes nominales respectives, dans l'ordre des poids décroissants,  $I_o$ ,  $I_o/2$ ,  $I_o/4$ ,  $I_o/8$  et  $I_o/16$ . Toutefois cette commande se fait à travers un multiplexeur 30, commandé par le signal SCE de sorte que c'est seulement si SCE est à 0 que les cinq bits de poids le plus fort sont transmis à travers le multiplexeur et commandent l'ensemble de conversion 28 pour produire un courant  $I_3$  qui constitue une partie du courant de sortie  $I_s$  du convertisseur 25 et qui est appliqué à la sortie S de celui-ci. Si SCE = 1 (phase d'étalonnage des cinq sources de l'ensemble 28), alors cinq bits issus d'un compteur à 5 bits 32 sont transmis à travers le multiplexeur 30 et commandent les 5 commutateurs de l'ensemble de conversion 28, pour leur donner différentes configurations 30 possibles au fur et à mesure du comptage et procéder chaque fois à l'étalonnage.

A la sortie S du convertisseur est encore relié un ensemble de conversion numérique-analogique supplémentaire 33 qui reçoit d'une mémoire vive (RAM) 35 des valeurs numériques de correction, enregistrées au cours de l'étalonnage, et qui produit 5 un courant de correction Ic appliqué à la sortie S du convertisseur. Cet ensemble de conversion est commandé par six bits de correction dont un bit de signe issus de la mémoire 35. Les six sources de courant qui le composent sont des sources d'amplitude  $-8Io/2^{N-1}$ ,  $+4Io/2^{N-1}$ ,  $2Io/2^{N-1}$ ,  $Io/2^{N-1}$ ,  $Io/2x2^{N-1}$ ,  $Io/4x2^{N-1}$  pour 10 effectuer une correction avec une résolution d'un quart de l'amplitude de la plus petite source de courant du convertisseur proprement dit.

Le signal SCE commande d'autre part un premier interrupteur 34 qui, en phase d'étalonnage ( $SCE = 1$ ), déconnecte la sortie 15 de l'ensemble de conversion 28 de la sortie S et l'applique à l'entrée 36 d'un circuit d'intégration 38, et un deuxième interrupteur 40 qui, en phase d'étalonnage ( $SCE = 1$ ), connecte à la sortie S une source de courant de substitution 42 qui produit un courant I4, lequel se substitue au courant I3 délivré par 20 l'ensemble de conversion 28. En dehors de la phase d'étalonnage des cinq sources de poids fort de l'ensemble de conversion 28, SCE est égal à zéro ; alors, d'une part la sortie de l'ensemble 28 est reconnectée à la sortie S du convertisseur, et d'autre part c'est 25 la source de substitution 42 qui est connectée à l'entrée du circuit d'intégration. Le courant de sortie du convertisseur est donc soit  $I1 + I2 + I3 + Ic$ , soit  $I1 + I2 + I4 + Ic$  selon que  $SCE = 0$  ou 1.

Le niveau logique du signal de commande d'étalonnage SCE des sources de poids fort est établi essentiellement à partir d'un 30 comparateur numérique 44 qui détermine si les six bits de poids fort D1 à D6 contenus dans le registre d'entrée 20 sont égaux à l'une des valeurs 10...0 ou 011..1 ou bien s'ils sont différents de ces valeurs.

Le procédé de l'invention repose sur le fait que les six 35 bits de poids fort du code d'entrée sont fréquemment égaux à des valeurs bien définies qui sont 100000 (courant supérieur au

courant moyen  $I_o$ ) ou 011111 (courant inférieur au courant moyen  $I_o$ ). Une source de substitution d'amplitude équivalente à ce que donnerait la combinaison 100000 peut donc être mise en service alors que le code est 100000, à la place de l'ensemble de conversion 5 28 que l'on peut étalonner pendant ce temps, et une autre source de substitution d'amplitude équivalente à ce que donnerait la combinaison 011111 peut être mise en service pendant que le code est 011111, à la place de l'ensemble de conversion 28 que l'on peut étalonner pendant ce temps.

10 En réalité, par une astuce logique, on met en service une seule source de substitution 42, d'amplitude correspondant à la combinaison binaire 011111 des six ( $n+1$ ) chiffres de poids fort, aussi bien lorsque le code binaire présente comme chiffres de poids forts D1 à D6 la combinaison 011111 que lorsqu'il 15 présente la combinaison 100000, et on inverse le dernier bit D6. Il est facile de montrer que dans ces deux cas l'addition de cette source d'amplitude correspondant à 011111, de la source correspondant au bit D6 inversé, et des sources correspondant aux dix derniers bits D7 à D16, produit un courant nominal égal à celui que 20 donneraient les 16 bits D1 à D16 commandant directement les sources de courant des ensembles de conversion 22, 24 et 28. Cette astuce logique explique la présence d'une source de substitution unique 42 et de la porte OU exclusif 26 qui inverse le bit D6 dès lors qu'on est en phase d'étalonnage de l'ensemble de conversion 25 28 ( $SCE = 1$ ) donc dès lors que la source de substitution 42 remplace l'ensemble de conversion 28.

L'amplitude de la source unique 42 a donc pour valeur nominale  $I_o (1/2 + 1/4 + \dots 1/2^n)$ .

Globalement, le fonctionnement du convertisseur est le 30 suivant :

Dans le cas où le comparateur 44 indique que les six bits de poids fort ne sont pas égaux aux valeurs 011111 ou 100000, le signal SCE est à zéro et on n'effectue pas d'étalonnage des sources de poids fort. Tous les bits du registre d'entrée commandent des sources respectives correspondant à leur poids binaire dans les ensembles de conversion 22, 24 et 28 et le courant de

sortie  $I_s$  du convertisseur est égal à  $I_1 + I_2 + I_3 + I_c$ , où  $I_1 + I_2$  représente, avec une précision globale de  $I_o/4x2^{N-1}$  ( $N=16$ ), le nombre  $D_6, D_7 \dots D_{16}$  du registre d'entrée,  $I_3$  représente le nombre  $D_1 \dots D_5$  avec une précision de seulement  $8 I_o/2^{N-1}$ , et  $I_c$  5 représente la correction, enregistrée pendant l'étalonnage, pour ramener  $I_3$  à une valeur juste avec une précision de  $I_o/4x2^{N-1}$ .

$I_c$  est défini par l'ensemble de conversion 33 à 6 bits composé de sources de courant d'amplitudes  $I_o/4x2^{N-1}$  à  $4I_o/2^{N-1}$  et  $-8I_o/2^{N-1}$ .

10 Ce cas où les six bits de poids fort sont différents de 011111 ou 100000 correspond, dans l'application pratique particulièrement considérée de la reproduction du son numérisé, à une amplitude de signal particulièrement forte, en positif ou négatif par rapport à un courant de repos  $I_o$  (correspondant au 15 nombre à 16 bits 1000...0).

On n'effectue l'étalonnage des n sources de l'ensemble de conversion 28 que si le comparateur 44 indique que les six bits  $D_1 \dots D_6$  sont égaux à 011111 ou 100000. S'ils deviennent différents, un signal d'interruption INTR est produit, après 20 inversion dans un inverseur 46, par la sortie du comparateur 44. Ce signal INTR est appliqué à une entrée d'interruption d'un séquenceur 48 qui établit le déroulement des séquences d'étalonnage. Lorsque le signal INTR est reçu, l'étalonnage est interrompu provisoirement jusqu'à ce que le niveau numérique 25 d'entrée soit redevenu "normal".

Lorsqu'on n'effectue pas d'étalonnage, les cinq chiffres de poids supérieur  $D_1 \dots D_5$  sont en outre transmis à la mémoire RAM 35 ; ils servent d'adresse à cette mémoire et désignent un mot de six bits correspondant à la correction enregistrée dans la mémoire 30 RAM lors de l'étalonnage de la combinaison de sources correspondant à la combinaison de chiffres  $D_1 \dots D_5$  : en effet, pour chaque combinaison binaire  $D_1 \dots D_5$ , un étalonnage a été fait et une valeur numérique de correction enregistrée en mémoire RAM à l'adresse  $D_1 \dots D_5$  correspondante.

35 La transmission des chiffres  $D_1 \dots D_5$  aux entrées d'adressage de la mémoire 35 se fait toutefois à travers un

multiplexeur 50 qui peut recevoir sur une entrée ces chiffres et qui peut recevoir sur une autre entrée les cinq chiffres de sortie du compteur à 5 bits 32 qui sert exclusivement aux phases d'étalonnage. Le multiplexeur 50 est commandé par le séquenceur 5 48, et plus précisément par une sortie qui fournit un signal R/W de lecture ou écriture en mémoire RAM : en mode d'écriture (signal R/W = 0), qui n'existe que pendant les phases d'étalonnage, ce sont les sorties du compteur 32 qui passent à travers le multiplexeur ; en mode de lecture (R/W = 1), ce sont 10 soit les chiffres d'entrée D1 à D5 qui sont transmis, soit encore un code 00000 si on est en phase d'étalonnage.

En pratique, le signal R/W commande également un circuit tampon de verrouillage 52 intercalé entre les sorties de données (6 bits) de la mémoire 35 et l'ensemble de conversion 15 supplémentaire de correction 33. En mode de lecture (R/W = 1), le circuit tampon 52 fonctionne en mode transparent de sorte que les entrées de l'ensemble de conversion 33 reçoivent directement une valeur numérique de correction enregistrée en mémoire 35. En mode d'écriture, le circuit 52 est verrouillé et contient la valeur 20 numérique précédemment chargée lorsqu'il était en mode transparent.

Enfin, le signal R/W issu du séquenceur commande la mémoire RAM 35 pour la faire fonctionner en lecture (R/W = 1) ou en écriture (R/W = 0).

25 Une porte ET multiple 54 recevant les cinq premiers bits du registre d'entrée 20 et commandée par la sortie d'un inverseur 56 recevant le signal de commande d'étalonnage SCE, permet de laisser passer les cinq bits vers la première entrée du multiplexeur 50 seulement lorsque SCE = 0 donc en dehors de la 30 phase d'étalonnage des cinq sources de poids fort. Lorsque SCE = 1 un code 00000 est transmis au multiplexeur pour désigner l'adresse 00000 à laquelle est enregistrée en mémoire RAM la correction relative à la source de substitution 42 ; en effet, pendant l'étalonnage de l'ensemble de conversion 28, c'est cette source de 35 substitution qui est en service et qui doit donc être corrigée de la même manière que n'importe quelle combinaison de sources de

poids fort.

La séquence d'étalonnage se déroule de la manière suivante, sous le contrôle du séquenceur 48 : le code d'entrée est supposé comprendre l'une des combinaisons 011111 ou 100000 pour 5 les six bits de poids fort (sinon on n'effectue pas l'étalonnage). Le séquenceur fournit un signal R/W = 1 (lecture) ; le compteur 32 à 5 bits reçoit un signal d'incrémentation INC5 du séquenceur ; on supposera que son contenu est différent de zéro après cette incrémentation ; un contenu nul du compteur 32 annulerait le 10 signal SCE grâce à une porte OU 58 recevant toutes les sorties du compteur et connectée à une entrée d'une porte ET 60 dont l'autre entrée reçoit la sortie du comparateur 44 ; ainsi, SCE est égal à 1 lorsque le comparateur 44 indique que les six bits de poids fort sont égaux à 011111 ou 100000 mais à condition que le contenu du 15 compteur 32 ne soit pas à zéro.

Le contenu du compteur à 5 bits 32 étant supposé non nul, le signal SCE est engendré ; l'adresse désignée en lecture pour la mémoire 35 est 00000 pour fournir la valeur de correction relative à la source de remplacement 42 ; le circuit tampon 52 en 20 mode transparent (R/W = 1) transmet cette adresse au circuit de conversion 33 qui établit un courant Ic correspondant.

Le séquenceur engendre un signal R13 de remise à zéro d'un compteur à 13 bits 62 actionné par une horloge 64 à fréquence élevée. Une porte ET 66 est intercalée entre l'horloge et l'entrée 25 de comptage du compteur 62 ; cette porte ET reçoit comme signal de validation un signal BLH issu du séquenceur, le comptage n'étant autorisé que lorsque BLH = 1.

Les six bits de poids le plus faible du compteur à 13 bits 62 sont reliées aux six entrées de données de la mémoire RAM 30 35 car c'est le contenu du compteur 62 après un cycle d'étalonnage qui représentera l'erreur de conversion à mettre en mémoire.

Le séquenceur fournit un signal INTG pour commander un commutateur 68 susceptible d'appliquer à l'entrée d'un intégrateur 70 soit le courant à étalonner (INTG = 1), soit une source de 35 courant de référence 72 établissant un courant Iréf de sens contraire aux courants des sources des ensembles de conversion

(INTG = 0). Le courant à étalonner est le courant I3 qui sort de l'ensemble de conversion 28 commandé par la combinaison de sortie courante du compteur 32 : on étalonne en effet les cinq sources de l'ensemble 28 dans toutes leurs différentes configurations 5 possibles définies par les états successifs du compteur 5 bits, chaque état correspondant à un cycle d'étalement.

Le processus d'intégration en vue de l'étalement se fait selon une quadruple rampe.

Au départ, le courant I3 est appliqué à l'intégrateur 70 10 et un comparateur 74 placé en sortie de l'intégrateur 70 bascule et fournit un signal COMP = 1 lorsque la tension de sortie de l'intégrateur passe au dessus de zéro.

Le signal COMP est appliquée au séquenceur 48 et commande l'inversion du signal INTG donc l'application à l'entrée de 15 l'intégrateur du courant Iréf de la source de référence 72. La tension de sortie de l'intégrateur descend au dessous de zéro et redéclenche le basculement du comparateur qui fournit au séquenceur 48 un signal COMP = 0. Cette procédure de charge et décharge à courant constant de l'intégrateur selon une double 20 rampe est préliminaire au cycle d'étalement proprement dit et sert à éliminer les erreurs dues au temps de réponse non nul du comparateur et à son seuil de basculement non nul.

Le séquenceur établit alors le signal BLH = 1 et le signal INTG = 1 pour d'une part déclencher le comptage du compteur 25 62 et d'autre part reconnecter le courant I3 à l'entrée de l'intégrateur 70.

Le compteur à 13 bits 62 compte à la fréquence fixe et rapide de l'horloge 64 pendant que le courant I3 est intégré. Lorsque le compteur 62 a fait un cycle complet et repasse à zéro, 30 il envoie un signal Z13 = 1 au séquenceur ; celui-ci arrête l'intégration qui aura donc duré un temps fixe, et il inverse à nouveau le signal INTG pour commuter le courant Iréf à la place du courant I3, en changeant donc le sens de l'intégration. C'est la deuxième intégration en double rampe, dans la même capacité de 35 l'intégrateur 70.

La tension de sortie de l'intégrateur décroît donc à

nouveau pendant que le compteur 62 compte.

Lorsque la tension de sortie est redevenue nulle, elle fait basculer le comparateur 74 qui fournit au séquenceur un signal COMP = 0. Ce dernier arrête immédiatement le comptage (BLH 5 = 0). On remarque que l'intégration négative jusqu'à basculement du comparateur se fait avec la même pente (Iréf) que l'intégration préliminaire ; c'est ce qui permet d'éliminer l'effet des imperfections du comparateur 74, et c'est la raison pour laquelle cette intégration en quadruple rampe est utilisée.

10 Le courant Iréf est choisi égal au courant de la source de poids  $I_0/2^{n-1}$  (correspondant au bit D5) de l'ensemble de conversion 28 du convertisseur. Cette égalité est vraie avec une précision de 12 bits donc avec une erreur au plus égale à la moitié de la plus petite source de courant correspondant au bit 15 D16 (en fait il vaut mieux s'arranger pour que cette précision soit légèrement meilleure).

Par conséquent, si la combinaison de cinq sources de poids le plus fort fournissait un courant I3 juste, ce courant serait un multiple du courant Iréf et la durée d'intégration avec 20 Iréf serait un multiple de la durée d'intégration avec I3. On retrouverait donc à la fin un contenu nul du compteur 62.

En fait, I3 n'est pas juste et le contenu du compteur 62 à la fin de l'intégration représente l'erreur sur le courant I3, exprimée en unités égales à un quart de la plus petite source de 25 courant de l'ensemble de conversion 22. Ceci résulte du fait que le compteur est à 13 bits ( $N-n+2$ ) et que Iréf correspond au cinquième bit (n<sup>ième</sup> bit).

Comme l'erreur sur la conversion des sources de poids fort n'excède pas huit fois la valeur de la plus petite source de 30 courant, on ne s'intéresse qu'aux derniers bits du compteur, en pratique les cinq derniers et un bit de signe qui peut être le bit précédent les cinq derniers. Ces bits sont appliqués aux entrées de données de la mémoire RAM 35.

Le séquenceur fait passer à zéro le signal R/W. Le circuit de verrouillage 52 garde alors en mémoire la valeur de correction de la source de courant de remplacement 42 pour que

celle-ci continue d'être corrigée ; le multiplexeur 50 bascule pour appliquer aux entrées d'adressage de la mémoire les sorties du compteur 32 à 5 bits, c'est à dire une adresse correspondant à la combinaison de bits en cours d'étalonnage. Enfin, R/W commande 5 l'écriture en mémoire RAM à cette adresse.

On notera toutefois que cette procédure d'écriture ne se déroule que si un nouveau code d'entrée n'est pas en cours d'introduction dans le registre 20. Un signal ND de nouvelle donnée passe à 1 et modifie le fonctionnement normal du séquenceur 10 en cas de changement de donnée pour maintenir provisoirement R/W à 1 (lecture) jusqu'à la fin du signal ND.

Après écriture, le séquenceur rétablit R/W à 1 et fournit un signal INC 5 d'incrémentation du compteur 32 pour passer à 15 un nouveau cycle d'étalonnage correspondant à la combinaison suivante de cinq bits.

Les cycles d'étalonnage se succèdent jusqu'à ce que le contenu du compteur 32 soit à zéro. Comme il n'y a pas besoin de faire un étalonnage dans le cas où les cinq sources de courant de poids fort sont déconnectées, on profite de l'adresse 00000 pour 20 stocker une valeur de correction de la source de substitution 42. On étalonne donc celle-ci suivant le même processus lorsque le contenu du compteur 32 est nul ; ceci se fait en annulant le signal SCE (grâce à la porte OU 58 et à la porte ET 60), ce qui a pour effet de remettre les commutateurs 34, 40, le multiplexeur 25 30, et la porte ET 54 dans un état similaire à celui qu'ils ont en dehors de la séquence d'étalonnage des cinq sources de poids fort.

Ces sources, commandées à travers le multiplexeur 30 par les cinq bits de poids fort, établissent un courant de sortie I3 30 corrigé par un courant de correction Ic établi à partir de la mémoire 35 adressée par les cinq bits de poids fort (porte ET 54 ouverte, multiplexeur 50 en position lecture R/W = 1).

Le courant de la source de substitution 42 est appliqué au circuit d'intégration 38 et le cycle d'étalonnage est identique 35 à ce qui a été décrit ci-dessus.

Si le signal d'entrée numérique sort de la dynamique

moyenne de 60 décibels où l'étalement est autorisé, les six bits de poids fort deviennent différents de 01111 ou 100000 et le comparateur 44 fournit un zéro logique qui, après inversion dans l'inverseur 46, établit un signal INTR d'interruption du 5 séquenceur.

Trois cas peuvent alors se produire :

1°/ le séquenceur a terminé les phases où le courant à étalement (I3 ou I4) est appliqué à l'entrée de l'intégrateur 70. La séquence d'étalement peut se poursuivre normalement jusqu'à la 10 fin du cycle car on n'a plus besoin pour l'étalement du courant délivré par les cinq sources de poids fort ; celles-ci peuvent donc servir à engendrer un courant I3 correspondant aux cinq bits de poids fort à l'entrée, ce courant étant transmis à la sortie S du convertisseur.

15 2°/ le compteur 32 à cinq bits est à zéro (on étalement la source de remplacement 42) ; on n'a donc pas besoin des cinq sources de poids fort pour l'étalement, le déroulement du cycle reste normal. Un signal de sortie Z5 de la porte OU 58 est transmis à cet effet au séquenceur.

20 3°/ Dans tous les autres cas, il faut interrompre le déroulement de l'étalement, l'horloge du compteur 62 à 13 bits est bloquée ( $BLH = 0$ ) ; le compteur 62 est remis à zéro (impulsion  $R13 = 1$ ) et on attend un nouveau signal  $SCE = 1$  pour reprendre le cycle dans la phase qui suit l'incrémentation du compteur 32 à 25 cinq bits.

Le circuit détaillé qui vient d'être décrit peut subir un certain nombre de modifications sans sortir du cadre de l'invention.

Par exemple, on peut utiliser deux sources de substitution au lieu d'une seule, ayant des valeurs correspondant aux codes 10000 et 01111 (chiffres de poids le plus fort), mises en service en fonction des résultats de deux comparateurs séparés. L'avantage qui en résulte est la possibilité d'augmenter de 6 décibels la dynamique moyenne de signal d'entrée pour laquelle 35 l'étalement est autorisé. L'inconvénient est surtout la nécessité de prévoir un étalement séparé pour chacune des sources de

substitution, et un rangement en mémoire à deux positions de mémoire séparées.

Une autre modification de circuit possible concerne le circuit de correction (33) : on l'a décrit sous forme d'un ensemble de conversion numérique-analogique recevant une information numérique de correction à 6 bits et fournissant un courant de correction  $I_c$  qui s'ajoute aux courants des autres ensembles de conversion. On pourrait prévoir que la sortie du circuit de verrouillage 52 est appliquée à une entrée d'un additionneur-soustracteur qui reçoit par ailleurs le code d'entrée contenu dans le registre 20 et qui établit un code modifié en fonction de la correction, pour commander les ensembles de conversion 22, 24, 28. L'ensemble de conversion 22 comporterait en outre dans ce cas des sources de courant d'amplitude  $I_0/2x2^{N-1}$  et  $I_0/4x2^{N-1}$  (correction avec une précision d'un quart de l'amplitude de la source de courant  $I_0/2^{N-1}$  correspondant au poids binaire le plus faible D16).

Bien entendu, la réalisation particulière qui a été décrite avec  $N = 16$  et  $n = 5$  n'est pas limitative. Elle ne sert que comme exemple pour l'explication, étant entendu qu'on a supposé que l'on savait bien faire des ensembles de conversion ayant une précision de 12 bits.

## REVENDICATIONS

1. Convertisseur numérique-analogique comportant une pluralité de sources de courant commandables (22, 24, 28), de poids binaires différents correspondant aux poids binaires des N chiffres (D1 à D16) d'un code numérique d'entrée du convertisseur, 5 pour produire un courant de sortie global (Is) d'amplitude proportionnelle au nombre représenté par ce code, un moyen d'étalonnage des n sources de poids le plus fort (28) pour fournir des indications numériques sur les erreurs de conversion entre le courant fourni par ces n sources et le courant nominal qu'elles 10 devraient fournir, une mémoire vive (35) pour enregistrer ces indications numériques et les restituer en fonction des besoins selon le code numérique à l'entrée du convertisseur, un moyen de correction (33) du courant de sortie, couplé à la sortie de la mémoire (35) et fournissant une correction fonction des indica- 15 tions contenues dans la mémoire, caractérisé par le fait qu'il est prévu une source de courant supplémentaire (42), de substitution, un comparateur numérique (44) recevant le code à l'entrée du convertisseur et apte à fournir un signal de commande si le code est compris entre des valeurs déterminées, et des moyens de com- 20 mutation (34, 40) commandés à partir de ce signal pour connecter à la sortie du convertisseur la source de substitution, déconnecter de cette sortie les n sources de poids le plus fort et les con- necter au moyen d'étalonnage, et autoriser le fonctionnement du moyen d'étalonnage, si le code est compris entre les valeurs 25 déterminées.

2. Convertisseur selon la revendication 1, caractérisé par le fait que l'amplitude de la source de courant de substitution (42) a pour valeur nominale  $I_0 (1/2 + 1/4 + \dots + 1/2^{n-1})$  où  $I_0$  est l'amplitude nominale de la source de courant de poids le plus 30 fort.

3. Convertisseur selon la revendication 2, caractérisé par le fait que la source de poids N-n fournissant un courant

$I_{O/2^n}$  est commandée par le chiffre de poids N-n lorsque la source de substitution est déconnectée de la sortie, et par l'inverse de ce chiffre lorsque la source de substitution est connectée à la sortie du convertisseur.

5           4. Convertisseur selon l'une des revendications 1 à 3, caractérisé par le fait que le comparateur (44) est apte à comparer les n+1 poids forts (D1 à D6) du code d'entrée aux valeurs 011...1 et 100...0 et, en cas d'égalité avec l'une de ces deux valeurs, à donner un ordre de connection de la source de substitution (42) en remplacement des n sources de poids le plus fort, et de connection d'une combinaison de ces n sources au moyen d'étalonnage.

10           5. Convertisseur selon la revendication 4, caractérisé par le fait que l'ordre de connection donné par le comparateur peut être inhibé au cours d'une partie de l'étalonnage, en vue de l'étalonnage de la source de substitution, et que le moyen d'étalonnage est apte à enregistrer une valeur de correction relative à la source de substitution, à une adresse spécifique (00000) de la mémoire vive (35).

15           20       6. Convertisseur selon l'une des revendications 1 à 5, caractérisé par le fait que le moyen d'étalonnage établit, à partir d'un compteur à n bits (32), des configurations successives de connection des n sources de poids le plus fort (28), que pour chaque configuration un cycle d'étalonnage est effectué, une valeur 25 de correction est enregistrée à une adresse de mémoire définie par le contenu du compteur (32), puis le compteur est incrémenté en vue d'un nouveau cycle.

20           7. Convertisseur selon la revendication 6, caractérisé par le fait que lorsque le compteur à n bits (32) est à zéro, un étalonnage de la source de substitution est effectué, les n sources de poids forts étant reconnectées à la sortie du convertisseur en fonction des n chiffres de poids fort (D1 à D5) du code d'entrée.

25           35       8. Convertisseur selon l'une des revendications 1 à 7, caractérisé par le fait que le moyen d'étalonnage est apte à effectuer une intégration à double rampe et comprend un

intégrateur (70), une source de courant de référence (72) d'amplitude sous multiple de l'amplitude des n sources de poids forts, et de signe contraire, un compteur (62) à au moins N-n bits, une horloge (64), et un séquenceur (48) pour :

- 5           1) connecter à l'intégrateur une combinaison des n sources de courant de poids forts, pour faire croître la tension de sortie de l'intégrateur à partir d'une valeur initiale pendant un temps correspondant à un cycle de comptage du compteur à au moins (N-n) bits,

- 10          2) connecter à l'intégrateur la source de référence, arrêter l'intégration quand la tension de sortie est revenue à sa valeur initiale, arrêter le comptage du compteur à au moins (N-n) bits, et enregistrer en mémoire vive le contenu de ce compteur à une adresse correspondant à la combinaison de n sources

- 15          considérée.

9. Convertisseur selon la revendication 8, caractérisé par le fait qu'avant l'intégration en double rampe du courant des n sources et de la source de courant de référence, on effectue une autre intégration en double rampe avec les mêmes sources de manière à faire basculer deux fois un comparateur placé en sortie de l'intégrateur.

1/2

Fig.1

2/2

Fig. 2