(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5441651号

(P5441651)

(45) 発行日 平成26年3月12日(2014.3.12)

(24) 登録日 平成25年12月27日(2013.12.27)

(51) Int.Cl.

H04N 5/357 (2011.01)

H04N 5/232 (2006.01)

F 1

H04N 5/335 570

H04N 5/232 A

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2009-278007 (P2009-278007)

(22) 出願日 平成21年12月7日 (2009.12.7)

(65) 公開番号 特開2011-120175 (P2011-120175A)

(43) 公開日 平成23年6月16日 (2011.6.16)

審査請求日 平成24年11月27日 (2012.11.27)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 衣笠 友壽

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 松永 隆志

(56) 参考文献 特開平09-200614 (JP, A)

最終頁に続く

(54) 【発明の名称】光電変換装置

## (57) 【特許請求の範囲】

## 【請求項 1】

対をなすラインセンサ部を有し、前記ラインセンサ部の各々が、光電変換された信号を出力するセンサセル部と、複数のメモリセル部と、を有する単位画素を複数有する焦点検出装置であって、前記焦点検出装置は、一の前記センサセル部を初期化したことによって生じるリセットノイズを、前記一のセンサセル部に対応して設けられた複数の前記メモリセル部に同時に書き込み、前記センサセル部または前記メモリセル部から出力された信号を受けて、前記センサセル部または前記メモリセル部に転送する転送部であって、前記センサセル部から出力された信号と、前記メモリセル部に書き込まれた前記リセットノイズおよび前記転送部で生じるノイズとの差分処理を行う転送部を備え、さらに前記ラインセンサ部を複数の領域に分けて、前記ラインセンサ部の端部を含まない一部の領域でデフォーカス量の検出を行い、所定のコントラストが得られた場合には各前記単位画素の一のメモリセル部を用いて前記差分処理を行い、前記所定のコントラストが得られない場合には、前記ラインセンサ部の全体の領域でデフォーカス量の検出を行い、前記一のメモリセル部とは異なるメモリセル部を用いて前記差分処理を行うことを特徴とする焦点検出装置。

10

20

**【請求項 2】**

前記センサセル部は、光電変換部と、光電変換部で生じた電荷を増幅して出力する増幅部とを備えることを特徴とする請求項 1 に記載の焦点検出装置。

**【請求項 3】**

請求項 1 または 2 に記載の焦点検出装置を備える撮像システム。

**【請求項 4】**

対をなすラインセンサ部を有し、

前記ラインセンサ部の各々が、光電変換された信号を出力するセンサセル部と、複数のメモリセル部と、を有する単位画素を複数有する焦点検出装置の駆動方法であって、前記焦点検出装置は、前記センサセル部または前記メモリセル部から出力された信号を受けて

10

、前記センサセル部または前記メモリセル部に転送する転送部であって、前記センサセル部から出力された信号と、前記メモリセル部に書き込まれた前記リセットノイズおよび前記転送部で生じるノイズとの差分処理を行う転送部を備え、さらに

一の前記センサセル部を初期化したことによって生じるリセットノイズを、前記一のセンサセル部に対応して設けられた複数の前記メモリセル部に同時に書き込み、

前記ラインセンサ部を複数の領域に分けて、前記ラインセンサ部の端部を含まない一部の領域でデフォーカス量の検出を行い、

所定のコントラストが得られた場合には各前記単位画素の一のメモリセル部を用いて前記差分処理を行い、

前記所定のコントラストが得られない場合には、前記ラインセンサ部の全体の領域でデフォーカス量の検出を行い、前記一のメモリセル部とは異なるメモリセル部を用いて前記差分処理を行うこと

20

を特徴とする焦点検出装置の駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は光電変換装置に関し、特に、光電変換を行う光電変換部と、光電変換部からの信号を転送する転送部と、光電変換部からの信号を保持する記憶部と、を備える光電変換装置に関する。

30

**【背景技術】****【0002】**

撮像システムにおいては、焦点を検出する A F ( A u t o F o c u s i n g ) センサを備えることが一般的である。近年の A F センサは、焦点検出の高速化とともに、検出精度を高めることが求められている。

**【0003】**

特許文献 1 には、センサセル部から出力された信号をメモリセル部に転送する転送系を備えた固体撮像装置が記載されている。この中で、メモリセル部は複数設けられても良いことが記載されている。

**【0004】**

特許文献 2 には、ラインセンサを複数の領域に分割した場合にそれぞれの領域に対応する蓄積信号を記憶するフレームメモリと、ラインセンサの全領域に対応する蓄積信号を記憶するフレームメモリと、を備える焦点検出装置が記載されている。特許文献 2 によれば、デフォーカス量が大きい場合でも高速に焦点検出を行えるとしている。

40

**【先行技術文献】****【特許文献】****【0005】**

【特許文献 1】特開平 09 - 200614 号公報

【特許文献 2】特開 2006 - 220684 号公報

**【発明の概要】****【発明が解決しようとする課題】**

10

20

30

40

50

**【0006】**

しかしながら、特許文献1および特許文献2のいずれにも、1つのセンサセル部に対して複数のメモリセル部を設ける具体的な回路構成もその動作も開示がない。

**【0007】**

本発明は、1つのセンサセル部に対して複数のメモリセル部を設けた構成における好適な光電変換装置を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

上記課題を解決する本発明は、対をなすラインセンサ部を有し、前記ラインセンサ部の各々が、光電変換された信号を出力するセンサセル部と、複数のメモリセル部と、を有する単位画素を複数有する焦点検出装置であって、前記焦点検出装置は、一の前記センサセル部を初期化したことによって生じるリセットノイズを、前記一のセンサセル部に対応して設けられた複数の前記メモリセル部に同時に書き込み、前記センサセル部または前記メモリセル部から出力された信号を受けて、前記センサセル部または前記メモリセル部に転送する転送部であって、前記センサセル部から出力された信号と、前記メモリセル部に書き込まれた前記リセットノイズおよび前記転送部で生じるノイズとの差分処理を行う転送部を備え、さらに前記ラインセンサ部を複数の領域に分けて、前記ラインセンサ部の端部を含まない一部の領域でデフォーカス量の検出を行い、所定のコントラストが得られた場合には各前記単位画素の一のメモリセル部を用いて前記差分処理を行い、前記所定のコントラストが得られない場合には、前記ラインセンサ部の全体の領域でデフォーカス量の検出を行い、前記一のメモリセル部とは異なるメモリセル部を用いて前記差分処理を行うこと

10

を特徴とする焦点検出装置である。

20

**【発明の効果】****【0009】**

本発明によれば、1つのセンサセル部に対して複数のメモリセル部を設けた光電変換装置において、好適な動作を実現できる。

**【図面の簡単な説明】****【0010】**

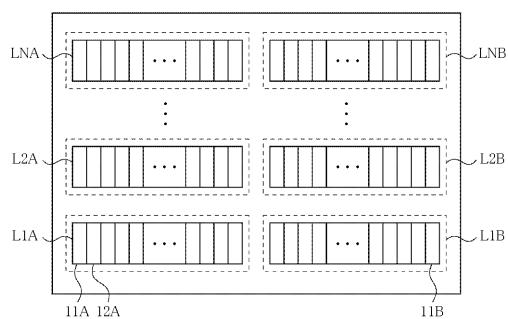

【図1】実施例1に係る位相差AF用の光電変換装置における撮像面を模式的に示す図である。

30

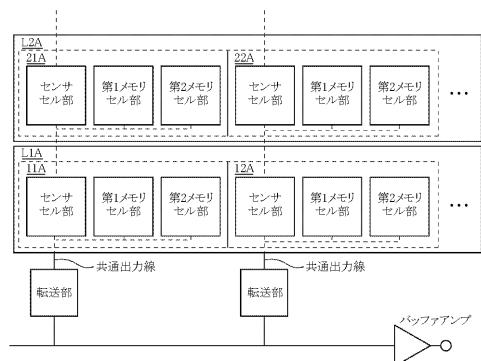

【図2】実施例1に係るラインセンサ部を示すブロック図である。

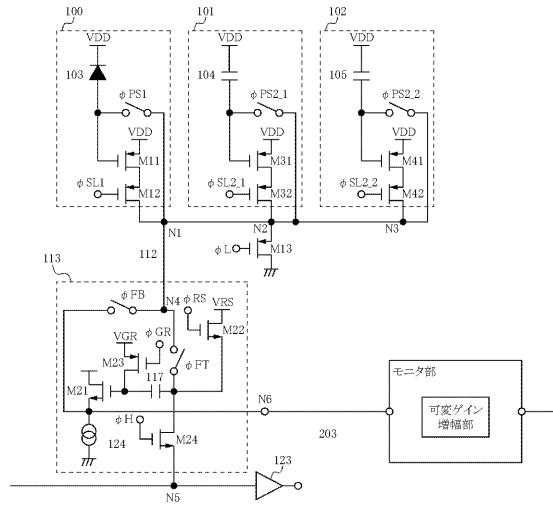

【図3】本発明の第1の実施例に係る光電変換装置の回路図である。

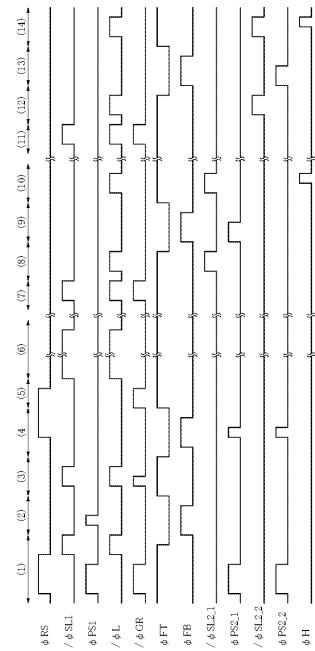

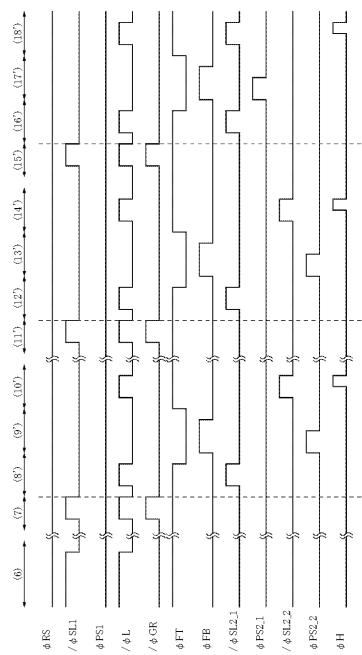

【図4】本発明の第1の実施例に係るタイミング図である。

【図5】本発明の第2の実施例に係るタイミング図である。

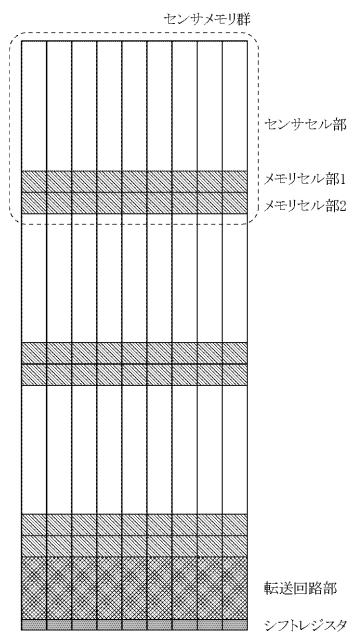

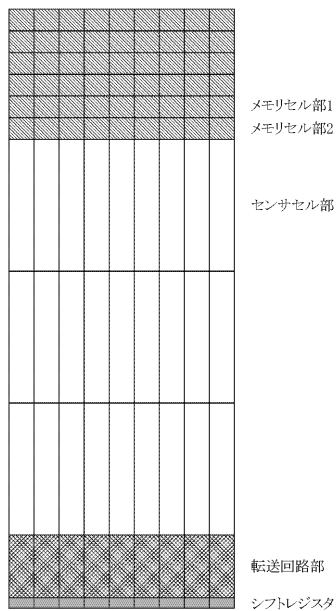

【図6】本発明の第1の実施例に係る光電変換装置のレイアウト図である。

【図7】本発明の第1の実施例に係る光電変換装置のレイアウト図である。

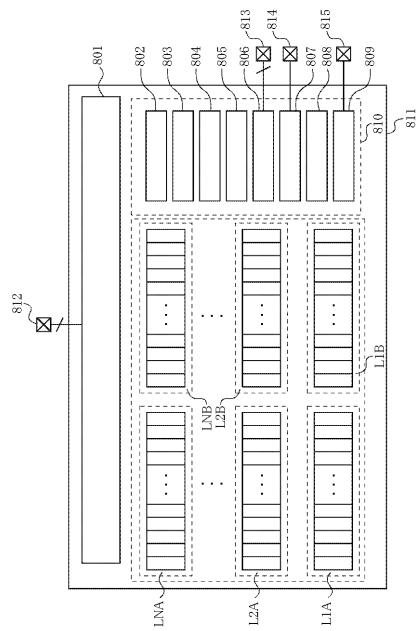

【図8】本発明の第3の実施例に係る焦点検出装置(AFセンサ)の構成例を示すブロック図である。

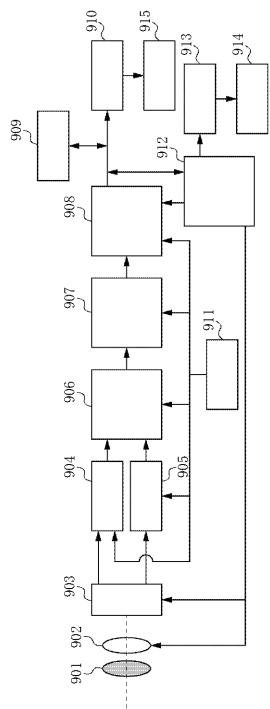

【図9】本発明の第4の実施例にかかる撮像システムの構成例を示すブロック図である。

40

**【発明を実施するための形態】****【0011】**

まず、本発明の利点を説明するために、仮に特許文献1に開示された構成において、特許文献2にあるように、1つのセンサセル部に対してメモリセル部を2つ設けることを考える。特許文献2によれば、蓄積動作に先だってセンサセル部のノイズ信号をメモリセル部に信号を書き込む動作が行われる。そのため、仮に特許文献1に開示された構成で2つのメモリセル部を設けると、メモリセル部へノイズ信号を書き込む動作が2回必要になる。そのため、ノイズ信号の書き込み動作の後に開始するオートゲインコントロール(Automatic Gain Control; 以下AGCと称する)を開始するタイミングが遅くなることが考えられる。

50

**【0012】**

上述の場合に問題となるのは、入射光の強度が強い場合である。入射光強度が強いということはセンサセル部が短い期間で信号の飽和レベルに達することを意味する。従って、A G C を開始するタイミングが遅くなると、A G C を開始するよりも前に信号が飽和レベルに達してしまい、A G C を適切に行えなくなるおそれがある。

**【0013】**

上記の問題に対処する本発明の具体的な実施例を以下に説明する。

**【0014】****(実施例1)**

図面を参照しながら本発明に係る第1の実施例を説明する。第1の実施例は、位相差焦点検出(Auto Focusing; AF)用の光電変換装置に適用した例を示す。10

**【0015】**

図1は、位相差AF用の光電変換装置における撮像面を模式的に示した図である。撮像面には、対となるラインセンサ部L1AとL1B、L2AとL2B、…LN AとLN Bが存在する。一对のラインセンサ部は撮像面のある領域における被写体のデフォーカス量を測定するために用いられ、このラインセンサ部の対を複数配列することで測距点を複数設け、AFの精度の向上を図るものである。各ラインセンサ部は、単位画素11A、12A、…を含んでいる。

**【0016】**

図2は、ラインセンサ部L1A、L2A、…に係る部分をより詳細に示したブロック図である。各単位画素はセンサセル部、第1メモリ部、及び第2メモリ部を備える構成で、共通出力線に接続されている。また、異なるラインセンサ部の同様の位置に存在する単位画素は、共通出力線を介して共通の転送部に接続される。各転送部は、共通のバッファアンプに接続される。ラインセンサ部L1B、L2B、…も図2と同様の構成である。20

**【0017】**

図3は、図2で示した構成のうちラインセンサ部LS1を抜き出しており、特に単位画素11Aと、これと接続された転送部とに着目して説明を行う。単位画素11Aは、センサセル部101、第1メモリセル部301、及び第2メモリセル部401とを含む。図3において、MOSトランジスタの制御電極並びにスイッチに付された「X」は、不図示の制御部から供給される信号を意味している。30

**【0018】**

単位画素11Aに着目すると、センサセル部100は光電変換部であるフォトダイオード(PD)103、センサセル部書き込みスイッチ106、及びトランジスタM11、M12を含む。PD103のアノードはセンサセル部書き込みスイッチ106の一方の端子とトランジスタM11の制御電極と接続され、カソードは電源電圧VDDに接続される。トランジスタM11及びM12は、MOSトランジスタM12が導通すると負荷MOSトランジスタM13とともにゲインが-1の反転アンプを構成する。センサセル部100は、この反転アンプを介してフォトダイオード103で光電変換された電荷量に基づく蓄積信号を共通出力線112に出力する。つまり、MOSトランジスタM12はセンサセル部100を選択するための選択スイッチとして機能する。センサセル部書き込みスイッチ106はフォトダイオード103のアノードと共に出力線112との導通または非導通を切り換えるもので、PMOSトランジスタ、NMOSトランジスタ、CMOSトランジスタなどで構成することができる。40

**【0019】**

メモリセル部101及び102は、センサセル部100におけるフォトダイオード103をメモリ容量104、105に置き換えた構成となっているので説明を省略する。本図では負荷MOSトランジスタM13がセンサセル部100、メモリセル部101及び102に共通に設けられているが、各セル部につき1つの負荷MOSトランジスタを設けても良い。50

**【0020】**

次に、転送部113について説明する。転送部113は、MOSトランジスタM21～M24、転送容量117、フィードバックスイッチ120及びトランスマースイッチ121を含む。トランスマースイッチ121の一方の端子は共通出力線112及びフィードバックスイッチ120の一方の端子と接続される。トランスマースイッチ121の他方の端子は、転送容量117の一方の端子、MOSトランジスタM22の一方の主電極、及びMOSトランジスタM24の一方の主電極に接続される。MOSトランジスタM22の他方の主電極は電源電圧VRSに接続される。光信号読み出しスイッチであるMOSトランジスタM24の他方の主電極はバッファアンプ123に接続される。転送容量117の他方の端子はMOSトランジスタM21の制御電極およびMOSトランジスタM23の一方の主電極に接続される。MOSトランジスタM21の一方の主電極は電源電圧VDDに接続され、他方の主電極は定電流源124、ノードN6、及びフィードバックスイッチ120の他方の端子に接続される。転送部は、後述する動作により、センサセル部から出力された信号と、メモリセル部に書き込まれたリセットノイズおよび転送部で生じるノイズとの差分処理を行う。

**【0021】**

以下では図3及び4を参照しながら本実施例に係る光電変換装置の動作を説明する。図4では、図3に示すスイッチやMOSトランジスタの制御電極に与えられる信号を示している。PMOSトランジスタに与えられる信号は反転信号として“/”を付している。従って、各スイッチ及びMOSトランジスタは、図4に示す対応する信号がハイレベルで導通する。

**【0022】**

期間(1)では、フォトダイオード103及びメモリ容量104、105をリセットする動作が行われる。その後、フォトダイオード103をリセットすることによってセンサセル部100で生じたノイズNsを転送容量117に書き込む動作を行う。

**【0023】**

まず、信号RS、FT、PS1、PS2\_1、PS2\_2及び/GRがハイレベルになることで、センサセル部書き込みスイッチ106、メモリセル部書き込みスイッチ107、108、トランスマースイッチ121、MOSトランジスタM22及びMOSトランジスタM23が導通する。これにより、フォトダイオード103及びメモリ容量104、105が電源電圧VRSにリセットされるとともに、転送容量117の両電極が電源電圧VRSおよびVGSにリセットされる。

**【0024】**

次に、信号/GRがローレベルになることで転送容量117の他方の端子がフローイングになる。そして信号PS1、PS2\_1、PS2\_2及びRSがローレベルになった後に、信号/SL1及び/Lがハイレベルになると、センサセル部100のリセット後のセンサノイズNsが転送容量117に書き込まれる。

**【0025】**

期間(2)で信号FBがハイレベルになると、転送容量117に保持されたセンサノイズNsに転送部113のノイズNtが重畠されたノイズNs+Ntが、MOSトランジスタM21と定電流源124とで構成されるソースフォロワによって共通出力線112に出力される。この期間に信号PS1が一時的にハイレベルとなることで、ノイズNs+Ntがセンサセル部100に書き込まれる。信号PS1がローレベルになったタイミングから、センサセル部の蓄積動作期間が開始する。

**【0026】**

期間(3)で信号/SL1、/Lがハイレベルになると、センサセル部100に保持されていた(Ns+Nt)が反転されて、これにNsが加わって出力される。すなわち、センサセル部100の出力は-(Ns+Nt)+Ns=-Ntとなる。このとき、/GRおよびFTがハイレベルになると転送容量117の一方の端子には-Ntが、他方の電極にはVGRが与えられる。そのg、信号/GRがローレベルになると転送容量1

17の他方の端子がフローティングとなり、転送容量117にはVGR+Ntの電位差が保持される。

#### 【0027】

期間(4)に信号RSがハイレベルになると転送容量117の一方の端子がVRSになり、転送部ノイズNt分だけ変動するので、他方の端子もNt分だけ変動する。このとき信号FBがハイレベルであるので、転送部113のソースフォロワからノイズ $2 \times Nt$ が出力されることになる。式には明示しないが、ノイズ $2 \times Nt$ に加えて、期間(1)でセンサセル部を初期化したことによって生じるランダムノイズ(以下、リセットノイズと称す)も重畠されている。

#### 【0028】

さらに、期間(4)では信号PS2\_1、PS2\_2もともにハイレベルであるので、スイッチ107および108を介してメモリセル部101、102にも $2 \times Nt$ が同時に書き込まれる。ここで同時とは、期間(4)において信号RSとFBとがともにハイレベルである期間に、信号PS2\_1、PS2\_2によって $2 \times Nt$ がメモリセル部101と102の両者に書き込まれることを意味する。信号PS2\_1とPS2\_2とが同時にローレベルに遷移することは必ずしも必要ではない。

10

#### 【0029】

期間(5)では、信号FTがハイレベルである。期間(5)に信号RSおよび/GRがハイレベルになると、共通出力線112と転送容量117の一方の端子がVRSに、他方の端子がVGRにリセットされる。その後、信号RSおよび/GRがローレベルにすることで、転送容量117の他方の端子、すなわちソースフォロワの入力をフローティングにする。

20

#### 【0030】

期間(6)からAGC動作が開始される。この期間では信号/SL1および/Lがハイレベルになるので、センサセル部100の反転アンプが動作して共通出力線にはセンサセル部100で光電変換された信号S1に応じたレベルが現れる。期間(5)までの動作でセンサセル部にはノイズNs+Nmが書き込まれていたので、センサセル部100から出力される信号は反転アンプの作用により $- (S1 + Ns + Nm)$ に、センサセル部100によるノイズNsが加わって $- (S1 + Nt)$ となる。この結果、転送容量117の他方の端子も $- (S1 + Nt)$ だけ変動するので、転送容量117の他方の端子の電位はVGR $- (S1 + Nt)$ となる。これに転送部のノイズNtが加わった信号がノードN6からモニタ部MONに入力されるので、モニタ部MONではノイズの影響のない光信号S1だけをモニタすることができる。期間(6)におけるセンサセル部100の出力変化は、端子122を介してリアルタイムでモニタ部MONにて観測される。モニタ部MONにはゲイン可変増幅部が含まれており、後述するコントラストの検出結果に応じてゲインが可変される。これをオートゲインコントロール(AGC)と呼ぶ。モニタ部MONによるモニタ動作の結果、期間(6)での蓄積動作が終了した時点での、センサセル部101から出力される光信号を-S2とする。

30

#### 【0031】

期間(7)では信号信号FTがハイレベルに保たれており、信号/SL1、/L1および/GRがハイレベルになることで、転送容量117の一方の電極の電位がVRSから $- (S2 + Nt)$ 分だけ変動する。

40

#### 【0032】

期間(8)に信号/SL2\_1および/L1がハイレベルになると、第1メモリセル部101に保持されていたノイズ $2Nt$ に、第1メモリセル部101のノイズNm1が加わって、 $- 2Nt + Nm1$ が転送容量117の一方の端子に与えられる。つまり、転送容量117には、 $- 2Nt + Nm1 - (- (S2 + Nt)) = S2 - Nt + Nm1$ 分の電位変動量が保持されることになる。

#### 【0033】

期間(9)では信号FTがローレベルにある。信号FBがハイレベルの期間に信号

50

/ P S 2 \_ 1 がハイレベルになると、転送部 1 1 3 からは、S 2 - N t + N m 1 にノイズ N t が加わって、S 2 + N m 1 が第 1 メモリセル部 1 0 1 に与えられる。

#### 【 0 0 3 4 】

期間 ( 1 0 ) に信号 F B がローレベルになり、信号 F T がハイレベルになる。この期間に信号 / L および / S L 2 \_ 1 がハイレベルになることで、第 1 メモリセル部 1 0 1 に保持された信号 S 2 + N m 1 が反転アンプによって反転出力され、これに第 1 メモリセル部 1 0 1 のノイズ N m 1 が加わって、- S 2 が転送容量 1 1 7 の一方の端子に与えられる。つまり、結果的にノイズの影響が低減された信号が出力されるものである。この期間に、不図示のシフトレジスタから信号 H が供給されると、信号 - S 2 がバッファアンプに伝達されて、不図示の後段の信号処理回路に出力される。

10

#### 【 0 0 3 5 】

期間 ( 1 1 ) ~ ( 1 4 ) に係る動作は、期間 ( 7 ) ~ ( 1 0 ) の動作を、第 2 メモリセル部 1 0 2 に対して行う。これにより、1 回の蓄積シーケンスでセンサセル部 1 0 0 から、異なる蓄積時間に基づく信号を取得することができる。これにより、高速な焦点検出動作が実現できる。

#### 【 0 0 3 6 】

以上で説明した動作を、焦点検出装置全体の動作と関連付けて、対をなすラインセンサ部 L 1 A と L 1 B とに着目して説明する。

#### 【 0 0 3 7 】

図 1において、ラインセンサ部 L 1 A と L 1 B とは、撮像面のある領域における被写体のデフォーカス量、すなわち、撮像システムのレンズの合焦位置からのずれ量を検出するために用いられる。

20

#### 【 0 0 3 8 】

特許文献 2 に記載された焦点検出装置と同様に、ラインセンサ部を複数の領域に分割し、まずは各ラインセンサ部の中央付近、すなわち端部を含まない領域でデフォーカス量を検出する（小デフォーカス量での検出）。仮にこの条件で所定のコントラストが得られた場合には、各单位画素に複数設けられたメモリセル部のうちの一つを用いて、ノイズ低減のための差分処理を転送部で行って信号を読み出す。

#### 【 0 0 3 9 】

一方、各ラインセンサ部の中央付近では所定のコントラストが得られない、すなわち大デフォーカスの状態では、各ラインセンサ部の全体の領域でデフォーカス量の検出を行い。この場合には、先述した小デフォーカス量での検出時に用いたメモリセル部とは異なるメモリセル部を用いて差分処理を行う。なお、所定のコントラストとは、用途や目的に応じて任意に設定できるものである。

30

#### 【 0 0 4 0 】

これにより、被写体が小デフォーカスの状態であれば、ラインセンサ部の一部の領域のみを読み出すことで高速な動作が可能となり、被写体が大デフォーカスの状態であったとしても、センサセル部を初期化して蓄積動作をやり直す必要がないために、高速な動作が実現できる。

#### 【 0 0 4 1 】

以上で説明したように、本発明で特徴的なのは期間 ( 4 ) において、転送部 1 1 3 から出力されるノイズ  $2 \times N_t$  を、メモリセル部 1 0 1 と 1 0 2 の両者に書き込むことである。つまり、センサセル部 1 0 0 を初期化したことによって生じるリセットノイズをメモリセル部 1 0 1 と 1 0 2 の両者に書き込んでいる。本実施例ではメモリセル部を 2 つ設けた例を説明したが、メモリセル部の数は 3 以上であってもよい。その場合には、期間 ( 7 ) ~ ( 1 0 ) の動作に対応する操作を、追加したメモリセル部に対しても行う。

40

#### 【 0 0 4 2 】

図 3 に示した光電変換装置のレイアウト例を図 6 及び 7 に示す。図 6 では、センサセル部と 2 つのメモリセル部を一つの組として、その組を行列状に配列したものである。転送部ならびにシフトレジスタは、各列に設けられた複数のセンサセル部とメモリセル部に対

50

して共通に設けられている。

**【0043】**

図7は、センサセル部のみが配列された領域と、メモリセル部のみが配列された領域とに分けてレイアウトした場合の図である。このレイアウトにおいても、転送部ならびにシフトレジスタは、各列に設けられた複数のセンサセル部とメモリセル部に対して共通に設けられている。

**【0044】**

(実施例2)

図5に示すタイミングチャートを参照しながら本発明の第2の実施例に係る動作を説明する。本実施例に係る動作は、図2に示した動作と期間(1)～(8)までは同一の動作であるので、ここでは期間(1)～(5)を省略している。10

**【0045】**

本実施例は、ある時刻までに各ラインセンサ部のセンサセル部で蓄積された信号が所望のレベル(以下、蓄積レベルと称す)に達しているか否かを判定するための光電変換装置の動作を説明するものである。

**【0046】**

期間(9')では信号FTがローレベルである。この期間に信号FBおよびPS2\_2が一時的にハイレベルとなると、実施例1の期間(8)で説明した信号S2(t1)-Nm1に転送部のノイズNm1が加わったS2(t1)+Nm1が第2メモリセル部102に書き込まれる。ここでS2(t1)は、時刻t1における信号であることを示すための表記で、実施例1で説明した信号S2と同じものである。20

**【0047】**

期間(10')には信号FBがローレベルになり、信号FTがハイレベルになる。この期間に信号/Lおよび/SL2\_2がハイレベルになると、第2メモリセル部102に保持された信号S2(t1)+Nm1が反転された上でノイズNm2が加わり、結果として-(S2(t1)+Nm1)+Nm2が共通出力線112に出力される。さらに不図示のシフトレジスタから信号Hが与えられると、この信号はバッファアンプ123から不図示の信号処理部へと伝達される。このようにしてバッファアンプ123を介して読み出された時刻t1における信号は、信号処理部にて、蓄積レベルに達しているか否かの判定が行われる。上述の説明から明らかのように、読み出された信号にはノイズNm2-Nm1が重畠されているが、モニタする信号S2のレベルに対して十分に小さいので、ノイズの影響は小さい。30

**【0048】**

時刻t1における信号S2(t1)が、所定の蓄積終了レベルに達していないと判定された場合には、期間(8')～(11')と同様の動作を繰り返して、時刻t2における信号を第2メモリセル部102から出力する。以降、取得された信号が所定の蓄積終了レベルに達するまで、同様の動作を繰り返す。ここで、所定の蓄積終了レベルとは目的に応じて設定しうるものである。

**【0049】**

上述のように、第1メモリセル部101に保持されたノイズ $2 \times Nt$ を用いて、第2メモリセル部102から繰り返し読み出すことで、バッファアンプの後段に設けられた信号処理部を用いて信号レベルのモニタを行うことができる。信号処理部をバッファアンプの後段に設けられるので、信号処理部をラインセンサ部とは異なる半導体基板上に形成することでラインセンサ部のレイアウトが容易になる。40

**【0050】**

(実施例3)

図8を参照しながら本発明に係る第3の実施例を説明する。図8は、本発明に係る光電変換装置を、位相差検出方式の焦点検出装置(以下AFセンサと称す)に適用した場合の構成例を示すブロック図である。

**【0051】**

A F センサ 8 1 1 は、ラインセンサ部 L 1 A、L 2 A、・・・及び L 1 B、L 2 B、・・・が配列されたセンサブロックと、外部インターフェースと A F センサのタイミング信号を生成する機能を持つロジックブロック 8 0 1、アナログ回路ブロック 8 1 0 とを含む。

#### 【 0 0 5 2 】

アナログ回路ブロック 8 1 0 は、A G C 回路 8 0 2 ~ 8 0 5 を備え、ラインセンサ部からの信号のモニタリングや、蓄積時間の制御を行う。アナログ回路ブロック 8 1 0 は更に、光電変換装置で用いられる参照電圧や参照電流を生成する参照電圧電流生成回路 8 0 6、温度計回路 8 0 7 等を含んでなる。

#### 【 0 0 5 3 】

ロジックブロック 8 0 1 はシリアル通信端子 8 1 2 を介して外部とのシリアル通信によって A F センサ 8 1 1 の駆動タイミングを制御する。

#### 【 0 0 5 4 】

本実施例においても、実施例 1 または 2 で説明した光電変換装置を用いることで、高速な焦点検出動作が実現できる。

#### 【 0 0 5 5 】

( 実施例 4 )

図 9 は、本発明の実施例 4 を示す撮像システムの構成例を示すブロック図である。

#### 【 0 0 5 6 】

9 0 1 は後述するレンズのプロテクトを行うバリア、9 0 2 は被写体の光学像を固体撮像装置 9 0 4 に結像するレンズ、9 0 3 はレンズを通過した光量を調整するための絞りである。9 0 4 はレンズで結像された被写体の光学像を画像信号として取得する固体撮像装置である。9 0 5 は先述の各実施例で説明した光電変換装置を用いた A F センサである。

#### 【 0 0 5 7 】

9 0 6 は固体撮像装置 9 0 4 や A F センサ 9 0 5 から出力される信号を処理するアナログ信号処理装置、9 0 7 は信号処理装置 9 0 6 から出力された信号をアナログデジタル変換する A / D 変換器である。9 0 8 は A / D 変換器 9 0 7 より出力された画像データに対して各種の補正や、データを圧縮するデジタル信号処理部である。

#### 【 0 0 5 8 】

9 0 9 は画像データを一時記憶するためのメモリ部、9 1 0 は外部コンピュータなどと通信するための外部 I / F 回路、9 1 1 はデジタル信号処理部 9 0 8 などに各種タイミング信号を出力するタイミング発生部である。9 1 2 は各種演算とカメラ全体を制御する全体制御・演算部、9 1 3 は記録媒体制御 I / F 部、9 1 4 は取得した画像データを記録、又は読み出しを行うための半導体メモリなどの着脱可能な記録媒体、9 1 5 は外部コンピュータである。

#### 【 0 0 5 9 】

次に、上記の撮像システムの撮影時の動作について説明する。

#### 【 0 0 6 0 】

バリア 9 0 1 がオープンされ、A F センサ 9 0 5 から出力された信号をもとに、全体制御・演算部 9 1 2 は前記したような位相差検出により被写体までの距離を演算する。その後、演算結果に基づいてレンズ 9 0 2 を駆動し、再び合焦しているか否かを判断し、合焦していないと判断したときには、再びレンズ 9 0 2 を駆動するオートフォーカス制御を行う。次いで、合焦が確認された後に固体撮像装置 9 0 4 による蓄積動作が始まる。固体撮像装置 9 0 4 の蓄積動作が終了すると、固体撮像装置 9 0 4 から出力された画像信号は A / D 変換器 9 0 7 でアナログデジタル変換され、デジタル信号処理部 9 0 8 を通り全体制御・演算によりメモリ部 9 0 9 に書き込まれる。その後、メモリ部 9 0 9 に蓄積されたデータは全体制御・演算部 9 1 2 の制御により記録媒体制御 I / F 部 9 1 0 を介して記録媒体 9 1 4 に記録される。また、外部 I / F 部 9 1 0 を通り直接コンピュータなどに入力してもよい。

#### 【 符号の説明 】

10

20

30

40

50

## 【0061】

- 100 センサセル部

- 101 第1メモリセル部

- 102 第2メモリセル部

- 103 フォトダイオード( P D )

- 104 メモリ容量

- 105 メモリ容量

- 113 転送部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 04 N 5 / 357

H 04 N 5 / 232