(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4567719号

(P4567719)

(45) 発行日 平成22年10月20日(2010.10.20)

(24) 登録日 平成22年8月13日(2010.8.13)

(51) Int.Cl.

H02M 3/07 (2006.01)

F 1

H02M 3/07

請求項の数 18 外国語出願 (全 20 頁)

(21) 出願番号 特願2007-268417 (P2007-268417)

(22) 出願日 平成19年10月15日 (2007.10.15)

(65) 公開番号 特開2009-89578 (P2009-89578A)

(43) 公開日 平成21年4月23日 (2009.4.23)

審査請求日 平成19年10月15日 (2007.10.15)

(31) 優先権主張番号 11/862,790

(32) 優先日 平成19年9月27日 (2007.9.27)

(33) 優先権主張国 米国(US)

(73) 特許権者 501447890

群聯電子股▲ふん▼有限公司

台灣新竹縣竹東鎮中興路四段669號2樓

(74) 代理人 100104156

弁理士 龍華 明裕

(72) 発明者 ユウートン リン

台灣新竹縣竹北市成功三路162號5樓

審査官 塩治 雅也

(56) 参考文献 特開2005-261185 (JP, A)

特開平06-303772 (JP, A)

最終頁に続く

(54) 【発明の名称】デジタルPWMを備える変換回路、その方法、および、付随するコントローラ

## (57) 【特許請求の範囲】

## 【請求項1】

変換回路であって、

一の入力電圧を受信し、かつ、一の制御クロック信号に基づき動作を切り替えることにより、前記入力電圧の大きさに従う一の出力電圧を出力する一の電圧変換ユニットと、

前記出力電圧と一の基準電圧とを比較することにより、一のパワーグッドパルス信号を生成する一の比較回路であって、前記パワーグッドパルス信号は、前記出力電圧が前記基準電圧より大きい場合に一の第1の論理状態になる比較回路と、

前記パワーグッドパルス信号と一のソースクロック信号とを受信することにより、前記制御クロック信号を生成する一のパルス幅周波数変調回路であって、前記ソースクロック信号のパルス幅は、前記パワーグッドパルス信号における前記第1の論理状態の維持時間によって予め定められた値ずつ増大或いは減少し、前記ソースクロック信号の周波数も前記パワーグッドパルス信号が前記第1の論理状態にある期間に変化し、前記パルス幅周波数が変調されたソースクロック信号は、前記制御クロック信号として出力されるパルス幅周波数変調回路と、

を含む変換回路。

## 【請求項2】

前記パルス幅周波数変調回路は、複数の直列接続遅延ユニットを含む一のパルス幅変調ユニットを含み、前記直列接続遅延ユニットの入力は、ソースクロック信号に結合され、該ソースクロック信号のパルス幅は、前記ソースクロック信号が通過する前記遅延ユニッ

10

20

トの数だけ前記予め定められた値ずつ増大或いは減少し、前記パルス幅変調ユニットからのパルス変調信号が生成される、請求項1に記載の変換回路。

**【請求項3】**

前記パルス幅変調ユニットは、複数のスイッチをさらに含み、該スイッチのそれぞれは、制御されることによって一の第1の論理ゲートを介し、前記遅延ユニットのそれぞれの出力と、前記パルス幅変調ユニットの前記出力との間に配置され、それによって異なるパルス幅を有する前記パルス変調された信号が生成される、請求項2に記載の変換回路。

**【請求項4】**

前記パルス幅周波数変調回路は、複数の制御信号を提供することにより、スイッチのオンまたはオフを制御する一のシフト回路を含む、請求項3に記載の変換回路。

10

**【請求項5】**

前記シフト回路は、一のトリガクロックパルスおよび一の指向性クロックパルスを受信し、前記シフト回路は、トリガされることにより前記トリガクロックパルスに基づき動作し、前記制御信号は、前記指向性クロックパルスに従いシフトされ、それによって前記パルス変調される信号のパルス幅が変化する、請求項4に記載の変換回路。

**【請求項6】**

前記指向性クロックパルスは、前記パルス変調された信号の前記パルス幅を前記予め定められた値ずつ増大すべくアクティブにされ、前記指向性クロックパルスは、前記パルス変調された信号の前記パルス幅を前記予め定められた値ずつ縮小すべく非アクティブにされ、前記パルス変調された信号の前記パルス幅は、一の予め決められた範囲を伴い変化する、請求項5に記載の変換回路。

20

**【請求項7】**

前記予め定められた値は、2つの隣接する前記遅延ユニットの間の遅延時間に対応する一のパルス幅である、請求項6に記載の変換回路。

**【請求項8】**

前記パルス幅周波数変調回路は、前記パワーグッドパルス信号が前記第1の論理状態のままであるときの回数をカウントし、かつ、該回数が一の予め決められた値に達したときはいつでも前記指向性クロックパルスおよび前記トリガクロックパルスを出力する一の計数回路を含み、該計数回路からの前記指向性クロックパルスは、アクティブにされる、請求項6に記載の変換回路。

30

**【請求項9】**

前記入力電圧は、前記基準電圧と比較され、前記入力電圧が前記基準電圧より大きい場合は、前記電圧変換ユニットが一の遅降レギュレータとして動作することを示し、前記変換回路における動作を切り替える複数のスイッチの一部は、前記出力電圧を上昇させることを停止する、請求項1に記載の変換回路。

**【請求項10】**

前記電圧変換ユニットが前記遅降レギュレータとして動作するとき、前記シフト回路により提供される前記制御信号の1つは、前記制御クロック信号が一のフルクロック幅モードで動作するかどうかを判断するのに用いられ、動作する場合、前記停止しているスイッチの一部は、再び動作するよう用いられる、請求項9に記載の変換回路。

40

**【請求項11】**

前記変換回路が始動するたびに、前記出力電圧が検出され、前記ソースクロック信号の前記第1のクロックの前記パルス幅周波数が変調されたソースクロック信号は、最小のパルス幅に調整される、請求項1に記載の変換回路。

**【請求項12】**

電圧変換方法であって、

一の入力電圧を受信し、かつ、一の制御クロック信号に基づき動作を切り替えることにより、前記入力電圧の大きさに従う一の出力電圧を出力する段階と、

前記出力電圧と、一の基準電圧とを比較することにより、一のパワーグッドパルス信号を生成する段階であって、前記パワーグッドパルス信号は、前記出力電圧が前記基準電圧

50

より大きい場合、一の第1の論理状態にある段階と、

前記パワーグッドパルス信号と一のソースクロック信号とを受信することにより、前記制御クロック信号を生成する段階であって、前記ソースクロック信号のパルス幅は、前記パワーグッドパルス信号における前記第1の論理状態の維持時間によって予め定められた値ずつ増大或いは減少し、前記ソースクロック信号の周波数も、前記パワーグッドパルス信号が前記第1の論理状態のままである期間に変化し、前記パルス幅周波数が変調されたソースクロック信号は、前記制御クロック信号として出力される段階と、

を含む、電圧変換方法。

#### 【請求項13】

前記パワーグッドパルス信号が前記第1の論理状態のままである前記期間、前記パワーグッドパルス信号が前記第1の論理状態のままであるときの回数を一の計数クロックに基づきカウントすることにより、前記回数が一の予め決められた回数に達したときはいつでも、前記ソースクロック信号の前記パルス幅は前記パワーグッドパルス信号における前記第1の論理状態の維持時間によって予め定められた値ずつ増大或いは減少し、前記ソースクロック信号の前記周波数も変更される、請求項12に記載の電圧変換方法。

10

#### 【請求項14】

前記入力電圧と前記基準電圧とを比較する段階をさらに含み、前記入力電圧が前記基準電圧より大きい場合は、前記電圧変換は遅降調整の働きをし、前記出力電圧の上昇は停止する、請求項12に記載の電圧変換方法。

#### 【請求項15】

前記電圧変換が開始されるたびに、前記ソースクロック信号の前記第1のクロックに対応する前記ソースクロック信号の前記パルス幅は、最小のパルス幅に調整される、請求項12に記載の電圧変換方法。

20

#### 【請求項16】

一のメモリ素子と一のホスト電力を提供する一のホストとの間に接続されるよう適合可能なコントローラであって、前記メモリ素子の動作に適合する一の電力に前記ホスト電力を調整する一の直流 - 直流電力マネージャを含み、

前記直流 - 直流電力マネージャは、

前記ホスト電力を受信し、かつ、一の制御クロック信号に基づき動作を切り替えることにより、前記ホスト電力の大きさに従う一の出力電圧を出力する一の電圧変換ユニットと、

30

前記出力電圧と一の基準電圧とを比較することにより、一のパワーグッドパルス信号を生成する一の比較回路であって、前記出力電圧が前記基準電圧より大きい場合、前記パワーグッドパルス信号は、一の第1の論理状態にある比較回路と、

前記パワーグッドパルス信号と一のソースクロック信号とを受信することにより、前記制御クロック信号を生成する一のパルス幅周波数変調回路であって、前記パワーグッドパルス信号が前記第1の論理状態のままである期間、前記ソースクロック信号のパルス幅は、前記パワーグッドパルス信号における前記第1の論理状態の維持時間によって予め定められた値ずつ増大或いは減少し、前記ソースクロック信号の周波数も変更され、前記パルス幅周波数が変調されたソースクロック信号は、前記制御クロック信号として出力されるパルス幅周波数変調回路と、を含むコントローラ。

40

#### 【請求項17】

前記パルス幅周波数変調回路は、複数の直列接続遅延ユニットを備える一のパルス幅変調ユニットを含み、前記直列接続遅延ユニットの入力は、前記ソースクロック信号に結合され、前記ソースクロック信号のパルス幅は、前記予め定められた値ずつ前記ソースクロック信号が通過する前記遅延ユニットの数だけ徐々に変更され、前記パルス幅変調ユニットから一のパルス変調された信号が生成される、請求項16に記載のコントローラ。

#### 【請求項18】

前記コントローラは、一のフラッシュメモリコントローラであり、前記メモリ素子は、一のフラッシュメモリ素子である、請求項16に記載のコントローラ。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、変換回路に関する。より詳しくは、本発明は、パルス幅周波数変調による変換回路、その方法、および、付随するコントローラに関する。

**【背景技術】****【0002】**

直流 - 直流コンバータのようなコンバータは、直流 (DC) 入力電圧を受け、かつ、DC 出力電圧を生成するデバイスである。通常、生成された出力は、入力とは異なる電圧レベルである。また、直流 - 直流コンバータは、ノイズ分離、パワーバス調整などを提供するため 10 に用いられる。

**【0003】**

主な変換回路設計は 3 つある。これらの変換回路は、所定の入力電圧に対する出力電圧の大きさおよび極性を決定する。第 1 のコンバータは、平均出力電圧が入力電圧より小さい順方向コンバータであるバックレギュレータである。第 2 のコンバータは、平均出力電圧が入力電圧より大きい蓄積エネルギーコンバータであるブーストレギュレータである。最後に、第 3 のコンバータは、出力電圧が入力電圧より小さいかまたは大きい蓄積エネルギーコンバータであるバックブーストレギュレータである。

**【0004】**

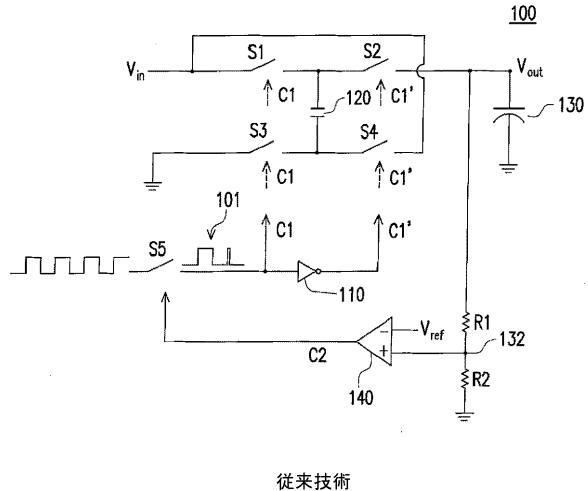

図 1 は、出力電圧のレベルを制御する従来のバックブースト回路の例を示す。図 1 のバックブースト回路 100 の場合、ノード 132 における電圧レベルと予め決められた基準電圧  $V_{ref}$  の電圧レベルとを比較するためにコンパレータ 140 が用いられる。図に示すように、ノード 132 の電圧レベルは、レジスタ R1 および R2 から構成される分圧器を介した出力電圧  $V_{out}$  によりもたらされる。ノード 132 の電圧レベルが基準電圧  $V_{ref}$  の電圧レベルに達すると、コンパレータ 140 の出力信号 C2 がスイッチ S5 をオフにするので、クロック信号 C1 の提供が停止する。これに対し、ノード 132 の電圧レベルが基準電圧  $V_{ref}$  より低い場合、コンパレータ 140 の出力信号 C2 はスイッチ S5 をオンにするので、クロック信号 C1 が提供されてバックブースト回路 100 は動作可能になる。したがって、出力電圧  $V_{out}$  の電位が十分高い場合、クロック信号 C1 の提供が停止でき、不必要的電力消費は減少するであろう。出力電圧  $V_{out}$  は、 $V_{in} * (R1 + R2) / R2$  と等しい。出力電圧  $V_{out}$  が望ましい電圧レベルに上下する場合、バックブースト回路 100 の出力端末には依然として負荷が存在するので、スイッチ S5 は頻繁にオンにされるかまたはオフにされることになる。スイッチ S5 のこのような切り替え動作は、短いパルス時間幅でオンにされる。短いパルス時間幅は、 $V_{out}$  で高周波雑音を生成し、この現象は、図 1 の参考番号 101 として示される。したがって、出力電圧  $V_{out}$  の信号品質は影響を受け、結果的に出力電圧  $V_{out}$  にノイズが存在するようになる。

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

パルス幅周波数変調 (Pulse Width Modulation) 機構を備える変換回路がここに提供される。パルス幅周波数変調機構において、動作のために周波数変調ユニットに印加されるクロックのパルス幅は、例えば、ステップサイズ機構により、徐々に変化するよう変調される。すなわち、印加されるクロックのパルス幅および周波数の増減は、変換回路の出力特性に関連して制御される。

**【0006】**

一実施形態では、本発明の変換回路は、電圧変換ユニット、比較回路、および、パルス幅周波数変調回路を含む。電圧変換ユニットは、入力電圧を受信し、制御クロック信号に基づき動作を切り替えることにより、入力電圧の大きさに従う出力電圧を出力する。比較回路は、出力電圧と基準電圧とを比較することによりパワーグッドパルス信号を生成し、出

10

20

30

40

50

力電圧が基準電圧より大きい場合、パワーゲッドパルス信号は、第1の論理状態にある。パルス幅周波数変調回路は、パワーゲッドパルス信号とソースクロック信号とを受信することにより、制御されたクロック信号を提供する。パワーゲッドパルス信号が第1の論理状態にある期間、ソースクロック信号のパルス幅は、ステップサイズ機構により徐々に変化し、ソースクロック信号の周波数も変化し、パルス幅周波数が変調されたソースクロック信号は、制御クロック信号として出力される。

#### 【0007】

一実施形態では、パルス幅周波数変調回路は、複数の直列接続遅延ユニットを含むパルス幅変調ユニットを備え、直列接続遅延ユニットの入力は、ソースクロック信号に結合される。ソースクロック信号のパルス幅は、ステップサイズ機構により、ソースクロック信号が通過する遅延ユニットの数だけ徐々に変更され、パルス幅変調ユニットからパルス変調された信号が生成される。上記パルス幅変調ユニットは、複数のスイッチをさらに備え、複数のスイッチのそれぞれは、制御されることにより遅延ユニットのそれぞれの出力と、パルス幅変調ユニットの出力との間に配置される。それによって異なるパルス幅を有するパルス変調信号が生成される。

10

#### 【0008】

一実施形態では、パルス幅周波数変調回路は、スイッチをオンまたはオフにする制御に複数の制御信号を提供する双方向シフト回路を含む。

#### 【0009】

上記双方向シフト回路は、トリガクロックパルスおよび双方向クロックパルスを受信し、双方向シフト回路は、トリガクロックパルスに基づき動作するようトリガされ、制御信号は、双方向クロックパルスに従いシフトされ、それによって、パルス変調された信号のパルス幅が変更される。

20

#### 【0010】

一実施形態において、パルス幅周波数変調回路は、パワーゲッドパルス信号が第1の論理状態のままであるときの回数をカウントし、かつ、回数が予め決められた値に達したときはいつでも指向性クロックパルスおよびトリガクロックパルスを出力する計数回路を含み、計数回路からの指向性クロックパルスはアクティブにされる。本発明は、メモリ素子とホスト電力を提供するホストとの間で接続されるよう適合されるコントローラを含む。コントローラは、ホスト電力をメモリ素子の動作に適合できる電力に調整する直流 - 直流電力マネージャを含む。直流 - 直流電力マネージャは、パルス幅周波数変調（P W F M）機構を備える前述の変換回路を含む。

30

#### 【0011】

本発明の上記および他の目的、特徴、および、利点を理解できるようにすべく、好適な実施形態が添付の図面と共に以下に詳しく説明される。

#### 【発明を実施するための最良の形態】

#### 【0012】

例えば、バック回路、ブースト回路、または、図2のバックブースト回路などの従来の直流 - 直流電圧コンバータにおけるノイズ問題を防止すべく、周波数変調機構が設けられ、バックブースト回路の出力電圧が予め決められた値より大きい場合には、クロック信号の提供を停止するのではなく制御する。

40

#### 【0013】

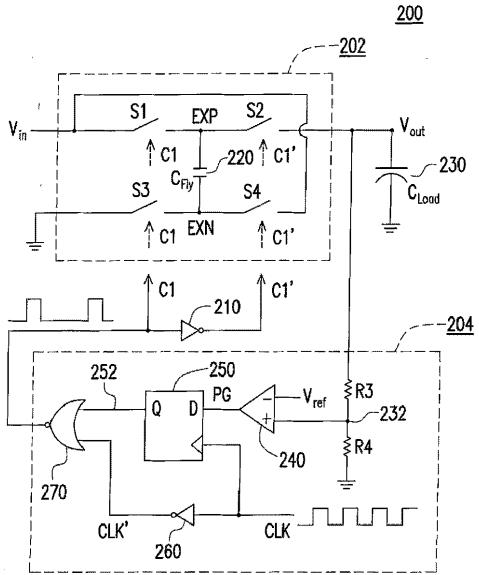

例えば、周波数変調機構を備えるバックブースト回路では、出力電圧は、制御クロック信号の周波数を変更することにより調整できる。例えば、図2に示すように、バックブーストユニット202および周波数変調ユニット204を含むバックブースト回路200は、制御クロック信号の周波数を制御する回路を設けることにより、ここに導入される。バックブーストユニット202では、クロック信号C1がスイッチS1およびS3を制御し、インバータ210によりクロック信号C1の位相を反転させることにより得られるコンプリメンタリ信号C1'がスイッチS2およびS4を制御する。クロック信号C1が論理レベルHであるとき、スイッチS1およびS3は、通電オン（ON）にされ、スイッチS

50

2 および S 4 は、通電オフ (OFF) にされる。切り替えフライングコンデンサ 220 の 1 つの端末に接続されるノード EXP における電位は、コンデンサ 220 を充電することにより入力電圧  $V_{in}$  まで上昇する。クロック信号 C1 が論理レベル L である場合、スイッチ S1 および S3 はオフにされ、スイッチ S2 および S4 は、オンにされる。このとき、コンデンサ 220 の他の端末に接続されるノード EXP は、スイッチ S4 を介し入力電圧  $V_{in}$  に結合され、コンデンサ 220 の 2 つの端末の間の電位差も入力電圧  $V_{in}$  のままである。したがって、ノード EXP の電位は、入力電圧  $V_{in}$  の 2 倍に上昇することが予測され、スイッチ S2 がオンにされ、負荷コンデンサ 230 が予測される出力電圧  $V_{out}$  に充電された後、出力電圧  $V_{out}$  は入力電圧  $V_{in}$  の 2 倍になる。

## 【0014】

10

出力電圧  $V_{out}$  の望ましいレベルが入力電圧の 2 倍でない場合には、出力電圧  $V_{out}$  のレベルを制御すべく基準電圧  $V_{ref}$  が提供される。周波数変調ユニット 204 は、クロック信号 C1 の周波数を制御するために用いられ、それによって、出力電圧  $V_{out}$  の電位の上昇率が制御される。一実施形態における周波数変調ユニット 204 は、例えば、コンパレータ 240、D タイプフリップフロップ 250、インバータ 260、および、NOR ゲート 270 を含む。

## 【0015】

図 2 に示すように、コンパレータ 240 の正入力端子は、ノード 232 に結合され、コンパレータ 240 の負端子は、予め決められた基準電圧  $V_{ref}$  に結合される。レジスタ R3 および R4 により構成される分圧器を介し出力電圧  $V_{out}$  に結合されるノード 232 の電圧レベルが基準電圧  $V_{ref}$  に達すると、コンパレータ 240 から出力されるクロックパルス PG (パワーグッド信号) は論理レベル L になり、ノード 232 の電圧レベルが基準電圧  $V_{ref}$  より低くなると、コンパレータ 240 からの信号 PG は、論理レベル H になる。

20

## 【0016】

クロックパルス PG に基づき、バックブーストユニット 202 に印加されるクロック信号 C1 の周波数は、しかるべき変化する。クロック信号 CLK は、周波数変調ユニット 204 の動作クロックとして提供される。クロック信号 CLK は、D タイプフリップフロップ 250 の動作を制御すべく提供される。すなわち、クロック信号 CLK の立下りエッジまたは立上りエッジが D タイプフリップフロップ 250 をトリガすることにより、(入力端子 D における) 入力信号が出力端子 Q に伝送される。論理演算は、NOR ゲート 270 により、D フリップフロップ 250 の出力信号 252 (出力端子 Q における信号) と、クロック信号 CLK をインバータ 260 により反転させた後に得られるコンプリメンタリクロック信号 CLK' とに実行され、バックブーストユニット 202 におけるスイッチを制御する周波数変調信号 C1 が得られる。

30

## 【0017】

コンパレータ 240 が PG 信号を出力するので、出力電圧  $V_{out}$  は、制御機構の動作期間において過充電されている可能性がある。出力電圧  $V_{out}$  の振幅が高くなり過ぎないようにすべく、コンデンサ 230 の容量は、コンデンサ 220 の容量より通常かなり大きい。したがって、出力電圧  $V_{out}$  の電位が入力電圧  $V_{in}$  の 2 倍になると、出力電圧  $V_{out}$  のレベルを低下させるべく、コンデンサ 230 の分圧効果が用いられる。コンデンサ 220 の容量は、 $C_{fly}$  であり、コンデンサ 230 の容量は  $C_{load}$  であり、初期出力電圧は  $V_{out1}$  であり、出力電圧  $V_{out2}$  は、コンデンサ 220 および 230 の分圧効果後の電圧であると仮定する。低下した出力電圧  $V_{out2}$  は、 $V_{out2} = (V_{out1} * C_{load} + 2V_{in} * C_{fly}) / (C_{load} + C_{fly})$  と等しい。

40

## 【0018】

しかしながら、バックブースト回路 200 が縮小デバイス、例えば、非常に小さなサイズ要件を満たすマイクロメモリカードに適用される場合、バックブースト回路 200 の厚みは制限され、それは、コンデンサ 230 の最大有効容量も制限されることを意味する。

50

この制限によりバックブースト回路 230 は、この分野でますます一般的になってきた縮小デバイスで用いられるのが難しくなる。

#### 【0019】

本願明細書において、パルス幅周波数変調機構を備える電圧変換回路が提供される。図 3A に示される例を挙げると、バックブースト回路 200 の出力端末では大容量の負荷コンデンサ 230 は必要ないので、バックブースト回路 200 は、縮小された小型デバイスを含む様々な電気デバイスに適用できる。パルス幅周波数変調機構では、制御クロック信号は、周波数だけではなくパルス幅によっても制御される。

#### 【0020】

本発明で提供されるパルス幅変調機構は、動作のため周波数変調ユニットに印加されるクロックのパルス幅を徐々に増減させている。すなわち、印加されるクロックのパルス幅の増減は、バックブースト回路の出力の電圧レベルに基づき制御される。

10

#### 【0021】

一実施形態では、パルス幅変調機構は、出力電圧と予め決められた基準電圧との比較に基づき PG 状態の時間幅をカウントすることにより実施される。PG 状態がカウント後、例えば 5 回以上論理レベル H のままである場合、印加されるクロックのパルス幅は、バックブースト回路の励起電荷量を減少させるべく、予め決められた値を伴い減少する。再びカウントした後にも PG 状態が 5 回以上論理レベル H のままである場合、バックブースト回路の出力電圧レベルは、依然として望ましい値より高過ぎ、印加されるクロックのパルス幅は、出力の励起電荷量を減少させるべく、同じ予め決められた値を伴い減少する。PG 状態がその位相を変化させ、カウント後 5 回以上論理レベル L のままである場合、印加されるクロックのパルス幅は、同じ予め決められた値分増大する。

20

#### 【0022】

印加されるクロックのパルス幅を増減する予め決められた値は、バックブースト回路の出力における負荷コンデンサの容量に依存する。クロックのパルス幅を変更するためのステップサイズ変動のような機構を用いることは、パルス幅を変更する周波数がそれほど高くない場合、バックブースト回路の出力電圧がクリーンであり、すなわち、バックブースト回路の出力におけるノイズは著しく減少するという根拠になる。

#### 【0023】

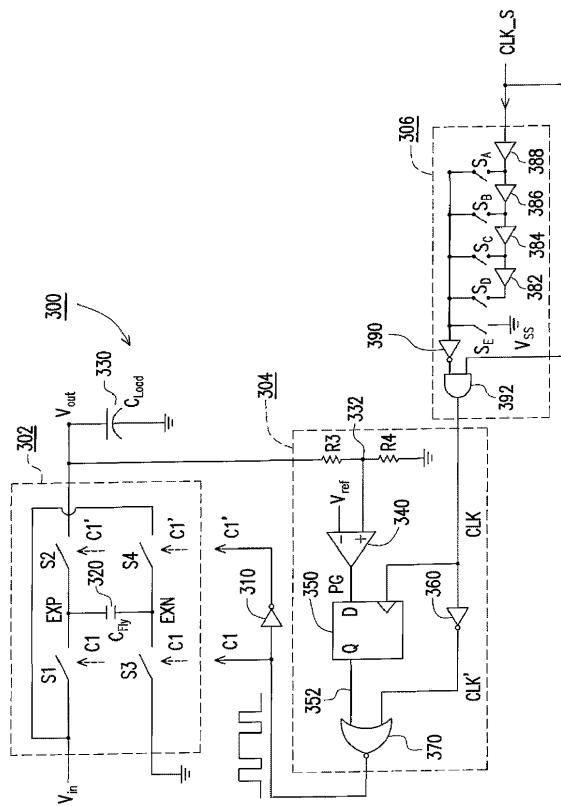

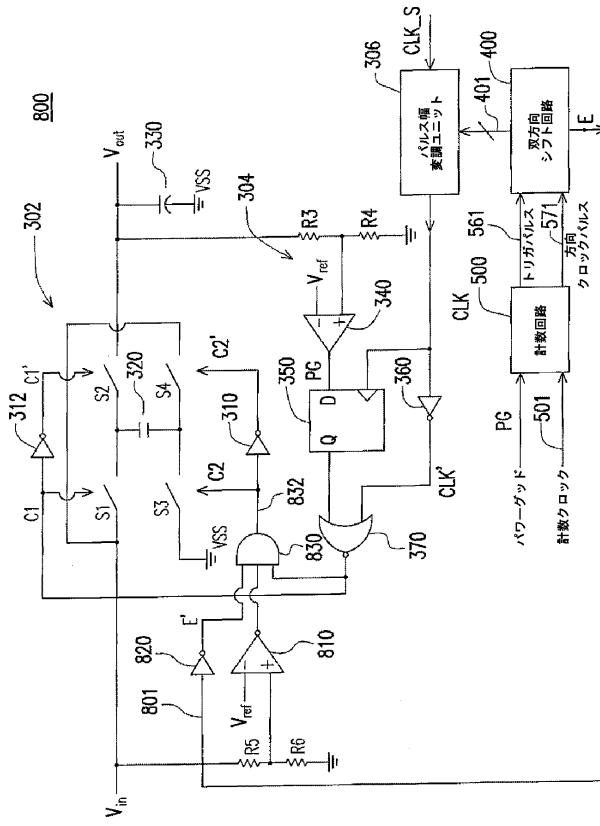

図 3A を参照されたい。図 3A は、本発明の一実施形態のバックブースト回路 300 を示す。バックブーストユニット 302 と周波数変調ユニット 304 とを含むバックブースト回路 300 は、制御クロック信号の周波数を制御する回路を設けることにより、ここに導入される。バックブーストユニット 302 では、クロック信号 C1 は、スイッチ S1 および S3 を制御し、クロック信号 C1 の位相をインバータ 310 で反転されることにより得られるコンプリメンタリ信号 C1' は、スイッチ S2 および S4 を制御する。クロック信号 C1 が論理レベル H である場合、スイッチ S1 および S3 は、通電オン (ON) にされ、スイッチ S2 および S4 は、通電オフ (OFF) にされる。切り替えフライングコンデンサ 320 の一方の端末に接続されるノード EXP における電位は、コンデンサ 320 を充電することにより入力電圧  $V_{in}$  まで上昇する。クロック信号 C1 が論理レベル L である場合、スイッチ S1 および S3 はオフにされ、スイッチ S2 および S4 は、オンにされる。このとき、コンデンサ 320 の他方の端末に接続されるノード EXP は、スイッチ S4 を介し入力電圧  $V_{in}$  に結合され、コンデンサ 320 の 2 つの端末の間の電位差も入力電圧  $V_{in}$  のままである。したがって、ノード EXP の電位は、入力電圧  $V_{in}$  の 2 倍に上昇することが予測され、スイッチ S2 がオンにされ、負荷コンデンサ 330 が予測される出力電圧  $V_{out}$  に充電された後、出力電圧  $V_{out}$  は入力電圧  $V_{in}$  の 2 倍になる。

30

#### 【0024】

出力電圧  $V_{out}$  の望ましいレベルが入力電圧の 2 倍でない場合には、出力電圧  $V_{out}$  のレベルを制御すべく基準電圧  $V_{ref}$  が提供される。周波数変調ユニット 304 は、クロック信号 C1 の周波数を制御するために用いられ、それによって、出力電圧  $V_{out}$

40

50

の電位の上昇率が制御される。一実施形態における周波数変調ユニット304は、例えば、コンパレータ340、Dタイプフリップフロップ350、インバータ360、および、NORゲート37を含む。

#### 【0025】

図3Aに示すように、コンパレータ340の正入力端子は、ノード332に結合され、コンパレータ340の負端子は、予め決められた基準電圧 $V_{ref}$ に結合される。例えばレジスタR3およびR4により構成される分圧器を介し出力電圧 $V_{out}$ に結合されるノード332の電圧レベルが基準電圧 $V_{ref}$ に達すると、コンパレータ340から出力されるクロックパルスPG(パワーグッド信号)は論理レベルLになり、ノード332の電圧レベルが基準電圧 $V_{ref}$ より低くなると、コンパレータ340からの信号PGは、論理レベルHになる。10

#### 【0026】

クロックパルスPGに基づき、バックブーストユニット302に印加されるクロック信号CLKの周波数は、しかるべき変化するであろう。クロック信号CLKは、周波数変調ユニット304の動作クロックとして提供される。クロック信号CLKは、Dタイプフリップフロップ350の動作を制御すべく提供される。すなわち、クロック信号CLKの立ち下りエッジまたは立ち上りエッジがDタイプフリップフロップ350をトリガすることにより、(入力端子Dにおける)入力信号が出力端子Qに伝送される。NORゲート370により、Dフリップフロップ350の出力信号352(出力端子Qにおける信号)と、クロック信号CLKをインバータ360により反転させた後に得られるコンプリメンタリクロック信号CLK'とに論理演算が実行され、バックブーストユニット302におけるスイッチを制御する周波数変調信号C1が得られる。20

#### 【0027】

コンパレータ340がPG信号を出力するので、出力電圧 $V_{out}$ は、制御機構の動作期間において過充電されている可能性がある。出力電圧 $V_{out}$ の振幅が高くなり過ぎないようにすべく、コンデンサ330の容量は、コンデンサ320の容量より通常かなり大きい。したがって、出力電圧 $V_{out}$ の電位が入力電圧 $V_{in}$ の2倍になると、出力電圧 $V_{out}$ のレベルを低下させるべく、コンデンサ330の分圧効果が用いられる。

#### 【0028】

バックブースト回路300は、パルス幅変調ユニット306をさらに含む。動作クロックとして周波数変調ユニット304に提供されるクロック信号CLKは、パルス幅変調ユニット306により異なるパルス幅で変調される。一実施形態では、パルス幅変調ユニット306は、複数の直列接続遅延素子、複数のスイッチ、インバータ390および論理ANDゲート392を含む。説明のため、例えば4つの直列接続遅延素子382、384、386、および、388と、5つのスイッチ $S_A$ 、 $S_B$ 、 $S_C$ 、 $S_D$ および $S_E$ が本願明細書中に導入されるが、これに限定されない。遅延素子388の入力は、クロック信号CLK\_Sに結合され、遅延素子388の出力は、遅延素子386の入力に結合される。これら遅延素子は、直列に接続され、それら遅延素子の出力は、スイッチ $S_A$ 、 $S_B$ 、 $S_C$ および $S_D$ を介しインバータ390の入力にそれぞれ結合される。インバータ390の入力は、スイッチ $S_E$ を介し電圧 $V_{ss}$ に結合される。インバータ390の出力は、ANDゲート392の入力の一方に結合される。ANDゲート392の入力のもう一方は、クロック信号CLK\_Sに結合される。3040

#### 【0029】

5つのスイッチ $S_A$ 、 $S_B$ 、 $S_C$ 、 $S_D$ および $S_E$ は、周波数変調ユニット304に提供されるクロック信号CLKのパルス幅を変調するよう制御される。

#### 【0030】

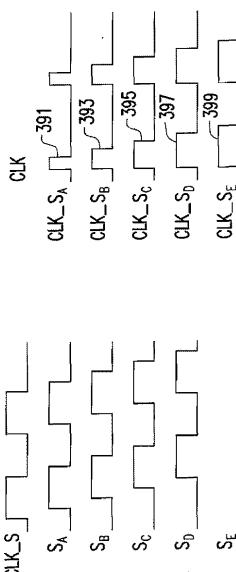

図3Bを参照されたい。図3Bは、スイッチ $S_A$ 、 $S_B$ 、 $S_C$ 、 $S_D$ および $S_E$ のオンまたはオフ状態により制御される異なるパルス幅を有するクロック信号CLKのタイミングチャートを示す。スイッチ $S_D$ がインバータ390にソースクロック信号CLK\_Sを導くようオンにされ、他のスイッチ $S_A$ 、 $S_B$ 、 $S_C$ および $S_E$ がオフにされる場合、ソ50

ースクロック信号 C\_LK\_S は、それら直列に接続される遅延素子 382、384、386 および 388 により遅延され、インバータ 390 を介し AND ゲート 392 の入力に出力される。パルス幅変調ユニット 306 からのクロック信号 C\_LK は、図 3B に示すような "C\_LK\_S\_D" として指定されるクロック信号 397 と同じくらいのパルス幅で変調される。同様に、スイッチ S\_c がソースクロック信号 C\_LK\_S をインバータ 390 に導くようオンにされ、他のスイッチ S\_A、S\_B、S\_D および S\_E がオフにされる場合、ソースクロック信号 C\_LK\_S は、それら直列接続された遅延素子 384、386 および 388 により遅延され、クロック信号 C\_LK は、図 3B に示すような "C\_LK\_S\_c" として指定されるクロック信号 395 と同じくらいのパルス幅で変調される。スイッチ S\_B がオンにされ、他のスイッチ S\_A、S\_C、S\_D および S\_E がオフにされる場合、ソースクロック信号 C\_LK\_S は、それら直列接続された遅延素子 386 および 388 により遅延され、クロック信号 C\_LK は、図 3B に示すような "C\_LK\_S\_B" として指定されるクロック信号 393 と同じくらいのパルス幅で変調される。スイッチ S\_A がオンにされ、他のスイッチ S\_B、S\_C、S\_D および S\_E がオフにされる場合、ソースクロック信号 C\_LK\_S は、遅延素子 388 により遅延され、クロック信号 C\_LK は、図 3B に示すような "C\_LK\_S\_A" として指定されるクロック信号 391 と同じくらいのパルス幅で変調される。スイッチ S\_E がオンにされ、他のスイッチ S\_A、S\_B、S\_C、および S\_D がオフにされる場合、クロック信号 C\_LK は、図 3B に示すような "C\_LK\_S\_E" として指定されるクロック信号 399 と同じくらいの、ソースクロック信号 C\_LK\_S のフルクロックパルス幅で変調される。

10

20

### 【0031】

パルス幅が大きな値で急激に頻繁に変化する場合のノイズ問題を避けるべく、本発明のバックブースト回路 300 は、ステップサイズ変動により実現可能な一実施形態におけるソースクロックのパルス幅を連続的に増減する機構を提供する。パルス幅の総変動は、直列接続遅延素子の段数に依存する。一実施形態では、「ステップサイズ」は、上述のような 2 つの隣接する遅延素子の間の遅延時間に対応するパルス幅である。遅延時間は、バックブースト回路の出力における負荷コンデンサの容量に依存する。図 3B に示される例を挙げると、ソースクロック信号 C\_LK\_S のパルス幅は、クロック信号 391 からクロック信号 399 まで順次変更される。ソースクロック信号 C\_LK\_S は、クロック信号 391 からクロック信号 393、395、397 および 399 まで順次シフトされるか、または、クロック信号 399 から、クロック信号 397、395、393 および 391 まで順次シフトされる。図 2 のバックブースト回路 200 において、コンデンサ 220 の容量が C\_F1y、コンデンサ 230 の容量が C\_Load の場合、初期出力電圧は V\_out1 であり、また、出力電圧 V\_out2 は、コンデンサ 220 および 230 の分圧効果後の電圧である。低下した出力電圧 V\_out2 は、 $V_{out2} = (V_{out1} * C_{load} + 2 * V_{in} * C_{F1y}) / (C_{load} + C_{F1y})$  と等しい。しかしながら、図 3 のバックブースト回路 300 において、ソースクロックのパルス幅を連続的に増減させる機構が設けられる。コンデンサ 320 の容量が C\_F1y であり、コンデンサ 330 の容量が C\_Load であると仮定すると、初期出力電圧は V\_out1 であり、出力電圧 V\_out2 は、コンデンサ 320 および 330 の分圧効果後の電圧である。低下した出力電圧 V\_out2 は、 $V_{out2} = \{V_{out1} * C_{load} + [1 + (1/N)] * V_{in} * C_{F1y}\} / (C_{load} + C_{F1y})$  に等しい。N は、図 3A に示されるような直列接続遅延素子の段数である。隣接する段の間ごとの変動は、 $(1/N) * V_{in}$  であり、これは、本実施形態のステップサイズ変動である。このように、出力電圧におけるノイズがバックブースト回路で同じ状況下では、図 3 におけるコンデンサ 330 の容量 C\_Load は、図 2 におけるコンデンサ 230 の C\_Load における容量の 1/N になる必要がある。

30

40

### 【0032】

パルス幅変調ユニット 306 の出力を順次シフトする機能を実現すべく、本発明のバックブースト回路 300 に双方向シフト機構が設けられる。一実施形態では、双方向シフト

50

機構は、制御信号をスイッチ  $S_A$ 、 $S_B$ 、 $S_C$ 、 $S_D$  および  $S_E$  に提供することにより実現でき、このことは、後に図 4 において例示する。

#### 【0033】

パルス幅変調ユニット 306 の出力を右方向にシフトする機能を実現すべく、すなわち、パルス幅変調ユニット 306 の出力のパルス幅を増減すべく、本発明のバックブースト回路 300A に計数機構が設けられる。一実施形態では、計数機構は、パワーグッドクロックパルス PG を参照用に用いる。パワーグッドクロックパルス PG は、出力電圧と予め決められた基準電圧とを比較することにより得られる。本実施形態では、計数機構は、パワーグッドクロックパルス PG と同じ状態のままであるときの回数をカウントする。例えば、PG が H 状態のままであるときをカウントすることにより予め決められた回数に達する場合、ソースクロック信号 CLK\_S のパルス幅は、クロック信号 399 からクロック信号 391 への順に変化する。すなわち、予め決められた値を伴い減少する。PG が L 状態のままであるときの決定回数をカウンタがカウントした場合、ソースクロック信号 CLK\_S のパルス幅は、クロック信号 391 からクロック信号 399 の順に変更される。すなわち、予め決められた値を伴い増大する。計数機構は、後に図 5 で詳細を示す。

10

#### 【0034】

本発明のバックブースト回路に設けられるパルス幅周波数変調機構は、左右シフト機構および計数機構を備える周波数変調機構およびパルス幅変調機構を使用する。バックブースト回路の出力電圧は、クリーンになることができ、それは、バックブースト回路の出力におけるノイズが著しく減少したことを意味する。

20

#### 【0035】

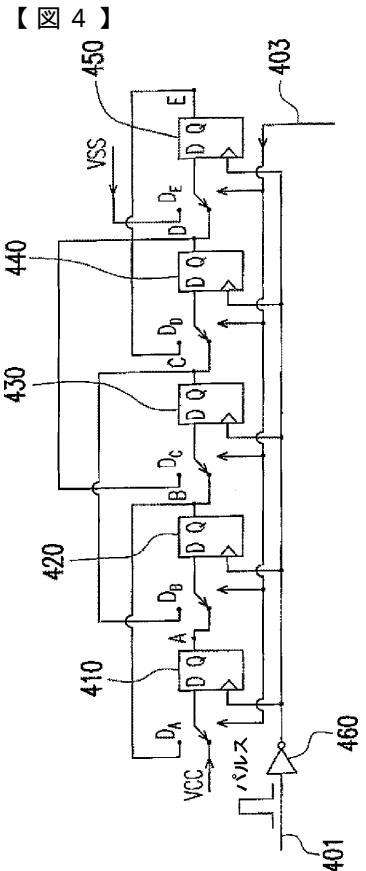

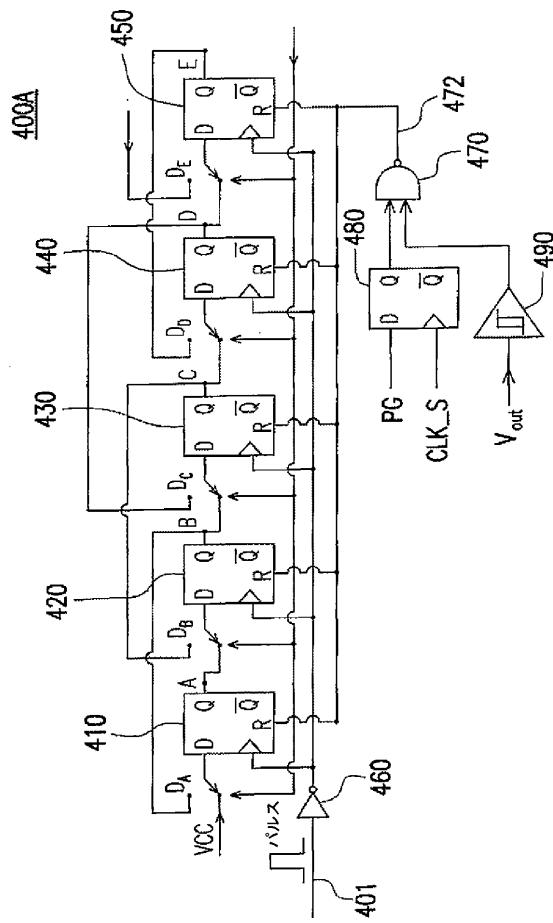

図 4 を参照すると、本発明の一実施形態の双方向シフト機構を示す回路図が提供される。

#### 【0036】

図 3B に示されるようなスイッチ  $S_A$ 、 $S_B$ 、 $S_C$ 、 $S_D$  および  $S_E$  をそれぞれ制御すべく、ノード A、B、C、D および E における信号が提供される。双方向シフト回路 400 は、5つのレジスタ 410、420、430、440 および 450 と、5つの二路スイッチ  $D_A$ 、 $D_B$ 、 $D_C$ 、 $D_D$  および  $D_E$  と、インバータ 460 とを含む。一実施形態では、レジスタ 410、420、430、440 および 450 は、D タイプフリップフロップにより実装される。一実施形態では、二路スイッチを交換すべくマルチプレックスを用いることができる。双方向シフト回路 400 の各レジスタ 410、420、430、440 および 450 にトリガパルス 401 が印加され、これら二路スイッチ  $D_A$ 、 $D_B$ 、 $D_C$ 、 $D_D$  および  $D_E$  にはシフト方向を制御するための方向クロックパルス 403 が印加される。トリガパルス 401 は、レジスタ 410、420、430、440 および 450 の動作をトリガするよう用いられる。方向クロックパルス 403 は、動作電圧 VCC (レジスタ 410 用) または、隣接するレジスタの出力 (レジスタ 420、430、440 および 450 用) に結合されるか、あるいは、隣接するレジスタの次のレジスタの出力 (レジスタ 410、420、430 および 440 用) またはその代わりに接地電圧 VSS (レジスタ 450 用) に結合されるレジスタ 410、420、430、440 および 450 の入力を制御するよう用いられる。

30

#### 【0037】

二路スイッチ  $D_A$  は、レジスタ 410 の入力を動作電圧 VCC あるいはレジスタ 420 の出力に結合するよう用いられる。二路スイッチ  $D_B$  は、レジスタ 420 の入力をレジスタ 410 の出力あるいはレジスタ 430 の出力に結合するよう用いられる。二路スイッチ  $D_C$  は、レジスタ 430 の入力をレジスタ 420 の出力あるいはレジスタ 440 の出力に結合するよう用いられる。二路スイッチ  $D_D$  は、レジスタ 440 の入力をレジスタ 430 の出力あるいはレジスタ 450 の出力に結合するよう用いられる。二路スイッチ  $D_E$  は、レジスタ 450 の入力を接地電圧 VSS あるいはレジスタ 440 の出力に結合するよう用いられる。

40

#### 【0038】

50

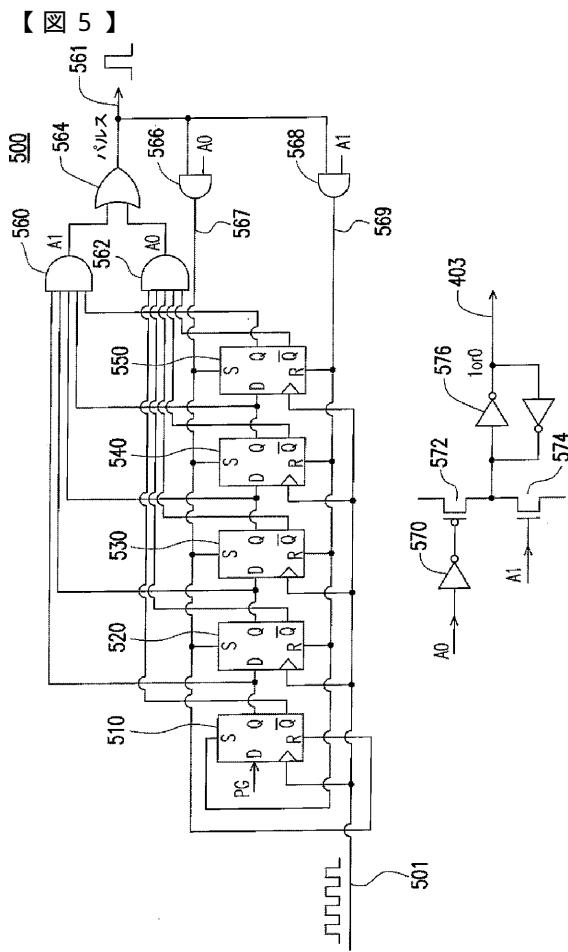

図5を参照されたい。図5は、本発明のバックブースト回路に設けられる計数機構の一実施形態を示す回路を表す。図4のトリガパルス401および方向クロックパルス403は、例えば、計数回路500をカウントすることにより生成される。生成されたトリガパルスは、双方向シフト回路400をトリガするよう用いられ、生成された方向クロックパルスは、双方向シフト回路400のシフト方向を制御するよう用いられる。計数回路500は、直列接続Dタイプフリップフロップ(DFF)ユニット510、520、530、540および550と、論理ANDゲート560、562、566および568と、論理ORゲート564と、インバータ570と、PMOSトランジスタ572と、NMOSトランジスタ574と、ラッチ回路576とを含む。一例においてソースクロック信号CLK\_Sと同じである計数クロック501は、DFFユニット510、520、530、540および550の動作をトリガするよう計数回路500に適用される。

#### 【0039】

計数クロック501の周波数は、計数回路500におけるカウントの周波数を決定できる。

#### 【0040】

DFFユニット510の入力D端子は、クロックパルスPG(図3Bのコンパレータ340から出力されるパワーゲッドラジオ信号PG)に結合される。直列接続されるDFFユニット510、520、530、540および550のQ端子の出力は、ANDゲート560の入力に接続される。直列接続されるDFFユニット510、520、530、および540のQ端子の出力は、次の段のDFFユニット520、530、540および550の入力にそれぞれ接続される。直列接続DFFユニット510、520、530、540および550の/Q(Q端子と相補的な)端子の出力は、ANDゲート562の入力に接続される。ANDゲート560および562の両方の出力A1およびA0は、ORゲート564の入力に結合され、トリガパルス561がしかるべき生成される。

#### 【0041】

トリガパルス561は、また、ANDゲート566の1つの入力と、ANDゲート568の1つの入力とに結合される。ANDゲート566の他の入力は、ANDゲート562の出力A0に結合される。ANDゲート568の他の入力は、ANDゲート560の出力A1に結合される。ANDゲート566の出力567は、DFFユニット510、520、530、540および550の端子(図に示す"S")をセットすべく結合される。ANDゲート568の出力569は、DFFユニット510、520、530、540および550の端子(図に示す"R")をリセットすべく結合される。

#### 【0042】

ANDゲート562の出力A0は、インバータ570を介しPMOSトランジスタ572のゲートに結合される。ANDゲート560の出力A1は、NMOSトランジスタ574のゲートに結合され、ラッチ回路576の1つの端子は、MOSトランジスタ572とNMOSトランジスタ574との間を相互接続するポイントに接続される。図4の双方向シフト回路のシフト方向を制御する方向クロックパルス403が生成される。

#### 【0043】

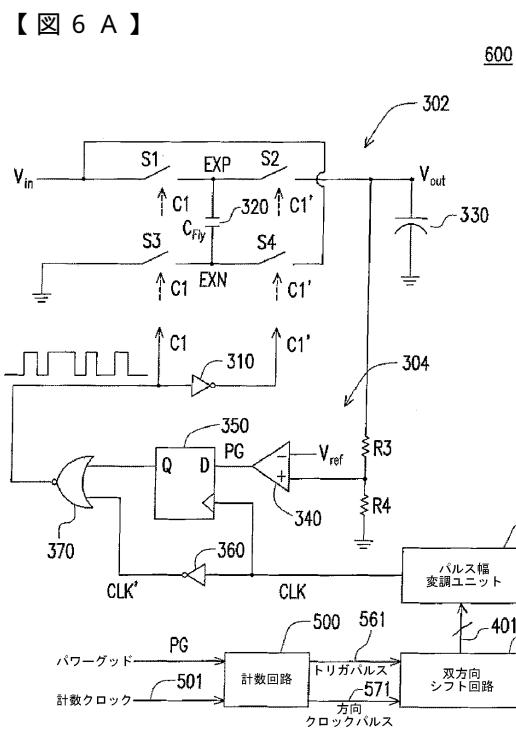

図6Aを参照されたい。図6Aは、本発明の一実施形態の変換回路の概略ブロック図を示す。一実施形態では、変換回路600は、バックブーストユニット302と、周波数変調ユニット304と、パルス幅変調ユニット306と、双方向シフト回路400と、計数回路500とを含む。図3B、図4および図5で説明したのと同じ機能を有する図6Aの要素および信号は、同じ参照符号で示され、対応する説明は、上記を参照することができる。

#### 【0044】

周波数変調ユニット304からのパワーゲッドラジオ信号PGを計数クロックに基づきカウントすることにより、トリガパルス561および方向クロックパルス571がしかるべき生成される。トリガパルス561および方向クロックパルス571は、双方向シフト回路400に印加される。受信されたトリガパルス561は、双方向シフト回路400をトリ

がすべく用いられ、生成された方向クロックパルスは、双方向シフト回路 400 のシフト方向を制御すべく用いられる。ソースクロック C L K\_S がパルス幅変調ユニット 306 に印加され、双方向シフト回路 400 からの複数の制御信号 401 の制御下で、変調されたクロック C L K は、周波数変調動作のための周波数変調ユニット 304 に印加される。パルス幅変調および周波数変調がソースクロック C L K\_S に対し実行された後に生成される制御クロック C 1 は、電圧変換動作のためのバックブーストユニット 302 に印加される。バックブーストユニット 302 におけるスイッチ S 1、S 2、S 3 および S 4 を制御することにより、変換された出力電圧  $V_{out}$  が得られる。

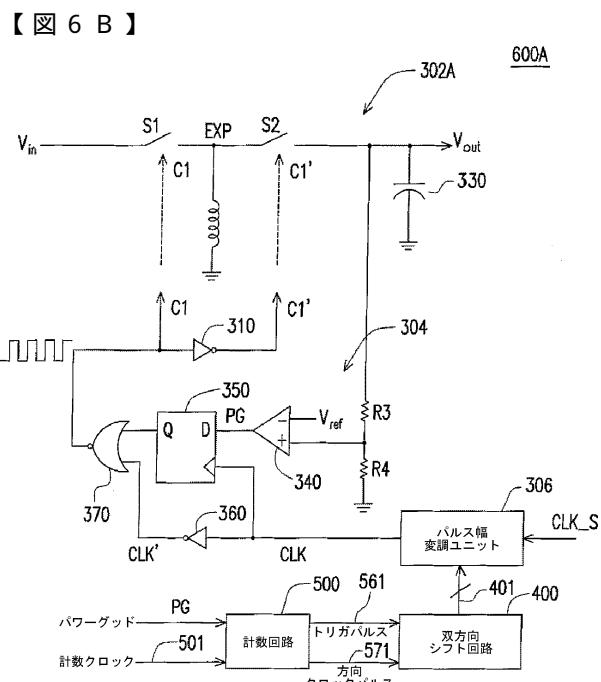

#### 【0045】

他の実施形態では、図 6 A のバックブーストユニット 302 は、バックレギュレータ、ブーストレギュレータ、バックブーストレギュレータ、または、あらゆる種類の直流 - 直流コンバータとも交換できる。コンデンサをエネルギー貯蔵手段として用いる代わりに、バックブーストユニット 302、バックレギュレータ、ブーストレギュレータ、バックブーストレギュレータ、あるいは、直流 - 直流コンバータにおいて、インダクタを用いることができる。例えば、図 6 B は、本発明の他の実施形態の変換回路の概略ブロック図を示す。変換回路 600A は、バックブーストユニット 302A と、周波数変調ユニット 304 と、パルス幅変調ユニット 306 と、双方向シフト回路 400 と、計数回路 500 とを含む。図 6 A および図 6 B における同じ参照符号の付された要素は、同じ機能を実行し、対応する説明は、前述の説明に関連する。変換回路 600A では、パルス幅変調および周波数変調がソースクロック C L K\_S に実行された後に生成される制御クロック C 1 が、電圧変換動作のためのバックブーストユニット 302A に印加される。バックブーストユニット 302A においてスイッチ S 1 および S 2 を制御することにより、変換された出力電圧  $V_{out}$  が得られる。

#### 【0046】

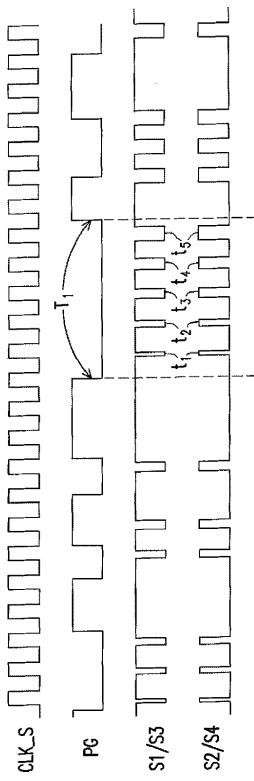

図 7 を参照されたい。図 7 は、図 6 のパルス幅周波数変調を用いた変換回路 600 のタイミングチャートを示す。クロックパルス PG が論理 L のままである状態なら、バックブーストユニット 302 のスイッチ S 1、S 2、S 3 および S 4 は、それらの位相をより頻繁に変えるであろうことは明らかである。さらに、クロックパルス PG が論理 L のままである期間が長くなると、スイッチ S 1 および S 3 が論理 L のままである期間も長くなり、スイッチ S 2 および S 4 が論理 H である期間も長くなるだろう。図 7 に示すように、クロックパルス PG が論理 L のままである期間 T 1 において、スイッチ S 1 / S 3 および S 2 / S 4 がそれらの位相を変更する回数は 5 回であり、スイッチ S 1 / S 3 が論理 L のままであることは、スイッチ S 2 / S 4 が論理 H のままである期間は、ますます長くなり、すなわち、 $t_5 > t_4 > t_3 > t_2 > t_1$  である。

#### 【0047】

スイッチ SW1 / SW3 およびスイッチ SW2 / SW4 のオン / オフを制御するクロックパルス PG の波形に示されるように、オン / オフを切り替えられるスイッチ SW1 / SW3 ( またはスイッチ SW2 / SW4 ) の時間幅は、クロックパルス PG の発生の頻度および幅に直接影響を受ける。クロックパルス PG が論理レベルで維持する回数をカウントする計数機構を用いるのは、主に、パルス幅が変調されたソースクロックが頻繁に変化しあまりないようにするためにあることに注目されたい。したがって、異なる用途次第で、あるいは、変換回路の応答速度における異なる必要条件に従い、基準値は、特定の論理レベルで維持する時間の基礎として採用される。当業者が本発明を簡単に実施できるようにする目的で。

#### 【0048】

本発明の変換回路が電圧降圧レギュレータに適用される場合は、例えばバルク変換回路のように、大きい正入力電圧を小さい正出力電圧に変換するためである。変換回路 600 における動作を切り替えるために必要なのは 2 つのスイッチ S 1 および S 2 だけであり、他のスイッチ S 3 および S 4 は、切り替え動作を禁じられる。コンデンサ 320 の容量は  $C_{F1y}$  であり、コンデンサ 330 の容量は  $C_{L0ad}$  であり、初期出力電圧は、 $V_{out}$

10

20

30

40

50

$t_3$  であり、出力電圧  $V_{out_4}$  は、コンデンサ 320 および 330 の分圧効果後の電圧であると仮定する。低下した出力電圧  $V_{out_2}$  は、 $V_{out_4} = (V_{out_3}^* C_{load} + V_{in}^* C_{fly}) / (C_{load} + C_{fly})$  に等しい。すなわち、電圧遅降動作は、常にスイッチ S3 をオンにし、スイッチ S4 をオフに保つことにより得る。切り替え動作の効率は、変換回路で使用されるスイッチが 2 つだけの場合に著しく向上する。

#### 【0049】

図 8 を参照されたい。図 8 は、本発明の他の実施例の変換回路の概略図を示す。変換回路 800 は、バックブーストユニット 302、周波数変調ユニット 304、パルス幅変調ユニット 306、双方向シフト回路 400、および、計数回路 500 を含む。図 3B、図 4、図 5、および、図 6 に記載されたものと同じ機能をもつ図 8 の要素および信号は、同じ参照符号で示され、対応する説明は、上記を参照することができる。変換回路 600 と比較すると、変換回路 800 には、電圧遅降機能としての回路が追加される。

#### 【0050】

回路では、コンパレータ 810 の 2 つの入力がその正入力における入力電圧  $V_{in}$  と、その負入力における基準電圧  $V_{ref}$  とにそれぞれ結合される。コンパレータ 810 の出力は、論理 AND ゲート 830 の 1 つの入力に結合される。動作を切り替える制御クロック C1 も、AND ゲート 830 の 1 つの入力に結合される。入力電圧  $V_{in}$  と比較すべく基準電圧  $V_{ref}$  が用いられ、入力電圧  $V_{in}$  が基準電圧  $V_{ref}$  より大きい場合は、入力電圧  $V_{in}$  が出力電圧  $V_{out}$  より大きいことを意味する。スイッチ S3 および S4 は、切り替え動作を禁じられる。図 4 に示すような双方向シフト回路 400 のノード E における信号 801 も、インバータ 820 を介し AND ゲート 830 の第 3 の入力に結合される。

#### 【0051】

信号 801 は、変換回路 800 が遅降レギュレータとして動作するかどうかを判断する。さらに、信号 801 は、制御クロック C1 のクロック幅がフルクロック幅モードで実行されるか、すなわち、切り替え動作はソースクロック CLK\_S と同じ完全なクロック幅で実行されるかどうかを判断するためにも用いられる。この時、負荷コンデンサ 330 における電流は非常に大きく、切り替え動作にスイッチ S3 および S4 が再び用いられる。

#### 【0052】

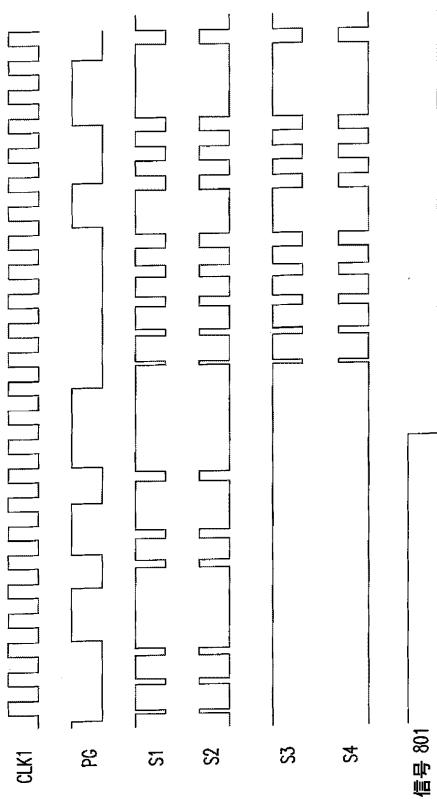

図 9 を参照されたい。図 9 は、図 8 のパルス幅周波数変調を用いる変換回路 800 のタイミングチャートである。変換回路 800 が遅降レギュレータとして動作する時間において、スイッチ S3 および S4 は、切り替え動作を禁じられる。しかしながら、図 4 の双方向シフト回路 400 のノード E における信号 801 が論理 H から論理 L に変化した場合、スイッチ S3 および S4 は、再び切り替え動作に用いられる。

#### 【0053】

ソフトスタート機構および短絡防止は、パワーマネジメント制御設計のための基本的な機能である。ソフトスタート回路は、プラグインまたはアウト時の過渡電流が原因で集積回路が熱くなるのを防ぐ。本発明の変換回路では、変換回路が始動される、すなわち、出力電圧  $V_{out}$  が検出されるたびに、パルス幅変調された第 1 のクロック信号は、最小パルス幅に調整される。

#### 【0054】

このような機能を達成すべく、図 10 に示すような、図 4 の双方向シフト機構に回路が追加される。図 4 に記載されたのと同じ機能を有する図 10 の要素および信号は、同じ参照符号として示され、対応する説明は、上記を参照することができる。双方向シフト回路 400A は、論理 NAND ゲート 470、D タイプフリップフロップ (DFF) 480、および、電圧検出器 490 をさらに含む。DFF 480 の入力端子 D は、パワーグッド (PG) パルスに結合され、動作クロックは、ソースクロック CLK\_S に結合される。DFF 480 の Q 端子における出力は、NAND ゲート 470 の入力に結合される。電圧検出器 490 の出力は、NAND ゲート 470 の他の入力に結合される。電圧検出器 490

10

20

30

40

50

の入力は、出力電圧  $V_{out}$  に結合される。PG パルスが第1の時間に検出される場合、あるいは、PG パルスが検出され、出力電圧  $V_{out}$  が電圧検出器 490 による望ましいレベルより低く検出される場合、NAND ゲート 470 の出力 472 は、2つの場合のどちらにおいても 5つのレジスタ 410、420、430、440 および 450 をリセットし、図 3B に示されるようなスイッチ SA をオンにすることによる最小パルス幅をもつクロック 391 は、周波数変調ユニット 304 に出力される。出力電圧  $V_{out}$  が低すぎるように検出された場合は、出力電圧  $V_{out}$  が設計で望まれるように予め決められたりセット値より低いことを意味する。

#### 【0055】

本発明において提供されるパルス幅変調機構は、動作のための周波数変調ユニットに印加されるクロックのパルス幅を徐々に増減させる。すなわち、印加されるクロックのパルス幅の増減は、バックブースト回路の出力の電圧レベルに基づき制御される。バックブースト回路が利用目的で設計される場合、懸念される課題は、バックブースト回路の出力に大きな短絡電流が生じるのを避けなければならないということである。もし、生じた場合、バックブースト回路を備える集積回路は深刻なダメージを受ける。短絡問題が解消されれば、バックブースト回路の出力は、円滑に開始され、正しい電圧レベルに調整される。本発明のバックブースト回路は、デジタル制御機構により動作するよう設計される。短絡が検出された場合、図 3B に示すようなスイッチ SA をオンにすることによる最小パルス幅を有するクロックは、切り替え動作のための周波数変調ユニット 304 に出力される。単純な設計により短絡の問題をかなり防止することができる。

#### 【0056】

携帯電話あるいは他の携帯機器で用いられるメモリカードは、ますます一般的になり、使用は急速に広がっている。しかしながら、電力消費について考えると、携帯機器の動作電圧は、例えば、電力を消費させない 3.3 ボルトあるいは 1.8 ボルトなどの異なる電圧で動作可能なように設計される。

#### 【0057】

異なる電圧レベルの動作電圧の互換性に対し、メモリカードは、デュアルボルテージメモリデバイス、例えば、デュアルボルテージ・セキュアデジタル (SD) カードまたはデュアルボルテージリデューストサイズ マルチメディア (DVR-S MMC) カードと名づけられた 2 つの異なる電力電圧 ( 例えば約 3.3V および約 1.8V ) で動作可能なように設計されている。例えば、フラッシュメモリカードなどのデュアルボルテージメモリデバイスに用いられる半導体メモリも、例えば約 3.3V および約 1.8V の 2 つの異なる電力電圧で動作可能である。異なる動作電圧の互換性を提供するために、例えば前述の 3.3V から 1.8V までの場合、携帯機器またはメモリカードの動作電圧は、正常に動作するよう注意深く調整されなければならない。本発明のバックブースト回路は、例えば、動作のための電圧間を調整するために、ホストとフラッシュメモリカードなどのメモリカードとの間に配置されるものとして実装される。

#### 【0058】

一実施形態では、直流 - 直流パワーマネージャは、少なくとも 1 つのフラッシュメモリと、ホスト電力を提供するホストとの間に接続されるコントローラ内に実装されることができる。ホスト電力が 3.3 ボルトであり、フラッシュメモリが 1.8 ボルトでのみ動作可能である場合、直流 - 直流パワーマネージャを備えるコントローラは、ホスト電力を 1.8 ボルトに調整してそれをフラッシュメモリに提供できる。ホスト電力が 1.8 ボルトであり、フラッシュメモリが 3.3 ボルトでのみ動作可能である場合、直流 - 直流パワーマネージャを備えるコントローラは、ホスト電力を 3.3 ボルトに調整してそれをフラッシュメモリに提供できる。

#### 【0059】

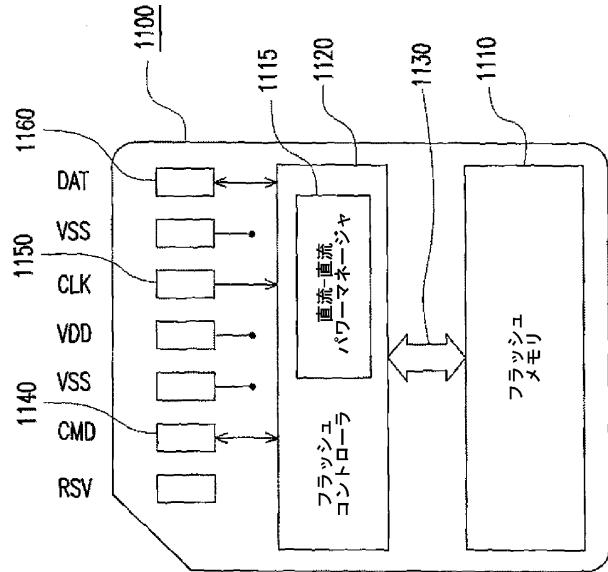

図 11 を参照されたい。図 11 は、本発明の一実施形態の直流 - 直流パワーマネージャを備えるマルチメディアカード (MMC) の概略図を示す。マルチメディアカード 110 は、フラッシュメモリデバイス 1110 と、該フラッシュメモリデバイス 1110 に内

10

20

30

40

50

部バス 1130 を介し結合されるフラッシュコントローラ 1120 とを含む。フラッシュコントローラ 1120 は、コマンドピン 1140、クロックピン 1150、および、データピン 1160 を含むホストバス（図示せず）と結合する。本実施形態における用語「フラッシュメモリデバイス」は、「フラッシュメモリデバイス」および「複数のフラッシュメモリ」のどちらの用語とも同義的に用いられる。

#### 【0060】

直流 - 直流パワーマネージャ 1120 は、パルス幅変調機構を備える本発明のバックブースト回路を含む。バックブースト回路の出力におけるノイズは、著しく減少し、マルチメディアカード（MMC）1100 は、直流 直流パワーマネージャ 1120 により異なる電圧で動作可能である。

10

#### 【0061】

本発明の範囲および趣旨を逸脱せずに本発明の構造に様々な修正および変更がなされ得ることは、当業者にとって明らかであろう。

#### 【0062】

前述の観点から、本発明は、本発明に加えられる修正および変更をカバーし、それらは、添付の請求項および請求項の均等物の範囲内に納まる。

#### 【図面の簡単な説明】

#### 【0063】

【図 1】従来のバックブースト回路を示す。

【図 2】バックブーストユニットと、制御クロック信号の周波数を制御する機能を備える周波数変調ユニットとを含むバックブースト回路を示す。

20

【図 3 A】本発明の一実施形態のパルス幅周波数変調機構を含むバックブースト回路を示す。

【図 3 B】図 3 A のバックブースト回路のタイミングチャートを示す。

【図 4】本発明の一実施形態の双方向シフト機構を示す回路を表す。

【図 5】本発明のバックブースト回路に設けられる計数機構の一実施形態を示す回路を表す。

【図 6 A - 6 B】本発明の一実施形態の変換回路の概略プロック図を示す。

【図 7】図 6 のパルス幅周波数変調を用いる変換回路のタイミングチャートを示す。

【図 8】本発明の他の実施形態の変換回路の概略図を示す。

30

【図 9】図 8 のパルス幅周波数変調を用いる変換回路のタイミングチャートを示す。

【図 10】ソフトスタート機能および短絡防止機能を有する、本発明の他の実施形態の双方向シフト機構を示す回路を表す。

【図 11】本発明の一実施形態の直流 - 直流電力マネージャを備えるマルチメディアカード（MMC）の概略図を示す。

【図1】

【図2】

【図3 A】

【図3 B】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

H 02 M      3 / 0 0