【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成24年5月31日(2012.5.31)

【公表番号】特表2011-511567(P2011-511567A)

【公表日】平成23年4月7日(2011.4.7)

【年通号数】公開・登録公報2011-014

【出願番号】特願2010-545100(P2010-545100)

【国際特許分類】

H 03K 19/0185 (2006.01)

【F I】

H 03K 19/00 101C

【誤訳訂正書】

【提出日】平成24年4月9日(2012.4.9)

【誤訳訂正1】

【訂正対象書類名】明細書

【訂正対象項目名】全文

【訂正方法】変更

【訂正の内容】

【発明の詳細な説明】

【発明の名称】レベルシフティング回路および方法

【技術分野】

【0001】

本開示は、一般的に、レベルシフティング回路および方法に関する。

【背景技術】

【0002】

技術の進歩は、より小さくより高性能なコンピュータ装置をもたらす結果となった。例えば、携帯無線電話機、携帯情報端末(PDAs)、および小さく軽量でユーザによって容易に持ち運ばれるペーディング装置のような、無線コンピュータ装置を含む様々なポータブルパーソナルコンピュータ装置が現在存在する。より具体的には、携帯電話およびインターネットプロトコル(IP)電話のような携帯無線電話機は、無線ネットワークによって音声およびデータパケットを通信することができる。さらに、多くのそのような無線電話が、そこに組込まれる他のタイプの装置を含む。例えば、無線電話はさらにデジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダおよびオーディオファイルプレーヤを含みうる。さらに、無線電話は、インターネットにアクセスするために使用することができるウェブブラウザアプリケーションのようなソフトウェアアプリケーションを含む実行命令を処理することができる。そのため、これらの無線電話は著しい演算能力を含むだろう。

【0003】

消費電力を低減するために、またこのようにして携帯装置の電池寿命を拡張するために、電源はますます低電圧で電子コンポーネントを動作させる。いくつかのコンポーネントは低電圧でうまく動作しうるが、他のコンポーネントは高電圧を要求しうる。したがって、異なる電圧で動作するコンポーネントを含む装置は、より高い電圧とより低い電圧との間で信号を変換するためにレベルシフタ(level shifter)を使用しうる。レベルシフタ回路設計は、入力遷移(input transition)への応答時間を改善することと低電圧での動作の範囲を改善することとのどちらかを選択することを多くの場合要求する。応答時間の増加は、動作の範囲を一般的に減少させ、その一方、動作の範囲を増加することは一般的には応答時間を減少させる。したがって、レベルシフタは、低電力動作中に装置の性能を制限しうる。

**【発明の概要】****【0004】**

特定の実施例では、入力電圧信号を受け取るための入力、および、レベルシフトされた電圧信号を供給するための出力を含む回路装置が開示される。その回路装置は、入力に連結された第1の弱状態保持パス(weak state holding path)、および、出力に連結された第2の弱状態保持パスを含む。その回路装置は、第1の弱状態保持パスおよび第2の弱状態保持パスに連結された電圧プルアップ論理回路(voltage pull-up logic circuit)をさらに含む。その回路装置は、電圧プルアップ論理回路のアクティブ化を選択的に制御するために電圧プルアップ論理回路に連結された制御パスをさらに含む。

**【0005】**

別の実施例では、メモリアレイ、および、第1のレベルシフティング回路によってメモリアレイに連結された第1の入力を含むシステムが開示される。そのシステムは、第2のレベルシフティング回路によってメモリアレイに連結された第2の入力をさらに含む。第1のレベルシフティング回路は、第1の入力を受け取るための入力、および、メモリアレイへ第1のレベルシフトされた電圧信号を供給するための出力をさらに含む。第1のレベルシフティング回路は、入力に連結された第1の弱状態保持パスをさらに含む。第1のレベルシフティング回路は、出力に連結された第2の弱状態保持パスをさらに含む。第1のレベルシフティング回路は、第1の弱状態保持パスおよび第2の弱状態保持パスに連結された電圧プルアップ論理回路を含む。第1のレベルシフティング回路は、電圧プルアップ論理回路のアクティブ化を選択的に制御するために電圧プルアップ論理回路に連結された制御パスをさらに含む。

**【0006】**

別の実施例では、電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取るための手段を含む装置が開示される。その装置は、レベルシフティング回路からの出力信号を供給するための手段をさらに含む。その装置は、レベルシフティング回路の電圧プルアップ論理回路を選択的にアクティブにするための手段をさらに含む。

**【0007】**

別の実施例では、電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取ることを含む方法が開示される。その方法はレベルシフティング回路からの出力信号を供給することを含む。その方法はレベルシフティング回路の電圧プルアップ論理回路を選択的にアクティブにすることをさらに含む。

**【0008】**

開示された実施例によって提供される1つの特定の利点は、弱状態保持パスによる広い電圧シフト範囲、および、電圧プルアップ論理回路による入力信号遷移への迅速な応答である。別の特定の利点は、レベルシフティング回路の動作が比較的寛容な(tolerant)プロセスであるということである。

**【0009】**

本開示の他の様様、利点および特徴は、以下のセクションつまり、図面の簡単な説明、詳細な説明および請求項を含む全体の出願の参照の後に明白になるだろう。

**【図面の簡単な説明】****【0010】**

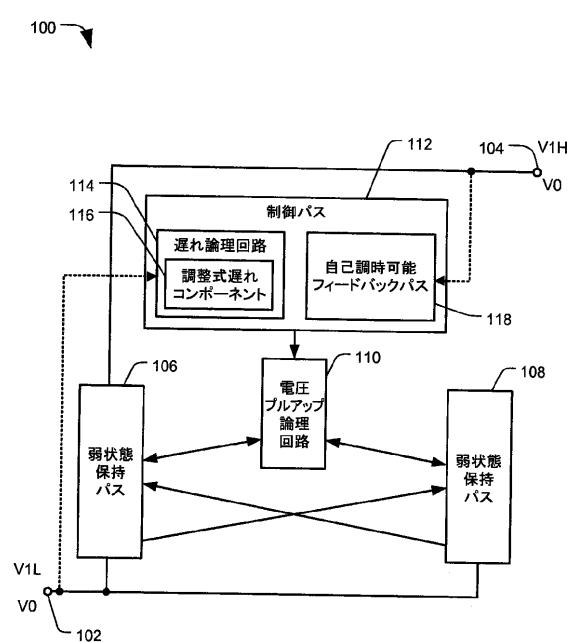

【図1】図1は、レベルシフティング回路装置の第1の実例となる実施例のブロック図である。

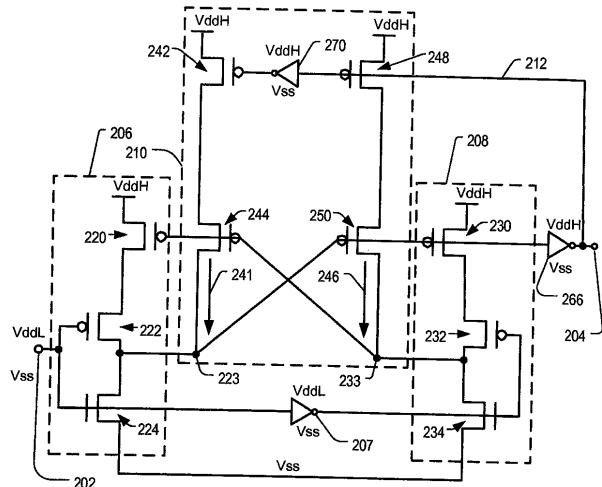

【図2】図2は、レベルシフティング回路装置の第2の実例となる実施例の回路図である。

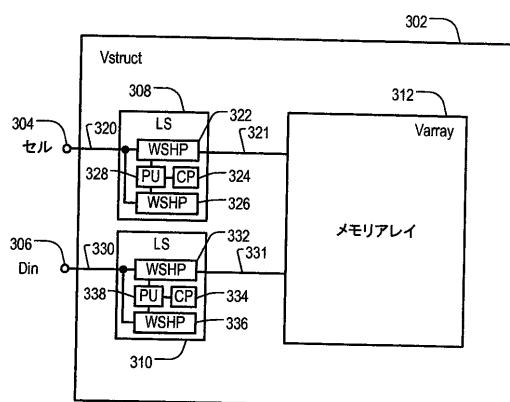

【図3】図3は、レベルシフティング回路装置を含むシステムの特定の実例となる実施例のブロック図である。

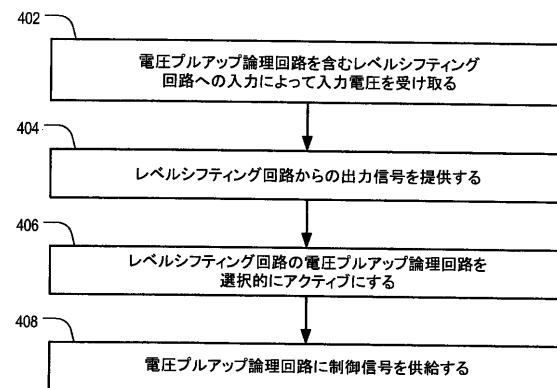

【図4】図4は、図1-3に例証された回路装置のような回路装置を使用する、レベルシフティングの方法の特定の実例となる実施例のフロー図である。

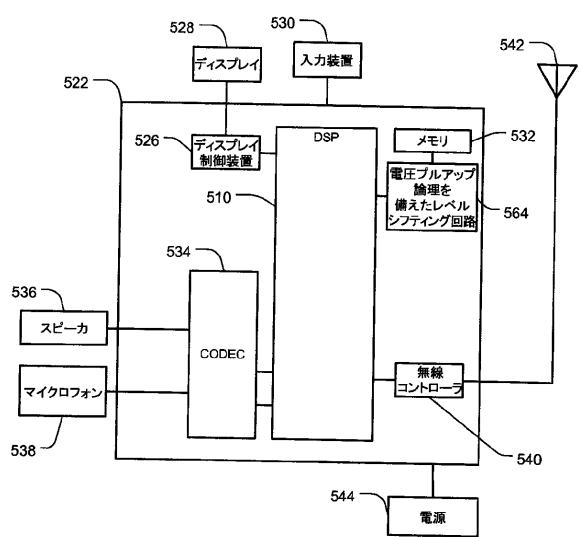

【図5】図5は、図1-4に記述された回路と方法の実施例が使用される代表的なモバ

イル通信装置のブロック図である。

【発明を実施するための形態】

【0011】

図1を参照して、レベルシフティング回路装置の第1の実例となる実施例が表現され、100と一般的に示される。レベルシフティング回路装置100は、入力電圧信号を受け取るための入力102を含む。出力104はレベルシフトされた電圧信号を提供する。第1の弱状態保持バス106は、入力102および出力104に連結される。第1の弱状態保持バス106は、入力102にさらに連結される第2の弱状態保持バス108に互いに連結される。電圧プルアップ論理回路110は、第1の弱状態保持バス106および第2の弱状態保持バス108の両方に連結される。制御バス112は、電圧プルアップ論理回路110に制御信号を供給するために連結される。

【0012】

特定の実施例では、入力102で受け取られた入力電圧信号は、ハイ状態(V1L)とロー状態(V0)との間の第1の電圧範囲内にある。入力電圧信号に応じて、第1の弱状態保持バス106は、ハイ状態(V1H)とロー状態(V0)の間の第2の電圧範囲内にあるレベルシフトされた電圧信号を出力104で生成する。特定の実施例では、第1の弱状態保持バス106および第2の弱状態保持バス108は、0.6-1.4Vあるいはその電圧以下のレベルシフティングを含む、入力電圧の広い範囲のレベルシフティングを可能にするように構成される。しかしながら、入力電圧の広い範囲上で動作することができる結果、第1の弱状態保持バス106および第2の弱状態保持バス108は、入力102で受け取られた入力信号の遷移に応じて比較的遅い遷移時間を示しうる。

【0013】

特定の実施例では、電圧プルアップ論理回路110は、第1の弱状態保持バス106および第2の弱状態保持バス108に電流を供給することにより、出力104でスイッチング速度を改善するよう作用する。弱状態保持バス106および108に電圧プルアップ論理回路110によって提供される追加電流は、入力信号の遷移に対する、より速い応答を可能にする。特定の実施例では、電圧プルアップ論理回路110は、入力102で受け取られた入力信号の検知された遷移に応じて第1の弱状態保持バス106および第2の弱状態保持バス108の少なくとも1つにレベルシフティング電流を供給するために主に動作する。電圧プルアップ論理回路110は、制御バス112に応答して、非遷移期間中の入力102で低電圧信号に対する弱状態保持バス106および108の感度を維持するために弱状態保持バス106および108に電流を供給することをやめる。

【0014】

制御バス112は電圧プルアップ論理回路110のアクティブ化を選択的に制御するのに適している。特定の実施例では、制御バス112は、出力104から電圧プルアップ論理回路110までの自己調時式フィードバックパス(self-timed feedback path)118を含む。制御バス112は、出力104で電圧レベル変化を検知し、出力104での遷移に基づいて特定の遅れが経過したと自己調時式フィードバックパス118が判断する場合に、弱状態保持バス106および108の1つ以上への電流をオフにするために電圧プルアップ制御論理110にアクティブ化信号を供給するよう作用しうる。

【0015】

別の実施例では、制御バス112は、入力102に連結された遅れ論理回路114を含む。この実施例では、制御バス112は、入力102での遷移を検知し、かつ電圧プルアップ論理回路110にアクティブ化信号を送るよう作用する。このアクティブ化信号は、電圧プルアップ論理回路110が、弱状態保持バス106、108あるいはそれら両方が論理状態(logic states)間で遷移することを支援するために電流の供給を開始することを引き起こしうる。制御バス112は、十分な遅れが入力102の遷移から経過したと判断する遅れ論理回路114に応じて、電圧プルアップ論理回路110に第2の制御信号を送るようさらに作用しうる。第2の制御信号は、電圧プルアップ論理回路110を非アクティブにして、入力電圧の広範囲に関して、弱状態保持バス106および108の通常動作

を再開しうる。特定の実施例では、遅れ論理回路 114 は調整可能であり、かつ、第 2 の制御信号に関連した遅れを制御するための調整可能遅れコンポーネント(adjustable delay component) 116 を含みうる。

#### 【0016】

動作中に、第 1 の入力信号は第 1 の電子コンポーネントから入力 102 で受け取られうる。レベルシフティング回路装置 100 は入力電圧レベルをシフトまたは変換し、出力 104 で出力電圧レベルを生成しうる。例えば、入力信号は、プロセッサ、バス、メモリあるいは他の電子コンポーネントから受け取られうる、また、出力は、プロセッサ、バス、メモリあるいは他の電子コンポーネントに提供されうる。第 1 の入力信号は、第 1 の電源に関連した電圧レベル V0 から V1L を反映しうる。出力 104 は、第 2 の電圧レベル V0 から V1H で動作する 1 つ以上の他の電子コンポーネントに連結されうる。実例となる例として、第 1 の電圧レベルは、0V から 1.0V までの電圧範囲に関連した信号でありうる、また、第 2 の電圧レベルは、0V から 3.3V までの電圧範囲に関連した信号でありうる。

#### 【0017】

第 2 の入力信号への入力 102 での遷移に応じて、第 1 および第 2 の弱状態保持バス 106 および 108 は、状態間で遷移し始める。電圧プルアップ論理回路 110 は、1 つ以上のトランジスタへ電荷(charge)を供給することによって電圧レベル遷移を支援するために第 1 の弱状態保持バス 106、第 2 の弱状態保持バス 108 あるいはそれら両方に電流を供給し始める。特定の実施例では、電圧プルアップ論理回路 110 は、弱状態保持バス 106 および 108 の少なくとも 1 つが状態間で遷移し始めたことを検知することに応じて電流を供給し始める。別の実施例では、電圧プルアップ論理回路 110 は代わりに、制御バス 112 からの制御信号に応じて電流を供給し始めるかも知れない。

#### 【0018】

例えば自己調時式フィードバックバス 118 や遅れ論理回路バス 114 によるような適切な遅れ期間の後、制御バス 112 は、弱状態保持バス 106 および 108 へ電流を供給することをやめるために、電圧プルアップ論理回路 110 を非アクティブにするために制御信号を提供する。電圧プルアップ論理回路 110 の非アクティブ化の後、互いに連結された弱状態保持バス 106 および 108 は、出力 104 で新しい出力電圧レベルを維持する。電圧プルアップ論理回路 110 を選択的にアクティブにすることによって、広範囲の入力動作電圧および速い出力レベル遷移が、レベルシフティング回路装置 100 によって両方とも提供される。

#### 【0019】

図 2 を参照して、レベルシフティング回路装置の第 2 の実例となる実施例が表現され、200 と一般的に示される。レベルシフティング回路装置 200 は、高電圧 VddL と低電圧 Vss の間の第 1 の電圧範囲に対応する入力信号を受け取るように構成された入力 202 を含む。レベルシフティング回路装置 200 は、高電圧 VddH によって表わされるハイ信号、および低電圧 Vss によって表わされるロー信号と共に、第 2 の電圧範囲への入力 202 のレベルシフティングに対応する出力信号を提供するように構成された出力 204 をさらに含む。レベルシフティング回路装置 200 は、第 1 の弱状態保持バス 206 および第 2 の弱状態保持バス 208 をさらに含む。第 1 の弱状態保持バス 206 は、入力 202 に連結され、また、第 2 の弱状態保持バス 208 は、第 1 の電圧範囲で動作するインバータ 207 を経由して入力 202 に連結される。電圧プルアップ論理回路 210 は、第 1 の弱状態保持バス 206 および第 2 の弱状態保持バス 208 の両方に連結される。制御バス 212 は、電圧プルアップ論理回路 210 および出力 204 に連結される。

#### 【0020】

特定の実施例では、第 1 の弱状態保持バス 206 は、電源電圧 VddH に連結された第 1 の端子と、第 2 の弱状態保持バス 208 に連結された制御端子と、第 3 の端子とを有する第 1 の弱 p チャネルトランジスタ(weak p-channel transistor) 220 を含む。第 1 の弱状態保持バス 206 は、第 1 の弱 p チャネルトランジスタ 220 の第 3 の端子に連結された第 4 の端子を含む第 2 の弱 p チャネルトランジスタ 222 をさらに含む。第 2 の弱 p

チャネルトランジスタ 222 は、入力 202 に連結された第 2 の制御端子、および第 1 のノード 223 に連結された第 5 の端子を有する。第 1 のノード 223 は電圧プルアップ論理回路 210 に連結される。第 1 の弱状態保持バス 206 は、第 1 のノード 223 に連結された第 6 の端子、入力 202 に連結された第 3 の制御端子、および第 2 の電源電圧  $V_{SS}$  に連結された第 7 の端子を含む強  $n$  チャネルトランジスタ (strong  $n$ -channel transistor) 224 をさらに有する。ここに使用されるように、強トランジスタは弱トランジスタに比して、例えばゲート電圧のような、制御端子で信号に対してより速い電流応答を有し、かつ弱トランジスタより広く、より短いチャネルを有しうる。例えば、弱  $p$  チャネルトランジスタ 220 および 222 は、およそ幅 0.12 マイクロメートル ( $\mu\text{m}$ ) で長さ 0.1  $\mu\text{m}$  であるチャネルを備えた  $p$  チャネル MOSFETs でありうる、また、強  $n$  チャネルトランジスタ 224 は、およそ幅 0.6  $\mu\text{m}$  で長さ 0.04  $\mu\text{m}$  であるチャネルを備えた  $n$  チャネル MOSFET でありうる。

#### 【0021】

特定の実施例では、第 2 の弱状態保持バス 208 は、電源電圧  $V_{DDH}$  に連結された第 1 の端子と、第 1 の弱状態保持バス 206 に連結された制御端子と、第 2 の弱  $p$  チャネルトランジスタ 232 に連結された第 3 の端子とを含む第 1 の弱  $p$  チャネルトランジスタ 230 を含む。第 2 の弱  $p$  チャネルトランジスタ 232 は、第 1 の弱  $p$  チャネルトランジスタ 230 の第 3 の端子に連結された第 4 の端子、インバータ 207 の出力に連結された第 2 の制御端子、および第 2 のノード 233 に連結された第 5 の端子を含む。強  $n$  チャネルトランジスタ 234 は、第 2 のノード 233 に連結された第 6 の端子、インバータ 207 の出力に連結された第 3 の制御端子、および第 2 の電源電圧  $V_{SS}$  に連結された第 7 の端子を有する。第 2 の弱状態保持バス 208 の第 2 のノード 233 は、第 1 の弱状態保持バス 206 の第 1 の弱  $p$  チャネルトランジスタ 220 の第 1 の制御端子に連結される。同様に、第 1 の弱状態保持バス 206 の第 1 のノード 223 は、第 2 の弱状態保持バス 208 の第 1 の弱  $p$  チャネルトランジスタ 230 の第 1 の制御端子に連結される。

#### 【0022】

プルアップ論理回路 210 は、第 2 の弱状態保持バス 208 に連結される第 1 の強プルアップバス (strong pull-up path) 241 を含み、第 1 の弱状態保持バス 206 に連結される第 2 の強プルアップバス 246 をさらに含む。第 1 の強プルアップバス 241 は、電源電圧  $V_{DDH}$  に連結された、かつ、制御バス 212 に連結された制御端子を有する第 1 の強  $p$  チャネルトランジスタ 242 を含む。第 1 の強プルアップバス 241 は、第 1 の強  $p$  チャネルトランジスタ 242 に連結されて、第 1 のノード 223 にさらに連結された第 2 の強  $p$  チャネルトランジスタ 244 を有する。第 2 の強  $p$  チャネルトランジスタ 244 は、第 2 のノード 233 に連結された制御端子を有する。

#### 【0023】

同様に、第 2 の強プルアップバス 246 は、電源電圧  $V_{DDH}$  に連結された、かつ、制御バス 212 に連結された制御端子を有する第 1 の強  $p$  チャネルトランジスタ 248 を有する。第 2 の強プルアップバス 246 は、第 1 の強  $p$  チャネルトランジスタ 248 と第 2 のノード 233 の間に連結されて、第 1 のノード 223 に連結された制御端子を有する、第 2 の強  $p$  チャネルトランジスタ 250 をさらに含む。

#### 【0024】

出力 204 は、出力インバータ 266 を経由して第 1 のノード 223 に連結される。制御バス 212 は、出力 204、第 2 の強プルアップバス 246 の第 1 の強  $p$  チャネルトランジスタ 248 の制御端子、および、インバータ 270 を経由した第 1 の強プルアップバス 241 の第 1 の強  $p$  チャネルトランジスタ 242 の制御端子に連結される。制御バス 212 は、出力 204 から電圧プルアップ論理回路 210 までの調時式フィードバックバスを含む。特に、電圧プルアップ論理回路 210 は、ノード 223 か 233 のうちの 1 つが、低電圧レベルから高電圧レベルに遷移するときに動作を開始し、第 1 のノード 223 での電圧遷移が強プルアップバス 241 および 246 のトランジスタ 242 および 248 の制御端子への出力インバータ 266 を介して伝搬するまで動作し続ける。強プルアップバ

ス241および246のトランジスタ242および248への制御バス212によって提供される、結果として生じる制御信号は、電圧プルアップ論理回路210を非アクティブにする。

【0025】

定常的な動作中に、電圧プルアップ論理回路210はオフである。特に、第1の強電流バス241のトランジスタ242および244の少なくとも1つはオフであり(つまり、通電していない)、また、第2の強電流バス246のトランジスタ248および250の少なくとも1つはオフである。

【0026】

ロー信号(例えばVss)が入力202で維持される場合、弱状態保持バス206の第1の強nチャネルトランジスタ224はオフであり、2つの弱pチャネルトランジスタ220と222はオンとなり、高電圧(例えば、「1」信号と認められるであろう電圧を含めるようにこのコンテキスト(context)の中で使用されたVddH)で第1のノード223にバイアスをかける。出力インバータ266は、第1のノード223に連結された入力を有し、低電圧(例えば「0」信号と認められるであろう電圧を含めるようにこのコンテキストの中で使用されたVss)を出力する。第2の弱状態保持バス208の強nチャネルトランジスタ234はオンであり、また、弱pチャネルトランジスタ230および232はオフであり、第2のノード233に低電圧でバイアスをかける。電圧プルアップ論理回路210では、第1の強プルアップバス241の第1のトランジスタ242はオフであり、また、第2のトランジスタ244はオンである。反対に、第2の強プルアップバス246の第1のトランジスタ248はオンであり、また、第2のトランジスタ250はオフである。

【0027】

入力202がロー信号からハイ信号(例えばVssからVddLまで)まで遷移する場合、第1の弱状態保持バス206の強nチャネルトランジスタ224はオンとなり、第1のノード223を高電圧状態(例えばVddH)から低電圧状態(例えばVss)にする。遷移の間、弱pチャネルトランジスタ220および222はVddHとVddLによって決定された状態で動作する。弱pチャネルトランジスタ222はオンでありうるが、nチャネルトランジスタ234に逆らって(fighting)高電圧状態で第1のノードにバイアスをかけ、より強いnチャネルトランジスタ224は低電圧状態に第1のノードを引く(pull)。同様に、第2の弱状態保持バス208の強nチャネルトランジスタ234がオフになると、第2のノード233を低電圧から高電圧にするが、その遷移は、弱pチャネルトランジスタ232による電流フロー(current flow)によって制限されている。

【0028】

しかしながら、第1のノード223がロー状態に遷移する場合、第2の強プルアップバス246の強pチャネルトランジスタ250はオンにされ、一方、トランジスタ248もオンのままである。したがって、電流は、強nチャネルトランジスタ234をチャージするため第2の強プルアップ電流バス246を介して流れる。第1のノード223がロー状態に遷移する場合、出力インバータ266は、ロー状態からハイ状態に遷移する。これは、トランジスタ248の制御端子へ制御バス212を介して提供され、第2の強プルアップバス246をオフにする。

【0029】

ハイ信号(例えばVddL)が入力202で維持されるとき、弱状態保持バス206の第1の強nチャネルトランジスタ224はオンのままであり、弱pチャネルトランジスタ220および222はオフであり、低電圧(例えばVddL)で第1のノード223にバイアスをかける。出力インバータ266は高電圧(例えばVddH)を出力する。第2の弱状態保持バス208の強nチャネルトランジスタ234はオフであり、高電圧で第2のノード233にバイアスをかける。電圧プルアップ論理回路210では、第1の強プルアップバス241の第1のトランジスタ242はオンであり、また、第2のトランジスタ244はオフである。反対に、第2の強プルアップバス246の第1のトランジスタ248は

オフであり、また、第2のトランジスタ250はオンである。

【0030】

入力202がハイ信号からロー信号(例えばVddLからVssまで)に遷移する場合、インバータ207の出力はロー状態からハイ状態に遷移して、第2の弱状態保持バス208の強nチャネルトランジスタ234をオンにし、また、第2のノード233を高電圧状態から低電圧状態にする。遷移の間、弱pチャネルトランジスタ230および232はVddHとVddLによって決定された状態で動作する。弱pチャネルトランジスタ232がオンである可能性がありうるが、nチャネルトランジスタ234に逆らって高電圧状態で第2のノードにバイアスをかけ、より強いnチャネルトランジスタ234が低電圧状態に第2のノードを引く(pull)。

【0031】

第2のノード233が低電圧状態に遷移する場合、第1の強プルアップバス241の強pチャネルトランジスタ244はオンにされ、一方、トランジスタ242はオンのままである。さらに、弱pチャネルトランジスタ220もオンにされる。したがって、電流は、第1の強プルアップ電流バス241およびさらに第1のノード222をチャージするための第1の弱状態保持バス206を介して流れ、一方、強nチャネルトランジスタ224はオフされる。第1のノード223がハイ状態に遷移する場合、出力インバータ266はハイ状態からロー状態に遷移する。これは、トランジスタ242の制御端子へ、制御バス212およびインバータ270を介して提供され、第1の強プルアップバス241をオフにする。

【0032】

したがって、入力202の遷移の間、ハイ状態からロー状態へのノード223および233のうちの1つの初期遷移は、それぞれの弱pチャネルトランジスタ220-222か230-232によって制限され、しかし、ロー状態からハイ状態への他方のノード223あるいは233の遷移は、電圧プルアップ制御回路210によって支援される。入力202がハイまたはロー信号で保持される場合、電圧プルアップ制御回路210はオフであり、また、互いに連結された弱状態保持バス206および208は、入力202での低電圧入力範囲に感度が良いままである。遷移が入力202で生じる場合、電圧プルアップ論理回路210は、新しい状態への遷移を加速するために、弱状態保持バス206および208への電流を供給するためにアクティブにする。電圧プルアップ論理回路210は、出力204で遷移を示す制御バス212に応じて非アクティブにする。したがって電圧プルアップ論理回路210は、入力202に応じて状態間の弱状態保持バス206と208遷移を支援するために電流のパルスを提供する。電圧プルアップ論理回路210を選択的にアクティブにすることによって、広範囲の入力動作電圧および速い出力レベル遷移は、レベルシフティング回路装置200によって両方とも提供される。

【0033】

図3は、レベルシフティング回路装置を含むシステム300の特定の実例となる実施例のプロック図である。機構(structure)302は、メモリセル選択信号を受け取るために連結された第1の入力304を含む。第2の入力306はデータ信号を受け取るために連結される。第1の入力304は第1のレベルシフティング回路308に提供され、また、第2の入力306は第2のレベルシフティング回路310に提供される。メモリアレイ312は第1のレベルシフティング回路308および第2のレベルシフティング回路310の出力を受け取るために連結される。機構302は第1の電圧レベルVstructで動作し、また、メモリアレイ312は第2の電圧レベルVarrayで動作する。

【0034】

第1のレベルシフティング回路308は、第1の入力304を受け取るための入力320、および、メモリアレイ312へ第1のレベルシフトされた電圧信号を供給するための出力321を含む。第1のレベルシフティング回路308は、入力320および出力321に連結された、第1の弱状態保持バス322を含む。第1の弱状態保持バス322は、第2の弱状態保持バス326のような相互連結回路にさらに連結される。電圧プルアップ

論理回路 328 は、第1の弱状態保持バス 322 および第2の弱状態保持バス 326 に連結される。制御バス 324 は、電圧プルアップ論理回路 328 の動作を選択的に制御するために、電圧プルアップ論理回路 328 に連結される。特定の実施例では、第1のレベルシフティング回路 308 は、図 1-2 に例証されたレベルシフティング回路装置 100 あるいは 200 を含みうる。

#### 【0035】

第2のレベルシフティング回路 310 は、第2の入力 306 を受け取るための入力 330、および、メモリアレイ 312 へ第1のレベルシフト電圧信号を提供するための出力 331 を含む。特定の実施例では、第2のレベルシフティング回路 310 は、入力 330 および出力 331 に連結された、第1の弱状態保持バス 332 を含む。第1の弱状態保持バス 332 は、第2の弱状態保持バス 336 のような相互連結回路にさらに連結される。電圧プルアップ論理回路 338 は、第1の弱状態保持バス 332 および第2の弱状態保持バス 336 に連結される。制御バス 334 は、電圧プルアップ論理回路 338 のアクティブ化を選択的に制御するために、電圧プルアップ論理回路 338 に連結される。特定の実施例では、第2のレベルシフティング回路 310 は、図 1-2 に例証された、レベルシフティング回路装置 100 あるいは 200 を含みうる。

#### 【0036】

動作中に、第1の入力 304 および第2の入力 306 の少なくとも1つは、Vstruct のような第1の電圧レベルにあるかもしれないが、メモリアレイ 312 は、Varray のような第2の電圧レベルで電源によって電力が供給されうる。例えば、第1の電圧レベルは第2の電圧レベル未満でありうる。レベルシフティング回路 306 と 308 は、入力 304 および 306 での電圧レベルを、メモリアレイ 312 に関して適切な電圧レベルへシフトさせうる。特定の実施例では、レベルシフティング回路 306 と 308 は、制御バス 324 および 334 によって選択的にアクティブにされる、プルアップ論理回路 328 および 338 をそれぞれ含み、従って、入力信号の変更に応じて速い遷移を可能にし、さらに広範囲の動作を可能にする。例えば、レベルシフティング回路 306 および 308 は 0.6-1.4V を含む電圧範囲において動作可能でありうる。

#### 【0037】

図 4 は、図 1-3 に例証された回路装置のような回路装置を使用する、レベルシフティングの方法の特定の実例となる実施例のフロー図である。402 で、入力電圧は、電圧プルアップ論理を含むレベルシフティング回路への入力で受け取られる。特定の実施例では、入力信号は第1の弱状態保持バスに適用される。第1の弱状態保持バスは、直列配列された強nチャネルトランジスタ、および多数の弱pチャネルトランジスタを含みうる。

#### 【0038】

404 へ移動して、出力信号はレベルシフティング回路から提供される。特定の実施例では、入力信号は第1の電圧を有し、また、出力信号は第2の電圧を有する。406 へ進んで、レベルシフティング回路の電圧プルアップ論理回路は、選択的にアクティブにされる。特定の実施例では、電圧プルアップ論理回路は、弱状態保持バスの遷移時間を減少させるために電荷 (charge) を提供する。

#### 【0039】

408 へ継続して、特定の実施例では、制御信号は電圧プルアップ論理回路に提供される。制御信号は出力信号に反応するフィードバック信号でありうる。特定の実施例では、制御信号は、電圧プルアップ論理回路が弱状態保持バスをチャージするのを中止することを引き起こす。特定の実施例では、電圧プルアップ論理回路の出力は入力信号に応じて開始して制御信号に応じて終了する電流パルスを含む。

#### 【0040】

図 5 は、図 1-4 に記述された回路と方法の実施例が使用される代表的なモバイル通信装置 500 のブロック図である。通信装置 500 は、デジタル信号プロセッサ (DSP) 510 のようなプロセッサを含む。電圧プルアップ論理 564 を備えたレベルシフティング回路は、DSP 510 とメモリデバイス 532 の間の電圧レベルシフトを提供する

ために、D S P 5 1 0 に連結される。実例となる実施例では、電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路は、図 1 - 3 に例証された回路装置 1 0 0 、 2 0 0 、 3 0 8 、あるいは 3 1 0 を含む。実例となる実施例では、電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路は、図 4 に例証された方法を行なう。

【 0 0 4 1 】

図 5 は、デジタル信号プロセッサ 5 1 0 およびディスプレイ 5 2 8 に連結されるディスプレイ制御装置 5 2 6 をさらに示す。コーダ / デコーダ ( コーデック ) 5 3 4 は、デジタル信号プロセッサ 5 1 0 にさらに連結されうる。スピーカ 5 3 6 およびマイクロフォン 5 3 8 はコーデック 5 3 4 に連結されうる。

【 0 0 4 2 】

図 5 は、無線制御装置 5 4 0 がデジタル信号プロセッサ 5 1 0 および無線アンテナ 5 4 2 に連結されうることをさらに示す。特定の実施例では、入力装置 5 3 0 および電源 5 4 4 はオンチップシステム 5 2 2 に連結される。さらに、特定の実施例中で、図 5 に例証されるように、ディスプレイ 5 2 8 、入力装置 5 3 0 、スピーカ 5 3 6 、マイクロフォン 5 3 8 、無線アンテナ 5 4 2 、および電源 5 4 4 は、オンチップシステム 5 2 2 の外側にある。しかしながら、各々は、インターフェースまたはコントローラのようなオンチップシステム 5 2 2 のコンポーネントに連結されるだろう。

【 0 0 4 3 】

電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路が、D S P 5 1 0 とメモリデバイス 5 3 2 の間のレベルシフトを提供するために連結されるように表現されているが、電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路は、異なる電圧レベルを使用する通信装置 5 0 0 の他のコンポーネント間のレベルシフティングを提供するためにも使用されうる。例えば、電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路は、オンチップシステム 5 2 2 と、ディスプレイ 5 2 8 、入力装置 5 3 0 、スピーカ 5 3 6 、マイクロフォン 5 3 8 、無線アンテナ 5 4 2 、電源 5 4 4 、あるいはそれの任意の組み合わせとの間に連結されうる。別の例として、電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路は、D S P 5 1 0 とオンチップシステム 5 2 2 のその他任意のコンポーネントとの間で連結されうる。さらに別の例として、電圧プルアップ論理 5 6 4 を備えたレベルシフティング回路は、D S P 5 1 0 の内の低電圧レベルで動作するレジスタファイルにおいてのように、D S P 5 1 0 のコンポーネントに関してレベルシフティングを供給するために、D S P 5 1 0 に一体化されうる。

【 0 0 4 4 】

開示されたシステムや方法と共に、電圧レベルシフティングは、例えば図 1 - 3 に例証された、入力 1 0 2 、 2 0 2 、 3 2 0 および 3 3 0 のような、電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取るための手段を含む装置によって行なわれうる。その装置は、例えば図 1 - 3 に例証されるような、出力 1 0 4 、 2 0 4 、 3 2 1 および 3 3 1 、ならびにそれぞれの出力に連結された対応する回路機構のようなレベルシフティング回路からの出力信号を提供するための手段をさらに含みうる。その装置は、図 1 - 3 に例証されるように、制御バス 1 1 2 、 2 1 2 、 3 2 4 および 3 3 4 のようなレベルシフティング回路の電圧プルアップ論理回路を選択的にアクティブにするための手段をさらに含みうる。

【 0 0 4 5 】

当業者は更に、本明細書において開示された実施例に関連して記載された、実例となる様々な論理ブロック、構造、モジュール、回路、及びアルゴリズムステップが、電子工学的ハードウェア、コンピュータソフトウェア、又はそれらの組合せとして実現されうることをよく理解するであろう。ハードウェアとソフトウェアとの相互置換性を明確に説明するために、様々な実例となる構成要素、ブロック、構造、モジュール、回路、及びステップが、それらの機能の観点から一般的に説明された。このような機能が、ハードウェアとして実現されるかソフトウェアとして実現されるかは、システム全体に課された設計制約及び特定のアプリケーションによる。当業者は、各特定のアプリケーションのために上述

した機能を様々な方法で実現することができるが、このような実現の決定は、本開示の範囲から逸脱させるものとして解釈されてはならない。

#### 【0046】

本明細書において開示された実施例に関連して記述された方法やアルゴリズムのステップは、ハードウェアによって直接、プロセッサによって実行されるソフトウェア・モジュールによって、又は、これらの組み合わせによって具現化されうる。ソフトウェア・モジュールは、RAMメモリ、フラッシュ・メモリ、ROMメモリ、PROMメモリ、EPRROMメモリ、EEPROMメモリ、レジスタ、ハード・ディスク、リムーバブル・ディスク、CD-ROM、あるいは当該技術分野で知られているその他任意の形式の記憶媒体に収納されうる。典型的な記憶媒体は、プロセッサがそこから情報を読み取り、またそこに情報を書き込むことができるよう、プロセッサに連結されるか、あるいは記憶媒体はプロセッサに統合されうる。このプロセッサと記憶媒体とは、ASIC内に存在することができる。ASICは、コンピュータ装置またはユーザ端末内に存在することができる。あるいはこのプロセッサと記憶媒体とは、コンピュータ装置またはユーザ端末内のディスクリートコンポーネントとして存在することができる。

#### 【0047】

本開示された実施例における上記記載は、当業者をして、本開示された実施例の製造又は利用を可能とするために提供される。これらの実施例への様々な変形例もまた、当業者には明らかであり、本明細書で定義された一般原理は、本発明の精神又は範囲から逸脱することなく他の実施形態にも適用されうる。従って現在の開示は、本明細書で示された実施例に限定することは意図されておらず、以下の請求項によって定義される原理及び新規特徴と整合が取れた最も広い範囲と出来る限り一致するよう意図されている。

#### 【誤訳訂正2】

【訂正対象書類名】特許請求の範囲

【訂正対象項目名】全文

【訂正方法】変更

【訂正の内容】

【特許請求の範囲】

【請求項1】

入力電圧信号を受け取るための入力と、

レベルシフトされた電圧信号を提供するための出力と、

前記入力に連結された第1の弱状態保持バスと、

前記出力に連結された第2の弱状態保持バスと、

前記第1の弱状態保持バスおよび前記第2の弱状態保持バスに連結された電圧プルアップ論理回路と、

前記電圧プルアップ論理回路のアクティピ化を選択的に制御するために前記電圧プルアップ論理回路に連結された制御バスと

を具備する回路装置。

【請求項2】

前記制御バスは、前記出力から前記電圧プルアップ論理回路までの自己調時式フィードバックバスをさらに具備する請求項1の回路装置。

【請求項3】

前記制御バスは、前記電圧プルアップ論理回路に前記入力を連結する請求項1の回路装置。

【請求項4】

前記制御バスは、タイミング遅れを提供するための遅れ論理回路を具備する請求項3の回路装置。

【請求項5】

前記遅れ論理回路は、調整可能遅れコンポーネントを具備する請求項4の回路装置。

【請求項6】

前記第1の弱状態保持バスは、

電源電圧に連結された第1の端子、前記第2の弱状態保持バスに連結された制御端子、および第3の端子を具備する第1の弱pチャネルトランジスタと、

前記第3の端子に連結された第4の端子、前記入力に連結された第2の制御端子、および前記電圧プルアップ論理回路に連結されたノードに連結された第5の端子を含む第2の弱pチャネルトランジスタと、

前記ノードに連結された第6の端子、前記入力に連結された第3の制御端子、および第2の電源電圧に連結された第7の端子を含む強nチャネルトランジスタとをさらに具備する請求項1の回路装置。

【請求項7】

前記第2の弱状態保持バスは、直列配列された強nチャネルトランジスタ、および多数の弱pチャネルトランジスタを具備する請求項1の回路装置。

【請求項8】

前記電圧プルアップ論理回路は、

少なくとも1つの第1のトランジスタを含む第1の強プルアップバス、および、少なくとも1つの第2のトランジスタを含む第2の強プルアップバスを具備し、前記少なくとも1つの第2のトランジスタは、前記少なくとも1つの第1のトランジスタに連結される請求項1の回路装置。

【請求項9】

前記第1の強プルアップバスおよび前記第2の強プルアップバスはインバータによって連結される請求項8の回路装置。

【請求項10】

前記第1の弱状態保持バスおよび前記第2の弱状態保持バスはインバータによって連結される請求項1の回路装置。

【請求項11】

前記第1の弱状態保持バスは第2の強プルアップバスに連結され、また、前記第2の弱状態保持バスは前記第1の強プルアップバスに連結される請求項10の回路装置。

【請求項12】

前記制御バスは、前記第2の弱状態保持バスのエレメントに連結されるインバータの出力に連結される請求項1の回路装置。

【請求項13】

メモリアレイと、

第1のレベルシフティング回路によって前記メモリアレイに連結された第1の入力と、

第2のレベルシフティング回路によって前記メモリアレイに連結された第2の入力とを具備し、

前記第1のレベルシフティング回路は、

前記第1の入力を受け取るための入力と、

前記メモリアレイへ第1のレベルシフトされた電圧信号を供給するための出力と、

前記入力と前記出力に連結された第1の弱状態保持バスと、

前記第1の弱状態保持バスに連結された相互連結回路と、

前記第1の弱状態保持バスに連結された電圧プルアップ論理回路と、

前記電圧プルアップ論理回路のアクティブ化を選択的に制御するために前記電圧プルアップ論理回路に連結された制御バスとを具備するシステム。

【請求項14】

前記相互連結回路は第2の弱状態保持バスを含む請求項13のシステム。

【請求項15】

前記メモリアレイは、第2の電圧レベルで電源によって電力供給され、また、前記第1の入力および前記第2の入力の少なくとも1つは第1の電圧レベルにある請求項13のシステム。

**【請求項 1 6】**

前記第1の電圧レベルは前記第2の電圧レベル未満である請求項15のシステム。

**【請求項 1 7】**

電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取ることと、

前記レベルシフティング回路からの出力信号を提供することと、

前記レベルシフティング回路の前記電圧プルアップ論理回路を選択的にアクティブにすることとを具備する方法。

**【請求項 1 8】**

前記電圧プルアップ論理回路に制御信号を供給することをさらに具備する請求項17の方法。

**【請求項 1 9】**

前記制御信号は前記出力信号に応答するフィードバック信号である請求項18の方法。

**【請求項 2 0】**

前記入力信号は第1の電圧を有し、前記出力信号は第2の電圧を有する請求項17の方法。

**【請求項 2 1】**

前記入力信号は第1の弱状態保持バスに適用される請求項17の方法。

**【請求項 2 2】**

前記第1の弱状態保持バスは、直列配列された強nチャネルトランジスタ、および多数の弱pチャネルトランジスタを具備する請求項21の方法。

**【請求項 2 3】**

電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取るための手段と、

前記レベルシフティング回路からの出力信号を提供するための手段と、

前記レベルシフティング回路の前記電圧プルアップ論理回路を選択的にアクティブにするための手段と

を具備する装置。

**【請求項 2 4】**

前記電圧プルアップ論理回路に制御信号を供給するための手段をさらに具備する請求項23の装置。

**【請求項 2 5】**

前記制御信号は前記出力信号に応答するフィードバック信号である請求項24のデバイス。

**【誤訳訂正3】**

【訂正対象書類名】図面

【訂正対象項目名】全図

【訂正方法】変更

【訂正の内容】

【図1】

図1

100

【図2】

図2

200

FIG. 2

FIG. 1

【図3】

図3

300

【図4】

図4

FIG. 4

FIG. 3

【図5】

図5

500

FIG. 5