(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5882579号

(P5882579)

(45) 発行日 平成28年3月9日(2016.3.9)

(24) 登録日 平成28年2月12日(2016.2.12)

(51) Int.Cl.

F 1

H01L 21/76 (2006.01)

H01L 21/322 (2006.01)H01L 21/76

H01L 21/322L

P

請求項の数 9 (全 19 頁)

(21) 出願番号 特願2010-278395 (P2010-278395)

(22) 出願日 平成22年12月14日 (2010.12.14)

(65) 公開番号 特開2012-129312 (P2012-129312A)

(43) 公開日 平成24年7月5日 (2012.7.5)

審査請求日 平成25年12月16日 (2013.12.16)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置の製造方法であって、

第1面および第2面を有する半導体基板の前記第1面および前記第2面の上に第1絶縁膜を形成する第1絶縁膜形成工程と、

前記第1面および前記第2面のうち前記第2面の側の前記第1絶縁膜を除去する第1絶縁膜除去工程と、

前記第1面の側の前記第1絶縁膜および前記半導体基板の前記第2面の上にポリシリコン膜を形成するポリシリコン膜形成工程と、

前記第1面の側および前記第2面の側の前記ポリシリコン膜の上に第2絶縁膜を形成する第2絶縁膜形成工程と、

開口を有するマスクを使って前記第1面の側の前記第2絶縁膜をエッチングする処理を含み、前記半導体基板の前記第1面における前記開口によって規定される領域に素子分離を形成する素子分離形成工程と、

前記素子分離形成工程の後に前記第1面の側および前記第2面の側の前記第2絶縁膜を除去する第2絶縁膜除去工程と、

前記第2面の側の前記ポリシリコン膜を残しながら前記第1面の側の前記ポリシリコン膜を除去するポリシリコン膜除去工程と、

前記ポリシリコン膜形成工程の後であって前記ポリシリコン膜除去工程の前に、前記第2面の側の前記ポリシリコン膜の上に保護膜を形成する保護膜形成工程と、

10

20

を含むことを特徴とする半導体装置の製造方法。

**【請求項 2】**

半導体装置の製造方法であって、

第1面および第2面を有する半導体基板の前記第1面および前記第2面の上に第1絶縁膜を形成する第1絶縁膜形成工程と、

前記第1面および前記第2面のうち前記第2面の側の前記第1絶縁膜を除去する第1絶縁膜除去工程と、

前記第1面の側の前記第1絶縁膜および前記半導体基板の前記第2面の上にポリシリコン膜を形成するポリシリコン膜形成工程と、

前記第1面の側および前記第2面の側の前記ポリシリコン膜の上に保護膜を形成する保護膜形成工程と、前記第1面の側および前記第2面の側の前記保護膜の上に第2絶縁膜を形成する第2絶縁膜形成工程と、

開口を有するマスクを使って前記第1面の側の前記第2絶縁膜をエッチングする処理を含み、前記半導体基板の前記第1面における前記開口によって規定される領域に素子分離を形成する素子分離形成工程と、

前記素子分離形成工程の後に前記第1面の側および前記第2面の側の前記第2絶縁膜を除去する第2絶縁膜除去工程と、

前記第2絶縁膜除去工程の後に前記第2面の側の前記ポリシリコン膜を残しながら前記第1面の側の前記ポリシリコン膜を除去するポリシリコン膜除去工程と、

を含むことを特徴とする半導体装置の製造方法。

10

**【請求項 3】**

半導体装置の製造方法であって、

第1面および第2面を有する半導体基板の前記第1面および前記第2面の上に第1絶縁膜を形成する第1絶縁膜形成工程と、

前記第1面および前記第2面のうち前記第2面の側の前記第1絶縁膜を除去する第1絶縁膜除去工程と、

前記第1面の側の前記第1絶縁膜および前記半導体基板の前記第2面の上にポリシリコン膜を形成するポリシリコン膜形成工程と、

前記第1面の側および前記第2面の側の前記ポリシリコン膜の上に保護膜を形成する保護膜形成工程と、前記第1面の側の前記保護膜を除去する保護膜除去工程と、

30

前記第1面の側の前記ポリシリコン膜の上および前記第2面の側の前記保護膜の上に第2絶縁膜を形成する第2絶縁膜形成工程と、

開口を有するマスクを使って前記第1面の側の前記第2絶縁膜をエッチングする処理を含み、前記半導体基板の前記第1面における前記開口によって規定される領域に素子分離を形成する素子分離形成工程と、

前記素子分離形成工程の後に前記第1面の側および前記第2面の側の前記第2絶縁膜を除去する第2絶縁膜除去工程と、

前記第2絶縁膜除去工程の後に前記第2面の側の前記ポリシリコン膜を残しながら前記第1面の側の前記ポリシリコン膜を除去するポリシリコン膜除去工程と、

を含むことを特徴とする半導体装置の製造方法。

40

**【請求項 4】**

半導体装置の製造方法であって、

第1面および第2面を有する半導体基板の前記第1面および前記第2面の上に第1絶縁膜を形成する第1絶縁膜形成工程と、

前記第1面および前記第2面のうち前記第2面の側の前記第1絶縁膜を除去する第1絶縁膜除去工程と、

前記第1面の側の前記第1絶縁膜および前記半導体基板の前記第2面の上にポリシリコン膜を形成するポリシリコン膜形成工程と、

前記第1面の側および前記第2面の側の前記ポリシリコン膜の上に第2絶縁膜を形成する第2絶縁膜形成工程と、

50

開口を有するマスクを使って前記第1面の側の前記第2絶縁膜をエッティングする処理を含み、前記半導体基板の前記第1面における前記開口によって規定される領域に素子分離を形成する素子分離形成工程と、

前記素子分離形成工程の後に前記第1面の側および前記第2面の側の前記第2絶縁膜を除去する第2絶縁膜除去工程と、

前記第2絶縁膜除去工程の後に前記第2面の側の前記ポリシリコン膜の上に保護膜を形成する保護膜形成工程と、

前記保護膜によって保護された前記第2面の側の前記ポリシリコン膜を残しながら前記第1面の側の前記ポリシリコン膜を除去するポリシリコン膜除去工程と、

を含むことを特徴とする半導体装置の製造方法。

10

**【請求項5】**

前記第1絶縁膜がシリコン酸化膜であり、前記第2絶縁膜がシリコン窒化膜であり、前記保護膜がシリコン酸化膜である、ことを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

**【請求項6】**

前記素子分離形成工程は、

前記マスクを使って前記半導体基板の前記第1面に溝を形成する工程と、

前記溝に絶縁体を充填する工程と、

CMP法により、前記第2絶縁膜が露出するまで、前記絶縁体を研磨する工程と、

を有することを特徴とする請求項5に記載の半導体装置の製造方法。

20

**【請求項7】**

前記保護膜は、50～200の範囲内の厚さを有するように形成され、

前記第2絶縁膜は1000～3000の範囲内の厚さを有するように形成される、

ことを特徴とする請求項5又は6に記載の半導体装置の製造方法。

**【請求項8】**

前記素子分離形成工程は、前記マスクを使って前記第2絶縁膜に酸化用開口部を形成し、前記酸化用開口部を通して前記第1面の側の前記ポリシリコン膜を酸化させるとともに前記半導体基板の前記第1面を部分的に酸化させる工程を含む、

ことを特徴とする請求項1乃至5に記載の半導体装置の製造方法。

**【請求項9】**

30

前記ポリシリコン膜除去工程において、前記第1面の側の前記ポリシリコン膜は、ウェットエッティングによって除去される

ことを特徴とする請求項1乃至8のいずれか1項に記載の半導体装置の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置の製造方法に関する。

**【背景技術】**

**【0002】**

半導体装置が形成されるべきシリコン基板には、半導体装置を製造する過程で、Fe(鉄)、Ni(ニッケル)などの金属不純物が混入することがある。金属不純物、特に重金属不純物がシリコン基板内で電気的に活性化されると、半導体装置の特性を著しく悪化させてしまう。

40

**【0003】**

特許文献1の段落0017-0020には、基板1の両面にシリコン酸化膜(2)を形成し、裏面のシリコン酸化膜(2)をエッティングにより除去し、基板の表面、裏面にそれぞれシリコン窒化膜(3、60)を形成することが開示されている。裏面に直接に形成されたシリコン窒化60膜は、金属不純物を除去するゲッタリングのための膜として機能する。特許文献1の段落0021-0024には、基板1の裏面に形成されたシリコン酸化膜(2)をエッティングにより除去し、基板の表面、裏面にそれぞれポリシリコン膜(50

50

、 55 ) を形成することが開示されている。裏面に直接に形成されたポリシリコン膜 ( 55 ) は、金属不純物を除去するゲッタリングのための膜として機能する。特許文献 1 に開示された上記の 2 つの方法は、半導体装置製造工程中 ( いわゆるインライン ) で、裏面にゲッタリング膜を形成することで、煩雑な工程を付加することなく、重金属不純物をゲッタリングする技術である ( 段落 0020 、 0024 ) 。

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献 1】特開平 7 - 7008 号公報**

**【発明の概要】**

10

**【発明が解決しようとする課題】**

**【0005】**

特許文献 1 に開示された製造方法に従って STI ( Shallow Trench Isolation ) などの素子分離を形成すると、ゲッタリング膜として形成した裏面側のポリシリコン膜が直ぐに除去されうる。素子分離の形成の際に裏面側のポリシリコン膜が直ぐに除去されてしまうと、十分なゲッタリング効果を得ることができない。

**【0006】**

本発明は、上記の課題認識を契機としてなされたものであり、ゲッタリングの効果を高めるために有利な技術を提供することを目的とする。

**【課題を解決するための手段】**

20

**【0007】**

本発明に係る半導体装置の製造方法は、第 1 面および第 2 面を有する半導体基板の前記第 1 面および前記第 2 面の上に第 1 絶縁膜を形成する第 1 絶縁膜形成工程と、前記第 1 面および前記第 2 面のうち前記第 2 面の側の前記第 1 絶縁膜を除去する第 1 絶縁膜除去工程と、前記第 1 面の側の前記第 1 絶縁膜および前記半導体基板の前記第 2 面の上にポリシリコン膜を形成するポリシリコン膜形成工程と、前記第 1 面の側および前記第 2 面の側の前記ポリシリコン膜の上に第 2 絶縁膜を形成する第 2 絶縁膜形成工程と、開口を有するマスクを使って前記第 1 面の側の前記第 2 絶縁膜をエッチングする処理を含み、前記半導体基板の前記第 1 面における前記開口によって規定される領域に素子分離を形成する素子分離形成工程と、前記素子分離工程の後に前記第 1 面の側および前記第 2 面の側の前記第 2 絶縁膜を除去する第 2 絶縁膜除去工程と、前記第 1 面および前記第 2 面のうち前記第 1 面の側の前記ポリシリコン膜を除去するポリシリコン膜除去工程と、前記ポリシリコン膜形成工程の後であって前記ポリシリコン膜除去工程の前に、前記ポリシリコン膜除去工程で前記第 2 面の側の前記ポリシリコン膜が除去されないように前記第 2 面の側の前記ポリシリコン膜を保護する保護膜を形成する保護膜形成工程とを含む。

30

**【発明の効果】**

**【0008】**

本発明によれば、ゲッタリングの効果を高めるために有利な技術を提供することができる。

**【図面の簡単な説明】**

40

**【0009】**

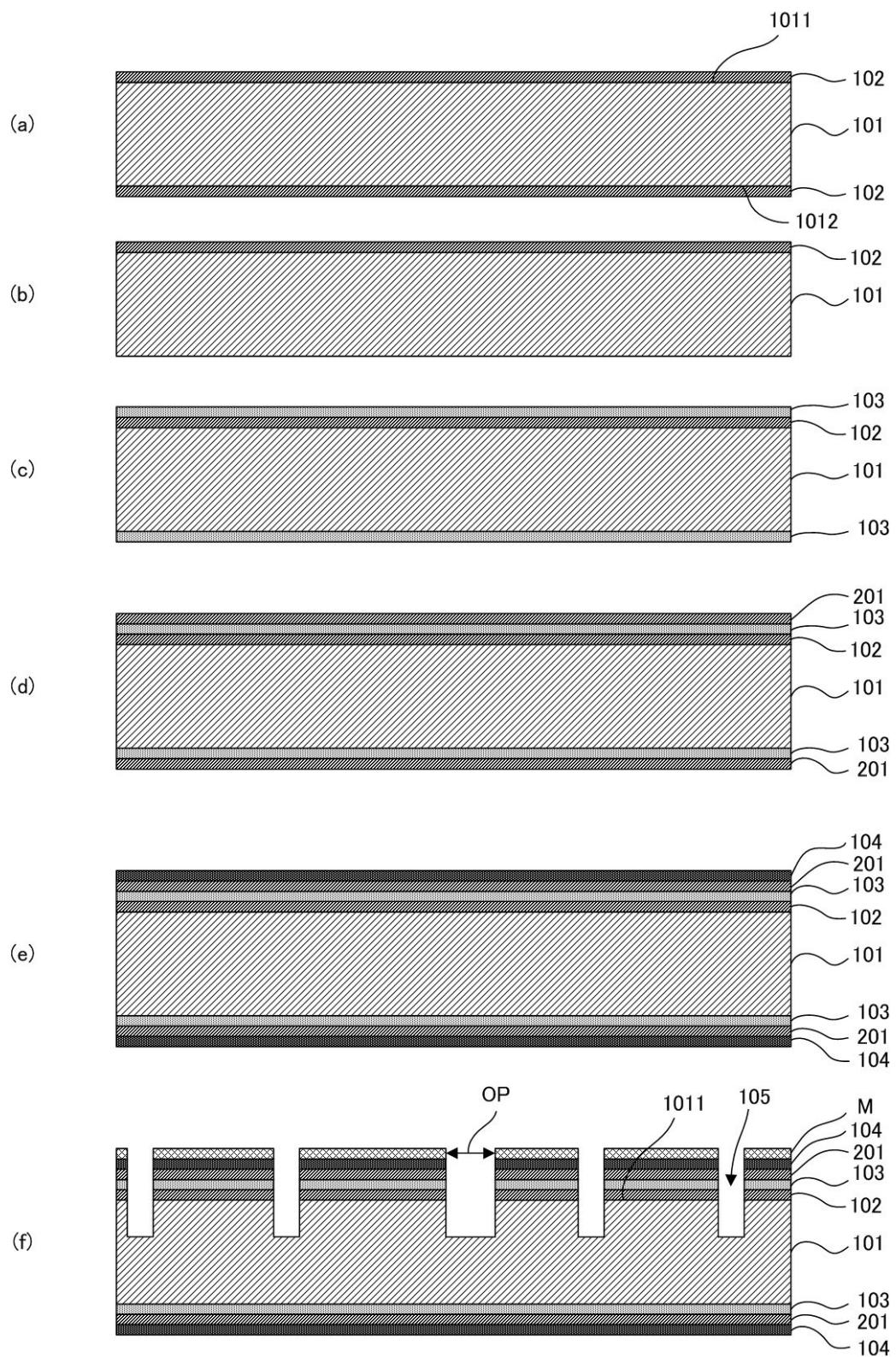

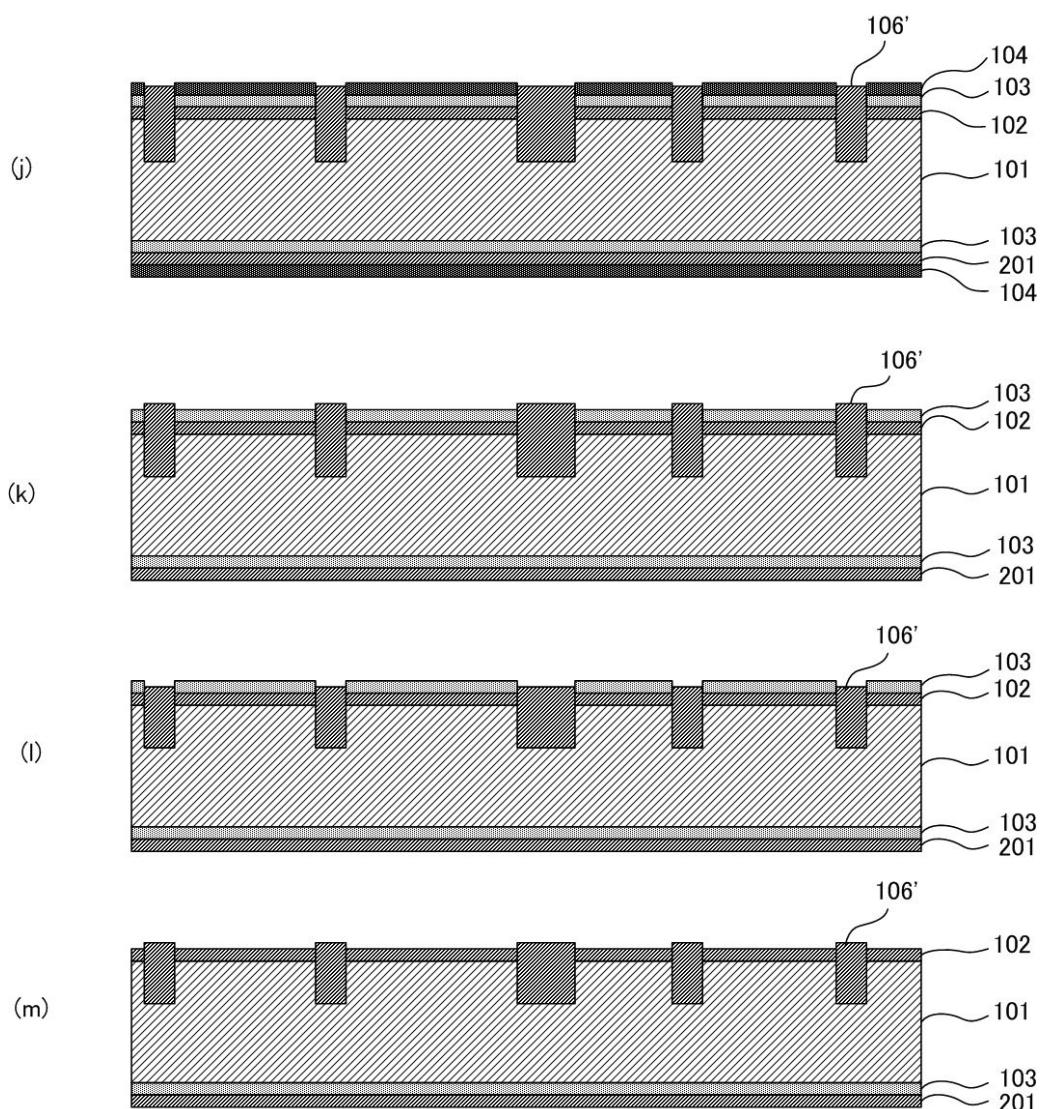

**【図 1】第 1 実施形態の半導体装置の製造方法を示す工程断面図。**

**【図 2】第 1 実施形態の半導体装置の製造方法を示す工程断面図。**

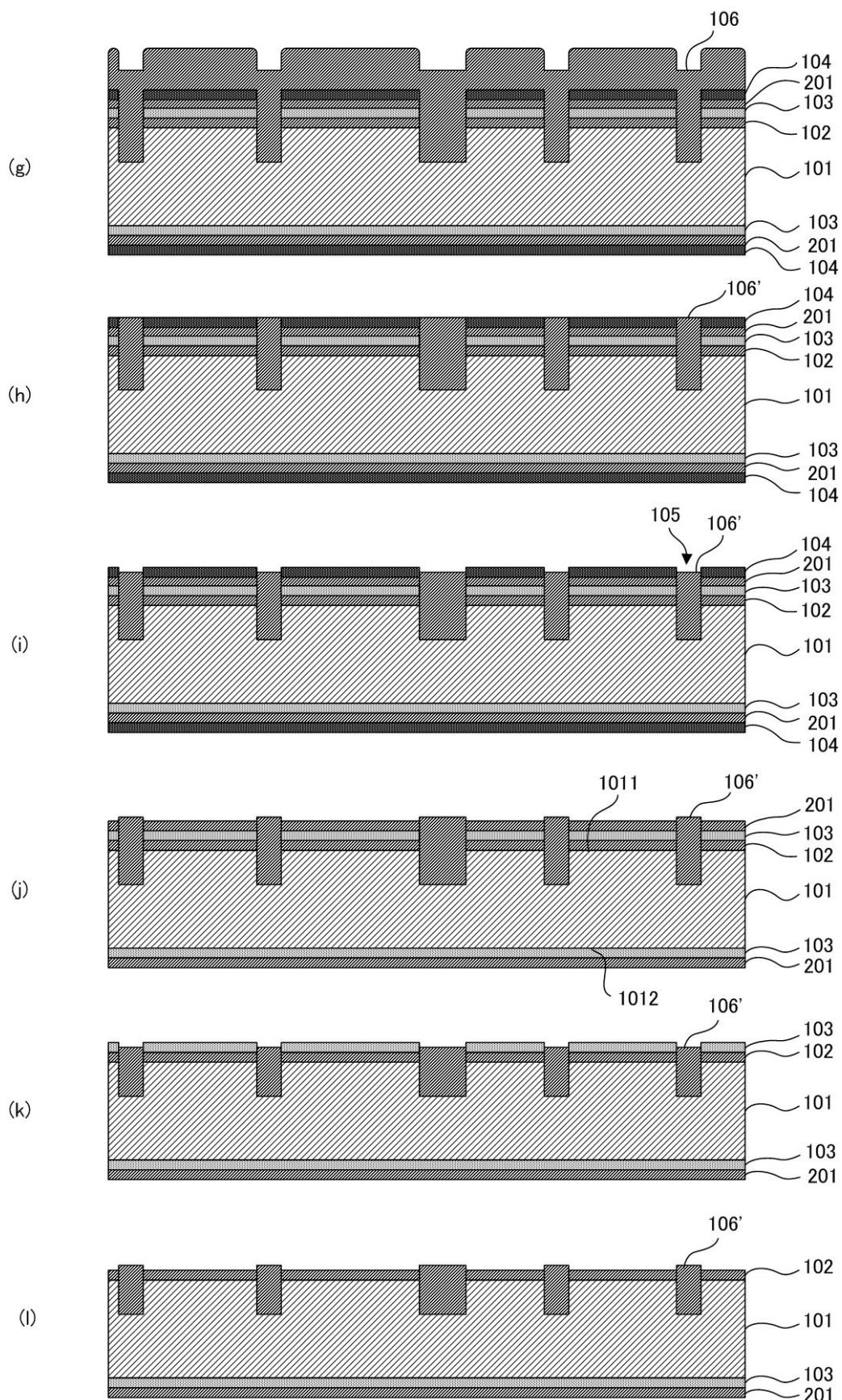

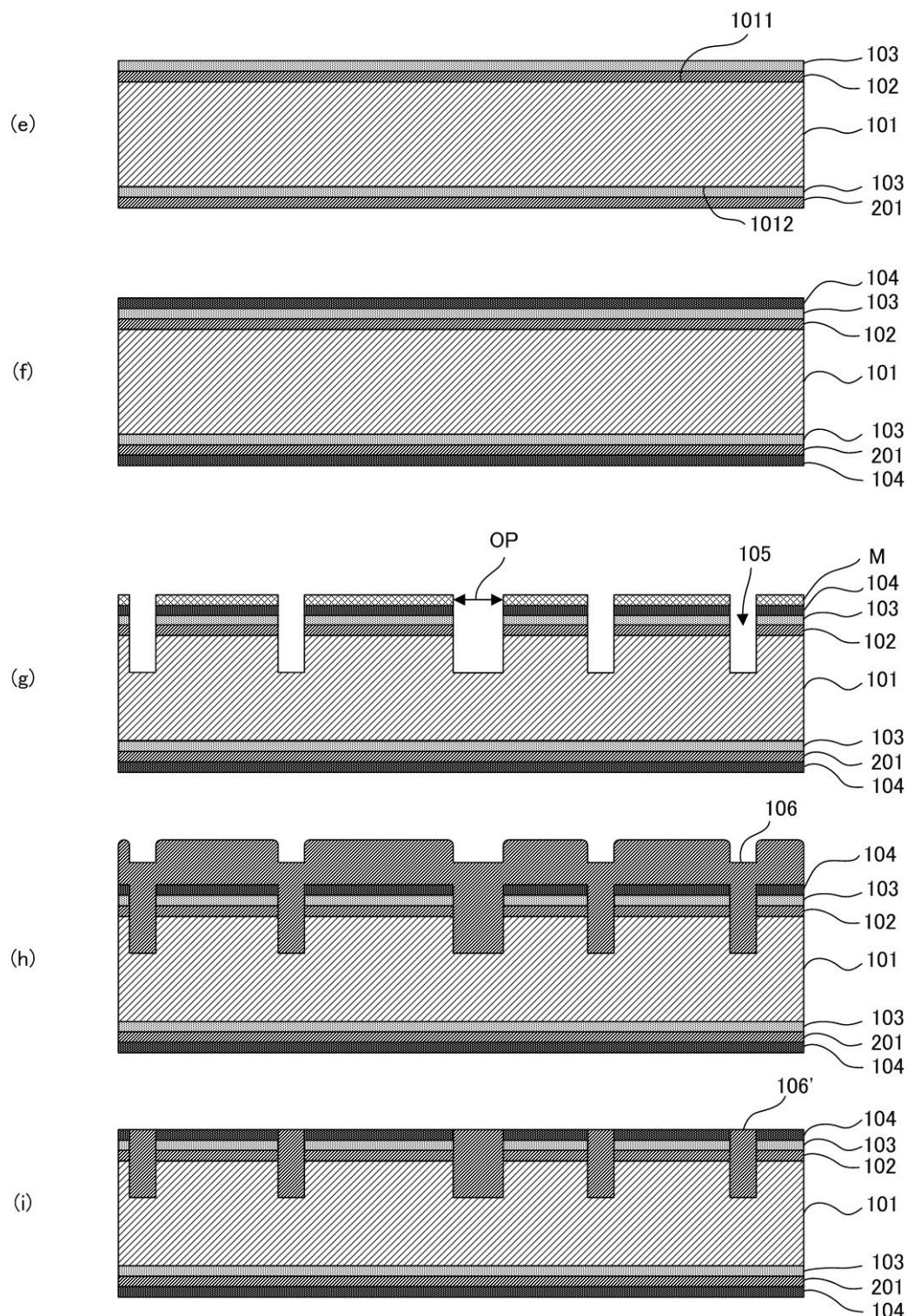

**【図 3】比較例の半導体装置の製造方法を示す工程断面図。**

**【図 4】比較例の半導体装置の製造方法を示す工程断面図。**

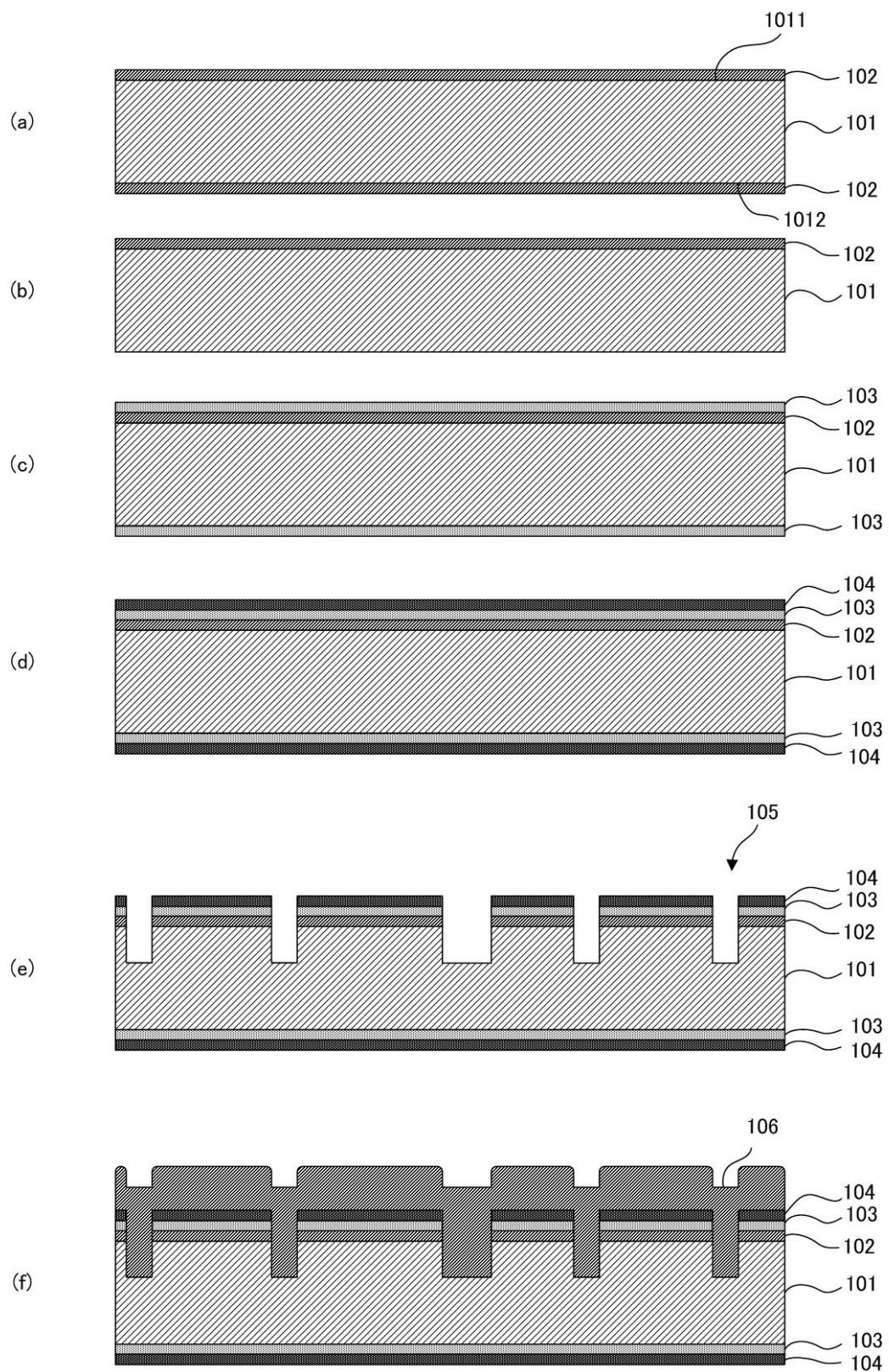

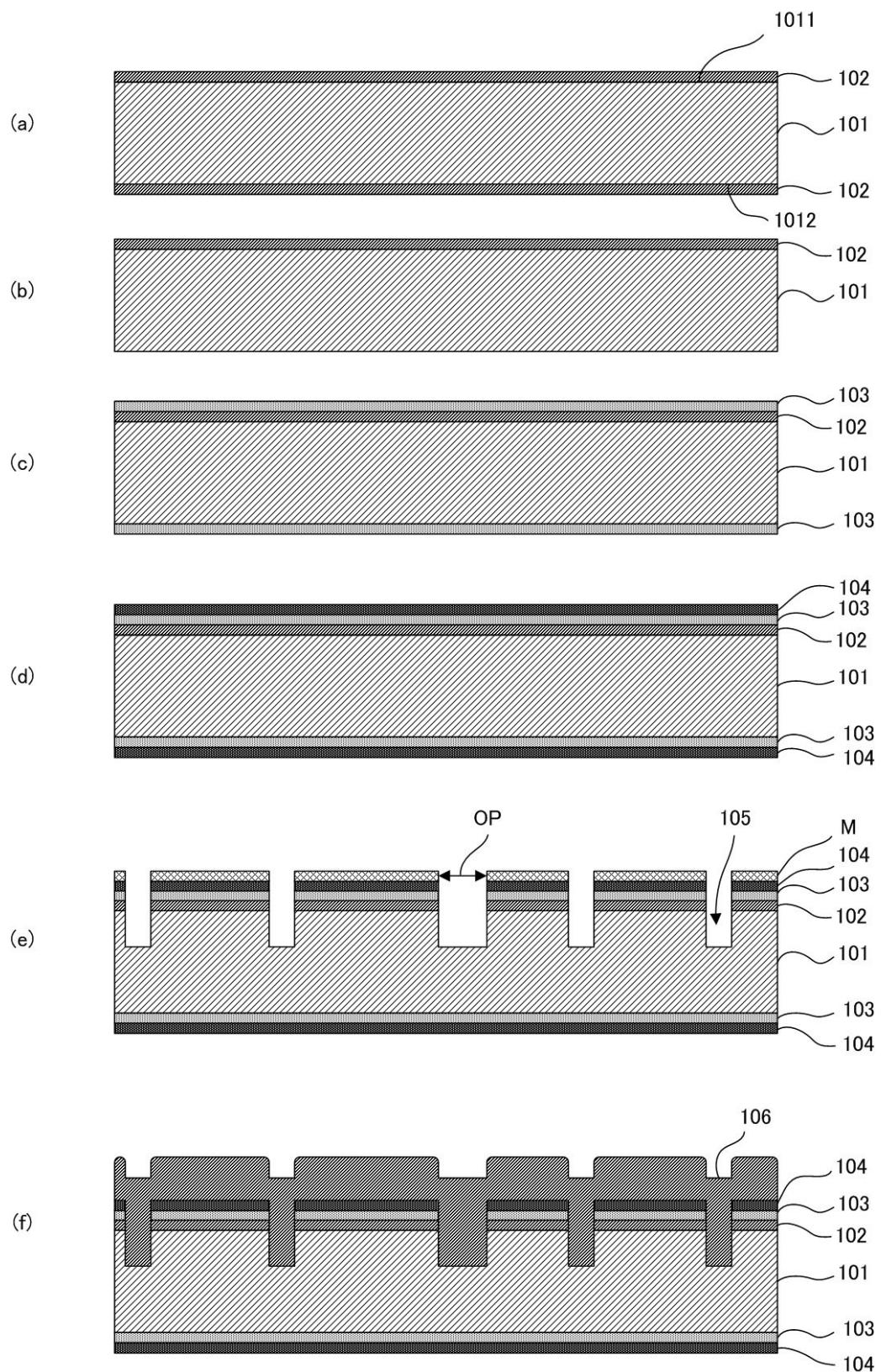

**【図 5】第 2 実施形態の半導体装置の製造方法を示す工程断面図。**

**【図 6】第 2 実施形態の半導体装置の製造方法を示す工程断面図。**

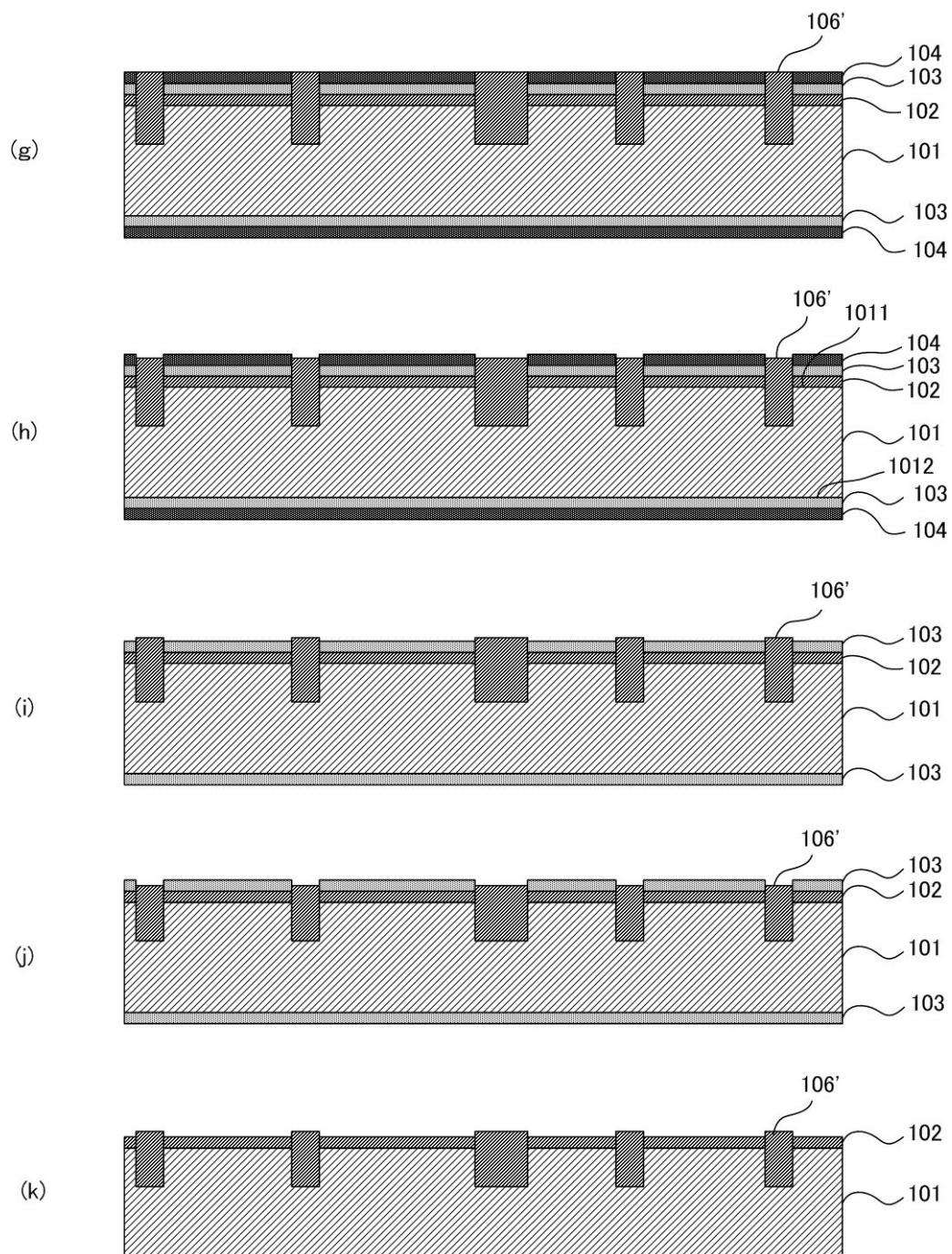

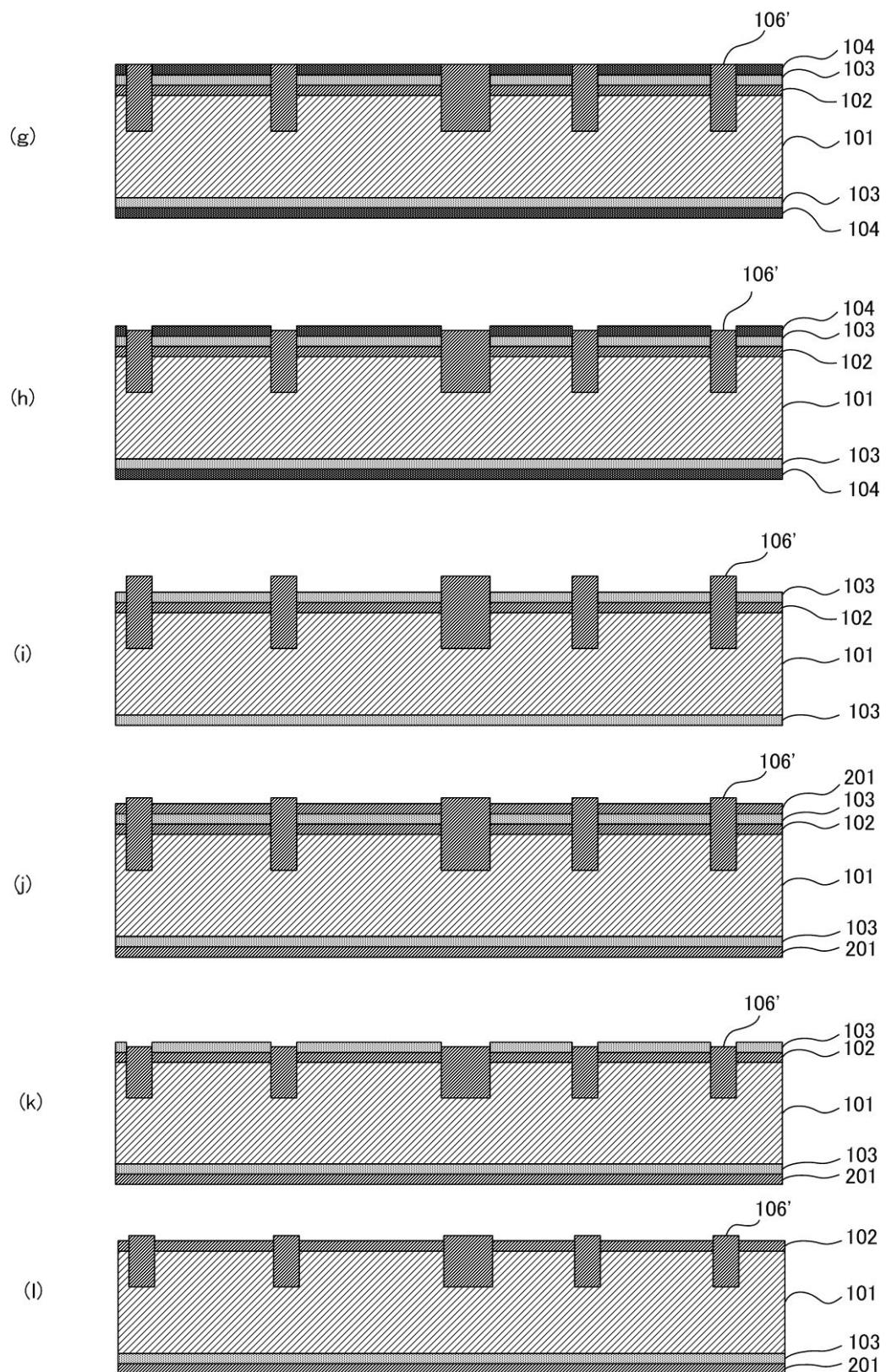

**【図 7】第 3 実施形態の半導体装置の製造方法を示す工程断面図。**

**【図 8】第 3 実施形態の半導体装置の製造方法を示す工程断面図。**

**【発明を実施するための形態】**

50

## 【0010】

本発明の実施形態を説明する前に、図3及び図4を参照しながら、比較例として、特許文献1に開示された技術を応用してSTI(Shallow Trench Isolation)法によりインラインで裏面にゲッタリング膜を形成する方法を説明する。まず、図3(a)に示す工程において、シリコン基板101の第1面(表面)1011および第2面(裏面)1012に、熱酸化法等により、シリコン酸化膜102を形成する。次いで、図3(b)に示す工程において、シリコン基板101の第1面1011および第2面1012のうち第2面1012のシリコン酸化膜102をエッチングにより除去する。次いで、図3(c)に示す工程において、第1面1011の側のシリコン酸化膜102およびシリコン基板101の第2面1012の上に、熱CVD法等により、ポリシリコン膜103を形成する。第2面1012の側に形成されるポリシリコン膜103は、シリコン基板101の第2面の上に直接に形成されており、後の工程において、ゲッタリング膜として作用する。

## 【0011】

次いで、図3(d)に示す工程において、第1面1011の側のポリシリコン膜103および第2面1012の側のポリシリコン膜103の上にシリコン窒化膜104を形成する。次いで、図3(e)に示す工程において、フォトリソグラフィーおよびドライエッチングにより、シリコン基板101に溝105を形成する。次いで、図3(f)に示す工程において、HDP(High Density Plasma)法等により、溝105が十分にシリコン酸化物(絶縁体)106によって充填されるようにシリコン酸化物106を形成する。次いで、図4(g)に示す工程において、CMP法により、シリコン窒化膜104が露出するまで、シリコン酸化物106を研磨して素子分離106'を形成する。

## 【0012】

次いで、図4(h)に示す工程において、シリコン窒化膜104の表面の薄い酸化膜を除去するために、HF(フッ化水素)水溶液等の薬液を用いてウェットエッチングを実施する。この工程により、溝105に充填されている素子分離106'の表面も僅かにエッチングされる。次いで、図4(i)に示す工程において、熱リン酸を用いたウェットエッチングにより、第1面1011の側および第2面1012の側のシリコン窒化膜104を除去する。次いで、図4(j)に示す工程において、第1面1011側のポリシリコン膜103の表面の薄い酸化膜を除去するために、HF水溶液等の薬液を用いてウェットエッチングを実施する。この工程により、溝105に充填されている素子分離106'の表面も僅かにエッチングされる。次いで、図4(k)に示す工程において、アルカリ系溶液等を用いたウェットエッチングにより、ポリシリコン膜103を除去する。この工程では、第1面の側のポリシリコン膜103とともに第2面の側のポリシリコン膜103も除去される。

## 【0013】

以上のように、図3および図4に示す比較例では、ゲッタリング膜として形成した第2面1012の側のポリシリコン膜103が図4(k)に示す工程で除去されてしまうので、十分なゲッタリング効果を得ることができない。

## 【0014】

なお、このような課題は、STIプロセスに限られるものではなく、ポリバッファLOCO法においても生じうる。ここで、ポリバッファLOCO法では、シリコン基板の上にシリコン酸化膜、ポリシリコン膜、シリコン窒化膜が順に形成される。その後、該シリコン窒化膜に開口が形成され、該開口を通して該ポリシリコンおよび該シリコン基板の表面を酸化させることによって素子分離用の酸化膜が形成される。ポリバッファLOCO法については、例えば、特開平3-187224号公報に記載されている。

## 【0015】

以下、図1および図2を参照しながら本発明の半導体装置の製造方法の第1実施形態を説明する。まず、図1(a)に示す工程(第1絶縁膜形成工程)において、第1面1011および第2面1012を有するシリコン基板(半導体基板)101の第1面1011お

10

20

30

40

50

および第2面1012の上にシリコン酸化膜(第1絶縁膜)102を形成する。シリコン酸化膜102は、例えば、酸化炉を使用し、酸化雰囲気中で、800～1000の範囲内の温度において形成されうる。シリコン酸化膜102は、例えば、100(オングストローム)～500の範囲内の厚さを有するように形成されうる。

#### 【0016】

次いで、図1(b)に示す工程(第1絶縁膜除去工程)において、シリコン基板101の第2面1012の側のシリコン酸化膜102を除去してシリコン基板101の第2面1012を露出させる。ここで、第1面1011および第2面1012のうち第2面1012の側のみをウェットエッティングすることによって、第2面1012の側のみ、シリコン酸化膜102を除去することができる。より具体的な方法を例示すれば、例えば、枚葉式洗浄装置を使用し、室温において、第2面1012の側のみを100:1程度の希釈HF水溶液によって処理することにより、第2面1012の側のみ、シリコン酸化膜102を除去することができる。

10

#### 【0017】

次いで、図1(c)に示す工程(ポリシリコン膜形成工程)では、シリコン基板101の第1面1011の側のシリコン酸化膜102およびシリコン基板101の第2面1012の上にポリシリコン膜103を形成する。ここで、ポリシリコン膜103は、第2面1012に接触するように形成される。ポリシリコン膜103は、例えば、減圧熱CVD装置を使用し、SiH<sub>4</sub>ガス雰囲気中で、530～650の範囲内の温度、10Pa～150Paの範囲内の圧力で形成されうる。ポリシリコン膜103は、例えば、200～1000Åの範囲内の厚さを有するように形成されうる。

20

#### 【0018】

次いで、図1(d)に示す工程(保護膜形成工程)では、第1面1011の側および第2面1012の側のポリシリコン膜103の上にシリコン酸化膜(保護膜)201を形成する。シリコン酸化膜201は、例えば、酸化炉を使用し、酸化雰囲気中で、800～1000の範囲内の温度で形成されうる。シリコン酸化膜201は、例えば、50～200の範囲内の厚さを有するように形成されうる。シリコン酸化膜201は、例えば、シリコン酸化膜形成用の減圧熱CVD装置を使用して形成されてもよい。シリコン酸化膜201は、ポリシリコン膜103を保護する保護膜として機能する。

30

#### 【0019】

次いで、図1(e)に示す工程(第2絶縁膜形成工程)において、第1面1011の側および第2面1012の側のポリシリコン膜103の上に、シリコン酸化膜201を介して、シリコン窒化膜(第2絶縁膜)104を形成する。シリコン窒化膜104は、例えば、減圧熱CVD装置を使用し、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>およびNH<sub>3</sub>の混合ガス雰囲気中で、650～850の範囲内の温度、10Pa～150Paの範囲内の圧力で形成されうる。シリコン窒化膜104は、例えば、1000～3000の範囲内の厚さを有するように形成されうる。

30

#### 【0020】

次いで、図1(f)～図2(h)に示す素子分離形成工程において、シリコン基板101の第1面1011に素子分離106'を形成する。該素子分離工程は、開口OPを有するレジストパターン等のマスクMを使って第1面1011の側のシリコン窒化膜104をエッティングする処理を含み、シリコン基板101の第1面1101における開口OPによって規定される領域に素子分離106'を形成する。より具体的な例を挙げて説明すると、図1(f)に示す工程において、シリコン窒化膜104の上にレジストパターン等のマスクMを形成する。そして、マスクMの開口OPを通して、第1面1011の側の、シリコン窒化膜104、シリコン酸化膜201、ポリシリコン膜103、シリコン酸化膜102をエッティングし、更にシリコン基板101をエッティングする。これによって、シリコン基板101の第1面1011に溝105が形成される。このエッティングは、例えば、ドライエッティング法によってなされうる。より具体的には、このエッティングは、CF<sub>4</sub>ガス等のフロロカーボン系のガスを使ってRIE(Reactive Ion Etching)

40

50

) 法によってなされうる。溝 105 の深さは、例えば、1000 ~ 3000 の範囲内で決定されうる。次いで、図 2 (g) に示す工程において、溝 105 の内部および基板の表面(即ち、シリコン酸化膜 201 の表面)にシリコン酸化物(絶縁体)106 を形成する。シリコン酸化物 106 は、例えば、Ar、O<sub>2</sub> および SiH<sub>4</sub> の混合ガスを処理ガスとして、300 ~ 500 の範囲内の温度で HDP(High Density Plassma) CVD 装置を使用して形成されうる。シリコン酸化物 106 は、例えば、3000 ~ 7000 の範囲内の厚さを有するように形成さうれうる。次に、図 2 (h) に示す工程において、エッティング及び CMP(Chemical Mechanical Polish) 法により、シリコン酸化物 106 を除去及び研磨する。この工程では、溝 105 の内部の素子分離 106' としてシリコン酸化物を残しつつシリコン窒化膜 104 の表面を露出させる。この CMP 法は、例えば、シリカ系スラリー やセリア系スラリーを用い、研磨布の回転数を 50 rpm ~ 100 rpm の範囲内とし、押し付け圧を 100 hPa ~ 300 hPa の範囲内として実施されうる。図 1 (f) ~ 図 2 (h) に示す素子分離形成工程は、STI(Shallow Trench Isolation) 法と呼ばれる。

10

#### 【0021】

図 1 (f) ~ 図 2 (h) に示す素子分離形成工程に代えて他の素子分離形成工程を実施してもよい。他の素子分離形成工程は、開口 OP を有するマスクを使って第 1 面 1011 の側のシリコン窒化膜 104 をエッティングする処理を含み、シリコン基板 101 の第 1 面 1011 における開口 OP によって規定される領域に素子分離 106' を形成する。この点では、他の素子分離形成工程は、図 1 (f) ~ 図 2 (h) に示す素子分離形成工程と共通している。しかし、当該他の素子分離形成工程は、シリコン窒化膜 104 をエッティングして酸化用開口部を形成した後、該酸化用開口部を通して第 1 面 1011 の側のポリシリコン膜 103 を酸化させるとともにシリコン基板 101 の第 1 面 1011 を部分的に酸化させる。この点では、当該他の素子分離形成工程は、図 1 (f) ~ 図 2 (h) に示す素子分離形成工程とは異なる。当該他の素子分離形成工程は、ポリバッファ LOCOS 法と呼ばれる。

20

#### 【0022】

次いで、図 2 (i) に示す工程では、溝 105 の内部のシリコン酸化物、即ち素子分離 106' の厚さを調整する。この処理は、例えば、ウェットエッティング法によって実施されうる。より具体的には、この処理は、例えば、バッチ式のウェットステーションを使用し、室温で、100 : 1 程度の希釈 HF 水溶液を処理液として実施されうる。

30

#### 【0023】

次いで、図 2 (j) に示す工程(第 2 絶縁膜除去工程)において、第 1 面 1011 の側のシリコン窒化膜 104 および第 2 面 1012 の側のシリコン窒化膜(第 2 絶縁膜)104 を除去する。第 1 面 1011 の側のシリコン酸化膜 201 および第 2 面 1012 の側のシリコン酸化膜 201 を露出させる。シリコン窒化膜 104 は、例えば、ウェットエッティング法によって除去されうる。より具体的には、シリコン窒化膜 104 は、例えば、バッチ式のウェットステーションを使用し、150 ~ 170 の範囲内の温度に調整されたリン酸液によって除去されうる。

40

#### 【0024】

次いで、図 2 (k) に示す工程において、シリコン基板 101 の第 1 面 1011 の側のシリコン酸化膜 201 を除去し、第 1 面 1011 の側のみ、ポリシリコン膜 103 を露出させる。シリコン酸化膜 201 は、例えば、ウェットエッティング法によって除去されうる。より具体的には、シリコン酸化膜 201 は、例えば、枚葉式洗浄装置を使用し、室温で、100 : 1 程度の希釈 HF 水溶液によって除去されうる。この工程の後、第 1 面 1011 の側は、ポリシリコン膜 103 が露出し、第 2 面 1012 の側は、シリコン酸化膜 201 が露出した状態となる。なお、図 2 (k) に示す工程は、図 2 (i) に示す工程と同様に、素子分離 106' の厚さの調整も兼ねている。

#### 【0025】

次に、図2(1)に示す工程(ポリシリコン膜除去工程)において、第1面1011および第2面1012のうち第1面1011の側のポリシリコン膜103を除去する。この際、第2面1012の側のシリコン酸化膜201は、第2面1012の側のポリシリコン膜103を保護する保護膜として機能する。ポリシリコン膜103は、例えば、アルカリ系の薬液を用いたウェットエッティング法によって除去されうる。より具体的には、ポリシリコン膜103は、例えば、バッチ式のウェットステーションを使用し、50～100の範囲内の温度で、アンモニア／過酸化水素／純水の混合液を処理液として実施されうる。このような条件では、ポリシリコン膜103とシリコン酸化膜201との間に高いエッティング選択比が得られる。

## 【0026】

10

以上の工程によって素子分離の形成処理が完了する。以降は、任意の方法にしたがってトランジスタ等の素子を形成し、半導体装置を完成させることができる。

## 【0027】

比較例では、ゲッタリング膜として形成した第2面の側のポリシリコン膜103が除去されてしまい、十分なゲッタリング効果を得ることができなかつた。これに対して、第1実施形態によれば、煩雑な工程を付加することなく、基板の第2面にポリシリコン膜103を残すことが可能となる。これによってゲッタリング効果を高めることができ、重金属不純物等の金属不純物による汚染による半導体装置の特性の悪化を抑制することができる。

## 【0028】

20

以下、図1、図5および図6を参照しながら本発明の半導体装置の製造方法の第2実施形態を説明する。第2実施形態は、図1(a)～(d)に示す工程について第1実施形態と同様であり、図1(d)に示す工程に次いで、図5(e)に示す工程が実施される。図1(a)～(d)に示す工程については、説明を省略する。

## 【0029】

図1(d)に示す工程の後に実施される図5(e)に示す工程において、第1面1011および第2面1012のうち第1面1011の側のシリコン酸化膜(保護膜)201を除去する。これにより、第1面1011の側のポリシリコン膜103が露出する。第1面1011の側のシリコン酸化膜201は、例えば、ウェットエッティング法によって除去されうる。より具体的には、第1面1011の側のシリコン酸化膜201は、例えば、枚葉式洗浄装置を使用し、室温で、100：1程度の希釈HF水溶液によって除去されうる。図5(e)に示す工程により、第1面1011の側にポリシリコン膜103が露出し、第2面1012の側にシリコン酸化膜201が露出した基板が得られる。

## 【0030】

30

次いで、図5(f)に示す工程(第2絶縁膜形成工程)において、第1面1011の側および第2面1012の側のポリシリコン膜103の上にシリコン窒化膜(第2絶縁膜)104を形成する。ここで、第1面1011の側については、ポリシリコン膜103の上に直接にシリコン窒化膜104を形成し、第2面1012の側については、ポリシリコン膜103の上にシリコン酸化膜201を介してシリコン窒化膜104を形成する。シリコン窒化膜104を形成するための条件は、図1(e)に示す工程における条件に従いうる。

## 【0031】

40

次いで、図5(g)～図5(i)に示す素子分離形成工程において、シリコン基板101の第1面1011に素子分離106'を形成する。この工程は、開口OPを有するレジストパターン等のマスクMを使って第1面1011の側のシリコン窒化膜104をエッティングする処理を含み、シリコン基板101の第1面1101における開口OPによって規定される領域に素子分離106'を形成する。より具体的な例を挙げて説明すると、図5(g)に示す工程において、シリコン窒化膜104の上にレジストパターン等のマスクMを形成する。そして、マスクMの開口OPを通して、第1面1011の側の、シリコン窒化膜104、シリコン酸化膜201、ポリシリコン膜103、シリコン酸化膜102を工

50

ツチングし、更にシリコン基板 101 をエッティングする。これによって、シリコン基板 101 の第1面 1011 に溝 105 が形成される。溝 105 を形成するための条件は、図 1 (f) に示す工程における条件に従いうる。図 5 (h) ~ (i) に示す工程は、図 2 (g) ~ (h) に示す工程と同様である。

#### 【0032】

次いで実施される図 6 (j)、(k) に示す工程は、図 2 (i)、(j) に示す工程と同様である。次いで、図 6 (l) に示す工程において、溝 105 の内部のシリコン酸化物、即ち素子分離 106' の厚さを調整する。この処理は、例えば、ウェットエッティング法によって実施されうる。より具体的には、この処理は、例えば、バッチ式のウェットステーションを使用し、室温で、100 : 1 程度の希釈 HF 水溶液を処理液として第1面 1011 の側に対してのみ実施されうる。

10

#### 【0033】

次いで実施される図 6 (m) に示す工程（ポリシリコン膜除去工程）は、図 2 (l) に示す工程と同様である。この工程では、第1面 1011 および第2面 1012 のうち第1面 1011 の側のポリシリコン膜 103 が除去される。この際、第2面 1012 の側のシリコン酸化膜 201 は、第2面 1012 の側のポリシリコン膜 103 を保護する保護膜として機能する。

#### 【0034】

以上の工程によって素子分離の形成処理が完了する。以降は、任意の方法にしたがってトランジスタ等の素子を形成し、半導体装置を完成させることができる。

20

#### 【0035】

以上のように、第2実施形態によれば、煩雑な工程を付加することなく、基板の第2面にポリシリコン膜 103 を残すことが可能となる。これによってゲッタリング効果を高めることができ、重金属不純物等の金属不純物による汚染による半導体装置の特性の悪化を抑制することができる。

#### 【0036】

以下、図 7 および図 8 を参照しながら本発明の半導体装置の製造方法の第3実施形態を説明する。図 7 (a) ~ (c) に示す工程は、図 1 (a) ~ (c) に示す工程とどうようである。

#### 【0037】

図 7 (c) に示す工程に次いで実施される図 7 (d) に示す工程（第2絶縁膜形成工程）では、第1面 1011 の側および第2面 1012 の側のポリシリコン膜 103 の上にシリコン窒化膜（第2絶縁膜）104 を形成する。ここで、第3実施形態では、第1面 1011 の側および第2面 1012 の側のポリシリコン膜 103 の上に、直接、シリコン窒化膜 104 が形成される。シリコン窒化膜 104 を形成するための条件は、図 1 (e) に示す工程における条件に従いうる。

30

#### 【0038】

次いで実施される図 7 (e)、図 7 (f)、図 8 (g)、図 8 (h) に示す工程は、図 1 (f)、図 2 (g)、図 2 (h)、図 2 (i) に示す工程と同様である。次いで実施される図 8 (i) に示す工程では、シリコン基板 101 の第1面 1011 および第2面 1012 の側に形成されたシリコン窒化膜 104 を除去してポリシリコン膜 103 を露出させる。シリコン窒化膜 104 を除去するための条件は、図 2 (j) に示す工程における条件に従いうる。

40

#### 【0039】

次いで、図 8 (j) に示す工程において、シリコン基板 101 の第1面 1011 および第2面 1012 の側のポリシリコン膜 103 上にシリコン酸化膜（保護膜）201 を形成する。シリコン酸化膜 201 を形成するための条件は、図 1 (d) に示す工程における条件に従いうる。次いで、図 8 (k) に示す工程において、シリコン基板 101 の第1面 1011 および第2面 1012 のうち第1面 1011 の側のシリコン酸化膜 201 を除去し、第1面 1011 の側のみ、ポリシリコン膜 103 を露出させる。シリコン酸化膜 201

50

を除去するための条件は、図 2 ( k ) に示す工程における条件に従いうる。

【 0 0 4 0 】

次いで実施される図 8 ( 1 ) に示す工程（ポリシリコン膜除去工程）は、図 2 ( 1 ) に示す工程と同様である。この工程では、第 1 面 1 0 1 1 および第 2 面 1 0 1 2 のうち第 1 面 1 0 1 1 の側のポリシリコン膜 1 0 3 が除去される。この際、第 2 面 1 0 1 2 の側のシリコン酸化膜 2 0 1 は、第 2 面 1 0 1 2 の側のポリシリコン膜 1 0 3 を保護する保護膜として機能する。

【 0 0 4 1 】

以上の工程によって素子分離の形成処理が完了する。以降は、任意の方法にしたがってトランジスタ等の素子を形成し、半導体装置を完成させることができる。

10

【 0 0 4 2 】

以上のように、第 3 実施形態によれば、煩雑な工程を付加することなく、基板の第 2 面に、ポリシリコン膜 1 0 3 を残すことが可能となる。これによってゲッタリング効果を高めることができ、重金属不純物等の金属不純物による汚染による半導体装置の特性の悪化を抑制することができる。なお、本発明の素子分離は、S T I 法やポリバッファ L O C O S 法に限定されず、M E S A 法やE D I 法にも適用可能である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 中澤 亨

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 右田 勝則

(56)参考文献 特開平09-120965(JP,A)

特開平01-046937(JP,A)

特開平05-235004(JP,A)

米国特許第05874325(US,A)

特開平04-014836(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 21/322