(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2015-531957

(P2015-531957A)

(43) 公表日 平成27年11月5日(2015.11.5)

(51) Int.Cl.

G 11 C 16/06 (2006.01)

G 11 C 16/04 (2006.01)

F 1

G 11 C 17/00

G 11 C 17/00

テーマコード(参考)

6 3 4 E

5 B 2 2 5

6 2 1 A

審査請求 未請求 予備審査請求 未請求 (全 17 頁)

(21) 出願番号 特願2015-532159 (P2015-532159)

(86) (22) 出願日 平成25年9月18日 (2013.9.18)

(85) 翻訳文提出日 平成27年5月1日 (2015.5.1)

(86) 国際出願番号 PCT/US2013/060302

(87) 国際公開番号 WO2014/047114

(87) 国際公開日 平成26年3月27日 (2014.3.27)

(31) 優先権主張番号 61/702,338

(32) 優先日 平成24年9月18日 (2012.9.18)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/029,741

(32) 優先日 平成25年9月17日 (2013.9.17)

(33) 優先権主張国 米国(US)

(71) 出願人 397050741

マイクロチップ テクノロジー インコーポレイテッド

MICROCHIP TECHNOLOGY INCORPORATED

アメリカ合衆国 85224-6199

アリゾナ チャンドラー ウエスト チャンドラー ブルヴァード 2355

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】自己バイアス電流基準

## (57) 【要約】

いかなるメモリセルもアサートされていないビット線上に出現する電流は、VDD電位でビット線と電力供給部との間に接続されるゲート-ドレイン短絡PMOSブルアップデバイスにバイアスをかけるように読み取が行われる前のビット線事前充電時間中に使用されてもよい。このPMOSブルアップデバイスのゲートに接続される静電容量は、いったん事前充電時間が完了すると、ドレインが切断されるときに、結果として生じたゲート-ソース電圧を「格納する」ために使用されてもよい。いったん読み取動作が開始すると、「格納された」結果として生じたゲート-ソース電圧を有する、PMOSブルアップデバイスの電流は、その読み取動作中にビット線に接続されるアサートされたメモリセルの状態を感知するための基準として、再利用される。

Figure 2

Figure 5

**【特許請求の範囲】****【請求項 1】**

フロー ティングゲートを有するメモリセルの充電状態を判定するための方法であって、前記方法は、

ビット線に連結された全てのメモリセルがアサート停止されるときに、前記ビット線内の第 1 の電流を感知するステップと、

前記第 1 の電流を電圧に変換するステップと、

前記電圧を格納するステップと、

前記格納された電圧に基づいて、基準電流を提供するステップと、

前記ビット線に接続された単一のメモリセルが、その読み取り動作中にアサートされるときに、前記基準電流を前記ビット線内の第 2 の電流と比較するステップと、

前記第 2 の電流との前記基準電流の前記比較から、前記単一のメモリセルに格納されたビット値充電状態を判定するステップと

を含む、方法。

**【請求項 2】**

前記第 1 の電流を感知するステップは、前記ビット線に連結された全てのメモリセルがアサート停止されるときに、第 1 のトランジスタのゲートおよびドレインを前記ビット線に連結するステップを含む、請求項 1 に記載の方法。

**【請求項 3】**

前記第 1 の電流を前記電圧に変換するステップは、前記感知された第 1 の電流から、前記第 1 のトランジスタの前記ゲートおよびソースにわたって前記電圧を生成するステップを含む、請求項 2 に記載の方法。

**【請求項 4】**

前記電圧を格納するステップは、第 2 のトランジスタのゲートおよびともに接続されたソース - ドレインにわたって前記電圧を連結するステップを含み、前記電圧は、前記第 2 のトランジスタのゲートとソース - ドレインとの間に形成された静電容量の間に格納される、請求項 3 に記載の方法。

**【請求項 5】**

前記電圧を格納するステップは、コンデンサにわたって前記電圧を連結するステップを含む、請求項 3 に記載の方法。

**【請求項 6】**

前記基準電流を提供するステップは、前記第 2 のトランジスタに格納された前記電圧に基づいて、前記第 1 のトランジスタを用いて前記基準電流を生成するステップを含む、請求項 4 に記載の方法。

**【請求項 7】**

前記基準電流を提供するステップは、前記コンデンサに格納された前記電圧に基づいて、前記第 1 のトランジスタを用いて前記基準電流を生成するステップを含む、請求項 5 に記載の方法。

**【請求項 8】**

前記基準電流を前記第 2 の電流と比較するステップは、前記メモリセルがアサートされた後に前記メモリセルと関連付けられる前記ビット線の前記電圧を監視するステップを含む、請求項 1 に記載の方法。

**【請求項 9】**

前記単一のメモリセルに格納された前記ビット値充電状態を判定するステップは、前記アサートされたメモリセルと関連付けられる前記ビット線の論理状態の変化または論理状態の欠如を検出するステップを含む、請求項 1 に記載の方法。

**【請求項 10】**

前記第 1 のトランジスタの前記ドレインは、前記ビット線に連結され、前記第 1 のトランジスタの前記ソースは、電力供給電圧に連結され、前記第 2 のトランジスタに格納された前記電圧は、前記基準電流を提供するように前記第 1 のトランジスタにバイアスをかけ

10

20

30

40

50

る、請求項 6 に記載の方法。

【請求項 1 1】

前記アサートされたメモリセルの読取動作中に、前記第 2 のトランジスタの中の前記格納された電圧は、前記ビット線に連結された前記アサートされたメモリセルの前記ビット値充電状態を感知するための前記基準電流を判定する際に使用される、請求項 1 に記載の方法。

【請求項 1 2】

前記第 1 および第 2 のトランジスタは、p 型金属酸化膜半導体 (PMOS) トランジスタである、請求項 4 に記載の方法。

【請求項 1 3】

前記第 1 および第 2 のトランジスタは、n 型金属酸化膜半導体 (NMOS) トランジスタである、請求項 4 に記載の方法。

【請求項 1 4】

フローティングゲートを有するメモリセルの充電状態を判定するための装置であって、前記装置は、第 1 のトランジスタを備え、

前記第 1 のトランジスタは、ビット線に連結された全てのメモリセルがアサート停止されるときに、前記ビット線に連結されるゲートおよびドレインと、電力供給電圧に連結されるソースとを有し、前記ビット線内の第 1 の電流が感知され、

前記第 1 のトランジスタは、前記第 1 の電流を電圧に変換し、

第 2 のトランジスタは、前記電圧を格納し、

前記第 1 のトランジスタは、前記第 2 のトランジスタからの前記格納された電圧に基づいて、基準電流を提供し、

前記基準電流は、前記ビット線に接続された単一のメモリセルが、その読取動作中にアサートされるときに、前記ビット線内の第 2 の電流と比較され、

前記単一のメモリセルに格納されたビット値充電状態は、前記第 2 の電流との前記基準電流の前記比較から判定される、装置。

【請求項 1 5】

前記第 1 のトランジスタを通る前記第 1 の電流は、前記第 1 のトランジスタの前記ゲートとソースとの間に前記電圧を生成する、請求項 1 4 に記載の装置。

【請求項 1 6】

前記電圧は、前記第 2 のトランジスタのゲートとソース - ドレインとの間に形成された静電容量の間に格納される、請求項 1 4 に記載の装置。

【請求項 1 7】

前記電圧は、コンデンサ上に格納される、請求項 1 4 に記載の装置。

【請求項 1 8】

前記基準電流は、前記アサートされたメモリセルと関連付けられる前記ビット線を用いて、前記第 2 の電流と比較される、請求項 1 4 に記載の装置。

【請求項 1 9】

前記単一のメモリセルに格納された前記ビット値充電状態は、前記アサートされたメモリセルと関連付けられる前記ビット線の論理状態の変化または論理状態の欠如を検出することによって判定される、請求項 1 4 に記載の装置。

【請求項 2 0】

前記第 1 および第 2 のトランジスタは、p 型金属酸化膜半導体 (PMOS) トランジスタである、請求項 1 4 に記載の装置。

【請求項 2 1】

前記第 1 および第 2 のトランジスタは、n 型金属酸化膜半導体 (NMOS) トランジスタである、請求項 1 4 に記載の装置。

【請求項 2 2】

フローティングゲートを有するメモリセルの充電状態を判定するための装置であって、前記装置は、第 1 のトランジスタを備え、

10

20

30

40

50

前記第1のトランジスタは、ビット線に連結された全てのメモリセルがアサート停止されるときに、前記ビット線に連結されるゲートおよびドレインと、電力供給電圧に連結されるソースとを有し、前記ビット線内の第1の電流が感知され、

前記第1のトランジスタは、前記第1の電流を電圧に変換し、

コンデンサは、前記電圧を格納し、

前記第1のトランジスタは、前記コンデンサからの前記格納された電圧に基づいて、基準電流を提供し、

前記基準電流は、前記ビット線に接続された単一のメモリセルが、その読み取り動作中にアサートされるときに、前記ビット線内の第2の電流と比較され、

前記単一のメモリセルに格納されたビット値充電状態は、前記第2の電流との前記基準電流の前記比較から判定される、装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

(関連の特許出願)

本出願は、2012年9月18日に出願された、David Francis Mietusによる「Self-Biasing Current Reference」という題名の共同所有された米国仮特許出願第61/702,338号に対して優先権を主張する。上記文献は、これによって、全ての目的のために参照することによって本明細書において援用される。 20

【0002】

(技術分野)

本開示は、自己バイアス電流基準に関し、具体的には、メモリセルで使用される自己バイアス電流基準に関する。

【背景技術】

【0003】

(背景)

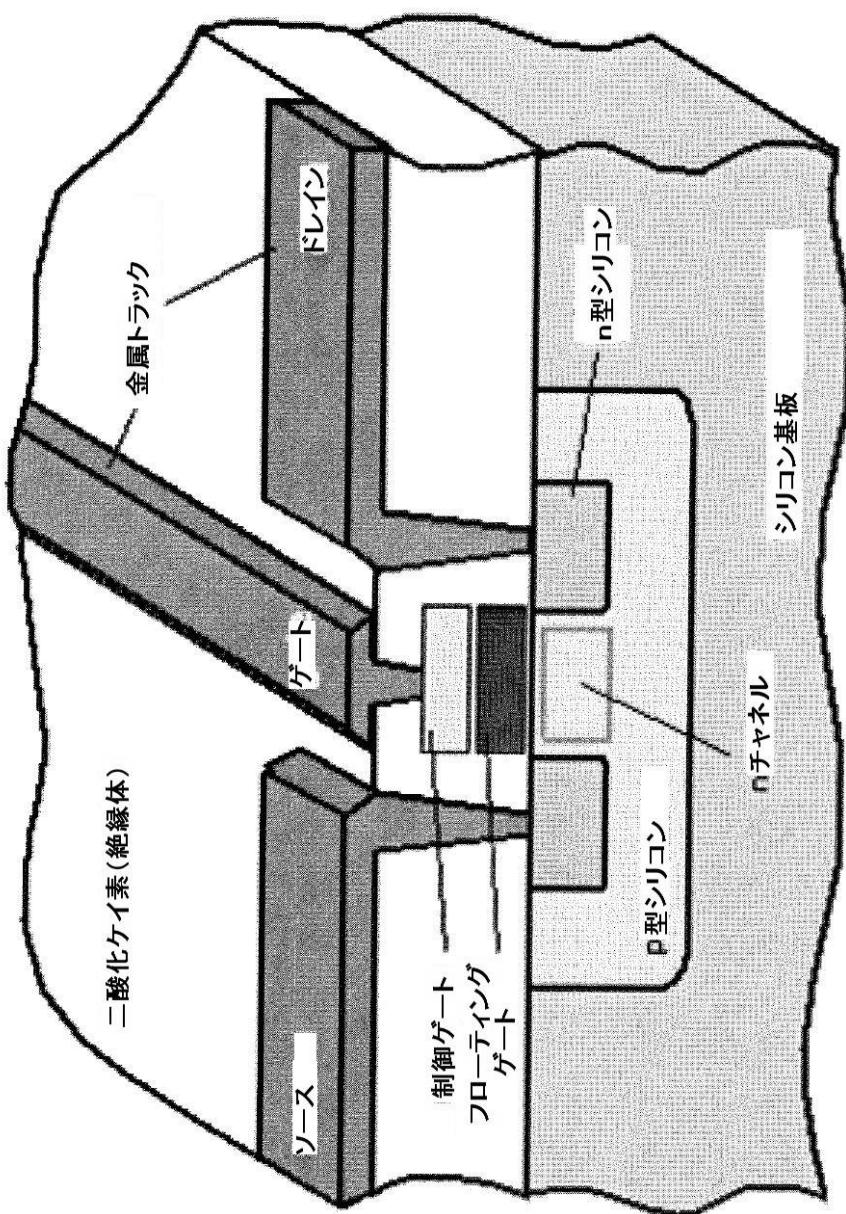

電気的消去可能かつプログラム可能な読み取り専用メモリ(EEPROM)は、電力を用いることなく、そのメモリコンテンツを保持することができる、書換可能メモリデバイスである。EEPROMは、書きレベルにおいてアドレス化可能なビットまたはバイトであり、これは、書き換えられる前に、ビットまたはバイトのいずれか一方が消去されなければならないことを意味する。EEPROMは、典型的には、命令およびデータを格納するために回路基板上で使用される。図1を参照すると、「フローティングゲート」は、格納されたビット電荷をEEPROMの中に保持する。相補型金属酸化膜半導体(CMOS)ベースのトランジスタ技術が、概して使用され、格納されたビット電荷を保持するよう、「フローティングゲート」を有する。いかなる電荷もフローティングゲート上に存在しないとき、トランジスタが正常に作用し、制御ゲート上のパルスが電流を流動させる。フローティングゲートが充電されるとき、この充電は、メモリセルトランジスタの正常な制御ゲート作用を阻止し、電流は、制御ゲート上のパルス中に流動しない。充電は、ソースおよびドレイン端子を接地し、電荷が酸化物を通してフローティングゲートまでトンネルするように、制御ゲートに十分な電圧をかけることによって達成される。別のトランジスタから導かれる逆電圧は、集積回路基板の中へ放散されることによって、フローティングゲート電荷を取り除く。 30

【0004】

メモリデバイスは、高い信頼性を必要とする。例えば、直列EEPROM製品を作成するためには、メモリアレイから適正なデータを読み出すデバイスの能力において制限を有し得る。例えば、過剰な「セル」漏出が、読み取られているアサートされたメモリセルの「オン」セルおよび「オフ」セル電流を区別する能力を最小限化/排除し得る。ビット線に接続される「リーカ」トランジスタの使用によって、オフセットを引き起こし得る。自己タイミング型読み取り方式の使用が、読み取り前にビット線放電を可能にし得る。 40

。読み取り電荷ポンプの使用が、「オン」セル電流の供給変動を最小限化し得る。

#### 【0005】

さらに、「オン」セル電流の劣化および/または制御されていない/誤った基準電流レベルが、感知増幅器性能を制限する。「オン」セル電流の耐久性関連劣化がある。使用される基準電圧/電流レベルは、使用されるプロセスとともに過度に変動し得る、および/または電圧供給および/または温度と対比して「オン」セル電流を追跡しない。ビット線漏出電流は、固定基準電流によって補償されることがない。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0006】

##### (要約)

したがって、外部基準電流および/または漏出補償を排除し、高温で漏出電流の効果を最小限化することによって回路機能を向上させ、読み取り動作中にビット線が完全  $V_{DD}$  電位まで事前充電されることを要求しないことによって低電力動作を可能にする、メモリセル電流の耐久性劣化に対する向上した耐性の必要性が、EEPROMメモリ製品に存在する。

#### 【0007】

実施形態によると、フローティングゲートを有するメモリセルの充電状態を判定するための方法は、ビット線に連結される全てのメモリセルがアサート停止され得るときに、ビット線内の第1の電流を感知するステップと、第1の電流を電圧に変換するステップと、電圧を格納するステップと、格納された電圧に基づいて、基準電流を提供するステップと、ビット線に接続される単一のメモリセルが、その読み取り動作中にアサートされ得るときに、基準電流をビット線内の第2の電流と比較するステップと、第2の電流との基準電流の比較から、単一のメモリセルに格納されたビット値充電状態を判定するステップとを含んでもよい。

#### 【0008】

本方法のさらなる実施形態によると、第1の電流を感知するステップは、ビット線に連結される全てのメモリセルがアサート停止され得るときに、第1のトランジスタのゲートおよびドレインをビット線に連結するステップを含んでもよい。本方法のさらなる実施形態によると、第1の電流を電圧に変換するステップは、感知された第1の電流から、第1のトランジスタのゲートおよびソースにわたって電圧を生成するステップを含んでもよい。本方法のさらなる実施形態によると、電圧を格納するステップは、第2のトランジスタのゲートおよびともに接続されたソース-ドレインにわたって電圧を連結するステップを含んでもよく、電圧は、第2のトランジスタのゲートとソース-ドレインとの間に形成される静電容量の間に格納されてもよい。本方法のさらなる実施形態によると、電圧を格納するステップは、コンデンサにわたって電圧を連結するステップを含んでもよい。本方法のさらなる実施形態によると、基準電流を提供するステップは、第2のトランジスタに格納された電圧に基づいて、第1のトランジスタを用いて基準電流を生成するステップを含んでもよい。

#### 【0009】

本方法のさらなる実施形態によると、基準電流を提供するステップは、コンデンサに格納された電圧に基づいて、第1のトランジスタを用いて基準電流を生成するステップを含んでもよい。本方法のさらなる実施形態によると、基準電流を第2の電流と比較するステップは、メモリセルがアサートされた後に上記メモリセルと関連付けられるビット線の電圧を監視するステップを含んでもよい。本方法のさらなる実施形態によると、単一のメモリセルに格納されたビット値充電状態を判定するステップは、アサートされたメモリセルと関連付けられるビット線の論理状態の変化またはその欠如を検出するステップを含んでもよい。本方法のさらなる実施形態によると、第1のトランジスタのドレインは、ビット線に連結されてもよく、第1のトランジスタのソースは、電力供給電圧に連結されてもよく、第2のトランジスタに格納された電圧は、基準電流を提供するように第1のトランジ

10

20

30

40

50

スタにバイアスをかける。本方法のさらなる実施形態によると、アサートされたメモリセルの読み取り動作中に、第2のトランジスタの中の格納された電圧は、ビット線に連結されるアサートされたメモリセルのビット値充電状態を感知するための基準電流を判定する際に使用されてもよい。本方法のさらなる実施形態によると、第1および第2のトランジスタは、p型金属酸化膜半導体(PMOS)トランジスタであってもよい。本方法のさらなる実施形態によると、第1および第2のトランジスタは、n型金属酸化膜半導体(NMOS)トランジスタであってもよい。

【0010】

別の実施形態によると、フローティングゲートを有するメモリセルの充電状態を判定するための装置は、ビット線に連結される全てのメモリセルがアサート停止され得るときに、ビット線に連結されるゲートおよびドレインと、電力供給電圧に連結されるソースとを有する、第1のトランジスタであって、ビット線内の第1の電流が感知され得る、第1のトランジスタを備えてもよく、第1のトランジスタは、第1の電流を電圧に変換し、第2のトランジスタは、電圧を格納し、第1のトランジスタは、第2のトランジスタからの格納された電圧に基づいて、基準電流を提供し、基準電流は、ビット線に接続される単一のメモリセルが、その読み取り動作中にアサートされ得るときに、ビット線内の第2の電流と比較されてもよく、単一のメモリセルに格納されたビット値充電状態は、第2の電流との基準電流の比較から判定されてもよい。

10

【0011】

さらなる実施形態によると、第1のトランジスタを通る第1の電流は、第1のトランジスタのゲートとソースとの間に電圧を生成する。さらなる実施形態によると、電圧は、第2のトランジスタのゲートとソース-ドレインとの間に形成される静電容量の間に格納されてもよい。さらなる実施形態によると、電圧は、コンデンサ上に格納されてもよい。さらなる実施形態によると、基準電流は、アサートされたメモリセルと関連付けられるビット線を用いて、第2の電流と比較されてもよい。さらなる実施形態によると、単一のメモリセルに格納されたビット値充電状態は、アサートされたメモリセルと関連付けられるビット線の論理状態の変化またはその欠如を検出することによって判定されてもよい。さらなる実施形態によると、第1および第2のトランジスタは、p型金属酸化膜半導体(PMOS)トランジスタであってもよい。さらなる実施形態によると、第1および第2のトランジスタは、n型金属酸化膜半導体(NMOS)トランジスタであってもよい。

20

【0012】

さらに別の実施形態によると、フローティングゲートを有するメモリセルの充電状態を判定するための装置は、ビット線に連結される全てのメモリセルがアサート停止され得るときに、ビット線に連結されるゲートおよびドレインと、電力供給電圧に連結されるソースとを有する、第1のトランジスタであって、ビット線内の第1の電流が感知され得る、第1のトランジスタを備えてもよく、第1のトランジスタは、第1の電流を電圧に変換し、コンデンサは、電圧を格納し、第1のトランジスタは、コンデンサからの格納された電圧に基づいて、基準電流を提供し、基準電流は、ビット線に接続される単一のメモリセルが、その読み取り動作中にアサートされ得るときに、ビット線内の第2の電流と比較されてもよく、単一のメモリセルに格納されたビット値充電状態は、第2の電流との基準電流の比較から判定されてもよい。

30

【0013】

本開示のより完全な理解が、添付図面と併せて解釈される以下の説明を参照することによって獲得され得る。

【図面の簡単な説明】

【0014】

【図1】図1は、本開示の教示による、電気的消去可能かつプログラム可能な読み取り専用メモリ(EEPROM)トランジスタの概略断面図を図示する。

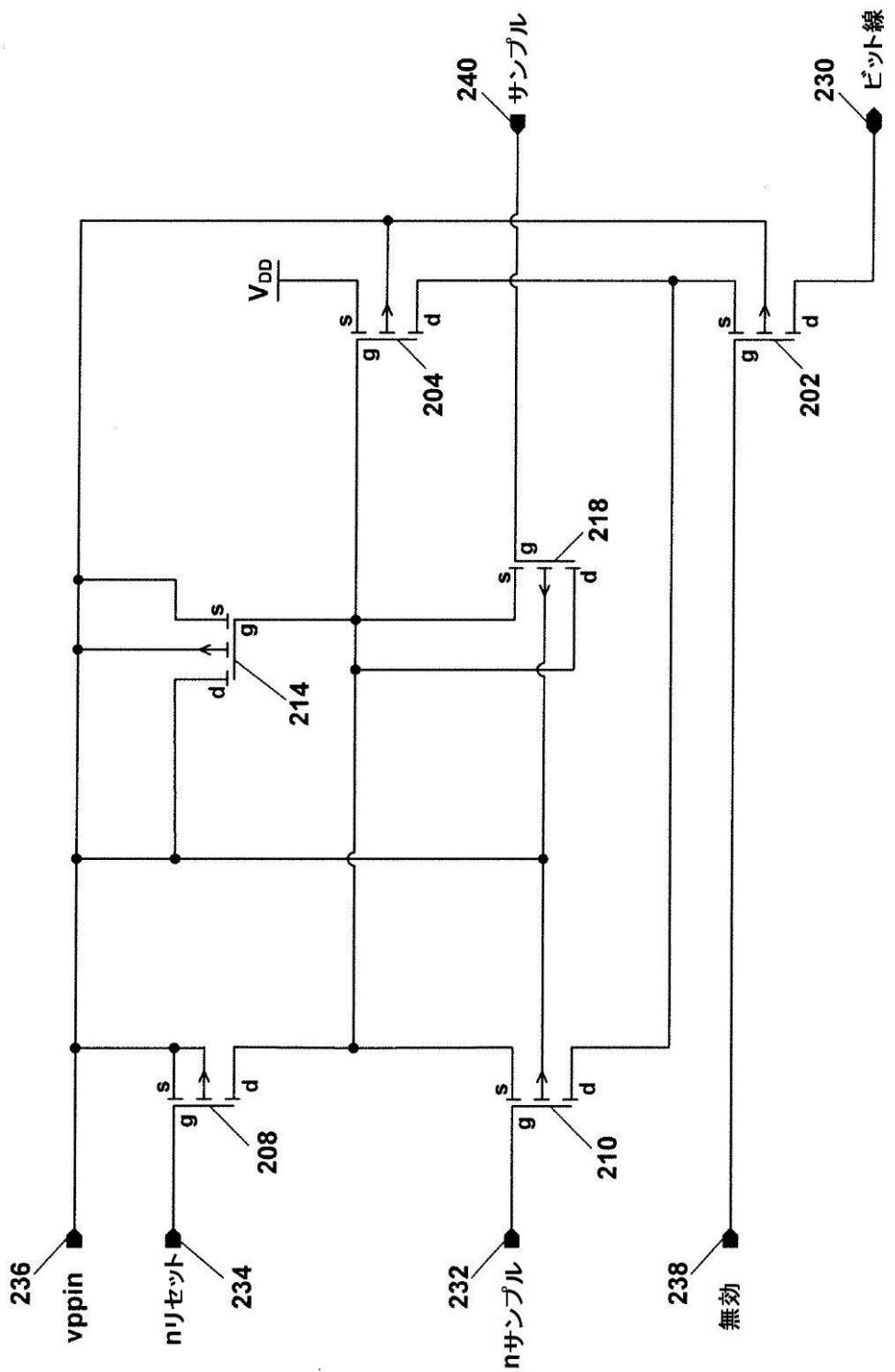

【図2】図2は、本開示の具体的な例示的実施形態による、自己バイアス電流基準の概略図を図示する。

40

50

【図3】図3は、図2に示される自己バイアス電流基準をモデル化するために使用される概略図を図示する。

【図4】図4は、アサートされたメモリセルの「オン」および「オフ」状態の両方について図3に示される回路のタイミング波形を図示する。

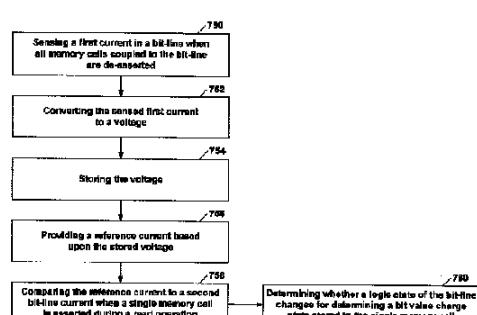

【図5】図5は、本開示の具体的な例示的実施形態による、自己バイアス電流基準を利用する用途の流れ図を図示する。

【発明を実施するための形態】

【0015】

本開示は、種々の修正および代替形態の影響を受け得るが、その具体的な例示的実施形態が、図面に示されており、本明細書で詳細に説明される。しかしながら、具体的な例示的実施形態の本明細書の説明は、本開示を本明細書で開示される特定の形態に限定することを目的としておらず、反対に、本開示は、添付の請求項によって定義されるような全ての修正および均等物を対象とするものであることを理解されたい。

10

【0016】

(詳細な説明)

本開示の種々の実施形態によると、アサートされていないメモリアレイビット線上に存在する電流が、感知され、電圧として格納されてもよい。次いで、この格納された電圧は、その読み取り動作中にアサートされたメモリセルの状態を感知するときに、基準電流を生成するために利用されてもよい。さらに、種々の実施形態によると、高温で漏出電流の効果を最小限化することによって、向上した回路機能が提供されてもよい。種々の実施形態は、アサートされたメモリセルの読み取り中にビット線が $V_{DD}$ 電位未満まで事前充電され得るため、低電力動作を可能にする。

20

【0017】

種々の実施形態によると、メモリセル電流の耐久性劣化に対する耐性が向上させられ、外部基準電圧、電流、および／または漏出補償の必要性が排除され得る。

【0018】

種々の実施形態によると、いかなるメモリセルもアサートされていないビット線上に出現する電流は、 $V_{DD}$ 電位でビット線と電力供給部との間に接続される、ゲート - ドレイン短絡PMOSプルアップデバイスにバイアスをかけるように読み取りが行われる前のビット線事前充電時間中に使用されてもよい。このPMOSプルアップデバイスのゲートに接続される静電容量は、いったん事前充電時間が完了すると、ドレインが切断されるときに、結果として生じたゲート - ソース電圧を「格納する」ために使用されてもよい。いったん読み取り動作が開始すると、「格納された」結果として生じたゲート - ソース電圧を有する、PMOSプルアップデバイスの電流は、その読み取り動作中にビット線に接続されるアサートされたメモリセルの状態を感知するための基準として、再利用される。

30

【0019】

ここで図面を参照すると、具体的な例示的実施形態の詳細が概略的に図示されている。図面中の類似要素は、類似番号によって表され、類似する要素は、異なる小文字接尾語を伴う類似番号によって表されるであろう。

【0020】

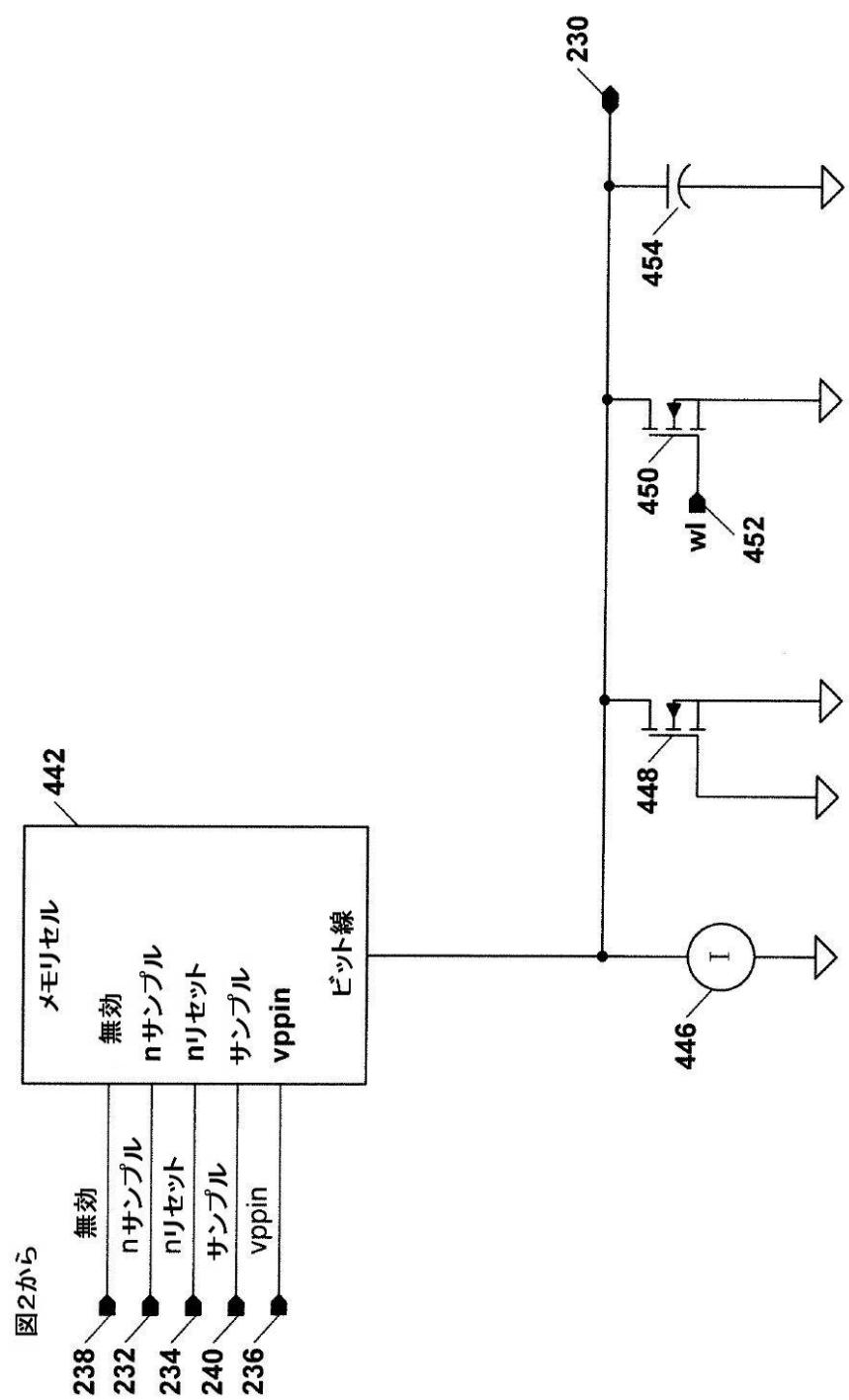

図2を参照すると、本開示の具体的な例示的実施形態による、自己バイアス電流基準の概略図が描寫されている。トランジスタ202、204、208、210、214、および218は、図2に示されるように、ともに配列および接続されるP型金属酸化膜半導体(PMOS)トランジスタであってもよく、ともに以下のように機能してもよい。ビット線230に取り付けられたEEPROMメモリアレイ(図示せず)のメモリセルの全てがアサート停止されるとき、nサンプルノード232上の論理低('0')をアサートし、トランジスタ210を介してトランジスタ204のゲートおよびドレインをともに連結されることによって、ビット線230上の電流が感知される。次いで、電流がトランジスタ204を通って流動し、それによって、この電圧のための「保持」コンデンサとしても機能する、トランジスタ214のゲート - ソースにわたって出現する電圧を生成する。本開

40

50

示の範囲内で、PMOSトランジスタの代わりにN型金属酸化膜半導体（NMOS）トランジスタが使用されてもよく、本開示の利益を有する、半導体およびメモリ回路設計における当業者であれば、NMOSトランジスタを使用して、そのような回路を設計できることが考慮される。

【0021】

nサンプルノード232が論理高（「1」）にアサート停止されるとき、トランジスタ204は、電流基準の役割を果たし、基準電流は、「保持」コンデンサの役割を果たすトランジスタ214のゲート-ソースにわたって格納される電圧によって判定される。次いで、この基準電流は、その読み取り動作中に、ビット線ノード230に接続される単一のアサートされたメモリセル（図示せず）からの電流に対して比較されてもよい。このアサートされたメモリセルからの電流に依存して、ビット線ノード230（トランジスタ202のドレイン）上に出現する電圧は、このアソートされたメモリセルのオン（高電流）またはオフ（低電流）状態、例えば、基準電流がアサートされたメモリセル電流より大きいときの第1の電圧レベル、および基準電流がアサートされたメモリセル電流より小さいときの第2の電圧レベルにおけるビット線ノード230に基づいて、その論理状態を変化させることができが観察され得る。観察される電流の変化が、以降でより完全に説明されるように、アサートされている単一のメモリセルの状態変化によって引き起こされるため、この動作は、ビット線ノード230に接続されるメモリセルの数とは無関係である。

10

【0022】

nリセットノード234が論理低にアサートされるとき、トランジスタ208は、電力循環中にトランジスタ204のゲート端子をvppinノード236上に存在するV<sub>DD</sub>電位まで放電するため、または読み取り動作を開始／終了するために使用されてもよい。トランジスタ218は、ノード240上のサンプル信号とともに、トランジスタ210をアサート停止させることに起因する「保持」ステップ電圧を相殺するために電荷補償として使用されてもよい。これは、トランジスタ204によって生成される基準電流が、メモリアレイビット線ノード230上に最初に存在した電流以上であることを保証するために必要とされ得る。トランジスタ202は、随意的であるが、好ましくは、本開示の種々の実施形態に従って利用される他のトランジスタから、書き込み動作中にビット線ノード230上に存在する高い電圧を隔離するために使用されることが可能。トランジスタ214のゲート-電圧を備える、「保持」コンデンサは、代替として、本開示の具体的な例示的実施形態に従って、実際のコンデンサを使用することによって提供され得ることに留意されたい。

20

【0023】

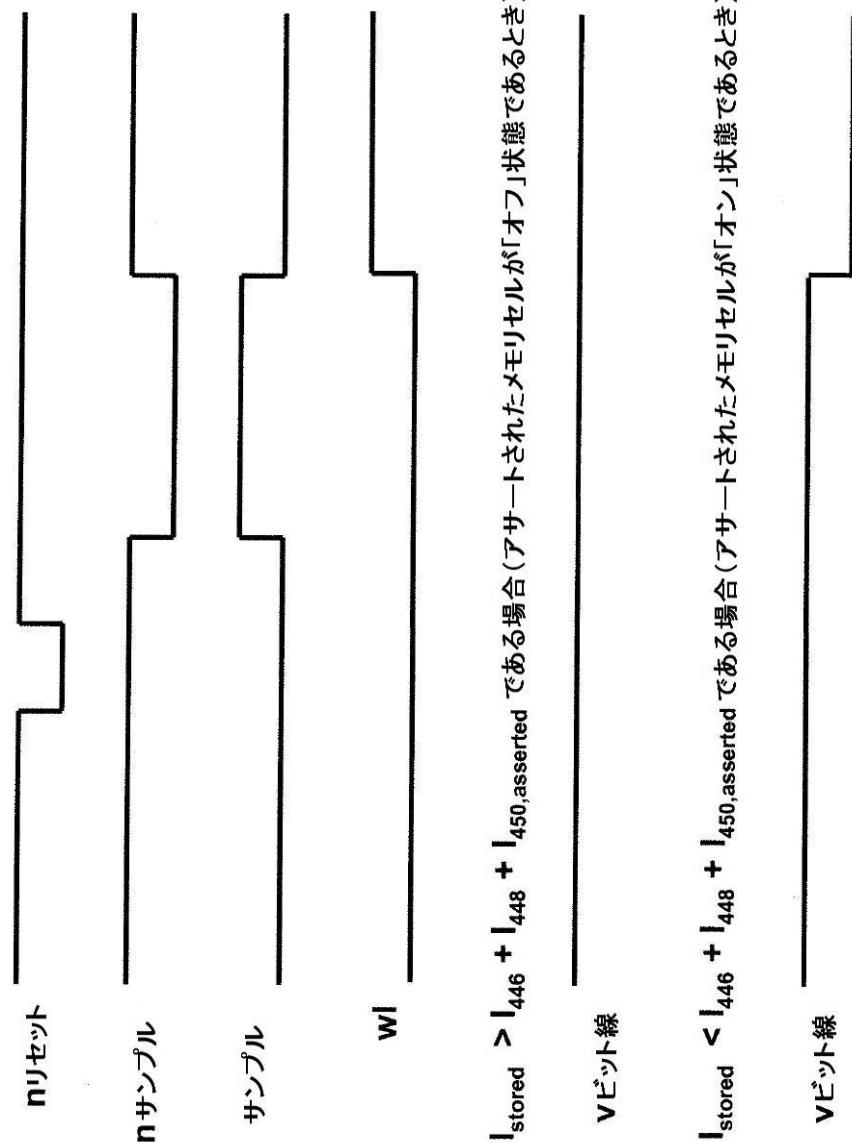

図3を参照すると、図2に示される自己バイアス電流基準（回路ブロック442）を利用する回路をモデル化するために使用される、概略図が描写されている。電流源446は、ビット線ノード230に接続する他の回路ブロック（図示せず）によって生成される、漏出電流を含むために使用される。トランジスタ448は、ビット線ノード230に接続される、大量のアサート停止されたメモリセルを含むために使用される。トランジスタ450は、読み取り動作のために、w1ノード452を用いて、アサートされるビット線ノード230に接続される単一のメモリセルを表す。コンデンサ454は、ビット線ノード230と関連付けられる寄生静電容量を含むために使用される。

30

【0024】

図4を参照すると、アサートされたメモリセルの「オン」および「オフ」状態の両方について図3に示される回路モデルと関連付けられる、読み取り動作タイミング波形が描写されている。読み取り動作は、nリセットノード234が、トランジスタ204のゲート端子をvppinノード236上に存在するV<sub>DD</sub>電位まで放電する論理低に簡潔にアサートされるときに始まる。これはまた、トランジスタ214のゲート端子上に存在する、任意の格納された電荷を放電する働きもする。読み取り動作は、トランジスタ214のゲート端子上に存在する格納された電荷によって判定されるように、トランジスタ202を介してトランジスタ204によって生成されている電流I<sub>store</sub>をもたらす、nサンプルノード2

40

50

32およびサンプルノード240を循環させることによって継続する。I<sub>store</sub>の値は、以下のように概算され得る。

I<sub>store</sub> ~ I<sub>446</sub> + I<sub>448</sub> + I<sub>450</sub>, de-asserted

【0025】

これはまた、トランジスタ204上に存在するゲート-ソース電圧によって判定されるように、v<sub>ppin</sub>ノード236上に存在するV<sub>DD</sub>電位を下回る電圧にビット線ノード230を強制させる。いったんサンプルノード232およびサンプルノード240の循環が完了すると、w1ノード452が遷移させられ、メモリセルトランジスタ450をアサートする。メモリセルトランジスタ450がアサートされると、ビット線ノード230は、2つの方法のうちの1つで応答するであろう。

1) メモリセルトランジスタ450が「オフ」状態である場合には、ビット線ノード230は、以下の事実に基づいて、不变(V<sub>dd</sub>電位に近い)のままである。

I<sub>store</sub> > I<sub>446</sub> + I<sub>448</sub> + I<sub>450</sub>, asserted

結果として、ビット線ノード230は、論理高状態にあると見なされ得る。

2) メモリセルトランジスタ450が「オン」状態である場合には、ビット線ノード230は、以下の事実に基づいて、接地電位近くまで放電されるであろう。

I<sub>store</sub> < I<sub>446</sub> + I<sub>448</sub> + I<sub>450</sub>, asserted

結果として、ビット線ノード230は、論理低状態にあると見なすことができる。

【0026】

したがって、メモリセルトランジスタ450の「オン」または「オフ」状態は、ビット線ノード230上に存在する電圧を監視することによって、容易に判定することができる。読取動作は、w1ノード452(図4では示されていない)を遷移させることによって、メモリセルトランジスタ450がアサート停止されるときに終了させられる。

【0027】

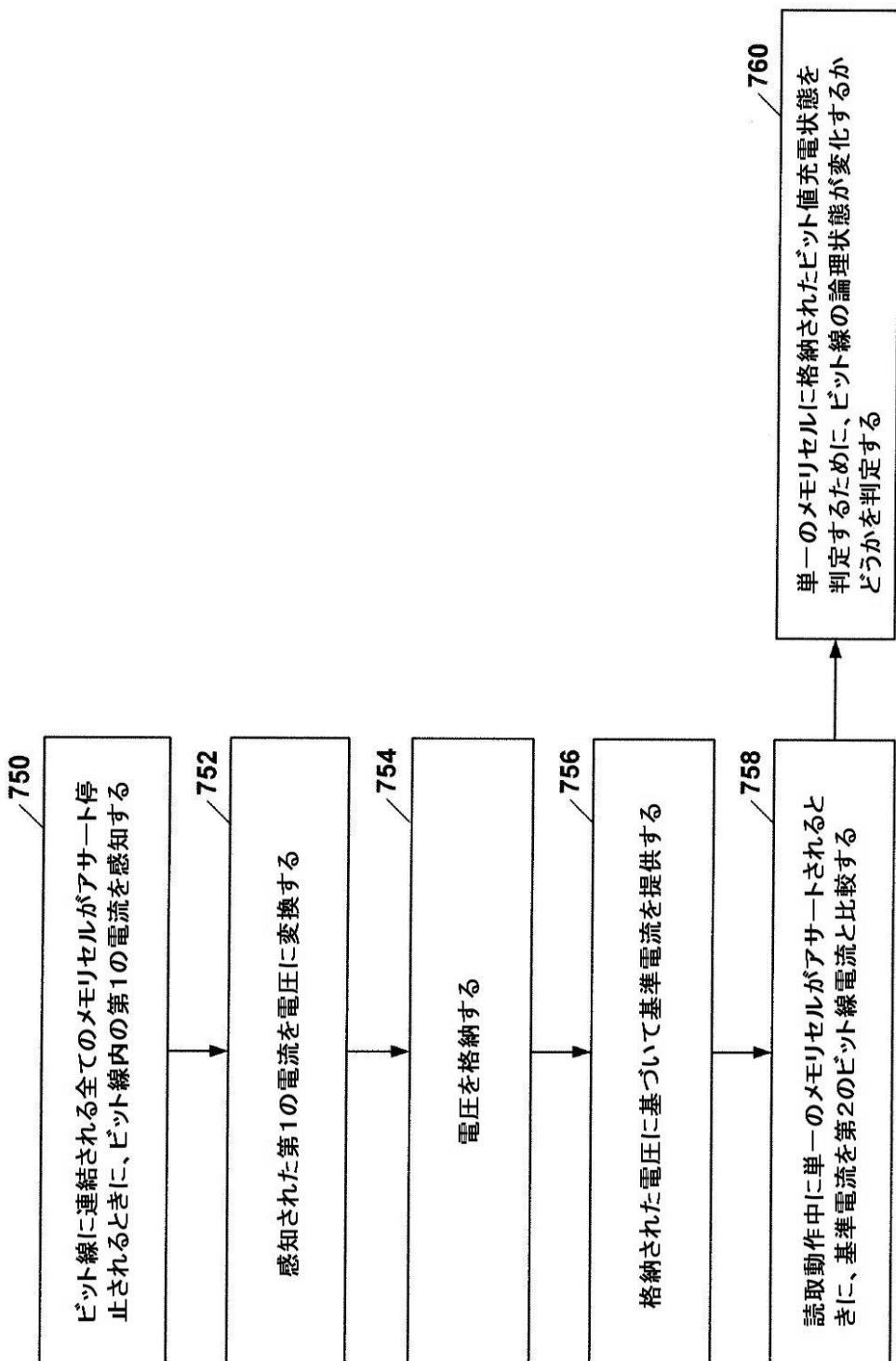

図5を参照すると、本開示の具体的な例示的実施形態による、自己バイアス電流基準を利用する回路と関連付けられる流れ図が描写されている。ステップ750では、ビット線に連結される全てのメモリセルがアサート停止されるときに、第1のビット線電流が感知される。ステップ752では、感知された第1のビット線電流が電圧に変換され、ステップ754では、電圧が、例えば、電圧格納コンデンサの役割を果たすトランジスタ214のゲート-ソース接合部に格納される。ステップ756では、格納された電圧に基づいて、基準電流が提供される。ステップ758では、それに連結される単一のメモリセルが読取動作中にアサートされるときに、基準電流が第2のビット線電流と比較される。ステップ760では、単一のメモリセルに格納されたビット値充電状態を判定するために、ビット線の論理状態が変化するかどうか判定が行われる。

【0028】

本開示の教示によると、EEPROMアレイからデータを適正に読み出すための既存の解決策の制限を効果的に排除する、「自己バイアス型」電流基準が生成され得る。供給電圧より小さい事前充電電圧の使用は、電力消費を削減する。本開示の種々の実施形態は、加工費を削減し、例えば、限定されないが、直列EEPROM製品等のよりロバストなメモリデバイスを可能にするために使用され得る。

【0029】

本開示の実施形態は、本開示の例示的実施形態を参照することにより、描写され、説明され、定義されているが、そのような参照は、本開示への制限を示唆せず、いかなるそのような制限も推測されるものではない。開示される主題は、本開示の利益を有する当業者に想起されるように、形態および機能の相当な修正、変更、および均等物が可能である。本開示の描写および説明された実施形態は、実施例にすぎず、本開示の範囲を包括しない。

【図 1】

EEPROM およびフラッシュトランジスタ

Figure 1

【図 2】

Figure 2

【図 3】

Figure 3

【図4】

Figure 4

【図5】

Figure 5

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2013/060302

A. CLASSIFICATION OF SUBJECT MATTER

INV. G11C16/24 G11C16/28 G11C7/06 G11C7/14

ADD. G11C13/00

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                     | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2011/286259 A1 (PERNER FREDERICK [US])<br>24 November 2011 (2011-11-24)<br>paragraph [0030] - paragraphs [0051],<br>[0055]; figures 2-4b,6<br>----- | 1-3,5,<br>7-9,22      |

| A         | US 2008/106945 A1 (JO SUNG-KYU [KR] ET AL)<br>8 May 2008 (2008-05-08)<br>paragraph [0026] - paragraph [0055];<br>figures 3-5<br>-----                  | 4,6,<br>10-21         |

| A         |                                                                                                                                                        | 1,8,9,<br>14,22       |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

16 January 2014

24/01/2014

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Cummings, Anthony

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2013/060302

| Patent document cited in search report | Publication date | Patent family member(s)            | Publication date         |

|----------------------------------------|------------------|------------------------------------|--------------------------|

| US 2011286259 A1                       | 24-11-2011       | NONE                               |                          |

| US 2008106945 A1                       | 08-05-2008       | CN 101174467 A<br>US 2008106945 A1 | 07-05-2008<br>08-05-2008 |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ

(72)発明者 ミエトゥス, デイビッド フランシス

アメリカ合衆国 アリゾナ 85138, マリコパ, ウエスト ウィルド ホース トレイル

43316

F ターム(参考) 5B225 BA02 CA14 DA01 EB01 ED09 EE02 EG10 EG16