(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4664725号

(P4664725)

(45) 発行日 平成23年4月6日(2011.4.6)

(24) 登録日 平成23年1月14日(2011.1.14)

(51) Int.Cl.

H01S 5/343 (2006.01)

G02F 1/017 (2006.01)

F 1

H01S 5/343

G02F 1/017 503

請求項の数 16 (全 15 頁)

|           |                               |           |                                                            |

|-----------|-------------------------------|-----------|------------------------------------------------------------|

| (21) 出願番号 | 特願2005-122016 (P2005-122016)  | (73) 特許権者 | 301005371<br>日本オプネクスト株式会社<br>神奈川県横浜市戸塚区戸塚町216番地            |

| (22) 出願日  | 平成17年4月20日 (2005.4.20)        | (74) 代理人  | 110000350<br>ボレール特許業務法人                                    |

| (65) 公開番号 | 特開2006-303147 (P2006-303147A) | (74) 代理人  | 100068504<br>弁理士 小川 勝男                                     |

| (43) 公開日  | 平成18年11月2日 (2006.11.2)        | (74) 代理人  | 100086656<br>弁理士 田中 恭助                                     |

| 審査請求日     | 平成19年11月8日 (2007.11.8)        | (72) 発明者  | 北谷 健<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所 中央研究所内            |

|           |                               | (72) 発明者  | 青木 雅博<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所 中央研究所内<br>最終頁に続く |

(54) 【発明の名称】半導体レーザ素子

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板と前記半導体基板上に形成された半導体多層構造とを備えた半導体素子であつて、

該光半導体素子を構成する多層構造内に、第1の半導体層、第2の半導体層、及びその両層の中間に位置する第3の半導体層から成る半導体層を1組、又は2組以上有し、

そのうちの少なくとも1組の前記半導体層において、前記第3の半導体層は交互に積層された第1種と第2種の半導体層を含むタイプII型の超格子層であり、前記第1種の半導体層は段階的に膜厚が減少し、前記第2種の半導体層は同じ膜厚を有し、

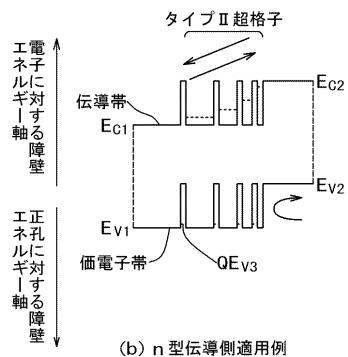

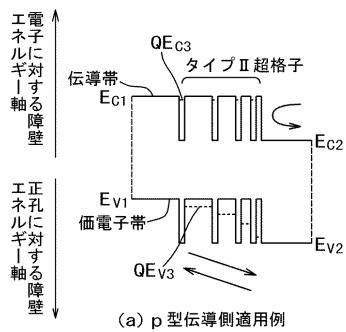

電子に対するエネルギー障壁として見た時に、第1の半導体層の伝導帯のエネルギー位置( $E_{C1}$ )は、第2の半導体層の伝導帯のエネルギー位置( $E_{C2}$ )より高く、且つ第3の半導体層の伝導帯における量子準位が形成されるエネルギー位置( $QE_{C3}$ )は、電圧が印加されていない $E_{C1}$ と $E_{C2}$ の間にあって、 $E_{C1}$ と $E_{C2}$ のエネルギー差の7割以上10割未満の値をとり、正孔に対するエネルギー障壁として見た時に、第1の半導体層の価電子帯のエネルギー位置( $E_{V1}$ )は、第2の半導体層の価電子帯のエネルギー位置( $E_{V2}$ )より低く、且つ第3の半導体層の価電子帯における量子準位が形成されるエネルギー位置( $QE_{V3}$ )は、電圧が印加されていない $E_{V1}$ と $E_{V2}$ の間にあって、 $E_{V1}$ と $QE_{V3}$ のエネルギー差が、第1の半導体層から、第2の半導体層の方向に向かって段階的に大きく成るように構成されていることを特徴とする半導体レーザ素子。

## 【請求項2】

10

20

請求項 1 に記載の半導体レーザ素子であって、光を発生する活性層と、発生した光を閉じ込めるクラッド層と、発生した光からレーザ光を得るための共振器構造を有することを特徴とする半導体レーザ素子。

【請求項 3】

請求項 1 に記載の半導体レーザ素子であって、光を吸収する吸収層と、光を閉じ込めるクラッド層を有し、吸収した光を電流として取り出すことを特徴とする半導体レーザ素子。

【請求項 4】

請求項 1 に記載の第 1、第 2、及び第 3 の半導体層は、III族元素として Al、Ga、In、B、Tl のうち少なくとも 1 種類の原子を有し、V 族原子として、N、P、As、Sb、Bi のうち少なくとも 1 種類の原子を有する III-V 族化合物半導体から選ばれることを特徴する半導体レーザ素子。

10

【請求項 5】

請求項 1 に記載の第 1、第 2、及び第 3 の半導体層は、AlAs、GaAs、InAs、AlP、GaP、InP、AlGaAs、GaInAs、AlGaInAs、GaAsP、GaInP、GaInAsP、GaInNAs、GaNAs、InNAs、GaNAsPから選ばれることを特徴とする半導体レーザ素子。

【請求項 6】

半導体基板と前記半導体基板上に形成された半導体多層構造とを備えた半導体素子であつて、

該光半導体素子を構成する多層構造内に、第 1 の半導体層、第 2 の半導体層、及びその両層の中間に位置する第 3 の半導体層から成る半導体層を 1 組、又は 2 組以上有し、

20

そのうちの少なくとも 1 組の前記半導体層において、前記第 3 の半導体層は、交互に積層された第 1 種と第 2 種の半導体層を含むタイプ II 型の超格子層であり、2 つの層に電圧が印加されないで、前記第 1 種の半導体層は段階的に膜厚が減少し、前記第 2 種の半導体層は同じ膜厚を有し、

正孔に対するエネルギー障壁として見た時に、第 1 の半導体層の価電子帯のエネルギー位置 ( $E_{V1}$ ) は、第 2 の半導体層の価電子帯のエネルギー位置 ( $E_{V2}$ ) より高く、且つ第 3 の半導体層の価電子帯における量子準位が形成されるエネルギー位置 ( $QE_{V3}$ ) は、電圧が印加されていない  $E_{V1}$  と  $E_{V2}$  の間にあって、 $E_{V1}$  と  $E_{V2}$  のエネルギー差の 7 割以上 10 割未満の値をとり、電子に対するエネルギー障壁として見た時に、第 1 の半導体層の伝導帯のエネルギー位置 ( $E_{C1}$ ) は、第 2 の半導体層の伝導帯のエネルギー位置 ( $E_{C2}$ ) より低く、且つ第 3 の半導体層の伝導帯における量子準位が形成されるエネルギー位置 ( $QE_{C3}$ ) は、電圧が印加されていない  $E_{C1}$  と  $E_{C2}$  の間にあって、 $E_{C1}$  と  $QE_{C3}$  のエネルギー差が、第 1 の半導体層から、第 2 の半導体層の方向に向かって段階的に大きくなるように構成されていることを特徴とする半導体レーザ素子。

30

【請求項 7】

請求項 6 に記載の半導体レーザ素子であつて、光を発生する活性層と、発生した光を閉じ込めるクラッド層と、発生した光からレーザ光を得るための共振器構造を有することを特徴とする半導体レーザ素子。

【請求項 8】

請求項 6 に記載の半導体レーザ素子であつて、光を吸収する吸収層と、光を閉じ込めるクラッド層を有し、吸収した光を電流として取り出すことを特徴とする半導体レーザ素子。

40

【請求項 9】

請求項 6 に記載の第 1、第 2、及び第 3 の半導体層は、III 族元素として Al、Ga、In、B、Tl のうち少なくとも 1 種類の原子を有し、V 族原子として、N、P、As、Sb、Bi のうち少なくとも 1 種類の原子を有する III-V 族化合物半導体から選ばれることを特徴とする半導体レーザ素子。

【請求項 10】

請求項 6 に記載の第 1、第 2、及び第 3 の半導体層は、AlAs、GaAs、InAs、AlP、GaP、

50

Imp、AlGaAs、GaInAs、AlGaInAs、GaAsP、GaInP、GaInAsP、GaInNAs、GaNAs、InNAs、GaN

PAsから選ばれることを特徴とする半導体レーザ素子。

【請求項 1 1】

半導体基板と前記半導体基板上に形成された半導体多層構造とを備えた半導体素子であ

つて、

該光半導体素子を構成する多層構造内に、タイプII型のヘテロ接合となる第1と第2の

半導体層、及びその中間に位置する第3の半導体層から成る半導体層を1組、又は2組以

上有し、

そのうちの少なくとも1組の前記半導体層において、第3の半導体層は二種類の半導体

層が交互に積層されてなるタイプII型超格子層であり、該超格子層を構成する一方の半導

体層の膜厚は0.2 nm以上100 nm以下の範囲で第1の半導体から、第2の半導体側に向かっ

て段階的に増大し、もう一方の半導体層の膜厚は均一に0.2 nm以上3 nm以下の範囲内の定

値に設定されていることを特徴とする半導体レーザ素子。

【請求項 1 2】

請求項 1 1 に記載の半導体レーザ素子であって、光を発生する活性層と、発生した光を

閉じ込めるクラッド層と、発生した光からレーザ光を得るために共振器構造を有すること

を特徴とする半導体レーザ素子。

【請求項 1 3】

請求項 1 1 に記載の半導体レーザ素子であって、光を吸収する吸収層と、光を閉じ込

めるクラッド層を有し、吸収した光を電流として取り出すことを特徴とする半導体レーザ素

子。

【請求項 1 4】

請求項 1 1 に記載の半導体レーザ素子であって、

前記第3の半導体層は、前記第1の半導体層の材料と前記第2の半導体層の材料が交互

に積層されてなるタイプII型超格子層であることを特徴とする半導体レーザ素子。

【請求項 1 5】

請求項 1 1 に記載の第1、第2、及び第3の半導体層は、III族元素としてAl、Ga、In

、B、TIのうち少なくとも1種類の原子を有し、V族原子として、N、P、As、Sb、Biのうち

少なくとも1種類の原子を有するIII-V族化合物半導体から選ばれることを特徴とする半

導体レーザ素子。

【請求項 1 6】

請求項 1 1 に記載の第1、第2、及び第3の半導体層は、AlAs、GaAs、InAs、AlP、GaP

、Imp、AlGaAs、GaInAs、AlGaInAs、GaAsP、GaInP、GaInAsP、GaInNAs、GaNAs、InNAs、G

anPAsから選ばれることを特徴とする半導体レーザ素子。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、光半導体素子に関し、特にヘテロ界面でのキャリアの伝導特性を改善する技

術に関する。

【背景技術】

【0 0 0 2】

近年のインターネット人口の爆発的増大等により、情報処理の大容量化に対する要求が

高まっている。LANやMANなどの比較的伝送距離の短い通信ネットワークにおいては、5-10

年後に、従来、幹線系通信網の伝送速度であったGb/sレベルの伝送速度が必要になると予

測されている。ここで用いられる光通信モジュールにおいては、先に述べた高速変調が可

能であるという性能面での要求に加えて、莫大な数の一般ユーザが使用することを念頭に

おき、低コストで提供することも必須の用件となる。よって、高温での特性劣化の小さい

半導体レーザが、その光源として適すると考えられる。

【0 0 0 3】

従来の半導体レーザ、変調器等の光通信用デバイスには、主にInP基板上に形成されるG

10

20

30

40

50

AlInAsPが用いられてきた。本材料は4種類の主構成元素から成る4元系材料であり、バンドギャップ、及び格子定数の設計自由度が高い。よって、光通信に適合した1.3μm、及び1.55μm帯の波長組成において、量子井戸活性層に所望の格子歪を導入することが容易であり、それにより素子の高性能化が達成されてきた。一方で、材料物性上、量子井戸活性層における井戸層と障壁層間の伝導帯のエネルギー差( $E_c$ )が小さいため、電子の閉じ込めが小さく高温での特性劣化が顕著である。また、同様の理由で活性層の利得が小さく、緩和振動周波数が小さい。以上から、GaInAsPを用いた半導体レーザでは、今後の高速化や低コスト化に対する要求を満たすことは困難であると予測されている。

#### 【0004】

それに対して、通信用半導体レーザの特性を抜本的に改善することが可能な材料として、近年、InP基板上に形成されるAlGaInAsの検討が各所で進められている。本材料で形成した量子井戸活性層は、GaInAsPと比較して  $E_c$  が大きいため、高温でも電子を有効に閉じ込められる。さらに活性層の利得が大きいため、高温・高速変調特性に優れた半導体レーザが実現可能である。また、同様の効果により、電界吸収型光変調器における消光特性の改善等も報告されている。

#### 【0005】

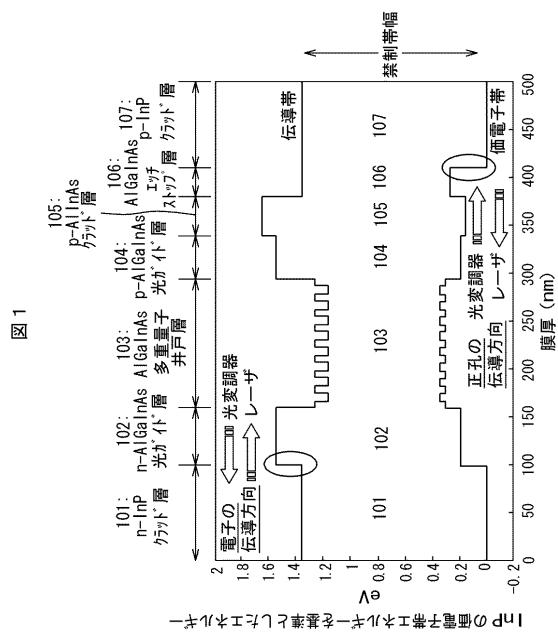

図1に、典型的なAlGaInAs系光素子のバンド構造図の一例を示す。図の上側の線は伝導帯のエネルギー位置、下側の線は価電子帯のエネルギー位置を示し、両線間の距離は、各層の禁制帯幅に相当する。例えば、AlGaInAs系光素子においても、クラッド層としてはInPが用いられている等、従来材料であるGaInAsP系の半導体層が適材適所に導入され、これまでにGaInAsP系素子に対して培われてきた素子設計・作製技術を要所に適用することにより、優れた性能が実現できている。

#### 【0006】

また、技術の別の例としてGaAs基板上に形成されるGaInNAsを活性層に用いた半導体レーザがある。GaInNAsも近年開発された半導体材料であるが、AlGaInAsと比較して、活性層にさらに大きな  $E_c$  を実現でき、更なる半導体レーザの高速化において非常に有望な材料であると期待されている。一方で、本材料は、N組成の増大に伴い発光特性が低下してしまう課題があるため、発振波長を1.3μm帯に適合させるためにIn組成を高くしている。その結果、+2%近い高圧縮歪を有するGaInNAs層が、井戸層に用いられている。この大きな格子歪は、素子の性能や長期信頼性へ悪影響を及ぼす可能性が高いため、障壁層としては、引張歪を有するGaNPs等を導入して歪補償構造とし、素子全体の平均格子歪量を低減しようとする試みが検討されている。

#### 【0007】

以上に挙げた2例に共通するのは、V族として少なくともAsを含むIII-V族化合物半導体層と、V族として少なくともAsとは異なる原子(例えばN, P)を含むIII-V族化合物半導体層の積層構造を導入することによって、良好な素子特性の実現を図っていることである。尚、このようなV族構成原子の異なる半導体層同士の積層構造が、ここで記述していない他の多くの素子にも適用され、特性改善に寄与し得る事は言うまでも無い。また、例としては半導体レーザ、及び光変調器等の光素子のみを挙げたが、本積層構造を適用して形成する限り、これに限定されるものではない。

#### 【0008】

【特許文献1】特開平10-27925号公報

【非特許文献1】ジャーナル・オブ・アプライドフィジックス 73巻、1993年、p.21

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

本願発明は、V族構成原子が異なるIII-V族化合物半導体層の積層構造を含む半導体素子、例えば、V族として少なくともAsを含むIII-V族化合物半導体層と、V族として少なくともAsとは異なる原子を含むIII-V族化合物半導体層の積層構造を含む半導体素子における

10

20

30

40

50

課題を解決し、良好な素子特性を実現しようとするものである。ここで、従来素子における課題を明確にするため、図1に挙げたAlGaInAs系光素子のバンド構造図に基づき、キャリアの伝導について考察する。ここでは代表的な光素子として、レーザ、及び電界吸収型光変調器を考えた。図において本願発明が着目するV族構成原子の異なる積層構造は、n-InPクラッド層101/n-AlGaInAs光ガイド層102へテロ界面、及びp-InGaInAsエッチストップ層106/p-InPクラッド層107へテロ界面に導入されている。これらへテロ界面のバンド構造では、材料物的に伝導帯、及び価電子帯共にバンドエネルギー差が生じ、AlGaInAs層の伝導帯、及び価電子帯エネルギー位置が、図中で両方共にInP層のそれよりも高くなっている。これは、所謂タイプIIのバンドラインナップと呼ばれるものである。

## 【0010】

10

レーザの場合、電子はn-InPクラッド層101側から伝導帯を伝導してAlGaInAs多重量子井戸活性層103に注入され、正孔はp-InPクラッド層107側から価電子帯を伝導してAlGaInAs多重量子井戸活性層103に注入されて、これらが再結合して発光を得る。一方、電界吸収型光変調器においては、レーザとは逆に、AlGaInAs多重量子井戸活性層103で吸収した光から電子と正孔が生成され、電子は伝導帯を伝導してn-InPクラッド層101側から取り出され、正孔は価電子帯を伝導してp-InPクラッド層107側から取り出される。ここで、InPクラッド層/AlGaInAs層へテロ界面のバンド構造がタイプIIであるため、レーザにおいては、n-InPクラッド層101/n-AlGaInAs光ガイド層102界面の伝導帯のエネルギー差( $E_c$ )が、電子の注入において障害となる。同様に、光変調器の場合は、p-AlGaInAsエッチストップ層106/p-InPクラッド層107へテロ界面の価電子帯のエネルギー障壁( $E_v$ )が、正孔の取り出しに対する障害となる。特に正孔は、電子と比較して有効質量が大きいので、エネルギー障壁を越えて伝導できるキャリアの割合がより小さくなる。そのため、例えば光変調器においては、InGaAlAs層内への正孔の蓄積低減が、素子特性改善への大きな課題となっている。

## 【0011】

20

また、別の例として先に挙げたGaInNAs半導体レーザにおいても、歪補償のために障壁層として導入したGaNPAと光ガイド層であるGaAsとのヘテロ界面が、V族構成原子の異なるタイプIIの積層構造となる。これは正孔の良好な注入に対する障害となり、しきい値電流増大などの素子特性劣化を引き起こすことが懸念される。

## 【0012】

30

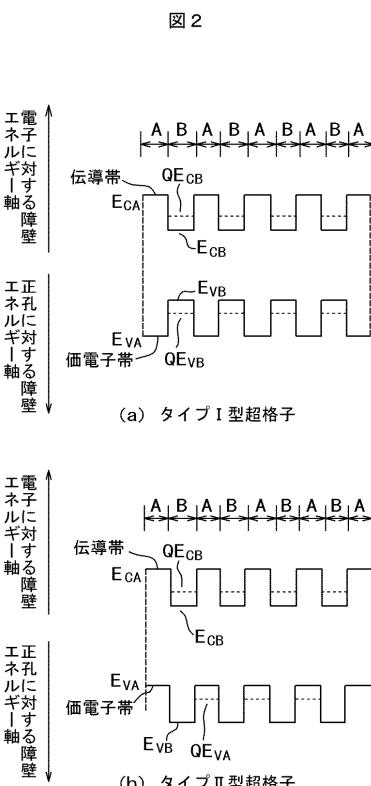

このような半導体ヘテロ界面におけるバンドエネルギー差の影響を低減し、キャリアの伝導特性を改善しようとする試みが、これまでに報告されている。その一例が、ヘテロ界面における超格子層の導入である。ここで超格子層について説明しておく。超格子層とは、異なる半導体Aと半導体Bを交互に複数層にわたって積層したものであり、半導体Aと半導体Bのヘテロ界面におけるバンドエネルギー構造から、大きく3つのタイプに分類される。ここでは、本発明に関連の深いタイプI型、及びタイプII型について詳しく説明しておく。

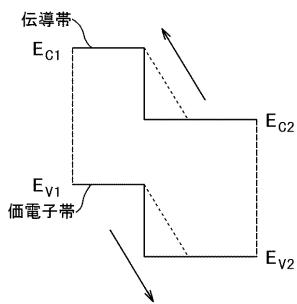

## 【0013】

図2に、タイプI、及びタイプII型超格子のバンド構造図を示した。図には、電子に対するエネルギー障壁高さ軸、及び、正孔に対するエネルギー障壁高さの軸を同時に示してある。電子に対するエネルギー障壁として見た時に、(a)に示すタイプI型は、半導体Aの伝導帯のエネルギー位置( $E_{CA}$ )が、半導体Bの伝導帯のエネルギー位置( $E_{CB}$ )よりも高く、且つ、正孔に対するエネルギー障壁として見た時に、半導体Aの価電子帯のエネルギー位置( $E_{VA}$ )が、半導体Bの価電子帯のエネルギー位置( $E_{VB}$ )も高くなっている。そのため、これら2種類の半導体を交互に積層した際には、伝導帯、価電子帯とともに、半導体Bの側が井戸層となる井戸型ポテンシャル構造が形成され、エネルギーの低い井戸層内に、電子、正孔が共に閉じ込められる。ここで、半導体Bの膜厚を電子の波動性が現れるくらい十分薄くしておくことにより、半導体Bの伝導帯、あるいは価電子帯頂上のエネルギーよりも少し離れた位置に(図の点線)量子準位 $QE_{CB}$ 、及び $QE_{VB}$ が形成され、半導体B内に閉じ込められた電子、及び正孔は、ある固有のエネルギー位置にしか存在できなくなる。伝導帯

40

50

側、価電子帯側共に、量子準位が半導体B側に形成されるのが、タイプI型超格子の大きな特徴である。一方、(b)に示すタイプII型は、タイプI型と同様に、電子に対するエネルギー障壁として見た時の半導体Aの伝導帯のエネルギー位置( $E_{CA}$ )は、半導体Bの伝導帯のエネルギー位置( $E_{CB}$ )よりも高いが、タイプI型と異なり、正孔に対するエネルギー障壁として見た時の半導体Aの価電子帯のエネルギー位置( $E_{VA}$ )は、半導体Bの価電子帯のエネルギー位置( $E_{VB}$ )よりも低くなっている。これにより、井戸層が、伝導帯側、及び価電子帯側で異なる層内に存在することになる。図の例では、伝導帯側の量子準位( $QE_{CB}$ )は、半導体B内に形成され、価電子帯側の量子準位( $QE_{VA}$ )は、半導体A内に形成される。量子準位が形成されるエネルギー位置は、井戸層の膜厚を変化させることにより、人為的に制御することが出来る。

10

#### 【0014】

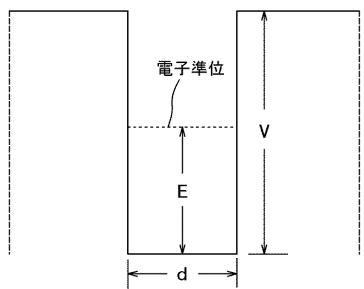

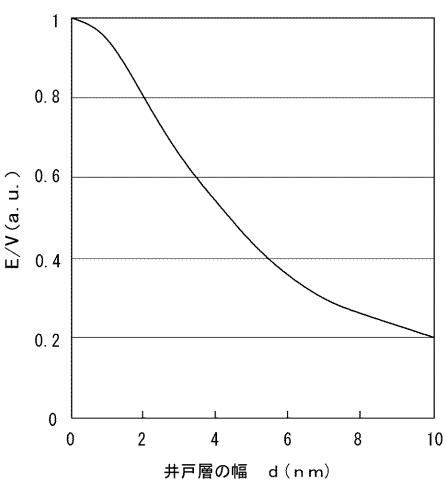

ここで、量子準位のエネルギー位置について計算した結果を次に示す。図3は、検討に用いた量子井戸構造のバンド構造図である。ここで、井戸幅をd、障壁層のエネルギー高さをV、量子準位のエネルギー高さをEとした。図4に、dに対するE/Vの値の検討結果を示す。dを厚くしていくことにより、E/Vが徐々に低下していくことがわかる。この計算においてはdは10 nmまでしか示されていないが、dを十分に厚くしていくと、キャリアの波動性が失われて量子準位は形成されなくなり、通常の半導体層と同様に、井戸層における伝導帯の頂上にキャリアが存在するようになる。

#### 【0015】

非特許文献1に記載されている例では、V族の構成元素が等しいGaAs/AlAsタイプI型のヘテロ界面に、これらの材料からなる超格子構造を導入することでキャリアの伝導特性の改善を図っている。ヘテロ界面のGaAs側からAlAs側に向かって、超格子層におけるGaAs層は徐々に薄くし、一方、超格子層におけるAlAs層は徐々に厚くしている。これにより、超格子内に形成される量子準位のエネルギーを、伝導帯、価電子帯共に、GaAs側からAlAs側に向かって徐々に高めることができ、伝導帯、価電子帯を同時に滑らかに接続することができる。本概念をタイプII型のヘテロ構造に適用した場合にも、同様の膜厚変化を適用すれば、同様の効果が得られる。その結果、図5(a)において、ヘテロ界面の近傍に点線で示したように、ヘテロ界面のバンドエネルギー差を、伝導帯と価電子帯において同時に低減できる。これが従来の技術によるバンド接続である。

20

ここで、半導体光素子においては、電子をn型側から、同時に正孔をp型側から活性層に注入する場合、或いは活性層から電子をn型側へ、同時に正孔をp型側へ取り出す場合があり、いずれの場合も、常に電子と正孔の伝導する流れが逆方向であることは既に述べた。

30

#### 【0016】

図5(a)の従来技術を用いては、伝導帯、価電子帯が同時に滑らかに接続されているため、一方のキャリア(例えば正孔)の伝導確率は向上するが、同時に他方のキャリア(例えば電子)が同方向に漏れ出す可能性も高めてしまう。これを解決するには、図5(b)に示すように、半導体ヘテロ界面において、一方のエネルギー帯(例えば価電子帯)におけるバンドエネルギー差を、段階的に低減してキャリア(例えば正孔)を平滑に伝導させ、他方のエネルギー帯(例えば伝導帯)においては、バンドエネルギー差を不連続のまま保持するように接続することでキャリア(例えば電子)がヘテロ接合外へ漏れ出すことを防止するバンド構造が望ましいと考えられるが、従来は、それを実現する具体的手段は発明されていなかった。

40

#### 【0017】

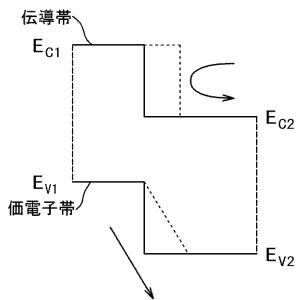

ここで従来技術の別の例として、特許文献1を挙げる。図6に素子のエネルギー・バンド図を示す。本公知例は、II-VI族化合物半導体であるp-ZnTe601とn-ZnSe603の間にZnTe/ZnSeからなるタイプII型の超格子層602を導入した構造である。超格子層におけるZnTe層の膜厚を0.3 nm、0.6 nm、0.9 nm、1.2 nm、1.5 nm、1.8 nm、2.4 nm、3 nm、5 nmと変化させ、一方、ZnSe層の膜厚は5 nmと一定値とした。価電子帯の量子準位のエネルギーは、p-ZnTe601側からn-ZnSe603側に向かって徐々に高い位置に形成されよう設計されており、これらが順バイアス印加時に一直線状に並ぶことにより、p-ZnTe601側からn-ZnSe603側へ

50

の正孔の注入効率の改善が成される。一方、伝導帯側においては、ZnSe層の膜厚が5 nmと厚いため、n-ZnSe603内の電子がZnTe/ZnSe超格子層602内に流入してしまう。よって、本公知例は、我々の発明した図5(b)に示す新規バンド構造の概念とは異なるものである。

【課題を解決するための手段】

【0018】

我々が鋭意検討した結果、タイプII型のヘテロ構造において、一方のエネルギー帯（例えば価電子帯）ではバンドエネルギー差の不連続を段階的に低減してキャリア（例えば正孔）を良好伝導させつつ、他方のエネルギー帯（例えば伝導帯）では、エネルギー不連続のままに保持して、もう一方のキャリア（例えば電子）に対する障壁効果を維持し得るエネルギーバンド構造を実現する手段が見出された。次に本発明の骨子を述べる。

10

【0019】

本願発明は、半導体基板と前記半導体基板上に形成された半導体多層構造とを備えた半導体素子であって、該光半導体素子を構成する多層構造内に、第1の半導体層、第2の半導体層、及びその両層の中間に位置する第3の半導体層から成る半導体層を1組、又は2組以上有し、そのうちの少なくとも1組の前記半導体層において、電子に対するエネルギー障壁として見た時に、第1の半導体層の伝導帯のエネルギー位置( $E_{C1}$ )は、第2の半導体層の伝導帯のエネルギー位置( $E_{C2}$ )より高く、且つ第3の半導体層の伝導帯における量子準位が形成されるエネルギー位置( $QE_{C3}$ )は、 $E_{C1}$ と $E_{C2}$ の間にあって、 $E_{C2}$ を基準として、 $E_{C1}$ と $E_{C2}$ のエネルギー差の7割以上10割未満の値をとり、正孔に対するエネルギー障壁として見た時に、第1の半導体層の価電子帯のエネルギー位置( $E_{V1}$ )は、第2の半導体層の価電子帯のエネルギー位置( $E_{V2}$ )より低く、且つ第3の半導体層の価電子帯における量子準位が形成されるエネルギー位置( $QE_{V3}$ )は、 $E_{V1}$ と $E_{V2}$ の間にあって、 $E_{V1}$ を基準として、 $E_{V1}$ と $QE_{V3}$ のエネルギー差が、第1の半導体層から、第2の半導体層の方向に向かって段階的に大きく成るように構成されることにより達成される。

20

【0020】

又は、半導体基板と前記半導体基板上に形成された半導体多層構造とを備えた半導体素子であって、該光半導体素子を構成する多層構造内に、第1の半導体層、第2の半導体層、及びその両層の中間に位置する第3の半導体層から成る半導体層を1組、又は2組以上有し、そのうちの少なくとも1組の前期半導体層において、正孔に対するエネルギー障壁として見た時に、第1の半導体層の価電子帯のエネルギー位置( $E_{V1}$ )は、第2の半導体層の価電子帯のエネルギー位置( $E_{V2}$ )より高く、且つ第3の半導体層の価電子帯における量子準位が形成されるエネルギー位置( $QE_{V3}$ )は、 $E_{V1}$ と $E_{V2}$ の間にあって、 $E_{V2}$ を基準として、 $E_{V1}$ と $E_{V2}$ のエネルギー差の7割以上10割未満の値をとり、電子に対するエネルギー障壁として見た時に、第1の半導体層の伝導帯のエネルギー位置( $E_{C1}$ )は、第2の半導体層の伝導帯のエネルギー位置( $E_{C2}$ )より低く、且つ第3の半導体層の伝導帯における量子準位が形成されるエネルギー位置( $QE_{C3}$ )は、 $E_{C1}$ と $E_{C2}$ の間にあって、 $E_{C1}$ を基準として、 $E_{C1}$ と $QE_{C3}$ のエネルギー差が、第1の半導体層から、第2の半導体層の方向に向かって段階的に大きく成るように構成されることにより達成される。

30

【0021】

或いは、半導体基板と前記半導体基板上に形成された半導体多層構造とを備えた半導体素子であって、該光半導体素子を構成する多層構造内に、タイプII型のヘテロ接合となる第1と第2の半導体層、及びその中間に位置する第3の半導体層から成る半導体層を1組、又は2組以上有し、そのうちの少なくとも1組の前期半導体層において、第3の半導体層はタイプII型超格子層であり、該超格子層を構成する一方の半導体層の膜厚は0.2 nm以上100 nm以下の範囲で第1の半導体から、第2の半導体側に向かって段階的に増大し、もう一方の半導体層の膜厚は0.2 nm以上3 nm以下の範囲内の所望の値に設定されていることにより達成される。

40

【0022】

次に、本発明のバンド構造を実現するための、伝導帯、及び価電子帯における量子準位のエネルギー位置設定に関する具体的根拠を述べる。既に述べたように、所望のエネルギ

50

一位置に量子準位を設定するためには、超格子層の各層の膜厚を精密に制御する必要があり、既に図4に計算結果を示している。

#### 【0023】

量子準位のエネルギー位置を段階的に大きくする側の超格子層における膜厚は、量子効果が得られなくなるために十分に厚い膜厚として100 nmを上限として、徐々に減少させることで達成可能である。このとき、下限値は、1原子層に相当する約0.2 nmとなる。次に、バンドエネルギー差を、不連続のままに保持する側の膜厚に関して検討を行った。Eを高めてVに近づけることにより、量子井戸内にキャリアが存在できる確率を小さくすることができるので、量子井戸内へのキャリアの進入を妨げることができる。具体的には、dを小さくすることによってEを高めることができる。このようなエネルギー位置への量子準位の形成により、半導体ヘテロ接合におけるバンドエネルギー差を、不連続のままに保持することができる。10

#### 【0024】

図4の結果から、dが3 nmのとき、EをVの約7割に相当するエネルギー値まで高められることがわかる。このような量子準位の形成により、半導体ヘテロ接合におけるバンドエネルギー差を、実効的に不連続のままに保持することができる。そこで、バンドエネルギー差を保持するための膜厚設定値を、1原子層に相当する下限値0.2 nmから、上限値3 nmの範囲の中の所望の値と定めた。超格子内において、本膜厚範囲内で膜厚が多少変動しても、障壁効果を維持することが出来る。量子準位のエネルギー位置は、ヘテロ接合を構成する半導体材料の種類によって多少変化するが、井戸層の膜厚が3 nm以下であれば十分な障壁効果を得ることができる。尚、本膜厚範囲は、量子準位のエネルギー位置を段階的に大きくする側では障壁層が十分薄いことと等価であり、トンネル効果によって、段階的にバンドエネルギー差を低減し、もう一方のキャリアに対する伝導確率を大幅に向上することもできる。これらの相乗効果により、本願発明の超格子構造を導入することで大幅なキャリア伝導特性の改善を図ることができる。20

#### 【0025】

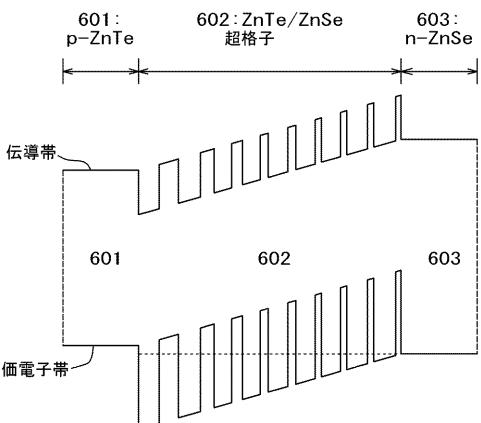

以上の検討結果から実現される本発明のバンド構造図の典型例を図7に示す。(a)は、p型伝導側に適用した例を示す。価電子帯側における量子準位( $QE_{V3}$ )を徐々に高めて、ヘテロ界面のバンドエネルギー差を段階的に低減し、正孔の伝導特性を改善する。一方で、伝導帯側では量子準位( $QE_{C3}$ )を障壁層の伝導帯位置付近まで高め、電子に対する障壁効果を維持した。また、(b)は、n型伝導側に適用した例を示す。伝導帯側における量子準位( $QE_{C3}$ )を徐々に高めて、ヘテロ界面のバンドエネルギー差を段階的に低減し、電子の伝導特性を改善する。一方で価電子帯側では、量子準位( $QE_{V3}$ )を障壁層の価電子帯付近の位置まで低下させ、正孔に対する障壁効果を維持した。尚、同様の効果が得られれば、適用場所、構造等はここのみに限定されるものではなく、最適な効果が得られるように構造を変形しても良い。30

#### 【発明の効果】

#### 【0026】

本発明によれば、半導体レーザにおける量子井戸活性層内のキャリアの閉じ込め効果を高めることができ、高温での特性劣化が改善され、活性層の利得を大きく取れる。従って、高温・高速変調特性に優れた半導体レーザが実現可能である、また電界吸収型光変調器等においては、キャリアの取り出し効率を改善し、消光特性の向上効果等も期待できる。40

#### 【発明を実施するための最良の形態】

#### 【0027】

具体的な実施の形態を説明するに先だって、本願発明の基本思想の詳細を説明する。本発明によれば、タイプIIのバンドラインナップを形成するヘテロ界面でのキャリアの伝導特性を改善するために、一方のエネルギー帯(例えば価電子帯)ではバンドエネルギー差の不連続を段階的に低減して、キャリア(例えば正孔)を良好に伝導させつつ、他方のエネルギー帯(例えば伝導帯)では、バンドエネルギー差を不連続のままに保持して、他方のキャリア(例えば電子)に対する障壁効果を維持し得るエネルギー・バンド構造を実現す50

ることができる。具体的には、ヘテロ界面にタイプII型超格子層を導入し、本超格子層を構成する一方の半導体層の膜厚を0.2 nm以上100 nm以下の範囲の値として、段階的に変化させ、他方の半導体層の膜厚を0.2 nm以上3 nm以下の範囲内の所望の値とすることで達成される。以下、本発明の具体的な実施の形態について記述する。

＜実施の形態1＞

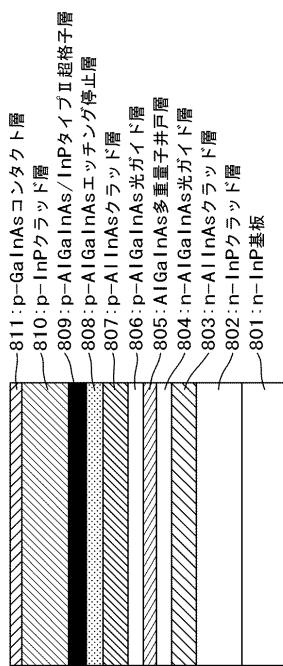

ここでは発明の実施の形態例1として、本発明による低抵抗AlGaInAs電界吸収型光変調器の作製について具体的に記述する。その素子構造を図8に示した。ここでは成長方法を有機金属気相堆積(MOCVD)法とした。MOCVD法では、III族元素の供給源として、トリエチルガリウム(TEG)、トリメチルインジウム(TMI)、トリメチルアルミニウム(TMAI)を用い、V族元素の供給源として、アルシン(AsH<sub>3</sub>)とフォスフィン(PH<sub>3</sub>)を用いた。また、n型不純物の導入ガスとしてジシラン(Si<sub>2</sub>H<sub>6</sub>)、p型不純物の導入ガスとしてジメチルジンク(DMZn)を用いた。但し、同様の構造が形成できれば、本発明の効果を得ることが可能であるので、成長法や原料に関しては、ここに記述したもののみに限定されるものではない。

【0028】

作製する半導体基板はn型InP基板801(n型ドーピング濃度=1×10<sup>18</sup>cm<sup>-3</sup>)を用いる。PH<sub>3</sub>雰囲気において、基板を昇温した後、基板温度600において第一番目の結晶成長工程として厚さ500 nmのn型InPクラッド層802(n型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)の成長を開始した。その後、厚さ50 nmのn型AlInAsクラッド層803(n型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)を成長した。さらに、厚さ50 nmのn型AlGaInAs光ガイド層804(n型ドーピング濃度=1×10<sup>18</sup>cm<sup>-3</sup>)、厚さ7 nmのノンドープAlGaInAs障壁層と厚さ9 nmのノンドープAlGaInAs井戸層からなる多重量子井戸層805(周期数:8)、厚さ45 nmのp型AlGaInAs光ガイド層806(p型ドーピング濃度=1×10<sup>17</sup>cm<sup>-3</sup>)からなる活性層を形成した後、厚さ40 nmのp型AlInAsクラッド層807(p型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)、厚さ30 nmのp型AlGaInAsエッチングストップ層808(p型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)を成長した。続いて本発明にかかわる最も重要な層である、p型AlGaInAs/InPタイプII超格子層809(p型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)を形成した。AlGaInAs層の膜厚は、10 nm、5 nm、3 nm、1 nmの順に変化させ、InP層の膜厚は、2 nmの一定値に保った。基板温度は、最初のn型InPクラッド層802内で700に達し、その後、Alを含む層内では700に保った。その後、p型InPクラッド層810(p型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)の一部を10 nm成長した後、成長中断し、成長温度を700から600に降温させた。基板温度が600に安定した後、p型InPクラッド層810(p型不純物濃度=1×10<sup>18</sup>cm<sup>-3</sup>)の残り1490 nmを成長し、成長温度を低下させながら、厚さ100 nmのp型GaInAsクラッド層811(p型不純物濃度=1×10<sup>19</sup>cm<sup>-3</sup>)を成長して結晶成長工程を終了した。

続いて、ストライプ構造作製工程、電極作製工程を経て、素子として完成した。作製された素子は、外部冷却器無しの動作状況下で10Gb/s動作を示した。また、変調時の光出力も+2dBmと良好であった。

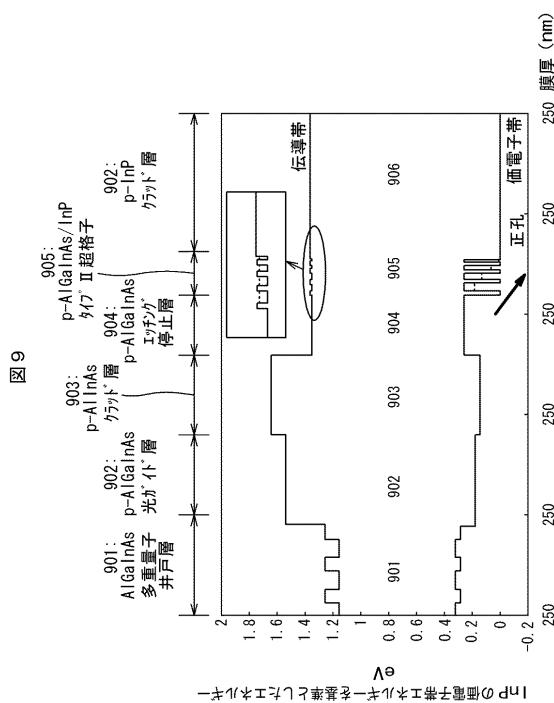

【0029】

図9に、本素子におけるタイプII型超格子導入部905付近のエネルギー・バンド図を示す。本発明によるタイプII型超格子層の導入により、量子準位を介して価電子帯におけるInGaAlAs904/InP906間のバンドエネルギー差が段階的に低減されている。これにより、正孔の蓄積を大幅に抑制できた。一方、伝導帯側においては、量子準位は量子井戸内の高いエネルギー位置に形成されている。この場合、InGaAlAs904/InP906間のバンドエネルギー差がそれほど大きくないため、電子に対する障壁効果は少ないが、InGaAlAs904/InP906間バンド構造を阻害することなくほぼ平坦に接続できるため、超格子層におけるキャリア損失が生じることは無かった。その結果、変調特性、及び光出力の改善効果が得られた。

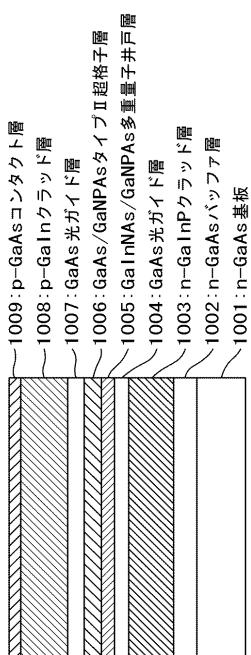

＜実施の形態2＞

ここでは、発明の実施の形態例2として、本発明によるGaInNAs半導体レーザの作製について具体的に記述する。その素子構造を図10に示した。活性層にGaInNAsを用いる場合には、Nの導入において、非平衡状態での成長法が有利であり、MOCVD法に加え、分子線エピタキシー(MBE)法等が成長方法として適している。ここでは成長方法をガスソースMBE(GS-MBE)法とした。GS-MBE法では、III族元素の供給源として、ガリウム(Ga)、インジ

10

20

30

40

50

ウム( In )を用い、V族元素の供給源として、砒素( As )に関してはAsH<sub>3</sub>を用い、燐( P )に関してはPH<sub>3</sub>を用いた。また、n型不純物としてシリコン( Si )、p型不純物原料としてベリリウム( Be )を用いた。なお、同様のドーピング濃度が達成できれば、p型不純物として亜鉛( Zn )や炭素( C )を用いても良い。また、窒素( N )についてはN<sub>2</sub>ガスをRFプラズマ励起したNラジカルを使用した。なお、窒素プラズマの励起は、その他にECR ( Electron Cyclotron Resonance : 電子サイクロトロン共鳴 ) プラズマを用いても行うことができる。但し、同様の構造が形成できれば、本発明の効果を得ることが可能であるので、成長法や原料に関しては、ここに記述したもののみに限定されるものではない。

### 【 0 0 3 0 】

作製する半導体基板はn型GaAs 基板1001 ( n型ドーピング濃度 =  $2 \times 10^{18} \text{ cm}^{-3}$  ) を用いる。AsH<sub>3</sub>雰囲気において基板を昇温した後、基板温度600 °Cにて、厚さ500 nmのn型GaAsバッファーレ1002(n型不純物濃度 =  $1 \times 10^{18} \text{ cm}^{-3}$ )の成長を開始した。その後、成長温度を500 °Cに低下させ、厚さ1300 nmのn型GaInPクラッド層1003(n型不純物濃度 =  $1 \times 10^{18} \text{ cm}^{-3}$ )を成長した。さらに、厚さ50 nmのノンドープGaAs光ガイド層1004、厚さ10 nmのノンドープGaNAs障壁層と厚さ6 nmのノンドープGaInNAs井戸層からなる歪補償型多重量子井戸層1005(周期数:3)を形成した。続いて、本発明にかかる最も重要な層であるノンドープGaAs/GaNAsタイプII超格子層1006を形成した。GaAs層の膜厚は、2 nm、5 nm、7 nm、10 nmの順に変化させ、GaNAs層の膜厚は、3 nmの一定値に保った。続いて、厚さ30 nmのノンドープGaAs光ガイド層1007、p型GaInPクラッド層1008(p型不純物濃度 =  $1 \times 10^{18} \text{ cm}^{-3}$ )、p型GaAsコンタクト層1009(p型不純物濃度 =  $1 \times 10^{19} \text{ cm}^{-3}$ )を形成し、結晶成長工程を終了した。

### 【 0 0 3 1 】

続いて、本多層成長ウェハに対し、レーザ作製のためのストライプ構造作製工程、電極作製工程を施し、素子として完成した。作製された素子は、閾値電流10mAで発振し、85 °Cの高温まで良好なレーザ発振特性を示した。また、10Gb/sを超える高速変調特性を示した。また、層全体の平均歪量の低減により、長期信頼性にも優れていた。

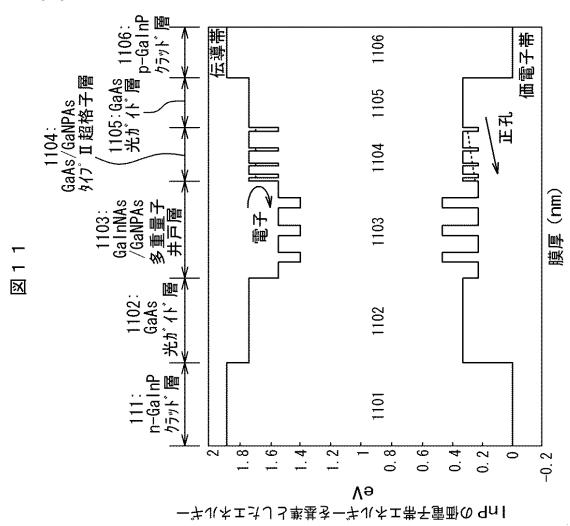

### 【 0 0 3 2 】

図1-1に、本素子におけるタイプII型超格子導入部付近のエネルギー・バンド図を示す。本発明によるタイプII型超格子層1104の導入により、量子準位を介して価電子帯のバンドエネルギー差が、段階的に低減されている。これにより、正孔の注入を効率良く行うことができた。一方、伝導帯側の量子準位は、井戸層内の高いエネルギー位置に形成され、電子に対する障壁効果を維持できており、注入された電子をロックして、活性層に効率良く閉じ込めることができた。以上の効果により、良好な素子特性を達成した。

### 【 0 0 3 3 】

以上のように、本発明によるバンド接続を適用した素子構造の実施例を2例挙げた。本発明による積層構造が、ここで記述していない他の多くの素子にも適用され、同様な改善効果をもたらすことは言うまでも無い。また、素子としては光半導体素子のみを想定し、光変調器、半導体レーザのみを挙げたが、本積層構造を適用して形成する限り、これに限定されるものではない。ここでは言及していないが、例えば、高移動度トランジスタやヘテロバイポーラトランジスタなどの化合物半導体電子素子にも適用可能である。また、材料としても、III-V族化合物半導体に限定されるものではなく、例えばII-VI族化合物半導体や、VI族混晶半導体におけるヘテロ接続界面に適用しても同様の効果が得られることは容易に想定できる。

### 【図面の簡単な説明】

#### 【 0 0 3 4 】

【図1】典型的なAlGaInAs系光素子のエネルギー・バンド図。

【図2】タイプI、及びタイプII超格子のバンドエネルギー図。

【図3】計算に用いた量子井戸構造の図。

【図4】量子準位エネルギー形成位置の量子井戸幅依存性を示す図。

【図5】従来技術と本発明によるバンド接続の図。

10

20

30

40

50

【図6】特開平10-27925に記載の素子におけるエネルギーバンド図。

【図7】本発明によるバンド接続の典型例であって、(a)はp型伝導側適用例、(b)はn型伝導側適用例を示す図。

【図8】本発明によるAlGaInAs電界吸収型変調器の断面構造図。

【図9】図8の素子におけるタイプII超格子導入部付近のエネルギーバンド図。

【図10】本発明によるGaInNAs半導体レーザの断面構造図。

【図11】図10の素子におけるタイプII超格子導入部付近のエネルギーバンド図。

【符号の説明】

【0035】

101...n型InPクラッド層、102...n型AlGaInAs光ガイド層、103...AlGaInAs多重量子井戸層、104...p型AlGaInAs光ガイド層、105...p型AlInAsクラッド層、106...p型AlGaInAsエッティング停止層、107...p型InPクラッド層。601...p型ZnTe、602...ZnTe/ZnSe超格子層、603...n型ZnSe。801...n型InP基板、802...n型InPクラッド層、803...n型AlInAsクラッド層、804...n型AlGaInAs光ガイド層、805...GaAlInAs多重量子井戸層、806...p型AlGaInAs光ガイド層、807...p型AlInAsクラッド層、808...p型AlGaInAsエッティング停止層、809...p型AlGaInAs/InPタイプII超格子層、810...p型InPクラッド層、811...p型GaInAsコンタクト層。901...AlGaInAs多重量子井戸層、902...p型AlGaInAs光ガイド層、903...p型AlInAsクラッド層、904...p型AlGaInAsエッティング停止層、905...p型AlGaInAs/InPタイプII超格子層、906...p型InPクラッド層。1001...n型GaAs基板、1002...n型GaAsバッファ層、1003...n型GaInPクラッド層、1004...GaAs光ガイド層、1005...GaInNAs/GaNPs多重量子井戸層、1006...GaAs/GaNPsタイプII超格子層、1007...GaAs光ガイド層、1008...p型GaInPクラッド層、1009...p型GaAsコンタクト層。1101...n型GaInPクラッド層、1102...GaAs光ガイド層、1103...GaInNAs/GaNPs多重量子井戸層、1104...GaAs/GaNPsタイプII超格子層、1105...GaAs光ガイド層、1106...p型GaInPクラッド層。

【図1】

【図2】

【図3】

図3

【図4】

図4

【図5】

図5

(a) 従来技術によるバンド接続

(b) 本発明のバンド接続

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

【図10】

図10

【図 1 1】

---

フロントページの続き

(72)発明者 土屋 朋信

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 高椋 健司

(56)参考文献 特開平08-070161 (JP, A)

特開平03-041791 (JP, A)

特開平06-237039 (JP, A)

特開平07-022712 (JP, A)

特開平10-079554 (JP, A)

特開2003-142783 (JP, A)

特開2000-164990 (JP, A)

特開平08-262381 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50