## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) . Int. Cl.<sup>8</sup>*G11C 8/00* (2006.01)

(45) 공고일자

2006년02월02일

(11) 등록번호

10-0548552

(24) 등록일자

2006년01월24일

(21) 출원번호

10-2002-0070726

(65) 공개번호

10-2004-0042427

(22) 출원일자

2002년11월14일

(43) 공개일자

2004년05월20일

(73) 특허권자

주식회사 하이닉스반도체

경기 이천시 부발읍 아미리 산136-1

(72) 발명자

박병일

경기도이천시부발읍아미리산136-1

(74) 대리인

강성배

심사관 : 황은택

(54) 디엘엘(DLL)의 확률적 락-인 불량 방지 회로

**요약**

본 발명은 디엘엘(DLL)의 확률적 락-인 불량 방지 회로에 관한 것으로, 종래의 디엘엘 회로는 특정 주파수와 공정전압온도(PVT:Process Voltage Temperature) 변동에 의한 내부 신호경로의 지연시간이 변경됨으로 인하여 야기되는 확률적 락-인 불량 문제점있었다. 본 발명은 이를 개선하기 위하여 분주기 및 위상 비교기의 인에이블신호를 상기 쉬프트 레지스터의 리세트신호를 반전시켜 생성하고 상기 딜레이 체인의 총 딜레이 만큼 지연시킨 후, 상기 기준클럭의 라이징 에지에 동기되어 '하이'로 천이되도록 하여 확률적 락-인 불량을 방지하도록 하는 딜레이 및 래치수단을 더 포함하여 구성함에 특징이 있다.

**대표도**

도 4

**색인어**

DLL, 락-인, 위상 검출, 딜레이, 확률적 불량

**명세서****도면의 간단한 설명**

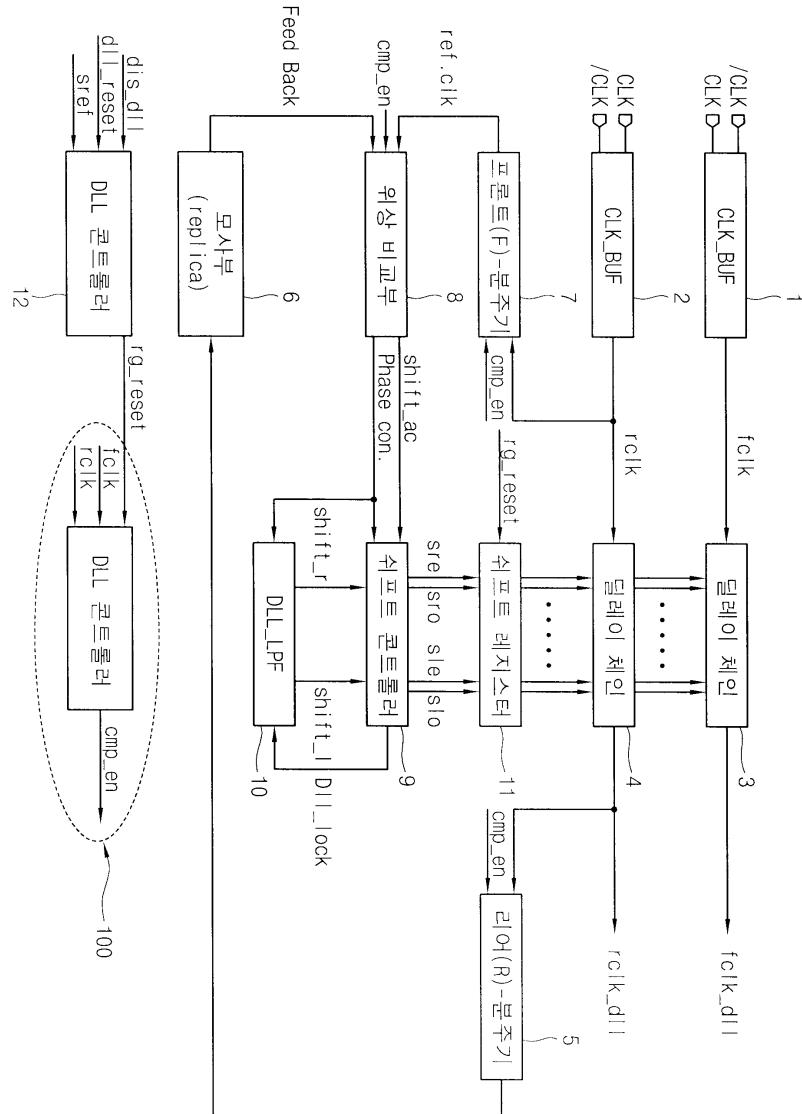

도 1은 종래의 DLL회로를 나타낸 블록도.

도 2는 종래의 클럭 분주기를 나타낸 상세 구성도.

도 3은 종래의 DLL 회로를 설명하기 위한 타이밍도.

도 4는 본 발명에 의한 확률적 락-인 불량 방지 회로를 가진 디엘엘 회로도.

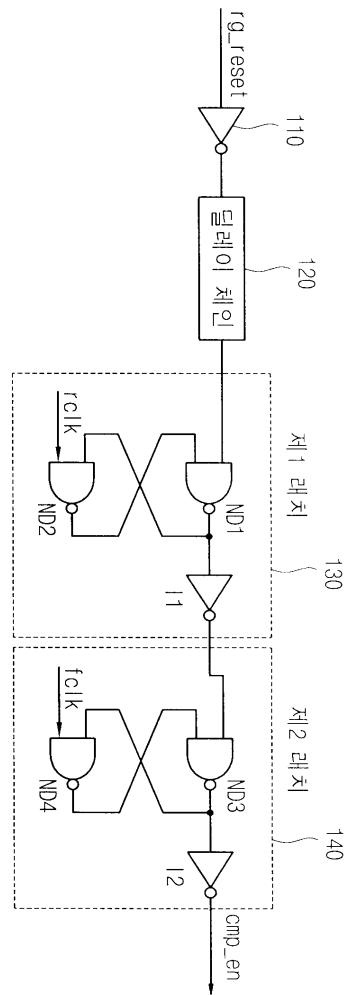

도 5는 본 발명에 의한 딜레이 및 래치부를 나타낸 상세 구성도

도 6은 본 발명에 의한 DLL 회로의 신호 지연 및 동기를 설명하기 위한 타이밍도.

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 더블 데이터 레이트 에스디램(DDR SDRAM)의 디엘엘(DLL:Delay Locked Loop)회로에 관한 것으로, 특히 본 주기에 의한 락-인 불량(Lock-in fail)을 방지하기 위하여 각각의 클럭 분주기가 동일한 클럭 펄스에서 분주를 시작 하도록 함으로써 확률적 락-인 불량을 방지할 수 있도록 한 디엘엘(DLL)의 확률적 락-인 불량 방지 회로에 관한 것이다.

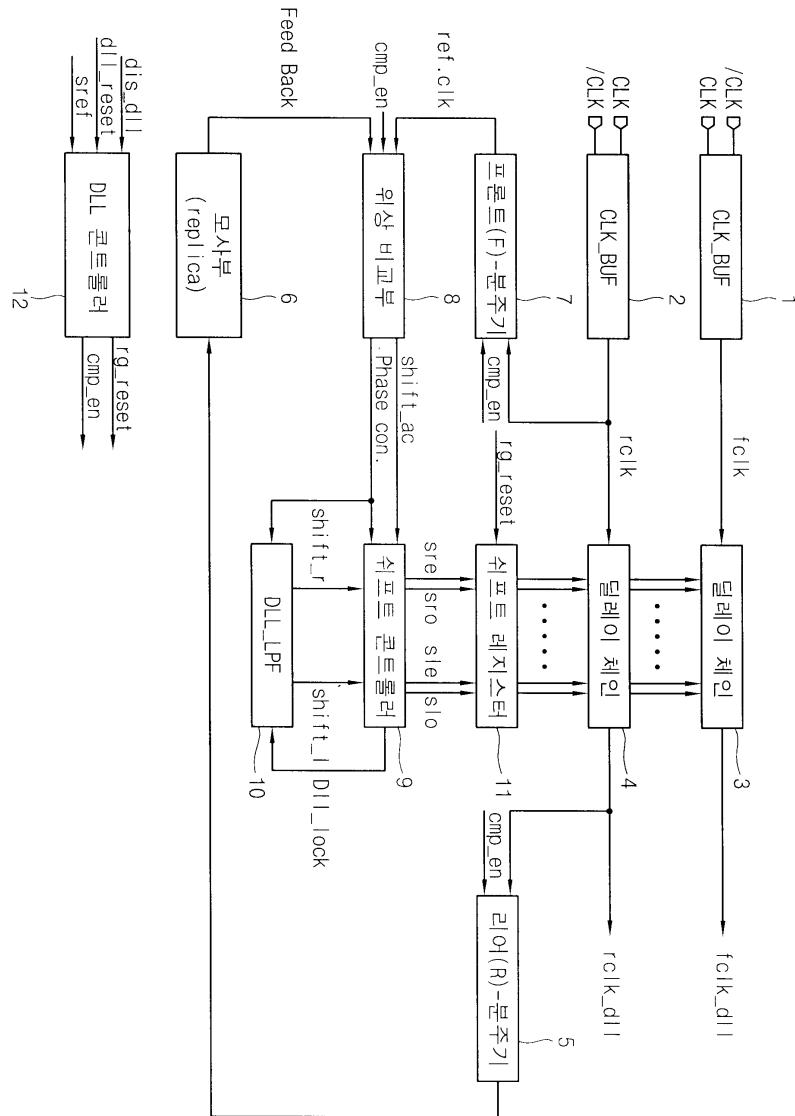

도 1은 종래 DLL회로의 블록도이다. 이에 도시된 바와 같이, 클럭신호(CLK,/CLK)에 응답하여 피드백 클럭(fclk)과 기준 클럭(rclk)를 발생시키는 제 1및 제 2클럭버퍼(CLK\_BUF)(1)(2)와, 상기 피드백 클럭(fclk)과 기준클럭(rclk)에 동기하여 디엘엘 피드백 클럭(fclk\_dll)과, 디엘엘 기준클럭(rclk\_dll)을 출력하는 딜레이 체인(3)(4)과, 상기 디엘엘 기준클럭(rclk\_dll)을 위상비교 인에이블신호(cmp\_en)에 의해 소정의 주파수로 분주를 하는 리어(R)-분주기(5)와, 실제 데이터 경로를 모사하여 그 지연시간 만큼 R-분주기(5)의 출력신호의 전달을 지연하는 모사부(Replica)(6)와, 상기 제2클럭버퍼(2)의 기준클럭(rclk)을 상기 위상비교 인에이블신호(cmp\_en)에 의해 소정의 주파수로 분주를 하는 프런트(F)-분주기(7)와, 상기 위상비교 인에이블신호(cmp\_en)에 의해 상기 프런트(F)-분주기(7)의 출력신호와 상기 모사부(6)의 출력신호를 위상 비교하여 쉬프트 제어신호(Shift\_ac)와 위상 콘트롤신호(Phase con.)를 출력하는 위상 비교부(8)와, 그 위상 비교부(8)의 쉬프트 제어신호 및 위상 콘트롤 신호에 의해 상기 딜레이 체인(3)(4)의 딜레이 단수를 제어하기 위한 쉬프트 콘트롤러(9)와, 상기 위상 제어신호(Phase con.)와 상기 쉬프트 콘트롤러(9)의 디엘엘\_락신호(Dll\_lock)에 의거하여 상기 쉬프트 콘트롤러(9)의 쉬프트 레프트(shift\_l) 및 쉬프트 라이트(shift\_r) 제어를 하는 디엘엘 저역통과필터(DLL\_LPF)(10)와, 상기 쉬프트 콘트롤러(9)의 제어에 의해 상기 딜레이 체인(3)(4)의 딜레이 단수를 좌측 또는 우측으로 쉬프트시켜 제어하기 위한 쉬프트 레지스터(11)와, 상기 쉬프트 레지스터(11)를 리세트하기 위한 레지스터 리세트신호(rg\_reset), 위상비교 인에이블신호(cmp\_en)발생하는 DLL 콘트롤러(12)를 포함하여 구성된다.

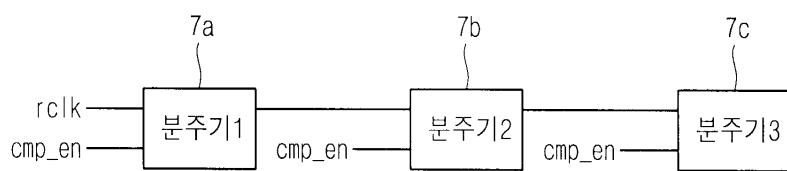

도 2는 종래의 클럭 분주기의 상세 구성도이다. 이는 R-분주기와 F-분주기의 구성으로서, 위상비교 인에이블신호(cmp\_en)에 의해 기준클럭(rclk)을 분주하는 제1분주기(7a), 제1분주기(7a)의 출력을 다시 분주하는 제2분주기(7b), 제2분주기(7b)의 출력을 다시 분주하는 제3분주기(7c)가 다단 구성으로 이루어진다.

이와같이 구성된 종래 DLL회로는, 기준클럭(rclk)과 피드백 클럭(fclk)을 위상 비교하여 그 비교한 결과를 받아들여 상기 딜레이 체인(3)(4)의 단 수를 좌우로 쉬프트하여 레프리커(6)에 모사된 각 버퍼들의 총 딜레이 만큼 앞선 DLL 클럭을 출력하도록 동작된다. 이때 비교되는 기준클럭(rclk)과 피드백 클럭은 각각의 클럭 분주기(7)(5)에서 딜레이 체인(3)(4) 전단과 후단의 클럭을 입력으로 하여 분주한 클럭이며, 이 신호의 위상차를 비교한다. 비교된 위상차가 딜레이 체인의 유니트 딜레이 보다 작을 경우 DLL 락-인(Lock-in)이 된 상태가 된다.

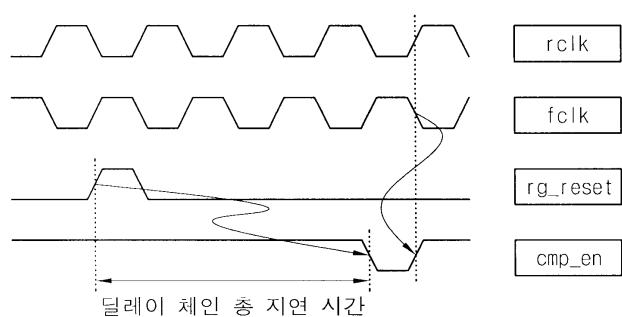

도 3은 종래 DLL 회로의 타이밍도이다. 이에 도시된 바와 같이, 특정 주파수 또는 공정전압온도(PVT:Process Voltage Temperature) 변동으로 인하여 내부 딜레이가 변하게 될때 분주기 인에이블신호(cmp\_en)가 기준클럭(rclk) 신호의 폴링 에지와 딜레이 체인의 첫번째 유니트 딜레이 스테이지를 지난 디엘엘 기준클럭(rclk\_dll) 신호의 폴링 에지 사이에서 '하이'로 친이하게 되면, R-분주기가 F-분주기 보다 1클럭주기(1tCK) 먼저 카운터를 시작하게 되어 딜레이를 증가 시켜야 될 상황에 딜레이를 감소시키는 동작을 하게 되므로 결국 영원히 DLL 락-인이 이루어지지 않는 애러현상이 발생한다.

또한 외부 클럭이 로우 주파수에서 하이 주파수로 변경될때 외부에서 디엘엘 리세트 명령(rg\_reset)을 주게 되는데, 이때 딜레이 체인을 진향하고 있는 클럭 펄스가 잔존하는 상태에서 위상비교 인에이블신호가 하이로 친이하게 되면 확률적인 DLL 락-인 불량 현상이 발생한다.

#### 발명이 이루고자 하는 기술적 과제

본 발명은 특정 주파수와 공정전압온도(PVT) 변동에 의한 내부 신호경로의 지연시간이 변경됨으로 인하여 야기되는 확률적 락-인 불량 문제점을 개선하기 위하여 위상비교 인에이블신호를 기준클럭신호의 라이징 에지에 동기되어 '하이'로 천이 되도록 하고, 로우 주파수에서 하이 주파수로 변경될때 리세트 타이밍에 의한 락-인 불량은 딜레이 체인의 총 딜레이 만큼 위상비교 인에이블신호를 지연시켜 하이로 천이하게 함으로서, 확률적 딜레이 락-인 불량을 방지하기 위한 것이다.

### 발명의 구성 및 작용

상기 목적을 달성하기 위한 본 발명에 따른 딜레이의 확률적 락-인 불량 방지 회로는 다단의 단수를 가진 딜레이 체인의 앞 뒤 클럭을 프런트 분주기와 리어 분주기를 통해 분주시킨 후 그 위상차이 만큼 쉬프트 레지스터를 통해 상기 딜레이 체인의 딜레이 단수를 좌우로 쉬프트시켜 딜레이 락-인하도록 이루어진 딜레이 회로에 있어서, 상기 쉬프트 레지스터를 리세트시키는 신호가 입력되어 반전되고 딜레이 체인수 만큼 딜레이되어 '로우'로 천이된 후 상기 기준클럭의 라이징 에지에 동기되어 '하이'로 천이되어 상기 분주기 및 위상비교기의 동작을 제어하는 위상비교 인에이블신호를 출력하여 확률적 락-인 불량을 방지하는 딜레이 및 래치수단을 더 포함한다.

상기 딜레이 및 래치수단은, 쉬프트 레지스터 리세트 신호를 반전시켜 상기 딜레이 체인과 같은 단수의 딜레이를 시키는 딜레이 체인과, 그 딜레이 체인을 통과해 딜레이된 신호를 기준클럭(rclk)에 동기시켜 래치시키는 제1래치와, 그 제1래치의 출력신호를 상기 피드백 클럭(fclk)에 동기시켜 래치시켜 상기 프런트 분주기와 리어 분주기의 인에이블신호(cmp\_en)로서 출력하는 제2래치를 포함하여 구성함에 특징이 있다.

이하, 본 발명의 실시예를 첨부된 도면을 참조해서 상세히 설명하면 다음과 같다.

도 4는 본 발명에 의한 확률적 락-인 불량 방지 회로를 가진 딜레이 회로도이다.

클럭버퍼(1)(2)의 클럭신호(fclk)(rclk)를 각각 딜레이 체인(3)(4)를 통해 딜레이 시켜 딜레이 클럭신호(fclk\_dll)(rclk\_dll)로서 출력하고, 상기 딜레이 체인(4)의 앞뒤 클럭신호(rclk)(rclk\_dll)를 각각 위상비교 인에이블신호(cmp\_en)에 의해 소정의 주파수로 분주를 하는 프런트(F)-분주기(7) 및 R(리어)-분주기(5)와, 실제 데이터 경로를 모사하여 그 지연시간 만큼 R-분주기(5)의 출력신호의 전달을 지연하는 모사부(Replica)(6)와, 상기 위상비교 인에이블신호(cmp\_en)에 의해 상기 F-분주기(7)의 출력신호와 상기 레프리커(6)의 출력신호를 위상 비교하여 쉬프트 제어신호(Shift\_ac)와 위상 콘트롤신호(Phase con.)를 출력하는 위상 비교부(8)와, 그 위상 비교부(8)의 쉬프트 제어신호 및 위상 콘트롤 신호에 의해 상기 딜레이 체인(3)(4)의 딜레이 단수를 제어하기 위한 쉬프트 콘트롤러(9)와, 상기 위상 제어신호(Phase con.)와 상기 쉬프트 콘트롤러(9)의 딜레이 딜레이\_락신호(Dll\_lock)에 의거하여 상기 쉬프트 콘트롤러(9)의 쉬프트 레프트(shift\_l) 및 쉬프트 라이트(shift\_r) 제어를 하는 딜레이 저역통과필터(DLL\_LPF)(10)와, 상기 쉬프트 콘트롤러(9)의 제어에 의해 상기 딜레이 체인(3)(4)의 딜레이 단수를 좌측 또는 우측으로 쉬프트 시켜 제어하기 위한 쉬프트 레지스터(11) 및 상기 각부의 동작 제어를 위한 레지스터 리세트 신호(rg\_reset)를 발생하는 DLL 콘트롤러(12)로 구성된 딜레이 회로에 있어서, 상기 DLL 콘트롤러(12)의 레지스터 리세트 신호(rg\_reset)를 입력받아 반전시킨 후 딜레이 체인수만큼 딜레이시켜 기준클럭(rclk) 및 피드백 클럭(fclk)에 위상을 동기시켜 래치된 신호를 상기 분주기(5)(7) 및 상기 위상비교기(8)를 제어하기 위한 위상비교 인에이블신호(cmp\_en)로서 출력하는 딜레이 및 래치부(100)를 더 포함하여 구성된다.

도 5는 본 발명에 의한 딜레이 및 래치부의 상세 구성도이다.

상기 딜레이 및 래치부(10)는, 쉬프트 레지스터(11)를 리세트 시키기 위해 상기 DLL 콘트롤러(12)에서 발생시킨 레지스터 리세트 신호(rg\_reset)를 반전시키는 인버터(110)와, 상기 딜레이 체인(3)(4)과 같은 단수의 딜레이를 시키는 딜레이 체인(120)과, 그 딜레이 체인(120)을 통과해 딜레이된 신호를 기준클럭(rclk)에 동기시켜 래치시키는 제1래치(130)와, 그 제1래치(130)의 출력신호를 상기 피드백 클럭(fclk)에 동기시켜 래치시켜 상기 프런트(F) 분주기(7)와 리어(R) 분주기(6)의 인에이블신호(cmp\_en)로서 출력하는 제2래치(140)를 포함하여 구성된다.

종래 기술에서 위상비교 인에이블신호(cmp\_en)는 딜레이 체인(3)(4)의 쉬프트 레지스터(11)를 초기화하는 레지스터 리세트신호(rg\_reset)와 마찬가지로 비동기(async) 신호로서 내부 딜레이를 가지고 있다. 따라서, PVT 변화에 종속적으로 신호가 하이로 천이하고, 이순간 분주기는 딜레이를 가지고 있으며, 클럭이 로우 주파수에서 하이 주파수로 변경될때 레지스터 리세트 신호에 의해 확률적 락-인 불량을 유발할 수가 있다.

이러한 불량을 방지하기 위하여 상기 위상비교 인에이블신호(cmp\_en)는 상기 레지스터 리세트 신호(rg\_reset)를 인버터(I10)를 통해 반전시켜 생성하며, 딜레이 체인(3)(4)이 가지는 최대 지연 시간만큼 딜레이를 가지도록 도 5에서와 같이 딜레이 체인(120)을 통해 지연시킨다. 여기서 생성된 신호의 폴링 에지는 래치(130)(140)의 제어입력과 관계없이 위상비교 인에이블신호(cmp\_en)가 로우로 천이되므로, 분주기(5)(7)가 디스에이블 상태로 변경된다.

즉, 딜레이 체인(120)의 출력신호중 폴링 에지는 제1래치(130)의 낸드게이트(ND1)에 입력되고, 그 낸드 게이트(ND1)는 다른 입력과 관계없이 로우 입력에 의해 출력이 하이가 되고, 그 하이는 인버터(I1)를 통해서 다시 로우로 반전되어 제2래치(140)에 입력된다. 마찬가지로 제2래치(140)도 낸드게이트(ND3)의 입력중 하나가 로우이므로 다른 입력과 관계없이 하이신호가 출력되고, 그 하이신호가 인버터(I2)를 통해 반전되어 로우 신호로서 위상비교 인에이블신호(cmp\_en)를 출력한다.

따라서, 레지스터 리세트신호(rg\_reset)가 폴링에지로 떨어지면, 그에 동기되어 위상 비교 인에이블신호(cmp\_en)가 로우 신호로 떨어지므로 분주기(5)(7)를 디스에이블 상태로 만든다.

이후, 상기 레지스터 리세트 신호(rg\_reset)가 변하면서 딜레이 체인(120)의 출력신호가 라이징 에지가 되면, 제1래치(130)는 기준클럭신호(rclk)의 로우 구간에서 신호를 받아들여 래치하게 되고, 래치된 신호는 제2래치부(140)에서 피드백 클럭신호(fclk)의 제어를 받아 그 피드백 클럭신호(fclk)의 폴링 에지에서 출력하게 된다.

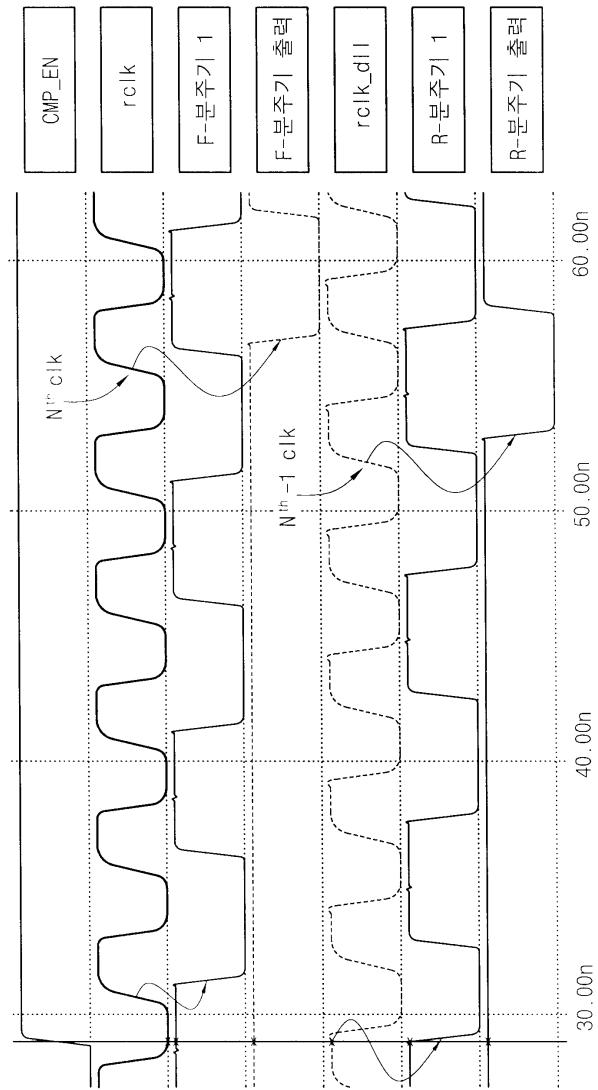

따라서 도 6에 도시된 바와 같이, 레지스터 리세트신호(rg\_reset)가 '하이'로 천이되면, 딜레이 체인(120)을 통해 상기 딜레이 체인(3)(4)의 총 딜레이 시간 만큼 지연된 후, 상기 제1래치(130)에서 기준클럭신호(rclk)의 폴링 에지에 동기하여 위상비교 인에이블신호(cmp\_en)가 폴링 에지가 되고, 제2래치(140)에서 피드백클럭신호(fclk)의 폴링에지에 동기하여 위상비교 인에이블신호(cmp\_en)가 라이징 에지가 된다. 즉, 기준클럭신호(rclk)의 라이징에지에 동기하여 '하이'로 천이하게된다. 이에 따라 분주되는 클럭의 폴링에지 사이에서 분주기가 인에이블 되는 것을 방지함으로써, 비동기 딜레이에 의한 딜레이 불량을 방지할 수 있게 된다.

### 발명의 효과

이상에서 상세히 설명한 바와 같이, 본 발명은 DLL 회로에서 위상 비교되는 신호의 각각의 분주기를 사용하는 경우에 발생할 수 있는 분주기 비동기 지연으로 인한 확률적 딜레이 불량을 방지할 수 있는 효과가 있다.

### (57) 청구의 범위

#### 청구항 1.

딜레이 체인의 앞 뒤 클럭을 분주기를 통해 분주시켜 위상 비교기를 통해 검출된 위상 차이 만큼 쉬프트 레지스터를 통해 상기 딜레이 체인의 딜레이 단수를 좌우로 쉬프트시켜 딜레이 불량을 방지하는 딜레이 회로에 있어서,

상기 쉬프트 레지스터를 리세트시키는 신호가 입력되어 반전되고 딜레이 체인수 만큼 딜레이되어 '로우'로 천이된 후 상기 기준클럭의 라이징 에지에 동기되어 '하이'로 천이되어 상기 분주기 및 위상비교기의 동작을 제어하는 위상비교 인에이블 신호를 출력하여 확률적 딜레이 불량을 방지하는 딜레이 및 래치수단을 더 포함하여 구성된 것을 특징으로 하는 딜레이 회로.

#### 청구항 2.

제 1 항에 있어서,

상기 딜레이 및 래치수단은 상기 쉬프트 레지스터 리세트 신호를 반전시켜 위상비교 인에이블신호를 생성하는 인버터와,

상기 인버터의 출력신호를 상기 클럭신호 딜레이 체인과 같은 딜레이 시간만큼 딜레이를 시키는 딜레이 체인과,

상기 딜레이 체인을 통과해 딜레이된 신호를 상기 기준클럭에 동기시켜 래치시키는 제1래치와,

상기 제1래치의 출력신호를 상기 피드백 클럭에 동기시켜 래치시켜 상기 프런트 분주기와 리어 분주기의 인에이블신호로서 출력하는 제2래치로 구성된 것을 특징으로 하는 디엘엘의 확률적 락-인 불량 방지 회로.

도면

도면1

도면2

피드백 분주기

도면3

도면 4

도면5

도면6