(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-60143

(P2009-60143A)

(43) 公開日 平成21年3月19日(2009.3.19)

| (51) Int.Cl.           | F 1        | テーマコード (参考) |

|------------------------|------------|-------------|

| HO1L 21/3205 (2006.01) | HO1L 21/88 | K 5FO32     |

| HO1L 23/52 (2006.01)   | HO1L 21/88 | S 5FO33     |

| HO1L 21/822 (2006.01)  | HO1L 27/04 | A 5FO38     |

| HO1L 27/04 (2006.01)   | HO1L 21/76 | L 5FO48     |

| HO1L 21/76 (2006.01)   | HO1L 27/08 | 331A        |

審査請求 有 請求項の数 8 O L (全 26 頁) 最終頁に続く

|            |                                     |          |                                                       |

|------------|-------------------------------------|----------|-------------------------------------------------------|

| (21) 出願番号  | 特願2008-306316 (P2008-306316)        | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区大手町二丁目6番2号       |

| (22) 出願日   | 平成20年12月1日 (2008.12.1)              | (74) 代理人 | 100080001<br>弁理士 筒井 大和                                |

| (62) 分割の表示 | 特願2007-187319 (P2007-187319)<br>の分割 | (72) 発明者 | 黒田 謙一<br>東京都小平市上水本町五丁目20番1号<br>株式会社日立製作所半導体グループ内      |

| 原出願日       | 平成12年11月20日 (2000.11.20)            | (72) 発明者 | 渡部 浩三<br>東京都小平市上水本町五丁目20番1号<br>株式会社日立製作所半導体グループ内      |

|            |                                     | (72) 発明者 | 山本 裕彦<br>東京都小平市上水本町5丁目22番1号<br>株式会社日立超エル・エス・アイ・システムズ内 |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】製造工程時間の増加を招くことなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供する。

【解決手段】相対的に面積の大きい第1ダミーパターンDP<sub>1</sub>と相対的に面積の小さい第2ダミーパターンDP<sub>2</sub>とをダミー領域FAに配置することによって、素子形成領域DAとダミー領域FAとの境界BL近くまでダミーパターンを配置することができる。これにより、分離溝内に埋め込まれた酸化シリコン膜の表面の平坦性をダミー領域FAの全域において向上することができる。さらに、ダミー領域FAのうち相対的に広い領域を上記第1ダミーパターンDP<sub>1</sub>で占めることで、マスクのデータ量の増加を抑えることができる。

【選択図】図1

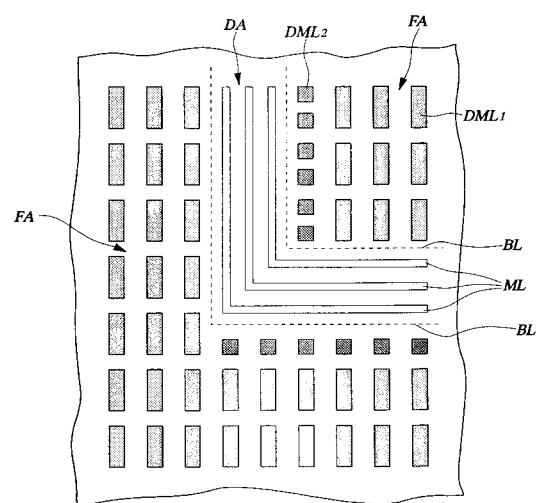

図 1

DA : 素子形成領域

FA : ダミー領域

DP1 : 第1ダミーパターン

DP2 : 第2ダミーパターン

## 【特許請求の範囲】

## 【請求項 1】

半導体基板に形成された半導体素子と、前記半導体素子を覆うように前記半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜上に形成された第1層配線と、前記第1層配線を覆うように前記第1層間絶縁膜上に形成された第2層間絶縁膜と、前記第2層間絶縁膜上に形成された第2層配線と、前記第2層配線を覆うように前記第2層間絶縁膜上に形成された第3層間絶縁膜とを有する半導体装置であって、

前記第1層配線は、前記半導体素子と接続された第1配線、前記半導体素子と接続されない第1ダミー配線および前記半導体素子と接続されない第2ダミー配線を含み、

前記第2層配線は、前記半導体素子と接続された第2配線、前記半導体素子と接続されない第3ダミー配線および前記半導体素子と接続されない第4ダミー配線を含み、

前記第2ダミー配線は前記第1ダミー配線よりも、その形状および面積が小さく、

前記第4ダミー配線は前記第3ダミー配線よりも、その形状および面積が小さく、

前記第1ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第2ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第3ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第4ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記複数の第1ダミー配線は、それぞれ規則的に配置されており、

前記複数の第2ダミー配線は、それぞれ規則的に配置されており、

前記複数の第3ダミー配線は、それぞれ規則的に配置されており、

前記複数の第4ダミー配線は、それぞれ規則的に配置されており、

前記複数の第2ダミー配線は、前記第1配線と隣接して配置され、かつ、前記第1配線と前記第1ダミー配線との間に位置しており、

前記複数の第4ダミー配線は、前記第2配線と隣接して配置され、かつ、前記第2配線と前記第3ダミー配線との間に位置していることを特徴とする半導体装置。

## 【請求項 2】

半導体基板に形成された半導体素子と、前記半導体素子を覆うように前記半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜上に形成された第1層配線と、前記第1層配線を覆うように前記第1層間絶縁膜上に形成された第2層間絶縁膜と、前記第2層間絶縁膜上に形成された第2層配線と、前記第2層配線を覆うように前記第2層間絶縁膜上に形成された第3層間絶縁膜とを有する半導体装置であって、

前記第1層配線は、前記半導体素子と接続された第1配線、前記半導体素子と接続されない第1ダミー配線および前記半導体素子と接続されない第2ダミー配線を含み、

前記第2層配線は、前記半導体素子と接続された第2配線、前記半導体素子と接続されない第3ダミー配線および前記半導体素子と接続されない第4ダミー配線を含み、

前記第2ダミー配線は前記第1ダミー配線よりも、その形状および面積が小さく、

前記第4ダミー配線は前記第3ダミー配線よりも、その形状および面積が小さく、

前記第1ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第2ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第3ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第4ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記複数の第1ダミー配線は、それぞれ規則的に配置されており、

前記複数の第2ダミー配線は、それぞれ規則的に配置されており、

前記複数の第3ダミー配線は、それぞれ規則的に配置されており、

前記複数の第4ダミー配線は、それぞれ規則的に配置されており、

前記複数の第2ダミー配線は、前記第1配線と隣接して配置され、かつ、前記第1配線と前記第1ダミー配線との間に位置しており、

前記複数の第4ダミー配線は、前記第2配線と隣接して配置され、かつ、前記第2配線と前記第3ダミー配線との間に位置しており、

前記第1層配線および前記第2層配線は、銅で形成されていることを特徴とする半導体

10

20

30

40

50

装置。

【請求項 3】

半導体基板に形成された半導体素子と、前記半導体素子を覆うように前記半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜上に形成された第1層配線と、前記第1層配線を覆うように前記第1層間絶縁膜上に形成された第2層間絶縁膜と、前記第2層間絶縁膜上に形成された第2層配線と、前記第2層配線を覆うように前記第2層間絶縁膜上に形成された第3層間絶縁膜とを有する半導体装置であって、

前記第1層配線は、前記半導体素子と接続された第1配線、前記半導体素子と接続されない第1ダミー配線および前記半導体素子と接続されない第2ダミー配線を含み、

前記第2層配線は、前記半導体素子と接続された第2配線、前記半導体素子と接続されない第3ダミー配線および前記半導体素子と接続されない第4ダミー配線を含み、

前記第2ダミー配線は前記第1ダミー配線よりも、その形状および面積が小さく、

前記第4ダミー配線は前記第3ダミー配線よりも、その形状および面積が小さく、

前記第1ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第2ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第3ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第4ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記複数の第1ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第2ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第3ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第4ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第2ダミー配線は、前記第1配線と隣接して配置され、かつ、前記第1配線と前記第1ダミー配線との間に位置しており、

前記複数の第4ダミー配線は、前記第2配線と隣接して配置され、かつ、前記第2配線と前記第3ダミー配線との間に位置していることを特徴とする半導体装置。

【請求項 4】

半導体基板に形成された半導体素子と、前記半導体素子を覆うように前記半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜上に形成された第1層配線と、前記第1層配線を覆うように前記第1層間絶縁膜上に形成された第2層間絶縁膜と、前記第2層間絶縁膜上に形成された第2層配線と、前記第2層配線を覆うように前記第2層間絶縁膜上に形成された第3層間絶縁膜とを有する半導体装置であって、

前記第1層配線は、前記半導体素子と接続された第1配線、前記半導体素子と接続されない第1ダミー配線および前記半導体素子と接続されない第2ダミー配線を含み、

前記第2層配線は、前記半導体素子と接続された第2配線、前記半導体素子と接続されない第3ダミー配線および前記半導体素子と接続されない第4ダミー配線を含み、

前記第2ダミー配線は前記第1ダミー配線よりも、その形状および面積が小さく、

前記第4ダミー配線は前記第3ダミー配線よりも、その形状および面積が小さく、

前記第1ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第2ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第3ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記第4ダミー配線は、複数形成され、かつ、それぞれ同一形状で形成されており、

前記複数の第1ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第2ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第3ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第4ダミー配線は、それぞれ同じ間隔で離れて配置されており、

前記複数の第2ダミー配線は、前記第1配線と隣接して配置され、かつ、前記第1配線と前記第1ダミー配線との間に位置しており、

前記複数の第4ダミー配線は、前記第2配線と隣接して配置され、かつ、前記第2配線と前記第3ダミー配線との間に位置しており、

前記第1層配線および前記第2層配線は、銅で形成されていることを特徴とする半導体

10

20

30

40

50

装置。

【請求項 5】

請求項 1 ~ 4 のいずれか 1 項に記載の半導体装置において、前記複数の第 1 ダミー配線の形状および前記複数の第 4 ダミー配線の形状は、それぞれ四角形であることを特徴とする半導体装置。

【請求項 6】

請求項 5 記載の半導体装置において、前記第 2 ダミー配線の一辺の寸法に前記複数の第 2 ダミー配線同士の間隔を加えた値は、前記第 1 ダミー配線の一辺の寸法に前記複数の第 1 ダミー配線同士の間隔を加えた値の整数分の一となっていることを特徴とする半導体装置。

10

【請求項 7】

請求項 1 ~ 6 のいずれか 1 項に記載の半導体装置において、前記複数の第 3 ダミー配線の形状および前記複数の第 4 ダミー配線の形状は、それぞれ四角形であることを特徴とする半導体装置。

【請求項 8】

請求項 7 記載の半導体装置において、前記第 4 ダミー配線の一辺の寸法に前記複数の第 4 ダミー配線同士の間隔を加えた値は、前記第 3 ダミー配線の一辺の寸法に前記複数の第 3 ダミー配線同士の間隔を加えた値の整数分の一となっていることを特徴とする半導体装置。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、その製造工程に CMP (chemical mechanical polishing) 法を用いた平坦化工程を含む半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

隣接する半導体素子を互いに電気的に分離するアイソレーションの一つに、素子分離領域となる半導体基板に溝を設け、これに絶縁膜を埋め込むことにより形成されるトレンチアイソレーション (trench isolation) がある。

30

【0003】

このトレンチアイソレーションは、たとえば以下の方法で形成される。まず、半導体基板の素子分離領域にドライエッチングによって、たとえば  $0.4 \mu m$  程度の深さの溝を形成し、次いで半導体基板に熱酸化処理を施すことによって、半導体基板の露出している表面に、たとえば  $20 nm$  程度の厚さの第 1 絶縁膜を形成する。この後、半導体基板上に第 2 絶縁膜を堆積して溝の内部を埋め込んだ後、この第 2 絶縁膜の表面を、たとえば CMP 法で研磨することによって溝の外部の第 2 絶縁膜を除去し、溝の内部にのみ第 2 絶縁膜を残すことでトレンチアイソレーションが形成される。

【0004】

ところで、素子分離領域の幅が相対的に大きくなると、CMP 工程において局所的に第 2 絶縁膜の研磨が速くなり、溝の中央部が窪む、いわゆるディッシング (dishing) 現象が生じやすくなる。しかし、このディッシング現象を抑えて素子分離領域における第 2 絶縁膜の表面の平坦性を向上する方法としては、いくつかの方法が提案されており、その一つにダミーパターンを設ける方法がある。

40

【0005】

たとえば、特開平 10-92921 号公報 (特許文献 1) には、アクティブデバイスのない部分とアクティブデバイスのある部分との占有密度が等しくなるように、各ダミー構造体が、アクティブデバイスのない部分に配置され、それにより半導体基板の表面に亘って研磨速度を均等にする方法が開示されている。

【0006】

50

また、本発明者は、素子分離領域に、規則的にダミーパターンを配置する方法について検討した。以下は、本発明者によって検討された技術であり、その概要は次のとおりである。

【0007】

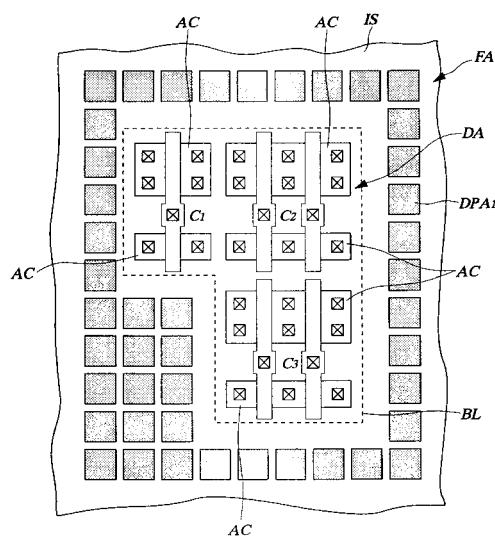

図28は、本発明者が検討した第1のダミーパターン配置方法を示す。半導体素子が形成される素子形成領域（図中、破線枠内の領域）DA以外の半導体素子が形成されないダミー領域（図中、破線枠外の領域）FAに、複数のダミーパターンDPA<sub>1</sub>が規則的に配置されている。複数のダミーパターンDPA<sub>1</sub>は、同一形状、同一寸法であって、これらがダミー領域FAに同一間隔で敷き詰められている。

【0008】

活性領域AC以外の素子形成領域DAおよびダミー領域FAが素子分離領域ISであって、通常は、この分離領域IS全体にトレンチアイソレーションが形成される。このため、特に、活性領域ACから離れたダミー領域FAにおいて、前記CMP工程でのディッシングが生じやすく、埋め込み絶縁膜の表面の平坦性が得られにくいという問題があった。しかし、複数のダミーパターンDPA<sub>1</sub>を配置することによって、ダミー領域FAにおけるディッシングを防ぐことが可能となり、ダミー領域FAにおける埋め込み絶縁膜の表面の平坦性を向上することができる。

【0009】

図29は、本発明者が検討した第2のダミーパターン配置方法を示す。前記図28と同様に、半導体素子が形成される素子形成領域DA以外の半導体素子が形成されないダミー領域FAに、複数のダミーパターンDPA<sub>2</sub>が規則的に配置されており、ダミー領域FAにおけるディッシングを防ぐことが可能である。ダミーパターンDPA<sub>2</sub>の寸法は、前記ダミーパターンDPA<sub>1</sub>の寸法と比して小さく、素子形成領域DAとダミー領域FAとの境界BL（図中、枠線で示す）近くのダミー領域FAにまで、ダミーパターンDPA<sub>2</sub>を配置することができる。

【特許文献1】特開平10-92921号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかしながら、本発明者が検討したところ、前記アクティブデバイスのない部分にダミー構造体を配置する場合、そのダミー構造体の中には形状が複雑となるものがあり、特に区画しているダミー構造体の内部に絶縁膜が完全に埋め込まれないという問題が生じた。また、形成するには小さすぎるダミー構造体を除去する工程が必要となるため、製造工程に要する時間が増加することも考えられた。

【0011】

さらに、前記第1のダミーパターン配置方法および前記第2のダミーパターン配置方法においては、以下の課題があることを本発明者は見いだした。

【0012】

まず、第1のダミーパターン配置方法では、ダミーパターンDPA<sub>1</sub>の寸法が相対的に大きいため、素子形成領域DAとダミー領域FAとの境界BLに近いダミー領域FAにおいて、ダミーパターンDPA<sub>1</sub>を配置することができない領域が生じ、この領域が相対的に広くなつた場合には、ディッシングが生ずることが明らかとなつた。

【0013】

第2のダミーパターン配置方法では、ダミーパターンDPA<sub>2</sub>の寸法が相対的に小さいことから、素子形成領域DAとダミー領域FAとの境界BL近くまでダミーパターンDPA<sub>2</sub>を配置することができる。これにより、前記ダミーパターンDPA<sub>1</sub>が配置できなかつた領域にも、ダミーパターンDPA<sub>2</sub>を配置することができるので、第2のダミーパターン配置方法では、第1のダミーパターン配置方法と比して、境界BLに近いダミー領域FAにまで埋め込み絶縁膜の表面の平坦性を向上することができる。

【0014】

10

20

30

40

50

しかしながら、第2のダミーパターン配置方法を用いると、ダミー領域FAに配置されるダミーパターンDPA<sub>2</sub>の数が多くなり、マスクを作成する際の座標データ量が著しく増加してしまう。これにより、計算機での演算処理時間が増加し、さらにマスク基板上へパターンを描画する時間が増加するため、マスクの作成のスループットが著しく低下するという問題が生ずる。特に、ASIC(application specific integrated circuit:特定用途向き集積回路)に、第2のダミーパターン配置方法を採用すると、マスクの作成に要する時間が増えるため、短期間でのASICの開発に支障を来すという問題がある。

【0015】

本発明の目的は、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供することにある。

10

【0016】

また、本発明の目的は、半導体装置の製造工程に要する時間を増加させることなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供することにある。

【0017】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0018】

本願において開示される発明のうち、代表的なものの一実施の形態を簡単に説明すれば、次のとおりである。

20

【0019】

この実施の形態は、回路素子が境界によって規定された素子形成領域と、境界に隣接する回路素子が形成されないダミー領域とからなり、ダミー領域は少なくとも2つのダミーパターン群を有する半導体装置である。各々のダミーパターン群には、平面的に占有する形状が互いに同一形状および互いに同一寸法の複数のダミーパターンが互いに行列状に離間して配置されており、複数のダミーパターンの行方向および/または列方向の寸法が各々のダミーパターン群の間で異なるものである。

【0020】

この実施の形態は、回路素子が形成される素子形成領域と、回路素子が形成されないダミー領域とが境界によって規定され、ダミー領域に少なくとも2つのダミーパターン群を形成する半導体装置の製造方法である。半導体基板の主面に、素子形成領域の活性領域を規定する第1分離溝と、ダミー領域の各々のダミーパターン群をなす複数のダミーパターンを行列状に分割する第2分離溝とを形成する工程と、第1分離溝および第2分離溝を埋め込むように、素子形成領域およびダミー領域を覆って絶縁膜を堆積する工程と、絶縁膜の表面を研磨して第1分離溝および第2分離溝の外部の絶縁膜を除去する工程とを有し、各々のダミーパターン群には、平面的に占有する形状が互いに同一形状および互いに同一寸法の複数のダミーパターンが形成されるが、ダミーパターンの行方向および/または列方向の寸法は各々のダミーパターン群の間で異なるものである。

30

【発明の効果】

【0021】

本願において開示される発明のうち、代表的なものの一実施の形態によって得られる効果を簡単に説明すれば以下のとおりである。

40

【0022】

少なくとも2つのダミーパターン群を配置することにより、複数の凹部に埋め込まれた部材表面の平坦性を向上することが可能となる。

【0023】

さらに、ダミー領域のうち相対的に広い領域を相対的に面積の大きいダミーパターンで占めることで、マスクを作成する際の座標データ量の増加を抑えてマスク作成に要する時間の増加を抑えることができる。これにより、半導体装置の製造工程に要する時間を増加

50

させることなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することが可能となる。

【発明を実施するための最良の形態】

【0024】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0025】

本実施の形態において説明された形状において、「正方形」「長方形」などの形状表現は、設計思考上の形状、マスクパターンのデータ上の形状、マスク上の形状およびパターンングされた集積回路装置上の実パターンの形状を含み、リソグラフィなどの加工上の問題などでコーナ部などが幾何学上の形状から若干変形されているものも実質的に含むものとする。

10

【0026】

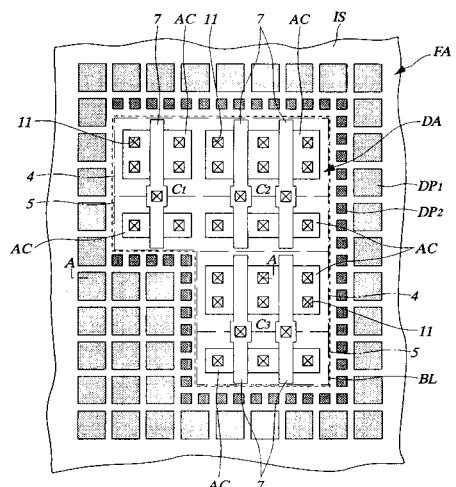

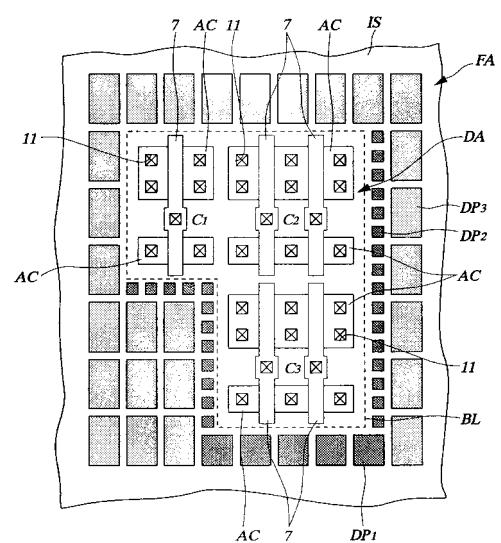

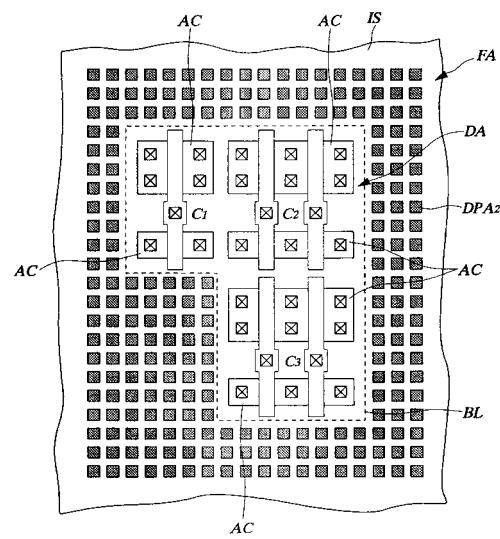

(実施の形態1)

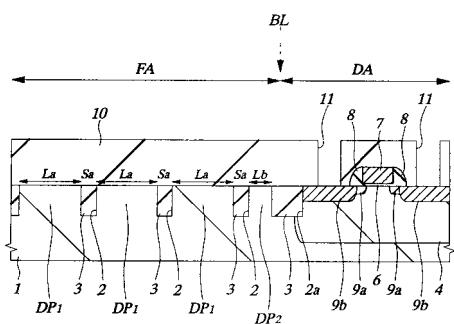

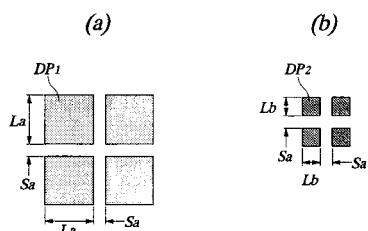

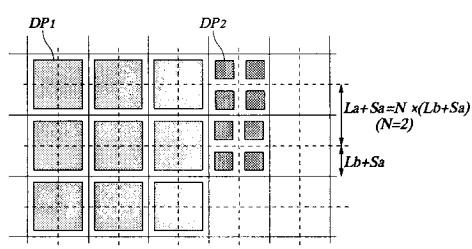

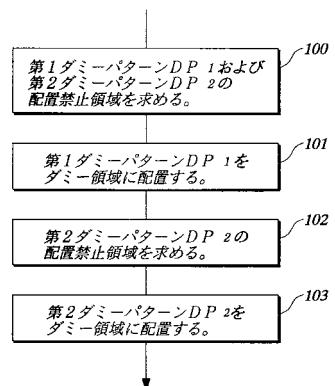

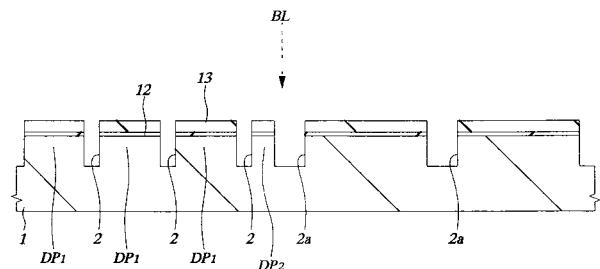

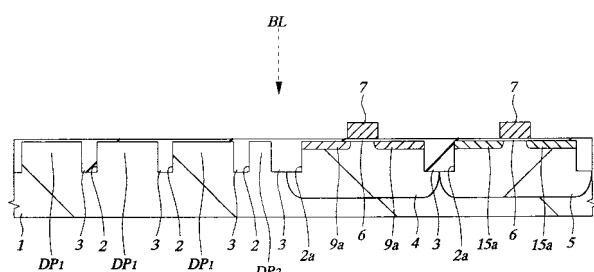

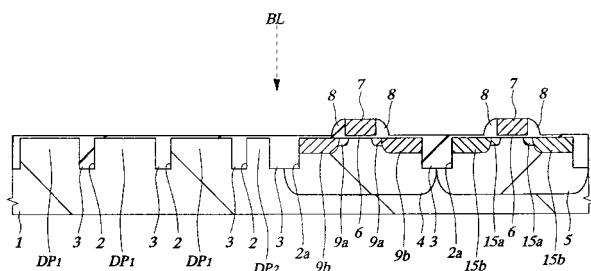

本実施の形態1であるダミーパターンの配置例を図1～図5によって説明する。図1は、ロジック集積回路装置の一例を示した要部平面図、図2は、図1のA-A線の断面図、図3は、ダミーパターンのピッチおよび寸法を説明するための平面図、図4は、ダミーパターンの配置の一例を説明するための平面図、図5は、ダミーパターンの作成方法の一例を示す工程図である。

20

【0027】

図1に示すように、破線で示す境界BLの内側が、半導体素子が形成される素子形成領域DAであり、境界BLの外側が、半導体素子が形成されないダミー領域FAである。

【0028】

素子形成領域DAとダミー領域FAとの境界BLは、素子分離領域IS上に延在する導体膜のレイアウトおよび活性領域ACのレイアウトから決められる。導体膜の下方にダミーパターンが形成されると容量負荷が増加するなどの問題が生じるため、導体膜とダミーパターンが重ならないように上記境界BLを決める必要がある。本実施の形態1では、素子分離領域IS上に延在する導体膜のレイアウトおよび活性領域ACのレイアウトを基に、これに容量負荷を低減するに必要な余裕寸法、リソグラフィ技術における合わせ精度などを考慮して、上記境界BLが決定される。

30

【0029】

素子形成領域DAには、図1および図2に示すように、CMOSFET (complementary metal oxide semiconductor Field effect transistor) C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>が形成されている。半導体基板1の主面に形成された分離溝2aに酸化シリコン膜3が埋め込まれた素子分離領域ISによって、活性領域ACが規定されている。

【0030】

半導体基板1の主面にはp型ウェル4およびn型ウェル5が形成されており、p型ウェル4にはnチャネルMISFET (metal insulator semiconductor FET)、n型ウェル5にはpチャネルMISFETが形成される。半導体基板1の主面上にはnチャネルMISFETおよびpチャネルMISFETのゲート絶縁膜6を介してゲート電極7が形成されている。ゲート絶縁膜6は、たとえば熱酸化法により形成された酸化シリコン膜とことができ、ゲート電極7は、たとえばCVD (chemical vapor deposition) 法により形成された多結晶シリコン膜とすることができます。多結晶シリコン膜の表面には、電気抵抗低減のためのシリサイド層が形成されていてもよい。また、ゲート電極7は活性領域ACから素子分離領域IS上に延在するように形成されている。

40

【0031】

nチャネルMISFETおよびpチャネルMISFETのゲート電極7の側壁にはサイドウォールスペーサ8が形成されている。このサイドウォールスペーサ8は、たとえば酸化シリコン膜または窒化シリコン膜とすることができます。また、nチャネルMISFET

50

のゲート電極 7 の両側の p 型ウェル 4 にはチャネル領域を挟んでソース、ドレイン拡張領域 9 a が形成され、さらにソース、ドレイン拡張領域 9 a の外側にはソース、ドレイン拡散領域 9 b が形成されている。同様に、図示はしないが、p チャネルM I S F E T のゲート電極 7 の両側の n 型ウェル 5 にはチャネル領域を挟んでソース、ドレイン拡張領域が形成され、さらにソース、ドレイン拡張領域の外側にはソース、ドレイン拡散領域が形成されている。n チャネルM I S F E T および p チャネルM I S F E T のソース、ドレインは、いわゆる L D D (lightly doped drain) 構造をなしている。

#### 【 0 0 3 2 】

素子形成領域 D A に形成された C M O S F E T C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub> は層間絶縁膜 1 0 で覆われてあり、この層間絶縁膜 1 0 には活性領域 A C の p 型ウェル 4 および n 型ウェル 5 、さらにゲート電極 7 に達するコンタクトホール 1 1 が形成されている。層間絶縁膜 1 0 は、たとえば酸化シリコン膜とすることができる、その表面はエッチバック法または C M P 法により平坦化されていることが好ましい。層間絶縁膜 1 0 上には配線が形成されるが、その図示は省略する。

#### 【 0 0 3 3 】

ダミー領域 F A には、複数の相対的に面積の大きい第 1 ダミーパターン D P <sub>1</sub> (図 1 中、相対的に薄い網掛けのハッチングで示す) および複数の相対的に面積の小さい第 2 ダミーパターン D P <sub>2</sub> (図 1 中、相対的に濃い網掛けのハッチングで示す半導体島) が規則的に配置されている。図 3 に示すように、第 1 ダミーパターン D P <sub>1</sub> は、一辺の寸法が行方向、列方向共に L a であって、活性領域 A C に相当する正方形の半導体島で構成され、ダミー領域のうち相対的に広い領域を占めている。第 2 ダミーパターン D P <sub>2</sub> は、一辺の寸法が行方向、列方向共に L b であって、活性領域 A C に相当する正方形の半導体島で構成され、ダミー領域のうち相対的に狭い領域に配置されている。

#### 【 0 0 3 4 】

ここで、第 1 ダミーパターン D P <sub>1</sub> の一辺の寸法 L a は第 2 ダミーパターン D P <sub>2</sub> の一辺の寸法 L b よりも大きく設定されるが、隣接する第 1 ダミーパターン D P <sub>1</sub> 間のスペース寸法と隣接する第 2 ダミーパターン D P <sub>2</sub> 間のスペース寸法とは同じスペース寸法 S a に設定されており、第 1 ダミーパターン D P <sub>1</sub> および第 2 ダミーパターン D P <sub>2</sub> はお互いに同じ間隔で離れている。

#### 【 0 0 3 5 】

また、図 4 に示すように、第 1 ダミーパターン D P <sub>1</sub> の一辺の寸法 L a にスペース寸法 S a を加えたパターンサイズは、行方向、列方向共に第 2 ダミーパターン D P <sub>2</sub> の一辺の寸法 L b にスペース寸法 S a を加えたパターンサイズの整数倍となっており、L a + S a = N × (L b + S a) (N 1 の整数) の関係を満たしている。これにより、ダミー領域 F A に寸法の異なる第 1 ダミーパターン D P <sub>1</sub> および第 2 ダミーパターン D P <sub>2</sub> を規則的に複数配置することができるので、マスクを作成する際の座標データが増加しても、計算機での演算処理時間の増加を抑えることが可能となる。

#### 【 0 0 3 6 】

また、第 1 ダミーパターン D P <sub>1</sub> の寸法 L a 、第 2 ダミーパターン D P <sub>2</sub> の寸法 L b およびスペース寸法 S a は、最小許容寸法 (パターン設計上許される最小寸法) 以上に設定されている。これらの値が最小許容寸法よりも小さくなると、素子分離領域 I S を形成する際、レジストパターンの剥離、ドライエッチング工程での分離溝の加工不良、または分離溝内への酸化シリコン膜の埋め込み不良などの問題が生ずるためである。たとえば第 1 ダミーパターン D P <sub>1</sub> の一辺の寸法 L a は 2.0 μm 、第 2 ダミーパターン D P <sub>2</sub> の一辺の寸法 L b は 0.8 μm 、スペース寸法 S a は 0.4 μm に設定される。

#### 【 0 0 3 7 】

次に、図 5 を用いて、ダミーパターンの配置方法を説明する。ダミーパターンは、まず計算機で自動プログラムを用いてその配置データが作成される。次いで、この配置データを基にマスク基板上にダミーパターンが描画され、マスクを介してダミーパターンが半導体基板に転写される。ここでは、自動プログラムを用いた第 1 ダミーパターン D P <sub>1</sub> およ

10

20

30

40

50

び第2ダミーパターンDP<sub>2</sub>の配置データの作成方法を説明する。

【0038】

まず、第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>の配置禁止領域（素子形成領域DA）を求める（図5の工程100）。前述したように、素子分離領域IS上に延在する導体膜のレイアウトおよび活性領域ACのレイアウトを基に、これに容量負荷を低減するに必要な余裕寸法、リソグラフィ技術における合わせ精度などを考慮して、上記配置禁止領域が決定される。すなわち、素子分離領域IS上に延在する導体膜の座標データおよび活性領域ACの座標データにそれぞれ規格寸法データが加えられ、得られた全てのデータのorをとることで配置禁止領域の座標データが求められる。たとえば、CMOSFETC<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>が形成される活性領域ACから2μm離れた領域を第1配置禁止領域とし、CMOSFETC<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>のゲート電極から1μm離れた領域を第2配置禁止領域とし、上記第1配置禁止領域と上記第2配置禁止領域のor領域を第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>の配置禁止領域とする。

10

【0039】

次に、相対的に面積の大きい第1ダミーパターンDP<sub>1</sub>をダミー領域FAの大部分に敷きつめる（図5の工程101）。たとえば半導体基板1の全面に第1ピッチでメッシュを作成した後、第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>の配置禁止領域に掛かるメッシュを除去する。または、半導体基板1の全面に第1ピッチでメッシュを作成した後、第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>の配置禁止領域のメッシュを除去し、さらに最小許容寸法以下のメッシュを除去する。この後、メッシュに第1ダミーパターンDP<sub>1</sub>を配置する。なお、ここでの第1ピッチとは、第1ダミーパターンDP<sub>1</sub>の一辺の寸法Laにスペース寸法Saを加えたパターンサイズ(La+Sa)である。

20

【0040】

次に、相対的に面積の小さい第2ダミーパターンDP<sub>2</sub>の配置禁止領域を求める（図5の工程102）。前記工程100で求めた第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>の配置禁止領域に、前記工程101で第1ダミーパターンDP<sub>1</sub>が敷き詰められた領域を加えて、第2ダミーパターンDP<sub>2</sub>の配置禁止領域とする。

【0041】

次に、相対的に面積の小さい第2ダミーパターンDP<sub>2</sub>をダミー領域FAに敷きつめる（図5の工程103）。たとえば半導体基板1の全面に第2ピッチでメッシュを作成した後、第2ダミーパターンDP<sub>2</sub>の配置禁止領域に掛かるメッシュを除去する。または、半導体基板1の全面に第2ピッチでメッシュを作成した後、第2ダミーパターンDP<sub>2</sub>の配置禁止領域のメッシュを除去し、さらに最小許容寸法以下のメッシュを除去する。この後、メッシュに第2ダミーパターンDP<sub>2</sub>を配置する。なお、ここでの第2ピッチとは、第2ダミーパターンDP<sub>2</sub>の一辺の寸法Lbにスペース寸法Saを加えたパターンサイズ(Lb+Sa)であって、さらに第2ダミーパターンDP<sub>2</sub>の第2ピッチは、第1ダミーパターンDP<sub>1</sub>の第1ピッチの整数(N)分の1、すなわち1/2となっている。第2ダミーパターンDP<sub>2</sub>の配置の容易さなどからも、第2ダミーパターンDP<sub>2</sub>の第2ピッチを第1ダミーパターンDP<sub>1</sub>の第1ピッチの整数分の1とするのが好ましい。

30

【0042】

なお、本実施の形態1では、素子形成領域DAから離れたダミー領域FAに複数の第1ダミーパターンDP<sub>1</sub>を配置し、素子形成領域DAに近いダミー領域FAに複数の第1ダミーパターンDP<sub>2</sub>を配置しているが、これに限定されないことは言うまでもない。たとえば素子形成領域DAに近いダミー領域FAに複数の第1ダミーパターンDP<sub>1</sub>を配置し、素子形成領域DAから遠いダミー領域FAに複数の第2ダミーパターンDP<sub>2</sub>を配置してもよく、あるいはダミー領域FAのほぼ全面に複数の第1ダミーパターンDP<sub>1</sub>を配置し、第2ピッチが生じた隣接する第1ダミーパターンDP<sub>1</sub>の間に複数の第2ダミーパターンDP<sub>2</sub>を配置してもよい。

40

【0043】

50

また、本実施の形態1では、素子形成領域DAに形成された半導体素子として、CMOSFETC<sub>1</sub>、C<sub>2</sub>、C<sub>3</sub>を例示したが、他の半導体素子、たとえばBi-CMOSトランジスタであってもよい。

【0044】

このように、本実施の形態1によれば、素子形成領域DAとダミー領域FAとの境界BL近くまで第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>を配置することができる、分離溝2, 2a内に埋め込まれた酸化シリコン膜3の表面の平坦性をダミー領域FAの全域において向上することができる。

【0045】

さらに、ダミー領域FAのうち相対的に広い領域を相対的に面積の大きい第1ダミーパターンDP<sub>1</sub>で占めることで、相対的に面積の小さい第2ダミーパターンDP<sub>2</sub>の配置数が相対的に少なくなり、マスクのデータ量の増加を抑えることができる。また、第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>の形状を正方形とすることにより、第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>は原点座標およびXY座標の最も少ないデータ量で表現することができる。これらにより、マスクを作成する際の座標データ量の増加を抑えることが可能となり、計算機での演算処理時間、マスク基板上へのパターン描画時間などの増加を抑えることができる。

【0046】

次に、本実施の形態1のロジック集積回路装置の製造方法の一例を図6～図16を用いて工程順に説明する。

【0047】

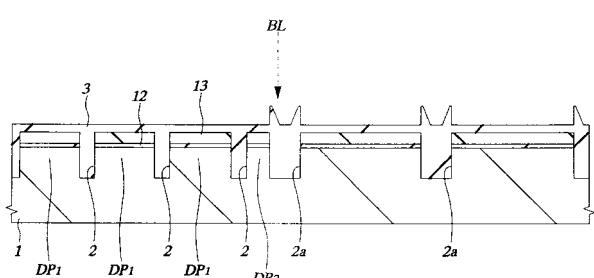

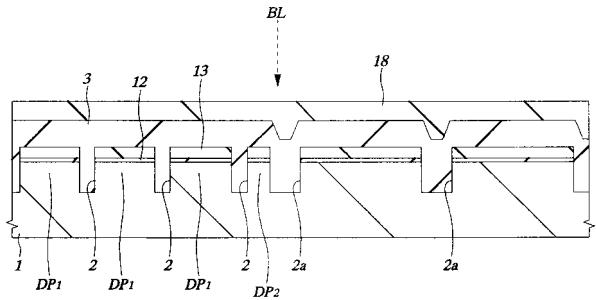

まず、図6に示すように、たとえばp型の単結晶シリコンからなる半導体基板1を用意する。次に、この半導体基板1を熱酸化してその表面に膜厚10nm程度の薄い酸化シリコン膜12を形成し、次いでその上層にCVD法で膜厚120～200nm程度の窒化シリコン膜13を堆積した後、レジストパターンをマスクとして窒化シリコン膜13、酸化シリコン膜12および半導体基板1を順次ドライエッティングすることにより、半導体基板1に深さ0.3～0.4μm程度の分離溝2, 2aを形成する。ダミー領域FAには、その全領域が分離溝とならないように第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>が設けられている。

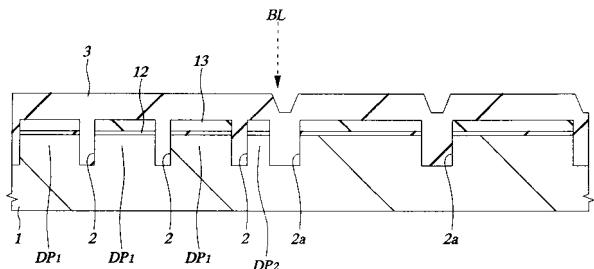

【0048】

次に、分離溝2, 2aの内壁の界面状態を清浄するために、半導体基板1に熱酸化処理を施して、図示はしないが、半導体基板1の露出している表面に10～30nm程度の薄い酸化シリコン膜を形成する。続いて、図7に示すように、半導体基板1上にCVD法またはプラズマCVD法で酸化シリコン膜3を堆積する。この酸化シリコン膜3の膜厚は、たとえば600～700nm程度であって、境界BLまたは素子形成領域DAに形成されやすい相対的に大きい分離溝2aに埋め込まれた酸化シリコン膜3の表面が窒化シリコン膜13の表面よりも高くなるように形成されている。

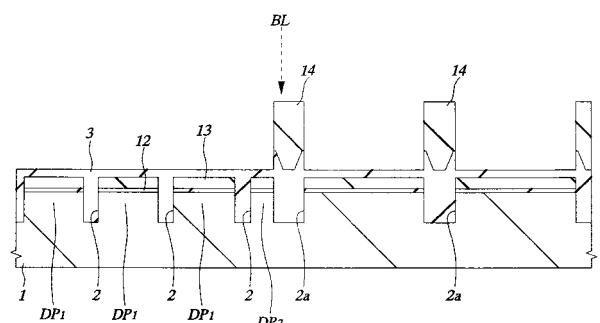

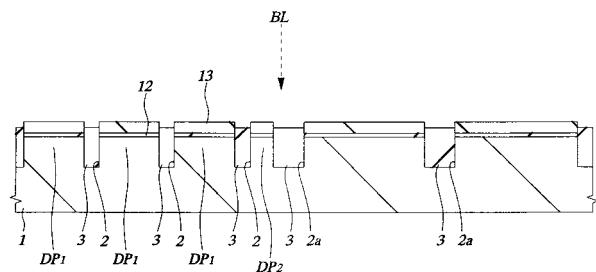

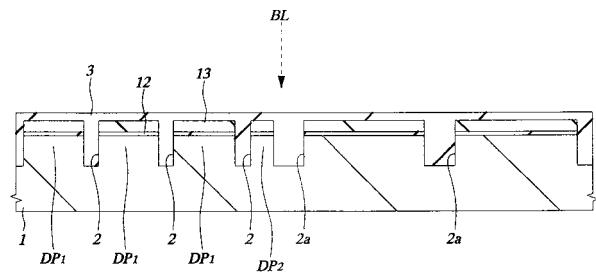

【0049】

次に、分離溝2の反転パターンのマスクを用意する。なお、このマスク上には、上記反転パターンのうち、境界BLまたは素子形成領域DAに形成されやすい相対的に大きい分離溝2aのみのパターンが描画されており、たとえば、0.6μmの特定寸法以下のパターンは除去される。このマスクを用いて酸化シリコン膜3上にレジストパターン14を形成し、図8に示すように、レジストパターン14をマスクとして酸化シリコン膜3をその膜厚の約1/2程度（たとえば300nm程度）エッティング除去する。これにより、後のCMP工程において、境界BLまたは素子形成領域DAに形成されやすい相対的に大きい分離溝2aに埋め込まれる酸化シリコン膜3の表面の平坦性を向上することができる。なお、レジストパターン14の下の酸化シリコン膜3には角状の突起が形成されるが、この突起は後のCMP工程で研磨される。

【0050】

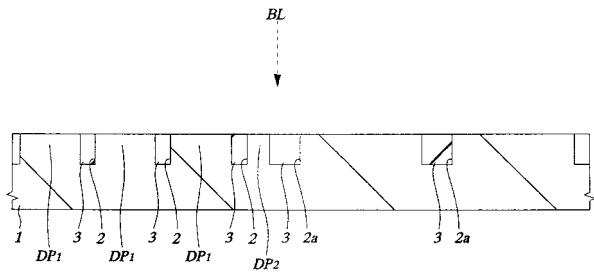

次に、図9に示すように、レジストパターン14を除去した後、図10に示すように、

10

20

30

40

50

CMP法で酸化シリコン膜3を研磨して、分離溝2, 2aの内部に酸化シリコン膜3を残す。この時、窒化シリコン膜13と酸化シリコン膜3との研磨速度を利用して、窒化シリコン膜13を研磨時のストップ層として機能させて、窒化シリコン膜13が削り取られないようにする。窒化シリコン膜13の削れ量は、たとえば60nm程度に抑えられる。続いて、半導体基板1を約1000°Cで熱処理することにより、分離溝2に埋め込んだ酸化シリコン膜3をデンシファイ(焼き締め)する。次に、図11に示すように、熱リン酸を用いたウェットエッティングで窒化シリコン膜13を除去し、続いてその下層の酸化シリコン膜12を除去する。

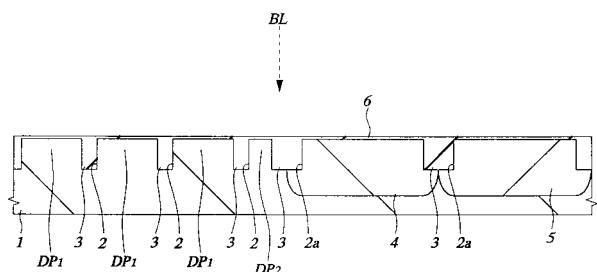

#### 【0051】

次に、図12に示すように、半導体基板1のnチャネルMISFETの形成領域にp型ウェル4を形成するためのp型不純物、たとえばボロン(B)をイオン注入し、pチャネルMISFETの形成領域にn型ウェル5を形成するためのn型不純物、たとえばリン(P)をイオン注入する。さらに、図示はしないが、チャネル領域に不純物をイオン注入する。この後、半導体基板1を熱酸化して、半導体基板1の表面にゲート絶縁膜6を、たとえば2nm程度の厚さで形成する。

#### 【0052】

次に、図13に示すように、半導体基板1上に多結晶シリコン膜をCVD法で堆積した後、レジストパターンをマスクとして多結晶シリコン膜をエッティングし、nチャネルMISFETおよびpチャネルMISFETのゲート電極7を形成する。続いて、半導体基板1に、たとえば800°C程度のドライ酸化処理を施す。

#### 【0053】

次いで、n型ウェル5をレジスト膜で覆った後、nチャネルMISFETのゲート電極7をマスクとしてp型ウェル4にn型不純物、たとえばヒ素(As)をイオン注入し、nチャネルMISFETのソース、ドレイン拡張領域9aを形成する。同様に、p型ウェル4をレジスト膜で覆った後、pチャネルMISFETのゲート電極7をマスクとしてn型ウェル5にp型不純物、たとえばフッ化ボロン(BF<sub>2</sub>)をイオン注入し、pチャネルMISFETのソース、ドレイン拡張領域15aを形成する。

#### 【0054】

次に、図14に示すように、半導体基板1上に絶縁膜、たとえば酸化シリコン膜または窒化シリコン膜をCVD法で堆積した後、この絶縁膜をRIE(reactive ion etching)法で異方性エッティングし、nチャネルMISFETのゲート電極7およびpチャネルMISFETのゲート電極7のそれぞれの側壁に、絶縁膜からなるサイドウォールスペーサ8を形成する。

#### 【0055】

次いで、n型ウェル5をレジスト膜で覆った後、nチャネルMISFETのゲート電極7およびサイドウォールスペーサ8をマスクとしてp型ウェル4にn型不純物、たとえばヒ素をイオン注入し、nチャネルMISFETのソース、ドレイン拡散領域9bを形成する。同様に、p型ウェル4をレジスト膜で覆った後、pチャネルMISFETのゲート電極7をマスクとしてn型ウェル5にp型不純物、たとえばフッ化ボロンをイオン注入し、pチャネルMISFETのソース、ドレイン拡散領域15bを形成する。

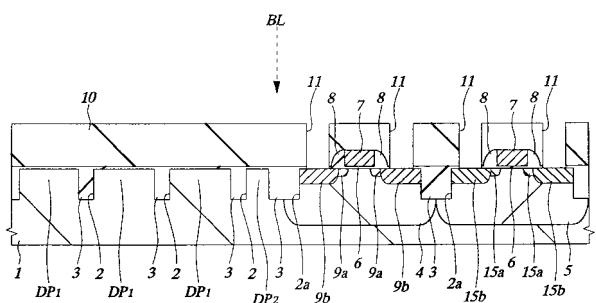

#### 【0056】

次に、図15に示すように、半導体基板1上に、たとえば酸化シリコン膜で構成される層間絶縁膜10を形成した後、この層間絶縁膜10の表面をエッチャック法またはCMP法を用いて平坦化する。次いで、レジストパターンをマスクとして層間絶縁膜10をエッティングし、nチャネルMISFETのソース、ドレイン拡散領域9bおよびpチャネルMISFETのソース、ドレイン拡散領域15bに達するコンタクトホール11を開孔する。なお、図示はしないが、同時にnチャネルMISFETおよびpチャネルMISFETのゲート電極7に達するコンタクトホールが形成される。

#### 【0057】

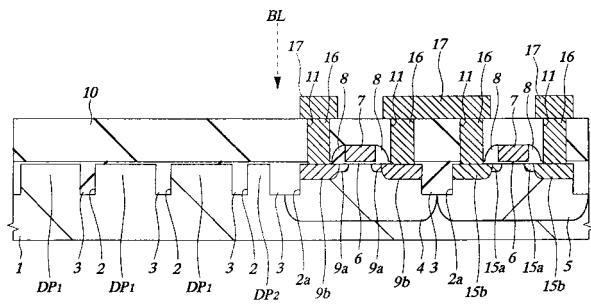

次いで、図16に示すように、層間絶縁膜10の上層に金属膜、たとえばタンゲステン

10

20

30

40

50

(W) 膜を堆積し、たとえばC M P法でこの金属膜の表面を平坦化することによって、上記コンタクトホール11の内部に金属膜を埋め込みプラグ16を形成する。その後、層間絶縁膜10の上層に堆積した金属膜をエッチングして第1層配線17を形成する。

【0058】

この後、第1層配線17よりも上層の配線を形成し、さらに表面保護膜を形成することによって、ロジック集積回路装置が略完成する。

【0059】

(実施の形態2)

本実施の形態2は、前記実施の形態1で説明した図1の構造を形成する場合の他の製造方法を説明するものである。

10

【0060】

本実施の形態2を説明する図17および図18は、前記実施の形態1において図6～図7で説明した製造工程を経た後の半導体基板の要部断面図を示している。

【0061】

ここでは、まず、半導体基板1に深さ0.3～0.4μm程度の分離溝2, 2aを形成し、次いで半導体基板1上にCVD法またはプラズマCVD法で酸化シリコン膜3を堆積する。

【0062】

次に、図17に示すように、酸化シリコン膜3の上層に塗布性絶縁膜18、たとえばSOG (spin on glass) 膜を形成する。この塗布性絶縁膜18は、その流動性から微細な段差がある場合にも、その表面を平坦化することができる。従って、上記酸化シリコン膜3の表面に窪みが生じた場合でも、塗布性絶縁膜18の表面は平坦化される。続いて半導体基板1に熱処理を施して、塗布性絶縁膜18中の溶剤を除去するとともに緻密化させる。この熱処理温度は、炉体アニールの場合は、たとえば400～500程度、RTA (rapid thermal annealing) の場合は、たとえば700～800程度とすることができる。

20

【0063】

次に、図18に示すように、エッチバック法で塗布性絶縁膜18をエッチングする。この際、酸化シリコン膜3のエッチング速度と塗布性絶縁膜18のエッチング速度とがほぼ同じとなる条件を用いて、塗布性絶縁膜18がほぼ全て除去するまでエッチングを行い、酸化シリコン膜3の表面を平坦化する。次いで、前記図10に示したように、C M P法で窒化シリコン膜2上の酸化シリコン膜3を研磨して、分離溝2, 2aの内部に酸化シリコン膜3を残す。

30

【0064】

これ以降は、前記実施の形態1の図11以降の図を用いて説明したのと同じなので説明を省略する。

【0065】

このように、本実施の形態2によれば、境界B Lまたは素子形成領域D Aに形成されやすい相対的に大きい分離溝2aに埋め込まれる酸化シリコン膜3の表面の平坦性を向上することができる。また、前記実施の形態1で酸化シリコン膜3の表面の平坦化に用いたレジストパターン14を転写するマスクが不要となるので、前記実施の形態1と比べて製造コストを抑えることができる。

40

【0066】

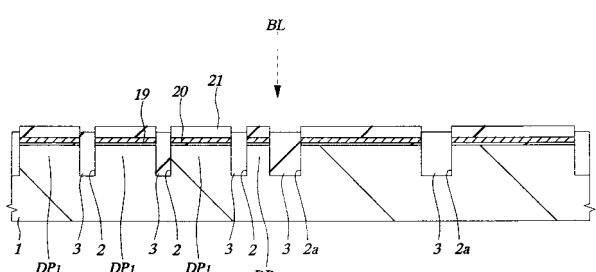

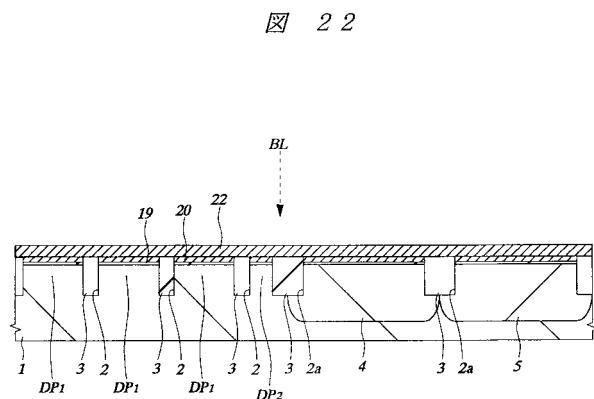

(実施の形態3)

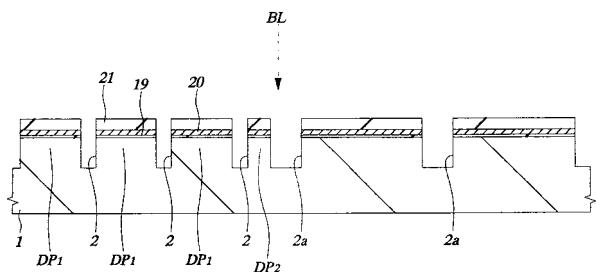

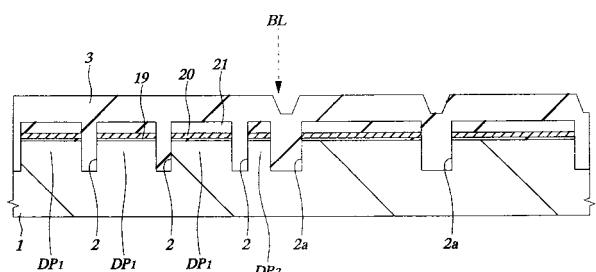

本実施の形態3は、前記実施の形態1で説明した図1の構造を形成する場合の他の製造方法を図19～図22を用いて説明するものである。

【0067】

まず、図19に示すように、たとえばp型の単結晶シリコンからなる半導体基板1を熱酸化してその表面に膜厚2～3nm程度の薄い酸化シリコン膜からなるゲート絶縁膜19を形成する。次いでその上層にCVD法で膜厚50nm程度の第1シリコン膜20および

50

120～200 nm程度の窒化シリコン膜21を順次堆積した後、レジストパターンをマスクとして窒化シリコン膜21、第1シリコン膜20およびゲート絶縁膜19を順次ドライエッチングする。上記第1シリコン膜20は非晶質シリコンまたは多結晶シリコンからなる。続いて上記レジストパターンを除去した後、窒化シリコン膜21をマスクとして半導体基板1をドライエッチングすることにより、半導体基板1に深さ0.3～0.4 μm程度の分離溝2, 2aを形成する。ダミー領域FAには、その全領域が分離溝とならないように第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>が設けられている。

【0068】

次に、図示はしないが、半導体基板1の露出している表面に10～30 nm程度の薄い酸化シリコン膜を形成した後、図20に示すように、半導体基板1上にCVD法またはプラズマCVD法で膜厚600～700 nm程度の酸化シリコン膜3を堆積する。次いで、図21に示すように、たとえば前記実施の形態1の図8～図10を用いて説明した製造方法と同様にして、分離溝2, 2aの内部に酸化シリコン膜3を残す。

10

【0069】

次に、図22に示すように、熱リン酸を用いたウェットエッチングで窒化シリコン膜21を除去する。この時、第1シリコン膜20は除去せず、CMOSFETC<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>のゲート電極の一部として用いる。次いで、半導体基板1のnチャネルMISFETの形成領域にp型ウェル4を形成するためのp型不純物をイオン注入し、pチャネルMISFETの形成領域にn型ウェル5を形成するためのn型不純物をイオン注入する。さらに、図示はしないが、チャネル領域に不純物をイオン注入する。この後、半導体基板1上に第2シリコン膜22を形成し、第1シリコン膜20および第2シリコン膜22からなる積層膜によって、CMOSFETC<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>のゲート電極が構成される。

20

【0070】

これ以降は、前記実施の形態1の図13以降の図を用いて説明したのと同じなので説明を省略する。

【0071】

このように、本実施の形態3によれば、素子分離領域ISの形成に用いた第1シリコン膜をCMOSFETC<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>のゲート電極の一部に用いることにより、素子分離領域ISに埋め込まれた酸化シリコン膜3の落ち込みによる分離溝の端部の丸みに起因したドレイン電流-ゲート電圧特性に生じるキンクを防止することができる。

30

【0072】

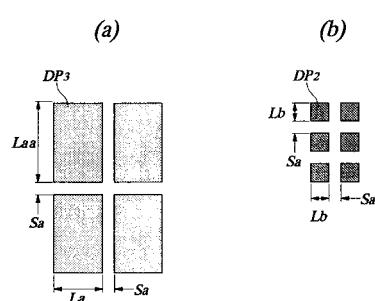

(実施の形態4)

本実施の形態4である他のダミーパターンの配置例を図23および図24によって説明する。図23は、ロジック集積回路装置の他の例を示した要部平面図、図24は、ダミーパターンのピッチおよび寸法を説明するための平面図である。

【0073】

図23に示すように、前記実施の形態1と同様に、破線で示す境界BLの内側が、半導体素子が形成される素子形成領域DAであって、この領域にはCMOSFETC<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>が形成されている。さらに境界BLの外側が、半導体素子が形成されないダミー領域FAである。

40

【0074】

ダミー領域FAには、前記実施の形態1で説明した第1ダミーパターンDP<sub>1</sub>および第2ダミーパターンDP<sub>2</sub>に加えて、さらにこれらよりも面積が大きい長方形の第3ダミーパターンDP<sub>3</sub>が配置されている。すなわち、ダミー領域FAには形状、面積の異なる3種類のダミーパターン(第1ダミーパターンDP<sub>1</sub>, 第2ダミーパターンDP<sub>2</sub>, 第3ダミーパターンDP<sub>3</sub>)が規則的に配置されている。上記第3ダミーパターンDP<sub>3</sub>は、活性領域ACに相当する長方形の半導体島(図23中、相対的に薄い網掛けのハッチングで示す)で構成されている。

【0075】

図24に示すように、第3ダミーパターンDP<sub>3</sub>の長辺の寸法Laaおよび短辺の寸法

50

L a は、第 2 ダミーパターン D P <sub>2</sub> の一辺の寸法 L b よりも大きく設定されるが、隣接する第 3 ダミーパターン D P <sub>3</sub> 間のスペース寸法は、隣接する第 2 ダミーパターン D P <sub>2</sub> 間のスペース寸法 S a と同じである。

#### 【0076】

また、第 3 ダミーパターン D P <sub>3</sub> の一辺の寸法は、行方向、列方向共に第 2 ダミーパターン D P <sub>2</sub> の一辺の寸法 L b にスペース寸法 S a を加えたパターンサイズの整数倍となっており、 $L a a + S a = N 1 (L b + S a)$ ， $L a + S a = N 2 \times (L b + S a)$  ( $N 1, N 2 \geq 1$  の整数) の関係を満たしている。これにより、ダミー領域 F A に寸法の異なる第 1 ダミーパターン D P <sub>1</sub>、第 2 ダミーパターン D P <sub>2</sub> および第 3 ダミーパターン D P <sub>3</sub> を規則的に複数配置することができるので、マスクを作成する際の座標データが増加しても、計算機での演算処理時間の増加を抑えることが可能となる。10

#### 【0077】

第 1 ダミーパターン D P <sub>1</sub>、第 2 ダミーパターン D P <sub>2</sub> および第 3 ダミーパターン D P <sub>3</sub> の配置データの作成は、前記実施の形態 1 で図 5 の工程図を用いて説明した第 1 ダミーパターン D P <sub>1</sub> および第 2 ダミーパターン D P <sub>2</sub> の配置データの作成方法と同様に行われる。

#### 【0078】

まず、第 1 ダミーパターン D P <sub>1</sub>、第 2 ダミーパターン D P <sub>2</sub> および第 3 ダミーパターン D P <sub>3</sub> の配置禁止領域（素子形成領域 D A）を求める。次いで、第 3 ダミーパターン D P <sub>3</sub> をダミー領域 F A の大部分に敷きつめる。たとえば半導体基板 1 の全面に第 3 ピッチでメッシュを作成した後、第 1 ダミーパターン D P <sub>1</sub>、第 2 ダミーパターン D P <sub>2</sub> および第 3 ダミーパターン D P <sub>3</sub> の配置禁止領域に掛かるメッシュを除去する。この後、メッシュに第 3 ダミーパターン D P <sub>3</sub> を配置する。なお、ここでの第 3 ピッチとは、一辺が第 3 ダミーパターン D P <sub>3</sub> の長辺の寸法 L a a にスペース寸法 S a を加えたパターンサイズ（ $L a a + S a$ ）、他辺が第 3 ダミーパターン D P <sub>3</sub> の短辺の寸法 L a にスペース寸法 S a を加えたパターンサイズ（ $L a + S a$ ）である。20

#### 【0079】

次に、第 1 ダミーパターン D P <sub>1</sub> の配置禁止領域を求める。第 1 ダミーパターン D P <sub>1</sub>、第 2 ダミーパターン D P <sub>2</sub> および第 3 ダミーパターン D P <sub>3</sub> の配置禁止領域に、第 3 ダミーパターン D P <sub>3</sub> が敷き詰められた領域を加えて、第 1 ダミーパターン D P <sub>1</sub> の配置禁止領域とする。次いで、第 1 ダミーパターン D P <sub>1</sub> をダミー領域 F A に敷きつめる。たとえば半導体基板 1 の全面に第 1 ピッチでメッシュを作成した後、第 1 ダミーパターン D P <sub>1</sub> の配置禁止領域に掛かるメッシュを除去する。この後、メッシュに第 1 ダミーパターン D P <sub>1</sub> を配置する。なお、ここでの第 1 ピッチとは、第 1 ダミーパターン D P <sub>1</sub> の一辺の寸法 L a にスペース寸法 S a を加えたパターンサイズ（ $L a + S a$ ）である。30

#### 【0080】

次に、第 2 ダミーパターン D P <sub>2</sub> の配置禁止領域を求める。第 1 ダミーパターン D P <sub>1</sub>、第 2 ダミーパターン D P <sub>2</sub> および第 3 ダミーパターン D P <sub>3</sub> の配置禁止領域に、第 1 ダミーパターン D P <sub>1</sub> および第 3 ダミーパターン D P <sub>3</sub> が敷き詰められた領域を加えて、第 2 ダミーパターン D P <sub>2</sub> の配置禁止領域とする。次いで、第 2 ダミーパターン D P <sub>2</sub> をダミー領域 F A に敷きつめる。たとえば半導体基板 1 の全面に第 2 ピッチでメッシュを作成した後、第 2 ダミーパターン D P <sub>2</sub> の配置禁止領域に掛かるメッシュを除去する。この後、メッシュに第 2 ダミーパターン D P <sub>2</sub> を配置する。なお、ここでの第 2 ピッチとは、第 2 ダミーパターン D P <sub>2</sub> の一辺の寸法 L b にスペース寸法 S a を加えたパターンサイズ（ $L b + S a$ ）である。40

#### 【0081】

このように、本実施の形態 4 によれば、ダミーパターンはその面積の大小に関わらず、任意の形状を選択することができ、また 3 種類あるいはそれ以上のダミーパターンを組み合わせることができる。これにより、ダミーパターンの配置の自由度が増して、分離溝 2，2 a 内に埋め込まれた酸化シリコン膜 3 の表面の平坦性を向上することができる。さら50

に、相対的に面積の大きいダミーパターン  $D P_3$  の配置数を増やすことで、マスクのデータ量の増加を抑えることができる。

【0082】

(実施の形態5)

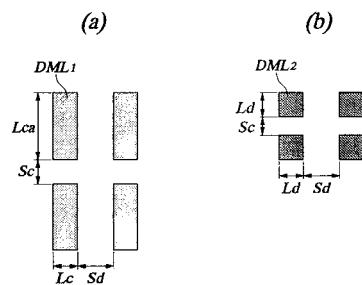

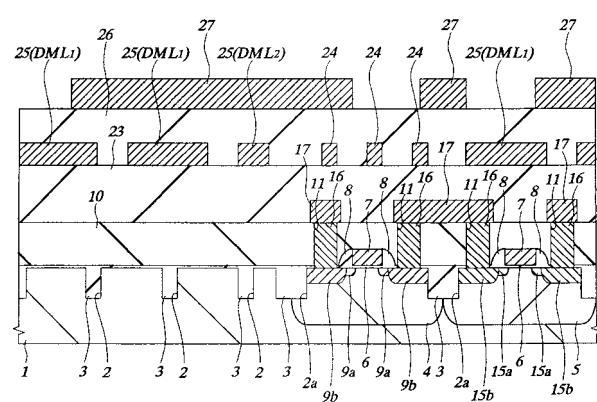

本実施の形態5である配線のダミーパターンの配置例を図25～図27によって説明する。図25は、配線のダミーパターンの一例を示す要部平面図、図26は、配線のダミーパターンのピッチおよび寸法を説明するための平面図、図27は、配線にダミーパターンを用いたロジック集積回路装置の一例を示す要部断面図である。

【0083】

配線工程における表面段差に起因した不都合を克服するための方法の一つに配線ダミー方式がある。この方式は、配線と同じ材料からなるダミーパターン(導電島)を配線の間に敷きつめる方法であって、配線を被覆する絶縁膜の平坦化、さらには表面段差の緩和に有効な手段である。この配線ダミー方式に本発明を適用した実施の形態5を以下に説明する。

【0084】

図25に示すように、破線で示す境界  $B_L$  の内側が、配線  $M_L$  が形成される素子形成領域  $D_A$  であり、境界  $B_L$  の外側が、配線  $M_L$  が形成されないダミー領域  $F_A$  である。

【0085】

ダミー領域  $F_A$  には、配線  $M_L$  と同一の導電層からなる複数の相対的に面積の大きい第1ダミー配線  $DML_1$  および複数の相対的に面積の小さい第2ダミー配線  $DML_2$  が規則的に配置されている。

【0086】

図26に示すように、ダミー領域  $F_A$  のうち相対的に広い領域を占める第1ダミー配線  $DML_1$  は、長辺の寸法が  $L_{ca}$ 、短辺の寸法が  $L_c$  の長方形の導電島(図25中、相対的に薄い網掛けのハッティングで示す)で構成され、第2ダミー配線  $DML_2$  は、一辺の寸法が行方向、列方向共に  $L_d$  の正方形の導電島(図25中、相対的に濃い網掛けのハッティングで示す)で構成されている。

【0087】

また、隣接する第1ダミー配線  $DML_1$  間の行間スペース寸法と隣接する第2ダミー配線  $DML_2$  間の行間スペース寸法とは同じスペース寸法  $S_c$  に設定され、隣接する第1ダミー配線  $DML_1$  間の列間スペース寸法と隣接する第2ダミー配線  $DML_2$  間の行間スペース寸法とは同じスペース寸法  $S_d$  に設定される。第1ダミー配線  $DML_1$  の幅  $L_{ca}$ 、 $L_c$  および第2ダミー配線  $DML_2$  の幅  $L_d$  は、リソグラフィ技術およびドライエッティング技術で要求される最小ライン幅以上とし、スペース  $S_c$ 、 $S_d$  は、リソグラフィ技術およびドライエッティング技術で要求される最小スペース幅以上とする。

【0088】

ここで、第1ダミー配線  $DML_1$  の長辺の寸法  $L_{ca}$  にスペース寸法  $S_c$  を加えたパターンサイズは、第2ダミー配線  $DML_2$  の一辺の寸法  $L_d$  にスペース寸法  $S_c$  を加えたパターンサイズの整数倍となっており、 $L_{ca} + S_c = N(L_d + S_c)$  ( $N$  1の整数)の関係を満たしている。同様に、第1ダミー配線  $DML_1$  の短辺の寸法  $L_c$  にスペース寸法  $S_d$  を加えたパターンサイズは、第2ダミー配線  $DML_2$  の一辺の寸法  $L_d$  にスペース寸法  $S_d$  を加えたパターンサイズの整数倍となっており、 $L_c + S_d = N(L_d + S_d)$  ( $N$  1の整数)の関係を満たしている。

【0089】

図27に、本実施の形態5の配線ダミー方式を適用したロジック集積回路装置の一例を示す半導体基板の要部断面図を示す。

【0090】

たとえば前記実施の形態1の図2に記載した  $C MOSFET C_1$ 、 $C_2$ 、 $C_3$  を覆って層間絶縁膜10が形成され、層間絶縁膜10上に、第1層配線17が形成されている。層間絶縁膜10の表面は  $CMP$  法またはエッチバック法などによって平坦化されている。さ

10

20

30

40

50

らに、第1層配線17は層間絶縁膜23によって覆われる。層間絶縁膜23の表面はエッチバック法などによって平坦化されている。

【0091】

層間絶縁膜23の上層には、第2層配線24およびダミー配線25が形成されている。ここで、ダミー配線25に、たとえば前記第1ダミー配線DML<sub>1</sub>および前記第2ダミー配線DML<sub>2</sub>が用いられる。第2層配線24およびダミー配線25は、同一の材料からなり同一工程で形成されるものである。材料としては、たとえばアルミニウム(A1)または銅(Cu)などの金属を例示することができる。

【0092】

第2層配線24およびダミー配線25は層間絶縁膜26によって覆われる。層間絶縁膜26は、たとえば酸化シリコン膜、SOG(spin on glass)および酸化シリコン膜からなる積層膜であり、上記酸化シリコン膜はTEOS(tetra ethyl ortho silicate: Si(OCH<sub>3</sub>)<sub>4</sub>)とオゾン(O<sub>3</sub>)とをソースガスに用いてプラズマCVD法で堆積されたTEOS酸化膜とすることができる。層間絶縁膜26の表面は、CMP法により研磨されたものであり、ダミー配線25(第1ダミー配線DML<sub>1</sub>、第2ダミー配線DML<sub>2</sub>)を用いることで、その表面は平坦化されている。

【0093】

さらに層間絶縁膜26の上層に第3層配線27が形成され、図示はしないが、最上層絶縁膜であるパッシベーション膜が形成されている。

【0094】

なお、本実施の形態5では、第2層配線24の形成工程でダミー配線25を配置したが、第1層配線17または第3層配線27の形成工程でダミー配線を配置してもよい。また、第3層配線27よりも上層の配線を形成した場合でも、これら配線の形成工程でダミー配線を配置することも可能である。

【0095】

このように、本実施の形態5によれば、相対的に面積の大きい第1ダミー配線DML<sub>1</sub>と相対的に面積の小さい第2ダミー配線DML<sub>2</sub>とを用いることにより、ダミー領域FAの全域にダミー配線25が配置できるので、第2層配線24の上層に形成される層間絶縁膜26の表面の平坦性が向上する。さらに、ダミー領域FAのうち相対的に広い領域を相対的に面積の大きい第1ダミー配線DML<sub>1</sub>で占めることで、相対的に面積の小さい第2ダミー配線DML<sub>2</sub>の配置数が相対的に少なくなり、マスクのデータ量の増加を抑えることができる。

【0096】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0097】

たとえば、前記実施の形態では、ダミーパターンの形状を正方形または長方形としているが、これに限られるものではなく、三角形、台形、円あるいは他の多角形としてもよい。

【産業上の利用可能性】

【0098】

本発明は、その製造工程にCMP法を用いた平坦化工程を含む半導体装置に適用することができる。

【図面の簡単な説明】

【0099】

【図1】本実施の形態1のロジック集積回路装置の一例を示した要部平面図である。

【図2】図1のA-A線の断面図である。

【図3】ダミーパターンのピッチおよび寸法を説明するための平面図である。

【図4】ダミーパターンの配置の一例を説明するための平面図である。

10

20

30

40

50

【図 5】ダミーパターンの作成方法の一例を示す工程図である。

【図 6】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 7】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 8】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 9】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 10】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。 10

【図 11】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 12】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 13】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 14】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 15】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。 20

【図 16】本実施の形態 1 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 17】本実施の形態 2 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 18】本実施の形態 2 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 19】本実施の形態 3 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。 30

【図 20】本実施の形態 3 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 21】本実施の形態 3 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 22】本実施の形態 3 であるロジック集積回路装置の製造方法の一例を工程順に示す半導体基板の要部断面図である。

【図 23】本実施の形態 4 の他のロジック集積回路装置の一例を示した要部平面図である。 40

【図 24】ダミーパターンのピッチおよび寸法を説明するための平面図である。

【図 25】本実施の形態 5 の配線のダミーパターンの一例を示す要部平面図である。

【図 26】配線のダミーパターンのピッチおよび寸法を説明するための平面図である。

【図 27】本実施の形態 5 の配線にダミーパターンを用いたロジック集積回路装置の一例を示す要部断面図である。

【図 28】本発明者が検討した第 1 のダミーパターンの配置方法を示す平面図である。

【図 29】本発明者が検討した第 2 のダミーパターンの配置方法を示す平面図である。

【符号の説明】

【0100】

1 半導体基板

2 分離溝

2a 分離溝

3 酸化シリコン膜

|                    |               |    |

|--------------------|---------------|----|

| 4                  | p型ウェル         |    |

| 5                  | n型ウェル         |    |

| 6                  | ゲート絶縁膜        |    |

| 7                  | ゲート電極         |    |

| 8                  | サイドウォールスペーサ   |    |

| 9 a                | ソース、ドレイン拡張領域  | 10 |

| 9 b                | ソース、ドレイン拡散領域  |    |

| 10                 | 層間絶縁膜         |    |

| 11                 | コンタクトホール      |    |

| 12                 | 酸化シリコン膜       |    |

| 13                 | 窒化シリコン膜       |    |

| 14                 | レジストパターン      |    |

| 15 a               | ソース、ドレイン拡張領域  |    |

| 15 b               | ソース、ドレイン拡散領域  |    |

| 16                 | プラグ           |    |

| 17                 | 第1層配線         |    |

| 18                 | 塗布性絶縁膜        |    |

| 19                 | ゲート絶縁膜        |    |

| 20                 | 第1シリコン膜       | 20 |

| 21                 | 窒化シリコン膜       |    |

| 22                 | 第2シリコン膜       |    |

| 23                 | 層間絶縁膜         |    |

| 24                 | 第2層配線         |    |

| 25                 | ダミー配線         |    |

| 26                 | 層間絶縁膜         |    |

| 27                 | 第3層配線         |    |

| D A                | 素子形成領域        |    |

| F A                | ダミー領域         |    |

| A C                | 活性領域          |    |

| I S                | 素子分離領域        | 30 |

| B L                | 境界            |    |

| M L                | 配線            |    |

| D P <sub>1</sub>   | 第1ダミーパターン     |    |

| D P <sub>2</sub>   | 第2ダミーパターン     |    |

| D P <sub>3</sub>   | 第3ダミーパターン     |    |

| D M L <sub>1</sub> | 第1ダミー配線       |    |

| D M L <sub>2</sub> | 第2ダミー配線       |    |

| D P A <sub>1</sub> | ダミーパターン       |    |

| D P A <sub>2</sub> | ダミーパターン       |    |

| C <sub>1</sub>     | C M O S F E T | 40 |

| C <sub>2</sub>     | C M O S F E T |    |

| C <sub>3</sub>     | C M O S F E T |    |

【図1】

図 1

DA : 素子形成領域

FA : ダミー領域

DP1 : 第1ダミーパターン

DP2 : 第2ダミーパターン

【図2】

図 2

【図3】

図 3

【図4】

図 4

【図5】

図 5

【図6】

図 6

【図7】

図 7

【図8】

図 8

【図9】

図 9

【図 1 0】

図 1 0

【図 1 1】

図 1 1

【図 1 2】

図 1 2

【図 1 3】

図 1 3

【 図 1 4 】

【 図 1 5 】

四 14

☒ 15

【図16】

【 図 1 7 】

四 16

☒ 17

【図 18】

図 18

【図 19】

図 19

【図 20】

図 20

【図 21】

図 21

【図 2 2】

【図 2 3】

図 2 3

【図 2 4】

図 2 4

【図 2 5】

図 2 5

【図 2 6】

図 2 6

【図 2 7】

図 2 7

【図 2 8】

図 2 8

【図 2 9】

図 2 9

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

H 01 L 27/08 (2006.01) H 01 L 27/08 321F

H 01 L 21/8238 (2006.01)

H 01 L 27/092 (2006.01)

F ターム(参考) 5F032 AA34 AA35 AA44 AA69 AA77 BA02 BB06 BB08 CA17 DA02

DA09 DA23 DA33 DA78

5F033 HH04 HH05 HH08 HH11 HH25 JJ19 KK01 KK04 KK25 MM07

MM21 MM29 PP06 QQ07 QQ08 QQ09 QQ13 QQ16 QQ19 QQ31

QQ37 QQ48 QQ58 QQ65 QQ73 QQ74 QQ76 QQ89 RR04 RR06

RR09 RR25 SS04 SS11 SS15 SS22 SS25 SS27 TT08 UU03

VV02 VV06 XX01 XX34

5F038 CA05 CA07 CA17 CA18 CD18 EZ11 EZ14 EZ15 EZ20

5F048 AA04 AA07 AC03 BA01 BB06 BB07 BB08 BB12 BC06 BE03

BF07 BF11 BF16 BG13 DA25 DA27