(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6612856号

(P6612856)

(45) 発行日 令和1年11月27日(2019.11.27)

(24) 登録日 令和1年11月8日(2019.11.8)

(51) Int.Cl.

G 11 C 11/412 (2006.01)

F 1

G 11 C 11/412 120

請求項の数 21 (全 20 頁)

|                    |                               |           |                                                                                                         |

|--------------------|-------------------------------|-----------|---------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2017-515940 (P2017-515940)  | (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775                   |

| (86) (22) 出願日      | 平成27年9月15日 (2015.9.15)        | (73) 特許権者 | 507175175<br>インダストリーアカデミック コーポレ<br>ーション ファウンデーション、ヨンセイ<br>ユニバーシティ<br>大韓民国 03722 ソウル ソデムン<br>一ク ヨンセイロ 50 |

| (65) 公表番号          | 特表2017-532710 (P2017-532710A) | (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                                  |

| (43) 公表日           | 平成29年11月2日 (2017.11.2)        | (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                                  |

| (86) 國際出願番号        | PCT/US2015/050236             |           |                                                                                                         |

| (87) 國際公開番号        | W02016/048722                 |           |                                                                                                         |

| (87) 國際公開日         | 平成28年3月31日 (2016.3.31)        |           |                                                                                                         |

| 審査請求日              | 平成30年9月6日 (2018.9.6)          |           |                                                                                                         |

| (31) 優先権主張番号       | 14/499, 149                   |           |                                                                                                         |

| (32) 優先日           | 平成26年9月27日 (2014.9.27)        |           |                                                                                                         |

| (33) 優先権主張国・地域又は機関 | 米国 (US)                       |           |                                                                                                         |

| 早期審査対象出願           |                               |           |                                                                                                         |

最終頁に続く

(54) 【発明の名称】 読出しディスター・パンスの低減された7トランジスタ・スタティックランダムアクセスメモリビットセル

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のプルアップトランジスタ、第1のプルダウントランジスタ、および第1の記憶ノードを備える、第1のインバータと、

第2のプルアップトランジスタ、第2のプルダウントランジスタ、および第2の記憶ノードを備える、第2のインバータであって、前記第2の記憶ノードは、前記第1のプルアップトランジスタおよび前記第1のプルダウントランジスタのゲートに結合されている、第2のインバータと、

前記第1の記憶ノードに直接結合されたアクセストランジスタと、

前記第1の記憶ノードを前記第2のプルアップトランジスタおよび前記第2のプルダウントランジスタのゲートに選択的に結合させるように構成された、トランスマッシュゲートであって、読み出し動作の間、前記第1の記憶ノードを、前記第2のプルアップトランジスタおよび前記第2のプルダウントランジスタのゲートから選択的に切り離すように構成されるトランスマッシュゲートと

を備え、

前記トランスマッシュゲートが、並列に結合されたPMOSトランジスタおよびNMOSトランジスタを備え、

前記NMOSトランジスタが、書き込みモードおよびスタンバイモードにおいてアクティブにされるように構成され、保持モードおよび読み出しモードにおいて非アクティブにされるように構成される、7トランジスタ・スタティックランダムアクセスメモリ(7T SRAM)ビットセ

ル。

**【請求項 2】**

前記PMOSトランジスタが、保持モードおよびスタンバイモードにおいてアクティブにされるように構成され、読み出しモードおよび書き込みモードにおいて非アクティブにされるように構成される、請求項1に記載の7T SRAMビットセル。

**【請求項 3】**

前記PMOSトランジスタのゲートが、前記アクセストランジスタのゲートに結合されたワード線に結合される、請求項1に記載の7T SRAMビットセル。

**【請求項 4】**

前記NMOSトランジスタのゲートが、第1の書き込みワード線に結合される、請求項1に記載の7T SRAMビットセル。 10

**【請求項 5】**

前記アクセストランジスタが、ビット線を前記第1の記憶ノードに結合させるように構成され、前記アクセストランジスタが、読み出しモードまたは書き込みモードにおいてアクティブにされるように構成される、請求項1に記載の7T SRAMビットセル。

**【請求項 6】**

前記第1のプルダウントランジスタが、第2の書き込みワード線に結合される、請求項5に記載の7T SRAMビットセル。

**【請求項 7】**

前記7T SRAMビットセルが書き込み動作のために選択されないとき、前記トランスマッシュョンゲートがオフにされるように構成される、請求項1に記載の7T SRAMビットセル。 20

**【請求項 8】**

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、パーソナルデジタルアシスタント(PDA)、固定位置データユニット、モバイル電話、およびコンピュータから成る群から選択されるデバイスに組み込まれる、請求項1に記載の7T SRAMビットセル。

**【請求項 9】**

前記第2の記憶ノードが、前記第1のプルダウントランジスタおよび前記第1のプルアップトランジスタのゲートに直接結合される、請求項1に記載の7T SRAMビットセル。

**【請求項 10】**

前記トランスマッシュョンゲートの第1の端子が、前記第1の記憶ノードに直接結合され、前記トランスマッシュョンゲートの第2の端子が、前記第2のプルダウントランジスタおよび前記第2のプルアップトランジスタの前記ゲートに直接結合される、請求項1に記載の7T SRAMビットセル。 30

**【請求項 11】**

7トランジスタスタッキックランダムアクセスメモリ(7T SRAM)ビットセルを動作させる方法であって、

読み出し動作の間、第1のインバータの第1の記憶ノードを第2のインバータのゲートから選択的に切り離すステップであって、前記第2のインバータの第2の記憶ノードは、前記第1のインバータのゲートに結合されている、選択的に切り離すステップと、 40

前記第1の記憶ノードに記憶されたデータ値を、前記第1の記憶ノードに直接結合されたアクセストランジスタを通じて読み出すステップとを含み、

前記選択的に切り離すステップが、並列に結合されたPMOSトランジスタおよびNMOSトランジスタから形成されるトランスマッシュョンゲートを選択的に非アクティブにするステップを含み、

前記方法がさらに、

保持モードの間、前記PMOSトランジスタを、前記アクセストランジスタに結合されたワード線を通じてオンにし、かつ前記NMOSトランジスタを、第1のワード線を通じてオフにすることによって、前記第1のインバータの前記第1の記憶ノードを前記第2のインバータ 50

の前記ゲートに選択的に結合させるステップをさらに含む、方法。

【請求項 12】

7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルを動作させる方法であって、

読み出し動作の間、第1のインバータの第1の記憶ノードを第2のインバータのゲートから選択的に切り離すステップであって、前記第2のインバータの第2の記憶ノードは、前記第1のインバータのゲートに結合されている、選択的に切り離すステップと、

前記第1の記憶ノードに記憶されたデータ値を、前記第1の記憶ノードに直接結合されたアクセストランジスタを通じて読み出すステップと

を含み、

10

前記方法が、さらに、

前記7T SRAMビットセルを備える複数の7T SRAMビットセルから成るロウに論理値の組合せを備えるデータパターンを書き込むために、第1の段階において、前記ロウ内の前記複数の7T SRAMビットセルに論理値「1」を書き込み、第2の段階において、前記ロウ内の前記複数の7T SRAMビットセルに、前記論理値の前記組合せを含む前記データパターンを書き込むステップをさらに含む、方法。

【請求項 13】

前記選択的に切り離すステップが、並列に結合されたPMOSトランジスタおよびNMOSトランジスタから形成されるトランスマッシュゲートを選択的に非アクティブにするステップを含む、請求項12に記載の方法。

20

【請求項 14】

書き込み動作の間、前記トランスマッシュゲートの前記NMOSトランジスタを、第1の書き込みワード線を通じてアクティブにすることによって、前記第1のインバータの前記第1の記憶ノードを前記第2のインバータの前記ゲートに選択的に結合させるステップをさらに含む、請求項11または13に記載の方法。

【請求項 15】

前記アクセストランジスタに結合されたビット線から前記第1の記憶ノードに論理値「0」を書き込むために、前記アクセストランジスタを、ワード線を通じてイネーブルするステップをさらに含む、請求項14に記載の方法。

30

【請求項 16】

前記第1の記憶ノードに前記論理値「0」を書き込むためのブーストを行うように、前記第1のインバータの第1のプルダウントランジスタを、論理「0」に駆動された第2の書き込みワード線に結合させるステップをさらに含む、請求項15に記載の方法。

【請求項 17】

前記アクセストランジスタに結合されたビット線から前記第1の記憶ノードに論理値「1」を書き込むために、前記アクセストランジスタを、ワード線を通じてイネーブルするステップをさらに含む、請求項14に記載の方法。

【請求項 18】

前記第1の記憶ノードに前記論理値「1」を書き込むためのブーストを行うように、前記第1のインバータの第1のプルダウントランジスタを、論理「1」に駆動された第2の書き込みワード線に結合させるステップをさらに含む、請求項17に記載の方法。

40

【請求項 19】

スタンバイモードの間、前記PMOSトランジスタを、前記アクセストランジスタに結合されたワード線を通じてオンにし、かつ前記NMOSトランジスタを、第1のワード線を通じてオンにすることによって、前記第1のインバータの前記第1の記憶ノードを前記第2のインバータの前記ゲートに選択的に結合させるステップをさらに含む、請求項11または13に記載の方法。

【請求項 20】

前記7T SRAMビットセルが書き込み動作のために選択されないとき、前記第1のインバータの前記第1の記憶ノードを前記第2のインバータの前記ゲートから選択的に切り離すステッ

50

プをさらに含む、請求項11または12に記載の方法。

【請求項 2 1】

7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルであって、

読み出し動作の間、第1のインバータの第1の記憶ノードを前記7T SRAMビットセルの第2の

インバータのゲートから選択的に切り離すための手段であって、前記第2のインバータの

第2の記憶ノードは、前記第1のインバータのゲートに結合されている、選択的に切り離す

ための手段と、

前記第1の記憶ノードに直接結合されるアクセストランジスタを通じて前記第1の記憶ノードに記憶されたデータ値を読み出すための手段と

を備え、

10

前記選択的に切り離すための手段が、並列に結合されたPMOSトランジスタおよびNMOSトランジスタを備え、

前記NMOSトランジスタが、書き込みモードおよびスタンバイモードにおいてアクティブに

されるように構成され、保持モードおよび読み出しモードにおいて非アクティブにされるよ

うに構成される、7T SRAMビットセル。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

開示する態様は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルに

関係するシステムおよび方法を含む。例示的態様は、読み出しはりバーンス(Read Disturbance)、

および半選択問題の影響の受けやすさが低減され、ノイズマージンが改

善された、7T SRAMビットセルに関する。

20

【背景技術】

【0 0 0 2】

メモリデバイスは、従来、データのビットをそれぞれが記憶するビットセルのアレイを

含む。各データビットは、論理0(「0」)または論理1(「1」)を表すことができ、これは、

ビットセルの状態に対応してよい。選択されたビットセルの読み出し動作の間、低電圧レ

ベルが論理「0」を表し、相対的により高い電圧レベルが論理「1」を表す。

【0 0 0 3】

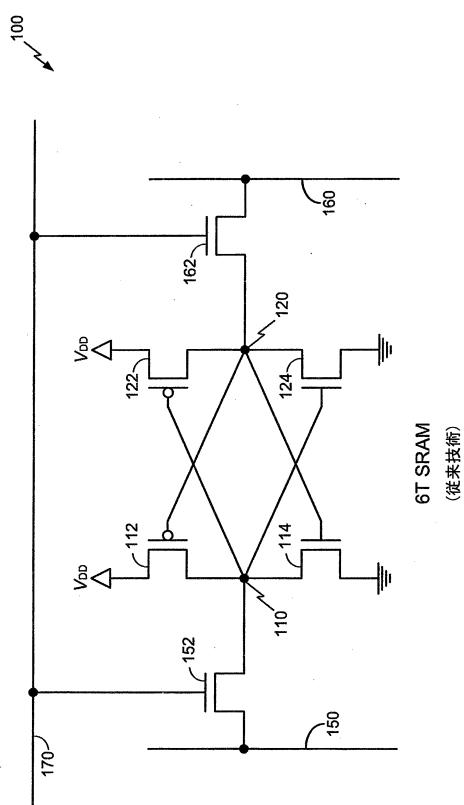

図1は、従来の6トランジスタスタティックランダムアクセスメモリ(6T SRAM)ビットセル100を示す。ビットセル100は、1対の交差結合されたインバータを備え、交差結合され

た各インバータは、記憶ノードによって分離されたpチャネル金属酸化膜半導体(PMOS)プ

ルアップトランジスタおよびnチャネル金属酸化膜(NMOS)プルダウントランジスタを備

える。第1のインバータが、第1の論理値を記憶する第1の記憶ノード110を備える。第1の記

憶ノード110は、第1のプルアップトランジスタ112と第1のプルダウントランジスタ114と

の間に配置される。第2のインバータが、第2の論理値を記憶する第2の記憶ノード120を備

える。第2の記憶ノード120は、第2のプルアップトランジスタ122と第2のプルダウントラ

ンジスタ124との間に配置される。この1対のインバータが交差結合されると、第1の論理

値が、第2の論理値とは反対または逆になる。

30

【0 0 0 4】

ビットセル100の読み出し動作では、ビット線150とビット線160が両方とも予備充電され

る。次いで、ワード線170が、ビットセル100を選択するために高電圧状態に設定され、それ

により、トランジスタ152および162がオンになる。6T SRAMビットセル100が論理「1」

を記憶している場合、一般性を失うことなく、論理「1」が第1のインバータの第1の記憶

ノード110のところに現れ、論理「0」が第2のインバータの第2の記憶ノード120のところ

に現れる。アクセストランジスタ152および162をオンにすることによって、ビット線150

上の電圧は、プルアップトランジスタ112によって維持されるが、ビット線160上の電圧は

、プルダウントランジスタ124によって放電される。センス増幅器(図示せず)を使用して

、ビット線150およびビット線160上に現れる差電圧を増幅すると、論理値「1」が読み出

される。一方、ビットセル100に論理「0」が記憶されている場合、論理「0」が第1の記憶

ノード110のところに現れ、論理「1」が第2の記憶ノード120のところに現れる。

40

50

ノード110のところに現れ、論理「1」が第2の記憶ノード120のところに現れる。ビットセル100の読み出しあは、ビット線150が放電され、ビット線160が高電圧に充電されたままになって、最終的に論理値「0」が読み出されることになるという意味で、上記のプロセスとは反対の結果になる。

#### 【0005】

ビットセル100の書き込み動作では、論理「1」を書き込む場合、ビット線150が高電圧状態に駆動され、ビット線160が低電圧状態に駆動される。次いで、ワード線170が、ビットセル100を選択するために高電圧状態に設定され、それにより、アクセストランジスタ152および162がオンになる。ビット線150が高電圧状態にあるので、論理「1」が第1の記憶ノード110に書き込まれ、ビット線160が低電圧状態にあるので、論理「0」が第2の記憶ノード120に書き込まれる。論理「0」の書き込みの場合には、ビット線160が高電圧状態に駆動され、ビット線150が低電圧状態に駆動されるという意味で、反対のプロセスが辿られる。

#### 【0006】

メモリデバイスが小型化するにつれて、その信頼性および性能が低下するという点で、問題が起きている。たとえば、スタティックノイズマージン(SNM)は、ビットセルの状態を意図せず反転させるおそれのある、(第1の記憶ノード110と第2の記憶ノード120との間で測定される)最小ノイズ電圧として定義される。読み出しきャティックノイズマージン(RSNM)は、ビットセルの読み出しきゃ動作の間にビットセルの状態を意図せず反転させるおそれのあるノイズ電圧量として定義される。ビットセルが小型化するにつれて、サイズ制約がビットセルのRSNMを低減させて、ビットセルが、たとえば温度変化またはプロセス変動から生じるノイズの影響をより受けやすくなるおそれがある。

#### 【0007】

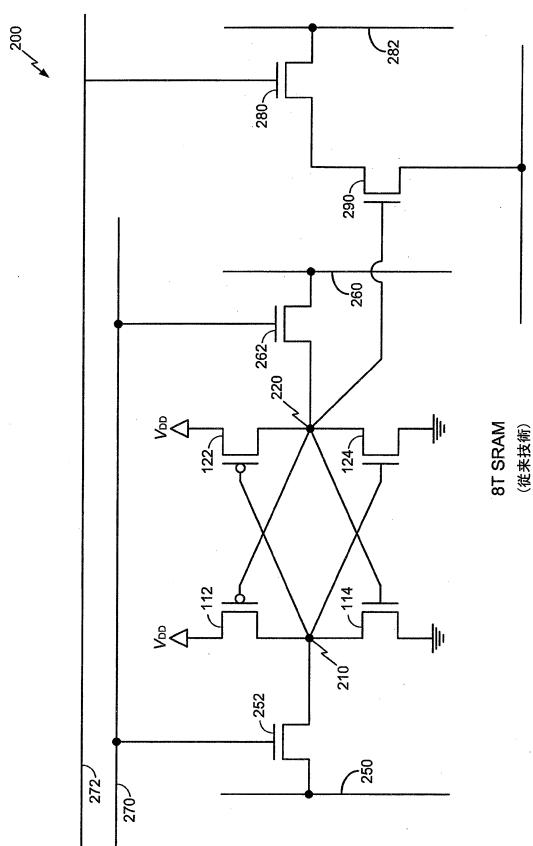

図2は、従来の8トランジスタスタティックランダムアクセスメモリ(8T SRAM)ビットセル200を示す。ビットセル200では、ビットセル100などの従来の6T SRAMビットセルの記憶ノード110および120に類似したデータ記憶ノード210および220が、読み出しひット線282から、デカップリングトランジスタ280および290を使用して切り離されている。読み出しひット線282がデータ記憶ノード210および220から切り離されているので、読み出しきゃ動作がビットセルの状態の意図しない反転を引き起こす可能性は、ずっと低い。したがって、ビットセル200のRSNMは、ビットセル200のアクティブな読み出しきゃ/書き込み動作が進行中でないときのノイズマージンに関係する、保持SNM(HSNM)以上である。しかしながら、ビットセル200は、2つの余分なデカップリングトランジスタ280および290から成るので、ビットセルの面積が増大する。

#### 【0008】

その上、読み出しひット線282に加えて、ビットセル200は、ビットセル200に対する読み出しきゃ動作に対してアクティブにされる読み出しきゃワード線272を含む。さらに、ビットセル200は、書き込み動作用に、別個の書き込みビット線250および260、ならびに別個の書き込みワード線270を備える。書き込みビット線250および260は、読み出しきゃ動作の間にそれらが使用されないことを除いて、ビットセル100のビット線150および160に類似している。同様に、書き込みワード線270も、読み出しきゃ動作の間に書き込みワード線270が使用されないことを除いて、ビットセル100のワード線170に類似している。

#### 【0009】

図2の8T SRAMのさらなる利点は、読み出しきゃ動作と書き込み動作に異なるトランジスタが使用されるということである。読み出しきゃ動作と書き込み動作に異なるトランジスタが使用されるので、それぞれのトランジスタを別々に最適化することができる。たとえば、書き込みアクセストランジスタ252および262を強化することによって、書き込み速度を改善することができる。しかしながら、書き込みアクセストランジスタの強化は、ターゲットビットセルに対する書き込み動作が、ターゲットビットセルだけでなくターゲットビットセルのロウ内の他のあらゆるセルにも影響を及ぼし得る、という問題を生み出すおそれがある。書き込みワード線がメモリアレイのロウ方向に配設されている(すなわち、メモリアレイの所与のロウ内

10

20

30

40

50

の各ビットセルがただ1本の書き込みワード線を共有している)ので、書き込み動作は、ロウ全体に影響を及ぼし得る。「半選択(Half-Selected)」問題として知られるこの問題は、図2に描かれたものなどの書き込み速度が最適化された8T SRAMの信頼性を損なうおそれがある。

#### 【0010】

8T SRAMにおける半選択問題に対して提案された1つの解決策が、書き込み動作に用いられるライトバック(Write-Back)方式である。ライトバック方式では、ロウ内のあらゆるビットセルが最初に読み出されて、記憶されている値が確認される。次いで、記憶されている値が、書き込まれるべきデータに基づいて修正され、この修正された値が、1つまたは複数のターゲットビットセルを含むすべてのビットセルに書き戻される。ライトバック方式は、1つまたは複数のターゲットビットセルを含むロウ内のあらゆるビットセルに対して書き込み動作を実施することによって、ロウをターゲットビットセルと単に共有しているだけのビットセル内でディスタンスを意図せず引き起こす、という問題を回避する。

10

#### 【0011】

しかしながら、ライトバック方式にはそれ自体の欠点がある。具体的には、書き込みサイクルごとにロウ全体に対して読み出し動作と書き込み動作の両方が実施されるので、電力消費が増大する。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0012】

20

したがって、従来の手法の前述の欠点を回避しながらビットセルのノイズマージンおよびデータ安定性を改善することが、必要とされている。

#### 【課題を解決するための手段】

#### 【0013】

例示的態様は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルに関するシステムおよび方法を含む。具体的には、例示的態様は、読み出しディスタンス、および半選択問題の影響の受けやすさが低減され、ノイズマージンが改善された、7T SRAMビットセルに関する。

#### 【0014】

30

たとえば、一例示的態様は、第1のプルアップトランジスタ、第1のプルダウントランジスタ、および第1の記憶ノードを備える、第1のインバータと、第2のプルアップトランジスタ、第2のプルダウントランジスタ、および第2の記憶ノードを備える、第2のインバータであって、第2の記憶ノードは、第1のプルアップトランジスタおよび第1のプルダウントランジスタのゲートに結合されている、第2のインバータとを備える、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルを対象とする。アクセストランジスタが、第1の記憶ノードに結合され、トランスマッシュゲートが、第1の記憶ノードを第2のプルアップトランジスタおよび第2のプルダウントランジスタのゲートに選択的に結合させるように構成される。

#### 【0015】

40

別の例示的態様は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルを動作させる方法であって、読み出し動作の間、第1のインバータの第1の記憶ノードを第2のインバータのゲートから選択的に切り離すことであって、第2のインバータの第2の記憶ノードは、第1のインバータのゲートに結合されている、選択的に切り離すことと、第1の記憶ノードに記憶されたデータ値を、第1の記憶ノードに結合されたアクセストランジスタを通じて読み出すことを含む、方法を対象とする。オプションの態様では、方法はさらに、書き込み動作、スタンバイモード、および保持モードの間、第1のインバータの第1の記憶ノードを第2のインバータのゲートに選択的に結合させることを含んでよい。

#### 【0016】

さらに別の例示的態様は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセルと、読み出し動作の間、第1のインバータの第1の記憶ノードを7T SRAMビット

50

セルの第2のインバータのゲートから選択的に切り離すための手段であって、第2のインバータの第2の記憶ノードは、第1のインバータのゲートに結合されている、選択的に切り離すための手段と、第1の記憶ノードに記憶されたデータ値を読み出すための手段とを備える、システムを対象とする。オプションの態様では、システムはさらに、書き込み動作、スタンバイモード、および保持モードの間、第1のインバータの第1の記憶ノードを第2のインバータのゲートに選択的に結合させるための手段を含む。

【0017】

添付の図面は、本発明の実施形態の説明の助けとなるように提示され、実施形態を限定するためではなく単に示すために提供されている。

【図面の簡単な説明】

10

【0018】

【図1】従来の6T SRAMの概略図である。

【図2】従来の8T SRAMの概略図である。

【図3】一例示的態様によるメモリデバイスおよび制御デバイスの高レベル図である。

【図4】一例示的態様によるメモリデバイスの高レベル状態図である。

【図5】一例示的態様による7トランジスタスタティックランダムアクセスメモリ(7T SRAM)の回路図である。

【図6】一例示的態様による7T SRAMの制御動作の制御表である。

【図7】一例示的態様による、スタンバイモードにあるときの図5の7T SRAMを示す図である。

20

【図8】一例示的態様による、保持モードにあるときの図5の7T SRAMを示す図である。

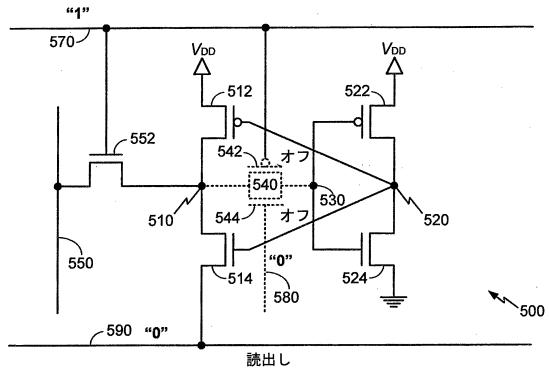

【図9】一例示的態様による、読み出しモードにあるときの図5の7T SRAMを示す図である。

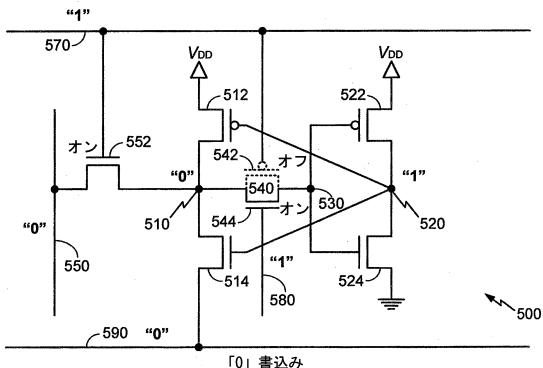

【図10】一例示的態様による、書き込みモード、具体的には「0」を書き込むためのモードにあるときの、図5の7T SRAMを示す図である。

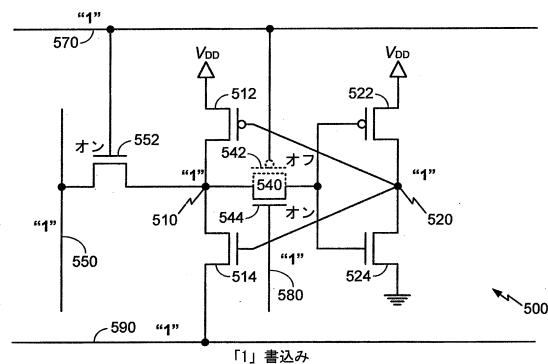

【図11】一例示的態様による、書き込みモード、具体的には「1」を書き込むためのモードにあるときの、図5の7T SRAMを示す図である。

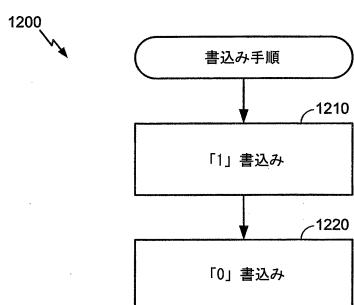

【図12】一例示的態様によるメモリデバイスを制御するための書き込み手順を示す図である。

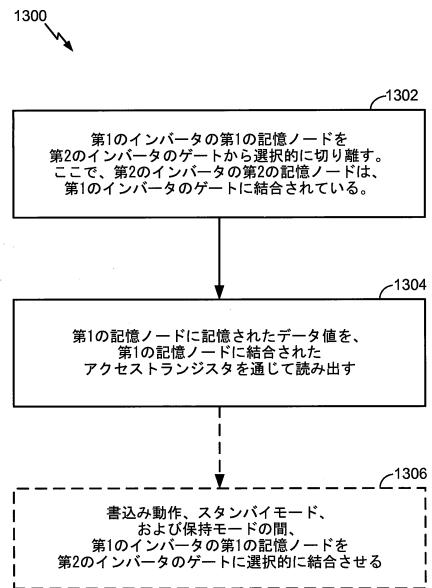

【図13】一例示的7T SRAMビットセルを動作させるための手順を示す図である。

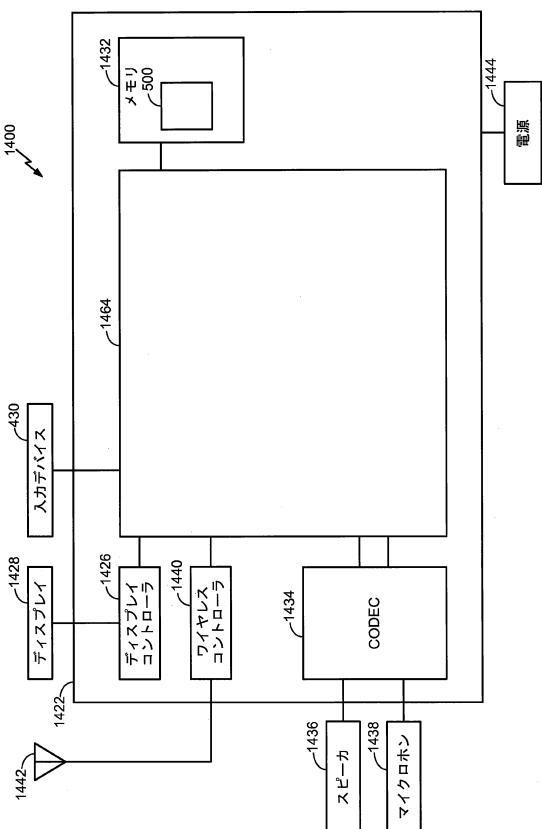

【図14】本開示の態様による一例示的メモリデバイスを含むワイヤレスデバイスの高レベル図である。

30

【発明を実施するための形態】

【0019】

本発明の態様は、本発明の特定の実施形態を対象とする以下の説明および関係する図面において開示される。本発明の範囲から逸脱することなく、代替実施形態が案出されてよい。加えて、本発明のよく知られた要素については、本発明の関連する詳細を曖昧にしないように、詳細に説明されず、または省略される。

【0020】

「例示的」および/または「例」という語は、本明細書において、「例、実例、または例示としての役割を果たすこと」を意味するために使用される。本明細書において「例示的」および/または「例」として説明されるどんな実施形態も、他の実施形態に比べて好ましいまたは有利であると必ずしも解釈すべきではない。同様に、「本発明の実施形態」という用語は、本発明のすべての実施形態が、論じられる特徴、利点、または動作モードを含むことを必要とするものではない。

40

【0021】

本明細書において使用される専門用語は、特定の実施形態について説明するためのものにすぎず、本発明の実施形態を限定するものではない。本明細書で使用される単数形「1つの(a)」、「1つの(an)」、および「その(the)」は、文脈が別段明確に示さない限り、複数形も含むものとする。「備える(comprises)」、「備える(comprising)」、「含む(includes)」、および/または「含む(including)」という用語は、本明細書において使用さ

50

れるとき、述べられた特徴、整数、ステップ、動作、要素、および/または構成要素の存在を明示するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成要素、および/またはそれらの群の存在または追加を妨げないことが、さらに理解されよう。

#### 【0022】

さらに、多くの実施形態について、たとえばコンピューティングデバイスの要素によって実施されるべき一連のアクションの点から説明される。本明細書において説明される様々なアクションは、特定の回路(たとえば特定用途向け集積回路(ASIC))によって、1つもしくは複数のプロセッサによって実行されているプログラム命令によって、または両方の組合せによって、実施できることが認識されよう。加えて、本明細書において説明されるこれらの一連のアクションは、実行時に、関連付けられたプロセッサに本明細書において説明される機能を実施させる、対応するコンピュータ命令セットが中に記憶された、任意の形態のコンピュータ可読記憶媒体内で全体が具現化されるものと見なすことができる。したがって、本発明の様々な態様は、そのすべてが特許請求される主題の範囲に含まれることが企図された、いくつかの異なる形態で具現化されてよい。加えて、本明細書において説明される実施形態の各々について、任意のそのような実施形態の対応する形態が、本明細書において、たとえば、説明したアクションを実施する「ように構成された論理」と説明されることがある。

#### 【0023】

本開示では、信号 $V_{DD}$ および $V_{SS}$ はそれぞれ、正の供給電圧および負の供給電圧/グランドに関係する電圧信号または電圧レベルである。いくつかの態様では、 $V_{DD}$ と表される信号値は、「論理高レベル」または「論理1」を表現するために使用されることがある。同様に、 $V_{SS}$ と表される信号値は、「論理低レベル」、「論理0」、「0」、または「グランド」を表現するために使用されることがある。一般に、信号 $V_{DD}$ および $V_{SS}$ は、いかに言及されていようとも、それぞれ論理値「1」および「0」を表して互いに区別可能な、2つの信号について記述するために使用され得る。

#### 【0024】

先に説明した従来の6T SRAMビットセルに再度言及すると、これらの従来のビットセルは、メモリデバイスのサイズが低下するにつれて、低下する読み出しタイミングノイズマージンを呈する。読み出し動作を書き込み動作から分離することによってこの問題に取り組もうとして8T SRAMを利用すると、2つの余分なトランジスタの使用が必要になる。その上、8T SRAMにおいて半選択問題を解決するためにライトバック方式を用いると、電力消費が増大する結果になる。

#### 【0025】

上記の欠点を克服するために、例示的態様では、例示的7T SRAM構造において、記憶セルへのアクセスにただ1本のビット線を利用し、かつ記憶セルを形成するインバータの交差結合を、トランスマッショングートを介して制御することによって、半選択問題を回避することができる。被選択口内の一例示的7T SRAMセルのすべてのトランスマッショングートを、読み出し動作の間、オフにすることができる。これによりライトバック方式の必要性が回避され、ダイナミック電力消費を低減させることができる。その上、ビット線がただ1本しかないので、全体的なビット線リーキが低下し、それによりスタンバイ電力消費が低減する。

#### 【0026】

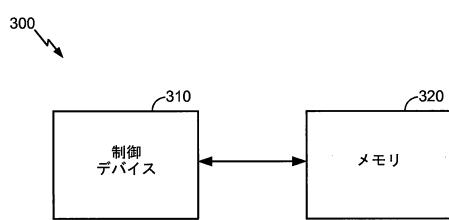

図3は、一例示的態様によるメモリ320を読み出し、かつ/またはメモリ320に書き込むためのシステム300を一般に示す。システム300では、制御デバイス310がメモリ320にメモリ制御信号を送る。メモリ320は、ロウおよびカラムの形で配列されたビットセルのアレイを備える。メモリ制御信号は、読み出しコマンド、書き込みコマンド、ロウ、カラム、および/もしくはある特定のビットセルのうちの1つもしくは複数を特定するデータアドレス、ならびに/またはメモリ320の動作を制御する他の信号を備えてよい。

#### 【0027】

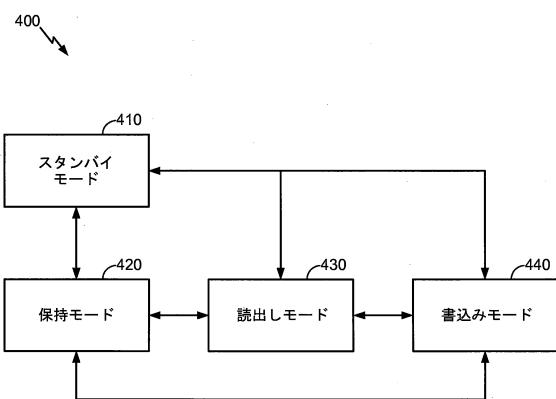

図4は、一実施形態によるメモリ320に属するビットセルの状態図400を一般に示す。ビ

10

20

30

40

50

ットセルの状態は、制御デバイス310によって制御されてよい。スタンバイモード410の間のスタンバイ動作では、メモリ320は、スタンバイまたはスリープモードにあり、ビットセルは、アクティブに使用されていない。場合によっては、スタンバイモード410において、メモリ320全体が、特定の実装形態に基づいて一部または完全にパワーダウンされることがある。したがって、スタンバイモード410の間、スタティックメモリビットセルは、電力消費を最小限に抑えながら、その中に記憶されたデータを維持するように構成される。

#### 【 0 0 2 8 】

保持モード420、読み出しモード430、および書き込みモード440などのアクティブモードでは、メモリ320は、スリープモードにない。メモリ320がアクティブであるとき、メモリ320に属するビットセルの各々は、読み出しモード430(データがビットセルから読み出されている場合)、書き込みモード440(データがビットセルに書き込まれている場合)、または保持モード420のいずれかにある。保持モード420では、ビットセルの状態が維持される。保持モード420は、メモリ320内の他のビットセルにおいて読み出し/書き込み動作が実施されているときに特定のビットセルについて保持モード420に入ってよい例示的な場合に、スリープモード410とは区別され得る。したがって、特定のビットセルについて、ビットセルの状態が保持モードの間維持される。読み出しモード430では、ビットセル内のデータを得るために少なくとも1つの読み出し動作が実施される。書き込みモード440では、少なくとも1つのビットセルにデータ値が書き込まれる。

#### 【 0 0 2 9 】

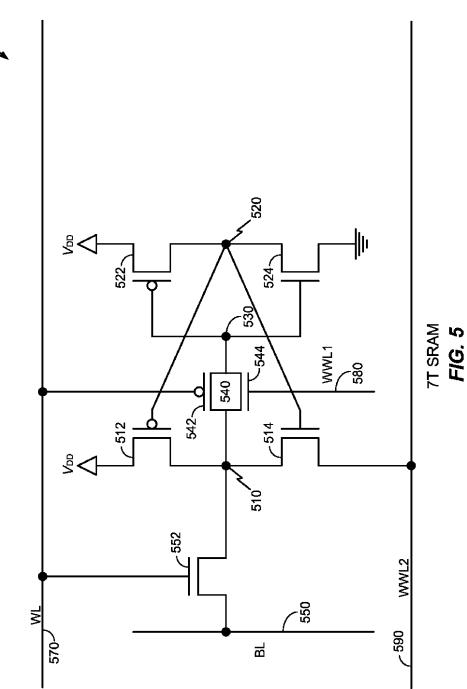

図5は、7トランジスタビットセル500の回路図を一般に示す。ビットセル500は、例示的態様では、7T SRAMビットセルとして構成される。メモリ320は、ビットセル500などのビットセルのアレイを備えてよい。ビットセル500は、第1のプルアップ(PMOS)トランジスタ512と第1のプルダウン(NMOS)トランジスタ514との間にある第1の記憶ノード510を備える第1のインバータと、第2のプルアップ(PMOS)トランジスタ522と第2のプルダウン(NMOS)トランジスタ524との間にある第2の記憶ノード520を備える第2のインバータとを備える。第1の記憶ノード510は、アクティブ(「オン」)または非アクティブ(「オフ」)にすることができるアクセストランジスタ552を介して、ビット線(BL)550に結合される。ビット線550は、アレイのカラム方向に配設されてよい。アクセストランジスタ552は、ゲートがワード線570に結合されたNMOSトランジスタでよい。

#### 【 0 0 3 0 】

ビットセル500では、トランジスタ512および514のゲートは、互いにかつ第2の記憶ノード520に結合される。トランジスタ522および524のゲートは、互いに結合されるが、ビットセル100とは対照的に、トランジスタ522および524のゲートは、第1の記憶ノード510に直接結合されない。代わりに、522および524のゲートは第1の記憶ノード510から、図示のようにそのそれぞれの端子が互いの端子に結合されるように並列に配置されたPMOSトランジスタ542およびNMOSトランジスタ544を備えるトランスマッシュゲート540によって、分離される。PMOSトランジスタ542とNMOSトランジスタ544の両方は、別々にアクティブ(「オン」)または非アクティブ(「オフ」)にすることができる。ゲートノード530が、トランスマッシュゲート540を介して、第1の記憶ノード510に結合される。PMOSトランジスタ542のゲートが、アレイのロウ方向に配設されてよいワード線(WL)570に結合される。NMOSトランジスタ544のゲートが、アレイのカラム方向に配設されてよい第1の書き込みワード線(WWL1)580に結合される。NMOSトランジスタ524は、グランドに結合されるが、NMOSトランジスタ514は、アレイのロウ方向に配設される第2の書き込みワード線(WWL2)590に結合される。

#### 【 0 0 3 1 】

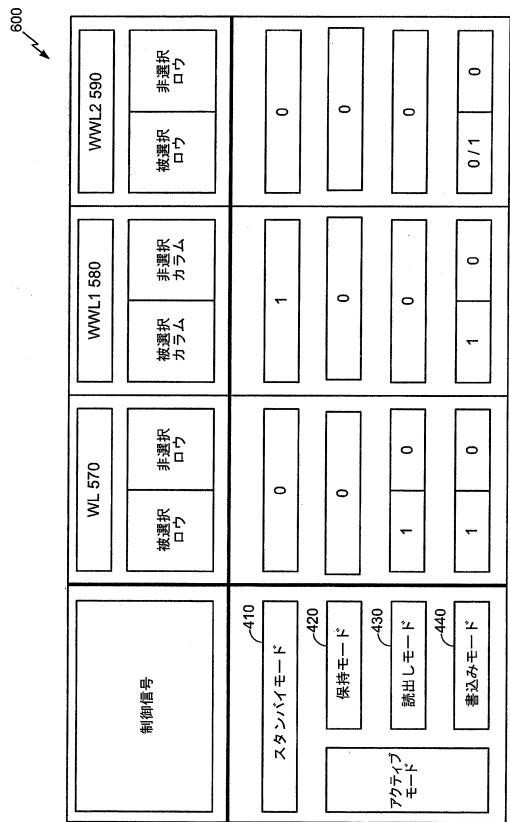

図6は、状態図400に従ってメモリ320内の各ビットセル500を制御するために制御デバイス310によって使用されてよい、制御表600を一般に示す。制御デバイス310は、ビットセル500のビット線550、ワード線570、ならびに第1および第2の書き込みワード線580および590を制御する。ワード線570、第1の書き込みワード線580、および第2の書き込みワード線590は

10

20

30

40

50

、(下記で図7～図11に関してさらに論じるように)制御表600に従って制御されてよい。

【0032】

制御表600は、モード410、420、430、および440、ならびにワード線570、第1の書込みワード線580、および第2の書込みワード線590の、被選択および非選択の口ウおよびカラムについての挙動を示す。メモリ320内の各ビットセル500に印加される信号を制御する制御デバイス310は、メモリ320内の各ビットセル500の挙動を制御する。具体的には、ワード線570、第1の書込みワード線580、および第2の書込みワード線590の各々が、表600に基づいて制御される。モードが選択された後、表600内にリストされている信号がそれぞれ、ワード線570、第1の書込みワード線580、および第2の書込みワード線590に印加される。

10

【0033】

スタンバイモード410では、ワード線570および第2の書込みワード線590が、論理「0」に駆動されるとともに、第1の書込みワード線580が、論理「1」に駆動される。保持モード420では、ワード線570、第1の書込みワード線580、および第2の書込みワード線590の各々が、論理「0」に駆動される。

【0034】

読み出しモード430では、第1の書込みワード線580および第2の書込みワード線590が、論理「0」に駆動される。しかしながら、ワード線570に印加される信号は、口ウごとに異なる。読み出し動作では、メモリ320のある特定のビットセルがターゲットになる。ある特定のビットセルは、それが配設されている口ウおよびカラムによって特定される。ターゲットビットセルが関連付けられている口ウは、「被選択」口ウであり、一方、残りの口ウは「非選択」である。(制御デバイス310は、各ビットセルのビット線550に印加される信号を含む他の信号も制御するが、制御方式のこの様子は、制御表600には示されていない。)図6からわかるように、制御デバイス310は、被選択口ウ(すなわち、読み出し動作のターゲットになっているビットセル500に関連付けられている口ウ)を「1」に駆動し、各非選択口ウを「0」に駆動する。図5からわかるように、ワード線570に印加される信号は、アクセスランジスタ552およびトランスマッショングート540のPMOSトランジスタ542の、それぞれのゲートに供給される。

20

【0035】

書き込みモード440では、ワード線570、第1の書込みワード線580、または第2の書込みワード線590に印加される信号は常に、信号が被選択口ウまたはカラムに印加されているか、それとも非選択口ウまたはカラムに印加されているかという関係になっている。具体的には、書き込み動作のターゲットになっているビットセルの口ウ(すなわち被選択口ウ)に関連付けられているワード線570は、「1」に駆動される。被選択口ウの第2の書込みワード線590は、書き込み動作が論理「0」についてのものであるか、それとも論理「1」についてのものであるかに基づいて、それぞれ、「0」または「1」に駆動される。その上、書き込み動作のターゲットになっているビットセルのカラム(すなわち被選択カラム)に関連付けられている第1の書込みワード線580も、「1」に駆動される。すべての非選択口ウおよびカラムは、「0」に駆動される。

30

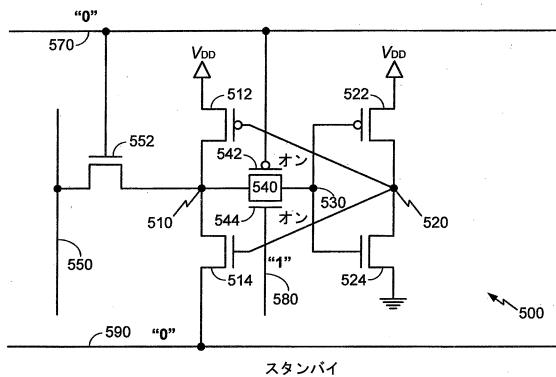

【0036】

図7は、スタンバイモード410にビットセル500を一般に示す。スタンバイモード410では、ワード線570が「0」に設定され、第1の書込みワード線580が「1」に設定され、第2の書込みワード線590が「0」に設定される。その結果、トランジスタ542と544の両方が、「オン」構成にあり、第1の記憶ノード510とゲートノード530との間で電流が自由に流れれる。その結果、スタンバイモード410では、ビットセル500の動作が、6T SRAMビットセル100の動作に類似している。具体的には、インバータが交差結合される。第1の記憶ノード510をトランジスタPMOSトランジスタ522およびNMOSトランジスタ524のゲートに結合させ、第2の記憶ノード520をトランジスタ512および514のゲートに結合させることにより、第1の記憶ノード510および第2の記憶ノード520のところに記憶されたデータが確実に維持されるようになる。6トランジスタメモリビットセル100のスタンバイモードとは異なり、ビット

40

50

線はただ1本しかない。したがって、ビット線リーク量が低減され、スタンバイモード410の間に、それほど電力が消費されない。

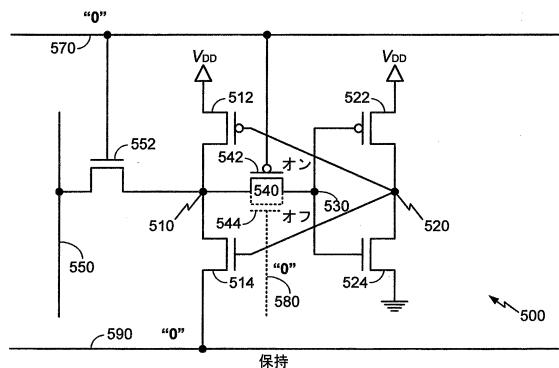

【0037】

図8は、ビットセル500が保持モード420にあるときの図5の回路図を一般に示す。保持モード420では、ワード線570および第2の書き込みワード線590が、ちょうどスタンバイモード410と同様に「0」に設定される。しかしながら、スタンバイモード410とは対照的に、第1の書き込みワード線580も「0」に設定される。その結果、PMOSトランジスタ542は「オン」構成にあるが、NMOSトランジスタ544は「オフ」構成にある。図8の編成では、ビットセル500の状態は維持される。

【0038】

図9は、ビットセル500が読み出しモード430にあるときの図5の回路図を一般に示す。読み出しモード430では、ワード線570が「1」に設定され、第1の書き込みワード線580が「0」に設定される。その結果、両方のトランジスタ542および544が「オフ」構成にあり、それにより、第1の記憶ノード510がゲートノード530から切り離される。第1の記憶ノード510をゲートノード530から切り離すと、読み出しディスターバンスの確率が低減する。特定の例では、ビットセル500が論理「0」を記憶しているとき、それは、第1の記憶ノード510が論理「0」の値を有し、第2の記憶ノード520が論理「1」の値を有していることを意味するが、ビット線550からNMOSトランジスタ514を通じて電圧が放電される読み出し動作が、第1の記憶ノード510のところに電圧上昇を引き起こすことがある。この電圧の上昇の可能性は、アクセストランジスタ552およびNMOSトランジスタ514が、ビット線550のところの高電圧と第2の書き込みワード線590のところの低電圧との間に置かれているときに発生し得る、分圧器効果(voltage divider effect)によって引き起こされる。しかしながら、第1の記憶ノード510のところの電圧上昇は、第1の記憶ノード510が522および524のゲートから切り離されているので、読み出しディスターバンスを引き起こさない。したがって、6トランジスタメモリビットセル100を反転させるおそれのある第1の記憶ノード510のところの電圧の上昇は、第1の記憶ノード510が522および524のゲートから切り離されているので、ビットセル500を反転させない。

【0039】

図10および図11は、ビットセル500が書き込みモード440にあるときの図5の回路図を一般に示す。図10では、ビットセル500の第1の記憶ノード510にデータ値「0」を書き込むことができるよう、ビット線550と第2の書き込みワード線590が両方とも論理「0」に設定される。書き込みモード440では、一般に、ワード線570と第1の書き込みワード線580が両方とも「1」に設定される。その結果、アクセストランジスタ552が「オン」構成にある。その上、PMOSトランジスタ542が「オフ」構成にあり、NMOSトランジスタ544が「オン」構成にある。

【0040】

したがって、図10では、電流は、ゲートノード530(ならびにPMOSトランジスタ522およびNMOSトランジスタ524のゲート)からNMOSトランジスタ544を介して第1の記憶ノード510へと、自由に通過することができ、電流は、第1の記憶ノード510からアクセストランジスタ552を介してビット線550へと、自由に通過することができる。その上、電流は、NMOSトランジスタ514が電流を通過させ始めると、第1の記憶ノード510から第2の書き込みワード線590へと自由に通過する。その結果、第1の記憶ノード510のところに(論理「1」を表す)初期電圧がある場合、前述の書き込み動作により、ビットセル500に論理「0」が書き込まれる。

【0041】

図11は、ビットセル500が書き込みモード440にあるときの図5の回路図を一般に示す。図11では、図10とは対照的に、論理「1」を表すデータをビットセル500の第1の記憶ノード510に書き込むことができるよう、ビット線550と第2の書き込みワード線590が両方とも論理「1」に設定される。書き込みモード440では、一般に、ワード線570と第1の書き込みワード線580が両方とも「1」に設定される。その結果、アクセストランジスタ552が「オン」構成

10

20

30

40

50

にある。その上、PMOSトランジスタ542が「オフ」構成にあり、NMOSトランジスタ544が「オン」構成にある。

#### 【0042】

したがって、図11では、電流は、ビット線550からアクセストランジスタ552を介して第1の記憶ノード510へと、自由に通過することができ、電流は、第1の記憶ノード510からNMOSトランジスタ544を介してゲートノード530(ならびに522および524のゲート)へと、自由に通過することができる。その上、第2の書き込みワード線590が論理「1」に設定されているので、電流は、アクセストランジスタ552を介して第1の記憶ノード510へと自由に通過することができる。その結果、前述の書き込み動作により、ビットセル500に論理「1」が書き込まれる。

10

#### 【0043】

ロウおよびカラムを備えるビットセルのアレイでは、ロウごとに1本のワード線があり、カラムごとに1本のビット線がある。したがって、所与のロウ内のあらゆるビットセルが、ただ1本のワード線を共有し、所与のカラム内のあらゆるビットセルが、ただ1本のビット線を共有する。所与のロウ内の特定のビットセルが、書き込み動作のターゲットになる、または書き込み動作のために選択されるとき、選択されたビットセルに関連付けられているワード線は、「1」に設定される。したがって、ターゲットビットセルとロウを共有する各ビットセルのアクセストランジスタ(たとえば552)が、オンにされる。これが、書き込み動作のために選択されないビットセルを含むロウ内のあらゆるビットセルが、そのそれぞれのビット線上に存在する電荷に晒される、いわゆる「半選択」問題の原因である。したがって、書き込み動作のために選択されないビットセルにおいて、半選択問題が緩和されるべきである。

20

#### 【0044】

したがって、半選択問題を緩和させるための解決策について、図5のビットセル500を参照して説明する。ビットセル500が半選択される(すなわち、選択されたビットセルと同じロウ内にあるが、書き込み動作のために選択されない)シナリオでは、ワード線570が「1」に設定される。その結果、アクセストランジスタ552がオンにされ、半選択されたビットセル500は、ビット線550上の電荷に晒される可能性がある。しかしながら、ワード線570は、PMOSトランジスタ542のゲートにも結合されているので、ワード線570上の論理「1」が、PMOSトランジスタ542をオフにする。その上、図6に示すように、第1の書き込みワード線580が「0」に設定される。したがって、NMOSトランジスタ544もまた、オフにされる。PMOSトランジスタ542とNMOSトランジスタ544の両方がオフにされるので、ゲートノード530のところの電圧は、たとえ第1の記憶ノード510のところの電圧が半選択の結果として変動を被っても、ディスターブされない。したがって、トランジスタPMOSトランジスタ522およびNMOSトランジスタ524を備えるインバータ、ならびにビットセル500全体が、安定状態にとどまり、ビットセル500は、読み出し動作の間、半選択問題から保護される。

30

#### 【0045】

図12は、メモリ320の動作を制御するための書き込み手順1200を一般に示す。書き込み手順1200は、制御デバイス310によって実施されてよい。制御デバイス310は、メモリ320に制御信号を送ることによって、書き込み手順1200を実施する。図12の書き込み手順1200は、アクセストランジスタ552の駆動強度が弱い場合、2段階で実現することができる。アクセストランジスタ552が弱いとき、選択されたビットセルに(たとえば図11に従って)「1」を書き込むことは、それにより、アクセストランジスタ552がビット線550から第1の記憶ノード510上に高電圧を通過させることが必要になるので、困難となり得る。一方、第1の記憶ノード510に(たとえば図10に従って)「0」を書き込むために、第1の記憶ノード510をドレインするほうが容易である。したがって、選択されたビットセルへの書き込みは、2段階で達成され得る。

40

#### 【0046】

第1の段階1210では、被選択ロウ内のあらゆるビットセルに、論理「1」が書き込まれる。この段階の間、所与のロウのワード線570および第2の書き込みワード線590は、(たとえば

50

図11に示すように)「1」に駆動される。これにより、アクセストランジスタ552が、オンにされ、ピット線550から第1の記憶ノード510上に信号「1」を駆動して、第1の記憶ノード510を論理「1」に駆動することが可能になる。さらに、第2の書き込みワード線590が「1」に駆動されるので、NMOSトランジスタ514を通じて第1の記憶ノード510に対して追加のブーストが行われる。たとえば、4つのピットセルから成るロウにデータパターン「1010」を書き込むには(たとえばピットセル[3]に「1」が書き込まれ、ピットセル[2]に「0」が書き込まれ、ピットセル[1]に「1」が書き込まれ、ピットセル[0]に「0」が書き込まれる、たとえばピットセル[3:0])、第1の段階1210は、ロウ内の4つのピットセルの各々に「1」を書き込む、すなわちピットセル[3:0]にパターン「1111」を書き込むことを含む。

【0047】

10

第2の段階1220では、4つのピットセルから成るロウに、所望のデータパターン「1010」が書き込まれる。具体的には、図10に示すように、所与のロウのワード線570が「1」に駆動され、一方、所与のロウの第2の書き込みワード線590が「0」に駆動される。値「0」が書き込まれることになっているピットセル[2]および[0]については、それらの対応するピット線550が、値「0」を伝達する。したがって、ピットセル[2]および[0]に「0」を書き込むために、それらの対応するアクセストランジスタ552が、オンにされ、それらの対応するピット線550からそれらの対応する第1の記憶ノード510上に「0」を駆動して、それぞれの第1の記憶ノード510のところに論理「0」を形成する。念を押しておくが、(「0」に駆動される)第2の書き込みワード線590は、第1の記憶ノード510を、ピットセル[2]および[0]のNMOSトランジスタ514を通じて論理「0」にドレインするために提供されている。値「1」が書き込まれることになっている残りのピットセル[3]および[1]については、それらがピットセル[2]および[0]と同じロウ内にあるので、ワード線570が「1」であり、第2の書き込みワード線590が「0」であるという、同じ組合せが保たれる。しかしながら、第2の段階1220では、ピットセル[3]および[1]には第1の段階1210からそれらにすでに「1」が記憶されているので、「1」の書き込みが困難ではない。より詳細には、ピットセル[3]および[1]については、それらの対応するピット線550が、値「1」を伝達し、それらのアクセストランジスタ552が、オンにされて、ピット線550から対応する第1の記憶ノード510に「1」を駆動する。第2のワード線590からの特別なブーストは、この場合の「1」の書き込みには必要にならない。したがって、複数の7T SRAMピットセルから成るロウに論理値「1」と論理値「0」との組合せを備えるデータパターンを書き込むために、第1の段階において、ロウ内の複数の7T SRAMピットセルに論理値「1」を書き込み、第2の段階において、ロウ内の複数の7T SRAMピットセルに、論理値「1」と論理値「0」との組合せを書き込む、2段階書き込み動作を使用することができる。

【0048】

20

したがって、例示的7T SRAMピットセルは、動作モードに基づいて第1の記憶ノード510およびゲートノード530を選択的に結合させ、または切り離すことのできる、トランスマッシュョンゲート540の使用によって、読み出しディスタンスおよび半選択問題を緩和させるように構成され、またノイズマージンを改善するようにも構成される。第2のワード線590を通じてブーストを行うことによって、7T SRAMピットセルの書き込み性も改善される。

30

【0049】

40

したがって、態様は、本明細書において開示したプロセス、機能、および/またはアルゴリズムを実施するための様々な方法を含むことが理解されよう。たとえば、図13に示すように、一態様は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ピットセル(たとえば500)を動作させる方法1300であって、読み出し動作(たとえば図9)の間、(たとえばトランスマッシュョンゲート540のNMOSトランジスタ544およびPMOSトランジスタ542をディスエーブルすることによって)、(たとえばトランジスタ512、514から形成される)第1のインバータの第1の記憶ノード(たとえば510)を、(たとえばトランジスタ522、524から形成される)第2のインバータの(たとえばゲートノード530のところの)ゲートから選択的に切り離すことであって、第2のインバータの第2の記憶ノード(たとえば520)は、第1の

50

インバータのゲートに結合されている、選択的に切り離すこと-ブロック1302と、第1の記憶ノードに記憶されたデータ値を、第1の記憶ノードに結合されたアクセストランジスタ(たとえば552)を通じて読み出すこと-ブロック1304とを含む、方法を含むことができる。加えて、点線で示されるオプションの態様では、方法1300は、書き込み動作の間(たとえばN MOSトランジスタ544をイネーブルすることによって、図10～図11)、スタンバイモードの間(たとえばNMOSトランジスタ544およびPMOSトランジスタ542をイネーブルすることによって、図7)、ならびに保持モードの間(たとえばPMOSトランジスタ542をイネーブルすることによって、図8)、第1のインバータの第1の記憶ノードを第2のインバータのゲートに選択的に結合させること-ブロック1306に関係するプロセスを包含してよい。

## 【0050】

10

同様に、一例示的態様は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ビットセル(たとえば500)を備えるシステムも含むことができる。システムは、(たとえばトランジスタ512、514から形成される)第1のインバータの第1の記憶ノード(たとえば510)を、(たとえばトランジスタ522、524から形成される)第2のインバータの(たとえばゲートノード530のところの)ゲートから選択的に切り離すための手段(たとえばトランスマッシュョンゲート540の非アクティブにされたNMOSトランジスタ544およびPMOSトランジスタ542)であって、第2のインバータの第2の記憶ノード(たとえば520)は、第1のインバータのゲートに結合されている、選択的に切り離すための手段と、第1の記憶ノードに記憶されたデータ値を読み出すための手段(たとえばアクセストランジスタ552)とを含むことができる。その上、システムはさらに、書き込み動作の間、第1のインバータの第1の記憶ノードを第2のインバータのゲートに選択的に結合させるための手段(たとえばアクティブにされたNMOSトランジスタ544、図10～図11)、スタンバイモードの間、第1のインバータの第1の記憶ノードを第2のインバータのゲートに選択的に結合させるための手段(たとえばアクティブにされたNMOSトランジスタ544およびPMOSトランジスタ542、図7)、ならびに保持モードの間、第1のインバータの第1の記憶ノードを第2のインバータのゲートに選択的に結合させるための手段(たとえばアクティブにされたPMOSトランジスタ542、図8)を備えてよい。

20

## 【0051】

図14を参照すると、例示的態様に従って構成されたマルチコアプロセッサを含むワイヤレスデバイスの特定の例示的な態様のブロック図が描かれており、全体的に1400と称される。デバイス1400は、図1の処理システム100を含んでよいプロセッサ1464を含む。図14は、プロセッサ1464およびディスプレイ1428に結合されている、ディスプレイコントローラ1426も示す。コーダ/デコーダ(CODEC)1434(たとえばオーディオおよび/または音声CODEC)を、プロセッサ1464に結合させることができる。(モデムを含んでよい)ワイヤレスコントローラ1440などの他の構成要素も、示されている。スピーカ1436およびマイクロホン1438を、CODEC1434に結合させることができる。図14は、ワイヤレスコントローラ1440をワイヤレスアンテナ1442に結合させることも示す。特定の一態様では、プロセッサ1464、ディスプレイコントローラ1426、メモリ1432、CODEC1434、およびワイヤレスコントローラ1440が、システムインパッケージまたはシステムオンチップデバイス1422内に含まれる。メモリ1432は、図5のSRAMビットセル500を備えてよい。それに加えてまたはその代わりに、プロセッサ1464は、SRAMビットセル500を備えるキャッシュやレジスタファイル(図示せず)などの、別のメモリ構造を含んでもよい。

30

## 【0052】

40

特定の一態様では、入力デバイス1430および電源1444が、システムオンチップデバイス1422に結合される。その上、特定の一態様では、図14に示すように、ディスプレイ1428、入力デバイス1430、スピーカ1436、マイクロホン1438、ワイヤレスアンテナ1442、および電源1444が、システムオンチップデバイス1422の外部にある。しかしながら、ディスプレイ1428、入力デバイス1430、スピーカ1436、マイクロホン1438、ワイヤレスアンテナ1442、および電源1444の各々は、インターフェースやコントローラなどの、システムオンチップデバイス1422の構成要素に結合させることができる。

## 【0053】

50

図14は、ワイヤレス通信デバイスを描いているが、プロセッサ1464およびメモリ1432は、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、パーソナルデジタルアシスタント(PDA)、モバイル電話、固定位置データユニット、またはコンピュータなどのデバイスに組み込まれてもよいことに留意されたい。場合によっては、プロセッサ1464、メモリ1432が、ワイヤレスデバイス1400の、ピットセル500などの例示的ピットセルを含む1つまたは複数の構成要素とともに、少なくとも1つの半導体ダイに組み込まれてもよい。

#### 【 0 0 5 4 】

情報および信号は、多様な異なる技術および技法のいずれかを使用して表されてよいことを、当業者なら理解するであろう。たとえば、上記の説明全体を通じて参照されることのあるデータ、命令、コマンド、情報、信号、ピット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表されてよい。

10

#### 【 0 0 5 5 】

さらに、本明細書において開示した実施形態に関連して説明した、様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実装されてよいことを、当業者なら理解するであろう。ハードウェアとソフトウェアのこの交換可能性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについては上記で、それらの機能の点から一般に説明してきた。そのような機能が、ハードウェアとして実装されるか、それともソフトウェアとして実装されるかは、特定の適用例、およびシステム全体に課せられる設計制約によって決まる。当業者なら、説明した機能を、特定の適用例ごとに様々な実装し得るが、そのような実装形態の決定は、本発明の範囲からの逸脱を引き起こすものと解釈すべきではない。

20

#### 【 0 0 5 6 】

本明細書において開示した実施形態に関連して説明した方法、シーケンス、および/またはアルゴリズムは、直接ハードウェアの形で、プロセッサによって実行されるソフトウェアモジュールの形で、またはその2つの組合せの形で、具現化されてよい。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られる任意の他の形態の記憶媒体内に存在してよい。例示的記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替手段として、記憶媒体は、プロセッサと一体を成してもよい。

30

#### 【 0 0 5 7 】

したがって、本発明の一実施形態は、7トランジスタスタティックランダムアクセスメモリ(7T SRAM)ピットセルを動作させるための方法を具現化するコンピュータ可読媒体を含むことができる。したがって、本発明は示した例に限定されず、本明細書において説明した機能を実施するための任意の手段が、本発明の実施形態に含まれる。

#### 【 0 0 5 8 】

前述の開示は、本発明の例示的な実施形態を示すが、添付の特許請求の範囲によって定められる本発明の範囲から逸脱することなく、本明細書において様々な変更および修正を行えることに留意されたい。本明細書において説明した本発明の実施形態による方法クレームに記載の機能、ステップ、および/またはアクションは、任意の特定の順序で実施されなくてもよい。さらに、本発明の要素は、単数形で説明または特許請求されていることがあるが、単数形に限定することが明示的に述べられていない限り、複数形が企図される。

40

#### 【 符号の説明 】

#### 【 0 0 5 9 】

300 システム

310 制御デバイス

50

|      |                             |    |

|------|-----------------------------|----|

| 320  | メモリ                         |    |

| 400  | 状態図                         |    |

| 410  | スタンバイモード、スリープモード            |    |

| 420  | 保持モード                       |    |

| 430  | 読み出しモード                     |    |

| 440  | 書き込みモード                     |    |

| 500  | 7トランジスタビットセル、SRAMビットセル      |    |

| 510  | 第1の記憶ノード                    |    |

| 512  | 第1のプルアップ(PMOS)トランジスタ        | 10 |

| 514  | 第1のプルダウン(NMOS)トランジスタ        |    |

| 520  | 第2の記憶ノード                    |    |

| 522  | 第2のプルアップ(PMOS)トランジスタ        |    |

| 524  | 第2のプルダウン(NMOS)トランジスタ        |    |

| 530  | ゲートノード                      |    |

| 540  | トランスマッシュショングート              |    |

| 542  | PMOSトランジスタ                  |    |

| 544  | NMOSトランジスタ                  |    |

| 550  | ビット線(BL)                    |    |

| 552  | アクセストランジスタ                  |    |

| 570  | ワード線(WL)                    | 20 |

| 580  | 第1の書き込みワード線(WWL1)           |    |

| 590  | 第2の書き込みワード線(WWL2)           |    |

| 600  | 制御表                         |    |

| 1400 | ブロック図、ワイヤレスデバイス             |    |

| 1422 | システムインパッケージまたはシステムオンチップデバイス |    |

| 1426 | ディスプレイコントローラ                |    |

| 1428 | ディスプレイ                      |    |

| 1432 | メモリ                         |    |

| 1434 | コーダ/デコーダ(CODEC)             |    |

| 1436 | スピーカ                        | 30 |

| 1438 | マイクロホン                      |    |

| 1440 | ワイヤレスコントローラ                 |    |

| 1442 | ワイヤレスアンテナ                   |    |

| 1444 | 電源                          |    |

| 1464 | プロセッサ                       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図 7】

【図 8】

【図 10】

【図 9】

【図 11】

【図12】

【図13】

【図14】

---

フロントページの続き

- (72)発明者 ソン - ウク・ジュン

大韓民国・ソウル・120-749・ソデムン - グ・ヨンセイ - ロ・50・エンジニアリング・ビルディング - 2・725

- (72)発明者 ヨンフェイ・ヤン

大韓民国・ソウル・120-749・ソデムン - グ・ヨンセイ - ロ・50・エンジニアリング・ビルディング - 2・725

- (72)発明者 スタンリー・スンチュル・ソン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

- (72)発明者 ジョンゼ・ワン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

- (72)発明者 チョー・フェイ・イエブ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

審査官 堀田 和義

- (56)参考文献 特表2008-545222 (JP, A)

米国特許出願公開第2009/0285011 (US, A1)

米国特許出願公開第2012/0224414 (US, A1)

特開平11-96767 (JP, A)

米国特許第6853578 (US, B1)

国際公開第2009/078220 (WO, A1)

国際公開第2011/013298 (WO, A1)

- (58)調査した分野(Int.Cl., DB名)

G 11 C 11/412