(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6366687号

(P6366687)

(45) 発行日 平成30年8月1日(2018.8.1)

(24) 登録日 平成30年7月13日(2018.7.13)

|               |              |

|---------------|--------------|

| (51) Int.Cl.  | F 1          |

| HO 1 L 21/337 | (2006.01)    |

| HO 1 L 21/338 | (2006.01)    |

| HO 1 L 29/808 | (2006.01)    |

| HO 1 L 29/812 | (2006.01)    |

| HO 1 L 29/778 | (2006.01)    |

|               | HO 1 L 29/80 |

請求項の数 21 (全 14 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-512060 (P2016-512060)  |

| (86) (22) 出願日 | 平成26年5月2日(2014.5.2)           |

| (65) 公表番号     | 特表2016-521008 (P2016-521008A) |

| (43) 公表日      | 平成28年7月14日(2016.7.14)         |

| (86) 國際出願番号   | PCT/US2014/036499             |

| (87) 國際公開番号   | W02014/179651                 |

| (87) 國際公開日    | 平成26年11月6日(2014.11.6)         |

| 審査請求日         | 平成29年4月27日(2017.4.27)         |

| (31) 優先権主張番号  | 61/819, 252                   |

| (32) 優先日      | 平成25年5月3日(2013.5.3)           |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 14/267, 185                   |

| (32) 優先日      | 平成26年5月1日(2014.5.1)           |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 397050741<br>マイクロチップ テクノロジー インコーポレイテッド<br>MICROCHIP TECHNOLOGY INCORPORATED<br>アメリカ合衆国 85224-6199<br>アリゾナ チャンドラー ウエスト チャンドラー ブルヴァード 2355 |

| (74) 代理人  | 100078282<br>弁理士 山本 秀策                                                                                                                   |

| (74) 代理人  | 100113413<br>弁理士 森下 夏樹                                                                                                                   |

最終頁に続く

(54) 【発明の名称】コンパクトな静電放電(E S D)保護構造

## (57) 【特許請求の範囲】

## 【請求項 1】

静電放電(E S D)保護素子であって、

ドレイン、少なくとも2つのゲート、およびソースを有する第1の電界効果トランジスタであって、前記第1の電界効果トランジスタの前記ドレインは、E S Dイベントから保護されるように回路のノードに結合される、第1の電界効果トランジスタと、

前記第1の電界効果トランジスタの前記ソースとコモンノードとの間に結合される少なくとも1つの第1のダイオードと、

前記少なくとも2つのゲートのうちの第1のゲートと前記コモンノードとの間に直列に結合される第1および第2の抵抗器であって、前記第1の抵抗器と前記第2の抵抗器との間の第1のノードは、前記少なくとも2つのゲートのうちの第2のゲートと結合される、第1および第2の抵抗器と

を備え、

前記第2の抵抗器は、前記少なくとも2つのゲートのうちの前記第2のゲートと前記コモンノードとの間に結合され、

前記回路の前記ノードに蓄積された負の静電電荷は、前記第2の抵抗器を通して前記コモンノードに排出される、E S D保護素子。

## 【請求項 2】

前記コモンノードは、電源コモンである、請求項1に記載のE S D保護素子。

## 【請求項 3】

10

20

ドレイン、少なくとも 2 つのゲート、およびソースを有する第 2 の電界効果トランジスタであって、前記第 2 の電界効果トランジスタの前記ドレインは、電源コモンに結合される、第 2 の電界効果トランジスタと、

前記少なくとも 1 つの第 1 のダイオードのカソードに結合されるカソードを有する少なくとも 1 つの第 2 のダイオードと、

前記第 2 の電界効果トランジスタの第 1 のゲートと前記コモンノードとの間に直列に結合される第 3 および第 4 の抵抗器であって、前記第 3 の抵抗器と前記第 4 の抵抗器との間の第 2 のノードは、前記第 2 の電界効果トランジスタの第 2 の 1 つのゲートと結合される、第 3 および第 4 の抵抗器と

をさらに備える、請求項 1 に記載の ESD 保護素子。

10

#### 【請求項 4】

前記第 1 の電界効果トランジスタの前記少なくとも 2 つのゲートのうちの一方は、トリガゲートであり、前記少なくとも 2 つのゲートのうちの別の一方は、放電ゲートである、請求項 1 に記載の ESD 保護素子。

#### 【請求項 5】

前記第 1 および第 2 の電界効果トランジスタの前記少なくとも 2 つのゲートのうちの一方は、トリガゲートであり、前記少なくとも 2 つのゲートのうちの別の一方は、放電ゲートである、請求項 3 に記載の ESD 保護素子。

#### 【請求項 6】

前記第 1 の電界効果トランジスタは、空乏モード電界効果トランジスタである、請求項 1 に記載の ESD 保護素子。

20

#### 【請求項 7】

前記第 1 および第 2 の電界効果トランジスタは、空乏モード電界効果トランジスタである、請求項 3 に記載の ESD 保護素子。

#### 【請求項 8】

前記少なくとも 1 つの第 1 のダイオードは、前記第 1 の電界効果トランジスタの前記ソースと前記コモンノードとの間に直列に接続される 2 つのダイオードである、請求項 1 に記載の ESD 保護素子。

#### 【請求項 9】

前記少なくとも 1 つの第 1 および第 2 のダイオードはそれぞれ、前記第 1 または第 2 の電界効果トランジスタの前記ソースと前記コモンノードとの間に直列に接続される 2 つのダイオードである、請求項 3 に記載の ESD 保護素子。

30

#### 【請求項 10】

前記電源コモンは、電気接地に結合される、請求項 2 に記載の ESD 保護素子。

#### 【請求項 11】

前記空乏モード電界効果トランジスタは、高電子移動度トランジスタ (HEMT) である、請求項 6 または 7 に記載の ESD 保護素子。

#### 【請求項 12】

前記 HEMT は、シユードモルフィック型 HEMT (pHEMT) である、請求項 11 に記載の ESD 保護素子。

40

#### 【請求項 13】

前記 HEMT は、メタモルフィック型 HEMT (mHEMT) である、請求項 11 に記載の ESD 保護素子。

#### 【請求項 14】

前記第 1 の電界効果トランジスタ、前記少なくとも 1 つの第 1 のダイオード、ならびに前記第 1 および第 2 の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合される、請求項 1 に記載の ESD 保護素子。

#### 【請求項 15】

前記第 1 および第 2 の電界効果トランジスタ、前記第 1 および第 2 のダイオード、ならびに前記第 1 、第 2 、第 3 および第 4 の抵抗器は、集積回路ダイ上に加工され、前記集積

50

回路ダイの外部接続に結合される前記回路のノードに結合される、請求項 3 に記載の ESD 保護素子。

【請求項 16】

前記第1の電界効果トランジスタ、前記少なくとも1つの第1のダイオード、ならびに、前記第1および第2の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合され、前記集積回路ダイの前記外部接続の機能は、アナログ入力、デジタル入力、アナログ出力、デジタル出力、アナログ入力／出力、デジタル入力／出力、電力接続、バイアス入力、および外部補償キャパシタから成る群から選択される、請求項2に記載のESD保護素子。

【請求項 17】

10

前記第1および第2の電界効果トランジスタ、前記少なくとも1つの第1および第2のダイオード、ならびに、前記第1、第2、第3および第4の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合され、前記集積回路ダイの前記外部接続の機能は、アナログ入力、デジタル入力、アナログ出力、デジタル出力、アナログ入力／出力、デジタル入力／出力、電力接続、バイアス入力、および外部補償キャパシタから成る群から選択される、請求項3に記載のESD保護素子。

【請求項 18】

前記第1の電界効果トランジスタ、前記少なくとも1つの第1のダイオード、ならびに、前記第1および第2の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合され、前記集積回路ダイの前記外部接続の機能は、無線周波数信号入力を備える、請求項2に記載のESD保護素子。

20

【請求項 19】

前記第1および第2の電界効果トランジスタ、前記少なくとも1つの第1および第2のダイオード、ならびに、前記第1、第2、第3および第4の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合され、前記集積回路ダイの前記外部接続の機能は、無線周波数信号入力を備える、請求項3に記載のESD保護素子。

【請求項 20】

前記第1の電界効果トランジスタ、前記少なくとも1つの第1のダイオード、ならびに、前記第1および第2の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合され、前記集積回路ダイの前記外部接続の機能は、無線周波数信号出力を備える、請求項2に記載のESD保護素子。

30

【請求項 21】

前記第1および第2の電界効果トランジスタ、前記少なくとも1つの第1および第2のダイオード、ならびに、前記第1、第2、第3および第4の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される前記回路のノードに結合され、前記集積回路ダイの前記外部接続の機能は、無線周波数信号出力を備える、請求項3に記載のESD保護素子。

【発明の詳細な説明】

【技術分野】

40

【0001】

(関連特許出願)

本願は、Pei-Ming Daniel Chow, Yon-Lin Kok, Jing Zhu、およびSteven Schellによる、“Compact ESD Protection Structure,”と題され、2012年5月3日に出願された、共有に係る米国仮特許出願第61/819,252号に対する優先権を主張するものであり、該米国仮特許出願は、あらゆる目的のために、参照により本明細書中に援用される。

【0002】

本開示は、半導体保護構造に関し、特に、静電放電(ESD)保護構造に関する。

50

**【背景技術】****【0003】**

ショットキーゲート空乏モード電界効果素子は、その纖細な金属ゲート構造（0.5 μmまたはそれより短い金属ゲート長）に起因して、ESD損傷に敏感である。CMOSシリコンまたはバイポーラトランジスタプロセスと異なり、コンパクトなESD保護ダイオードを形成するために、高電子移動度トランジスタ（HEMT）プロセスにおいて利用可能なロバストなP-N接合ダイオードは存在しない。ヘテロ構造FET（HFET）または変調ドープFET（MODFET）としても知られる、HEMTは、ドープ領域（概して、MOSFETの場合）の代わりに、チャネルとして異なるバンドギャップ（すなわち、ヘテロ接合）を伴う2つの材料間の接合を組み込む、電界効果トランジスタである。いくつかのバージョンのHEMTが存在し、例えば、シュードモルフィック型HEMT（pHEMT）、メタモルフィック型HEMT（mHEMT）、誘導HEMT等が挙げられる。pHEMT素子のゲートとともに形成される、いくつかの大型ショットキーダイオードは、アクティブHEMT回路を適正に保護するために直列にカスケード化される必要がある。これらの複数のショットキーダイオードは、高価なGaN集積回路ダイ内において広い面積を消費する。

**【0004】**

ホットキャリアダイオードとしても知られる、ショットキーダイオードは、低順方向電圧降下および超高速切替作用を有する、半導体ダイオードである。電流がダイオードを通して流動するとき、ダイオード端子を横断してわずかな電圧降下が存在する。通常ダイオードは、0.6～1.7ボルトの電圧降下を有するであろう一方、ショットキーダイオード電圧降下は、通常、0.15～0.45ボルトである。このようなより低い電圧降下は、より優れたシステム効率およびより高い切替スピードを提供する。ショットキーダイオードでは、半導体-金属接合は、半導体と金属との間に形成され、したがって、ショットキー障壁を生成する。N型半導体は、ショットキーダイオードのカソードとして作用し、金属側は、アノードとして作用する。本ショットキー障壁は、低順方向電圧降下および超高速切替の両方をもたらす。ESD保護は、いくつかの大型ショットキーダイオードをカスケード化することによって提供することができます。ショットキーダイオードの低ターンオン電圧に起因して、いくつかのスタッカされたダイオードが、動作電圧に対処するために要求され、広い面積が、電流に対処するために要求される。したがって、ショットキーダイオード構成の使用は、広いダイ面積を要求する。

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

したがって、ショットキーダイオードの使用を要求しない、HEMTおよび他の半導体素子と互換性がある、効率的かつコンパクトなESD保護構造の必要性が存在する。

**【課題を解決するための手段】****【0006】**

ある実施形態によると、静電放電（ESD）保護素子は、ドレイン、少なくとも2つのゲート、およびソースを有する、電界効果トランジスタ（FET）であって、そのドレインは、ESDイベントから保護されるように、回路のノードに結合され得る、電界効果トランジスタと、FETのソースと電源コモンとの間に結合される、少なくとも1つのダイオードと、FETの少なくとも2つのゲート間に結合される、第1の抵抗器と、少なくとも2つのゲートのうちの一方および電源コモンに結合される、第2の抵抗器とを備えてよい。

**【0007】**

さらなる実施形態によると、少なくとも2つのゲートのうちの一方は、トリガゲートであってもよく、少なくとも2つのゲートのうちの別の一方は、放電ゲートであってもよい。さらなる実施形態によると、FETは、空乏モードFETであってもよい。さらなる実施形態によると、少なくとも1つのダイオードは、FETのソースと電源コモンとの間に

直列に接続される 2 つのダイオードであってもよい。さらなる実施形態によると、電源コモンは、電気接地に結合されてもよい。さらなる実施形態によると、空乏モード F E T は、高電子移動度トランジスタ ( H E M T ) であってもよい。さらなる実施形態によると、H E M T は、シードモルフィック型 H E M T ( p H E M T ) であってもよい。さらなる実施形態によると、H E M T は、メタモルフィック型 H E M T ( m H E M T ) であってもよい。さらなる実施形態によると、H E M T は、誘導 H E M T であってもよい。

#### 【 0 0 0 8 】

さらなる実施形態によると、F E T 、少なくとも 1 つのダイオード、ならびに第 1 および第 2 の抵抗器は、集積回路ダイ上に加工され、集積回路ダイの外部接続に結合され得る、回路ノードに結合されてもよい。さらなる実施形態によると、集積回路ダイの外部接続の機能は、アナログ入力、デジタル入力、アナログ出力、デジタル出力、アナログ入力 / 出力、デジタル入力 / 出力、電力接続、バイアス入力、および外部補償キャパシタから成る群から選択されてもよい。10

#### 【 0 0 0 9 】

別の実施形態によると、静電放電 ( E S D ) 保護素子は、ドレイン、少なくとも 2 つのゲート、およびソースを有する、第 1 の電界効果トランジスタ ( F E T ) であって、そのドレインは、E S D イベントから保護されるように回路のノードに結合され得る、第 1 の電界効果トランジスタと、第 1 の F E T のソースに結合されるアノードを有する、少なくとも 1 つの第 1 のダイオードと、第 1 の F E T の少なくとも 2 つのゲート間に結合される、第 1 の抵抗器と、少なくとも 2 つのゲートのうちの一方および少なくとも 1 つの第 1 のダイオードのカソードに結合される、第 2 の抵抗器と、ドレイン、少なくとも 2 つのゲート、およびソースを有する、第 2 の電界効果トランジスタ ( F E T ) であって、そのドレインは、電源コモンに結合され得る、第 2 の電界効果トランジスタと、少なくとも 1 つの第 1 のダイオードのカソードに結合されるカソードを有する、少なくとも 1 つの第 2 のダイオードと、第 2 の F E T の少なくとも 2 つのゲート間に結合される、第 3 の抵抗器と、第 2 の F E T の少なくとも 2 つのゲートのうちの一方および少なくとも 1 つの第 2 のダイオードのカソードに結合される、第 4 の抵抗器とを備えてよい。20

#### 【 0 0 1 0 】

さらなる実施形態によると、第 1 および第 2 の F E T の少なくとも 2 つのゲートのうちの一方は、トリガゲートであってもよく、第 1 および第 2 の F E T の少なくとも 2 つのゲートのうちの別の一方は、放電ゲートであってもよい。さらなる実施形態によると、第 1 および第 2 の F E T は、空乏モード F E T であってもよい。さらなる実施形態によると、少なくとも 1 つの第 1 および第 2 のダイオードは、それぞれ、第 1 および第 2 の F E T のソース間に直列に接続される、2 つのダイオードであってもよい。さらなる実施形態によると、電源コモンは、電気接地に結合されてもよい。さらなる実施形態によると、第 1 および第 2 の空乏モード F E T は、高電子移動度トランジスタ ( H E M T ) であってもよい。さらなる実施形態によると、H E M T は、シードモルフィック型 H E M T ( p H E M T ) 、メタモルフィック型 H E M T ( m H E M T ) および誘導 H E M T から成る群から選択されてもよい。30

#### 【 0 0 1 1 】

さらなる実施形態によると、第 1 および第 2 の F E T 、少なくとも 1 つの第 1 および第 2 のダイオード、ならびに第 1 、第 2 、第 3 、および第 4 の抵抗器は、集積回路ダイ上に加工され、集積回路ダイの外部接続に結合され得る、回路ノードに結合されてもよい。さらなる実施形態によると、集積回路ダイの外部接続の機能は、無線周波数信号入力を備えてもよい。さらなる実施形態によると、集積回路ダイの外部接続の機能は、無線周波数信号出力を備えてもよい。40

本発明は、例えば、以下を提供する。

#### ( 項目 1 )

静電放電 ( E S D ) 保護素子であって

ドレイン、少なくとも 2 つのゲート、およびソースを有する、電界効果トランジスタ (

50

FET) であって、そのドレインは、ESDイベントから保護されるように、回路のノードに結合される、電界効果トランジスタと、

前記FETのソースと電源コモンとの間に結合される、少なくとも1つのダイオードと、

前記FETの少なくとも2つのゲート間に結合される、第1の抵抗器と、

前記少なくとも2つのゲートのうちの一方および前記電源コモンに結合される、第2の抵抗器と、

を備える、ESD保護素子。

(項目2)

前記少なくとも2つのゲートのうちの一方は、トリガゲートであって、前記少なくとも2つのゲートのうちの別の一方は、放電ゲートである、項目1に記載のESD保護素子。

(項目3)

前記FETは、空乏モードFETである、項目1に記載のESD保護素子。

(項目4)

前記少なくとも1つのダイオードは、前記FETのソースと電源コモンとの間に直列に接続される2つのダイオードである、項目1に記載のESD保護素子。

(項目5)

前記電源コモンは、電気接地に結合される、項目1に記載のESD保護素子。

(項目6)

前記空乏モードFETは、高電子移動度トランジスタ(HEMT)である、項目3に記載のESD保護素子。

(項目7)

前記HEMTは、シュードモルフィック型HEMT(pHEMT)である、項目6に記載のESD保護素子。

(項目8)

前記HEMTは、メタモルフィック型HEMT(mHEMT)である、項目6に記載のESD保護素子。

(項目9)

前記HEMTは、誘導HEMTである、項目6に記載のESD保護素子。

(項目10)

前記FET、前記少なくとも1つのダイオード、ならびに前記第1および第2の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される回路ノードに結合される、項目1に記載のESD保護素子。

(項目11)

前記集積回路ダイの外部接続の機能は、アナログ入力、デジタル入力、アナログ出力、デジタル出力、アナログ入力/出力、デジタル入力/出力、電力接続、バイアス入力、および外部補償キャパシタから成る群から選択される、項目10に記載のESD保護素子。

(項目12)

静電放電(ESD)保護素子であって、

ドレイン、少なくとも2つのゲート、およびソースを有する、第1の電界効果トランジスタ(FET)であって、そのドレインは、ESDイベントから保護されるように、回路のノードに結合される、第1の電界効果トランジスタと、

前記第1のFETのソースに結合されるアノードを有する、少なくとも1つの第1のダイオードと、

前記第1のFETの少なくとも2つのゲート間に結合される、第1の抵抗器と、

前記少なくとも2つのゲートのうちの一方および前記少なくとも1つの第1のダイオードのカソードに結合される、第2の抵抗器と、

ドレイン、少なくとも2つのゲート、およびソースを有する、第2の電界効果トランジスタ(FET)であって、そのドレインは、電源コモンに結合される、第2の電界効果トランジスタと、

10

20

30

40

50

前記少なくとも 1 つの第 1 のダイオードのカソードに結合されるカソードを有する、少なくとも 1 つの第 2 のダイオードと、

前記第 2 の F E T の少なくとも 2 つのゲート間に結合される、第 3 の抵抗器と、

前記第 2 の F E T の少なくとも 2 つのゲートのうちの一方および前記少なくとも 1 つの第 2 のダイオードのカソードに結合される、第 4 の抵抗器と、

を備える、E S D 保護素子。

(項目 13)

前記第 1 および第 2 の F E T の少なくとも 2 つのゲートのうちの一方は、トリガゲートであって、前記第 1 および第 2 の F E T の少なくとも 2 つのゲートのうちの別の一方は、放電ゲートである、項目 12 に記載の E S D 保護素子。

10

(項目 14)

前記第 1 および第 2 の F E T は、空乏モード F E T である、項目 12 に記載の E S D 保護素子。

(項目 15)

前記少なくとも 1 つの第 1 および第 2 のダイオードは、それぞれ、前記第 1 および第 2 の F E T のソース間に直列に接続される、2 つのダイオードである、項目 12 に記載の E S D 保護素子。

(項目 16)

前記電源コモンは、電気接地に結合される、項目 12 に記載の E S D 保護素子。

(項目 17)

前記第 1 および第 2 の空乏モード F E T は、高電子移動度トランジスタ ( H E M T ) である、項目 14 に記載の E S D 保護素子。

20

(項目 18)

前記 H E M T は、シュードモルフィック型 H E M T ( p H E M T ) 、メタモルフィック型 H E M T ( m H E M T ) および誘導 H E M T から成る群から選択される、項目 17 に記載の E S D 保護素子。

(項目 19)

前記第 1 および第 2 の F E T 、前記第 1 および第 2 の少なくとも 1 つのダイオード、ならびに前記第 1 、第 2 、第 3 、および第 4 の抵抗器は、集積回路ダイ上に加工され、前記集積回路ダイの外部接続に結合される回路ノードに結合される、項目 12 に記載の E S D 保護素子。

30

(項目 20)

前記集積回路ダイの外部接続の機能は、無線周波数信号入力を備える、項目 19 に記載の E S D 保護素子。

(項目 21)

前記集積回路ダイの外部接続の機能は、無線周波数信号出力を備える、項目 19 に記載の E S D 保護素子。

【図面の簡単な説明】

【0012】

本開示のより完全な理解は、付随の図面と関連して検討される以下の説明を参照することによって得られ得る。

40

【0013】

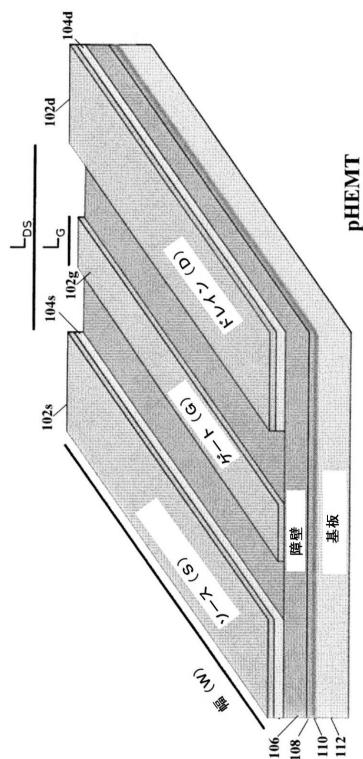

【図 1】図 1 は、本開示の教示による、H E M T 素子の概略等角断面図を図示する。

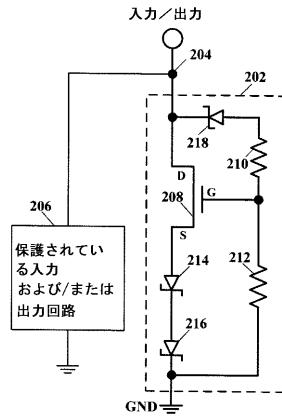

【図 2】図 2 は、直流 ( D C ) および制御ポートのための従来技術の単一極性空乏モード F E T E S D 保護素子の概略図を図示する。

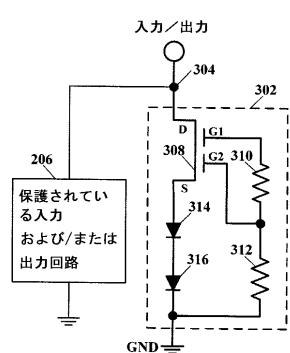

【図 3】図 3 は、本開示の具体的例示的実施形態による、直流 ( D C ) および制御ポートのための単一極性多重ゲートショットキー空乏モード F E T E S D 保護素子の概略図を図示する。

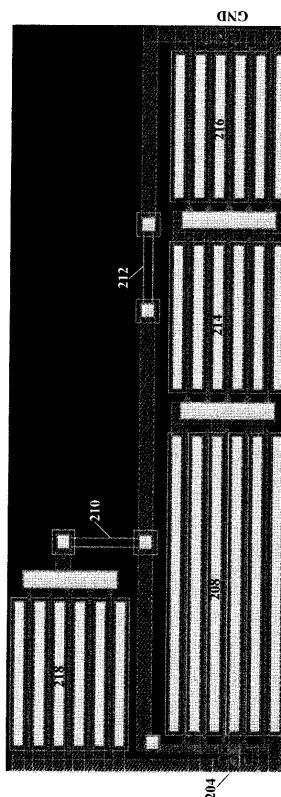

【図 4】図 4 は、図 2 に示される E S D 保護素子のための従来技術の構造の概略平面図を図示する。

50

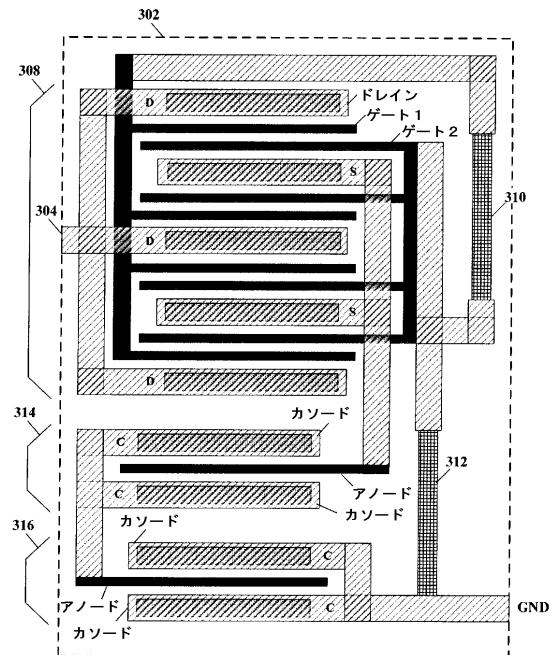

【図5】図5は、本開示の具体的例示的実施形態による、図3に示されるE S D保護素子の構造の概略平面図を図示する。

【図6】図6は、本開示の具体的例示的実施形態による、図3に示されるE S D保護素子のための構造のより詳細な概略平面図を図示する。

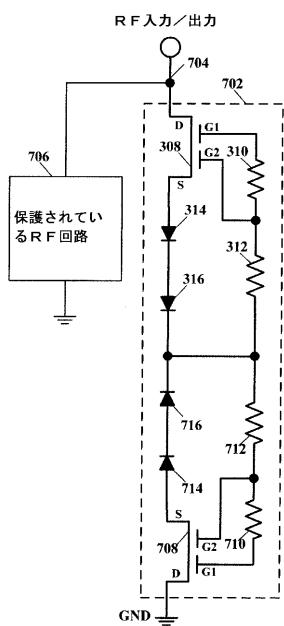

【図7】図7は、本開示の別の具体的例示的実施形態による、無線周波数(R F)ポートのための二重極性多重ゲートショットキー空乏モードF E T E S D保護素子の概略図を図示する。

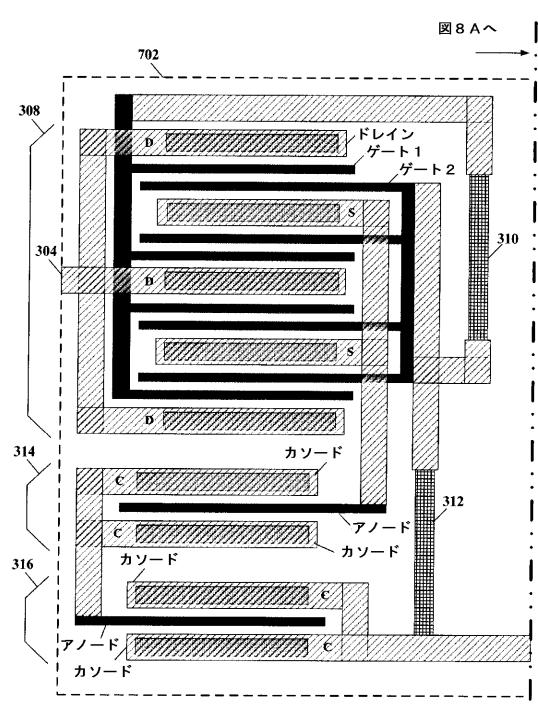

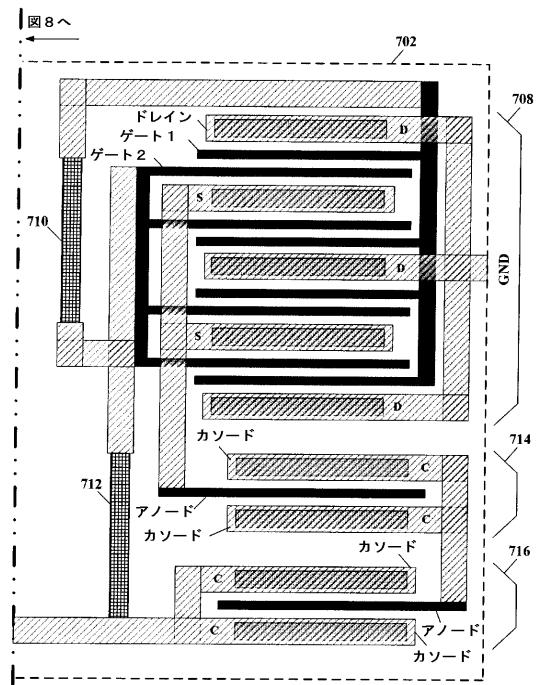

【図8】図8および8 Aは、本開示の具体的例示的実施形態による、図7に示されるE S D保護素子のための構造の概略平面図を図示する。

【図8 A】図8および8 Aは、本開示の具体的例示的実施形態による、図7に示されるE S D保護素子のための構造の概略平面図を図示する。 10

#### 【0014】

本開示は、種々の修正および代替形態を受け入れ可能であるが、その具体的例示的実施形態が、図面に示され、本明細書に詳細に説明される。しかしながら、具体的例示的実施形態の本明細書における説明は、本開示を本明細書に開示される特定の形態に限定することを意図するものではなく、対照的に、本開示は、添付の請求項によって定義される全修正および均等物を網羅することを理解されたい。

#### 【発明を実施するための形態】

#### 【0015】

種々の実施形態によると、ヘテロ構造F E Tまたは変調ドープF E Tとしても知られる、シュードモルフィック型高電子移動度トランジスタ(p H E M T)が、本明細書に開示される種々の実施形態による、コンパクトなE S D保護素子の概念を説明するために、本明細書では実施例として使用される。従来、いくつかの大型ショットキーダイオードは、電圧を増加させ、アクティブ回路を適正に保護するために、p H E M T素子のゲートとともに形成され、直列にカスケード化されていた。これらの複数のダイオード素子は、高価なG a A s集積回路ダイ内で広い面積を消耗していた。本開示の種々の実施形態によると、多重ゲートH E M Tを使用して、コンパクトなE S D保護素子を形成することが提案されている。H E M T素子の多重ゲートは、E S D保護素子および構造に続く回路の保護のためのE S Dトリガおよび電荷排出経路を形成するために使用されてもよい。E S D保護素子構造は、複数のダイオードE S D素子構造よりもはるかに小さい面積内にレイアウトされることができる。種々のタイプのH E M T素子、例えば、p H E M T、m H E M T、誘導H E M T等が、本明細書に開示されるE S D保護素子と併用されてもよいことが検討され、本開示の範囲内である。 20

#### 【0016】

ここで図面を参照すると、例示的実施形態の詳細が、図式的に図示される。図面中の同一要素は、同一番号によって表され、類似要素は、異なる小文字添え字を伴う同一番号によって表されるであろう。

#### 【0017】

図1を参照すると、描写されるのは、本開示の教示による、H E M T素子の概略等角断面図である。p H E M Tは、例証目的のために示されるが、他のH E M T素子も同様に、本開示の教示に従って使用され得ることが検討され、本発明の範囲内である。H E M T素子は、基板112と、2次元電子ガス層110と、スペーサ108と、障壁106と、キャッピング層104と、金属ドレイン、ソース、およびゲート電極102とを備えてよい。ソース、ゲート、およびドレイン金属102は、限定ではないが、金を備えてよい。障壁106は、限定ではないが、アルミニウムガリウムヒ素(A1 G a A s)を備えてよい。スペーサ108は、限定ではないが、ガリウムヒ素(G a A s)を備えてよい。2次元電子ガス層110は、限定ではないが、インジウムガリウムヒ素(I n G a A s)を備えてよい。基板は、限定ではないが、高抵抗率G a A sを備えてよい。第1の抵抗器210は、約500オーム～約2000オームの抵抗値を有してもよい。第2の抵抗器212は、約2000オームの抵抗値を有してもよい。 40

10

20

30

30

40

50

## 【0018】

図2および4を参照すると、描寫されるのは、直流(DC)および制御ポートのための従来技術の単一極性空乏モードFET ESD保護素子の概略図と、図2に示されるESD保護素子のための従来技術の構造の概略平面図である。単一極性单一ゲートESD保護素子202が、集積回路パッケージ(図示せず)の回路206の制御信号および/またはバイアス供給ノード(ピン)を保護するために使用されている。ESD保護素子202は、ドレイン(D)、ソース(S)、および単一ゲート(G)を有する、電界効果トランジスタ(FET)208と、第1および第2のショットキーダイオード214および216と、第3のダイオード218と、第1および第2のゲート抵抗器210および212とを備えてもよい。第3のダイオード218は、ESDイベントが生じると、伝導し(なだれ降伏状態になる)、それによって、トランジスタ208をオンにする、トリガダイオードである。ショットキーダイオード214および216は、電圧レベルシフトのために使用され、空乏モードトランジスタ208が、通常動作の間にオンになって電流を伝導させることを防止する。

10

## 【0019】

図3、5、および6を参照すると、描寫されるのは、本開示の具体的例示的実施形態による、直流(DC)および制御ポートのための単一極性多重ゲートショットキー空乏モードFET ESD保護素子の概略図と、図3に示される、ESD保護素子のための構造の概略平面図である。ショットキー多重ゲートを有する単一極性ESD保護素子302は、集積回路パッケージ(図示せず)の回路306の制御信号および/またはバイアス供給ノード(ピン)を保護するために使用されてもよい。ESD保護素子302は、ドレイン(D)と、ソース(S)と、第1および第2のトリガゲート(G1およびG2)と、第1および第2のダイオード314および316と、第1および第2のゲート抵抗器310および312とを有する、多重ゲートショットキー空乏モード電界効果トランジスタ(FET)308、例えば、HEMT素子を備えてもよい。FET308は、2つまたはそれを上回るゲートを有し得ることも検討され、本開示の範囲内である。少なくとも1つのレベルシフトダイオードは、FETのソース308と電源コモン、例えば、電気接地との間に結合されてもよい。FET308のドレインは、集積回路(IC)パッケージ(図示せず)の外部接続(ピン)に結合され得る、ノード304に結合されてもよい。ICパッケージの外部接続(ピン)は、例えば、限定ではないが、アナログ入力、デジタル入力、アナログ出力、デジタル出力、アナログ入力/出力、デジタル入力/出力、電力接続、バイアス入力、外部補償キャパシタ等として使用されてもよい。

20

30

## 【0020】

負の静電電荷が、ノード304に蓄積すると、第2のトリガゲート(G2)は、順方向にバイアスされ、これらの電荷を第2のゲート抵抗器312を通して接地に排出する。正の静電電荷が、ノード304に蓄積すると、正の電位が、第1のトリガゲート(G1)が逆方向降伏状態になるまで、蓄積されるであろう。本降伏電流は、接地に流動し、第2のゲート抵抗器312を横断して、正の電位を確立するであろう。したがって、十分な電圧の提供は、ゲート/ソース電位が、直列に接続された第1および第2のダイオード314および316のターンオン電圧より正となると、その第2のゲートG2を用いて、FET308をオンにする。これらの第1および第2のダイオード314および316は、FETのソース308と電源コモン、例えば、接地との間に結合され、電圧レベルシフトを提供し、空乏モードトランジスタが、オンになる(伝導しない)ことを防止する。FET308のドレイン電流は、ノード304における正の静電電荷を消散させるための別の経路を提供し、第1のトリガゲートG1が、第1のトリガゲートG1を損傷し得る、過剰降伏電流を有することを防止するのに役立つ。

40

## 【0021】

故に、多重ゲート構造FET308は、トリガダイオード素子および放電ゲートFETを組み合わせ、貴重な集積回路ダイ面積を節約するための独特な方法である。加えて、3つのアクティブ素子面積のみが、単一極性多重ゲートESD保護素子302のために必要

50

である(1)FET308、2)および3)第1および第2のダイオード314および316)。従来技術のESD保護素子202は、4つのアクティブ素子面積(1)FET208、2)トリガ第3のダイオード218、3)および4)レベルシフトダイオード214および216)を要求する。したがって、従来技術のESD保護素子202は、本開示の教示による、同一ESD保護レベルを達成するために、集積回路ダイ(図示せず)上に、単一極性多重ゲートESD保護素子302より広いアクティブ素子面積を要求する。

#### 【0022】

図7、8、および8Aを参照すると、描寫されるのは、本開示の別の具体的例示的実施形態による、無線周波数(RF)ポートのための二重極性多重ゲートショットキー空乏モードFET ESD保護素子の概略図と、図7に示されるESD保護素子のための構造の概略平面図である。二重極性多重ゲートショットキー空乏モードFET ESD保護素子702は、集積回路パッケージ(図示せず)の回路706の制御、信号、および/またはバイアス供給ノード(ピン)を保護するために使用されてもよい。ESD保護素子702は、ドレイン、ソース、および第1および第2のゲート(G1およびG2)を有する、第1のHEMT素子308と、第1および第2のダイオード314および316と、第1および第2のゲート抵抗器310および312と、ドレイン、ソース、および第1および第2のゲート(G1およびG2)を有する、第2のHEMT素子708と、第3および第4のダイオード714および716と、第3および第4のゲート抵抗器710および712とを備えてもよい。ESD保護素子702は、有利には、高RF電力素子と関連付けられたRFポートと併用されてもよい。本ESD保護回路は、大規模な正および負のRF電圧振幅の存在下で使用されてもよい。本二重極性多重ゲートFET ESD保護素子702の作用原理は、実質的に、単一極性多重ゲートESD保護素子308のものに類似する。要素708-716は、要素308-316の鏡像として機能する。

10

#### 【0023】

本開示の実施形態が、本開示の例示的実施形態を参考することによって、描寫、説明、および定義されたが、そのような参照は、本開示の限定を含意するものではなく、そのような限定は、推測されない。開示される主題は、当業者および本開示の利益を有する者に想起されるであろうように、形態および機能において、少なからず修正、改変、および均等物が可能である。本開示の描寫および説明される実施形態は、実施例にすぎず、本開示の範囲の包括ではない。

20

30

【図1】

【図2】

FIGURE 2 (従来技術)

【図3】

FIGURE 3

【図4】

FIGURE 4 (従来技術)

【図5】

FIGURE 5

【図6】

FIGURE 6

【図7】

FIGURE 7

【図8】

FIGURE 8

【図 8 A】

**FIGURE 8A**

---

フロントページの続き

|                          |                |

|--------------------------|----------------|

| (51)Int.Cl.              | F I            |

| H 01 L 21/822 (2006.01)  | H 01 L 27/04 H |

| H 01 L 27/04 (2006.01)   | H 01 L 27/06 F |

| H 01 L 21/8232 (2006.01) |                |

| H 01 L 27/06 (2006.01)   |                |

(72)発明者 チョウ，ペイ - ミン ダニエル

アメリカ合衆国 カリフォルニア 90025，ロサンゼルス，マニング アベニュー 20

51

(72)発明者 コク，ヨン - リン

アメリカ合衆国 カリフォルニア 90703，セリトス，スターク アベニュー 1890

9

(72)発明者 ズー，ジン

アメリカ合衆国 カリフォルニア 90404，サンタ モニカ，カンザス アベニュー 2

546，アパートメント 104

(72)発明者 シェル，スティーブン

アメリカ合衆国 カリフォルニア 90503，トーランス，トムリー アベニュー 206

01

審査官 恩田 和彦

(56)参考文献 米国特許第07881029(US, B1)

特開2003-347417(JP, A)

米国特許出願公開第2012/0262828(US, A1)

特開2006-165182(JP, A)

特表2007-521651(JP, A)

特表2010-503217(JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |           |

|--------|-----------|

| H 01 L | 21 / 337  |

| H 01 L | 21 / 338  |

| H 01 L | 21 / 822  |

| H 01 L | 21 / 8232 |

| H 01 L | 27 / 04   |

| H 01 L | 27 / 06   |

| H 01 L | 29 / 778  |

| H 01 L | 29 / 808  |

| H 01 L | 29 / 812  |