# **PCT**

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>3</sup> : |    | (11) International Publication Number: | WO 82/ 02311           |

|---------------------------------------------------------|----|----------------------------------------|------------------------|

| H04N 5/44                                               | A1 | (43) International Publication Date:   | 8 July 1982 (08.07.82) |

(21) International Application Number: PCT/US81/01449

(22) International Filing Date: 28 October 1981 (28.10.81)

(31) Priority Application Number: 220,607

(32) Priority Date: 29 December 1980 (29.12.80)

(33) Priority Country: US

(71) Applicant: MOTOROLA, INC. [US/US]; 1303 East Algonquin Road, Schaumburg, IL 60196 (US).

(72) Inventor: LUNN, Gerald K.; 7325 E. Garfield Street, Scottsdale, AZ 85257 (US).

(57) Abstract

(74) Agents: GILLMAN, James William et al.; Motorola, Inc. Patent Department, 4350 East Camelback Road, Suite 200F, Phoenix, AZ 85018 (US).

(81) Designated States: DE (European patent), FR (European patent), GB (European patent), JP.

Published

With international search report.

(54) Title: LARGE SCALE, SINGLE CHIP INTEGRATED CIRCUIT TELEVISION RECEIVER SUBSYSTEMS

A single chip integrated circuit (50) that performs the electronic functions of a monochrome television receiver with the exception of the RF tuner, sound channel, and power output stages. The circuit includes video IF/detector (52, 60) and video processing (66) as well as a two loop horizontal phase locked loop (104, 106, 108, 110) for locking the horizontal flyback to the horizontal sync pulses. In addition, a vertical processing stage related to the horizontal sync pulses, is included for producing vertical flyback. The circuit operates in a vertical narrow window mode when coincidence occurs between the vertical sync pulses and the output of a vertical countdown circuit to thereby reduce interference from noise and operates in a wide window mode when vertical sync pulses are lost or not yet acquired to allow fast acquisition of the vertical sync pulses.

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                      | KP | Domannela Banalata Banalata ak Kana   |

|----|------------------------------|----|---------------------------------------|

| AU |                              |    | Democratic People's Republic of Korea |

|    | Australia                    | LI | Liechtenstein                         |

| BE | Belgium                      | LK | Sri Lanka                             |

| BR | Brazil                       | LU | Luxembourg                            |

| CF | Central African Republic     | MC | Monaco                                |

| CG | Congo                        | МG | Madagascar                            |

| CH | Switzerland                  | MW | Malawi                                |

| CM | Cameroon                     | NL | Netherlands                           |

| DE | Germany, Federal Republic of | NO | Norway                                |

| DK | Denmark                      | RO | Romania                               |

| FI | Finland                      | SE | Sweden                                |

| FR | France                       | SN | Senegal                               |

| GA | Gabon                        | SU | Soviet Union                          |

| GB | United Kingdom               | TD | Chad                                  |

| HU | Hungary                      | TG | Togo                                  |

| JР | Japan                        | US | United States of America              |

|    |                              |    |                                       |

# LARGE SCALE, SINGLE CHIP INTEGRATED CIRCUIT TELEVISION RECEIVER SUBSYSTEMS

## CROSS REFERENCE TO RELATED APPLICATIONS

5

- 1. SC-80041 "Horizontal Oscillator"

- 2. SC-80044 "Horizontal Phase Detector Gain Control"

- 3. SC-80977 "Horizontal Phase Lock Loop For Television"

- 4. SC-80978 "Variable Capacitance Circuit"

- 10 5. SC-80071 "Linear Full Wave Rectifier Circuit"

- 6. SC-80976 "Sync Separator"

- 7. SC-80980 "Integrator Circuit For Separating Vertical Sync Pulses"

15

#### BACKGROUND OF THE INVENTION

#### Field of the Art:

The present invention relates to television circuits and, more particularly, to a partitioning scheme for a television receiver for providing the video and signal processing circuits on a single large scale integrated circuit.

## Description of the Prior Art:

Since the first television receiver was built comprising discrete circuitry and vacuum tubes television receivers have evolved to the present wherein the television receiver comprises a plurality of integrated circuits in combination with the tuner and high powered portions of the circuit as well as the cathode ray tube (CRT) utilized to provide the television picture.

Generally, contemporary television receivers include a radio frequency (RF) tuner which is coupled to a tuned input of an intermediate frequency (IF) stage the output of which is coupled to both a video processing stage and a signal processing stage wherein the video composite TV

15

signal is processed to drive the cathode ray tube with the output of the signal processing stage being utilized to drive the horizontal and vertical deflection yokes of the television cathode ray tube so that the video information 5 supplied from the video processor is converted to a recognizable picture on the CRT.

Typically, contemporary television receivers require a minimum of four integrated circuits to provide the functions of a basic black and white television receiver. 10 For example, the television receiver can be partitioned in a manner wherein four integrated circuits may be utilized to provide (1) video IF amplifier and video detection (2) video signal processing (3) horizontal sync information processing and (4) vertical sync information processing.

The aforedescribed combination of multiple integrated circuits results in a problem that is related to all such television receivers which is caused by undesirous signal radiation that occurs to a greater or lesser extent because of the use of external coils in tuned circuits required for 20 detection of the composite TV stereo operating in a high signal environment. For instance, this radiation usually emanates from a portion of the television receiver where the IF signal levels are at the highest: usually at the interface of the video detector stage of the television 25 receiver where the external tuned circuits are utilized for video detection. Another problem with television receivers utilizing multiple integrated circuits is that exact DC signal bias levels must be maintained between each one of the multiple integrated circuits. It is quite difficult to 30 achieve these bias levels and an attempt to so requires external biasing circuitry to be utilized. Still further, the use of multiple integrated circuits can be relatively expensive when compared to a television receiver that required only a single large scale integrated chip to provide the aforementioned functions.

Hence, the present invention is concerned with combining the basic functions of a television receiver, i.e., the IF amplifier/detector stage, video processing and signal processing circuits into a single large scale 5 integrated circuit having optimum partitioning. Such a single integrated circuit can eliminate radiation problems as aforedescribed with elimination of tuned circuits by the use thereof as well as save costs by eliminating the need for multiple integrated circuits.

10

15

# SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide a large scale integrated circuit television subsystem.

There's another object of the present invention to provide a large scale integrated circuit incorporating the basic functions of a television receiver including the IF amplifier, video detecting and processing, horizontal and 20 vertical processing circuits therefor.

A still further object of the present invention is to provide a large scale integrated circuit to be utilized in a television receiver having a horizontal and vertical processing circuit for producing vertical and horizontal sync pulses which are related to each other.

In accordance with the above and other objects there is provided a large scale integrated circuit having circuit partitioning for providing basic functions of a black and white television receiver including an IF amplifier 30 section, a video detector, a signal processor, a video signal processor, horizontal and vertical processors therein.

One feature of the present invention is that the video detector circuit eliminates the use of tuned circuits such that radiation problems which frequently occur in prior art

television receivers are eliminated or at least greatly reduced.

#### BRIEF DESCRIPTION OF THE DRAWINGS

5

15

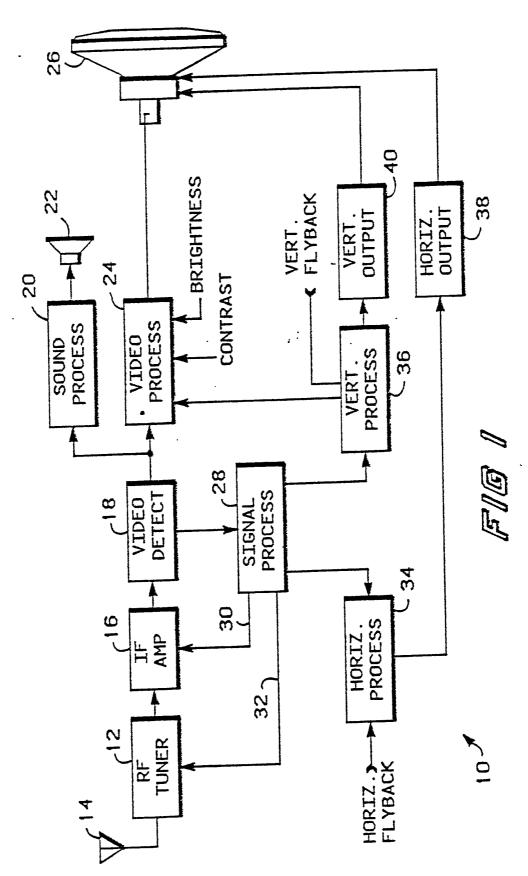

Fig. 1 is a block diagram illustrating a typical black and white television receiver;

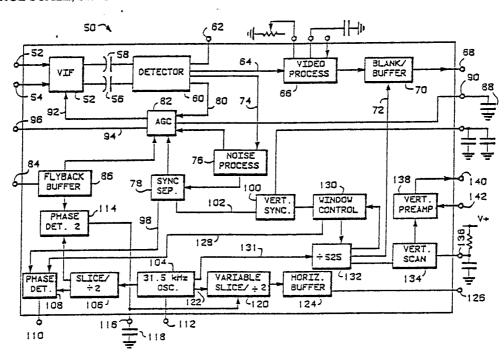

Fig. 2 is a block diagram of the television receiver of the present invention;

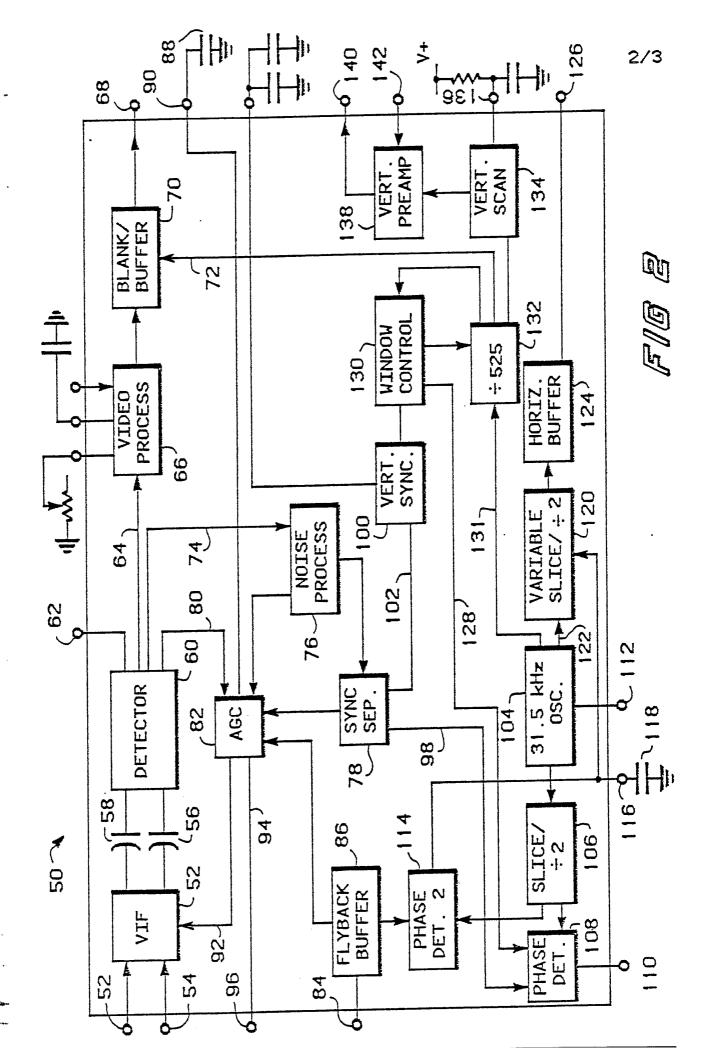

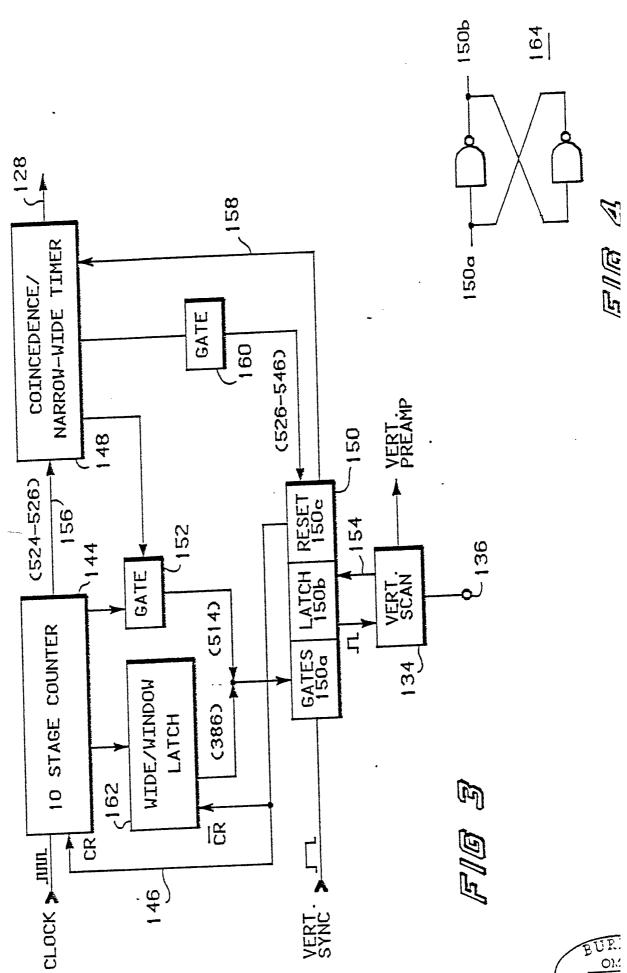

10 Fig. 3 is a block diagram of a vertical countdown circuitry of the present invention; and

Fig. 4 is a schematic diagram of a latch circuit utilized in the vertical countdown circuitry of Fig. 3.

#### DETAILED DESCRIPTION OF THE INVENTION

Turning to Fig. 1, there is shown a typical black and white television receiver which is generally understood to those skilled in the art. Television receiver (10), as 20 shown, comprises a RF tuner section 12 which is coupled to antenna 14 to receive the television composite signal. tuner 12 includes a voltage controlled oscillator for converting the composite television signal to an IF frequency which is then applied via a tuned stage to the 25 input of IF amplifier section 16. The output of IF amplifier section 16 is applied to video detector 18 wherein the video information, as well as the vertical and horizontal sync information are detected and separated from the sound information carrying signal. The sound signal is 30 processed through sound processing circuit 20 to be reproduced as audio at speaker 22. The video information is processed through video processing circuit 24 to drive the cathode of cathode ray tube 26 to develop the television picture in conjunction with the vertical and 35 horizontal deflection circuits V and H which surround tube 26. An output is also supplied from video detector 18 to

35

signal processing cirucit 28, which as known provides several functional outputs, i.e., gated automatic gain control signals are provided for controlling the gains of the IF amplifier stage 16 and the RF tuner 12 via leads 30 and 32 respectively, also, the horizontal and vertical sync pulses are separated with RF noise spikes eliminated from the sync pulses. The respective pulses are supplied to horizontal and vertical processing circuits 34 and 36. Video processing circuit 24 is shown as receiving contrast and brightness control signals as is understood to vary the signal drive to the cathode of cathode ray tube 26. Video processing circuit 24 also receives a blanking signal from vertical processing circuit 36 to blank the screen of the tube 26 during the vertical flyback period of the

Horizontal and vertical processing circuits 34 and 36 each typically include a free running oscillator which may be locked by the respective horizontal and vertical sync pulses supplied thereto for synching the horizontal and vertical scanning to the received video signal. Horizontal scanning information is sampled from the currents introduced through the horizontal deflection coils, H and V, which are positioned about tube 26 in order to maintain synchronization and linearity of drive. The outputs from horizontal and vertical circuits 34 and 36 are supplied to horizontal and vertical output amplifiers 38 and 40 respectively to drive the aforementioned deflection coils.

It should be understood that although the foregoing description refers to a black and white television receiver that those skilled in the art understand that a color receiver is also explained in that only a chroma demodulator and driver stages need be added to the television receiver in a known manner in conjunction with a color cathode ray tube.

Typically, contemporary television receiver 10 comprises a minimum of four integrated circuits (IC's) for

providing the IF, video detection, horizontal sync and vertical sync processing. As an example, television receiver 10 can be realized using the following available ICs which are manufactured by Motorola Inc.:

5

|    | TELEVISION CIRCUIT                 | IC          |

|----|------------------------------------|-------------|

|    | IF Amplifier 16                    | MCl349/1350 |

|    | Video Dectector and Video          | MC1330/1350 |

|    | Processing Circuits 18 and 24      |             |

| 10 | Sound Processing Circuit 20        | TDAll90     |

|    | Signal Processing Circuit 28       | MC1344      |

|    | Horizontal Processing Circuit 34   | MCl391      |

|    | Vertical Processing Circuit 36     | MC1393      |

|    | As mentioned previously, prior art | television  |

receivers of the type described above suffer from several disadvantages, i.e. radiation problems and maintenance of accurate dc levels between individual integrated circuits. The present invention relates to specific partitioning of the several individual stages described above into a large scale integrated circuit to eliminate radiation problems generally arising in the video detector portion by eliminating the need for tuned circuits as well as eliminating the need for several dc biasing circuits for maintaining the dc levels between the individual integrated circuits.

Turning now to Fig. 2, there is shown a large scale integrated television receiver subsystem circuit 50 of the preferred embodiment wherein partitioning of the IF and video processing circuity is accomplished on one single integrated circuit to eliminate the aforementioned problems of the prior art. As illustrated single integrated circuit television receiver subsystem 50 includes video IF amplifier stage 52 to which is supplied the composite television signal at input terminals 52 and 54 from a RF tuner section (not shown). The output of the video IF section is coupled via coupling capacitors 56 and 58 to the

input of video detector 60. Coupling capacitors 58 and 56 are integrated on the integrated circuit whereby video detector 60 is ac coupled to video IF amplifier 52. output at output terminal 62 from video detector is 5 supplied to the sound processor section of the television receiver which is not part of the integrated circuit subsystem 50. Copending patent application, Serial No. , entitled "Linear Full Wave Rectifier Circuit" which is incorporated herein by reference describes a 10 circuit that may be utilized for detecting the video television composite signal. The composite video information signal appearing at the output of video detector 60 is supplied via lead 64 to video processor. circuit 66 and is processed in like manner for prior art 15 processor circuits to provide the luma information to the cathode of the cathode ray tube at output 68 of subsystem circuit 50. It is to be understood that if a color television receiver is to utilize single subsystem circuit 50 that chroma demodulator and detector circuits would be 20 coupled to output terminal 68 to provide chroma information to a color tube. The output of video processing circuit 66 is coupled to output 68 through a blank/buffer circuit 70 which receives a blanking input signal via lead 72 to provide the blanking function to the television tube during 25 vertical flyback. Still another output of detector 60 is taken via lead 74 and supplied to noise processing circuit 76 for eliminating noise spikes from the composite video signal appearing at output 74. Noise processing circuit 76 provides the aforementioned function in a known manner 30 wherein the noise spikes are inverted and then added back to the signal for example, to eliminate the same therefrom so that noise spikes will not affect the operation of the sync separator circuit 78. The output of noise processor circuit 76 as well as sync separator 78 and output 80 of 35 video detector 60 is supplied to automatic gain control

(AGC) circuit 82. The horizontal flyback signal supplied

at input terminal 84 via buffer circuit 86 is also supplied to an input of AGC circuit 82 to develop a gated gain control signal at the outputs of thereof in response to a gain control voltage being developed across an external capacitor 88 supplied to input terminal 90 of the television receiver subsystem 50. AGC circuit 82 operates in a known manner to first vary the gain of the video IF section 52 via lead 92 and then to vary the gain of the RF tuner via lead 94 which is connected at an output pin 96 of television receiver subsystem 50.

The output of noise processor circuit 76 is supplied to sync separator 78 to separate the horizontal and vertical sync pulses are separated from the video composite signal as is well known in the art. A possible circuit 15 which may be utilized as sync separator 78 is described in detail in referenced patent application, Serial No. , entitled "Sync Separator" which is also incorporated herein by reference. The horizontal sync pulses from sync separator 78 and supplied to a horizontal processor circuit 20 via lead 98 with the vertical sync pulse information being supplied to vertical sync circuit 100 via lead 102. Vertical sync circuit 100 may include an integrator circuit described in copending patent application, Serial No. , entitled "Integrator Circuit For Separating 25 Vertical Sync Pulses", which is incorporated herein by reference.

As illustrated, the horizontal processor portion of television receiver subsystem circuit 50 operates to lock the horizontal flyback signal to the horizontal sync pulse which is in turn locked to the horizontal oscillator 104. An oscillator suitable for use as horizontal oscillator 104 is described in copending patent application, Serial No.

\_\_\_\_\_\_\_, entitled "Horizontal Oscillator", and incorporated herein by reference operates at a frequency equal to twice the horizontal line frequency, i.e., 31.5 kHz. In the present embodiment, the horizontal processing circuit

besides including horizontal oscillator 104, comprises a phase lock loop circuit comprising two loops. loop includes oscillator 104 which is a free running oscillator line the output thereof being provided to a 5 slicer and divide by two circuit 106. The output of slicer circuit 106 is provided to a first phase detector 108 which is gated by the horizontal sync pulses provided from sync separator 78 via lead 98. The output of phase detector 108 is provided at an output 110 to a low pass filter (not 10 shown) and is returned to the input of the horizontal oscillator 104 at an input pin 112. In this manner, the frequency of the horizontal oscillator 104 is varied such that the horizontal sync pulses are centered about the trailing edges of the output pulses of the horizontal 15 oscillator 104. The second loop of the two-loop horizontal phase lock loop circuit includes oscillator 104, slicer/ divide by two circuit 106, and a second phase detector 114 which is gated by the flyback pulses from the horizontal deflection circuit of the television receiver and supplied 20 at input terminal 84 through flyback buffer 86. The output of phase detector 114 is supplied at an output 116 to a low pass filter which may be, as shown, capacitor 118 to bias a variable slicer/divide by two circuit 120 which also receives the horizontal oscillator pulses via lead 122. this manner, the horizontal flyback pulse is centered about a point on the output of the oscillator such that the horizontal flyback pulses are locked with respect to the horizontal sync pulses to the horizontal oscillator. A detailed description of a horizontal processor circuit that may be utilized in the present invention is provided in aforereferenced copending patent application, Serial No. , entitled "Horizontal Phase Lock Loop For

\_\_\_\_\_\_, entitled "Horizontal Phase Lock Loop For Television" which is incorporated herein by reference. The output of variable slicer 120 supplied through a horizontal buffer circuit 124 to output pin 126. As understood, the output from the horizontal processor circuit, at output pin

126, is supplied to a horizontal driver amplifier to drive the horizontal deflection coils of the cathode ray tube of the television receiver. Phase detector 108 is shown as also receiving an input control signal via lead 128 from a 5 window control circuit 130. As is fully explained in copending patent application, Serial No. \_\_\_\_\_, entitled "Horizontal Phase Detector Gain Control", and incorporated herein by reference, the gain of the phase detector 108 is varied by this control signal supplied from window control 10 circuit 130 in accordance with the television receiver being either in sync or not with the television composite signal. Hence, if the television receiver is in sync the gain of phase detector 108 is at a nominal value and is then increased if the television is not in sync to the 15 incoming composite television signal, this increases the bandwidth of the phased locked loop to effect a faster pull-in of the horizontal sync pulses as is understood. An output of horizontal oscillator 104 is taken via lead 131 and is supplied to a vertical countdown circuit 132. 20 Vertical sync pulses are also supplied to the vertical processor circuit from vertical sync circuit 100. As will be fully explained hereinafter, the vertical sync pulses are utilized to reset vertical countdown circuit 132, a divide by 525 counter, such that in response to the input pulses supplied from the horizontal oscillator 104, a vertical flyback pulse is derived once each frame, as is required to sync the vertical picture scanning to the received video signal. Vertical countdown circuit 132 also supplies the aforementioned blanking signal via lead 72 to 30 blanking buffer 70. The output of the vertical countdown circuit 132 is provided to vertical scan circuit 134. output of vertical countdown circuit 132 is essentially the vertical sync pulse which is then utilized to generate a ramp signal across the RC combination connected at pin 136 to derive the vertical flyback pulse via vertical 35 preamplifier 138 to the vertical deflection coils of the

5

30

tube at output 140. A feedback signal generated through the vertical deflection coils of the tube is supplied at input pin 142 to an input of vertical preamp 138 to insure tracking of the vertical flyback pulse.

Turning to Figs. 3 and 4, the combined operation of vertical countdown circuit 32 and window control circuit 130 can be explained. Window control circuit 130 is fully discussed in the aforereferenced application, Serial No.

, entitled, "Horizontal Phase Detector Gain Control" 10 with respect to generating a gain control signal for varying the gain of phase detector 108 when the television receiver incorporating the present invention is out of sync. The foregoing patent application is incorporated herein by reference. Briefly, the output pulses of

15 horizontal oscillator 104 are supplied to the input of countdown circuit 132 to initiate vertical countdown. Vertical countdown circuit 132 comprises a ten stage counter 144 as understood. The horizontal oscillator clock pulses are divided by 525 by the counter to provide a

20 decode signal once each frame of the television picture to coincide with the vertical sync pulse supplied from vertical sync circuit 100. Vertical countdown circuit 132 includes a reset circuit 150 for among other things providing a reset pulse via lead 146 to reset counter 144 25 on the occurrence of a vertical sync pulse.

In normal operation, with the television receiver in sync, the vertical snyc pulse is supplied to a plurality of serially connected logic gate inverters 150a at the input of reset circuit 150. These gates may be enabled at the 514th count of counter 144 by gate 152 to allow the sync pulse to pass to latch portion 150b of reset circuit 150. The latch portion provides an output both at the input of reset portion 150c of reset circuit 150 and to the input of vertical scan circuit 134 to initiate the vertical flyback 35 period as previously discussed. The structure of the latch circuit is shown in Fig. 4 and includes a pair of

integrated injection logic (I<sup>2</sup>L) NAND gates as shown. At a predetermined level of the ramp signal generated at terminal 136 a stop signal is initiated from vertical scan circuit 134 via lead 154 to put latch portion 150b in its latched state to thereby inhibit the input to vertical scan circuit 134 as well as to reset reset portion 150c.

Therefore, in addition to initiating the vertical flyback period, the horizontal sync pulse produces a reset signal to reset counter 144. The reset portion of reset cirucit 150 may be a D-type flip flop circuit.

Between the 524th and 526th counts of the counter a narrow window pulse is produced via output lead 156 to the input of coincidence detector 148 of window control circuit 130. If coincidence occurs during this narrow window with 15 the reset signals applied via lead 158, coincidence detector 148 maintains the nominal gain of phase detector 108 and gate 152 is enabled to in turn enable the gates of circuit 150. Thus, a narrow window is established between counts 514 to 526 within which coincidence of the vertical 20 sync pulse must occur. If vertical sync is lost for one reason or another such that a vertical sync pulse does not occur during this narrow window pulse, counter 144 provides a decode signal at count 526 through "OR" gate 160 to produce a reset pulse to the counter. However, after eight 25 missing sync pulses window control circuit 130 defaults to a wide window mode to vary the gain of phase detector 108 as well as to open the period that the gates of reset cirucit 150 are enabled. In this wide window mode, gate 152 is disabled by coincidence detector 148 which therefore 30 enables wide window latch 162 to enable the gates of reset counter 150 at the 86th count from counter 144. Simultaneously, gate 160 is enabled to provide a decode signal at the 546th count. Thus, a wide window pulse is initiated to occur between the 86th and 546th count. 35 soon as a vertical sync pulse is acquired during the wide window mode, window control circuit 130 reverts back to the

narrow window mode of operation. Hence, during normal operating conditions a narrow window mode of opeation is established in television subsystem 50 to inhibit noise interfering with vertical synchronization of the television receiver with a wide window mode being defaulted to when vertical sync pulses are lost for one reason or another to thereby allow fast acquisition thereof.

Thus, what has been described is a single chip integrated circuit that will perform the electronic functions of a monochrome television receiver with the exception of the tuner, sound channel and power output stages. It is to be understood that the aforedescribed single chip integrated circuit can be utilized in conjunction with a chroma demodulator detector stage to provide a color television receiver.

\_\_\_\_\_\_

-14-

#### Claims

- . l. A television subsystem for performing all of the electronic functions of a television receiver that are required between the RF tuner and the power output stages of the receiver but for the sound channel wherein the subsystem is a single integrated circuit chip.

- 2. The television subsystem of claim 1 wherein said 10 chip includes therein:

- a video amplifier coupled to inputs of the chip for receiving the composite television signal supplied from the RF tuner;

- a video detector and video processor for

15 providing luma information at a first output of the chip;

a signal processor coupled to an output of said

video detector for providing a gain control signal,

horizontal and vertical sync signals at respective

outputs;

- a gated automatic gain control circuit responsive "to said gain control signal from said signal processor and both horizontal sync and horizontal flyback signals for providing gain control of said video amplifier;

- a horizontal processor circuit coupled to said

25 signal processor and including a two-loop phase locked loop

for locking said horizontal flyback signal in relation to

said horizontal sync pulses to produce horizontal

deflection output signals at a second output of the

subsystem; and

- a vertical processor circuit which receives an input from said horizontal processor circuit which occurs at a frequency twice the frequency of the horizontal flyback signal and a vertical sync pulse for producing vertical deflection output signals at a third output of the subsystem.

3. A single chip television subsystem integrated circuit for a television receiver, comprising:

a video IF amplifier coupled to inputs of the subsystem for receiving a television composite signal supplied from a RF tuner;

a video detector and video signal processor circuit coupled to the output of said video IF amplifier for providing luma information signals at a first output of the subsystem;

a signal processor circuit for developing both horizontal and vertical sync pulses, said signal processor circuit being coupled to the output of said video detector;

a horizontal signal processor circuit responsive to said horizontal sync pulses and horizontal flyback signals supplied thereto from the horizontal deflection circuitry of the television receiver for producing horizontal deflection output signals at a horizontal line frequency at a second output of the subsystem; and

a vertical signal processor circuit responsive both to said vertical sync pulses and a clocking signal supplied from said horizontal signal processor circuit for producing vertical deflection output signals at a third output of the subsystem.

25

30

20

4. The subsystem of claim 3 wherein:

said clocking signals supplied to said vertical

processor circuit from said horizontal processor circuit

occur at twice the horizontal line frequency; and

said horizontal processor circuit includes a two loop phase locked loop such that said horizontal flyback signals are locked in relation to said horizontal sync pulses with said phase locked loop including a free running oscillator operating at twice said horizontal line

35 frequency, said frequency thereof being varied such that

the output from said oscillator occurs in relation to said horizontal sync pulses.

5. The subsystem of claim 4 wherein said vertical processor includes:

a window control circuit; and

a countdown circuit coupled with said window control circuit for receiving said vertical sync pulses and said clocking signals such that the subsystem operates in a vertical narrow window mode when coincidence occurs between said vertical sync pulses and a reset window pulse produced by said countdown circuit, the subsystem operating in a wide window mode in the absence of said coincidence until such time said coincidence is reestablished, the gain of one of said two loops of said horizontal phase locked loop being varied in accordance with each mode of operation.

- 6. In a television receiver including a RF tuner, sound channel, power output driver stages for driving a.

20 cathode ray tube, the improvement comprising the partitioning of a subsystem of the receiver wherein a single chip integrated circuit is provided to produce the video electronic functions of the televison receiver required between the RF tuner and power output driver stages thereof.

- 7. The television receiver of claim 6 wherein said single chip integrated circuit includes:

a video IF amplifier coupled to inputs of the 30 chip for receiving the output from the RF tuner;

a video detector and video signal processor coupled to an output of said IF amplifier for providing luma signal information to the tube at a first output of the chip;

a signal processor for providing horizontal and vertical sync pulses at respective outputs, said signal

processor being coupled to an output of said ivdeo detector;

a horizontal processor responsive to said

horizontal sync pulses and to generated horizontal flyback

signals supplied thereto from the horizontal deflection

circuit of the television receiver to phase lock said

horizontal flyback signals to said horizontal sync pulses

for providing horizontal deflection signals to said

horizontal deflection circuit at a second output of the

subsystem; and

a vertical processor receiving said vertical sync pulses and input control signals from said horizontal processor which operates in a first or a second mode depending on said vertical sync pulses occurring in coincidence with a coincidence signal generated from said input control signals for providing vertical deflection signals to vertical deflection circuits of the television receiver to provide vertical flyback periods.

WO 82/02311 PCT/US81/01449

\_\_\_

BUR. OM WI WI WI ERN,

# INTERNATIONAL SEARCH REPORT

International Application No PCT/US 8 1 / 0 1 4 4 9

| I. CLASSIFICATION OF SUBJECT MATTER (if several classification symbols apply, indicate all) *     |                                                                                    |                                                                                                                   |                                                                                                                                                                                                                                                 |                                                           |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| According to International Patent Classification (IPC) or to both National Classification and IPC |                                                                                    |                                                                                                                   |                                                                                                                                                                                                                                                 |                                                           |  |  |  |  |  |

| 1                                                                                                 | NT CL <sup>3</sup><br>)4N 5/4                                                      |                                                                                                                   | ASS 455/333,<br>8.                                                                                                                                                                                                                              |                                                           |  |  |  |  |  |

| II. FIEL                                                                                          | DS SEARCI                                                                          |                                                                                                                   |                                                                                                                                                                                                                                                 | · · · · · · · · · · · · · · · · · · ·                     |  |  |  |  |  |

| Minimum Documentation Searched 4                                                                  |                                                                                    |                                                                                                                   |                                                                                                                                                                                                                                                 |                                                           |  |  |  |  |  |

| Classifica                                                                                        | tion System                                                                        |                                                                                                                   | Classification Symbols                                                                                                                                                                                                                          |                                                           |  |  |  |  |  |

| υ.                                                                                                | S                                                                                  | 358/148,153,158,188<br>455/333,334                                                                                |                                                                                                                                                                                                                                                 |                                                           |  |  |  |  |  |

|                                                                                                   |                                                                                    | <del>-</del>                                                                                                      | r than Minimum Documentation<br>ts are Included in the Fields Searched <sup>5</sup>                                                                                                                                                             |                                                           |  |  |  |  |  |

| III. DOCUMENTS CONSIDERED TO BE RELEVANT 14                                                       |                                                                                    |                                                                                                                   |                                                                                                                                                                                                                                                 |                                                           |  |  |  |  |  |

| Category *                                                                                        | Citati                                                                             | on of Document, 16 with indication, where ap                                                                      | propriate, of the relevant passages 17                                                                                                                                                                                                          | Relevant to Claim No. 18                                  |  |  |  |  |  |

| Х                                                                                                 | US,A,                                                                              | 4,162,451, Published ASH                                                                                          | d 24 JULY 1979,                                                                                                                                                                                                                                 | 1-7                                                       |  |  |  |  |  |

| X                                                                                                 | US,A,                                                                              | 4,237,487, Published<br>1980, IKEDA                                                                               | d 2 DECEMBER                                                                                                                                                                                                                                    | 1_7                                                       |  |  |  |  |  |

| Х                                                                                                 | US,A,                                                                              | 3,673,498, Published HARFORD                                                                                      | d 27 JUNE 1972                                                                                                                                                                                                                                  | 1-7                                                       |  |  |  |  |  |

| A                                                                                                 | US,A,                                                                              | 3,560,865, Published 1971, HARFORD                                                                                | d 2 FEBRUARY                                                                                                                                                                                                                                    |                                                           |  |  |  |  |  |

| * Special                                                                                         | categories of                                                                      | cited documents: 15                                                                                               |                                                                                                                                                                                                                                                 | -                                                         |  |  |  |  |  |

| "A" docur "E" earlie filing "L" docum to in "O" docum other                                       | ment defining r document is date nent cited for the other car ment referring means | the general state of the art out published on or after the international special reason other than those referred | "P" document published prior to the in on or after the priority date claims "T" later document published on or aff date or priority date and not in corbut cited to understand the principle the invention "X" document of particular relevance | er the international filing inflict with the application, |  |  |  |  |  |

|                                                                                                   | Actual Com                                                                         | pletion of the International Search 2                                                                             | Date of Mailing of this International Sec                                                                                                                                                                                                       | arch Report :                                             |  |  |  |  |  |

|                                                                                                   |                                                                                    | PY 1082                                                                                                           | 2 1 JAN 19                                                                                                                                                                                                                                      | ·                                                         |  |  |  |  |  |

|                                                                                                   | al Searching                                                                       |                                                                                                                   | Signature of Authorized Officer 20                                                                                                                                                                                                              |                                                           |  |  |  |  |  |

| TOI                                                                                               | 2/[]\                                                                              |                                                                                                                   | Richard Murray                                                                                                                                                                                                                                  | $\supset$ 1                                               |  |  |  |  |  |