(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5542643号

(P5542643)

(45) 発行日 平成26年7月9日(2014.7.9)

(24) 登録日 平成26年5月16日(2014.5.16)

(51) Int.Cl.

G06F 11/28 (2006.01)

F 1

G 06 F 11/28 3 4 O C

請求項の数 5 (全 16 頁)

(21) 出願番号 特願2010-275797 (P2010-275797)

(22) 出願日 平成22年12月10日 (2010.12.10)

(65) 公開番号 特開2012-123726 (P2012-123726A)

(43) 公開日 平成24年6月28日 (2012.6.28)

審査請求日 平成25年9月5日 (2013.9.5)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100099461

弁理士 溝井 章司

(74) 代理人 100122035

弁理士 渡辺 敏雄

(72) 発明者 外山 正勝

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 多賀 実

最終頁に続く

(54) 【発明の名称】シミュレーション装置及びシミュレーションプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

ターゲットとなるソフトウェアをシミュレーションするシミュレーション装置において、

前記ソフトウェアの命令を実行する命令セットシミュレータ部と、

前記命令セットシミュレータ部による前記命令の実行に応じて進行させる時刻であって、

実時間の進行による現実の時刻とは異なるシミュレーション時刻を進行させるシミュレーション時刻管理部と、

前記命令セットシミュレータ部の実行している前記命令がアイドル処理かどうかを判定するアイドル判定処理を実行するアイドル処理判定部と、

前記アイドル処理判定部によって、前記命令セットシミュレータ部の実行中の命令がアイドル処理と判定されると、前記シミュレーション時刻管理部の管理する前記シミュレーション時刻を前記アイドル処理の終了まで進行させる時間補正部とを備えたことを特徴とするシミュレーション装置。

## 【請求項 2】

前記シミュレーション装置は、さらに、

所定のイベントのシミュレーションの実行要求を通知する実行要求通知を受信すると、前記実行要求通知の通知する前記イベントのシミュレーションを実行し、前記イベントの前記シミュレーションの結果に応じて、前記命令セットシミュレータ部に割り込み要求を送信するイベントシミュレータ部と、

10

20

前記イベントシミュレータ部のシミュレーションするべき少なくとも一つのイベントであって、前記シミュレーション時刻を基準とする発生時刻を示すイベント発生時刻を持つイベントを管理すると共に、前記シミュレーション時刻管理部の管理する前記シミュレーション時刻を参照することにより前記イベントが前記発生時刻に達していると判断した場合には、前記発生時刻に達している前記イベントに関する前記実行要求通知を前記イベントシミュレータ部に通知するイベント管理部とを備え、

前記時間補正部は、

前記アイドル処理判定部によって、前記命令セットシミュレータ部の実行中の命令がアイドル処理と判定されると、前記イベント管理部の管理する前記イベントのうち次に発生するべき前記イベントの前記発生時刻を参照し、次に発生するべき前記イベントの前記発生時刻まで前記シミュレーション時刻管理部の管理する前記シミュレーション時刻を進行させることを特徴とする請求項1記載のシミュレーション装置。10

#### 【請求項3】

前記命令セットシミュレータ部は、

ジャンプ命令を実行したときに、前記アイドル処理判定部を呼び出し、

前記アイドル処理判定部は、

前記命令セットシミュレータ部に呼び出されたときに、前記アイドル判定処理を実行することを特徴とする請求項1または2のいずれかに記載のシミュレーション装置。

#### 【請求項4】

前記シミュレーション装置は、さらに、

実時間の進行による現実の時刻を管理すると共に、前記シミュレーション時刻管理部が進行させる前記シミュレーション時刻が前記現実の時刻よりも進んでいる場合には、前記命令セットシミュレータ部による前記ソフトウェアの命令の実行を一時停止させて、前記シミュレーション時刻管理部によって管理される前記シミュレーション時刻を前記現実の時刻に合わせる実時間調整部を備えたことを特徴とする請求項1～3のいずれかに記載のシミュレーション装置。20

#### 【請求項5】

ターゲットとなるソフトウェアをシミュレーションするシミュレーションプログラムにおいて、30

- (1) 前記ソフトウェアの命令を実行する処理と、

- (2) 前記命令の実行に応じて進行させる時刻であって、実時間の進行による現実の時刻とは異なるシミュレーション時刻を進行させる処理と、

- (3) 実行している前記命令がアイドル処理かどうかを判定する処理と、

- (4) 実行中の命令がアイドル処理と判定されると、前記シミュレーション時刻を前記アイドル処理の終了まで進行させる処理と、

- をコンピュータに実行させるためのシミュレーションプログラム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この発明は、例えば組込み装置で実行されるプログラムをシミュレーションする、シミュレーション装置及びシミュレーションプログラムに関する。

##### 【背景技術】

##### 【0002】

組込み装置のアーキテクチャ設計、動作検証、性能解析、ソフトウェア開発などを目的とし、組込み装置のハードウェアの持つ機能をソフトウェアでモデル化し、その上でターゲットソフトウェア131を実行するための仮想環境を提供する手段として、シミュレータがある。シミュレータは、シミュレーションの対象範囲、目的、ハードウェア機能をモデル化するときの抽象度や精度によって、多様な形態が存在する。そのなかの1つの形態として、ターゲットとなる組込み装置で使われるCPU用にコンパイル、リンクされたオ40

10

20

30

40

50

プロジェクトコードを、ターゲットとは異なる C P U で動作するホストコンピュータにおいて解釈し、メモリやレジスタの内容の変化を擬似的に再現する、命令セットシミュレータがある。命令セットシミュレータは、ターゲット C P U の命令列をそのまま実行可能であるため、ターゲットソフトウェア 131 の構成や処理内容に関与しない。そのため、実行すべき処理が無くなり C P U が空き状態となっている、C P U アイドル処理であっても、実際の C P U と同様に命令列の解釈、実行を行う。

C P U アイドル処理は、ジャンプ命令を繰り返し実行する、単純なループ処理で実現されることが多い。これに対し、特許文献 1 では、実行した命令列の履歴からループ処理を検出し、ループを規定回数繰り返した後のメモリやレジスタの内容を予測し、結果を反映することで、ループ回数分の命令実行を短縮する手段が開示されている。

10

#### 【先行技術文献】

##### 【特許文献】

##### 【0003】

【特許文献 1】特開平 8 - 69392 号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

コントローラのような入出力処理の完了が実時間で要求される組込み装置では、リアルタイムオペレーティングシステム（R T O S）が導入され、処理をタスクや割込みハンドラという単位で実行する。通常タスクや割込みハンドラは、ある決められた実時間制約（デッドライン）に確実に処理が完了するよう、最悪ケースでの実行時間で処理内容が設計される。そのため、通常ケースではマージン分は C P U アイドル処理となり、次の割込み事象を待つために時間を消費するための命令列を実行することになる。

20

##### 【0005】

C P U アイドル処理は、空き時間に実行される意味のない処理であるため、その命令列を忠実にシミュレーションしたとしても、意味のある演算結果は得られない。この意味のない命令実行に対しても、ホストコンピュータの C P U リソースが割り当てられ、一定の処理時間がかかる。従って、C P U アイドル処理のために C P U リソースを使わないようすれば、シミュレーション時間は短縮され、実行結果を早く得ることができる。

その 1 つの手段として、特許文献 1 では、ループに係る命令をスキップする方式が示されている。なお、C P U アイドル処理は、単純なループ処理で実現する他に、C P U コアを停止させて低消費電力状態に移行し待機する処理として実現する場合があり、その場合 C P U の命令実行は停止してしまうため、特許文献 1 に記載のループを短縮する手法は使えない。

30

##### 【0006】

ここで、C P U アイドル処理が解除される条件に注目すると、C P U に対し割込みなどの外部事象を与える必要があることがわかる。従って、本発明では、現在シミュレーション実行している命令の C P U アイドル処理の部分であることを検出する手段により、ターゲットソフトウェアが C P U アイドル処理の実行に遷移したことを検出した際に、次の入出力イベントが発生する時刻までシミュレータ内部の時間を強制的に進める。その結果、ターゲットソフトウェアでは、C P U アイドル処理に入った瞬間に次の割込みが発生し、C P U アイドル処理はキャンセルされ、割込みハンドラやタスク処理が実行される。これにより、C P U アイドル処理に係るシミュレーション時間を短縮すること目的とする。

40

##### 【課題を解決するための手段】

##### 【0007】

この発明のシミュレーション装置は、

ターゲットとなるソフトウェアをシミュレーションするシミュレーション装置において、

前記ソフトウェアの命令を実行する命令セットシミュレータ部と、

前記命令セットシミュレータ部による前記命令の実行に応じて進行させる時刻であって

50

、実時間の進行による現実の時刻とは異なるシミュレーション時刻を進行させるシミュレーション時刻管理部と、

前記命令セットシミュレータ部の実行している前記命令がアイドル処理かどうかを判定するアイドル判定処理を実行するアイドル処理判定部と、

前記アイドル処理判定部によって、前記命令セットシミュレータ部の実行中の命令がアイドル処理と判定されると、前記シミュレーション時刻管理部の管理する前記シミュレーション時刻を前記アイドル処理の終了まで進行させる時間補正部とを備えたことを特徴とする。

**【発明の効果】**

**【0008】**

10

この発明により、ターゲットとなるソフトウェアをシミュレーションするシミュレーション装置において、CPUアイドル処理となるシミュレーション時間を短縮するシミュレーション装置を提供できる。

**【図面の簡単な説明】**

**【0009】**

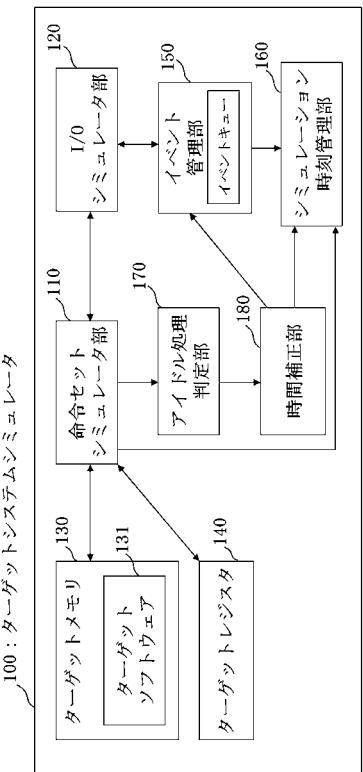

【図1】実施の形態1におけるターゲットシステムシミュレータ100のブロック図。

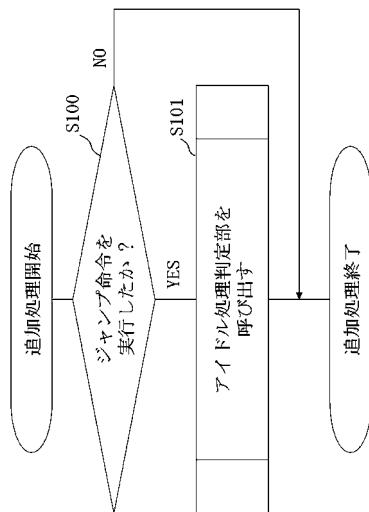

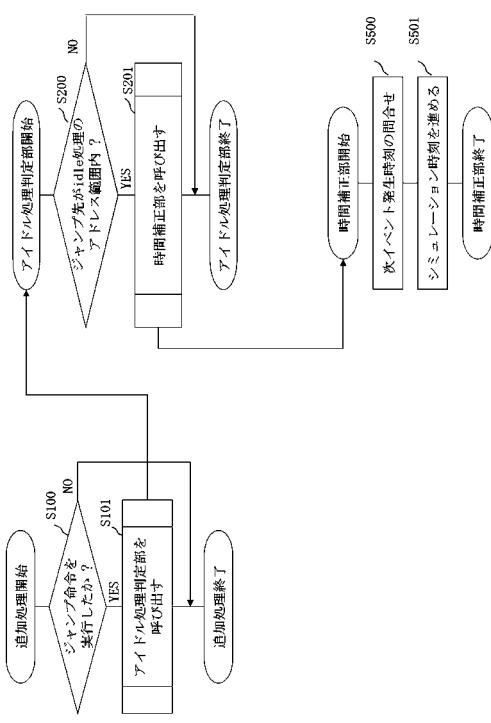

【図2】実施の形態1における命令セットシミュレータ部110のフローチャート。

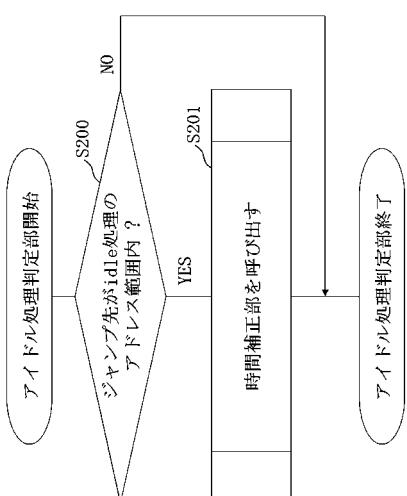

【図3】実施の形態1におけるアイドル処理判定部170のフローチャート。

【図4】実施の形態1における時間補正部180のフローチャート。

【図5】図2、図3、図4を連結した図。

20

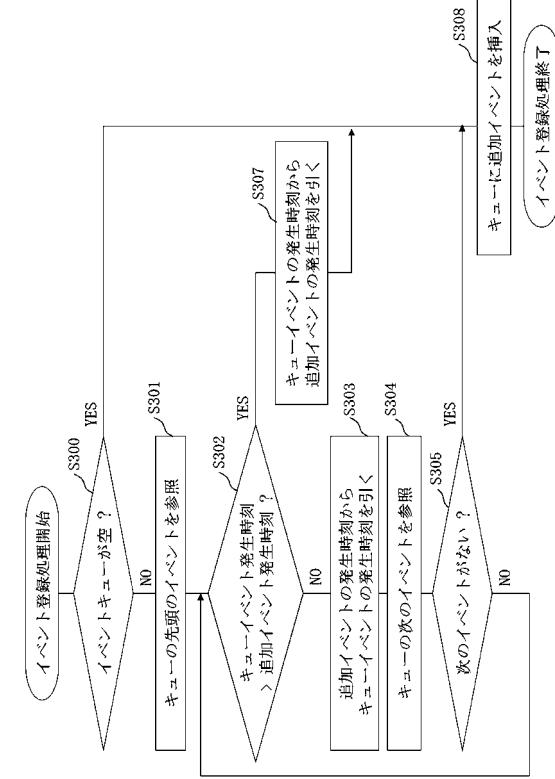

【図6】実施の形態1におけるI/Oシミュレータ部120によるイベント管理部150への登録処理を示すローチャート。

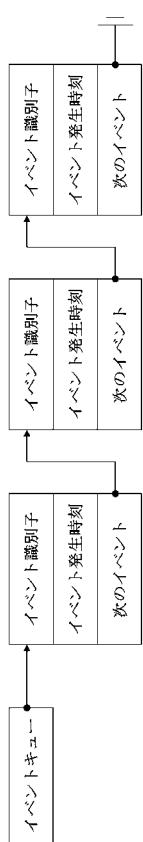

【図7】実施の形態1におけるイベント管理部150のもつイベントキューを示す図。

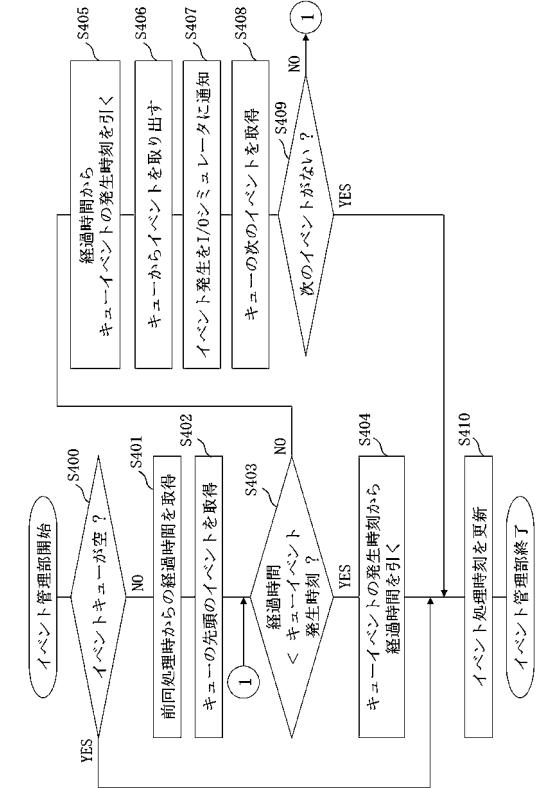

【図8】実施の形態1におけるイベント管理部150によるイベント処理動作を示すフローチャート。

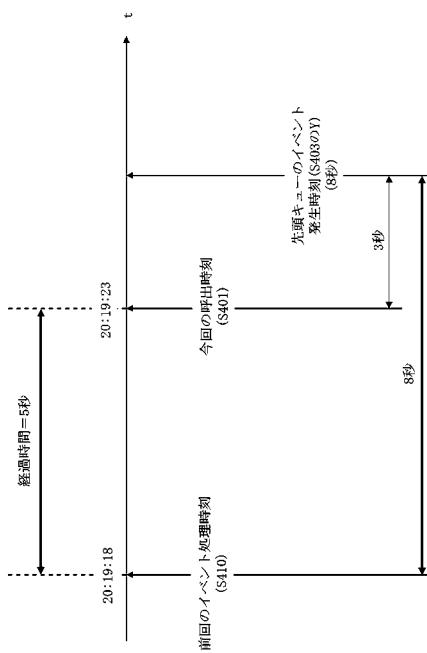

【図9】実施の形態1におけるイベント管理部150のイベント処理動作を説明する図。

【図10】実施の形態1におけるイベント管理部150のイベント処理動作を説明する図。

【図11】実施の形態1における効果を示す図。

【図12】実施の形態2におけるターゲットシステムシミュレータ100-2のブロック図。

30

【図13】実施の形態2における実時間調整部190のフローチャート。

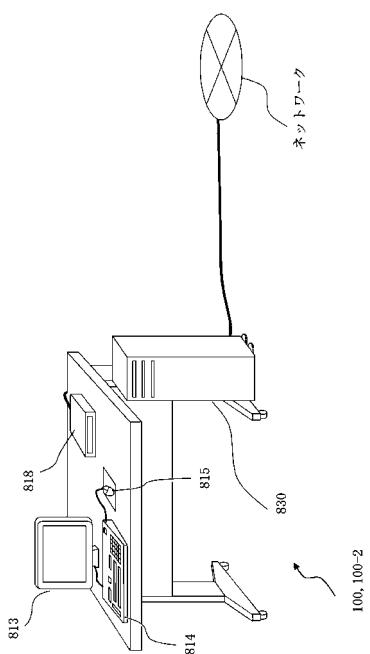

【図14】実施の形態3におけるターゲットシステムシミュレータを実行する計算機の外観。

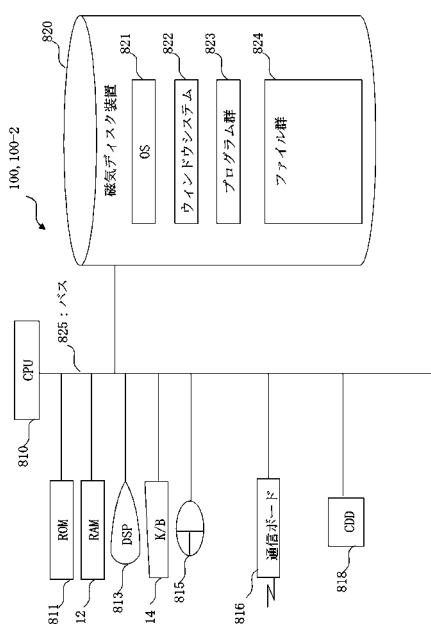

【図15】実施の形態3におけるターゲットシステムシミュレータを実行する計算機のハードウェア構成。

**【発明を実施するための形態】**

**【0010】**

実施の形態1.

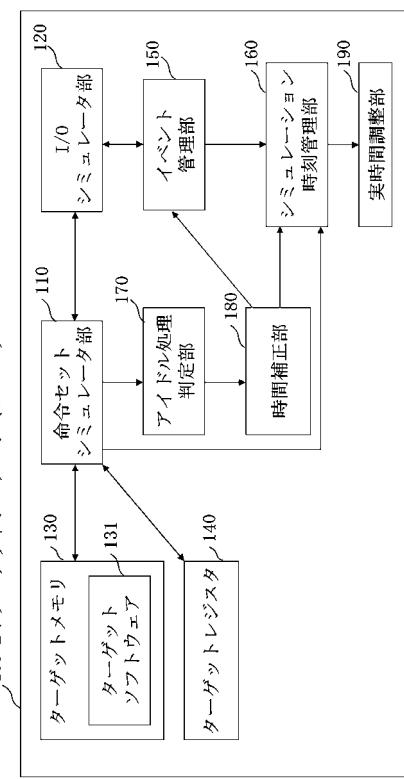

図1は、実施の形態1におけるターゲットシステムシミュレータ100の構成を示している。ターゲットシステムシミュレータ100は、ターゲットである組込み装置をソフトウェアで模擬した装置である。ターゲットシステムシミュレータ100は、CPU命令をシミュレーションする命令セットシミュレータ部110と、周辺装置の割込みや入出力をシミュレーションするI/Oシミュレータ部120(イベントシミュレータ)と、ターゲットメモリ130と、ターゲットレジスタ140と、イベント管理部150、シミュレーション時刻管理部160、アイドル処理判定部170、時間補正部180を備える。

**【0011】**

ターゲットメモリ130は、ターゲットのメモリ内容を再現し保持する。また、ターゲットレジスタ140は、ターゲットのレジスタ内容を再現し保持する。ターゲットシステムシミュレータ100で実行するターゲットソフトウェア131は、ターゲットメモリ1

40

50

30にロードされる。

#### 【0012】

命令セットシミュレータ部110は、ターゲットメモリ130からターゲットソフトウェア131の命令コードを取り出し、解釈、実行する。その際、ターゲットレジスタ140、ターゲットメモリ130およびI/Oシミュレータ部120に対し、その命令の演算結果を反映する。

#### 【0013】

I/Oシミュレータ部120は、CPU以外の周辺装置の機能をソフトウェアでモデル化したものである。I/Oシミュレータ部120は、命令セットシミュレータ部110からの入出力要求に対応してデータを供給する他に、仕様により規定されるタイミングで、命令セットシミュレータ部110に対し割込み要求を出す。10

#### 【0014】

この割込みの発生や入出力の変化をイベントとして、イベント管理部150は、イベントの発生タイミングを管理する。イベント管理部150は、シミュレーション時刻管理部160が管理するシミュレーション時刻に従って、イベントの発生タイミングを把握する。。

#### 【0015】

シミュレーション時刻管理部160が管理するのは、シミュレーション実行にかかっている実時間ではなく、シミュレーションのターゲットとなっているシステム内で進行し把握される時間である。例えば、実際の組込み装置上で10000命令実行するのに1ミリ秒かかるており、シミュレータで10000命令実行するのに10ミリ秒かかっていたとする。このとき、実時間では10ミリ秒の時間が経過していたとしても、ターゲットの内部状態は1ミリ秒相当分しか進行していないため、シミュレーション時刻は1ミリ秒となる。シミュレーション時刻は、命令セットシミュレータ部110が命令をシミュレーション実行した結果、その命令実行にかかるマシンサイクル数をシミュレーション時刻管理部160に通知し、シミュレーション時刻管理部160は通知されたマシンサイクルに相当する時間を進める。20

#### 【0016】

アイドル処理判定部170は、実行中のターゲットソフトウェア131がアイドル状態に遷移しているかどうかを判定する手段である。アイドル処理判定部170は、アイドル状態を検出した場合は、時間補正部180に対し、シミュレーション時刻を進めるよう要求する。30

#### 【0017】

時間補正部180は、イベント管理部150に対して次のイベントが発生するまでの時間を問い合わせ、その結果をもとにシミュレーション時刻管理部160に対し時間を強制的に進める要求を出す。

#### 【0018】

(動作の説明)

次に動作について説明する。

図2は、命令セットシミュレータ部110に追加する処理内容を示したフローチャートである。40

図3は、アイドル処理判定部170の処理内容を示したフローチャートである。

図4は、時間補正部180のフローチャートを示す。

図5は、図2、図3、図4の関係を示した。

#### 【0019】

命令セットシミュレータ部110は、通常は、CPUの命令フェッチ、デコード、データフェッチ、命令実行、結果格納の、5つの実行ステージを機能単位とし、プログラムカウンタを進めながら1命令につき1ループ回してシミュレーション実行を進めていく。図2に示す追加処理は、結果格納ステージの後に追加する。S100では、命令セットシミュレータ部110は、今回の実行ループで実行した命令の種別を判定する。もしジャンプ

50

命令を実行していた場合は、S 1 0 1 でアイドル処理判定部 1 7 0 を呼び出す。

#### 【0020】

図3に示すように、S 2 0 0 では、アイドル処理判定部 1 7 0 は、実行したジャンプ命令のジャンプ先のアドレスが、ターゲットソフトウェア 1 3 1 の C P U アイドル処理の命令コードが配置してあるアドレスの範囲内にあるかどうかを判定する。C P U アイドル処理のアドレスは、シンボル情報から取得することができる。もしジャンプ先が C P U アイドル処理であることを検出した場合は、アイドル処理判定部 1 7 0 は、S 2 0 1 で時間補正部 1 8 0 を呼び出す。

#### 【0021】

図4は、時間補正部 1 8 0 の処理を表すフローチャートを示している。

10

なお、イベント管理部 1 5 0 の管理するイベントキュー、イベント発生時刻については、図6～図8の説明で後述する。

S 5 0 0 では、時間補正部 1 8 0 は、イベント管理部 1 5 0 が管理しているイベントキューを参照し、次のイベント発生時刻を取得する。イベントがなにも登録されていなければ0とする。次に、S 5 0 1 では、時間補正部 1 8 0 は、シミュレーション時刻管理部 1 6 0 に対し、S 5 0 0 で取得した次のイベント発生時刻をシミュレーション時刻に加算するよう要求する。この結果、次回のイベント管理部 1 5 0 の定期処理において、必ずイベントが発生することになる。これにより割込みが発生すれば、ターゲットソフトウェア 1 3 1 は C P U アイドル処理を即座に抜け出し、割込みハンドラ処理を実行する。

#### 【0022】

20

図6は、I / O シミュレータ部 1 2 0 が、割込み等の C P U の命令実行に対して非同期に発生する入出力事象を実現するために、その事象に対応するイベント（イベント識別子）を発生タイミング（イベント発生時刻）と共に、イベント管理部 1 5 0 に登録する処理を示したフローチャートである。本処理は、I / O シミュレータ部 1 2 0 内で行われる割込み処理等に対応するイベント識別子と、その発生時刻（追加イベント発生時刻）とをパラメータとして呼び出される。なお、イベント発生時刻（後述する図5に記載）は、実時間ではなくシミュレーション時刻を基準とし、現在からどれだけ時間が経過した後にイベントを通知するかを、相対時間で指定するものである。

#### 【0023】

30

図7は、イベント管理部 1 5 0 の有するイベントキューの構造を示す図である。図6の動作の主体は、I / O シミュレータ部 1 2 0 である。最初に S 3 0 0 では、I / O シミュレータ部 1 2 0 は、図7の構造のイベントキューを調べ、既にイベントが登録されているか確認する。イベントキューは、イベントを管理する個々の構造体要素をポインタで繋いだものである。イベント発生時刻は、ひとつ手前の構造体要素からの経過時間が格納される。最終要素のポインタは N U L L となっている。イベントが何も登録されていない場合は、イベントキュー自体が N U L L になる。従って、I / O シミュレータ部 1 2 0 はイベントキューが N U L L であれば、S 3 0 8 でキューにイベント要素を追加する。それ以外は S 3 0 1 に進む。S 3 0 1 では、イベントキューの先頭要素を参照し、イベント識別子とイベント発生時刻（キューイベント発生時刻）を取得する。S 3 0 2 では、キューイベント発生時刻と追加イベント発生時刻の値を比較する。キューイベント発生時刻の方が大きければ、キューイベント発生時刻から追加イベント発生時刻を引き、S 3 0 8 でキューイベントの要素の手前に追加イベントの要素を挿入する。追加イベント発生時刻の方が大きければ、S 3 0 3 で追加イベント発生時刻からキューイベント発生時刻を引き、S 3 0 4 でキューイベントの次の要素を参照する。そして、S 3 0 5 でイベント要素が終端の N U L L であるかチェックし、N U L L であれば S 3 0 8 でその手前（キューの最後）に追加イベントの要素を挿入する。次のイベント要素がある場合は、S 3 0 2 に戻り、同様の処理を繰り返すことにより、イベントが発生する順番にソートされ、さらに各イベント要素は手前のイベント発生時点からの経過時間で管理されるようになる。

40

#### 【0024】

図8は、イベント管理部 1 5 0 が、命令セットシミュレータ部 1 1 0 から定期的に呼ば

50

れて、イベントの発生有無をチェックする処理を表すフローチャートである。図8の動作の主体は、イベント管理部150である。

また図9、図10は、図8を説明するための図である。図9、図10を参照しながら図8を説明する。

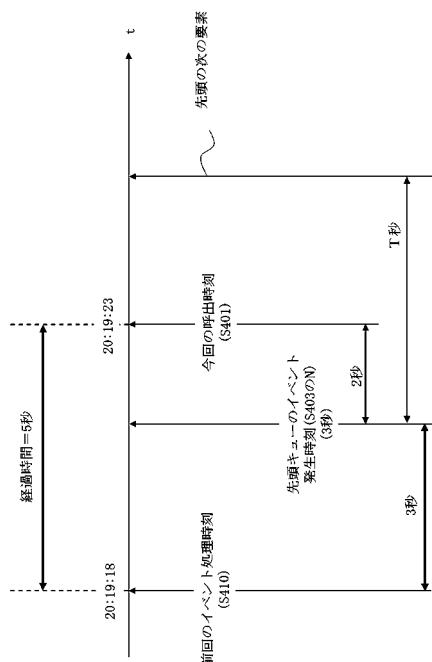

#### 【0025】

S400で、イベント管理部150は、図7のイベントキューの要素を調べ、NULLであれば、S410で、シミュレーション時刻管理部160によって管理している現在のシミュレーション時刻を参照し、イベント処理時刻として内部に保存した後、処理を終了する。

イベント要素があれば、S401に進む。以下では説明のためにシミュレーション時刻を用いて説明するが説明の便宜のため、時間の単位は「秒」とした。 10

#### 【0026】

S401では、シミュレーション時刻管理部160によって管理している現在のシミュレーション時刻(20:19:23)を参照するとともに、

S410にて保存されている前回処理した時刻を示すイベント処理時刻(20:19:18)を取得し、その差分によって経過時間(23 - 18 = 5秒)を算出する。

S402でイベントキューの先頭要素を参照し、S403ではS401で求めた経過時間とキューイベント発生時刻を比較する。なお、前述のようにイベント発生時刻はひとつ手前の構造体要素(言い換えれば前回のイベント処理時刻(S410))からの経過時間であるので、経過時間とイベント発生時刻との比較が可能である。 20

#### 【0027】

##### (経過時間 < イベント発生時刻の場合)

図9に示すように経過時間(5秒)のほうが小さければ(例えばイベント発生時刻が8秒とする)、S404でキューイベント発生時刻(8秒)から経過時間(5秒)を引いて3秒を算出し、取得したイベントキューのイベント発生時刻を算出した差分(3秒)に書き換える。その後、S410に進み、イベント処理時刻を取得した現在の時刻(20:19:23)に更新する。すなわち、取得した次回発生すべきイベントの発生時刻を差分(3秒)に書き換えることは、更新された現在の時刻(20:19:23)からのイベント発生時刻としたことを意味する。

#### 【0028】

##### (経過時間 > イベント発生時刻の場合)

図10はキューイベント発生時刻の方が小さい場合を示す。図10に示すように、経過時間(5秒)よりも、キューイベント発生時刻(3秒とする)の方が小さいか同じであれば、イベント発生時刻が経過していることになる。このため、イベント管理部150は、S405以降のイベント通知処理に進む。

S405では、経過時間(5秒)からキューイベント発生時刻(3秒)を引いておく。そして、図10に示すように、得られた差分(2秒)だけ、次のイベント発生時刻からを差し引いておく。これは、この後にS410に進んだときに、イベント処理時刻を取得した現在の時刻(20:19:23)に更新するので、現在の時刻(20:19:23)を基準に次回のイベント(「T - 2」秒後)を発生させるためである。 40

S406では、ポインタを操作することによって該当キューイベント要素(イベント発生時刻に到達した要素)をイベントキューの接続構造から削除し、

S407では、該当キューイベントのイベント識別子(実行要求通知の一例)をI/Oシミュレータ部120に送信することで、指定されたイベントの発生時刻となったことを知らせる。この処理に対応し、I/Oシミュレータ部120では、イベント識別子に対応するイベントのシミュレーションが行われ、その結果割込みの要求が発生した場合は、命令セットシミュレータ部110に対し割込み要求を出力することになる。

S408では、イベント管理部150は、キューイベントの次の要素を参照し、

S409で次のイベント要素がないと判断されれば(S409のNO)、S410(取得した現在のシミュレーション時刻に更新する処理)に進む。次のイベント要素があれば 50

、S 4 0 3 に戻り、同様の処理を繰り返す。

#### 【0029】

本実施の形態 1 によれば、C P U アイドル処理から抜け出すきっかけとなる割込みの発生が早められる。このため、C P U アイドル処理として実行されるはずの命令列のシミュレーションがスキップされ、その結果、シミュレーションにかかる実時間が削減される。また、C P U アイドル処理の命令列を操作するものではないため、C P U アイドル処理が単純なビギループ処理で実現されていても、または消費電力を低減するためにC P U スリープ命令でC P U の動作自体を停止する処理で実現されていても適用可能である。

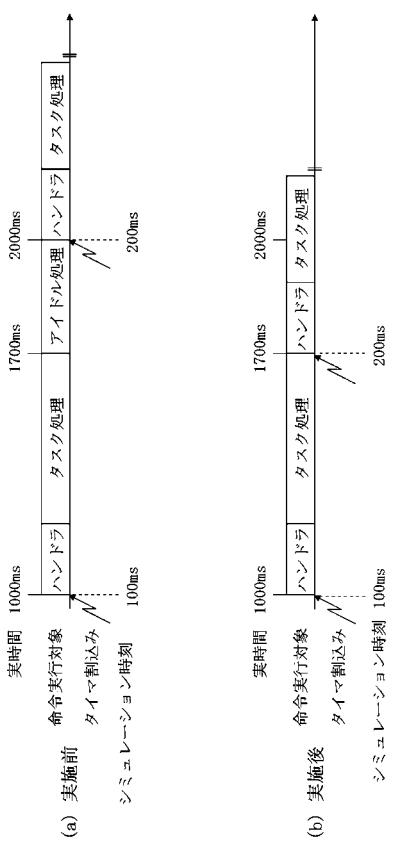

図 1 1 の ( a ) はターゲットシステムシミュレータ 1 0 0 の方式を適用しない場合（実施前）を示し、( b ) はターゲットシステムシミュレータ 1 0 0 の方式を適用する場合（実施後）を示す図である。図 1 1 に示すように、1 0 0 m s 間隔で発生するタイマ割込みに対応してハンドラが起動され、そこからタスク処理が行われた後、C P U アイドル状態に遷移する処理モデルとなっている。シミュレーション実行速度はターゲットの組込み装置の実行速度の 1 / 1 0 、つまりシミュレーション時間は 10 倍かかるものとする。本実施の形態 1 の方式を適用しない ( a ) の場合は、実時間 1 7 0 0 m s の時点から C P U アイドル処理となり、実時間 2 0 0 0 m s の時点で割込みが発生することで C P U アイドル処理を抜け出し、次の周期処理を行っている。一方、本実施の形態 1 を適用する ( b ) の場合は、C P U アイドル処理に入るはずの 1 7 0 0 m s の時点で、シミュレーション時刻を強制的に進めてしまうため、即座に割込みが発生し、次の周期処理が実行される。この例では、この周期処理を実行するためにかかるシミュレーションの実時間を 3 0 0 m s 削減できている。

#### 【0030】

実施の形態 2 。

図 1 2 、図 1 3 を参照して実施の形態 2 を説明する。

図 1 1 は、実施の形態 2 におけるターゲットシステムシミュレータ 1 0 0 - 2 の機能構成を示している。図 1 との違いは、図 1 2 では実時間調整部 1 9 0 を有する点である。シミュレーション時刻管理部 1 6 0 がシミュレーション時刻を進める際に呼び出された場合に、実時間調整部 1 9 0 は、シミュレーション時刻が実時間よりも進んでいる場合にシミュレーション時刻を実時間に合わせるために、ターゲットシステムシミュレータ 1 0 0 - 2 が実行されているホストコンピュータの C P U リソースを解放する機能を持つ。

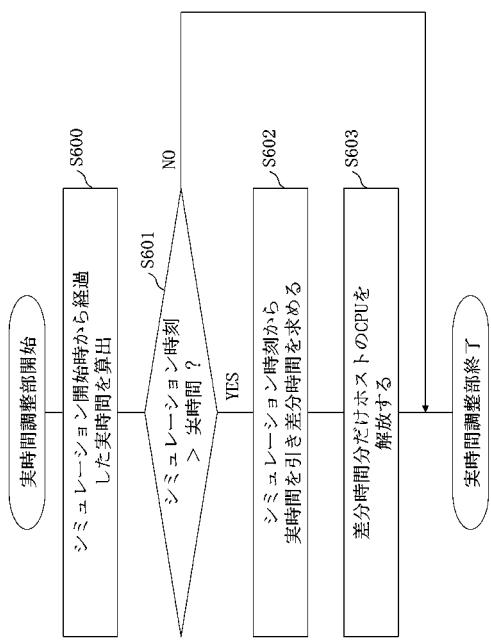

#### 【0031】

次に動作について説明する。

図 1 3 は、実施の形態 2 で追加された実時間調整部 1 9 0 の処理内容を示したフローチャートである。

最初に S 6 0 0 では、シミュレーション実行を開始してから経過した「実時間」を算出する。時間情報は、ホストコンピュータのタイマを、ホストコンピュータ上で動作している O S の A P I によって参照して取得する。起点となる実時間は、シミュレーション実行開始時に内部情報として保持されている。

次に S 6 0 1 で、シミュレーション時刻管理部 1 6 0 で管理されているシミュレーション時刻と、S 6 0 0 で算出した実時間を比較する。高速な C P U を備えるホストコンピュータ上において低速な C P U を備えるターゲットの組込み装置をシミュレーションする場合、シミュレーション実行の速度が実際のターゲットの組込み装置の実行速度よりも早くなる場合がある。また、C P U アイドル処理に相当する時間をスキップしたことにより、シミュレーション時刻が実時間を追い越す場合がある。以上のような場合には、シミュレーション時刻の方が実時間よりも大きくなるため、そのときは S 6 0 2 以降の処理を実行する。

S 6 0 2 では、進んでいるシミュレーション時刻から実時間を引いて、相対的な差分時間を算出する。

そして S 6 0 3 では、ホストコンピュータの O S の A P I によって「差分時間の分だけ」シミュレータのプロセス、あるいはスレッドを停止させる。これにより、ターゲットシ

10

20

30

40

50

システムシミュレータ 100 - 2 によるホストコンピュータの CPU リソースの使用を放棄する。すなわち、シミュレーション時刻と実時間が一致したとき、シミュレータの実行が再開される。

#### 【0032】

本実施の形態 2 によれば、ターゲットの組込み装置が待機状態の時などの処理負荷が低い状態をシミュレーションする場合に、CPU アイドル処理の命令実行をスキップするためにシミュレーション時刻を強制的に進めるとともに、実時間に比べて進みすぎた時間分だけホストコンピュータの CPU リソースを解放する。このため、シミュレーション実行時のホストコンピュータの処理負荷を下げる、他のアプリケーション（例えばエディタ）の実行により多くの CPU リソースを割り当てることが可能となる。10 シミュレーションの方法としては、できるだけ早く結果を得るためにホストコンピュータの CPU リソースを占有して処理を行う場合と、ターゲットの組込み装置と同じタイミングで動作を確認したい場合とがあり、本実施例は後者をより低負荷、より効率的に実現するものである。

#### 【0033】

実施の形態 3 。

図 14、図 15 を参照して実施の形態 3 を説明する。実施の形態 3 は、コンピュータであるターゲットシステムシミュレータ 100、100 - 2 のハードウェア構成を説明する。20

図 14 は、コンピュータであるターゲットシステムシミュレータの外観の一例を示す図である。20

図 15 は、ターゲットシステムシミュレータのハードウェア資源の一例を示す図である。

#### 【0034】

外観を示す図 14において、ターゲットシステムシミュレータは、システムユニット 830、CRT (Cathode-Ray-Tube) や LCD (液晶) の表示画面を有する表示装置 813、キーボード 814 (Key-Board: K/B)、マウス 815、コンパクトディスク装置 818 (CDD: Compact Disk Drive) などのハードウェア資源を備え、これらはケーブルや信号線で接続されている。システムユニット 830 はネットワークに接続している。30

#### 【0035】

またハードウェア資源を示す図 15において、ターゲットシステムシミュレータは、プログラムを実行する CPU 810 (Central Processing Unit) を備えている。CPU 810 は、バス 825 を介して ROM (Read Only Memory) 811、RAM (Random Access Memory) 812、表示装置 813、キーボード 814、マウス 815、通信ボード 816、CDD 818、磁気ディスク装置 820 と接続され、これらのハードウェアデバイスを制御する。磁気ディスク装置 820 の代わりに、光ディスク装置、フラッシュメモリなどの記憶装置でもよい。30

#### 【0036】

RAM 812 は、揮発性メモリの一例である。ROM 811、CDD 818、磁気ディスク装置 820 等の記憶媒体は、不揮発性メモリの一例である。これらは、「記憶装置」あるいは記憶部、格納部、バッファの一例である。通信ボード 816、キーボード 814 などは、入力部、入力装置の一例である。また、通信ボード 816、表示装置 813 などは、出力部、出力装置の一例である。通信ボード 816 は、ネットワークに接続されている。40

#### 【0037】

磁気ディスク装置 820 には、オペレーティングシステム 821 (OS)、ウィンドウシステム 822、プログラム群 823、ファイル群 824 が記憶されている。プログラム群 823 のプログラムは、CPU 810、オペレーティングシステム 821、ウィンドウシステム 822 により実行される。

#### 【0038】

50

20

30

40

50

上記プログラム群 823 には、以上の実施の形態の説明において「～部」として説明した機能を実行するプログラムが記憶されている。プログラムは、C P U 810 により読み出され実行される。

#### 【 0039 】

ファイル群 824 には、以上の実施の形態の説明において、「～の判定結果」、「～の算出結果」、「～の抽出結果」、「～の生成結果」、「～の処理結果」として説明した情報や、データや信号値や変数値やパラメータなどが、「～ファイル」や「～データベース」の各項目として記憶されている。「～ファイル」や「～データベース」は、ディスクやメモリなどの記録媒体に記憶される。ディスクやメモリなどの記憶媒体に記憶された情報やデータや信号値や変数値やパラメータは、読み書き回路を介して C P U 810 によりメインメモリやキャッシュメモリに読み出され、抽出・検索・参照・比較・演算・計算・処理・出力・印刷・表示などの C P U の動作に用いられる。抽出・検索・参照・比較・演算・計算・処理・出力・印刷・表示の C P U の動作の間、情報やデータや信号値や変数値やパラメータは、メインメモリやキャッシュメモリやバッファメモリに一時的に記憶される。10

#### 【 0040 】

また、以上に述べた実施の形態の説明において、データや信号値は、R A M 812 のメモリ、C D D 818 のコンパクトディスク、磁気ディスク装置 820 の磁気ディスク、その他光ディスク、ミニディスク、D V D ( D i g i t a l · V e r s a t i l e · D i s k ) 等の記録媒体に記録される。また、データや信号は、バス 825 や信号線やケーブルその他の伝送媒体によりオンライン伝送される。20

#### 【 0041 】

また、以上の実施の形態の説明において、「～部」として説明したものは、「～手段」、であってもよく、また、「～ステップ」、「～手順」、「～処理」であってもよい。すなわち、「～部」として説明したものは、ソフトウェアのみ、或いは、ソフトウェアとハードウェアとの組み合わせ、さらには、ファームウェアとの組み合わせで実施されても構わない。ファームウェアとソフトウェアは、プログラムとして、磁気ディスク、フレキシブルディスク、光ディスク、コンパクトディスク、ミニディスク、D V D 等の記録媒体に記憶される。プログラムは C P U 810 により読み出され、C P U 810 により実行される。すなわち、プログラムは、以上に述べた「～部」としてコンピュータを機能させるものである。あるいは、以上に述べた「～部」の手順や方法をコンピュータに実行せるものである。30

#### 【 0042 】

以上の実施の形態では、シミュレーション装置としてのターゲットシステムシミュレータを説明したが、のターゲットシステムシミュレータはシミュレーションプログラムとしても把握できることは以上の説明から当然である。

#### 【 0043 】

以上の実施の形態では以下を特徴とするシミュレーション装置を説明した。

( 1 ) ターゲットシステムシミュレータ 100 は、ターゲットの組込み装置のハードウェア構成をソフトウェアで実現したもので、ターゲットの組込み装置用にコンパイル、リンクされたターゲットソフトウェア 131 の C P U 命令コードを解釈し実行する命令セットシミュレータ部 110 と、ターゲットの組込み装置のハードウェア仕様に従って命令セットシミュレータ部 110 に対して割込みや入出力を仮想的に発生させる I / O シミュレータ部 120 との組み合わせによって成り立っている。40

( 2 ) 命令セットシミュレータ部 110 がターゲットソフトウェア 131 の C P U 命令コードに従い操作する対象となるターゲットメモリ 130 とターゲットレジスタ 140 を備え、ターゲットソフトウェア 131 はターゲットメモリ 130 内にロードされている。

( 3 ) I / O シミュレータ部 120 の割込みや入出力をイベントとして一元管理するイベント管理部 150 と、イベントの発生タイミングを把握するためのシミュレーション時刻管理部 160 を備える。50

(4) 命令セットシミュレータ部 110 が実行中の命令コードが C P U アイドル処理に含まれるものか判別するアイドル処理判定部 170 と、C P U アイドル処理を検出した場合にシミュレーション時刻を強制的に進める時間補正部 180 を備える。

(5) ホストコンピュータのアプリケーションとしてターゲットシミュレータは実行される。

#### 【0044】

以上の実施の形態では以下を特徴とするシミュレーション装置を説明した。

(1) 命令セットシミュレータ部 110 がジャンプ命令を実行した際に、アイドル処理判定部 170 を呼び出す。

(2) 命令セットシミュレータ部 110 で実行しているターゲットソフトウェア 131 の C P U 命令コードが C P U アイドル処理に含まれることをアイドル処理判定部 170 が検出した場合、時間補正部 180 によってイベント管理部 150 に登録されているイベントで最も早いタイミングで発生するものの発生時刻まで、シミュレーション時刻管理部 160 で管理しているシミュレーション時刻を強制的に進める。 10

#### 【0045】

以上の実施の形態では以下を特徴とするシミュレーション装置を説明した。

(1) シミュレーション時刻と実時間を合わせるためにターゲットシステムシミュレータ 100 の動作 / 停止状態を制御する実時間調整部 190 を備える。

#### 【0046】

以上の実施の形態では以下を特徴とするシミュレーション装置を説明した。 20

シミュレーション時刻が実時間よりも進んでいる場合に、実時間調整部 190 によって進行している差分時間分だけターゲットシステムシミュレータ 100 の実行を停止させ、ホストコンピュータの C P U リソースを解放する。

#### 【符号の説明】

#### 【0047】

100, 100 - 2 ターゲットシステムシミュレータ、110 命令セットシミュレータ部、120 I/O シミュレータ部、130 ターゲットメモリ、131 ターゲットソフトウェア、140 ターゲットレジスタ、150 イベント管理部、160 シミュレーション時刻管理部、170 アイドル処理判定部、180 時間補正部、190 時間調整部。 30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開2001-154881(JP,A)

特開2000-010813(JP,A)

特開平7-160537(JP,A)

特開2010-113619(JP,A)

特開2003-186936(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 455

G 06 F 11 / 28

G 06 F 19 / 00