# MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102010901897487 |

|------------------------------|-----------------|

| Data Deposito                | 10/12/2010      |

| Data Pubblicazione           | 10/06/2012      |

Classifiche IPC

Titolo

MODIFICA DELLO STATO DI RESET PER AUMENTARE IL MARGINE DI LETTURA DI UNA MEMORIA A CAMBIAMENTO DI FASE Descrizione dell'Invenzione Industriale dal titolo: -POL005-

# "MODIFICA DELLO STATO DI RESET PER AUMENTARE IL MARGINE DI LETTURA DI UNA MEMORIA A CAMBIAMENTO DI FASE"

Del Politecnico di Milano, di nazionalità Italiana, con sede in Piazza L. da Vinci, 32 - 20133 Milano, codice fiscale 80057930150 ed elettivamente domiciliata, ai fini del presente incarico, presso i Mandatari Ing. Marco CAMOLESE (Iscr. Albo No. 882BM), Ing. Antonio DI BERNARDO (Iscr. Albo No. 1163BM), Ing. Andrea GRIMALDO (Iscr. Albo No. 1060BM) e Dott. Giancarlo REPOSIO (Iscr. Albo No. 1168BM), c/o Metroconsult S.r.l., Foro Buonaparte 51, 20121 Milano.

# Inventori designati:

- Daniele IELMINI

- Mattia BONIARDI

- Andrea REDAELLI

- Agostino PIROVANO

- Fabio PELLIZZER

Depositata il No.

\* \* \* \* \*

# DESCRIZIONE

#### ARTE NOTA

# Campo della tecnica:

L'argomento divulgato qui di seguito riguarda le tecniche che coinvolgono un fenomeno di rilassamento strutturale

(SR) per produrre una maggiore resistenza di uno stato di reset della memoria a cambiamento di fase.

#### Informazione:

Le memorie a cambiamento di fase (PCM) possono operare sulla base, almeno in parte, dei comportamenti e delle proprietà di uno o più particolari materiali a cambiamento di fase, come i vetri calcogenuri e / o il tellururo di germanio antimonio (GST), solo per citare alcuni esempi. Gli stati cristallino e amorfo di tali materiali hanno differenti resistività elettriche, offrendo in tal modo per l'immagazzinamento dell'informazione digitale. Lo stato amorfo, alto resistivo, rappresentare un primo stato binario memorizzato e lo stato cristallino, basso resistivo, può rappresentare un secondo stato binario memorizzato. Naturalmente, una tale rappresentazione binaria dell'informazione memorizzata costituisce solo un mero esempio: la memoria PCM può anche essere utilizzata per memorizzare stati multilivello, rappresentati ad esempio dai diversi livelli di resistività del materiale a cambiamento di fase.

La ricerca sui materiali alternativi a cambiamento di fase ne sta migliorando le proprietà in termini di affidabilità e prestazioni e ha condotto a studi su varie leghe e composizioni ottenute da un diagramma ternario GeSbTe, per esempio. Anche se certe composizioni possono

effettivamente indurre tale maggiore affidabilità e/o prestazioni, il margine di resistenza, o finestra di programmazione, tra gli stati di set e reset potrebbe essere al contrario ridotto rispetto ai margini di altri materiali a cambiamento di fase. Tale riduzione della finestra di programmazione può portare ad un margine di lettura più stretto tra gli stati di set e reset. Una memoria PCM con una ridotta finestra di programmazione può incorrere in un maggiore numero di errori di lettura rispetto ad una PCM avente una finestra di programmazione più ampia.

#### BREVE DESCRIZIONE DELLE FIGURE

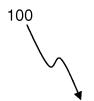

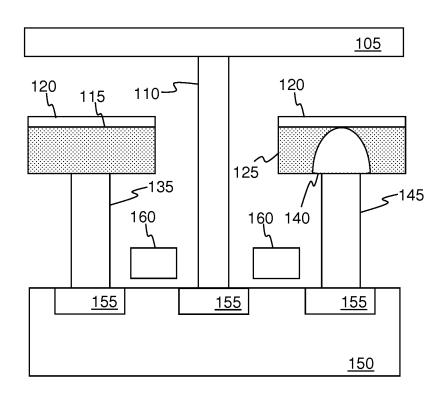

Una realizzazione non limitante e non esaustiva descritta con riferimento alle sequenti figure, in cui i numeri di riferimento si riferiscono alle parti indicate nelle varie figure non diversamente specificato. se FIG. 1 è un diagramma schematico di una parte della memoria a cambiamento di fase, secondo una realizzazione. FIG. 2 è un diagramma di stato che mostra le possibili più valori transizioni tra due e/o di resistenza corrispondenti a stati logici di una cella PCM, secondo una realizzazione.

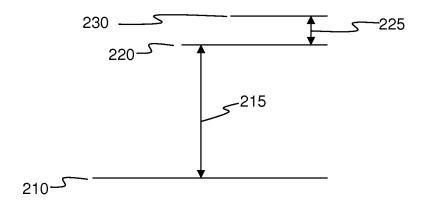

FIG. 3 è un grafico della resistenza di una cella di memoria in funzione della durata del fronte di discesa (TET), secondo una realizzazione.

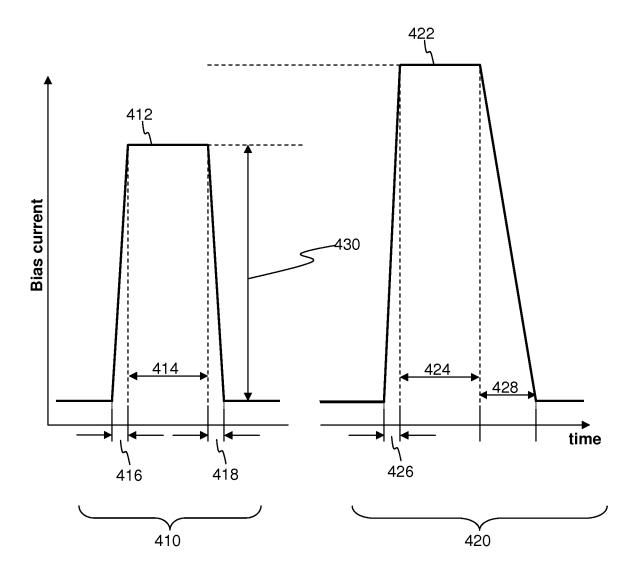

FIG. 4 è un grafico delle caratteristiche di una forma d'onda di segnale di programmazione, secondo una realizzazione.

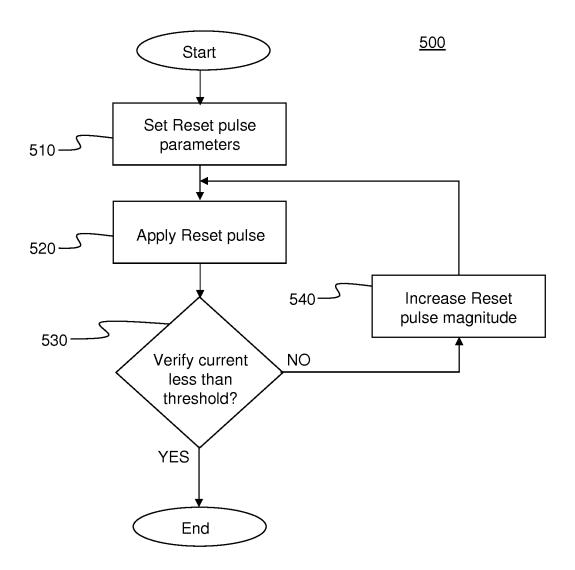

FIG. 5 è un diagramma di flusso di una procedura di programmazione – verifica, secondo una realizzazione.

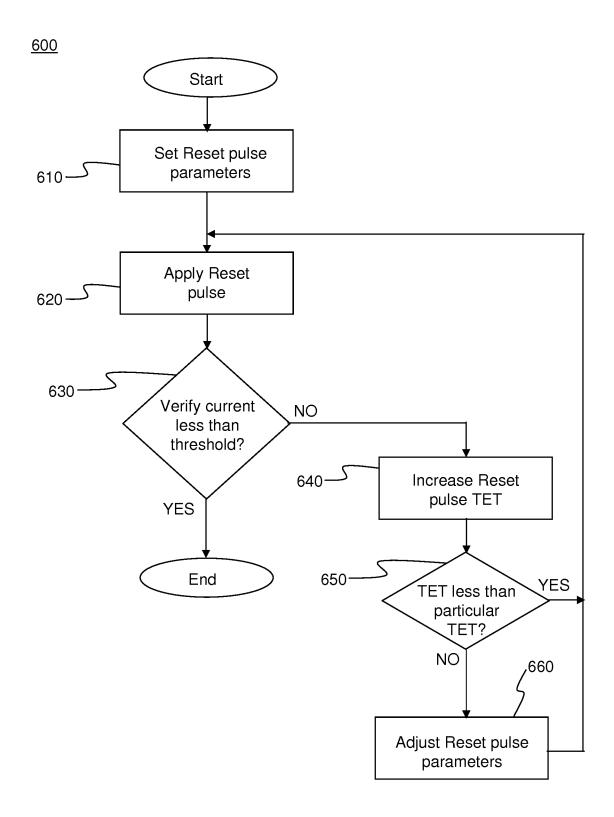

FIG. 6 è un diagramma di flusso di una procedura di programmazione – verifica, secondo un'altra realizzazione.

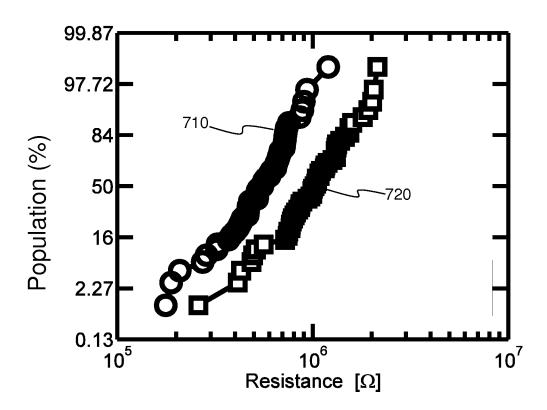

FIG. 7 è un diagramma che mostra la distribuzione di resistenza di una cella di memoria, secondo una realizzazione.

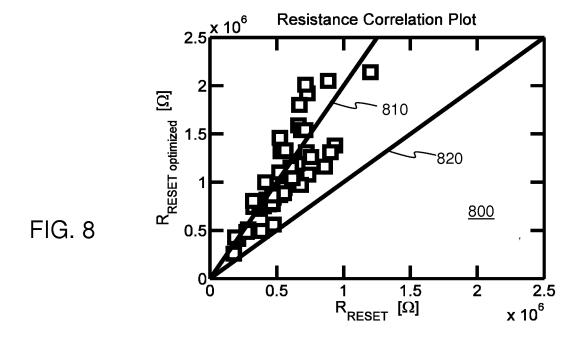

FIG. 8 è un diagramma che mostra la distribuzione di resistenza di una cella di memoria, secondo un'altra realizzazione.

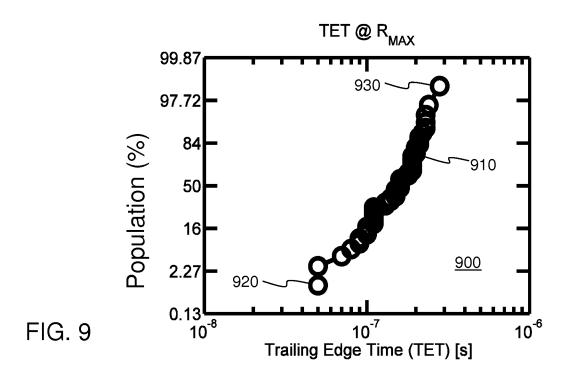

FIG. 9 è un diagramma che mostra la distribuzione di TET di una cella di memoria, secondo una realizzazione.

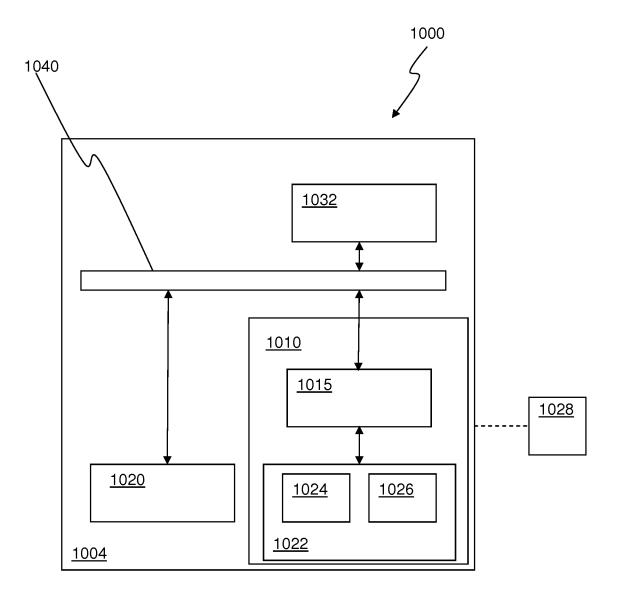

FIG. 10 è un diagramma schematico che illustra il modello per la realizzazione di un sistema di elaborazione.

#### DESCRIZIONE DETTAGLIATA

Il riferimento all'interno di questa specifica a "una realizzazione" o "la realizzazione" significa che una particolare proprietà, struttura o caratteristica descritta in connessione con la realizzazione è inclusa in almeno una realizzazione dell'oggetto rivendicato. Così, le diciture "in una realizzazione" o "la realizzazione" presenti in vari luoghi in tutta questa specifica non sono necessariamente tutte riferiti alla stessa realizzazione. Inoltre, le

particolari proprietà, strutture, o caratteristiche possono combinate in 0 più realizzazioni. una In una realizzazione, una cella PCM può essere fissata nello stato di reset per mezzo della fusione del materiale a cambiamento di fase, risultante dall'applicazione di impulso elettrico di ampiezza relativamente elevata e durata relativamente breve. Al contrario, una cella PCM può essere programmata nello stato di set applicando un impulso elettrico di ampiezza relativamente più piccola, mantenendo il materiale sotto il suo punto fusione, con una durata relativamente più lunga, che può anche avere, ad esempio, un fronte di discesa relativamente ripido. Una cella PCM può anche essere programmata nello stato di set mediante l'applicazione di impulso elettrico avente un maggiore, pilotando il materiale al di sopra del suo punto di fusione, possibilmente con un graduale fronte di discesa, per consentire al materiale fuso di organizzare la propria struttura secondo quella propria della fase cristallina. In questo contesto, tale impulso e procedura di reset e / o set essere indicati come impulso di "scrittura" possono "programmazione" processo di "scrittura" е "programmazione".

In una realizzazione, un processo di programmazione delle celle di memoria che coinvolge un fenomeno di rilassamento strutturale (SR) può portare ad un'auspicabile maggiore

resistenza di uno stato di reset di una cella PCM. Un simile aumento della resistenza a sua volta può comportare ampliamento di una finestra di programmazione tra stati di set e reset di una cella PCM. Il SR si può verificare in materiali in uno stato amorfo, per esempio. In tale stato, un l'equilibrio attraverso materiale può raggiungere arrangiamento della propria struttura molecolare. Ad esempio, un materiale a cambiamento di fase può sperimentare il SR dopo essere stato raffreddato, riscaldato, o mantenuto ad una temperatura inferiore a una temperatura di transizione del materiale. Il SR può essere indicato come un fenomeno di invecchiamento / 0 stagionatura del е materiale. Naturalmente, tali dettagli relativi al SR sono a mero titolo esemplificativo, e l'oggetto rivendicato non è così limitato. In una particolare implementazione, il SR del materiale a cambiamento di fase in una cella PCM può essere realizzato con l'aggiunta di un tempo di discesa (TET) ad una durata di un impulso elettrico di reset, come spiegato in dettaglio di un tale può comportare seguito. L'aggiunta di TETspostamento di uno stato di reset su un livello di resistenza più alto se paragonato allo stato di reset che risulta da un impulso di reset senza l'aggiunta di un TET. Di consequenza, un margine di lettura tra due stati di una cella PCM può essere volutamente ampliato. Un simile aumento della resistenza può essere il risultato di uno o più meccanismi

fisici di SR in una fase amorfa di un materiale calcogenuro, per esempio. In particolare, un impulso di reset che include un TET aggiunto può essere in grado di accelerare il SR entro poche centinaia di nanosecondi, per esempio, risultando in un maggior valore di resistenza dopo l'applicazione di un impulso di programmazione. Naturalmente, tali dettagli di un'applicazione di un impulso di reset modificato e del SR risultante sono a mero titolo esemplificativo, e l'argomento rivendicato non è così limitato.

FIG. 1 è un diagramma schematico di una parte della memoria a cambiamento di fase 100, secondo una realizzazione. Tale porzione include due celle di memoria, ciascuna delle quali si trova in uno stato di memoria differente per scopi illustrativi. Un substrato semiconduttore 150 può includere le regioni drogate N 155, anche se altre configurazioni, compreso l'uso di regioni drogate P per esempio, possono essere utilizzate. La memoria a cambiamento di fase 100, può comprendere word lines 160, bit line 105, e contatto di bit line 110. Per rappresentare uno stato della memoria, un riscaldatore 145 che contatta una porzione di materiale a cambiamento di fase 125 si può riscaldare per fondere una parte 140 di materiale a cambiamento di fase 125, che può quindi essere raffreddato in tempi relativamente brevi per ottenere un GST amorfo, per esempio. Un tale materiale amorfo può essere relativamente alto resistivo, con conseguente

120. connessione alto resistiva ad un contatto Per rappresentare un altro stato della memoria, un riscaldatore 135 che contatta una porzione di materiale a cambiamento di fase 115 si può riscaldare per fondere una parte del materiale a cambiamento di fase 115, che può quindi essere raffreddato in modo relativamente lento per ottenere un materiale policristallino, a bassa resistenza. Tale materiale policristallino a cambiamento di fase 115 può quindi portare ad una connessione a bassa resistenza al contatto 120. Ovviamente, i dettagli di tale porzione di una cella PCM sono a mero titolo esemplificativo, e l'argomento rivendicato non è così limitato.

Come indicato in precedenza, una porzione di materiale a cambiamento di fase 140 óuq essere riscaldata successivamente raffreddata da un impulso di reset modificato con l'aggiunta di un TET, con un consequente stato di reset caratterizzato da una resistenza maggiore. Di consequenza, una differenza di resistenza tra la porzione di materiale a cambiamento di fase 140 (stato di reset) e quella di materiale policristallino a cambiamento di fase 115 (stato di set) può essere aumentata. Un tale aumento può migliorare un processo di lettura di celle di memoria di una PCM, dato che un tale processo può più facilmente discriminare tra uno stato di reset e di set, per FIG. 2 è un diagramma di stato che mostra possibili

più valori di transizioni tra due e/o corrispondenti a stati logici di una cella PCM, secondo una realizzazione. Ad esempio, una cella PCM può comprendere un materiale a cambiamento di fase che si può trovare in uno stato amorfo con una resistenza relativamente elevata o in uno stato cristallino con una resistenza relativamente bassa, come spiegato sopra. Le transizioni tra tali stati possono avviate mediante l'applicazione di un elettrico a una cella PCM in modo da fondere selettivamente, raffreddare e / o cristallizzare il materiale a cambiamento di fase. Un basso livello di resistenza 210 può corrispondere ad uno stato di set di una cella PCM, in cui il materiale a cambiamento di fase è cristallizzato e ha una resistenza relativamente bassa. Un alto livello di resistenza 220 può corrispondere ad uno stato di reset di una cella PCM, in cui il materiale a cambiamento di fase è in uno stato amorfo e ha resistenza relativamente elevata. Una differenza di valore di resistenza tra il livello a bassa resistenza 210 e quello ad alta resistenza 220 può corrispondere a un margine 215 di lettura tra uno stato logico basso (set) e uno alto (reset) di una cella PCM. Un livello alto resistivo innalzato 230 può corrispondere ad uno stato di reset modificato di una cella PCM, in cui il materiale amorfo a cambiamento di fase può essere stagionato per mezzo del SR per aumentare la resistenza di un margine 225. Di conseguenza, il margine di

lettura 215 può essere aumentato del margine 225, con consequente allargamento di una finestra di programmazione stati set reset di una cella di е FIG. 3 è un diagramma di resistenza 300 di una cella di memoria in funzione del TET, secondo una realizzazione. Tale resistenza può dipendere, almeno in parte, dal fatto che il materiale a cambiamento di fase incluso nella cella memoria, si trovi in una fase amorfa e / o una fase cristallina, come discusso in precedenza. Tale condizione di fase può essere selezionata regolando la temperatura di un elemento riscaldatore nella cella di memoria. Ad esempio, la regolazione di un valore di una tensione applicata e / o la regolazione della durata temporale di tale tensione applicata comprendere una tecnica per la selezione particolare condizione di fase del materiale a cambiamento di fase. In una particolare implementazione, il TET può essere aggiunto alla durata di un impulso di reset per spostare uno stato di reset ad un livello di resistenza più elevato rispetto a uno stato di reset risultante da un impulso di reset senza TET aggiunto. L'aggiunta di un tale TET può comprendere una tecnica per integrare la regolazione della temperatura del materiale a cambiamento di fase in un impulso di reset. Il TET aggiunto svolge la funzione di spegnere lentamente la corrente (tensione) di programmazione durante un impulso di reset, e quindi può raffreddare lentamente il materiale a cambiamento di fase. Di consequenza, il diagramma 300 comprende una rappresentazione di resistenza in funzione di tale tempo di spegnimento, a partire da un TET pari a 10 nanosecondi (ns), che può corrispondere ad un raffreddamento relativamente veloce, e continua fino a TET di 600 ns. Il grafico dati 310 comprende la resistenza di una cella di memoria contro TET per una tensione di picco dell'impulso di 2.0 volt. Ιl grafico dati 320 comprende resistenza di una cella di memoria contro TET per tensione di picco dell'impulso di reset di 2.3 volt. Le differenze tra detti diagrammi di dati sono illustrate di sequito. Naturalmente, i dettagli particolari del diagramma 300 sono solo meri esempi di come le resistenze delle celle essere determinate per una implementazione, e l'oggetto rivendicato non è così limitato. Facendo riferimento al diagramma di dati 310, il materiale a cambiamento di fase può trovarsi in uno stato amorfo in modo la resistenza della cella di memoria possa essere relativamente alta per un impulso di reset con un TET in un intervallo da 10 ns a circa 100 ns. Oltre un TET di circa 120 ns, il materiale a cambiamento di fase può trovarsi in uno stato cristallino in modo che la resistenza della cella di memoria possa essere relativamente bassa (la resistenza intermedia può corrispondere al materiale a cambiamento di fase esistente in una miscela di stati amorfi e cristallini,

per esempio). Tale comportamento del grafico di dati 310 può essere spiegato come seque. Un TET relativamente breve (ad esempio, meno di circa 100 ns) aggiunto ad un impulso di reset può fornire un raffreddamento sufficientemente veloce del materiale a cambiamento di fase in modo che il materiale a cambiamento di fase rimanga in uno stato amorfo stabilito momento della comparsa dell'impulso di reset. D'altra parte, un TET relativamente lungo (ad esempio, maggiore di circa 100 ns) aggiunto all'impulso di reset può fornire un raffreddamento sufficientemente lento del materiale cambiamento di fase in modo che il materiale a cambiamento di fase cristallizzi in una fase cristallina corrispondente ad resistenza relativamente bassa. D'altro canto, tale impulso di reset con un TET relativamente lungo potrebbe comprendere essenzialmente un impulso di set, che può essere utilizzato per avviare una transizione del materiale cambiamento di fase in cristallino. uno stato In una realizzazione, gli effetti del SR possono essere introdotti aumentando sufficientemente la tensione di picco di un impulso di reset. In un caso specifico, una tale tensione può essere aumentata da 2,0 volt (ad esempio, grafico dati 310) a 2.3 volt, ad esempio per il grafico di dati 320, che viene descritto come segue. Facendo riferimento ai diagrammi di dati 320, un materiale a cambiamento di fase può esistere in uno stato amorfo in modo che la resistenza della cella di memoria possa essere relativamente alta per un impulso di reset con una TET in un intervallo da 10 ns a circa 250 ns. All'interno di questo intervallo, gli effetti del SR possono essere manifestati come un aumento della resistenza delle celle di memoria quando il TET si avvicina a circa 250 ns. In particolare, tale aumento di resistenza può portare ad uno stato di reset modificato ed avente una maggiore resistenza rispetto ad un caso in cui non sia aggiunto un TET (ad esempio, zero TET) e / o in cui non sia sufficientemente aumentata la tensione di picco di un impulso di reset, per esempio. In altre parole, una resistenza di uno stato di reset di una cella di memoria può essere aumentata di un margine 330 aggiungendo un TET di circa 200 ns e aumentando sufficientemente la tensione di picco di un impulso di reset.

Continuando con il grafico di dati 320, oltre un TET di circa 250 ns, il materiale a cambiamento di fase può esistere in uno stato cristallino in modo che la resistenza della cella di memoria possa essere relativamente bassa. Per quanto riguarda il caso del diagramma 310, un TET relativamente breve (ad esempio, meno di circa 250 ns) aggiunto ad un impulso di reset può fornire un raffreddamento del materiale a cambiamento di fase sufficientemente veloce in modo che il materiale a cambiamento di fase rimanga in uno stato amorfo stabilito dall'impulso di reset. D'altra parte, un TET

relativamente lungo (ad esempio, maggiore di circa 250 ns) aggiunto all'impulso di reset può fornire un raffreddamento sufficientemente lento del materiale a cambiamento di fase in modo che il materiale a cambiamento di fase cristallizzi in una cristallina corrispondente ad una resistenza relativamente bassa. Pertanto, al fine di beneficiare di una maggiore resistenza, come ad esempio dal margine 330, esempio, una selezione di TET può indurre la determinazione di un TET desiderato che sia abbastanza lungo da aumentare la resistenza (per esempio, ad un TET di 250 ns), ma non così lungo da consentire la cristallizzazione del materiale a cambiamento di fase (ad esempio, ad un TET di 300 ns), con consequente resistenza relativamente bassa. Naturalmente, tali valori di tensione di picco e di TET sono solo meri esempi, e l'argomento rivendicato non è così limitato.

FIG. 4 è un diagramma delle caratteristiche di una forma d'onda di segnale di programmazione, secondo una realizzazione. Ad esempio, tale segnale di polarizzazione può comprendere un impulso di reset, come discusso in precedenza. In particolare, l'impulso di reset 410 include un tempo di salita 416, un tempo di discesa 418, una durata 414 e un valore di corrente (tensione) di picco 412. L'impulso di reset modificato 420 dispone di un tempo di salita 426, un tempo di discesa corrispondente al TET 428, durata 424, e un valore di corrente (tensione) di picco 422. L'applicazione di

un impulso di reset 410 oppure di un impulso di reset modificato 420 ad una cella di memoria può portare materiale a cambiamento di fase incluso nella cella memoria ad uno stato amorfo ad alta resistenza. Tuttavia, l'applicazione di un impulso di reset modificato 420 ad una memoria può portare ad uno stato amorfo materiale a cambiamento di fase a più alta resistenza, all'applicazione di un impulso di rispetto reset Rispetto all'impulso di reset 410, l'impulso di reset modificato 420 può includere un TET allungato 428 e una più elevata corrente (tensione) di picco 422. Un tale allungato e / o valore di picco può portare ad una maggiore alta resistenza derivante dal SR, per esempio. Per illustrare esempio particolare, la corrente di picco 422 può consistere in 300 micro-ampere rispetto alla corrente picco 412 che può consistere in 200 micro-ampere. Naturalmente, tali valori sono solo esempi, e l'argomento rivendicato non è così limitato.

flusso di FIG. 5 è un diagramma di un processo di programmazione/verifica 500 ai fini della scrittura di un particolare bit di informazione in una cella di memoria, secondo una realizzazione. Un tale processo può includere una procedura per verificare che tale particolare bit sia stato scritto correttamente nella cella di memoria. Τn บทล implementazione, tale bit particolare può comprendere uno "zero" o bit di reset. Qui, un impulso di reset può essere una memoria per а cella di fondere successivamente raffreddare il materiale a cambiamento fase nella cella di memoria in modo che il materiale a cambiamento di fase abbia una resistenza relativamente un processo di verifica può Di consequenza, includere una tecnica per verificare che il materiale a cambiamento di fase si trovi nello stato di reset ad una tale resistenza elevata successivamente all'applicazione di un impulso di reset.

blocco 510, i parametri di un impulso di reset applicare ad una cella di memoria particolare possono essere determinati. Ad esempio, tali parametri possono includere un valore di corrente di picco di un impulso di reset, una larghezza di un impulso di reset, e / o i tempi di salita e discesa di un impulso di reset. In una particolare per esempio, un impulso di reset può implementazione, includere una corrente di picco di 150 micro-ampere e un tempo di discesa di 10 ns per una cella di memoria, mentre un impulso di reset per un'altra cella di memoria può includere una corrente di picco di 200 micro- ampere e un tempo di discesa di 10 ns. Tuttavia, questi sono solo esempi parametri per un impulso di reset, e l'oggetto rivendicato non si limita a questo aspetto. Nel blocco 520, un impulso di reset avente i parametri determinati al blocco 510 può essere

applicato ad una cella di memoria per scrivere un bit "zero" nella cella di memoria, corrispondente ad uno stato ad alta implementazione, tale bit In una memorizzato in una cella di memoria può portare ad una corrente di verifica relativamente bassa dell'applicazione di una tensione di verifica ai capi della cella di memoria, per esempio. In tal modo, se un bit "zero" sia stato scritto correttamente nella cella di memoria può essere confermato determinando se una corrente di verifica sia inferiore o meno rispetto ad un particolare valore di soglia. di Tale discriminazione óuq effettuata nel blocco di controllo 530. Se una corrente di verifica è inferiore a tale soglia particolare di corrente, allora la procedura 500 può terminare, dal momento che la memorizzazione di un bit "zero", corrispondente ad uno stato amorfo avente resistenza relativamente elevata, è verificata. Tuttavia, se una corrente di verifica è maggiore rispetto ad una particolare soglia di corrente, la memorizzazione di un bit "zero" potrebbe avere fallito, in quanto una corrente di verifica più alta di quella desiderata può indicare che la resistenza della cella di memoria non è stata programmata ad un valore sufficientemente alto di reset. Tale caso può verificarsi, ad esempio, se il materiale cambiamento di fase nella cella di memoria è in una fase mista di uno stato amorfo e di uno stato cristallino. Dunque il processo 500 può procedere al blocco 540, dove l'ampiezza di un impulso di reset da applicare di nuovo (nel blocco 520) alla cella di memoria può essere aumentata. Un tale incremento può essere sufficiente a programmare nello stato di reset il materiale a cambiamento di fase della cella di memoria, in uno stato a resistenza sufficientemente alta. Se così accade, il processo 500 può terminare. Altrimenti, se la resistenza della cella di memoria non è ancora sufficientemente elevata, il processo 500 può procedere di nuovo al blocco 540 e l'ampiezza di un impulso di reset può essere aumentata ulteriormente. Tale ciclo può continuare fino a che la corrente di verifica è inferiore ad una corrente di soglia, indicando così che la resistenza della cella di memoria è sufficientemente elevata. Naturalmente, questi dettagli del processo 500 sono a mero titolo esemplificativo, e l'argomento rivendicato non è così limitato.

FIG. 6 è un diagramma di flusso di una procedura di programmazione / verifica 600 per scrivere un particolare bit di informazione in una cella di memoria, secondo un'altra realizzazione. Una simile procedura può includere un processo per verificare che tale bit particolare sia stato scritto correttamente nella cella di memoria. In una implementazione, tale bit particolare può includere uno "zero" o bit di reset. Qui, un impulso di reset può essere applicato ad una cella di memoria per fondere e successivamente raffreddare il

materiale a cambiamento di fase nella cella di memoria in modo che il materiale a cambiamento di fase abbia una relativamente elevata. resistenza In una implementazione, ad esempio, tale resistenza elevata può includere un margine di resistenza, come il margine 330 mostrato in FIG. 3, come risultato dell'applicazione di un impulso di reset modificato che consenta il verificarsi del SR, per esempio. Di consequenza, un processo di verifica può comprendere una tecnica per verificare che il materiale a cambiamento di fase sia stato programmato in reset, a tale resistenza elevata, successivamente all'applicazione di un impulso di reset modificato. Tale impulso di reset modificato descritto. óuq includere un TET aggiunto, come sopra Nel blocco 610, i parametri di un impulso di reset modificato da applicare ad una particolare cella di memoria possono determinati. Ad esempio, tali parametri essere includere un valore di corrente di picco di un impulso di reset, una durata di un impulso di reset, un tempo di salita di un impulso di reset e / o un TET di un impulso di reset. In una particolare implementazione, per esempio, un impulso reset modificato può includere una corrente di picco di relativamente più grande (ad es, il 20% più alta) rispetto ad una corrente di picco utilizzata nel processo 500. Tale impulso di reset modificato può anche includere un TET lungo rispetto a un relativamente più tempo di discesa

utilizzato nel processo 500. Per illustrare un esempio particolare, un impulso di reset modificato può includere una corrente di picco di 180 micro-ampere e un TET di 50 ns per una cella di memoria, mentre un impulso di reset modificato per un'altra cella di memoria può includere una corrente di picco di 240 micro-ampere e un TET di 50 ns. Naturalmente, questi sono solo esempi di parametri di impulsi di reset modificati, e l'oggetto rivendicato non è limitato a questo riguardo. Nel blocco 620, un impulso di reset modificato avente parametri determinati nel blocco 610 può essere applicato ad una cella di memoria per scrivere un bit "zero" nella cella di memoria, corrispondente ad uno stato ad alta implementazione, tale bit resistenza. Ιn una "zero" immagazzinato in una cella di memoria può risultare in una verifica corrente di relativamente bassa dell'applicazione di una tensione di verifica ai capi la cella di memoria, per esempio. In tal modo, se un bit "zero" sia stato scritto correttamente nella cella di memoria può essere confermato dal discriminare se una corrente verifica sia o meno inferiore ad un determinato valore di soglia. Inoltre, se un margine addizionale corrente di desiderato di resistenza 330 sia associato o meno ad un bit "zero", può essere confermato da tale discriminazione, che può essere effettuata nel blocco di controllo 630. Se una corrente di verifica è inferiore a una determinata corrente

di soglia, allora il processo 600 può concludersi, in quanto la memorizzazione di un bit "zero", corrispondente ad una resistenza relativamente elevata, che include un aggiunto di resistenza, è verificato. Tuttavia, corrente di verifica è maggiore rispetto a una soglia particolare di corrente, la memorizzazione di un bit "zero" potrebbe non essere riuscita e / o la resistenza della cella di potrebbe essere ulteriormente memoria incrementata mediante applicazione di un impulso di reset modificato che consenta il verificarsi del SR, per esempio. Così il processo 600 può procedere al blocco 640 dove un TET di un impulso di reset modificato può essere aumentato di una particolare quantità. Per esempio, nel blocco 640, un TET di 50 ns può essere incrementato di una quantità di 10 ns. Qui, un TET comprensivo di tali ulteriori 10 ns, applicato ad una cella di memoria, può portare ad un valore maggiore di resistenza della cella di memoria.

Nel blocco di controllo 650, può essere eseguito un controllo, se un TET più una parte del tempo aggiunto nel blocco 640 si mantenga o meno inferiore ad un particolare valore di TET. Se è così, il processo 600 può procedere al blocco 620 dove un impulso di reset modificato ed avente un TET aumentato può essere applicato alla cella di memoria. Tuttavia, se un TET derivante da un aumento effettuato nel blocco 640 non risulta inferiore a tale TET particolare,

allora il processo 600 può procedere al blocco 660 dove i parametri di impulso di reset, in aggiunta al TET, possono modificati. Ad esempio, tali parametri includere un valore di incremento di tempo in cui il TET è aumentato nel blocco 640. In tal caso, una risoluzione del passo con cui il TET è aumentato nel blocco 640 può essere regolato. Altri parametri che possono essere aggiustati nel blocco 660 possono includere un valore di corrente di picco modificato, per dell'impulso di reset esempio. Dί consequenza, varie combinazioni di corrente di picco e TET di un impulso di reset modificato possono essere applicate ad una cella di memoria. In particolare, il processo 600 può procedere al blocco 620 dove un impulso di reset modificato con i parametri regolati può essere applicato alla cella di memoria. Tali parametri aggiustati possono essere sufficienti per portare in reset il materiale a cambiamento di fase, in uno stato ad alta resistenza sufficientemente elevato. Se è così, processo il 600 può terminare. Altrimenti, resistenza della cella di memoria non risulta sufficientemente alta, il processo 600 può procedere di nuovo al blocco 640 e il TET dell'impulso di reset modificato può essere aumentato ulteriormente. Tale ciclo del processo può continuare fino a quando la corrente di verifica è inferiore a una soglia di corrente, indicando così che l'incremento di resistenza della cella di memoria è sufficientemente elevato.

Naturalmente, tali dettagli relativi al processo 600 sono a mero titolo esemplificativo, e l' argomento rivendicato non è così limitato.

FIG. 7 è un grafico 700 che mostra una distribuzione delle resistenze di una cella di memoria, secondo una realizzazione. I dati 710 comprendono resistenze di una popolazione di celle di memoria in uno stato di reset ad alta resistenza (ad esempio, bit "zero"). Un processo di reset applicato a tali celle di memoria può implicare un impulso di reset, che non include un TET aggiunto, per esempio. D'altra parte, i dati 720 mostrano resistenze di una popolazione di celle di memoria in uno stato di reset ad alta resistenza migliorato. Un processo di reset applicato a tali celle di memoria può implicare un impulso di reset modificato che include un TET aggiunto, come sopra descritto, per esempio. Il grafico 700 può dimostrare che dopo l'applicazione di un impulso di reset modificato che include un TET aggiunto, si può ottenere un livello di resistenza più elevato di una cella di memoria in confronto ad un livello di resistenza ottenuto con un impulso di reset senza TET Naturalmente, i dettagli della figura 700 sono a mero titolo esemplificativo, e l'argomento rivendicato non limitato.

FIG. 8 è un diagramma 800 che mostra una distribuzione di resistenze di una cella di memoria, secondo un'altra

realizzazione. I dati 820 comprendono i valori resistenza di celle di memoria in stato di reset ad alta resistenza (ad esempio, bit "zero"). Il processo di reset della cella di memoria può anche comportare un impulso di reset che non include un TET aggiunto, per esempio. D'altra parte, i dati mostrano resistenze 810 di una popolazione di celle di memoria nello stato di reset migliorato, ad alta resistenza. Un processo di reset applicato a tali celle di memoria può implicare un impulso di reset modificato che include un TET aggiunto, come sopra descritto, per esempio. correlazione 800 óuq dimostrare una distribuzioni di resistenza indicate in FIG. 7, dimostrando che un impulso di reset modificato che include un TET aggiunto può raddoppiare il livello di resistenza di cella di memoria rispetto alla resistenza ottenuta da un impulso di reset che non dispone di un TET aggiunto, per esempio. Naturalmente, tali dettagli del diagramma 800 sono a mero titolo esemplificativo, e l'argomento rivendicato non è così limitato.

FIG. 9 è un digramma 900 che mostra una distribuzione di TET di una cella di memoria, secondo una realizzazione. I dati 910 comprendono una popolazione di celle di memoria in uno stato di reset a maggiore alta resistenza per vari valori di TET. Ad esempio, i dati 920 potrebbero indicare che una percentuale relativamente piccola di celle di memoria

raggiunge un tale stato migliorato ad alta resistenza, se il TET è relativamente breve. In confronto, i dati 930 potrebbero indicare che una percentuale relativamente elevata di celle di memoria raggiunge uno stato potenziato ad alta resistenza, se il TET è relativamente lungo. Naturalmente, tali dettagli del diagramma 900 sono solo esempi di TET per le celle di memoria, e l'argomento rivendicato non è così limitato.

FIG. 10 è un diagramma schematico che illustra เมทล realizzazione esemplare di un sistema di calcolo 1000 che comprende un dispositivo di memoria 1010. Tale dispositivo di elaborazione può comprendere uno o più processori, esempio, per eseguire un'applicazione e / o altro codice. Ad esempio, un dispositivo di memoria 1010 può includere un sistema di memoria che include una PCM 100, mostrata in FIG. 1. Un dispositivo di calcolo 1004 può essere rappresentativo di un qualsiasi dispositivo, un impianto, o una macchina che può essere configurabile per la gestione del dispositivo di memoria 1010. Un dispositivo di memoria 1010 può includere un controller di memoria 1015 e una memoria 1022. A titolo esemplificativo ma non esaustivo, un dispositivo di calcolo 1004 può comprendere: uno o più dispositivi di elaborazione e / o piattaforme, come, ad esempio, un computer desktop, un computer portatile, una workstation, un dispositivo server, o simili, uno o più personal computer o dispositivi di

comunicazione o di apparecchi, come, ad esempio, un assistente digitale personale, dispositivi di comunicazione mobile, o simili, un sistema di calcolo e / o associato fornitore di servizi, come, ad esempio, un database o un provider di memorizzazione di dati di servizio / sistema e / o qualsiasi combinazione.

E' noto che la totalità o parte dei vari dispositivi di sistema indicati in 1000, i processi e i metodi di come ulteriormente descritto nel presente documento, possono essere implementati usando o comprendendo hardware, firmware, software, o qualsiasi combinazione. Così, a esemplificativo ma non esaustivo, il dispositivo di calcolo 1004 può includere almeno una unità di elaborazione 1020 che è operativamente accoppiata alla memoria 1022 attraverso un bus 1040 e un host o un controller di memoria 1015. L'unità di elaborazione 1020 è rappresentativa di una o più circuiti configurabili per effettuare almeno una parte di procedura di elaborazione dati o di processo. Ιn esemplificativo e non limitativo, l'unità di elaborazione 1020 può comprendere uno o più processori, controller, microprocessori, microcontrollori, circuiti integrati per applicazioni specifiche, processori di segnali digitali, dispositivi di logiche programmabili, FPGA, e simili, o qualsiasi combinazione. L'unità di elaborazione 1020 può comprendere un sistema operativo configurato per comunicare

con controller di memoria 1015. Un tale sistema operativo potrebbe, ad esempio, generare i comandi da inviare al controller di memoria 1015 attraverso il bus 1040. Tali comandi possono comprendere leggere e / o scrivere i comandi. In risposta a un comando di scrittura, ad esempio, il controller di memoria 1015 può fornire un impulso di reset, tale impulso di reset modificato 420 comprendente un TET 428, FIG. 4, ad esempio. In particolare, il mostrato in controllore di memoria 1015 può applicare un impulso di reset modificato 420 ad un array di celle PCM per posizionare le celle PCM in uno stato di reset, per misurare le correnti associate a uno stato di reset ad alta resistenza delle celle PCM, per confrontare le correnti di lettura con una corrente particolare di riferimento e per applicare un impulso di reset modificato singolarmente alle celle PCM per posizionare le celle PCM in uno stato di resistenza migliorata, in cui l'impulso di reset modificato include un TET aggiunto in risposta a quello di confronto.

La memoria 1022 è rappresentativa di un meccanismo di archiviazione dei dati. La memoria 1022 può includere, ad esempio, una memoria primaria 1024 e/o una memoria secondaria 1026. La memoria primaria 1024 può includere, ad esempio, una memoria ad accesso casuale, una memoria di sola lettura, ecc.. Come illustrato in questo esempio essendo separati dall'unità di calcolo 1020, dovrebbe essere chiaro che tutta

o parte della memoria primaria 1024 può essere fornita all'interno o altrimenti co-allocata/accoppiata all'unità di elaborazione 1020.

La memoria secondaria 1026 può includere, ad esempio, lo stesso tipo o similari di memoria come memoria principale e / o uno o più dispositivi di memorizzazione di dati o sistemi, quali, ad esempio, un disco, un disco ottico, un'unità a nastro, una unità di memoria a stato solido, ecc.. In alcune implementazioni, la memoria secondaria 1026 può essere operativamente ricettiva di, o comunque configurabile per essere accoppiabile con un supporto informatico leggibile 1028. Un supporto informatico leggibile 1028 può includere, ad esempio, qualsiasi mezzo che può trasportare e / o rendere i dati accessibili, codice e / o istruzioni per uno o più dei dispositivi del sistema 1000.

Il dispositivo di elaborazione 1004 può includere, ad esempio, un input / output 1032. L'input / output 1032 è rappresentativo di uno o più dispositivi o funzioni che possono essere configurabili per accettare oppure introdurre input umani e / o della macchina e / o di uno o più dispositivi o funzioni che possono essere configurabili per fornire oppure dare output umani e / o della macchina. A titolo esemplificativo ma non esaustivo, il dispositivo di input / output 1032 può comprendere un display operativamente configurato, un altoparlante, una tastiera, un mouse, un

trackball, un touch screen, una porta dati, ecc..

I termini "e", "e / o", "o" come qui utilizzati possono includere una varietà di significati che dipenderà, almeno in parte dal contesto in cui vengono utilizzati. In genere, "e / o", nonché "o" se utilizzato come elemento associativo di una lista, ad esempio A, B o C, è destinato a dire A, B e C, qui usato in senso inclusivo, nonché A, B o C, qui usato in senso esclusivo. Il riferimento in questa specifica a "una realizzazione" o "la realizzazione" significa che una caratteristica particolare, una struttura o caratteristica descritta in connessione con la realizzazione è inclusa in almeno una realizzazione dell'oggetto rivendicato. Così, i significati delle frasi "in una realizzazione" o "la realizzazione" nelle varie parti di tutta questa trattazione non sono necessariamente tutti riferiti alla stessa realizzazione. Inoltre, le peculiarità, le strutture, o le caratteristiche possono essere combinate più realizzazioni. in una Mentre sono stati illustrati e descritti quelli che sono attualmente considerati come esempi di realizzazioni, sarà compreso da coloro che sono competenti nella materia che diverse altre modifiche possono essere fatte, e gli equivalenti possono essere sostituiti, senza uscire dall'oggetto rivendicato. Inoltre, molte modifiche possono

essere introdotte per adattare una particolare situazione agli insegnamenti introdotti dall'oggetto rivendicato senza discostarsi dal concetto centrale qui descritto. Pertanto, si intende che l'oggetto rivendicato non è limitato alla particolare realizzazione divulgata, ma che tale argomento rivendicato può anche includere tutte le realizzazioni che rientrano nel campo delle rivendicazioni allegate, ed equivalenti.

#### RIVENDICAZIONI

Quanto è rivendicato è:

1. Un metodo che comprende:

l'applicazione di un impulso di polarizzazione ad una cella di memoria a cambiamento di fase (PCM), per posizionare tale cella PCM in uno stato ad alta resistenza in risposta a un comando di scrittura;

la misura di una corrente di lettura associata allo stato di reset ad alta resistenza di detta cella PCM, e l'applicazione alla suddetta cella PCM di un impulso di polarizzazione modificato per posizionare detta cella PCM in uno stato di resistenza maggiore, in cui detto impulso di polarizzazione modificato include l'aggiunta di un tempo del fronte di discesa (TET) in risposta ad una comparazione della detta corrente di lettura con una particolare corrente di riferimento.

- 2. Il metodo della rivendicazione 1, in cui detto impulso di polarizzazione modificato viene applicato alla detta cella PCM in risposta alla detta corrente di lettura se questa risulta superiore a detta particolare corrente di riferimento.

- 3. Il metodo della rivendicazione 1, che comprende inoltre:

la misurazione di una nuova corrente di lettura associata con detto stato di maggiore resistenza di tale cella PCM,

la decisione se sia opportuno riapplicare detto impulso di polarizzazione modificato che include un aumento del tempo del fronte di discesa alla detta cella PCM, essendo detta decisione basata, almeno in parte, su un confronto di questa nuova corrente di lettura con detta particolare corrente di riferimento.

- 4. Il metodo della rivendicazione 1, in cui un valore di corrente di picco di tale impulso di polarizzazione è sostanzialmente uguale al valore di corrente di picco di tale impulso di polarizzazione modificato.

- 5. Il metodo della rivendicazione 1, che comprende inoltre:

- l'aumentare della corrente di picco di tale impulso di polarizzazione modificato ad un valore nettamente superiore a quello del detto impulso di polarizzazione.

- 6. Il metodo della rivendicazione 1, in cui detta cella PCM nel detto stato di maggiore resistenza comprende un materiale a cambiamento di fase in uno stato amorfo.

- 7. Il metodo della rivendicazione 6, in cui detta cella PCM in detto stato di maggiore resistenza comprende detto materiale a cambiamento di fase in detto stato amorfo modificato dal rilassamento strutturale.

- 8. Il metodo della rivendicazione 1, che comprende inoltre:

l'applicazione di detto impulso di polarizzazione individualmente alle successive celle PCM in una memoria PCM per posizionare tali celle PCM in detto stato ad alta resistenza;

l'aggiunta di un TET a detti individuali impulsi di polarizzazione.

9. Un dispositivo di memoria non volatile che comprende: una matrice di celle di memoria a cambiamento di fase (PCM), comprendente un materiale a cambiamento di fase, e un controllore per:

applicare un impulso di polarizzazione ad almeno una di tali celle PCM per posizionare almeno una delle dette celle PCM in uno stato ad alta resistenza in risposta ad un comando di scrittura;

misurare le correnti di lettura associate a detti stati ad alta resistenza di dette celle PCM;

applicare un impulso modificato ad almeno una delle dette celle PCM per inserire almeno una di dette celle PCM in uno stato di maggiore resistenza, in cui detto impulso di polarizzazione modificato include l'aggiunta di un tempo di discesa del fronte (TET) in risposta ad una comparazione di detta corrente di lettura con una particolare corrente di riferimento.

10. Il dispositivo di memoria non volatile della rivendicazione 9, in cui detto impulso di polarizzazione

modificato è applicato ad almeno una di dette celle PCM in risposta a correnti di lettura che sono superiori a detta particolare corrente di riferimento durante il suddetto confronto.

11. Il dispositivo di memoria non volatile della rivendicazione 9, in cui detto controllore è ulteriormente adattato per:

misurare nuove correnti di lettura associate al detto stato di maggiore resistenza delle dette celle PCM; determinare se applicare nuovamente detto impulso di polarizzazione modificato che comprende un fronte di discesa aumentato ad almeno una di dette celle PCM basandosi, almeno in parte, su un confronto di dette nuove correnti di lettura con detta particolare corrente di riferimento.

- 12. Il dispositivo di memoria non volatile della rivendicazione 9, in cui un valore della corrente di picco di detto impulso di polarizzazione è sostanzialmente uguale al valore della corrente di picco di detto impulso di polarizzazione modificato.

- 13. Il dispositivo di memoria non volatile della rivendicazione 9 in cui detto controllore è ulteriormente modificato per:

aumentare la corrente di picco di detto impulso di polarizzazione modificato ad un valore nettamente

superiore a quello del detto impulso di polarizzazione.

- 14. Il dispositivo di memoria non volatile della rivendicazione 9, in cui detta cella PCM in detto stato ad alta resistenza si compone di un materiale a cambiamento di fase in uno stato amorfo.

- 15. Il dispositivo di memoria non volatile della rivendicazione 14, in cui detta cella PCM in detto stato a più elevata resistenza si compone di detto materiale a cambiamento di fase in detto stato amorfo modificato dal rilassamento strutturale.

# 16 Un sistema che comprende:

un dispositivo di memoria composto da una matrice di celle di memoria a cambiamento di fase (PCM), composte da un materiale a cambiamento di fase, detto dispositivo di memoria ulteriormente comprendente un controllore di memoria per:

applicare un impulso di polarizzazione ad almeno una di dette celle PCM per posizionare almeno una delle dette celle PCM in uno stato ad alta resistenza in risposta a un comando di scrittura;

misurare correnti di lettura associate a stati ad alta resistenza di dette celle PCM;

applicare un impulso di polarizzazione modificato ad almeno una delle dette celle PCM per portare almeno una di dette celle PCM in uno stato di resistenza superiore,

in cui detto impulso di polarizzazione modificato include un aggiunto tempo del fronte di discesa (TET) in risposta alla comparazione di detta corrente di lettura con una particolare corrente di riferimento, e

un processore per ospitare una o più applicazioni e per inviare detto comando di scrittura al controllore di memoria per fornire l'accesso a dette celle di memoria in detta matrice di celle di memoria.

- 17. Il sistema della rivendicazione 16, in cui un valore di corrente di picco di detto impulso di polarizzazione è sostanzialmente uguale al valore della corrente di picco di detto impulso di polarizzazione modificato.

- 18. Il sistema della rivendicazione 16 in cui detto controllore è ulteriormente modificato per:

aumentare una corrente di picco di detto impulso di polarizzazione modificato ad un valore nettamente superiore a quello del detto impulso di polarizzazione.

- 19. Il sistema della rivendicazione 16, in cui detta cella PCM in detto stato ad alta resistenza si compone di un materiale a cambiamento di fase in uno stato amorfo.

- 20. Il sistema della rivendicazione 16, in cui dette celle PCM in detto stato a più elevata resistenza si compongono di detto materiale a cambiamento di fase in detto stato amorfo modificato dal rilassamento strutturale.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 10