(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-508090

(P2005-508090A)

(43) 公表日 平成17年3月24日(2005.3.24)

(51) Int.Cl.<sup>7</sup>

H01L 21/66

H01L 21/02

F 1

H01L 21/66

H01L 21/02

テーマコード(参考)

Z

4M106

Z

Z

審査請求 未請求 予備審査請求 有 (全 51 頁)

(21) 出願番号 特願2003-541045 (P2003-541045)

(86) (22) 出願日 平成14年8月9日 (2002.8.9)

(85) 翻訳文提出日 平成16年4月30日 (2004.4.30)

(86) 國際出願番号 PCT/US2002/025402

(87) 國際公開番号 WO2003/038888

(87) 國際公開日 平成15年5月8日 (2003.5.8)

(31) 優先権主張番号 10/020,551

(32) 優先日 平成13年10月30日 (2001.10.30)

(33) 優先権主張国 米国(US)

(71) 出願人 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノゼ、ピイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68(番地なし)

(74) 代理人 100099324

弁理士 鈴木 正剛

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】組み込み計測法を使用したカスケード制御の方法および装置

## (57) 【要約】

半導体ウェハ(105)の処理のカスケード制御を実行する方法および装置。処理のため第1の半導体ウェハ(105)が受け入れられ、処理のため第2の半導体ウェハ(105)が受け入れられる。第1の半導体ウェハおよび第2の半導体ウェハ(105)に対するカスケード処理操作が実行され、ここでカスケード処理操作は、第1の半導体ウェハ(105)が処理されている期間の少なくとも一部の間に、第2の半導体ウェハ(105)に関連するプロセス前計測データを取得することを含む。

**【特許請求の範囲】****【請求項 1】**

処理のため第1の半導体ウェハ(105)を受け取るステップと、

処理のため第2の半導体ウェハ(105)を受け取るステップと、

前記第1の半導体ウェハおよび前記第2の半導体ウェハ(105)に対してカスケード処理操作を実行するステップと、を有し、前記カスケード処理操作は、前記第1の半導体ウェハ(105)が処理されている期間の少なくとも一部の間に、前記第2の半導体ウェハ(105)に関連するプロセス前計測データを取得することを含む方法。

**【請求項 2】**

前記第2の半導体ウェハ(105)が処理されている期間の少なくとも一部の間に、前記第1の半導体ウェハ(105)に関連するプロセス後計測データを取得するステップをさらに有する請求項1に記載の方法。 10

**【請求項 3】**

プロセス前計測データを取得する前記ステップは、組み込み計測装置(310)を使用してプロセス前計測データを取得するステップをさらに有する請求項1に記載の方法。

**【請求項 4】**

プロセス後計測データを取得する前記ステップは、組み込み計測装置(310)を使用してプロセス後計測データを取得するステップをさらに有する請求項2に記載の方法。

**【請求項 5】**

前記第1の半導体ウェハおよび前記第2の半導体ウェハ(105)に対してカスケード処理操作を実行する前記ステップは、

前記第1の半導体ウェハ(105)に関連するプロセス前計測データを取得するステップと、 20

前記第1の半導体ウェハ(105)に関連するプロセス前計測データを取得した後に、前記第1の半導体ウェハ(105)を処理することと、

前記第1の半導体ウェハ(105)が処理されている期間の少なくとも一部の間に、前記第2の半導体ウェハ(105)に関連するプロセス前計測データを取得するステップと、

前記第1の半導体ウェハ(105)の前記処理の後に、前記第1の半導体ウェハに関連する(105)プロセス後計測データを取得することと、

前記第1の半導体ウェハ(105)に関連する前記プロセス前計測データを取得した後に、前記第1の半導体ウェハ(105)を処理することと、

前記第2の半導体ウェハ(105)に関連するプロセス前計測データを取得することと、 30

前記第2の半導体ウェハ(105)の前記処理の後に、前記第2の半導体ウェハ(105)を処理することと、

前記第2の半導体ウェハ(105)の前記処理に応答してプロセス後計測データを取得することと、を有する請求項1に記載の方法。

**【請求項 6】**

半導体ウェハ(105)の処理のカスケード制御を実行するシステムであって、前記システムは、

カスケード処理操作を実行するプロセス制御装置(350)と、前記カスケード処理操作は、

第1の半導体ウェハ(105)に関連するプロセス前データを取得することと、 40

前記第1の半導体ウェハ(105)に関連する前記プロセス前計測データを取得した後に、前記第1の半導体ウェハ(105)を処理することと、

前記第1の半導体ウェハ(105)が処理されている期間の少なくとも一部の間に、第2の半導体ウェハ(105)に関連するプロセス前データを取得することと、

前記第2の半導体ウェハ(105)に関連する前記プロセス前データを取得した後に、前記第2の半導体ウェハ(105)を処理することと、

前記第2の半導体ウェハ(105)が処理されている期間の少なくとも一部の間に、前記第1の半導体ウェハ(105)に関連するプロセス後データを取得することと、

前記第2の半導体ウェハ(105)の前記処理の後に、前記第2の半導体ウェハ(105)を処理することと、を含むことと、

50

前記プロセス制御装置（350）と作動的に結合され、前記インラインのプロセス前計測データおよび前記インラインのプロセス後計測データの少なくとも一方を受け取るためのインライン・カスケード計測データ記録ユニット（320）と、

前記プロセス制御装置（350）および前記インライン・カスケード計測データ記録ユニット（320）と作動的に結合され、前記インラインのプロセス前計測データおよび前記インラインのプロセス後計測データの少なくとも一方に応答してフィードバック機能を実行するためのフィードバック／フィードフォワード・ユニット（580）と、を有することを特徴とするシステム。

#### 【請求項7】

コンピュータによって実行されたときに、

処理のため第1の半導体ウェハ（105）を受け取るステップと、

処理のため第2の半導体ウェハ（105）を受け取るステップと、

前記第1の半導体ウェハおよび前記第2の半導体ウェハ（105）に対してカスケード処理操作を実行するステップと、を有し、前記カスケード処理操作は、前記第1の半導体ウェハ（105）が処理されている期間の少なくとも一部の間に、前記第2の半導体ウェハ（105）に関連するプロセス前計測データを取得する方法を実行する命令と共に符号化されたコンピュータ可読プログラム記録デバイス。

#### 【請求項8】

コンピュータによって実行されたときに、請求項7に記載の方法を実行する命令と共に符号化されたコンピュータ可読プログラム記録装置であって、前記方法は、前記第2の半導体ウェハ（105）が処理されている期間の少なくとも一部の間に、前記第1の半導体ウェハ（105）に関連するプロセス後計測データを取得するステップをさらに有するコンピュータ可読プログラム記録デバイス。

#### 【請求項9】

コンピュータによって実行されたときに、請求項7に記載の方法を実行する命令と共に符号化されたコンピュータ可読プログラム記録装置であって、プロセス前計測データを取得する前記ステップは、組み込み計測装置（310）を使用してプロセス前計測データを取得するステップをさらに有するコンピュータ可読プログラム記録デバイス。

#### 【請求項10】

コンピュータによって実行されたときに、請求項7に記載の方法を実行する命令と共にエンコードされたコンピュータ可読プログラム記録装置であって、前記第1の半導体ウェハおよび前記第2の半導体ウェハ（105）に対してカスケード処理操作を実行する前記ステップは、

前記第1の半導体ウェハ（105）からプロセス前計測データを取得するステップと、前記第1の半導体ウェハ（105）から前記プロセス前計測データを取得したことに応答して、前記第1の半導体ウェハ（105）を処理するステップと、

前記第1の半導体ウェハ（105）が処理されている期間の少なくとも一部の間に、前記第2の半導体ウェハ（105）からプロセス前計測データを取得するステップと、

前記第1の半導体ウェハ（105）の前記処理に応答して、前記第1の半導体ウェハ（105）からプロセス後計測データを取得するステップと、

前記第1の半導体ウェハ（105）に関連する（105）プロセス後計測データが取得されている期間の少なくとも一部の間に、前記第2の半導体ウェハ（105）から前記プロセス前計測データを取得したことに応答して、前記第2の半導体ウェハ（105）を処理するステップと、

前記第2の半導体ウェハ（105）の前記処理に応答して、プロセス後計測データを取得するステップと、を有するコンピュータ可読プログラム記録デバイス。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、一般に半導体製造に関し、より詳細には、半導体ウェハのカスケード処理を実

10

20

30

40

50

行する方法および装置に関する。

【背景技術】

【0002】

製造業における爆発的な技術の進歩により、新しい革新的な製造プロセスが数多く生み出された。今日の製造プロセス、とりわけ半導体製造プロセスでは、多くの重要な工程が必要とされる。通常、これらはプロセスの中核をなす工程であり、このため、通常多くの入力を微調整して、生産を適切に制御する必要がある。

【0003】

半導体デバイスの製造においては、半導体の原材料からパッケージング済みの半導体デバイスを製造するまでに、別個のプロセス工程が数多く要求される。半導体材料を成長させる最初の工程から、半導体結晶を切断して個々のウェハを作製する工程、製造段階（エッチング、ドーピング、イオン注入等）、パッケージング、完成したデバイスの最終検査に至るまでの各種プロセスはそれぞれ非常に異なり、特化されているため、これらのプロセスは、異なる制御方式を採用している別の製造場所で実施されることがある。

【0004】

一般に、プロセス工程の集まりは、時にロットと呼ばれる半導体ウェハの集合体に対して実行される。例えば、さまざまな材料から構成されるプロセス層が、ウェハの上部に形成され得る。続いて、公知のフォトリソグラフィ技術によって、このプロセス層の上部にパターン形成したフォトレジスト層が形成され得る。通常はこの後に、パターン形成したフォトレジスト層をマスクとして使用して、プロセス層に対してエッチング・プロセスが実行される。このエッチング・プロセスによって、プロセス層に、フィーチャーと呼ばれるさまざまな構造やオブジェクトが形成される。このような構造は、トランジスタのゲート電極構造として使用することができる。また、半導体ウェハの基板にトレチ（溝）構造が形成されることがよくある。トレチ構造の一例として、浅部トレチ・アイソレーション(Shallow Trench Isolation: STI)構造があり、この構造は、半導体ウェハ上にある電気的領域の絶縁に用いられることがある。典型的には、テトラエトキシシラン(TEOS)を使用してウェハおよびSTI構造に二酸化シリコンを形成することによって、半導体ウェハに形成されたSTI構造に埋め込みが行われる。

【0005】

通常は、半導体製造施設にある製造装置は、製造フレームワークすなわち処理の各構成要素のネットワークと相互に通信を行っている。各製造装置は、通常は装置インターフェースと接続されている。装置インターフェースは、製造ネットワークが接続されているマシン・インターフェースに接続されており、これにより、製造装置と製造フレームワークとの間の通信が可能となる。概して、マシン・インターフェースは、高度プロセス制御(Advanced Process Control System: APC)システムの一環をなしうる。APCシステムは、制御スクリプトを起動する。この制御スクリプトは、製造プロセスの実行に必要とされるデータを自動的に取得するソフトウェア・プログラムであり得る。

【0006】

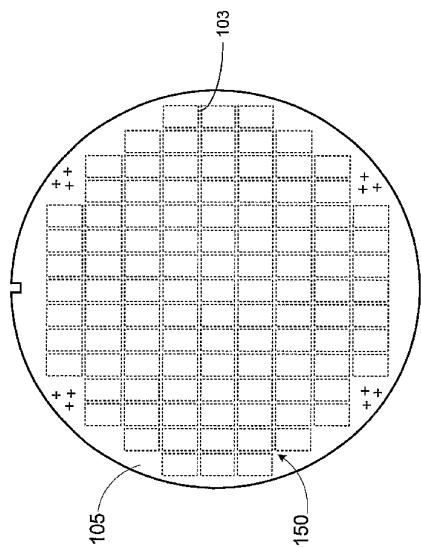

図1に、代表的な半導体ウェハ105を示す。通常、ウェハ105は、格子150に配置された複数の半導体ダイ103を含んでいる。使用するフォトマスクによって異なるが、ステッパーにより、一度に約1~4のダイ位置に対してフォトリソグラフィが行われる。フォトリソグラフィ工程は、通常は、パターンを形成しようとしている1つ以上のプロセス層の上部に、パターン形成したフォトレジスト層を形成するために行われる。パターン形成したフォトレジスト層は、その下のポリシリコン、金属または絶縁材料の層などの材料の層に対して実施されるウェット・エッチングまたはドライ・エッチングのプロセス中にマスクとして使用され、下地層に所望のパターンが転写される。パターン形成したフォトレジスト層は、複数の構造を有する。この例には、ポリシリコンのラインなどの線状の構造や、開口状の構造などがあり、これらが下地のプロセス層に複製される。

【0007】

半導体ウェハの製造時に行われる従来の手順では、複数の工程を連続して実行する必要が

10

20

30

40

50

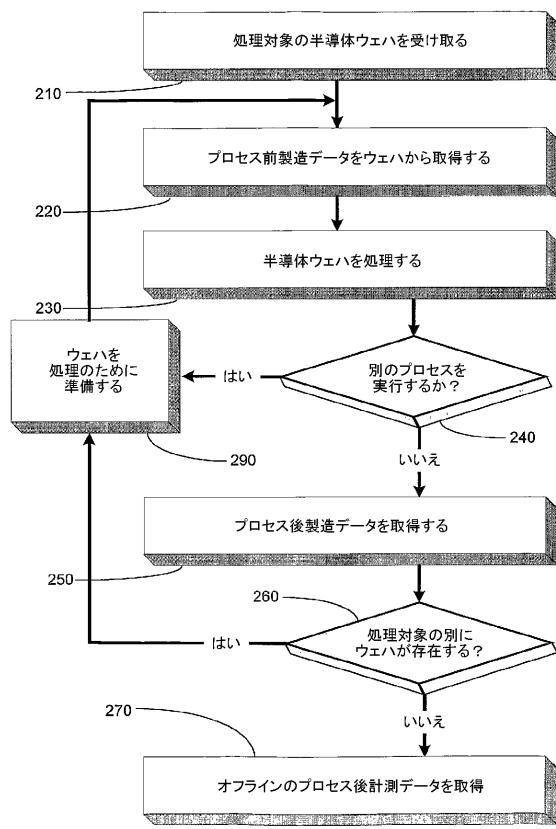

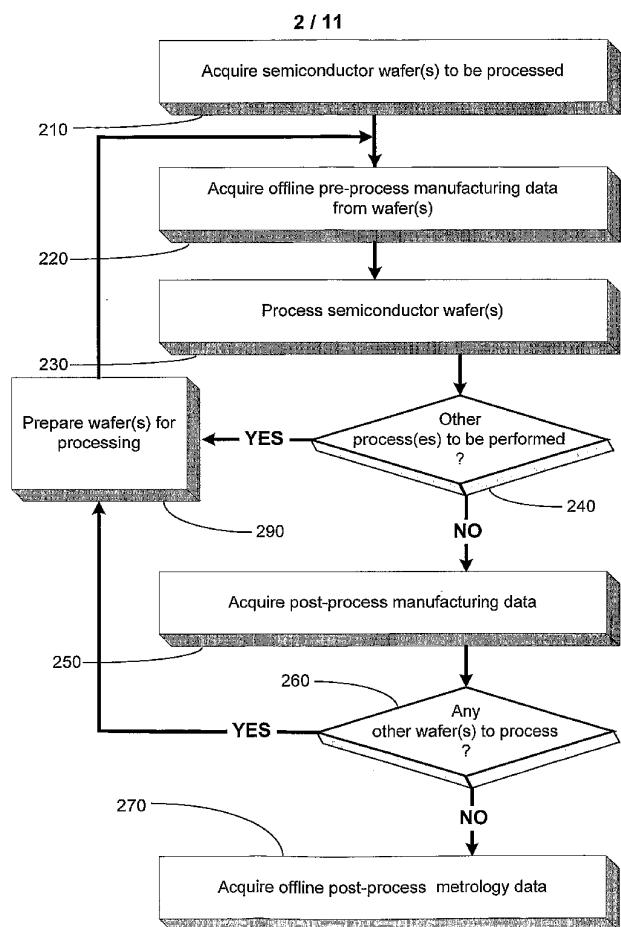

ある。図2に、このような工程のフローチャートを示す。製造システムが、処理しようとしている半導体ウェハ105を受け取る(ブロック210)。製造システムは、ウェハ105の組を受け入れると、半導体ウェハ105から、プロセス前の製造データ(例えば、計測データ等)を取得する(ブロック220)。

#### 【0008】

一部のプロセスでは、ウェハ105から取得するこの製造データが、半導体ウェハ105のプロセス前スクリーニングに関わることがある。例えば、化学機械研磨(CMP)プロセスの実行前に、処理しようとしている半導体ウェハ105から得たプロセス前データを使用して、CMPプロセスを変更する制御パラメータを設定してもよい。製造システムは、プロセス前データを取得すると、半導体ウェハ105を処理する(ブロック230)。10

#### 【0009】

製造システムは、半導体ウェハ105の処理を終えると、半導体ウェハ105に対して別のプロセスを実行する必要があるかどうかを判断する(ブロック240)。製造システムが、半導体ウェハ105に別のプロセスを実行する必要があると判断すると、プロセス前計測データが取得され、半導体ウェハ105に対して別のプロセスが実行され得る(フローチャートのブロック230～ブロック240～ブロック220の経路を参照)。製造システムは、複数の処理装置を使用して、半導体ウェハ105に複数のプロセスを実行してもよい。

#### 【0010】

製造システムが、半導体ウェハ105に別のプロセスを実行する必要がないと判断すると、製造システムは、処理済みのウェハ105からプロセス後製造データを取得し得る(ブロック250)。通常、プロセス後製造データには、半導体ウェハ105に形成した複数の構造の測定値が含まれる。ブロック260において、処理すべき半導体ウェハ105が他に存在すると判断した場合、製造システムは次の処理対象ウェハ105を受け入れて、上記の処理を繰り返す(ブロック250, 270)。処理対象の半導体ウェハ105が他にない場合、製造システムは処理モードを終了する(ブロック270)。20

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0011】

図2に示した各工程は、一般に連続して実行されるため、プロセス・フローにおいて製造システムが頻繁に中断する。計測装置を使用したプロセス前データを取得し、続いてウェハ105を処理し、次にプロセス後製造データを取得することを連続して行うと、処理効率が低下しかねない。半導体ウェハのプロセス・フローにおいて中断が発生すれば、効率が低下し、エラーが発生する可能性がある。このような効率の低下による製造時間のロスは、コストを発生させるほか、製品の納期に悪影響を与えるおそれがある。また、半導体ウェハ105に生じたエラーにより、処理済みの半導体ウェハ105から得られるデバイスの歩留まりが低下するおそれもある。30

#### 【0012】

本発明は、上記の問題のうちの1つ以上を克服するか、少なくとも軽減することを目的とする。40

##### 【課題を解決するための手段】

#### 【0013】

本発明の一態様においては、半導体ウェハの処理のカスケード制御を実行するための方法が提供される。半導体ウェハの処理のカスケード制御を実行する方法および装置が提供される。処理のため第1の半導体ウェハが受け入れられる。処理のため第2の半導体ウェハが受け入れられる。第1の半導体ウェハおよび第2の半導体ウェハに対するカスケード処理操作が実行される。このカスケード処理操作には、第1の半導体ウェハを処理している期間の少なくとも一部の間に、第2の半導体ウェハに関連するプロセス前計測データを取得することが含まれる。

#### 【0014】

10

20

30

40

50

本発明の別の態様においては、半導体ウェハの処理のカスケード制御を実行するシステムが提供される。本発明のシステムは、カスケード処理操作を実行するプロセス制御装置を有し、カスケード処理操作は、第1の半導体ウェハに関連するプロセス前データを取得することと、第1の半導体ウェハに関連するプロセス前計測データを取得した後に、第1の半導体ウェハを処理することと、第1の半導体ウェハを処理している期間の少なくとも一部の間に、第2の半導体ウェハに関連するプロセス前データを取得することと、第2の半導体ウェハに関連するプロセス前データを取得した後に、第2の半導体ウェハを処理することと、第2の半導体ウェハを処理している期間の少なくとも一部の間に、第1の半導体ウェハに関連するプロセス後データを取得することと、第2の半導体ウェハの処理の後に、第2の半導体ウェハに関連するプロセス後データを取得することとを含む。また、このシステムは、プロセス制御装置と作動的に結合され、インラインのプロセス前計測データおよびインラインのプロセス後計測データの少なくとも一方を受け取るためのインライン・カスケード計測データ記録ユニットと、プロセス制御装置およびインライン・カスケード計測データ記録ユニットと作動的に結合され、インラインのプロセス前計測データおよびインラインのプロセス後計測データの少なくとも一方に応答してフィードバック機能を実行するためのフィードバック／フィードフォワード・ユニットとを有する。

【発明を実施するための最良の形態】

【0015】

添付の図面と併せて下記の説明を読めば、本発明が理解されるであろう。添付の図面においては、同一の参照符号は同じ要素を指している。

【0016】

本発明は、種々に変形および代替形態を取り得るが、その特定の実施形態が、図面に例として図示され、ここに詳細に記載されているに過ぎない。しかし、詳細な説明は、本発明を特定の実施形態に限定することを意図するものではなく、反対に、添付の特許請求の範囲によって規定される本発明の精神ならびに範囲に含まれる全ての変形例、均等物および代替例を含むことを理解すべきである。

【0017】

本発明の例示的な諸実施形態を下記に記載する。簡潔を期すために、本明細書に実際の実装の特徴を全て記載することはしない。当然、実際の実施形態の開発においては、システム上の制約およびビジネス上の制約に適合させるなど、開発の具体的な目的を達するために、実装に固有の判断が数多く必要とされ、この判断は実装によって変わるということが理解される。さらに、この種の開発作業は複雑かつ時間がかかるものであるが、本開示による利益を受ける当業者にとって日常的な作業であるということが理解されよう。

【0018】

半導体製造に関わる数多くの別個のプロセスが存在する。多くの場合、半導体デバイスが複数の製造プロセス装置で処理される。一部のプロセスの実行前および実行後の少なくともいづれかにおいて、計測データなどの製造データの収集が行われることが多い。例えば、化学機械研磨（C M P）プロセスを実行する前に、プロセス前データを収集して、研磨量を決定することが望ましい。同様に、堆積プロセスの後に、半導体ウェハに堆積された材料の量を決定するため、および半導体ウェハに行う後続のプロセスの制御パラメータを調整するためにプロセス後データを収集することが望ましい。しかし、プロセス前計測データおよびプロセス後計測データを取得すること、特にオフライン方式で取得することにより、製造プロセス・フローの効率が低下する可能性がある。本発明の種々の実施形態では、計測データの取得工程と製造プロセス工程とをカスケード方式で実行し、これにより処理フローの効率を向上させる。

【0019】

一実施形態においては、本発明の諸実施形態によるカスケーディング制御システムとは、ネストされた制御ループ・システムを指す。本発明の諸実施形態によるカスケード・システムは、内側のウェハ間制御ループ（例えば、第1のフィードバック・ループ）と、外側のロット間制御ループ（例えば、第2のフィードバック・ループ）とを提供する。一実施

形態においては、内側のフィードバック・ループはウェハ間制御ループを提供し、外側のフィードバック・ループはロット間制御ループを提供する。これについては、図7とその説明に記載する。

#### 【0020】

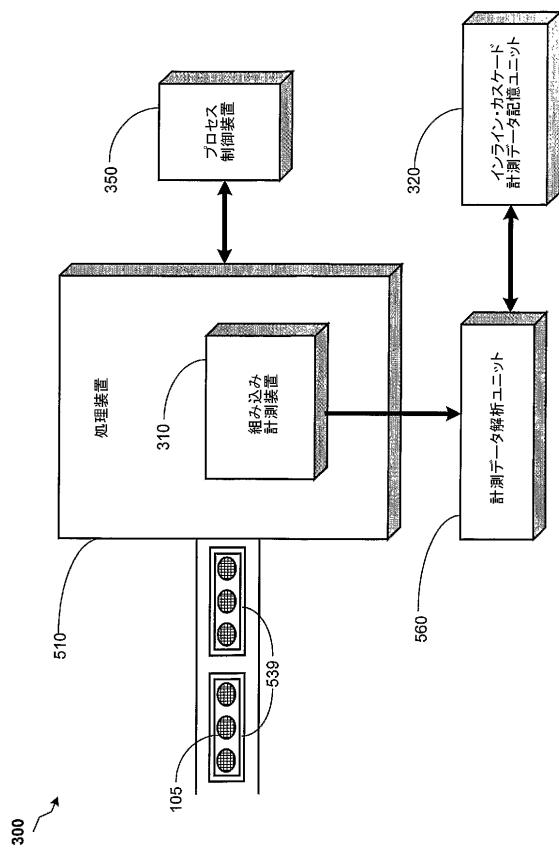

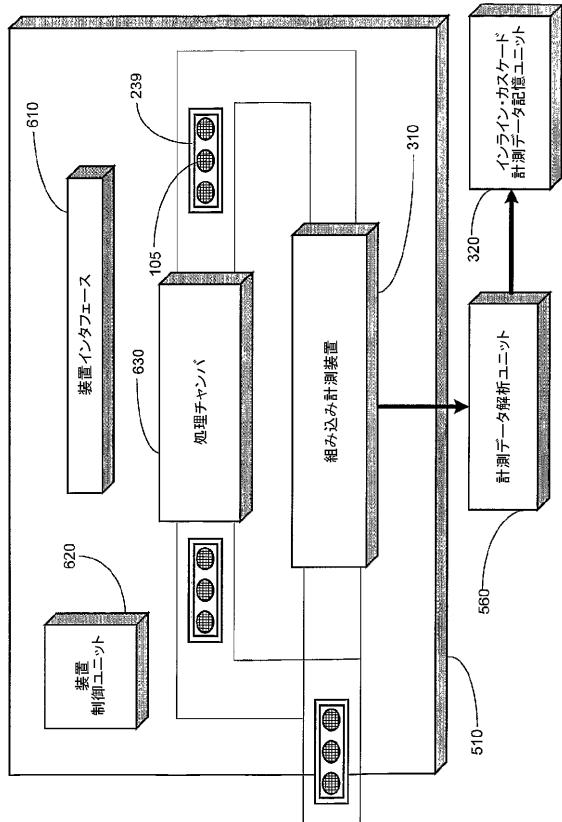

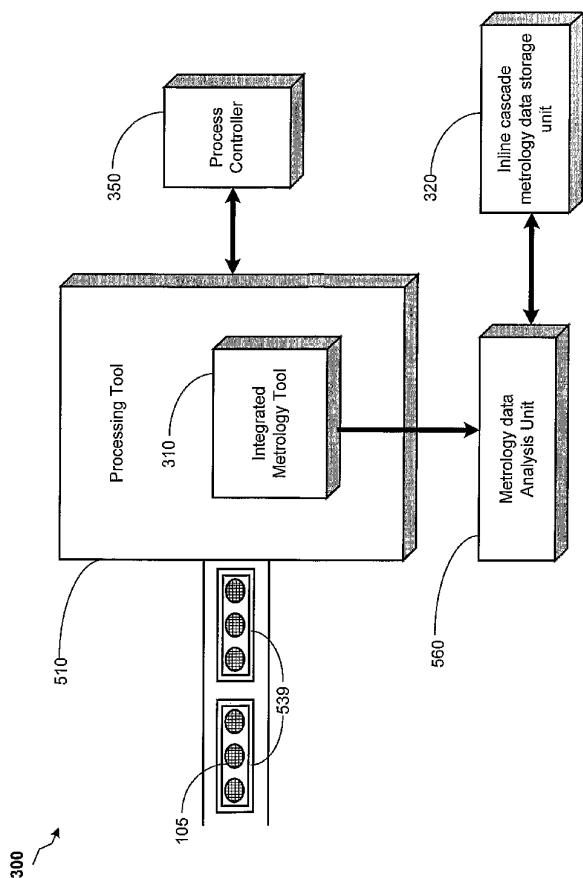

図3に、本発明の一実施形態が教示する方法を実行可能なシステム300を示す。一実施形態においては、処理装置510は、組み込み計測装置310を備える。一実施形態においては、組み込み計測装置310は、インライン計測データを取得する（例えば、半導体ウェハ105が処理装置510の制御下にあるときに、半導体ウェハ105の計測データを取得するなど）ことができる。インライン計測データの取得は、一般に、外部の計測データ装置を使用する必要があるオフライン計測データの取得に比べ、製造プロセス・フローを阻害する程度が低い。カセット539に納められた半導体ウェハ105の組が、処理装置510に提供される。本発明の諸実施形態は、組み込み計測装置310を使用してカスケード処理機能を実行するための処理装置510を備えている。カスケード処理機能を実行する処理は、プロセス制御装置350によって制御されている。

10

#### 【0021】

一実施形態においては、カスケード処理機能には、複数の製造機能を連続して実行するか、重複して実行するか、この両方を行うことが含まれる。例えば、本発明の一実施形態によるカスケード処理機能においては、半導体ウェハ105の第1の組に関連したプロセス前計測データを取得することと、半導体ウェハ105の第2の組のプロセス前データが取得されている期間の少なくとも一部の間に、半導体ウェハ105の第1の組を処理することと、半導体ウェハ105の第2の組の処理が実行されている期間の少なくとも一部の間に、半導体ウェハ105の第1の組に関連したプロセス後計測データを取得することを提供する。このようなカスケード処理は、複数の半導体ウェハ105を処理して解析する処理フローの効率を一層向上させる。一実施形態においては、プロセス前計測データとプロセス後計測データとは、組み込み計測装置によって取得される。これについては下記に詳細に記載する。

20

#### 【0022】

組み込み計測装置310によって取得されたデータは、計測データ解析ユニット560に送られる。計測データ解析ユニット560は、オフライン計測装置550（図5参照）によって取得された計測データをまとめ、解析して、検査された特定の半導体ウェハ105と関連付ける。計測データ解析ユニット560は、ソフトウェア・ユニット、ハードウェア・ユニット、またはファームウェア・ユニットのいずれであってもよい。種々の実施形態においては、計測データ解析ユニット560は、コンピュータ・システム530に組み込まれていても、あるいはオフライン計測装置550に組み込まれていてもよい。

30

#### 【0023】

一実施形態においては、システム300は、カスケード処理操作の実行中に、組み込み計測装置310によって取得されたインライン・カスケード計測データを、インライン・カスケード計測データ記録ユニット320に記録する。インライン・カスケード計測データ記録ユニット320に記録される計測データには、半導体ウェハ105に形成された構造の線幅、STIトレーナーのトレーナー深さ、半導体ウェハ105に形成されたトレーナー構造の（垂直面に対する）側壁角などを表すデータの組が含まれる。一実施形態においては、インライン・カスケード計測データ記録ユニット320にあるデータは、半導体ウェハ105の処理の効率および精度を向上させるためのフィードバック補正に使用され得る。

40

#### 【0024】

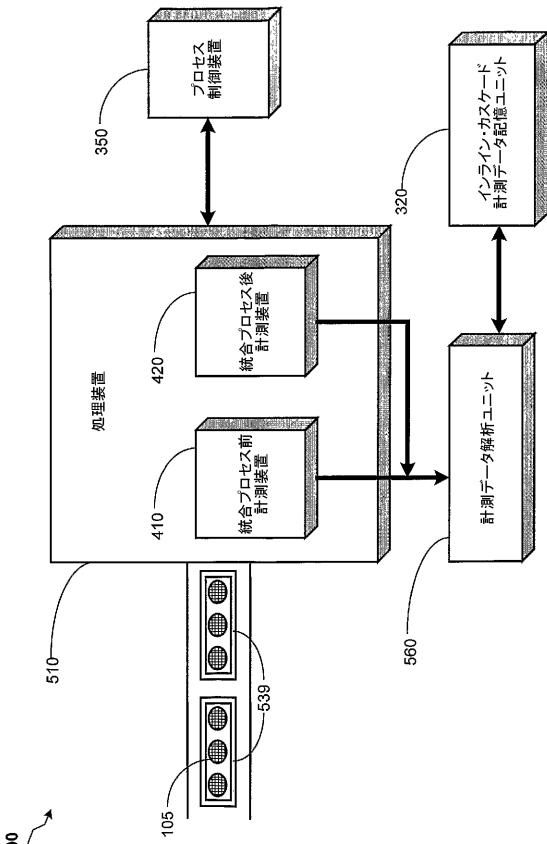

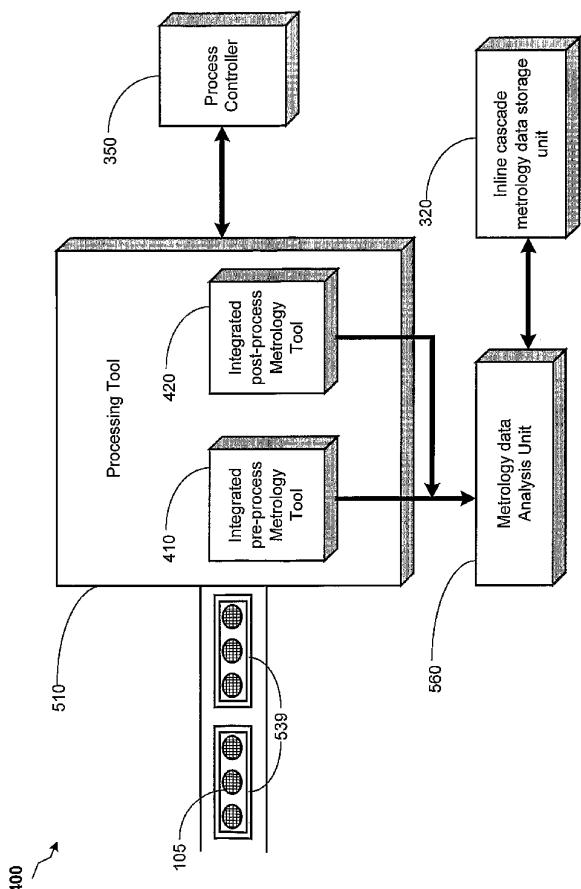

図4を参照すると、カスケード処理機能を実行するためのシステム300に用いられる処理装置510の別の実施形態が示される。図4に示す処理装置510は、組み込みプロセス前計測装置410と組み込みプロセス後計測装置420とを備える。半導体ウェハ105は、処理される前に組み込みプロセス前計測装置410によって解析される。例えば、処理装置が半導体ウェハ105に対してCMPプロセスを実行する前に、組み込みプロセス前計測装置410によって半導体ウェハ105が解析される。こうして得られたプロセ

50

ス前計測データは、その後 C M P プロセスをより正確に制御するために用いることができる。

#### 【 0 0 2 5 】

多くの場合、半導体ウェハ 105 の処理の後に、処理装置 510 が、組み込みプロセス後計測装置 420 を使用してプロセス後計測データを取得する。その間に、第 2 のカセット 539 に格納されている半導体ウェハ 105 の第 2 の組が、組み込みプロセス前計測装置 410 に送られて解析された後、処理装置 510 によって処理される。処理装置 510 は、カスケード処理方式を使用することによって、プロセス前データの取得と、半導体ウェハ 105 の処理と、プロセス後の組み込み計測データの取得とをカスケード方式で実施できるようになり、処理装置 510 の機能を同時に、かつ効率の高い方法で利用できるようになる。組み込みプロセス前計測装置 410 と組み込みプロセス後計測装置 420 とは、各々データを計測データ解析ユニット 560 に送って処理させる。次に、計測データがインライン・カスケード計測データ記録ユニット 320 に記録されて、後に、システム 300 が、より効率的なフィードバック解析を実行するためにこのデータを利用できるようにする。図 4 に示すカスケード処理機能の実行処理は、プロセス制御装置 350 によって制御されている。10

#### 【 0 0 2 6 】

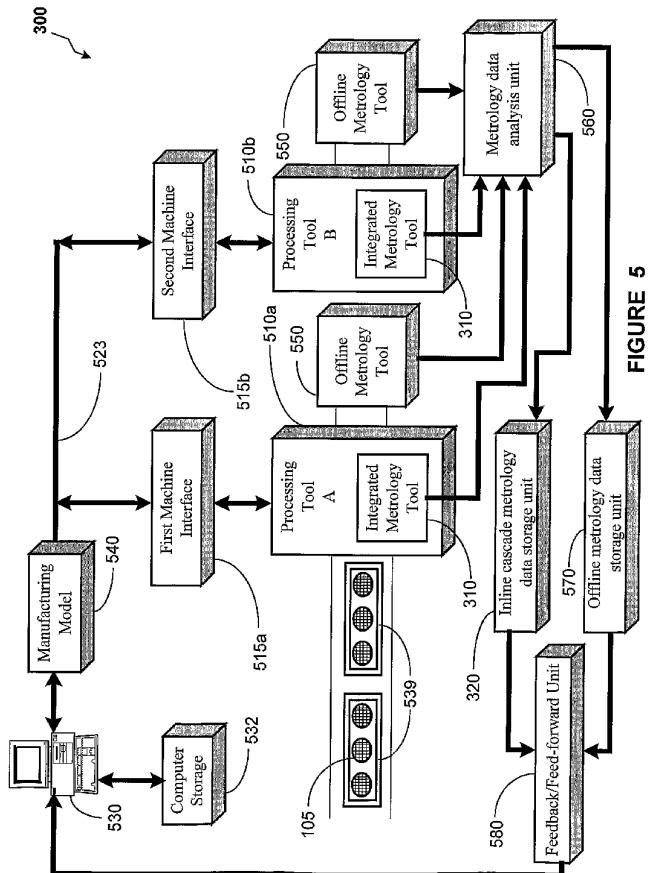

図 5 に、本発明の一実施形態によるシステム 300 の詳細ブロック図を示す。一実施形態においては、半導体ウェハ 105 は、線 523 に示す複数の制御入力信号、すなわち製造パラメータを用いて、処理装置 510a, 510b によって処理される。一実施形態においては、線 523 に示す複数の制御入力信号すなわち製造パラメータが、マシン・インターフェース 515a, 515b を介してコンピュータ・システム 530 から処理装置 510a, 510b に送信される。一実施形態においては、第 1 マシン・インターフェース 515a および第 2 マシン・インターフェース 515b は、処理装置 510a, 510b の外部に存在する。別の実施形態においては、第 1 マシン・インターフェース 515a および第 2 マシン・インターフェース 515b は、処理装置 510a, 510b の内部に存在する。半導体ウェハ 105 が複数の処理装置 510 に供給されて、そこから搬出される。一実施形態においては、半導体ウェハ 105 は、処理装置 510 に手動で供給される。別の実施形態においては、半導体ウェハ 105 は、処理装置 510 に自動で（例えば、ロボットによる半導体ウェハ 105 の移送などにより）供給される。一実施形態においては、複数の半導体ウェハ 105 はロット単位で（例えば、カセット 539 内に並べて）処理装置 510 に搬送される。20

#### 【 0 0 2 7 】

一実施形態においては、コンピュータ・システム 530 は、第 1 マシン・インターフェース 515a および第 2 マシン・インターフェース 515b に、線 523 に示す制御入力信号、すなわち製造パラメータを送信する。コンピュータ・システム 530 は、処理操作を制御することができる。コンピュータ・システム 530 は、コンピュータ記録装置 532 に結合されており、コンピュータ記録装置 532 は、複数のソフトウェア・プログラムおよびデータの組を有し得る。コンピュータ・システム 530 は、本明細書に記載の操作を実行することができる 1 つのプロセッサ（図示なし）を少なくとも 1 つ備え得る。コンピュータ・システム 530 は、製造モデルを使用して、線 523 に示す制御入力信号を生成する。一実施形態においては、製造モデル 540 は、線 523 で送信される複数の制御入力パラメータを決定する製造レシピを有している。30

#### 【 0 0 2 8 】

一実施形態においては、製造モデル 540 は、特定の製造プロセスを実現する処理スクリプトおよび入力制御を定義する。処理装置 A 510a に宛てた線 523 の制御入力信号（または制御入力パラメータ）は、第 1 マシン・インターフェース 515a によって受理され処理される。処理装置 B 510b に宛てた線 523 の制御入力信号は、第 2 マシン・インターフェース 515b によって受理され処理される半導体製造プロセスにおいて使用される処理装置 510a, 510b の例として、ステッパー装置やエッチング・プロセス装40

10

20

30

40

50

置などがある。

【0029】

処理装置510a, 510bによって処理された1枚以上の半導体ウェハ105は、オフライン計測装置550に送信されて、計測データが取得され得る。オフライン計測装置550は、光波散乱計測データ取得装置、重ね合わせエラー測定装置、微小寸法測定装置(critical dimension measurement tool)などであり得る。一実施形態においては、1枚以上の処理済み半導体ウェハ105が計測装置550によって検査される。さらに、処理装置510内の組み込み計測装置310によって計測データが収集される。組み込み計測装置310が取得したデータとオフライン計測装置550が取得したデータとは、計測データ解析ユニット560によって収集される。このデータには、線幅の測定値、トレンチ深さ、側壁角などが含まれ得る。上記したように、計測データ解析ユニット560は、オフライン計測装置550によって取得されたデータをまとめ、解析して、検査された特定の半導体ウェハ105と関連付ける。10

【0030】

一実施形態においては、計測データ解析ユニット560は、組み込み計測装置310からのインライン・カスケード計測データを記録するため、これをインライン・カスケード計測データ記録ユニット320に送る。さらに、計測データ解析ユニット560は、オフライン計測データを記録するため、これをオフライン計測データ記録ユニット570に送る。システム300は、オンライン・カスケード計測データとオフライン計測データとを取得して、フィードバック解析およびフィードフォワード解析を実行することができる。オンライン計測データとオフライン計測データとは、フィードバック・データとフィードフォワード・データとを生成するために、フィードバック/フィードフォワード・ユニット580に送られる。フィードバック・データとフィードフォワード・データとは、コンピュータ・システム530によって解析される。その後、コンピュータ・システム530は、製造モデル540を使用して、処理装置510の動作を制御する制御入力パラメータを変更する。一実施形態においては、オンライン・カスケード計測データ記録ユニット320、オフライン計測データ記録ユニット570およびフィードバック/フィードフォワード・ユニット580のうちの少なくともいずれかは、独立したユニットとして使用されることもあれば、コンピュータ・システム530に組み込まれることもあるソフトウェア部品またはファームウェア部品である。20

【0031】

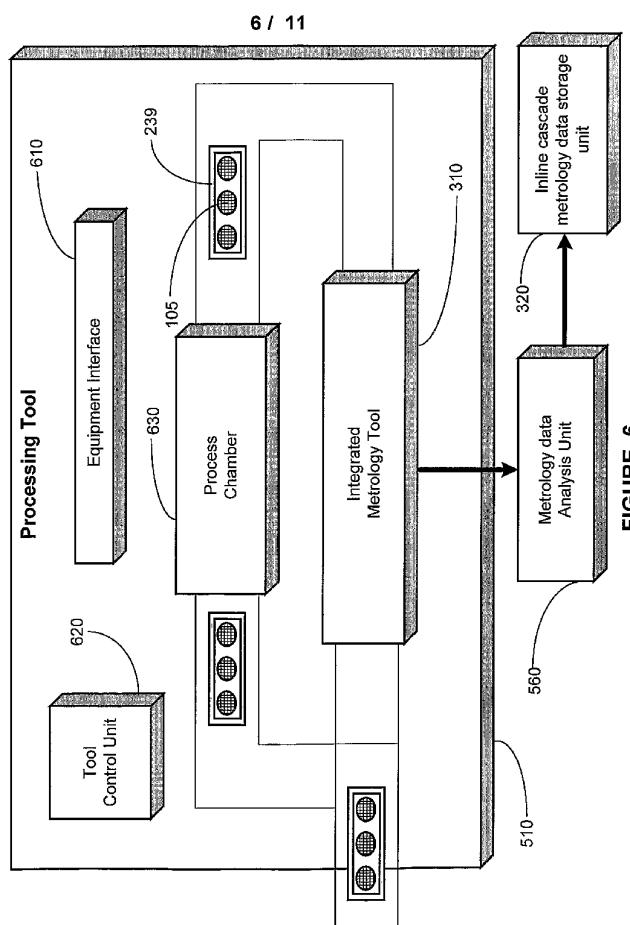

図6は、本発明の一実施形態による処理装置および処理フローをさらに詳細に示す図である。一実施形態においては、処理装置は、装置インタフェース610、装置制御ユニット620、処理チャンバ630および組み込み計測装置310を備える。装置インタフェース610は、処理装置510と、コンピュータ・システム530、製造モデル540、マシン・インタフェース515などのシステム300の別の部分とが通信できるようにする。装置制御ユニット620は、処理装置510の動作を制御する。装置制御ユニット620は、装置インタフェース610を介してコンピュータ・システム530から命令およびデータを受け取ることができる。また、装置制御ユニット620は、装置インタフェース610を介してシステム300の他の部分に組み込み計測データなどのデータを送信することもできる。30

【0032】

カセット539に格納されている半導体ウェハ105の第1の組が、処理装置510によって受け入れられ、組み込み計測装置310によって検査されてプロセス前計測データが取得される。次に、半導体ウェハ105の第1の組は、処理のためチャンバ630に搬送される。その間に、プロセス前計測データを取得するために、組み込み計測装置310が半導体ウェハ105の第2の組を受け入れる。40

【0033】

半導体ウェハ105の第2の組から計測データを取得しているほぼその間に、半導体ウェハ105の第1の組が、チャンバ630によって処理され得る。半導体ウェハ105の第50

1の組の処理が完了すると、装置制御ユニット620は、処理が完了した半導体ウェハ105の第1の組からプロセス後計測データを取得するよう、組み込み計測装置310に指示する。その間に、半導体ウェハ105の第2の組が、処理のためチャンバ630に搬送される。このカスケード処理システムは、多量の計測データを迅速に取得し、このデータはフィードバック解析に即時に使用することができる。組み込み計測装置310によって取得されたデータは、計測データ解析装置560に送られる。次に、この計測データは、システム300がフィードバック処理を行うために取得できるよう、インライン・カスケード計測データ記録ユニット320に記録される。続いて、半導体ウェハ105の第3、第4、第5～第nの組が、上記のカスケード方式によって処理されて、処理装置510が効率的に使用される。さらに、本発明の諸実施形態を使用すれば、計測データを、フィードバック処理およびフィードフォワード処理のため即時に使用できるようになる。10

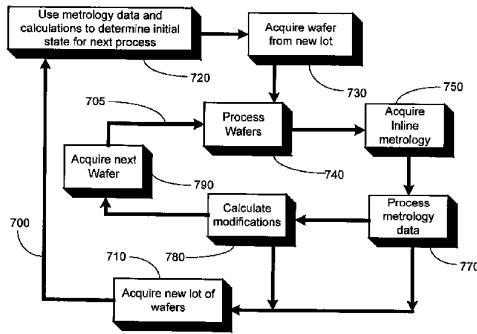

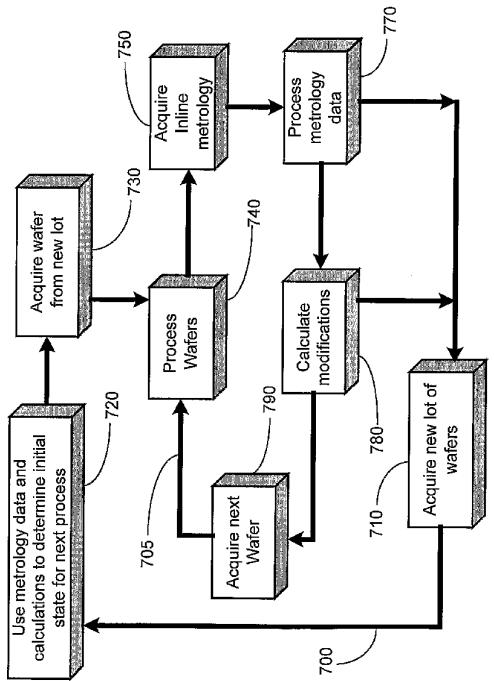

#### 【0034】

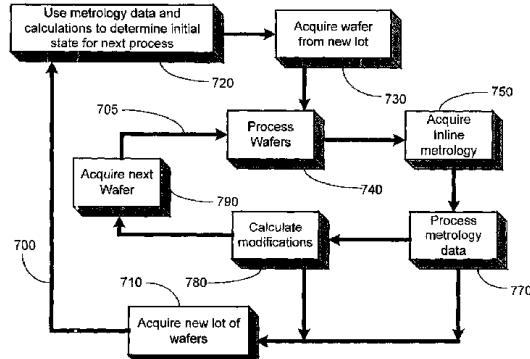

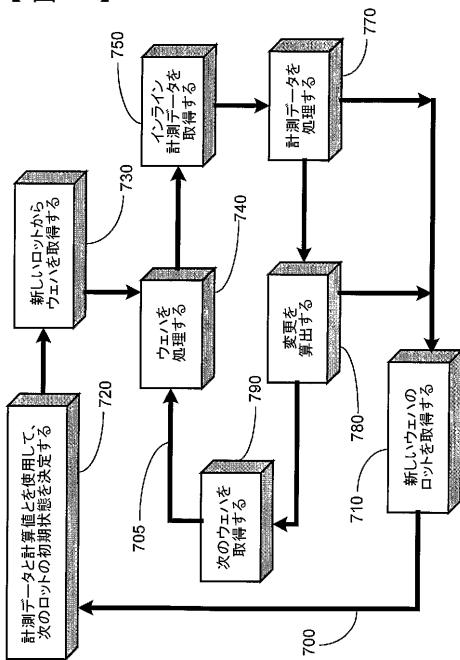

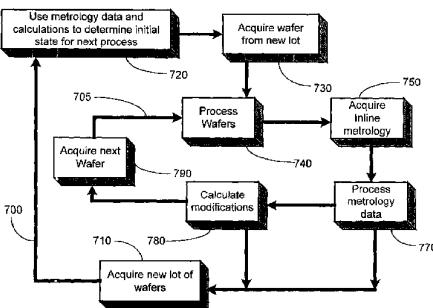

一実施形態においては、本発明の諸実施形態が教示する方法を使用したシステム300は、複数のフィードバック・ループを使用して、半導体ウェハ105の製造の効率および精度を向上させている。図7に、半導体ウェハの製造時に使用される2つのフィードバック・ループを示す。システム300によって使用されるフィードバック・ループには、ラン・ツー・ランのフィードバック・ループ(run-to-run feedback loop)700とウェハ間のフィードバック・ループ705とが含まれる。2つのフィードバック・ループ(700, 705)は、製造プロセス中に協調して使用され、制御入力パラメータが調整される。換言すれば、この2つのフィードバック・ループ(700, 705)は、半導体ウェハ105の処理中のカスケーディング制御機能の実行に使用され得る。20

#### 【0035】

内側のループは、ウェハ間のフィードバック・ループ705であり、半導体ウェハ105の処理(ロック740)と、処理が完了した半導体ウェハ105からのインライン計測データの取得(ロック750)とが含まれる。次に、システム300はこの計測データを処理する。この処理には、半導体ウェハ105に存在するエラー量の算出が含まれる(ロック770)。システム300は、このエラーに基づいて、処理装置510を制御する制御入力パラメータの変更を算出する(ロック780)。続いて、システムは、次に処理する半導体ウェハ105を取得して、このウェハ105が、変更された制御入力パラメータを用いて処理され(ロック790～ロック740)、ウェハ間のフィードバック・ループ705が形成される。30

#### 【0036】

ウェハ間のフィードバック・ループ705によって、1枚の半導体ウェハ105の処理から得たエラーを、インライン計測装置310によって迅速に取得することができる。続いてこの計測データが処理されて、次の半導体ウェハ105を処理するためのフィードバック・データとして使用される。図7に示すウェハ間のフィードバック・ループ705により、半導体ウェハ105の特定のロットのエラーをより正確に訂正できるようになる。

#### 【0037】

算出されたエラー量と変更値とを収集して、次の半導体ウェハ105の組のエラーを訂正することによって、ラン・ツー・ランのフィードバック・ループ700が、ウェハ間のフィードバック・ループ705とほぼ同時に形成される。システム300は、半導体ウェハ105の新しいロットを取得し(ロック710)、ウェハ間のフィードバック・ループ705で得たデータと計算値とを使用して、半導体ウェハ105の次のロットの処理に使用する制御入力パラメータの初期状態を定義する(ロック720)。次に、システム300は、新しい半導体ウェハ105のロットから半導体ウェハ105を取得し、処理のために搬送する(ロック730～ロック740)。続いて、ウェハ間のフィードバック・ループ705が繰り返されて、得られた計算値が、半導体ウェハ105の次のロットに使用される。このため、ラン・ツー・ランのフィードバック・ループ700とウェハ間のフィードバック・ループ705の2つのフィードバック・ループは、別個に使用することができると共に、時には並行して実行でき、処理済みの半導体ウェハ105をより効率的4050

かつ正確に製造できるようになる。

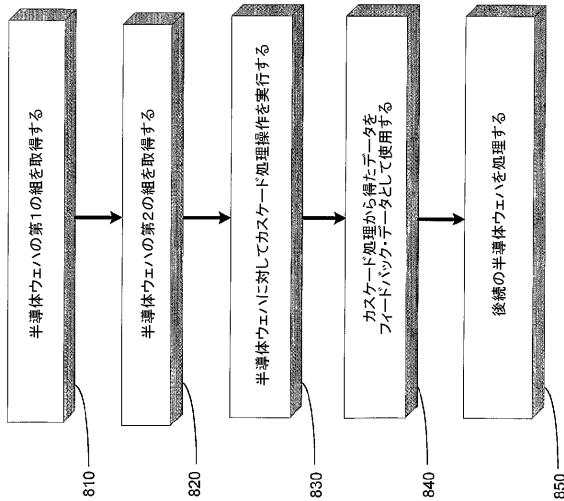

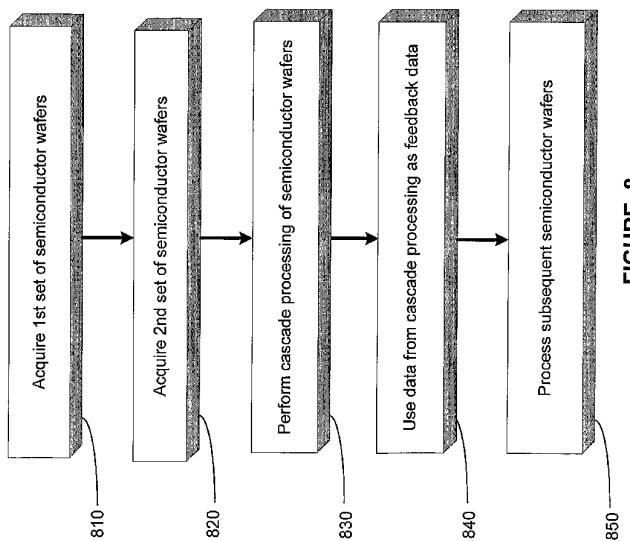

【0038】

図8に、本発明の一実施形態による方法を示すフローチャートを示す。システム300は、処理のため半導体ウェハ105の第1の組を取得する(ブロック810)。処理装置510の装置制御ユニット620は、受け取った半導体ウェハ105の第1の組を処理するために、装置インターフェース610を介してデータと制御入力パラメータとを受け取る。また、システム300は、半導体ウェハ105の第2の組を、処理のために処理装置510に送る(ブロック820)。

【0039】

一実施形態においては、半導体ウェハ105の第1の組と第2の組とは、カセット539に収納されて処理装置510に搬送される。別の実施形態においては、システム300は、種々のカセット539に入った半導体ウェハ105の組を3組以上受け入れてもよい。システム300は、半導体ウェハ105の複数の組に対してカスケード処理操作を実行する(ブロック830)。ブロック830に示すカスケード処理を実行する各ステップについては、下記に詳述する(図9参照およびその説明を参照のこと)。

【0040】

引き続き図8を参照すると、システム300は、カスケード処理操作をひとたび実行すると、カスケード処理操作によって得たデータをフィードバック・データとして使用する(ブロック840)。一実施形態においては、システム300は、カスケード処理中に取得した計測データを使用して、ラン・ツー・ランのフィードバック700のほか、ウェハ間のフィードバック705を実行する。システム300は、このフィードバック・データを使用して、検出されたエラーを低減させるため、変更された制御パラメータを用いて、後続のウェハ105を処理する(ブロック850)。

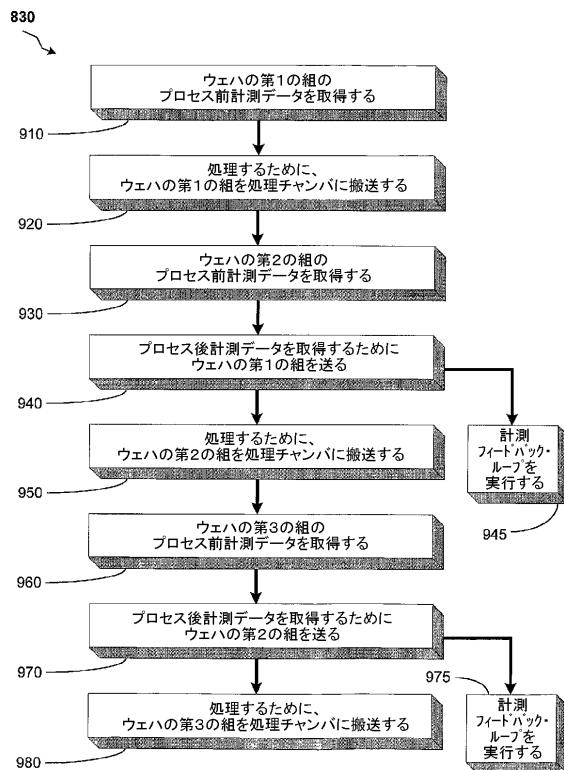

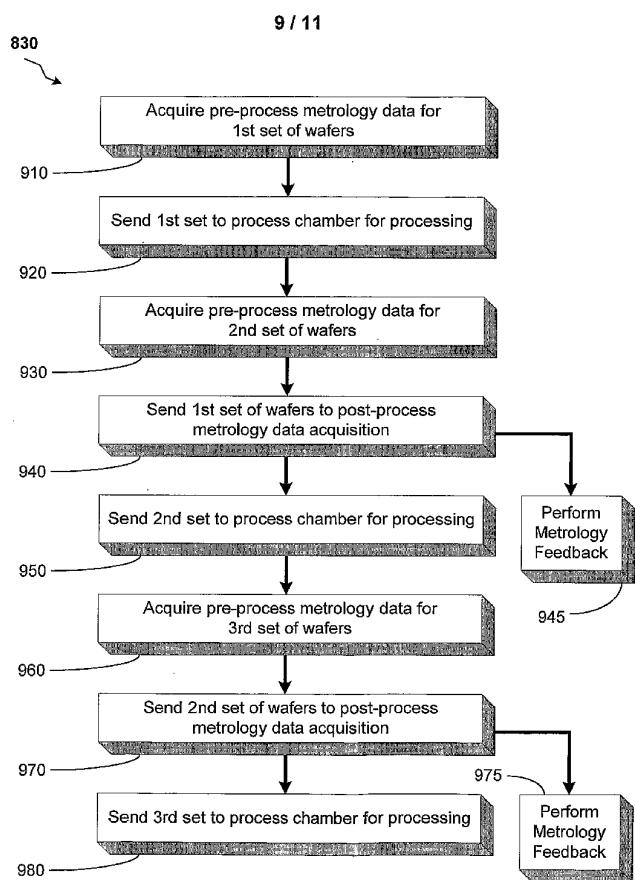

【0041】

図9に、本発明の一実施形態による、図8のブロック830に示すカスケード処理操作のステップを示すフローチャートを示す。システム300は、半導体ウェハ105の第1の組のプロセス前計測データを取得する(ブロック910)。一実施形態においては、プロセス前計測データの計測は、処理装置510内の組み込み計測装置310を使用して行われる。処理装置510が、半導体ウェハ105の第1の組からプロセス前計測データをひとたび取得すると、処理装置510は、半導体ウェハ105の第1の組を、処理のために、処理装置内の組み込み計測装置310から処理装置内の処理チャンバ630に搬送する(ブロック920)。一実施形態においては、装置制御ユニット620は、処理装置510内の半導体ウェハ105の複数の組の移動を制御する。

【0042】

次に、処理装置510は、半導体ウェハ105の第2の組からプロセス前計測データを取得する(ブロック930)。半導体ウェハ105の第2の組のプロセス前計測データは、組み込み計測装置310を使用して取得される。一実施形態においては、チャンバ630内での半導体ウェハ105の第1の組の処理と、組み込み計測装置310による、半導体ウェハ105の第2の組のプロセス前計測データの取得とが、時間的にほぼ並行して実行される。一実施形態においては、プロセス前計測データを使用して、後続の半導体ウェハ105の処理の制御設定を、フィードフォワード方式に変更することができる。

【0043】

半導体ウェハ105の第1の組の処理が完了すると、処理装置510は、半導体ウェハ105を、プロセス後計測データ取得ステップに送る(ブロック940)。一実施形態においては、プロセス後計測データの取得は、組み込み計測装置310によって実行される。別の実施形態においては、プロセス前計測データは、別個の組み込みプロセス前計測装置410によって取得され、プロセス後計測データの取得は、別個の組み込みプロセス後計測装置420によって実行される。図9に示す実施形態においては、プロセス前計測データとプロセス後計測データとは、いずれも組み込み計測装置310によって取得される。一実施形態においては、プロセス後計測データを使用して、前の半導体ウェハ105への

10

20

30

40

50

処理で生じたエラーを補償するために、後続の半導体ウェハ105の処理における制御設定を、フィードバック制御方式に変更することができる。

#### 【0044】

システム300が半導体ウェハ105の第1の組からプロセス後計測データを取得している間に、処理装置510は、半導体ウェハ105の第2の組を、処理のために処理チャンバ630に搬送する（ブロック950）。その間に、半導体ウェハ105の第1の組から取得したデータ（すなわち、プロセス前計測データおよびプロセス後計測データ）が使用されて、ウェハ間のフィードバック・ループ705およびラン・ツー・ランのフィードバック・ループ700の計測フィードバックが実行される（ブロック945）。計測フィードバック・ループを実行する実施形態の一例とその説明は下記に記載する（図11参照）10。

#### 【0045】

引き続き図9を参照すると、半導体ウェハ105の第2の組がチャンバ630内で処理されている間に、システム300は、半導体ウェハ105の第3の組を処理装置510に搬送する。半導体ウェハ105の第3の組は、組み込み計測データ取得ツール310に搬送されて、プロセス前計測データが取得される（ブロック960）。半導体ウェハ105の第2の組がチャンバ630で処理されると、半導体ウェハ105の第2の組が、プロセス後計測データ取得ステップに送られる（ブロック970）。続いて、半導体ウェハの第3の組が、処理のためチャンバ630に搬送される（ブロック980）。その間に、半導体ウェハ105の第2の組に関する計測データ（すなわち、半導体ウェハ105の第2の組に関するプロセス前計測データおよびプロセス後計測データ）を用いた第2の計測フィードバック処理が開始される（ブロック975）。このカスケード処理のプロセスが、組み込み計測装置310によって、半導体ウェハ105複数の組に対して繰り返され得る。20

#### 【0046】

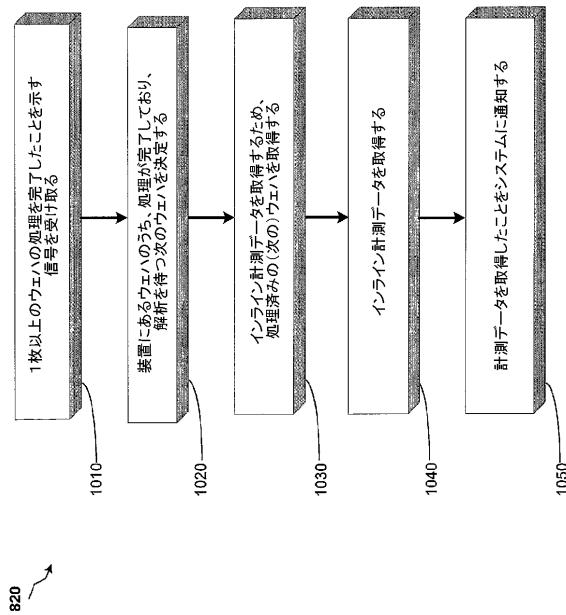

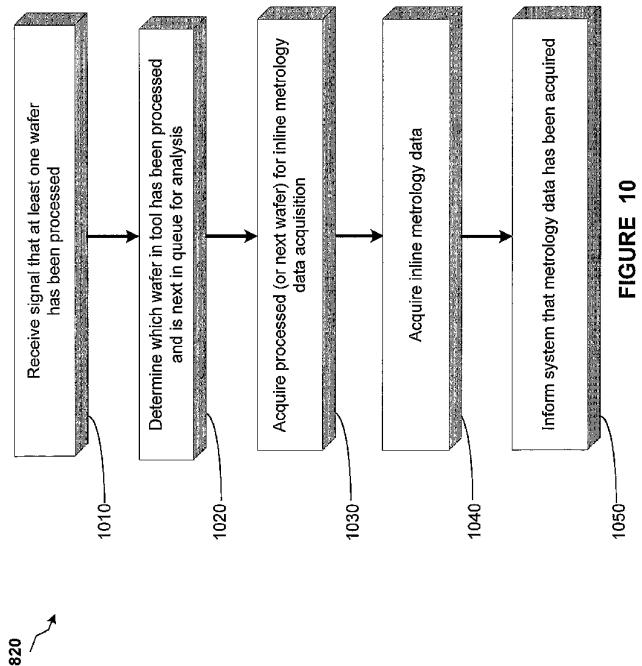

図10は、本発明の一実施形態による、ブロック910, 930, 960に示すオンライン計測データを取得するための方法を示すフローチャートである。システム300が半導体ウェハ105の処理を完了した後にプロセス後データを取得するにあたり、システム300は、1枚以上の半導体ウェハ105の処理が完了したことを示す信号を受け取る（ブロック1010）。システム300が、半導体ウェハ105の組から計測データの取得が可能なことを認識すると、処理装置510にあるウェハのうち、次に解析すべき半導体ウェハ105を決定する（ブロック1020）。システム300が、オンライン計測解析を行う半導体ウェハ105を特定すると、処理装置510は、オンライン計測データを取得するために、この特定の半導体ウェハ105を組み込み計測データ装置310に搬送する（ブロック1030）。30

#### 【0047】

次に、システム300は、対象の半導体ウェハ105からオンライン計測データを取得する（ブロック1040）。オンライン計測データの取得は、処理装置510にある組み込み計測装置310が行う。このため、計測データが、リアルタイムもしくはほぼリアルタイムにシステム300に提供される。オンライン計測データが取得されると、計測データが取得されたことが、処理装置510の処理チャンバ630に対して通知される（ブロック1050）。一実施形態においては、処理チャンバ630は、データが取得されたことを装置インターフェース610を介してコンピュータ・システム530に通知し、これにより、コンピュータ・システム530は、オンライン計測データに応答して行う処理を実行できるようになる。図9のブロック910, 930, 960に示すように、図10に示すステップを使用して、プロセス前計測データとプロセス後計測データとを取得することが可能である。図9のブロック910, 930, 960に示すように、図10のステップが完了すると、オンライン計測データを取得する処理は実質的に完了する。40

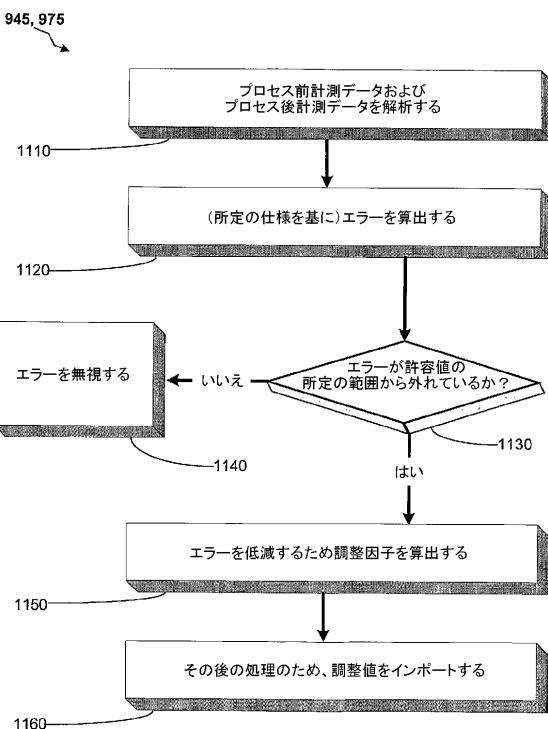

#### 【0048】

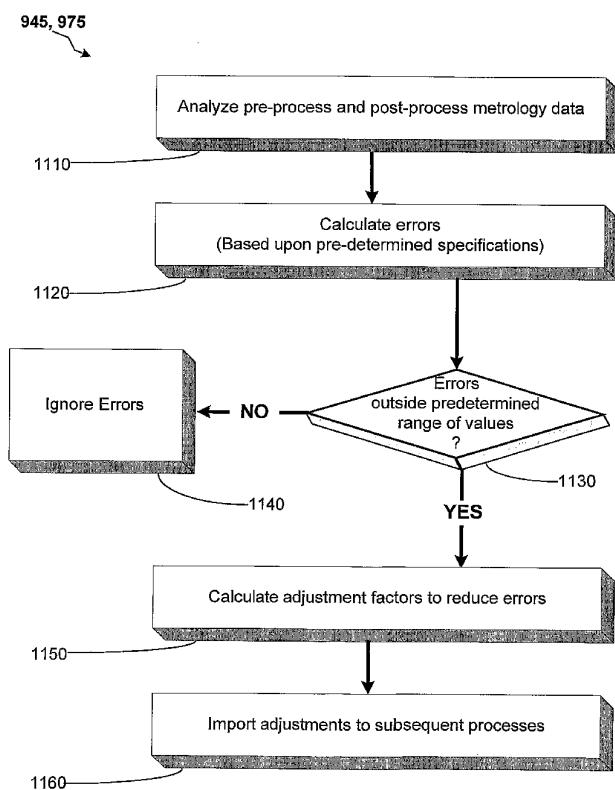

図11に、図9のブロック945, 975に示す計測フィードバック・ステップを実行する一実施形態のフローチャートを示す。システムは、半導体ウェハ105の特定の組に関50

するプロセス前計測データとプロセス後計測データとを解析する（ブロック 1110）。例えば、半導体ウェハ 105 の第 1 の組に関するプロセス前計測データとプロセス後計測データとが、ウェハ間のフィードバック調整ループ 705 およびラン - ツ - ランのフィードバック・ループ 700 の少なくともいずれかのために解析される。システムは、プロセス前計測データとプロセス後計測データとに基づいてエラーを算出する（ブロック 1120）。一実施形態においては、算出されたエラーと所定の仕様とが比較されて、エラーの有無が判定される。例えば、微小寸法の値、トレンチの側壁の角度、トレンチ深さなどの、半導体ウェハ 105 の基板に形成されたトレンチに関するデータと、トレンチのこれら値の許容値の所定の範囲とが比較される。

#### 【0049】

10

次に、システム 300 は、検出されたエラーが許容値の所定の範囲から外れているかどうかを判定する（ブロック 1130）。システム 300 が、検出されたエラーが許容値の所定の範囲から外れていないと判断すると、システム 300 は通常はこのエラーを無視して、正常な処理操作を続行する（ブロック 1140）。システム 300 が、検出されたエラーが許容値の所定の範囲から外れていると判断すると、システム 300 は、半導体ウェハ 105 のその後の処理に用いる、制御入力パラメータの調整因子を計算する（ブロック 1150）。一実施形態においては、検出されたエラーを低減するために、制御入力パラメータが変更される。次に、システム 300 は、半導体ウェハ 105 のその後の処理に使用するため、算出した調整値をインポートする（ブロック 1160）。例えば、その後の処理でのトレンチ構造の精度をさらに向上させるため、半導体ウェハ 105 の基板にトレンチ構造を形成するための制御調整値が変更される。図 11 に示したフィードバック方法は、ラン - ツ - ランのフィードバック制御ループ 700 のほか、ウェハ間のフィードバック・ループ 705 とに対して実行され得る。本発明の教示は、半導体デバイスの製造における種々の処理手順に用いることができる。

20

20

#### 【0050】

30

本発明の原理は、ケー・エル・エー・テンコール・インコーポレイテッド（KLA Tencor, Inc.）が提唱しているカタリスト（Catalyst）システムなどの高度プロセス制御（APC）フレームワークに用いることが可能である。カタリスト・システムは、半導体製造装置材料協会（SEMI）のコンピュータ統合生産（CIM）フレームワークに準拠したシステム技術を用いており、高度プロセス制御（APC）フレームワークをベースとしている。CIM（SEMI E81-0699-CIM フレームワーク・ドメイン・アーキテクチャ暫定仕様）および APC（SEMI E 93-0999-CIM フレームワークプロセス制御コンポーネント暫定仕様）の仕様は、SEMI から公的に入手可能である。APC は、本発明が教示する制御方法を実装するための好ましいプラットフォームである。一部の実施形態においては、APC は工場規模のソフトウェア・システムであり得、このため、本発明が教示する制御方法は、工場に存在するほぼあらゆる半導体製造装置に応用することが可能である。また、APC フレームワークによって、プロセスの性能のリモート・アクセスと監視とが可能となる。さらに、APC フレームワークを使用することによって、ローカル・ドライブを使用する場合と比べて、データの保管の利便性および柔軟性が向上すると共に、コストを抑えることができる。APC プラットフォームでは必要なソフトウェア・コードを非常に柔軟に記述できるため、APC プラットフォームによって、一層高度な制御が可能となる。

40

#### 【0051】

40

本発明が教示する制御方法を APC フレームワークに配置するには、数多くのソフトウェア・コンポーネントが必要となる可能性がある。APC フレームワーク内のコンポーネントのほかに、制御システムに関わる各半導体製造装置用のコンピュータ・スクリプトが記述される。半導体製造工場で制御システム内の半導体製造装置が起動されると、通常はこの半導体製造装置がスクリプトを呼び出して、重ね合わせ制御装置などのプロセス制御装置が必要とする動作を開始する。この制御方法は、一般にこれらのスクリプトに定義されて実行される。このようなスクリプトの開発には、制御システムの開発の多くの部分が含

50

まれる。本発明の原理は、他の種類の製造フレームワークにも実装可能である。

【0052】

上記に記載した特定の実施形態は例に過ぎず、本発明は、本開示の教示から利益を得る当業者にとって自明の、同等の別法によって変更および実施されてもよい。さらに、ここに記載した構成または設計の詳細が、添付の特許請求の範囲以外によって制限を受けることはない。このため、上記に記載した特定の実施形態を変形または変更することが可能であり、この種の変形例の全てが本発明の範囲ならびに趣旨に含まれることが意図されることが明らかである。したがって、ここに保護を請求する対象は、添付の特許請求の範囲に記載したとおりである。

【図面の簡単な説明】

10

【0053】

【図1】先行技術による、処理対象の半導体ウェハの略式図である。

【図2】半導体ウェハの製造における先行技術による処理フローを示すフローチャートである。

【図3】本発明の例示的な実施形態によるシステムの略式ブロック図である。

【図4】本発明の別の例示的な実施形態によるシステムの略式ブロック図である。

【図5】図4の本発明の例示的な実施形態による処理装置を示すさらに詳細なブロック図である。

【図6】図3、4の本発明の例示的な実施形態による処理装置を示すさらに詳細なブロック図である。

20

【図7】本発明の例示的な実施形態による、製造システムに使用されるラン・ツー・ランのフィードバック・ループおよびウェハ間のフィードバック・ループを示すブロック図である。

【図8】本発明の例示的な実施形態による方法を示すフローチャートである。

【図9】図6に示す本発明の例示的な実施形態による半導体ウェハのカスケード処理を実行する方法を示すフローチャートである。

【図10】本発明の例示的な実施形態による、図9に示すようなプロセス前計測データを取得する方法を示すフローチャートである。

【図11】本発明の例示的な実施形態による、図9に示すような計測データのフィードバック方法を示すフローチャートである。

30

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 10】

820

【図 11】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

8 May 2003 (08.05.2003)

PCT

(10) International Publication Number

WO 03/038888 A2(51) International Patent Classification<sup>2</sup>: H01L 21/66

(81) Designated States (national): AE, AG, AI, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CI, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GI, GM, HR, HU, ID, IL, IN, IS, JP, KU, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(21) International Application Number: PCT/US02/25402

(22) International Filing Date: 9 August 2002 (09.08.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/020,551 30 October 2001 (30.10.2001) US(71) Applicant: ADVANCED MICRO DEVICES, INC.

[US/US]; One AMD Place, Mail Stop 68, P.O. Box 3453,

Sunnyvale, CA 94088-3453 (US).(72) Inventors: PASADYN, Alexander, J.; 8717 Dandelion

Trail, Austin, TX 78745 (US). BODE, Christopher, A.;

4700 Staggerbrush Road #738, Austin, TX 78749 (US).(74) Agent: DRAKE, Paul, S.; Advanced Micro Devices, Inc.,

5304 East Ben White Boulevard, Mail Stop 562, Austin,

TX 78741 (US).(81) Designated States (regional): ARPO patent (GI, GM,

KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW),

Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

European patent (AT, BE, BG, CH, CY, CZ, DE, DK, BE,

ES, FI, FR, GR, IE, IT, LU, MC, NL, PT, SE, SK,

TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ,

GW, ML, MR, NE, SN, TD, TG).(84) Published:

without international search report and to be republished

upon receipt of that reportFor two-letter codes and other abbreviations, refer to the "Guide-

ance Notes on Codes and Abbreviations" appearing at the begin-

ning of each regular issue of the PCT Gazette.

(54) Title: METHOD AND APPARATUS FOR CASCADE CONTROL, USING INTEGRATED METROLOGY

A2

(57) Abstract: A method and an apparatus for performing cascade control of processing of semiconductor wafers (105). A first semiconductor wafer (105) for processing is received. A second semiconductor wafer (105) for processing is received. A cascade processing operation upon the first and the second semiconductor wafers (105) is performed, wherein the cascade processing operation comprises acquiring pre-process metrology data related to the second semiconductor wafer (105) during at least a portion of a time period wherein the first semiconductor wafer (105) is being processed.

WO 03/038888 A2

WO 03/038888

PCT/US02/25402

**METHOD AND APPARATUS FOR CASCADE CONTROL USING INTEGRATED METROLOGY****TECHNICAL FIELD**

This invention relates generally to semiconductor manufacturing, and, more particularly, to a method and apparatus for performing a cascading processing of semiconductor wafers.

**BACKGROUND ART**

The technology explosion in the manufacturing industry has resulted in many new and innovative manufacturing processes. Today's manufacturing processes, particularly semiconductor manufacturing processes, call for a large number of important steps. These process steps are usually vital, and therefore, require a number of inputs that are generally fine-tuned to maintain proper manufacturing control.

The manufacture of semiconductor devices requires a number of discrete process steps to create a packaged semiconductor device from raw semiconductor material. The various processes, from the initial growth of the semiconductor material, the slicing of the semiconductor crystal into individual wafers, the fabrication stages (etching, doping, ion implanting, or the like), to the packaging and final testing of the completed device, are so different from one another and specialized that the processes may be performed in different manufacturing locations that contain different control schemes.

Generally, a set of processing steps is performed on a group of semiconductor wafers, sometimes referred to as a lot. For example, a process layer composed of a variety of materials may be formed above a wafer. Thereafter, a patterned layer of photoresist may be formed above the process layer using known photolithography techniques. Typically, an etch process is then performed on the process layer using the patterned layer of photoresist as a mask. This etching process results in formation of various features or objects in the process layer. Such features may be used for a gate electrode structure for transistors. Many times, trench structures are also formed on the substrate of the semiconductor wafer. One example of a trench structure is a shallow trench isolation (STI) structure, which can be used to isolate electrical areas on a semiconductor wafer. Typically, STI structures formed on the semiconductor wafers are filled by forming silicon dioxide using tetraethoxysilane (TEOS), over the wafer and in the STI structures.

The manufacturing tools within a semiconductor manufacturing facility typically communicate with a manufacturing framework or a network of processing modules. Each manufacturing tool is generally connected to an equipment interface. The equipment interface is connected to a machine interface to which a manufacturing network is connected, thereby facilitating communications between the manufacturing tool and the manufacturing framework. The machine interface can generally be part of an advanced process control (APC) system. The APC system initiates a control script, which can be a software program that automatically retrieves the data needed to execute a manufacturing process.

Figure 1 illustrates a typical semiconductor wafer 105. The wafer 105 typically includes a plurality of individual semiconductor die 103 arranged in a grid 150. Photolithography steps are typically performed by a stepper on approximately one to four die locations at a time, depending on

WO 03/038888

PCT/US02/25402

the specific photomask employed. Photolithography steps are generally performed to form patterned layers of photoresist above one or more process layers that are to be patterned. The patterned photoresist layer can be used as a mask during etching processes, wet or dry, performed on the underlying layer or layers of material, e.g., a layer of polysilicon, metal or insulating material, to transfer the desired pattern to the underlying layer. The patterned layer of photoresist is comprised of a plurality of features, e.g., line-type features, such as a polysilicon line, or opening-type features, that are to be replicated in an underlying process layer.

Conventional procedures during manufacturing of semiconductor wafers call for a set of steps that are performed in series. Turning now to Figure 2, a flowchart depiction of such steps are illustrated. The manufacturing system acquires semiconductor wafers 105 that are to be processed (block 210). Once a set of wafers 105 to be processed is acquired, the manufacturing system acquires pre-processing manufacturing data (e.g., metrology data and the like) from the semiconductor wafers 105 (block 220).

For certain processes, the manufacturing data acquired from the wafer 105 may involve a pre-process screening of the semiconductor wafers 105. For example, before performing a chemical-mechanical polishing (CMP) process, pre-processing data acquired from the semiconductor wafers 105 that are about to be processed, can be used to set control parameters that affect the CMP process. Once pre-processing data is acquired, the manufacturing system processes the semiconductor wafers 105 (block 230).

After processing the semiconductor wafers 105, the manufacturing system determines whether additional processes are to be performed on the semiconductor wafers 105 (block 240). When the manufacturing system determines that additional processes are to be performed on the semiconductor wafers 105, pre-process metrology data may be acquired and additional processes are performed on the semiconductor wafers 105 (see flowchart path: block 230—block 240—block 220). The manufacturing system may use a plurality of processing tools to perform a plurality of processing on the semiconductor wafers 105.

When the manufacturing system determines that additional processes are not to be performed on the semiconductor wafers 105, the manufacturing system may acquire post-process manufacturing data from the processed wafers 105 (block 250). Generally, the post-process manufacturing data includes measurements of a plurality of structures formed on the semiconductor wafers 105. If there are other semiconductor wafers 105 to be processed, as determined in block 260, the manufacturing system acquires the next wafer 105 to be processed and repeats the processes described above (blocks 250, 270). Alternatively, if there are no additional semiconductor wafers 105 to be processed, the manufacturing system stops the processing mode (block 270).

The steps illustrated by Figure 2 are generally performed in series, causing the manufacturing system to execute frequent breaks in the process flow. Acquiring pre-process data using a metrology tool, then processing the wafer 105, then acquiring post-process manufacturing data, can be an inefficient process when performed in series. Any interruption in a process flow of semiconductor wafers can cause inefficiencies and errors. Manufacturing time lost due to such inefficiencies can be very costly, and can adversely affect product delivery schedules. Errors in the semiconductor wafers

WO 03/038888

PCT/US02/25402

105 can adversely affect the yields of the devices produced from the processed semiconductor wafers 105.

The present invention is directed to overcoming, or at least reducing the effects of, one or more of the problems set forth above.

5

**DISCLOSURE OF INVENTION**

In one aspect of the present invention, a method is provided for performing cascade control of processing of semiconductor wafers. A method and an apparatus for performing cascade control of processing of semiconductor wafers. A first semiconductor wafer for processing is received. A second semiconductor wafer for processing is received. A cascade processing operation upon the first and the second semiconductor wafers is performed, wherein the cascade processing operation comprises acquiring pre-process metrology data related to the second semiconductor wafer during at least a portion of a time period wherein the first semiconductor wafer is being processed.

In another aspect of the present invention, a system is provided for performing cascade control of processing of semiconductor wafers. The system of the present invention comprises: a process controller to perform a cascade process operation, the cascade process operation comprising: acquiring pre-process data related to a first semiconductor wafer; processing the first semiconductor wafer after the acquiring of the pre-process data relating to the first semiconductor wafer; acquiring pre-process data related to a second semiconductor wafer during at least a portion of a time period wherein the first semiconductor wafer being processed; processing the second semiconductor wafer after the acquiring of the pre-process data related to the second semiconductor wafer acquiring post-process data related to the first semiconductor wafer during at least a portion of a time period wherein the second semiconductor wafer is being processed; and acquiring post-process data related to the second semiconductor wafer after the processing of the second semiconductor wafer. The system also comprises: an inline cascade metrology data storage unit operatively coupled to the process controller, the inline cascade metrology data storage unit to receive at least one of an inline pre-process metrology data and an inline post-process metrology data; and a feedback/feed-forward unit operatively coupled to the process controller and the inline cascade metrology data storage unit, the feedback/feed-forward unit to perform a feedback function in response to at least one of the inline pre-process metrology data and the inline post-process metrology data.

**BRIEF DESCRIPTION OF THE DRAWINGS**

The invention may be understood by reference to the following description taken in conjunction with the accompanying drawings, in which like reference numerals identify like elements, and in which:

35 Figure 1 is a simplified diagram of a prior art semiconductor wafer being processed;

Figure 2 illustrates a simplified flowchart depiction of a prior art process flow during manufacturing of semiconductor wafers;

Figure 3 is a block diagram representation of a system in accordance with one illustrative embodiment of the present invention;

WO 03/038888

PCT/US02/25402

Figure 4 is a block diagram representation of a system in accordance with an alternative illustrative embodiment of the present invention;

Figure 5 illustrates a more detailed block diagram representation of a processing tool shown in Figure 4, in accordance with one illustrative embodiment of the present invention;

5 Figure 6 illustrates a more detailed block diagram representation of the system shown in Figures 3 and 4, in accordance with one illustrative embodiment of the present invention;

Figure 7 illustrates a block diagram representation of a run-to-run feedback loop and a wafer-to-wafer feedback loop utilized in a manufacturing system, in accordance with one illustrative embodiment of the present invention;

10 Figure 8 illustrates a flowchart depiction of a method in accordance with one illustrative embodiment of the present invention;

Figure 9 illustrates a flowchart depiction of a method of performing a cascade processing of semiconductor wafers, as indicated in Figure 6, in accordance with one illustrative embodiment of the present invention;

15 Figure 10 illustrates a flowchart depiction of a method of acquiring pre-process metrology data, as indicated in Figure 9, in accordance with illustrative one embodiment of the present invention; and

Figure 11 illustrates a flowchart depiction of a method performing a metrology data feedback, as indicated in Figure 9, in accordance with one illustrative embodiment of the present invention.

20 While the invention is susceptible to various modifications and alternative forms, specific embodiments thereof have been shown by way of example in the drawings and are herein described in detail. It should be understood, however, that the description herein of specific embodiments is not intended to limit the invention to the particular forms disclosed, but on the contrary, the intention is to cover all modifications, equivalents, and alternatives falling within the spirit and scope of the invention

25 as defined by the appended claims.

#### MODE(S) FOR CARRYING OUT THE INVENTION

Illustrative embodiments of the invention are described below. In the interest of clarity, not all features of an actual implementation are described in this specification. It will of course be appreciated that in the development of any such actual embodiment, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with system-related and business-related constraints, which will vary from one implementation to another. Moreover, it will be appreciated that such a development effort might be complex and time-consuming, but would nevertheless be a routine undertaking for those of ordinary skill in the art having the benefit of this disclosure.

30 There are many discrete processes that are involved in semiconductor manufacturing. Many times, semiconductor devices are stepped through multiple manufacturing process tools. Often, manufacturing data, including metrology data, is collected before and/or after some processes are performed. For example, before a chemical-mechanical polishing (CMP) process is performed, it is desirable to collect pre-processing data to determine how much polishing is to be performed.

40 Similarly, after performing a deposition process, it is desirable to collect post-processing data to

WO 03/038888

PCT/US02/25402

determine how much material was deposited on the semiconductor wafer, and to adjust control parameters of subsequent processes performed on the semiconductor wafer. However, acquiring pre-process and post-process metrology data, particularly in an offline manner, can cause a manufacturing process flow to become inefficient. Embodiments of the present invention provide for performing a metrology data acquisition and manufacturing process steps in a cascading fashion, resulting in more efficient process flow.

In one embodiment, the cascading control system provided by embodiments of the present invention refers to a nested system of control loop. The cascade system provided by embodiments of the present invention provides an inner, wafer-to-wafer control loop (e.g., a first feedback loop) and an outer, lot-to-lot control loop (e.g., a second feedback loop). In one embodiment, an inner feedback loop provides a wafer-to-wafer control loop, while an outer feedback loop provides a lot-to-lot control loop, which are illustrated in Figure 7 and accompanying description.

Turning now to Figure 3, a system 300 capable of performing the methods taught by one embodiment of the present invention, is illustrated. In one embodiment, a processing tool 510 comprises an integrated metrology tool 310. In one embodiment, the integrated metrology tool 310 is capable of acquiring inline metrology data (e.g., acquiring metrology data of semiconductor wafer 105 while they are still under the control of the processing tool 510). Acquiring inline metrology data is generally less intrusive to a manufacturing process flow, as compared to acquiring offline metrology data, which requires the use of an external metrology data tool. A set of semiconductor wafers 105 in a cassette 539 are provided to the processing tool 510. Embodiments of the present invention provide for the processing tool 510 to perform a cascade processing function using the integrated metrology tool 310. The process of performing the cascade processing function is controlled by a process controller 350.

In one embodiment, a cascade processing function includes performing a plurality of manufacturing functions in a sequential and/or overlapping manner. For example, a cascade processing function, in accordance with one embodiment of the present invention, provides for: acquiring pre-process metrology data relating to a first set of semiconductor wafers 105; processing the first set of semiconductor wafers 105 in at least a portion of a time period, during which pre-process data for a second set of semiconductor wafers 105 is acquired; and acquiring post-process metrology data relating to the first set of semiconductor wafers 105 in at least a portion of a time period, during which processing of the second set of semiconductor wafers 105 is performed. This cascading process provides for more efficient processing flow in which a plurality of semiconductor wafers 105 are processed and analyzed. In one embodiment, the pre-process and post-process metrology data is acquired using an integrated metrology tool, which is described in more detail below.

Data acquired by the integrated metrology tool 310 is sent to a metrology data analysis unit 560. The metrology data analysis unit 560 organizes, analyses, and correlates metrology data acquired by the offline metrology tool 550 (see Figure 5) to particular semiconductor wafers 105 that were examined. The metrology data analysis unit 560 can be a software unit, a hardware unit, or a

WO 03/038888

PCT/US02/25402

firmware unit. In various embodiments, the metrology data analysis unit 560 is integrated into the computer system 530 or may be integrated into the offline metrology tool 550.

In one embodiment, the system 300 stores inline cascade metrology data, acquired by the integrated metrology tool 310, while performing a cascade process operation, into the inline cascade metrology data storage unit 320. The metrology data stored in the inline cascade metrology data storage unit 320 includes sets of data that represent the line width of structures formed on the semiconductor wafer 105, the trench depth of an STI trench, the side-wall angle (with respect to the vertical plane) of trench structures formed on the semiconductor wafer 105, and the like. In one embodiment, data in the inline cascade metrology data storage unit 320 can be used for feedback correction in order to improve the efficiency and accuracy of processing of semiconductor wafers 105.

Turning now to Figure 4, an alternative embodiment of the processing tool 510, employed by the system 300 to perform a cascade processing function, is illustrated. The processing tool 510 illustrated in Figure 4 comprises an integrated pre-process metrology tool 410 and an integrated post-process metrology tool 420. Semiconductor wafers 105 are analyzed by the integrated pre-process metrology tool 410 before they are processed. For example, the semiconductor wafers 105 are analyzed by the integrated pre-process metrology tool 410 before the processing tool performs a CMP process upon the semiconductor wafer 105. The resulting pre-process metrology data can then be used to control the CMP process more accurately.

Many times, subsequent to processing a semiconductor wafer 105, the processing tool 510 acquires post-process metrology data using the integrated post-process metrology tool 420. Meanwhile, a second set of semiconductor wafers 105, carried by a second cassette 539 is sent to the pre-process integrated metrology tool 410 for analysis before being processed by the processing tool 510. Using the cascade processing technique, the processing tool 510 can perform pre-process data acquisition, processing of semiconductor wafers 105, and post-process integrated metrology data acquisition in a cascade manner, such that the capabilities of the processing tool 510 is utilized in a more simultaneous and efficient fashion. The integrated pre-process metrology tool 410 and the integrated post-process metrology tool 420 send their respective data to the metrology data analysis unit 560 for processing. The metrology data is then stored in the inline cascade metrology data storage unit 320, which is then available for the system 300 for performing more efficient feedback analysis. The process of performing the cascade processing function illustrated in Figure 4 is controlled by a process controller 350.

Turning now to Figure 5, a more detailed block diagram of the system 300 in accordance with one embodiment of the present invention is illustrated. In one embodiment, semiconductor wafers 105, are processed on processing tools 510a, 510b using a plurality of control input signals, or manufacturing parameters, on a line 523. In one embodiment, control input signals, or manufacturing parameters, on the line 523 are sent to the processing tools 510a, 510b from a computer system 530 via machine interfaces 515a, 515b. In one embodiment, the first and second machine interfaces 515a, 515b are located outside the processing tools 510a, 510b. In an alternative embodiment, the first and second machine interfaces 515a, 515b are located within the processing tools 510a, 510b. In one embodiment, the semiconductor wafers 105 are provided to and carried from a plurality of processing tools 510. In

WO 03/038888

PCT/US02/25402

one embodiment, semiconductor wafer 105 may be provided to a processing tool 510 manually. In an alternative embodiment, semiconductor wafer 105 may be provided to a processing tool 510 in an automatic fashion (e.g., robotic movement of semiconductor wafer 105). In one embodiment, a plurality of semiconductor wafers 105 are transported in lots (e.g., stacked in the cassettes 539) to the processing tools 510.

In one embodiment, the computer system 530 sends control input signals, or manufacturing parameters, on the line 523 to the first and second machine interfaces 515a, 515b. The computer system 530 is capable of controlling processing operations. The computer system 530 is coupled to a computer storage 532 that may contain a plurality of software programs and data sets. The computer system 530 may contain one or more processors (not shown) that are capable of performing the operations described herein. The computer system 530 employs a manufacturing model 540 to generate control input signals on the line 523. In one embodiment, the manufacturing model 540 contains a manufacturing recipe that determines a plurality of control input parameters that are sent on the line 523.

15 In one embodiment, the manufacturing model 540 defines a process script and input control that implement a particular manufacturing process. The control input signals (or control input parameters) on the line 523 that are intended for processing tool A 510a are received and processed by the first machine interface 515a. The control input signals on the line 523 that are intended for processing tool B 510b are received and processed by the second machine interface 515b.

20 Examples of the processing tools 510a, 510b used in semiconductor manufacturing processes are steppers, etch process tools, and the like.

One or more of the semiconductor wafers 105 that are processed by the processing tools 510a, 510b can also be sent to an offline metrology tool 550 for acquisition of metrology data. The offline metrology tool 550 can be a scatterometry data acquisition tool, an overlay-error measurement tool, a critical dimension measurement tool, and the like. In one embodiment, one or more processed semiconductor wafers 105 are examined by a metrology tool 550. Furthermore, metrology data is collected by the integrated metrology tool 310 within the processing tools 510. Data from the integrated metrology tool 310 and the offline metrology tool 550 are collected by the metrology data analysis unit 560. The data may include line width measurement, depth of trenches, sidewall angles, 30 and the like. As described above, the metrology data analysis unit 560 organizes, analyses, and correlates metrology data acquired by the metrology tool 550 to particular semiconductor wafers 105 that were examined.

In one embodiment, the metrology data analysis unit 560 sends inline cascade metrology data from the integrated metrology tool 310 to the inline cascade metrology data storage unit 320 for storage. Furthermore, metrology data analysis unit 560 sends offline metrology data to an offline metrology data storage unit 570 for storage. The system 300 is able to retrieve inline cascade metrology data and offline metrology data and perform feedback and feed-forward analysis. The inline metrology data and the offline metrology data are sent to the feedback/feed-forward unit 580 for generation of feedback and feed-forward data. The feedback and feed-forward data are analyzed by 40 the computer system 530, which then uses the manufacturing model 540 to modify control input

WO 03/038888

PCT/US02/25402

parameters that control the operation of the processing tools 510. In one embodiment, the inline cascade metrology data storage unit 320, the offline metrology data storage unit 570, and/or the feedback/feed-forward unit 580 are software or firmware components that can be a standalone unit or can be integrated into the computer system 530.

5 Turning now to Figure 6, a more detailed illustration of the processing tool and the process flow in accordance with one embodiment of the present invention is illustrated. In one embodiment, the processing tool comprises an equipment interface 610, a tool control unit 620, a processing chamber 630, and an integrated metrology tool 310. The equipment interface 610 facilitates communications between the processing tool 510 and other parts of the system 300, such as the computer system 530, the manufacturing model 540, and the machine interface 515. The tool control unit 620 controls the operations of the processing tools 510. The tool control unit 620 is capable of receiving instructions and data from the computer system 530, via the equipment interface 610. The tool control unit 620 is also capable of sending data, such as integrated metrology data, to other portions of the system 300 via the equipment interface 610.

10 15 A first set of semiconductor wafers 105, carried by the cassette 539, is received by the processing tool 510 and examined by the integrated metrology tool 310 for pre-process metrology data acquisition. The first set of semiconductor wafers 105 are then sent to the chamber 630 for processing. Meanwhile, a second set of semiconductor wafers 105 is received by the integrated metrology tool 310 for pre-process metrology data acquisition.

20 25 During the approximate time that the metrology data is acquired from the second set of semiconductor wafers 105, the first set of semiconductor wafers 105 can be processed by the chamber 630. Upon completion of the processing of the first set of semiconductor wafers 105, the tool control unit 620 prompts the integrated metrology tool 310 to acquire post-process metrology data from the processed first set of semiconductor wafers 105. Meanwhile, the second set of semiconductor wafers 105 are sent to the process chamber 630 for processing. This cascade process system produces a significant amount of quickly acquired metrology data that can be used for immediate feedback analysis. Data from the integrated metrology tool 310 is sent to the metrology data analysis tool 560. The metrology data is then stored into the inline cascade metrology data storage unit 320 for retrieval by system 300 for feedback processing. Subsequently, a third, a fourth, 30 and a fifth through nth set of semiconductor wafers 105 can be processed in the cascade fashion described above for efficient usage of the processing tool 510. Furthermore, more immediate use of metrology data for feedback and feed-forward processes are possible using embodiments of the present invention.

35 In one embodiment, the system 300, using the methods taught by embodiments of the present invention, can perform the multiple feedback loops to improve the efficiency and accuracy of the manufacturing of semiconductor wafers 105. Turning now to Figure 7, two feedback loops that are used during semiconductor wafer manufacturing are illustrated. The feedback loops utilized by the system 300 includes a run-to-run feedback loop 700 and a wafer-to-wafer feedback loop 705. Both feedback loops (700 and 705) can be used in concert during a manufacturing process for

WO 03/038888

PCT/US02/25402

adjustment of control input parameters. In other words, both feedback loops (700 and 705) can be used to perform a cascading controlling function during processing of semiconductor wafers 105.

The inner loop, which is the wafer-to-wafer feedback loop 705, comprises processing a semiconductor wafer 105 (block 740) and acquiring inline metrology data from the processed semiconductor wafer 105 (block 750). The system 300 then processes the metrology data, which includes calculating the amount of error existing on the semiconductor wafer 105 (block 770). The system 300 then calculates modifications to control input parameters that control the processing tools 510, based upon the errors (block 780). The system then acquires the next semiconductor wafer 105 to be processed, and the wafer 105 is processed using the modified control input parameters (block 790-block 740), thereby forming a wafer-to-wafer feedback loop 705.

Using the wafer-to-wafer feedback loop 705, errors acquired from the processing of one semiconductor wafer 105 can be acquired quickly using the inline metrology tool 310. The metrology data is then processed and used as feedback data for the processing of the next semiconductor wafer 105. The wafer-to-wafer feedback loop 705 illustrated in Figure 7 provides for more accurate correction of errors within a particular lot of semiconductor wafers 105.

The run-to-run feedback loop 700 is created approximately simultaneously with the wafer-to-wafer feedback loop 705 by collecting the calculated errors and modifications and using them to correct errors during the next set of semiconductor wafers 105. The system 300 acquires a new lot of semiconductor wafers 105 (block 710) and uses data and calculations acquired from the wafer-to-wafer feedback loop 705 to define an initial state of the control input parameters used for processing the next lot of semiconductor wafers 105 (block 720). The system 300 then acquires semiconductor wafers 105 from the new lot of semiconductor wafers 105 and sends them to be processed (block 730 through block 740). The wafer-to-wafer feedback loop 705 is then repeated and the resulting calculations are used for a subsequent lot of semiconductor wafers 105. Therefore, two feedback loops, the run-to-run feedback loop 700 and the wafer-to-wafer feedback loop 705 are used separately, and sometimes simultaneously, to manufacture more efficiently and accurately processed semiconductor wafers 105.

Turning now to Figure 8, a flowchart depiction of a method in accordance with one embodiment of the present invention, is illustrated. The system 300 acquires a first set of semiconductor wafers 105 for processing (block 810). The tool control unit 620 in the processing tool 510 receives data and control input parameters via the equipment interface 610, for processing the incoming first set of semiconductor wafers 105. The system 300 also sends a second set of semiconductor wafers 105 to the processing tool 510 for processing (block 820).

In one embodiment, the first and the second set of semiconductor wafers 105 are sent to the processing tool 510 in cassettes 539. In an alternative embodiment, the system 300 receives more than two sets of semiconductor wafers 105 in various cassettes 539. The system 300 performs a cascade processing operation on the plurality of sets of semiconductor wafers 105 (block 830). A more detailed illustration of the steps for performing the cascade processing indicated in block 830 is provided below (see Figure 9 and accompanying description).

WO 03/038888

PCT/US02/25402

Continuing referring to Figure 8, once the system 300 performs the cascade processing operation, the system 300 uses data resulting from the cascade processing operation as feedback data (block 840). In one embodiment, the system 300 uses metrology data acquired during the cascade processing to perform a wafer-to-wafer feedback 705, as well as a run-to-run feedback 700.

- 5 Using the feedback data, the system 300 processes subsequent wafers 105 using modified control parameters in order to reduce the errors detected (block 850).

Turning now to Figure 9, a flowchart depiction of the steps for performing the cascade processing operation indicated in block 830 of Figure 8, in accordance with one embodiment of the present invention, is illustrated. The system 300 acquires pre-process metrology data for the first set 10 of semiconductor wafers 105 (block 910). In one embodiment, the pre-process metrology data is performed using the integrated metrology tool 310 located within the processing tool 510. Once the processing tool 510 acquires pre-processing metrology data from the first set of semiconductor wafers 105, the processing tool 510 sends the first set of semiconductor wafers 105 from its integrated metrology tool 310 to its process chamber 630 for processing (block 920). In one embodiment, the tool control unit 620 controls the movement of multiple sets of semiconductor wafers 105 within the processing tool 510.

The processing tool 510 then acquires pre-processing metrology data from the second set of semiconductor wafers 105 (block 930). The pre-processing metrology data for the second set of semiconductor wafers 105 are acquired using the integrated metrology tool 310. In one embodiment, 20 the processing of the first set of semiconductor wafers 105 in the chamber 630 and the acquisition of pre-processing metrology data for the second set of semiconductor wafers 105 acquired by the integrated metrology tool 310 is performed approximately during overlapping periods of time. In one embodiment, the pre-processing metrology data can be used to modify control settings for a subsequent processing of semiconductor wafers 105 in a feed-forward control fashion.

25 Upon completion of the processing of the first set of semiconductor wafers 105, the processing tool 510 sends the semiconductor wafers 105 to a post-process metrology data acquisition step (block 940). In one embodiment, the post-process metrology data acquisition is performed by the integrated metrology tool 310. In an alternative embodiment, the pre-processing metrology data is acquired by a separate pre-process integrated metrology tool 410, and the post-process metrology data acquisition is performed by a separate post-process integrated metrology tool 420. In the illustrative embodiment described in Figure 9, the pre-processing metrology data and the post-process metrology data are both acquired by the integrated metrology tool 310. In one embodiment, the post-process metrology data can be used to modify control settings to modify 30 subsequent processing of semiconductor wafers 105 in order to compensate for errors from previous processing of the semiconductor wafers 105, in a feedback control fashion.

While the system 300 is acquiring post-processing metrology data from the first set of semiconductor wafers 105, the processing tool 510 sends the second set of semiconductor wafers 105 to the process chamber 630 for processing (block 950). Meanwhile, the data acquired from the first set of semiconductor wafers 105 (i.e., the pre-process metrology data and the post-process 40 metrology data) are used to perform a metrology feedback for a wafer-to-wafer feedback loop 705

WO 03/038888

PCT/US02/25402

and a run-to-run feedback loop 700 (block 945). One illustrative embodiment of performing the metrology feedback loop is described below, as well as in its accompanying description (see Figure 11).

Continuing referring to Figure 9, while the second set of semiconductor wafers 105 are being processed in the chamber 630, the system 300 sends a third set of semiconductor wafers 105 to the processing tool 510. The third set of semiconductor wafers 105 are sent to the integrated metrology data acquisition tool 310 for pre-processing metrology data acquisition (block 960). Once the second set of semiconductor wafers 105 are processed in the chamber 630, the second set of semiconductor wafers 105 are sent to the post-process metrology data acquisition step (block 970). Subsequently, 5 the third set of semiconductor wafers are sent to the chamber 630 for processing (block 980). Meanwhile, a second metrology feedback process is initiated using metrology data relating to the second set of semiconductor wafers 105 (i.e., the pre-process and post-process metrology data relating to the second set of semiconductor wafers 105) (block 975). This process of cascade 10 processing can be repeated for a plurality of sets of semiconductor wafers 105 using integrated 15 metrology tools 310.

Turning now to Figure 10, a flowchart depiction of a method for acquiring inline metrology data, as indicated in blocks 910, 930, and 960, in accordance with one embodiment of the present invention is illustrated. In acquiring post-process data, after the system 300 processes a 20 semiconductor wafer 105, a signal is received by the system 300 indicating that at least one semiconductor wafer 105 has been processed (block 1010). When the system 300 realizes that a set of semiconductor wafers 105 are available for metrology data acquisition, a determination is made as 25 to which semiconductor wafer 105 in the processing tool 510 is next in queue for analysis (block 1020). Once the system 300 targets a particular semiconductor wafer 105 for inline metrology analysis, the processing tool 510 sends that particular semiconductor wafer 105 to the integrated metrology data tool 310 for inline metrology data acquisition (block 1030).

The system 300 then acquires inline metrology data from the targeted semiconductor wafer 105 (block 1040). The integrated metrology tool 310 within the processing tool 510 acquires the inline 30 metrology data. Therefore, real time or near real time metrology data is provided to the system 300. Once inline metrology data is acquired, the process chamber 630 in the processing tool 510 is informed that metrology data has been acquired (block 1050). In one embodiment, the process 35 chamber 630 informs the computer system 530 via the equipment interface 610 of the data acquisition, so the computer system 530 can execute an operation that is responsive to the inline metrology data. The steps described in Figure 10 can be used to acquire pre-process and post-process metrology data, as indicated in blocks 910, 930, and 960 in Figure 9. The completion of the 40 steps illustrated in Figure 10 substantially completes the process of acquiring inline metrology data, as indicated in blocks 910, 930, and 960 in Figure 9.

Turning now to Figure 11, a flowchart depiction of one embodiment of performing the metrology feedback steps indicated in blocks 945 and 975 of Figure 9 is illustrated. The system 45 analyzes pre-process and post-process metrology data relating to a particular set of semiconductor wafers 105 (block 1110). For example, the pre-process and post-process metrology data relating to

WO 03/038888

PCT/US02/25402

the first set of semiconductor wafers 105 is analyzed for a wafer-to-wafer feedback adjustment loop 705 and/or for a run-to-run feedback loop 700. The system calculates errors based upon the pre-process and post-process metrology data (block 1120). In one embodiment, the calculated errors are compared to a predetermined specification to determine if an error exists. For example, data relating to a trench deposited on the substrate on the semiconductor wafer 105 is compared to a predetermined range of acceptable values of such a trench, such as the critical dimension values, the angle of the side walls of the trench, the trench depth, and the like.

5 The system 300 then makes a determination whether the detected error is outside a predetermined range of acceptable values (block 1130). When the system 300 determines that the detected error is not outside a predetermined range of acceptable values, the system 300 generally ignores the error and continues normal processing operations (block 1140). When the system 300 determines that the error detected is outside an acceptable predetermined range of acceptable values, the system 300 calculates an adjustment factor for the control input parameters for subsequent processing of semiconductor wafers 105 (block 1150). In one embodiment, modifications 10 to control input parameters are made in order to reduce the detected errors. The system 300 then imports the calculated adjustments in order to implement them on subsequent processing of semiconductor wafers 105 (block 1160). For example, modifications to the control adjustments for forming a trench structure on the substrate of a semiconductor wafer 105 are made to further refine 15 the accuracy of subsequent trench structures. The feedback method described in Figure 11 can be performed for a wafer-to-wafer feedback loop 705 as well as for a run-to-run feedback control loop 700. The teachings of the present invention can be utilized for a variety of processing procedures in semiconductor device manufacturing.

The principles taught by the present invention can be implemented in an Advanced Process Control (APC) Framework, such as a Catalyst system offered by KLA Tencor, Inc. The Catalyst 25 system uses Semiconductor Equipment and Materials International (SEMI) Computer Integrated Manufacturing (CIM) Framework compliant system technologies, and is based on the Advanced Process Control (APC) Framework. CIM (SEMI E81-0899 - Provisional Specification for CIM Framework Domain Architecture) and APC (SEMI E93-0999 - Provisional Specification for CIM Framework Advanced Process Control Component) specifications are publicly available from SEMI. 30 The APC is a preferred platform from which to implement the control strategy taught by the present invention. In some embodiments, the APC can be a factory-wide software system, therefore, the control strategies taught by the present invention can be applied to virtually any of the semiconductor manufacturing tools on the factory floor. The APC framework also allows for remote access and monitoring of the process performance. Furthermore, by utilizing the APC framework, data storage 35 can be more convenient, more flexible, and less expensive than local drives. The APC platform allows for more sophisticated types of control because it provides a significant amount of flexibility in writing the necessary software code.

Deployment of the control strategy taught by the present invention onto the APC framework could require a number of software components. In addition to components within the APC 40 framework, a computer script is written for each of the semiconductor manufacturing tools involved in

WO 03/038888

PCT/US02/25402

the control system. When a semiconductor manufacturing tool in the control system is started in the semiconductor manufacturing fab, it generally calls upon a script to initiate the action that is required by the process controller, such as the overlay controller. The control methods are generally defined and performed in these scripts. The development of these scripts can comprise a significant portion 5 of the development of a control system. The principles taught by the present invention can be implemented into other types of manufacturing frameworks.

The particular embodiments disclosed above are illustrative only, as the invention may be modified and practiced in different but equivalent manners apparent to those skilled in the art having the benefit of the teachings herein. Furthermore, no limitations are intended to the details of 10 construction or design herein shown, other than as described in the claims below. It is therefore evident that the particular embodiments disclosed above may be altered or modified and all such variations are considered within the scope and spirit of the invention. Accordingly, the protection sought herein is as set forth in the claims below.

WO 03/038888

PCT/US02/25402

**CLAIMS**

1. A method, comprising:

receiving a first semiconductor wafer (105) for processing;

receiving a second semiconductor wafer (105) for processing; and

5 performing a cascade processing operation upon said first and said second semiconductor wafers (105), wherein said cascade processing operation comprises acquiring pre-process metrology data related to said second semiconductor wafer (105) during at least a portion of a time period wherein said first semiconductor wafer (105) is being processed.

- 10 2. The method described in claim 1, further comprising acquiring post-process metrology data relating to said first semiconductor wafer (105) during at least a portion of a time period wherein said second semiconductor wafer (105) is being processed.

- 15 3. The method described in claim 1, wherein acquiring pre-process metrology data further comprises acquiring pre-process metrology data using an integrated metrology tool (310).

- 20 4. The method described in claim 2, wherein acquiring post-process metrology data further comprises acquiring post-process metrology data using an integrated metrology tool (310).

- 25 5. The method described in claim 1, wherein performing a cascade processing operation upon said first and said second semiconductor wafer (105) further comprises:

acquiring pre-process metrology data related to said first semiconductor wafer (105);

processing said first semiconductor wafer (105) after acquiring said pre-process metrology data related to said first semiconductor wafer (105);

acquiring pre-process metrology related to said second semiconductor wafer (105) during at least a portion of a time period wherein said first semiconductor wafer (105) being processed;

acquiring post-process metrology data related to said first semiconductor wafer (105) after said processing of said first semiconductor wafer (105);

30 processing said second semiconductor wafer (105) during at least a portion of a time period wherein post-process metrology data related to said first semiconductor wafer (105) is acquired; and

acquiring post-process metrology data in response to said processing of said second semiconductor wafer (105) after said processing of said second semiconductor wafer (105).

35

WO 03/038888

PCT/US02/25402

6. A system for performing cascade control of processing of semiconductor wafers (105),

CHARACTERIZED IN THAT,

the system comprising:

5 a process controller (350) to perform a cascade process operation, said cascade process operation comprising:

acquiring pre-process data related to a first semiconductor wafer (105);

processing said first semiconductor wafer (105) after said acquiring of said pre-process data relating to said first semiconductor wafer (105);

10 acquiring pre-process data related to a second semiconductor wafer (105) during at least a portion of a time period wherein said first semiconductor wafer (105) is being processed;

processing said second semiconductor wafer (105) after said acquiring of said pre-process data related to said second semiconductor wafer (105);

15 acquiring post-process data related to said first semiconductor wafer (105) during at least a portion of a time period wherein said second semiconductor wafer (105) is being processed;

acquiring post-process data related to said second semiconductor wafer (105) after said processing of said second semiconductor wafer (105);

20 an inline cascade metrology data storage unit (320) operatively coupled to said process controller (350), said inline cascade metrology data storage unit (320) to receive at least one of an inline pre-process metrology data and an inline post-process metrology data; and

25 a feedback/feed-forward unit (580) operatively coupled to said process controller (350) and said inline cascade metrology data storage unit (320), said feedback/feed-forward unit (580) to perform a feedback function in response to at least one of said inline pre-process metrology data and said inline post-process metrology data.

30 7. A computer readable program storage device encoded with instructions that, when executed by a computer, performs a method, comprising:

receiving a first semiconductor wafer (105) for processing;

receiving a second semiconductor wafer (105) for processing; and

35 performing a cascade processing operation upon said first and said second semiconductor wafers (105), wherein said cascade processing operation comprises acquiring pre-process metrology data related to said second semiconductor wafer (105) during at least a portion of a time period wherein said first semiconductor wafer (105) is being processed.

40

WO 03/038888

PCT/US02/25402

8. The computer readable program storage device encoded with instructions that, when executed by a computer, performs the method described in claim 7, the method further comprising acquiring post-process metrology data relating to said first semiconductor wafer (105) during at least a portion of a time period wherein said second semiconductor wafer (105) being processed.

5

9. The computer readable program storage device encoded with instructions that, when executed by a computer, performs the method described in claim 7, wherein acquiring pre-process metrology data further comprises acquiring pre-process metrology data using an integrated metrology tool (310).

10

10. The computer readable program storage device encoded with instructions that, when executed by a computer, performs the method described in claim 7, wherein performing a cascade processing operation upon said first and said second semiconductor wafer (105) further comprises:

acquiring pre-process metrology data from said first semiconductor wafer (105);

processing said first semiconductor wafer (105) in response to said acquiring said pre-process metrology data from said first semiconductor wafer (105);

acquiring pre-process metrology from said second semiconductor wafer (105) during at least a portion of a time period wherein said first semiconductor wafer (105) being processed;

20

acquiring post-process metrology data from said first semiconductor wafer (105) in response to said processing of said first semiconductor wafer (105);

processing said second semiconductor wafer (105) in response to said acquiring said pre-process metrology data from said second semiconductor wafer (105) during at least a portion of a time period wherein post-process metrology data related to said first semiconductor wafer (105) is acquired; and

25

acquiring post-process metrology data in response to said processing of said second semiconductor wafer (105).

WO 03/038888

PCT/US02/25402

1 / 11

FIGURE 1

WO 03/038888

PCT/US02/25402

FIGURE 2

WO 03/038888

PCT/US02/25402

3 / 11

FIGURE 3

WO 03/038888

PCT/US02/25402

4 / 11

FIGURE 4

WO 03/038888

PCT/US02/25402

5 / 11

FIGURE 5

WO 03/038888

PCT/US02/25402

FIGURE 6

FIGURE 7

**FIGURE 8**

WO 03/038888

PCT/US02/25402

FIGURE 9

FIGURE 10

WO 03/038888

PCT/US02/25402

11 / 11

FIGURE 11

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

8 May 2003 (08.05.2003)

PCT

(10) International Publication Number