(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7594058号**

**(P7594058)**

(45)発行日 令和6年12月3日(2024.12.3)

(24)登録日 令和6年11月25日(2024.11.25)

(51)国際特許分類

|        |                  |        |       |   |

|--------|------------------|--------|-------|---|

| H 01 L | 23/36 (2006.01)  | H 01 L | 23/36 | C |

| H 01 L | 23/373 (2006.01) | H 01 L | 23/36 | M |

| H 01 L | 25/07 (2006.01)  | H 01 L | 25/04 | C |

| H 01 L | 25/18 (2023.01)  | H 01 L | 25/14 | Z |

| H 01 L | 25/10 (2006.01)  | H 01 L | 23/12 | N |

請求項の数 20 外国語出願 (全17頁) 最終頁に続く

(21)出願番号 特願2023-120819(P2023-120819)

(22)出願日 令和5年7月25日(2023.7.25)

(65)公開番号 特開2024-19075(P2024-19075A)

(43)公開日 令和6年2月8日(2024.2.8)

審査請求日 令和6年8月20日(2024.8.20)

(31)優先権主張番号 17/874,462

(32)優先日 令和4年7月27日(2022.7.27)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73)特許権者 507342261

トヨタ モーター エンジニアリング ア

ンド マニュファクチャリング ノース

アメリカ、インコーポレイティド

アメリカ合衆国、75024 テキサス

州、ブレイノ、ダブリュ1-3シー・ヘ

ッドクオーターズ・ドライブ、6565

(74)代理人 100099759

弁理士 青木 篤

(74)代理人 100123582

弁理士 三橋 真二

(74)代理人 100092624

弁理士 鶴田 準一

(74)代理人 100147555

弁理士 伊藤 公一

最終頁に続く

(54)【発明の名称】 埋め込まれたパワーエレクトロニクスデバイスを有するパワーエレクトロニクスアセンブリ

**(57)【特許請求の範囲】****【請求項1】**

電気絶縁性の基材と、

前記基材に埋め込まれるパワーエレクトロニクスデバイスアセンブリであって、

内部グラファイト層と、前記内部グラファイト層を覆う金属層と、凹部を備える前記

金属層の第1表面と、を備えるSセルと、

前記第1表面の凹部内に配置されたパワーエレクトロニクスデバイスと、

を備える前記パワーエレクトロニクスデバイスアセンブリと、

を備える回路基板アセンブリを備える、

パワーエレクトロニクスアセンブリ。

**【請求項2】**

前記回路基板アセンブリは、前記基材に埋め込まれ、前記パワーエレクトロニクスデバ

イスに熱的に結合された複数のサーマルビアをさらに備える、

請求項1に記載のパワーエレクトロニクスアセンブリ。

**【請求項3】**

前記Sセルは、幅より長い長さを有する、

請求項1に記載のパワーエレクトロニクスアセンブリ。

**【請求項4】**

コールドプレートをさらに備え、

前記回路基板アセンブリは、接合層によって前記コールドプレートの表面に接合される、

請求項 1 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 5】**

前記接合層は、電気絶縁性である、

請求項 4 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 6】**

前記接合層は、RMS 接合層である、

請求項 4 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 7】**

前記 S セルは、前記金属層の第 2 表面に接合された金属化絶縁層をさらに含む、

請求項 1 に記載のパワーエレクトロニクスアセンブリ。

10

**【請求項 8】**

コールドプレートをさらに備え、

前記 S セルの前記金属化絶縁層は、前記回路基板アセンブリの表面に露出しており、

前記回路基板アセンブリは、前記 S セルの前記金属化絶縁層が前記コールドプレートの表面に接合される、

請求項 7 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 9】**

前記回路基板アセンブリは、RMS ボンディングによって前記 S セルの金属化絶縁層が前記コールドプレートの表面に接合される、

請求項 8 に記載のパワーエレクトロニクスアセンブリ。

20

**【請求項 10】**

前記 S セルは、前記金属化絶縁層に接合される第 2 金属層をさらに備える、

請求項 7 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 11】**

前記回路基板アセンブリは、前記第 2 金属層に熱的に結合された複数のサーマルビアをさらに備える、

請求項 10 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 12】**

前記 S セルは、

第 1 DBM 金属層と、

30

前記第 1 DBM 金属層に接合されるセラミック層と、

前記セラミック層に接合される第 2 DBM 金属層と、

を備える直接接合金屬基板を、さらに備える、

請求項 1 に記載のパワーエレクトロニクスアセンブリ。

**【請求項 13】**

コールドプレートをさらに備え、

前記第 2 DBM 金属層は、前記回路基板アセンブリの表面に露出しており、

前記回路基板アセンブリは、前記 S セルの前記第 2 DBM 金属層が前記コールドプレートの前記第 1 表面に接合される、

請求項 12 に記載のパワーエレクトロニクスアセンブリ。

40

**【請求項 14】**

電気絶縁性の基材と、

前記基材に埋め込まれた複数のパワーエレクトロニクスデバイスアセンブリであって、

内部グラファイト層と、前記内部グラファイト層を覆う金属層と、前記金属層の第 2 表面上に接合される絶縁層と、凹部を備える前記金属層の第 1 表面と、を備える S セルと、

前記第 1 表面の凹部内に配置されたパワーエレクトロニクスデバイスと、

を備える各パワーエレクトロニクスデバイスアセンブリと、

前記基材の表面上の表面金属層と、

前記 S セルを前記表面金属層に熱的に結合する複数のサーマルビアと、

を備える回路基板アセンブリと、

50

前記回路基板アセンブリの前記表面金属層がコールドプレートの第1表面に接合されている、コールドプレートと、

を備える、

パワーエレクトロニクスアセンブリ。

【請求項15】

前記Sセルは、幅より長い長さを有する、

請求項14に記載のパワーエレクトロニクスアセンブリ。

【請求項16】

前記絶縁層は、金属化絶縁層を備える、

請求項14に記載のパワーエレクトロニクスアセンブリ。

10

【請求項17】

前記絶縁層は、

第1DBM金属層と、

前記第1DBM金属層に接合されるセラミック層と、

前記セラミック層に接合される第2DBM金属層と、

を備える直接接合金屬基板を備える、

請求項14に記載のパワーエレクトロニクスアセンブリ。

【請求項18】

前記コールドプレートの前記第1表面とは反対側の第2表面に取り付けられたコンデンサ

をさらに備える、

20

請求項14に記載のパワーエレクトロニクスアセンブリ。

【請求項19】

前記コールドプレートは、流体室、流体入口、及び流体出口を備え、

前記流体入口及び前記流体出口は、前記流体室に熱的に結合される、

請求項14に記載のパワーエレクトロニクスアセンブリ。

【請求項20】

前記回路基板アセンブリは、締結具と熱グリース層によって前記コールドプレートの前記

第1表面に取り付けられる、

請求項14に記載のパワーエレクトロニクスアセンブリ。

30

【発明の詳細な説明】

【技術分野】

【0001】

本明細書は、一般に、パワーエレクトロニクスアセンブリに関し、より具体的には、コンパクトなパッケージサイズを実現しつつ、全体として低い熱抵抗を有するパワーエレクトロニクスアセンブリのための装置及び方法に関する。

【背景技術】

【0002】

自動車における電子機器の使用が増加しているため、電子システムをよりコンパクトにする必要がある。このような電子システムの構成要素の1つに、インバータ回路のスイッチとして使用されるパワーエレクトロニクスデバイスがある。パワーエレクトロニクスデバイスでは、大量の熱が発生するため、高い冷却要求がある。

40

【0003】

さらに、従来はシリコンで構成されていたパワーエレクトロニクスデバイスを現在は炭化ケイ素で構成する傾向がある。炭化ケイ素を使用すると、デバイスの設置面積が小さくなるため、熱流束が大きくなる。このような理由から、コンパクトなパッケージサイズを維持しながら、パワーエレクトロニクスデバイスの冷却を改善する必要性が生じている。

【発明の概要】

【0004】

或る実施形態では、パワーエレクトロニクスアセンブリは、電気絶縁性の基材と、基材に埋め込まれたパワーエレクトロニクスデバイスアセンブリと、を含む回路基板アセンブ

50

リを含む。パワーエレクトロニクスデバイスアセンブリは、内部グラファイト層と、内部グラファイト層を覆う金属層と、第1表面内に設けられた凹部を備える金属層の第1表面と、を含むSセル(S-cell)を含む。パワーエレクトロニクスデバイスアセンブリは、第1表面の凹部内に配置されたパワーエレクトロニクスデバイスをさらに含む。

#### 【0005】

別の実施形態では、パワーエレクトロニクスアセンブリは、回路基板アセンブリとコールドプレートとを含む。回路基板アセンブリは、電気絶縁性の基材と、基材に埋め込まれた複数のパワーエレクトロニクスデバイスアセンブリとを含む。各パワーエレクトロニクスデバイスアセンブリは、内部グラファイト層と、内部グラファイト層を覆う金属層と、金属層の第2表面に接合された絶縁層と、第1表面内に設けられた凹部を備える金属層の第1表面と、をさらに含むSセルを含む。パワーエレクトロニクスデバイスアセンブリは、第1表面の凹部内に配置されたパワーエレクトロニクスデバイスをさらに含む。回路基板アセンブリは、基材の表面上の表面金属層と、Sセルを表面金属層に熱的に結合する複数のサーマルビア(thermal via)と、をさらに含む。回路基板アセンブリの表面金属層は、コールドプレートの第1表面に接合されている。

10

#### 【0006】

本明細書で説明する実施形態によって提供されるこれらの特徴及び追加の特徴は、図面と併せて以下の詳細な説明を考慮することにより、より完全に理解されるであろう。

#### 【図面の簡単な説明】

#### 【0007】

図面に記載された実施形態は、本質的に例示的かつ説明的であり、特許請求の範囲によって定義される主題を限定することを意図するものではない。例示的な実施形態に関する以下の詳細な説明は、同様の構造が同様の参照番号で示され、以下の図面と併せて読むと理解することができる。

20

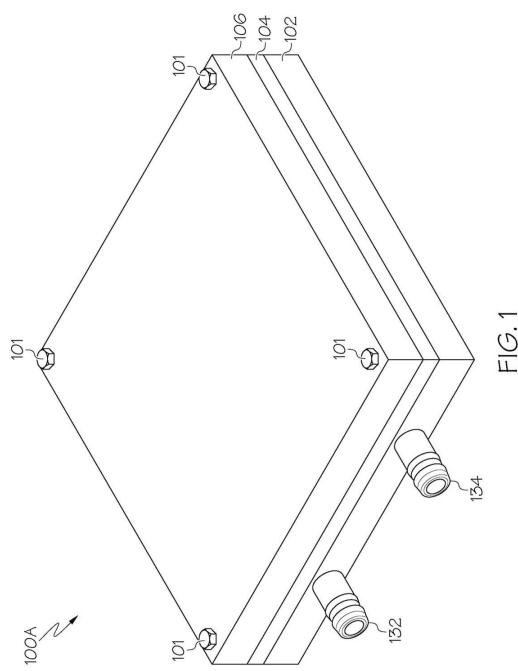

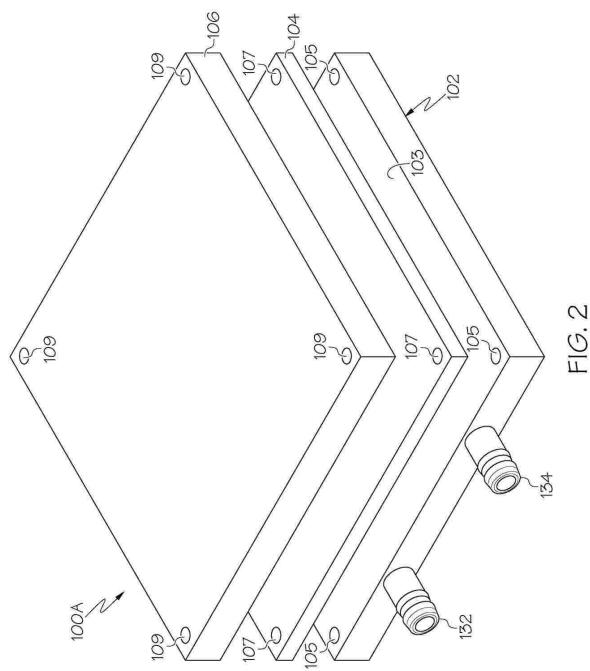

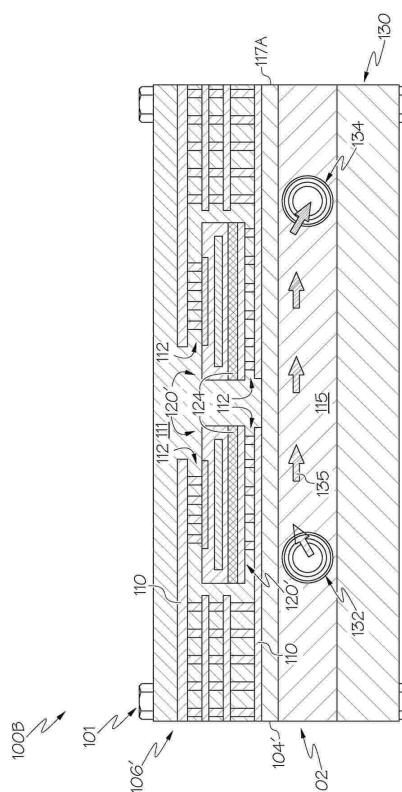

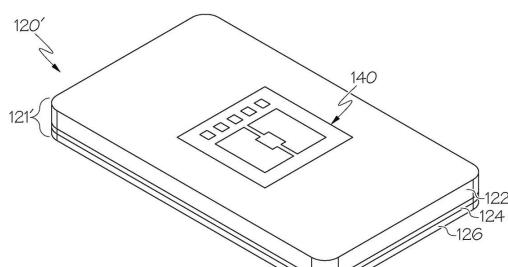

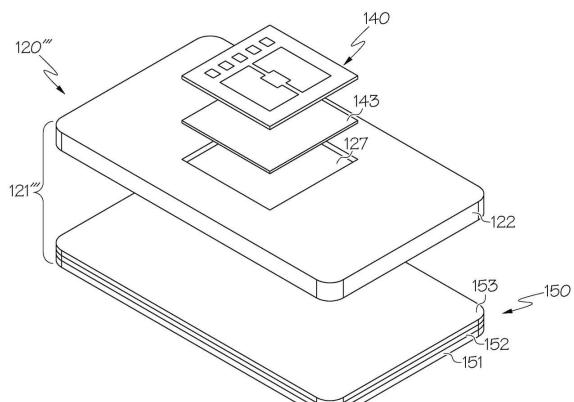

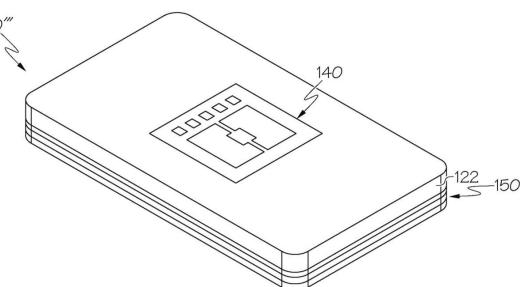

【図1】図1は、本明細書で説明及び図示される1つ又は複数の実施形態によるパワーエレクトロニクスアセンブリの概略斜視図である。

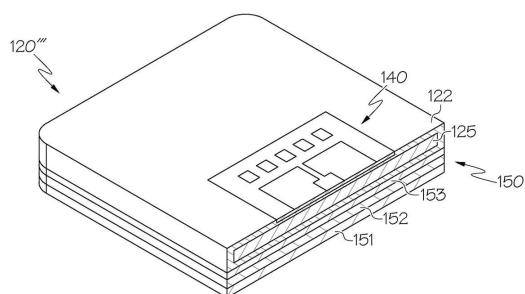

【図2】図2は、本明細書で説明及び図示される1つ又は複数の実施形態による、図1に図示された例示的なパワーエレクトロニクスアセンブリの概略分解斜視図である。

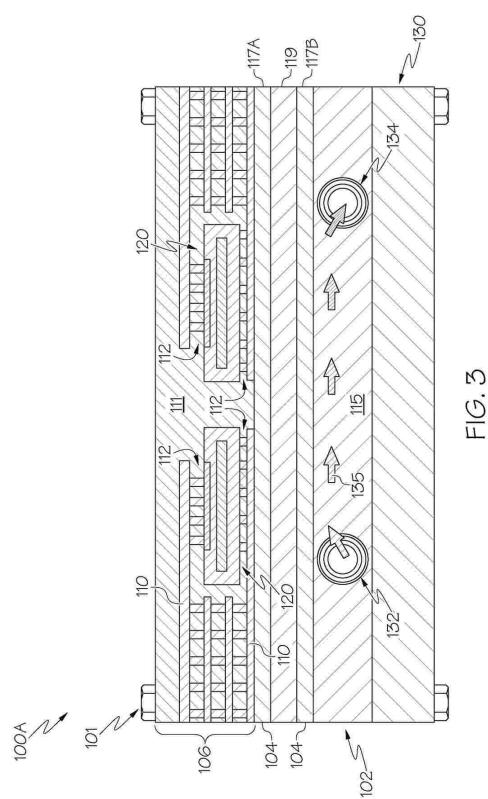

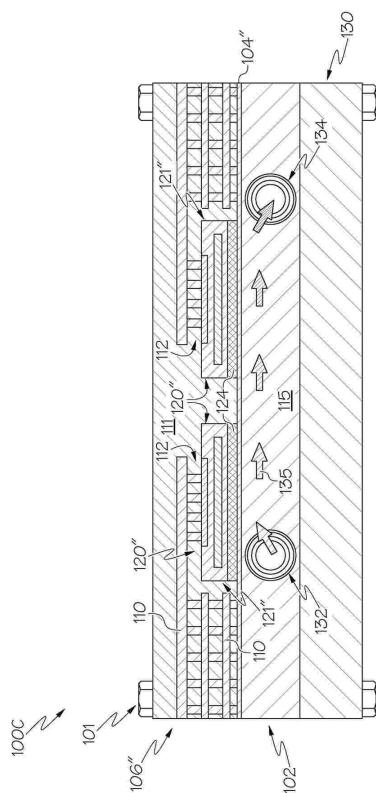

【図3】図3は、本明細書で説明及び図示される1つ又は複数の実施形態による例示的なパワーエレクトロニクスアセンブリの概略断面図である。

30

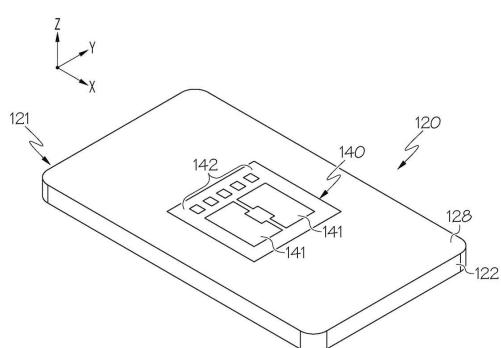

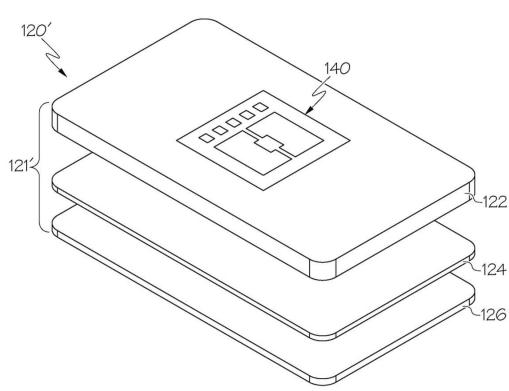

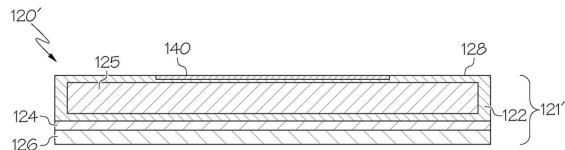

【図4】図4は、本明細書で説明及び図示される1つ又は複数の実施形態による例示的なSセルの概略上面斜視図である。

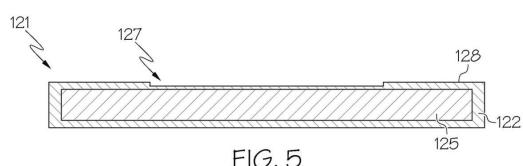

【図5】図5は、本明細書で説明及び図示される1つ又は複数の実施形態による例示的なSセルの概略断面図である。

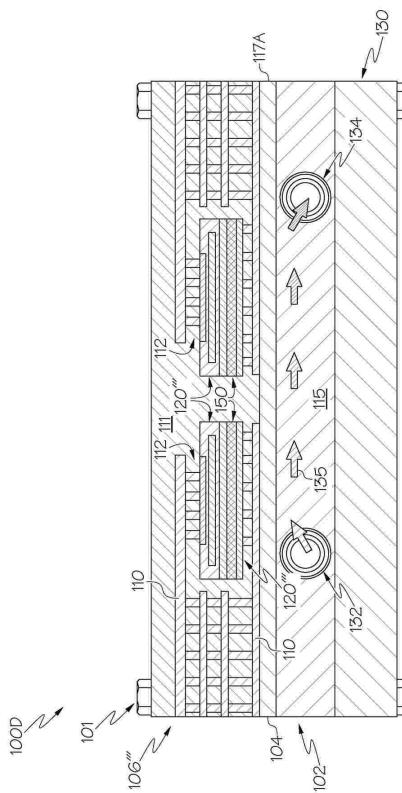

【図6】図6は、本明細書で説明及び図示される1つ又は複数の実施形態による別の例示的なパワーエレクトロニクスアセンブリの概略断面図である。

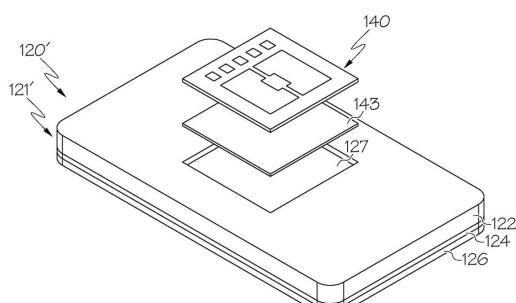

【図7】図7は、本明細書で説明及び図示される1つ又は複数の実施形態による、図6に図示されたパワーエレクトロニクスアセンブリの例示的なパワーエレクトロニクスデバイスアセンブリの概略部分分解図である。

40

【図8】図8は、本明細書で説明及び図示される1つ又は複数の実施形態による、図7に図示された例示的なパワーエレクトロニクスデバイスの別の概略部分分解図である。

【図9】図9は、本明細書で説明及び図示される1つ又は複数の実施形態による、図7に図示された例示的なパワーエレクトロニクスデバイスの概略斜視組立図である。

【図10】図10は、本明細書で説明及び図示される1つ又は複数の実施形態による、図7に図示された例示的なパワーエレクトロニクスデバイスの概略断面図である。

【図11】図11は、本明細書で説明及び図示される1つ又は複数の実施形態による別の例示的なパワーエレクトロニクスアセンブリの概略断面図である。

【図12】図12は、本明細書で説明及び図示される1つ又は複数の実施形態による別の例示的なパワーエレクトロニクスアセンブリの概略断面図である。

【図13】図13は、本明細書で説明及び図示される1つ又は複数の実施形態による、図

50

12に図示されたパワーエレクトロニクスアセンブリの例示的なパワーエレクトロニクスデバイスの概略部分分解図である。

【図14】図14は、本明細書で説明及び図示される1つ又は複数の実施形態による、図13に図示された例示的なパワーエレクトロニクスデバイスの概略斜視組立図である。

【図15】図15は、本明細書で説明及び図示される1つ又は複数の実施形態による、図13に図示された例示的なパワーエレクトロニクスデバイスの概略切断斜視図である。

#### 【発明を実施するための形態】

##### 【0008】

本明細書で説明する実施形態は、一般に、プリント回路基板などの回路基板に直接埋め込まれる1つ又は複数のパワーエレクトロニクスデバイスアセンブリを有するパワーエレクトロニクスアセンブリに向けられている。1つ又は複数のパワーエレクトロニクスデバイスアセンブリを回路基板に完全に埋め込むことによって、回路基板とパワーエレクトロニクスアセンブリのコールドプレート(cold plate)との間の放熱グリース層が除去され得る。放熱グリース層の除去により、パワーエレクトロニクスデバイスとコールドプレートとの間の熱抵抗が減少し、放熱性能が向上する。

10

##### 【0009】

本開示のパワーエレクトロニクスデバイスアセンブリは、本明細書においてSセルと呼ばれる実装基材(mounting substrate)に取り付けられるパワーエレクトロニクスデバイスを備える。以下に、より詳細に説明するように、Sセルは、熱拡散能力を強化するグラファイト層を含む。さらに、本開示の実施形態は、パワーエレクトロニクスデバイスをコールドプレートから電気的に絶縁する1つ又は複数の電気絶縁層を含む。例えば、Sセルの電気絶縁層は、電気絶縁がSセル自体によって提供されるため、プリント回路基板とコールドプレートとの間の電気絶縁層の除去を可能にする。

20

##### 【0010】

以下に、より詳細に説明するように、本開示のSセルは、コールドプレートに向かって熱流束の流れを促進するグラファイト層により、強化された放熱特性を提供する。

##### 【0011】

本明細書に記載のパワーエレクトロニクスデバイスアセンブリ、回路基板アセンブリ、及びパワーエレクトロニクスアセンブリは、電気自動車やハイブリッド電気自動車などの電動化車両、任意の電気モータ、発電機、産業用工具、家庭用電化製品などに使用することができるが、これらに限定されるものではない。本明細書に記載のパワーエレクトロニクスアセンブリは、電気モータ、及び/又はバッテリに電気的に結合され、直流(DC)電力を交流(AC)電力に変換するように動作可能なインバータ回路として構成され得る。

30

##### 【0012】

本明細書で使用する「パワーエレクトロニクスデバイス」とは、直流電力を交流電力に変換するために、及びその逆に変換するために使用されるあらゆる電気部品を意味する。実施形態は、AC-ACコンバータ、及びDC-DCコンバータの用途にも使用され得る。パワーエレクトロニクスデバイスの非限定的な例としては、金属酸化膜半導体電界効果トランジスタ(MOSFET)、絶縁ゲート型バイポーラトランジスタ(IGBT)、サイリスタ、及びパワートランジスタが挙げられる。

40

##### 【0013】

本明細書で使用される「完全に埋め込まれた」という表現は、部品の各表面が基材によって取り囲まれている(surrounded)ことを意味する。例えば、パワーエレクトロニクスデバイスアセンブリが回路基板基材(circuit board substrate)によって完全に埋め込まれている場合、回路基板基材の材料が回路基板基材の各表面を覆っていることを意味する。部品の1つ又は複数の表面が露出している場合、部品は「部分的に埋め込まれている」ことになる。

##### 【0014】

本明細書で使用する「Sセル」とは、パワーエレクトロニクスデバイスに固定されて動作可能な実装基材であり、グラファイト層を取り囲む少なくとも金属層(例えば、銅)を

50

含む。

#### 【 0 0 1 5 】

パワーエレクトロニクスデバイスアセンブリ、回路基板アセンブリ、及びパワーエレクトロニクスアセンブリの様々な実施形態を以下に詳細に説明する。可能な限り、同じ参照番号が、同じ又は同様の部品を参照するために図面全体を通して使用される。

#### 【 0 0 1 6 】

ここで図 1 及び図 2 を参照すると、例示的なパワーエレクトロニクスアセンブリ 100 が、それぞれ組立図及び分解図で図示されている。図 1 及び図 2 によって図示されるパワーエレクトロニクスアセンブリ 100 は、コールドプレート 102、接合層 104、及び回路基板アセンブリ 106 を含む。コールドプレート 102 は、回路基板アセンブリ 106 の基材材料 (substrate material) 内に埋め込まれたパワーエレクトロニクスデバイス 140 ( 例えは、図 3 を参照 ) から熱流束を除去することができる任意のデバイスとすることができる。コールドプレートの非限定的な例としては、ヒートシンク、単相液体冷却、二相液体冷却、ベイパーーチャンバー (vapor chamber) が挙げられる。図 1 及び図 2 は、単相液体冷却装置として構成されたコールドプレート 102 を図示している。コールドプレート 102 は、コールドプレート 102 内の流体室 115 に流体的に結合された流体入口 132 及び流体出口 134 を含む。図 3 を簡単に参照すると、リザーバ ( 図示せず ) からの冷却液 135 は、流体入口 132 を通って流体室 115 に流入し、流体出口 134 を通って流体室 115 から流出し、冷却液から熱を除去するための熱交換器 ( 図示せず ) を通った後などにリザーバに戻される。図示しないが、冷却液 135 への熱伝達のための追加表面積を提供するために、流体室 115 にフィンを配列してもよい。図 3 に示すように、冷たい冷却液 135 は流体入口 132 からコールドプレート 102 に流入し、流体室 115 を流れ、温められた冷却液として流体出口 134 から流出する。

10

20

30

#### 【 0 0 1 7 】

回路基板アセンブリ 106 は、コールドプレート 102 の第 1 表面 103 に取り付けられる。図 1 及び図 2 は、回路基板アセンブリ 106 が、コールドプレート 102 のスルーホール 105、接合層 104 のスルーホール 107、および回路基板アセンブリ 106 のスルーホールを介して配置された締結具 101 ( 例えは、ボルト及びナット ) によって、コールドプレート 102 の第 1 表面 103 に取り付けられている状態を示している。締結具 101 が使用される場合、接合層 104 は、回路基板アセンブリ 106 とコールドプレート 102 との間の熱抵抗を低下させるための放熱グリース層としてもよい。

30

#### 【 0 0 1 8 】

他の実施形態では、回路基板アセンブリ 106 は、はんだ層として構成された接合層 104 によってコールドプレート 102 の第 1 表面 103 に取り付けられる。例えは、回路基板アセンブリ 106 の底面は、回路基板アセンブリ 106 がはんだ層によってコールドプレート 102 の第 1 表面 103 に取り付けられることを可能にする金属層を含むことができる。他の接合方法を利用してもよいことを理解されたい。

#### 【 0 0 1 9 】

次に図 3 を参照すると、例示的なパワーエレクトロニクスアセンブリ 100A の断面図が図示されている。図示された実施形態では、追加の電気部品 130 がコールドプレート 102 の第 2 表面に取り付けられている。非限定的な例として、追加の電気部品 130 は、例えは、インバータ回路のコンデンサとすることができます。他の実施形態では、追加の電気部品 130 は、コールドプレート 102 に取り付けられていなくてもよいことを理解されたい。

40

#### 【 0 0 2 0 】

回路基板アセンブリ 106 は、電気絶縁材料で作られた基材 (substrate) 111 を備える。電気絶縁材料は、限定するものではないが、FR-4 などのプリント回路基板の製造に使用される材料とすることができる。回路基板アセンブリ 106 は、埋め込まれた金属層 110 ( 又は他の導電層 )、複数のビア 112 ( 例えは、導電ビアとサーマルビアとの両方 )、及び複数のパワーエレクトロニクスデバイスアセンブリ 120 をさらに備える。

50

**【 0 0 2 1 】**

非限定的な例として、回路基板アセンブリ 106 は、電気自動車用のインバータ回路のための 6 つのパワーエレクトロニクスデバイスアセンブリ 120 を含むことができる。しかしながら、用途に応じて任意の数のパワーエレクトロニクスデバイスアセンブリを利用することができますを理解されたい。

**【 0 0 2 2 】**

各パワーエレクトロニクスデバイスアセンブリ 120 は、S セル 121 と、S セル 121 に取り付けられたパワーエレクトロニクスデバイス 140 と、を含む。上述のように、S セル 121 は、パワーエレクトロニクスデバイス 140 が取り付けられる基材である。これは、パワーエレクトロニクスデバイス 140 の底面の電極に接続するための導電性表面を提供する。S セル 121 はさらに、熱拡散機能を提供する。

10

**【 0 0 2 3 】**

図 4 及び図 5 は、それぞれ、例示的な S セル 121 を示す上面斜視図及び断面図である。図 4 及び図 5 によって図示される S セル 121 は、金属層 122 によって封止される内部グラファイト層 125 を含む。金属層 122 は、パワーエレクトロニクスデバイス 140 を受容する寸法を有する凹部 (recess) 127 を有する表面 128 を含む。以下により詳細に説明するように、金属層 122 は、パワーエレクトロニクスデバイス 140 の底面上の電極に電気的接続を行うために導電性ビアが接触し得る導電性表面 128 を提供する。凹部 127 は、例えば化学エッティングによって形成することができる。

**【 0 0 2 4 】**

金属層 122 は、任意の適切な金属または合金で作ることができる。非限定的な例として、銅及びアルミニウムを金属層 122 として使用することができる。

20

**【 0 0 2 5 】**

グラファイト層 125 は、S セル 121 を横切る熱とコールドプレート 102 に向かう熱の両方の拡散を促すために設けられている。グラファイトの結晶構造は、高い熱伝導率を提供し、コールドプレート 102 に向かって熱流束を伝導するのに有用である。しかしながら、グラファイトは、等温プロファイルを持たない。むしろ、グラファイトは、2 つの軸に沿って高い熱伝導率を有し、第 3 の軸では低い熱伝導率を有する非等温プロファイルを持つ。グラファイトの非等温プロファイルを考慮するため、S セル 121 は、その長さ寸法が幅寸法よりも大きくなるような長方形の形状に設計されている。図 4 を参照すると、グラファイト層 125 は、X 軸及び Z 軸に沿って高い熱伝導率を有する。したがって、S セル 121 は、X 軸に沿った長さ寸法が Y 軸に沿った幅寸法よりも大きくなるように設計される。熱流束は X 軸及び Z 軸に沿って優先的に移動する。以下により詳細に説明するように、サーマルビア 112 は、熱流束を受け、それをコールドプレート 102 に向かって移動させるために、X 軸に沿った S セルの縁部に設けることができる。熱流束はまた、Z 軸に沿ってコールドプレート 102 に向かって移動する。

30

**【 0 0 2 6 】**

再び図 3 を参照すると、複数の電極 141, 142、及び金属層 122 への電気的接続は、複数のビア 112 によって行われる場合がある。これらのビアは、パワーエレクトロニクスデバイス 140 に駆動信号を提供するとともに、スイッチング電流のための電流経路を提供することができる。いくつかの実施形態において、ビア 112 のいくつかは、駆動信号又はスイッチング電流を伝達しないサーマルビアとして構成されてもよいことに留意されたい。

40

**【 0 0 2 7 】**

回路基板アセンブリ 106 は、接合層 104 によってコールドプレート 102 に接合される。図 3 によって示される実施形態では、接合層 104 は、回路基板アセンブリ 106 とコールドプレート 102 との間の機械的接合と、回路基板アセンブリ 106 とコールドプレート 102 との間の電気的絶縁と、の両方を提供する。図 3 の接合層 104 は、電気絶縁特性を有する反応性多層システム (RMS; reactive multilayer system) 接合層である。RMS ボンディングプロセスでは、金属箔や電気絶縁材料箔などの箔の積層を点

50

火火花によって反応状態にし、金属間結合を引き起こす反応を生じさせる。反応した R M S 接合層は、金属底面（例えば、露出した金属層 110 の形態）を有する回路基板アセンブリ 106 を、同じく金属（例えば、アルミニウム又は銅）であるコールドプレート 102 に接合する。いくつかの実施形態では、第 1 の金属層 117A が回路基板アセンブリ 106 上に設けられ、第 2 の金属層 117B がコールドプレート 102 上に設けられて、接合を強化する。例えば、第 1 及び第 2 の金属層 117A, 117B はそれぞれ、はんだ層、又はろう付け層であってもよい。

#### 【 0 0 2 8 】

R M S 接合層 104 は、優れた熱特性を提供し、それにより、熱流束がパワーエレクトロニクスデバイス 140 からコールドプレート 102 へ移動することを可能にするとともに、電気的絶縁を提供する。回路基板アセンブリ 106 をコールドプレート 102 に接合するだけでなく電気絶縁も提供する接合層 104 を設けることにより、別個の専用の電気絶縁層は不要となる。これにより、パワーエレクトロニクスアセンブリ 100A のパッケージ全体のサイズが小さくなる。パワーエレクトロニクスアセンブリ 100A のパッケージ全体のサイズは、回路基板アセンブリ 106 の内部にパワーエレクトロニクスデバイスアセンブリ 120 を埋め込むことによって、さらに小さくなる。

#### 【 0 0 2 9 】

次に図 6 を参照すると、別のパワーエレクトロニクスデバイスアセンブリ 100B が図示されている。図 1 - 3 に描かれているように接合層によって電気的絶縁を提供するのではなく、回路基板アセンブリ 106' とコールドプレート 102 との間の電気的絶縁は、1 つ又は複数のパワーエレクトロニクスデバイスアセンブリ 120' の S セル 121' の金属化絶縁層 (metallized insulation layer) 124 によって提供される。

#### 【 0 0 3 0 】

図 6 によって示される実施形態の接合層 104' は、限定するものではないが、はんだ層、ろう付け層、又は R M S 接合層などの任意の接合層として構成することができる。1 つ以上の露出した金属層 110（例えば、銅層）は、接合層 104' が接合される回路基板アセンブリ 106' の金属表面を提供する。いくつかの実施形態では、アセンブリ 100B が締結具 101 によって一緒に保持されるので、接合層 104' は熱グリース層であってもよい。サーマルビア 112 は、パワーエレクトロニクスデバイスアセンブリ 120' の底部から回路基板アセンブリ 106' の底部に向かって延び、パワーエレクトロニクスデバイス 140 によって発生する熱流束のための熱経路を提供する。

#### 【 0 0 3 1 】

図 7 及び図 8 は、図 6 の例示的なパワーエレクトロニクスデバイスアセンブリ 120' の部分分解図であり、図 9 は、例示的なパワーエレクトロニクスデバイスアセンブリ 120' の上面斜視図であり、図 10 は、例示的なパワーエレクトロニクスデバイスアセンブリ 120' の断面図である。パワーエレクトロニクスデバイスアセンブリ 120' は、S セル 121' に取り付けられたパワーエレクトロニクスデバイス 140 を含む。図 7 - 10 を全体的に参照すると、S セル 121' は、銅層などの金属層 122 によって封止された内部グラファイト層 125 を備える。金属層 122 は、パワーエレクトロニクスデバイス 140 を受容する寸法を有する凹部 127 を有する表面 128 を含む。上述したように、グラファイト層 125 は熱特性を向上させる。

#### 【 0 0 3 2 】

図 7 は、凹部 127 に対するパワーエレクトロニクスデバイス 140 及び接合層 143 を示す。パワーエレクトロニクスデバイス 140 を金属層 122 に固定する接合層 143 は、例えば、はんだ層であってもよい。別の例として、接合層 143 は、液相拡散接合層 (transient liquid phase bond layer) 143 であってもよい。パワーエレクトロニクスデバイス 140 は、その上面に複数の電極 141, 142 を含む。大きい電極 141 は電源電極であってもよく、小さい電極 142 は信号電極であってもよい。図 7 - 10 では見えないが、パワーエレクトロニクスデバイス 140 は、その底面に 1 つ以上の電極をさらに含むことに留意されたい。パワーエレクトロニクスデバイスの底面上の 1 つ以上の電

10

20

30

40

50

極は、凹部 127 にパワーエレクトロニクスデバイス 140 を配置することによって、第 2 金属層 126 に電気的に接続される。このように、パワーエレクトロニクスデバイス 140 の底面電極への電気的接続は、第 2 金属層 126 を経由して行うことができる。

#### 【0033】

S セル 121' は、金属層 122 とコールドプレート 102 との間に電気的絶縁を提供する金属化絶縁層 124 をさらに備える。金属化絶縁層 124 は、金属層 122 に接着できるように金属化 (metallize) されている。金属化絶縁層 124 は、限定するものではないが、セラミック材料などの任意の電気絶縁材料から作られてもよい。非限定的な例として、金属化絶縁層 124 は金属化アルミナであってもよい。金属化絶縁層 124 の絶縁材料の金属化により、それを接合することが可能になる。金属化絶縁層 124 の主要面は金属化されるべきであるが、側縁 (side edge) は電気的短絡を防止するために金属化されるべきではないことに留意されたい。10

#### 【0034】

例示的な S セル 121' は、金属化絶縁層 124 に接合される第 2 金属層 126 をさらに備える。金属化絶縁層 124 は、任意の接合技術によって金属層 122 及び第 2 金属層 126 に接合することができる。第 2 金属層 126 は、図 6 に示されるようにサーマルビア 112 が熱流束を底部金属層 110、ひいてはコールドプレート 102 に向かって移動させるための熱接続点を提供するように、追加の熱拡散を提供する。例えば、S セル 121' の第 2 金属層 126 に接触するように示されるビア 112 は、コールドプレート 102 に近い底部層に向かって熱流束を伝導するように設けられた熱伝導専用ビアであってもよい。さらに、サーマルビア 112 は、金属層 122 からコールドプレート 102 に向かって熱流束を下に移動させるために、金属層 122 の上面の端部に電気的に結合されてもよい。このようにして、熱流束はパワーエレクトロニクスデバイス 140 から離れ、コールドプレート 102 に向かって最適に誘導される。20

#### 【0035】

図 11 は、パワーエレクトロニクスデバイスアセンブリ 120'' の S セル 121'' が第 2 金属層を含まないことを除いて、図 6 のものと同様のパワーエレクトロニクスデバイスアセンブリ 110C を示す。むしろ、各 S セル 121'' の金属化絶縁層 124 は、回路基板アセンブリ 106'' の基材 111 材料によって露出される。金属化絶縁層 124 の露出は、回路基板アセンブリ 106'' が、介在する層によってではなく、金属化絶縁層 124 においてコールドプレート 102 の表面に直接接着される能力を提供する。例えば、回路基板アセンブリ 106'' は、1 つ以上の金属層 110 及び金属化絶縁層 124 をコールドプレート 102 の表面に接合する接合層 104'' (例えば、はんだ層) によって接着することができる。これは、パワーエレクトロニクスデバイスアセンブリ 110C のサイズを縮小することができるので、アドバンテージとなり得る。30

#### 【0036】

図 12 は、図 6 に図示されたパワーエレクトロニクスアセンブリ 100B と同様のパワーエレクトロニクスアセンブリ 100D を図示する。電気的絶縁が金属化絶縁層 124 によって提供されるのではなく、パワーエレクトロニクスアセンブリ 100D の電気的絶縁は、パワーエレクトロニクスデバイスアセンブリ 120''' の S セル 121''' の直接接合金属基板 (direct-bonded-metal substrate) 150 層によって提供される。40

#### 【0037】

図 13 は、接合層 143 によって S セル 121''' の凹部 127 に貼り付けられたパワーエレクトロニクスデバイス 140 からなる例示的なパワーエレクトロニクスデバイスアセンブリ 120''' の部分分解図を示す。図 14 は、パワーエレクトロニクスデバイスアセンブリ 120''' の斜視組立図である。図 15 は、パワーエレクトロニクスデバイスアセンブリ 120''' の切断斜視図である。図 13 - 15 を参照すると、例示的な S セル 121''' は、金属層 122 によって封止されたグラファイト層 125 を含む。S セル 121''' は、金属層 122 の底面に接合される直接接合金属 (DBM; direct-bonded-metal) 基板 150 をさらに含む。DBM 基板 150 は、例えば、直接接合銅 (DBC) 基板であってもよ50

い。DBM基板150は、アルミナなどのセラミック材料であってもよい絶縁層152を有する。DBM基板150はまた、絶縁層152（例えばセラミック層）の第1表面に直接接合された第1DBM金属層151と、絶縁層152の第2表面に直接接合された第2DBM金属層153と、を有する。

#### 【0038】

第2DBM金属層153は、銅であってもよく、金属層122の底面に接合されている。絶縁層152は、パワーエレクトロニクスデバイスに電気絶縁を提供する。

#### 【0039】

再び図12を参照すると、複数のサーマルピア112が第1DBM層151に接触し、Sセル121<sup>'''</sup>からの熱流束を回路基板アセンブリ106<sup>'''</sup>の底部にもたらすために底部金属層110に向かって伸びている。次いで、回路基板アセンブリ106<sup>'''</sup>は、露出した金属層110において、例えばはんだ層であってもよい接合層104によってコールドプレート102の表面に接合されてもよい。

10

#### 【0040】

図11のパワーエレクトロニクスアセンブリと同様に、いくつかの実施形態では、第1DBM層151は、回路基板アセンブリ106<sup>'''</sup>の基材111材料によって露出されてもよい。そのような実施形態では、回路基板アセンブリ106<sup>'''</sup>は、介在する金属層ではなく、第1DBM層151においてコールドプレート102の表面に接合されてもよい。

20

#### 【0041】

ここで、本開示の実施形態は、回路基板基材内に完全に埋め込まれたSセルを含む回路基板アセンブリ、パワーエレクトロニクスデバイスアセンブリ、及びパワーエレクトロニクスアセンブリに向けられていることを理解されたい。本明細書に記載の実施形態のSセルは、熱性能を向上させるために、封止されたグラファイト層を含む。電気的絶縁は、Sセルの構成要素を電気的に絶縁することによって提供することができる。パワーエレクトロニクスデバイスアセンブリを回路基板に直接埋め込むとともに、回路基板とコールドプレートとの間の個別の電気絶縁層を除去することにより、パワーエレクトロニクスアセンブリの全体的なサイズが大幅に縮小され、同時に熱性能も向上する。

20

#### 【0042】

本明細書において、「実質的」及び「約」という用語は、任意の定量的な比較、値、測定、又は他の表現に起因し得る、内在する不確実性の程度を表すために利用され得ることに留意されたい。これらの用語はまた、本明細書において、定量的な表現が、問題となる主題の基本的な機能の変化をもたらすことなく、述べられた基準から変わり得る程度を表すために利用される。

30

#### 【0043】

特定の実施形態が本明細書で図示及び記載されているが、様々な他の変更及び修正が、請求された主題の趣旨及び範囲から逸脱することなく行われ得ることを理解されたい。更に、請求された主題の様々な態様が本明細書に記載されているが、このような態様は、組み合わされて利用される必要はない。したがって、添付の特許請求の範囲は、請求された主題の範囲内にある全てのこののような変更及び修正を包含することが意図される。

30

#### 【0044】

特許請求の主題の精神及び範囲から逸脱することなく、本明細書に記載された実施形態に様々な修正及び変更がなされ得ることは、当業者にとって明らかであろう。したがって、本明細書は、そのような修正及び変更が添付の特許請求の範囲及びその等価物の範囲内に入ることを条件として、本明細書に記載の様々な実施形態の修正及び変更を網羅することが意図される。

40

本明細書に開示される発明は以下の態様を含む。

<態様1>

電気絶縁性の基材と、

前記基材に埋め込まれるパワーエレクトロニクスデバイスアセンブリであって、

内部グラファイト層と、前記内部グラファイト層を覆う金属層と、凹部を備える前記金属

50

層の第1表面と、を備えるSセルと、

前記第1表面の凹部内に配置されたパワーエレクトロニクスデバイスと、

を備える前記パワーエレクトロニクスデバイスアセンブリと、

を備える回路基板アセンブリを備える、

パワーエレクトロニクスアセンブリ。

< 様様 2 >

前記回路基板アセンブリは、前記基材に埋め込まれ、前記パワーエレクトロニクスデバイスに熱的に結合された複数のサーマルピアをさらに備える、

態様1に記載のパワーエレクトロニクスアセンブリ。

< 様様 3 >

10

前記Sセルは、幅より長い長さを有する、

態様1に記載のパワーエレクトロニクスアセンブリ。

< 様様 4 >

コールドプレートをさらに備え、

前記回路基板アセンブリは、接合層によって前記コールドプレートの表面に接合される、

態様1に記載のパワーエレクトロニクスアセンブリ。

< 様様 5 >

前記接合層は、電気絶縁性である、

請求項4に記載のパワーエレクトロニクスアセンブリ。

< 様様 6 >

20

前記接合層は、RMS接合層である、

態様4に記載のパワーエレクトロニクスアセンブリ。

< 様様 7 >

前記Sセルは、前記金属層の第2表面に接合された金属化絶縁層をさらに含む、

態様1に記載のパワーエレクトロニクスアセンブリ。

< 様様 8 >

コールドプレートをさらに備え、

前記Sセルの前記金属化絶縁層は、前記回路基板アセンブリの表面に露出しており、

前記回路基板アセンブリは、前記Sセルの前記金属化絶縁層が前記コールドプレートの表面に接合される、

30

態様7に記載のパワーエレクトロニクスアセンブリ。

< 様様 9 >

前記回路基板アセンブリは、RMSボンディングによって前記Sセルの金属化絶縁層が前記コールドプレートの表面に接合される、

態様8に記載のパワーエレクトロニクスアセンブリ。

< 様様 10 >

前記Sセルは、前記金属化絶縁層に接合される第2金属層をさらに備える、

態様7に記載のパワーエレクトロニクスアセンブリ。

< 様様 11 >

前記回路基板アセンブリは、前記第2金属層に熱的に結合された複数のサーマルピアをさらに備える、

40

態様10に記載のパワーエレクトロニクスアセンブリ。

< 様様 12 >

前記Sセルは、

第1DBM金属層と、

前記第1DBM金属層に接合されるセラミック層と、

前記セラミック層に接合される第2DBM金属層と、

を備える直接接合金屬基板を、さらに備える、

態様1に記載のパワーエレクトロニクスアセンブリ。

< 様様 13 >

50

コールドプレートをさらに備え、

前記第2DBM金属層は、前記回路基板アセンブリの表面に露出しており、

前記回路基板アセンブリは、前記Sセルの前記第2DBM金属層が前記コールドプレートの前記第1表面上に接合される。

態様12に記載のパワーエレクトロニクスアセンブリ。

< 態様14 >

電気絶縁性の基材と、

前記基材に埋め込まれた複数のパワーエレクトロニクスデバイスアセンブリであって、内部グラファイト層と、前記内部グラファイト層を覆う金属層と、前記金属層の第2表面に接合される絶縁層と、凹部を備える前記金属層の第1表面と、を備えるSセルと、

10

前記第1表面の凹部内に配置されたパワーエレクトロニクスデバイスと、

を備える各パワーエレクトロニクスデバイスアセンブリと、

前記基材の表面上の表面金属層と、

前記Sセルを前記表面金属層に熱的に結合する複数のサーマルビアと、

を備える回路基板アセンブリと、

前記回路基板アセンブリの前記表面金属層がコールドプレートの第1表面上に接合されている、コールドプレートと、

を備える、

パワーエレクトロニクスアセンブリ。

< 態様15 >

20

前記Sセルは、幅より長い長さを有する、

態様14に記載のパワーエレクトロニクスアセンブリ。

< 態様16 >

前記絶縁層は、金属化絶縁層を備える、

態様14に記載のパワーエレクトロニクスアセンブリ。

< 態様17 >

前記絶縁層は、

第1DBM金属層と、

前記第1DBM金属層に接合されるセラミック層と、

前記セラミック層に接合される第2DBM金属層と、

を備える直接接合金属基板を備える、

30

態様14に記載のパワーエレクトロニクスアセンブリ。

< 態様18 >

前記コールドプレートの前記第1表面とは反対側の第2表面上に取り付けられたコンデンサをさらに備える、

態様14に記載のパワーエレクトロニクスアセンブリ。

< 態様19 >

前記コールドプレートは、流体室、流体入口、及び流体出口を備え、

前記流体入口及び前記流体出口は、前記流体室に熱的に結合される、

態様14に記載のパワーエレクトロニクスアセンブリ。

40

< 態様20 >

前記回路基板アセンブリは、締結具と熱グリース層によって前記コールドプレートの前記第1表面上に取り付けられる、

態様14に記載のパワーエレクトロニクスアセンブリ。

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

FIG. 5

【図 6】

FIG. 6

10

20

30

【図 7】

FIG. 7

【図 8】

FIG. 8

40

50

【図 9】

FIG. 9

【図 10】

FIG. 10

10

【図 11】

FIG. 11

【図 12】

FIG. 12

20

30

40

50

【図 1 3】

FIG. 13

【図 1 4】

FIG. 14

10

【図 1 5】

FIG. 15

20

30

40

50

## フロントページの続き

## (51)国際特許分類

|        | F I             |        |      |

|--------|-----------------|--------|------|

| H 01 L | 25/11 (2006.01) | H 05 K | 1/02 |

| H 01 L | 23/12 (2006.01) | H 05 K | 1/02 |

| H 05 K | 1/02 (2006.01)  | H 05 K | 3/46 |

| H 05 K | 3/46 (2006.01)  | H 05 K | 7/20 |

| H 05 K | 7/20 (2006.01)  |        | N    |

(74)代理人 100123593

弁理士 関根 宣夫

(74)代理人 100133835

弁理士 河野 努

(74)代理人 100167461

弁理士 上木 亮平

(72)発明者 フォン チョウ

アメリカ合衆国, ミシガン 48105, アナーバー, アッシュコンブ ドライブ 2794

(72)発明者 諸川 紘嗣

アメリカ合衆国, ミシガン 48178, サウス ライオン, ウィノーイング サークル サウス 5

8575

審査官 栗栖 正和

(56)参考文献 米国特許出願公開第2021/0210477(US, A1)

特開2018-022792(JP, A)

特開昭52-135678(JP, A)

米国特許出願公開第2012/0152510(US, A1)

米国特許出願公開第2016/0209133(US, A1)

米国特許出願公開第2008/0286602(US, A1)

米国特許第5100737(US, A)

(58)調査した分野 (Int.Cl., DB名)

H 01 L 23 / 36

H 01 L 23 / 373

H 01 L 25 / 07

H 01 L 25 / 10

H 01 L 23 / 12

H 05 K 1 / 02

H 05 K 3 / 46

H 05 K 7 / 20